Patents

Literature

126results about How to "Improve process uniformity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

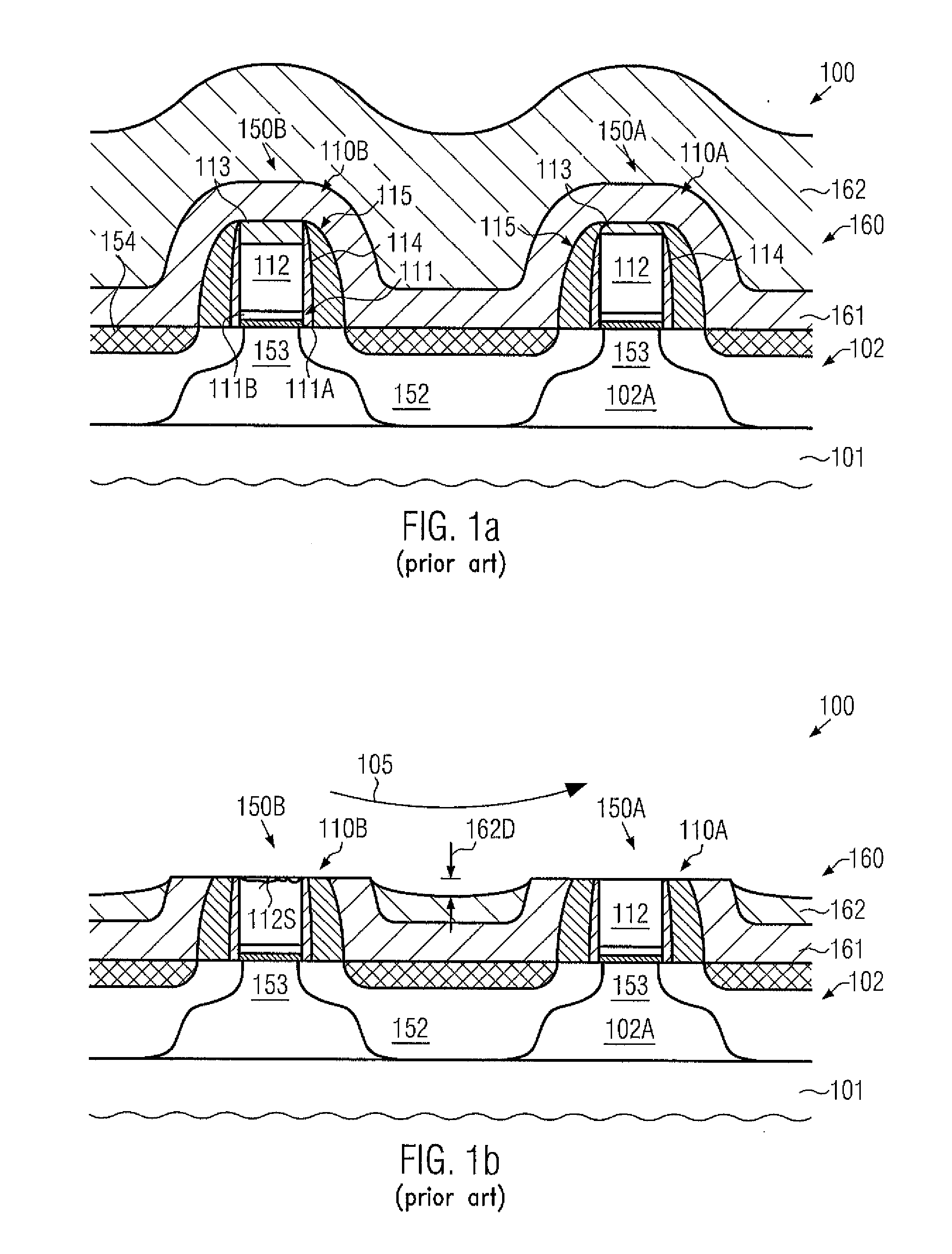

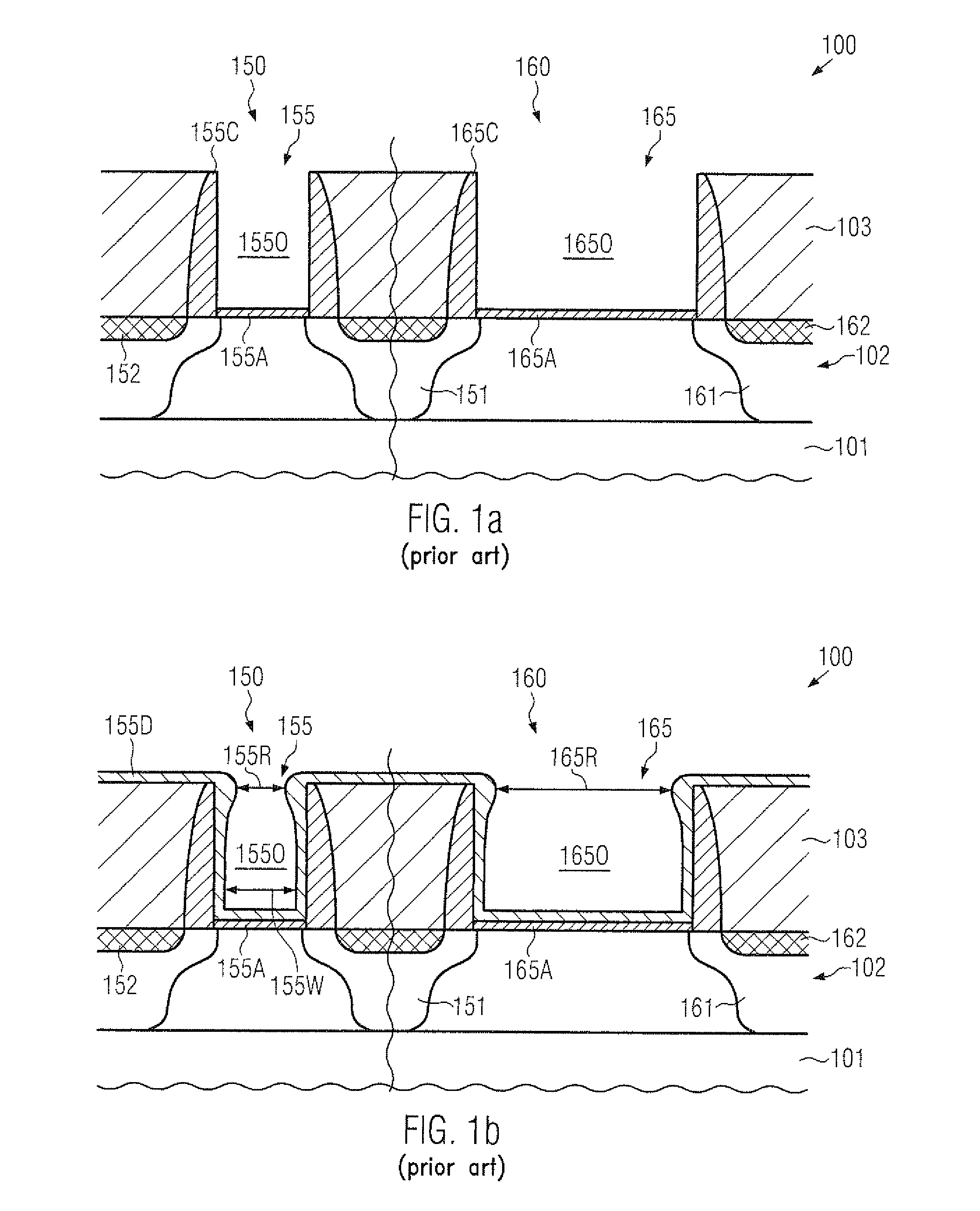

Technique for forming recessed strained drain/source regions in NMOS and PMOS transistors

ActiveUS20070045729A1High carrier mobilityIncrease flexibilityTransistorSolid-state devicesFloating body effectEngineering

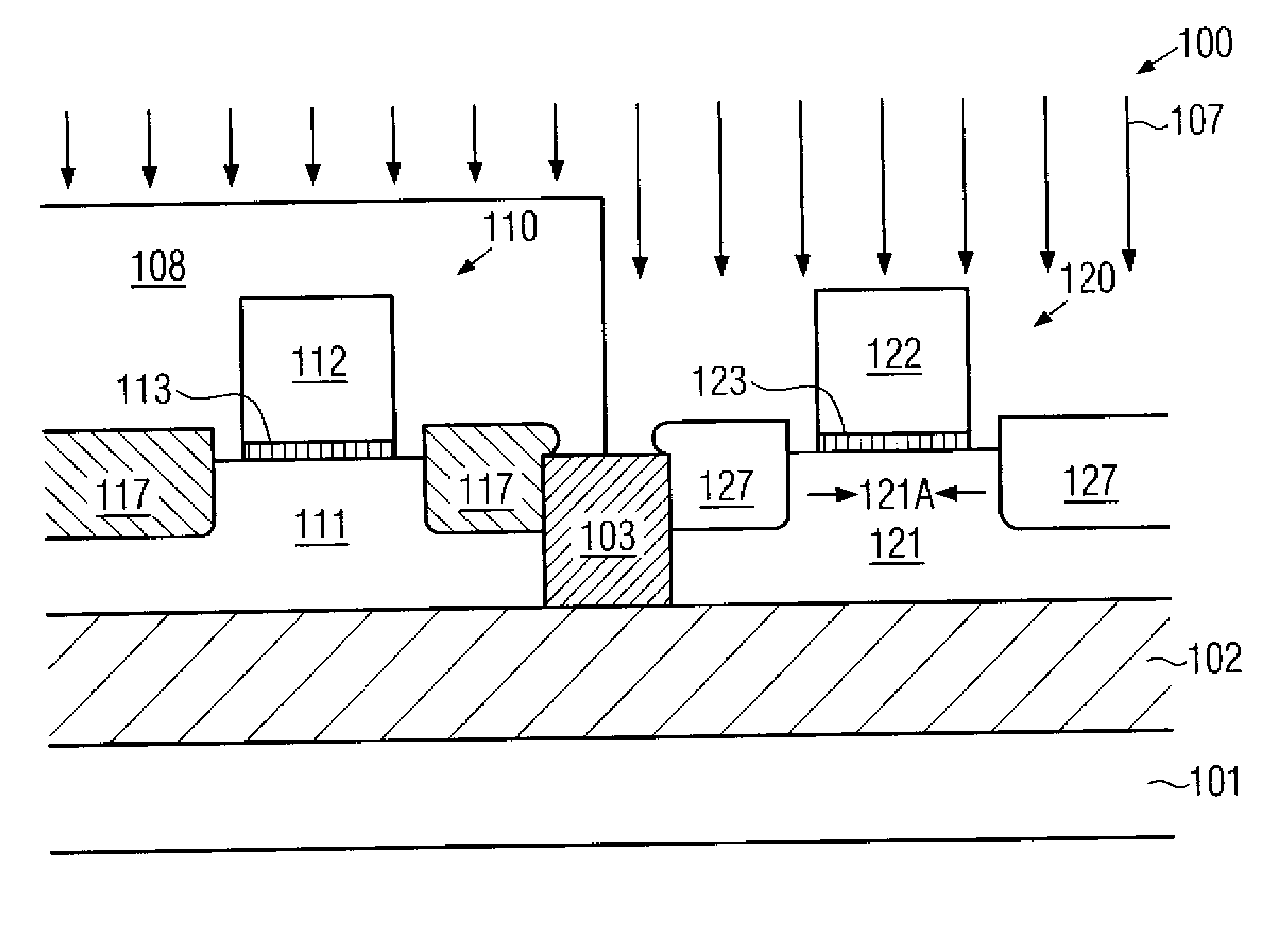

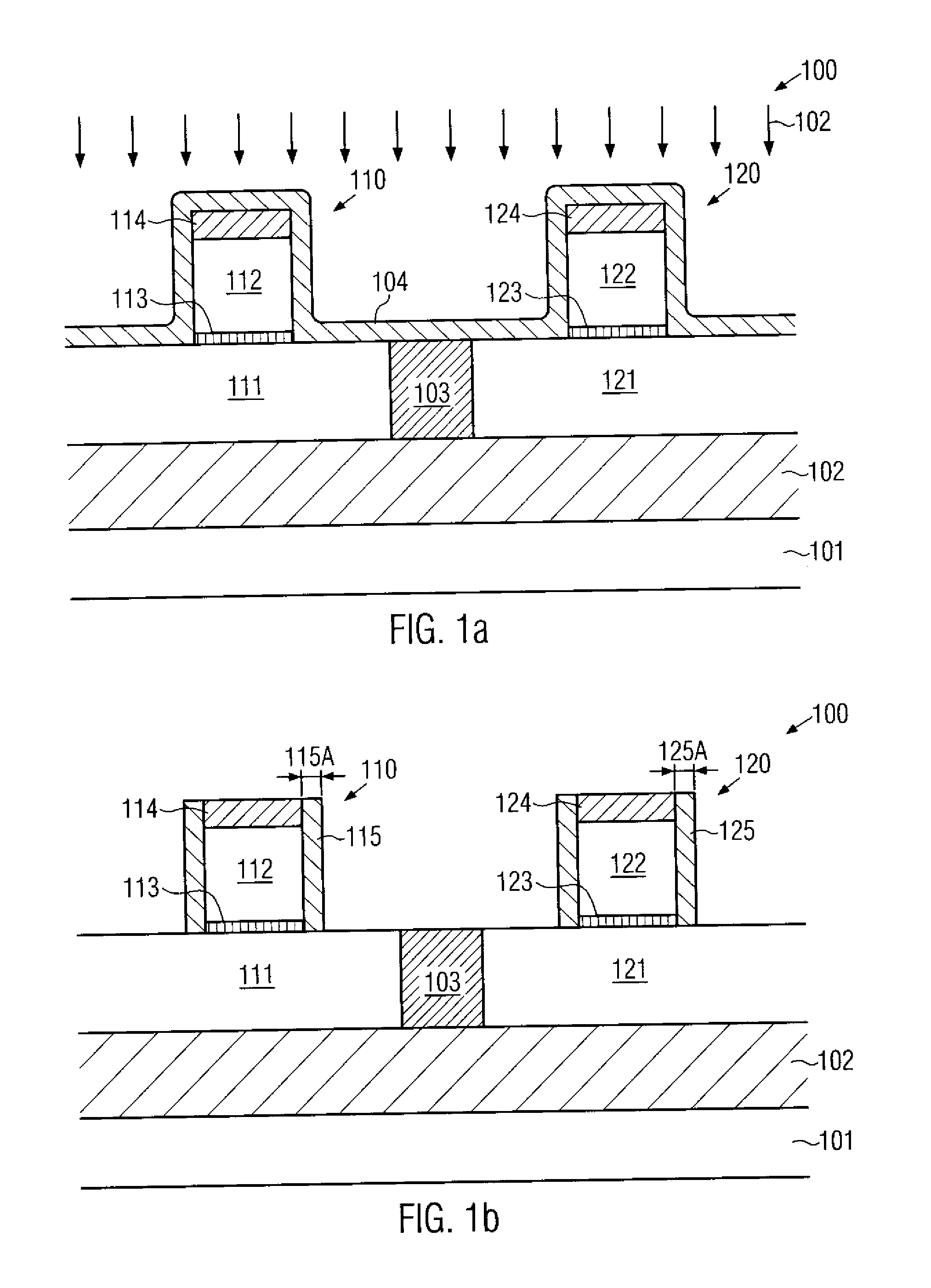

By forming a strained semiconductor layer in a PMOS transistor, a corresponding compressively strained channel region may be achieved, while, on the other hand, a corresponding strain in the NMOS transistor may be relaxed. Due to the reduced junction resistance caused by the reduced band gap of silicon / germanium in the NMOS transistor, an overall performance gain is accomplished, wherein, particularly in partially depleted SOI devices, the deleterious floating body effect is also reduced, due to the increased leakage currents generated by the silicon / germanium layer in the PMOS and NMOS transistor.

Owner:ADVANCED MICRO DEVICES INC

Laser cladding Co-based alloy powder for conductor roll

InactiveCN101187022ASolve repair problemsImprove performanceMetallic material coating processesChemical compositionAlloy substrate

Provided is cobalt-based alloy powder for laser cladding electricity conducting roller, the weight percentages of the chemical components of the material are that Cr is 24-30%, W is 6-10%, Mo is 3-6%, Ni takes 6-12%, Fe holds 2-10%, Mn is 0.5-2%, Si holds 0.2-2%, V is 0.1-0.6%, B takes 0.3-1.5%, C holds 0.5-2.5%, Y2O3 is 0-0.5%, Hf takes 0-0.5%, La2O3 holds 0-0.5%, Ce is 0-0.5%, and the rest is Co. The invention has the advantages that with multiple strengthened methods, the alloy substrate is strengthened and the crystal boundary quality is improved, which enables the alloy to achieve perfect combination property, thereby achieving medium rigidity and relatively high intensity of the alloy, simultaneously forming self-fluxing alloy and reducing alloy melting point, and increasing properties of oxidation resistance, abrasion resistance, corrosion resistance, and certain electricity conduction.

Owner:SHENYANG DALU LASER TECH

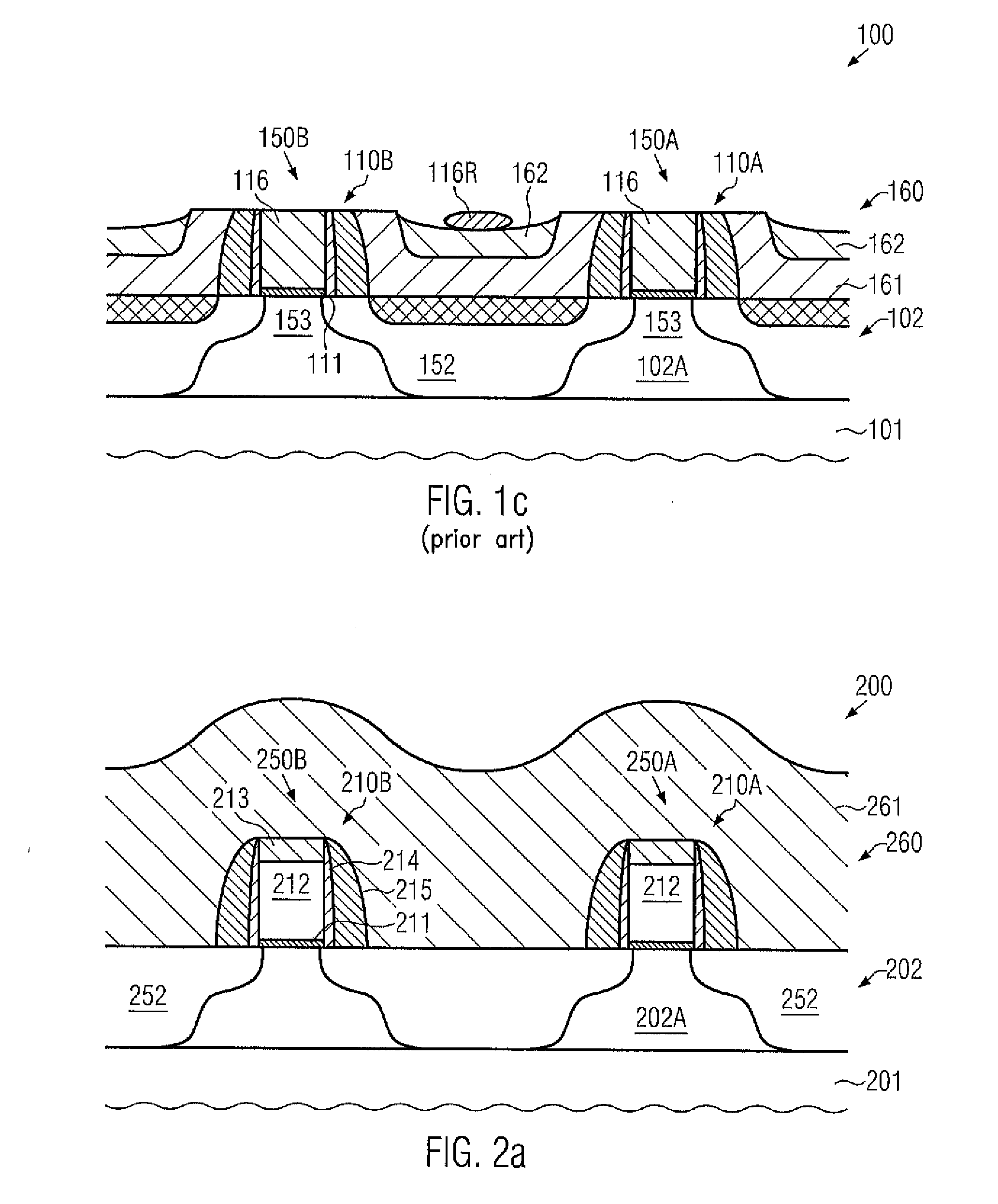

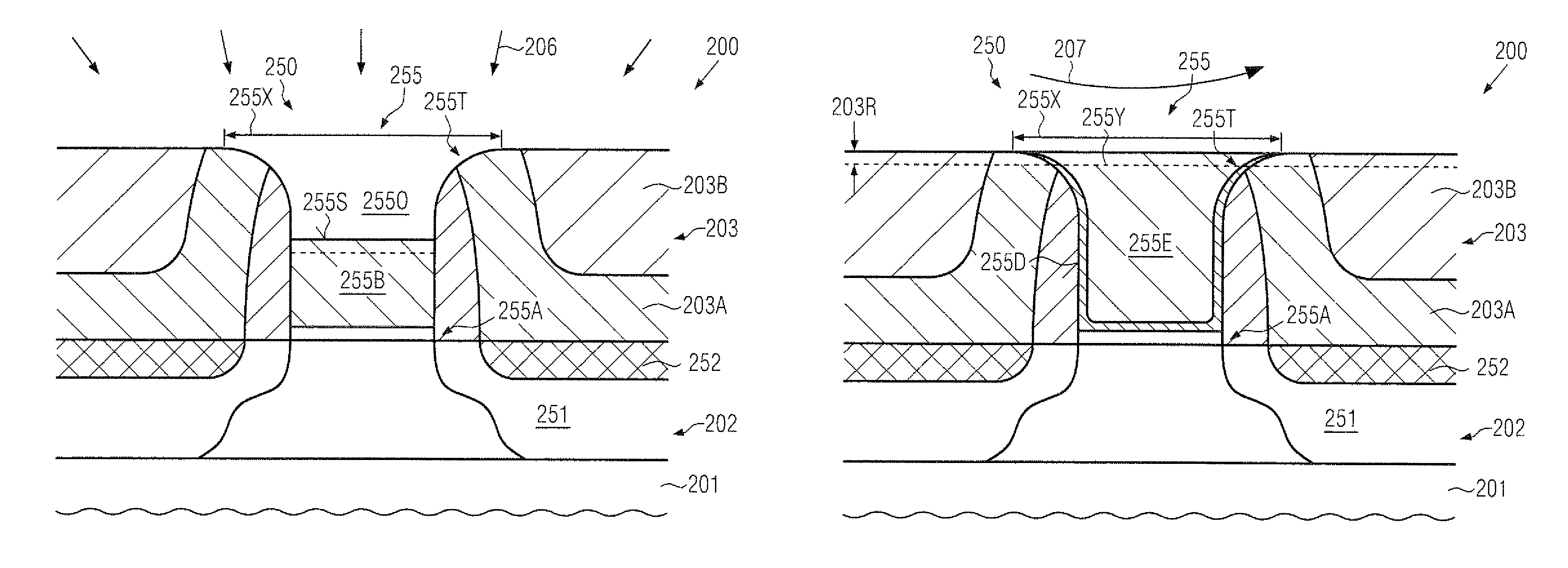

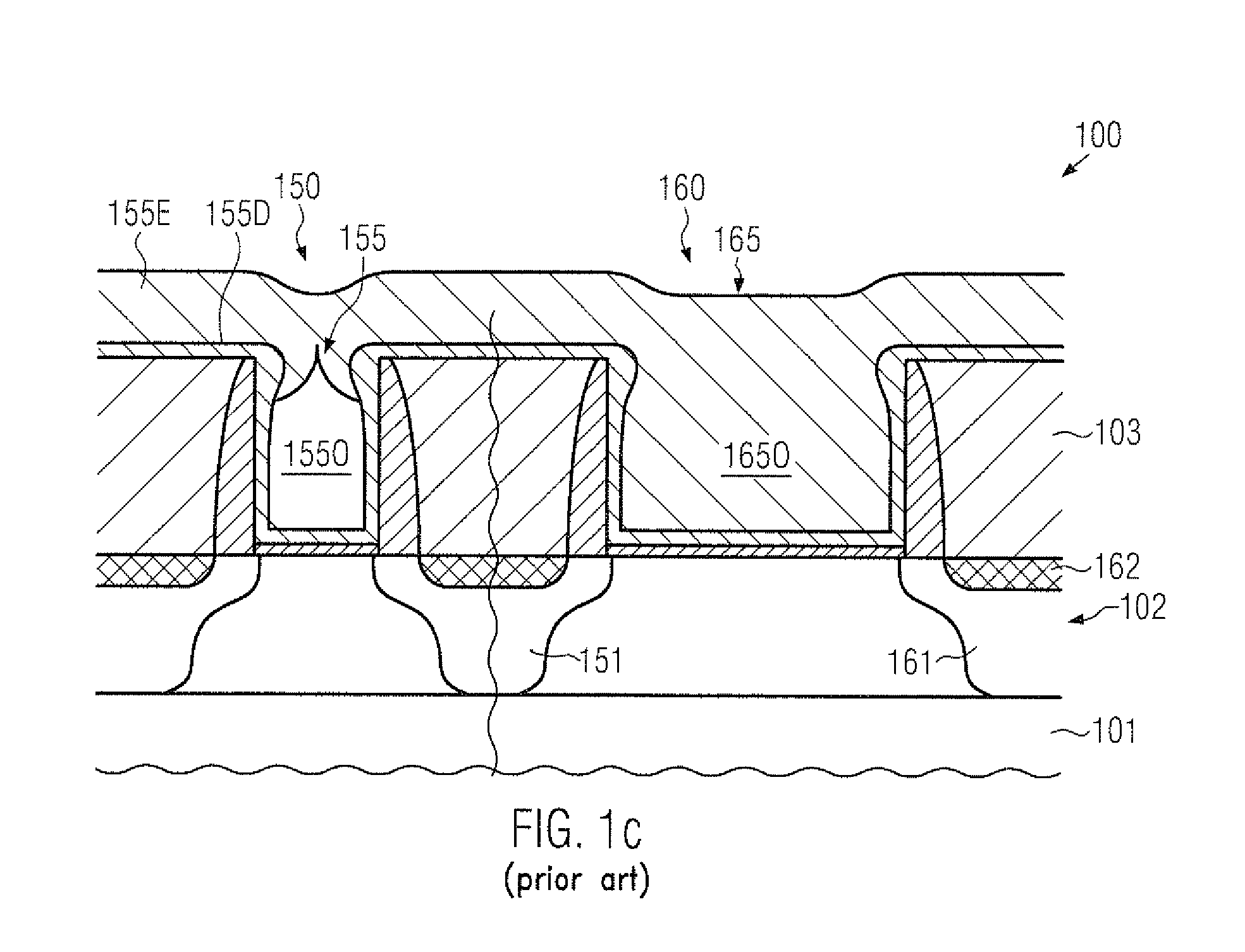

Replacement Gate Approach for High-K Metal Gate Stacks Based on a Non-Conformal Interlayer Dielectric

InactiveUS20120001263A1Superior process uniformityEnhance uniformitySemiconductor/solid-state device manufacturingSemiconductor devicesSilicon nitrideDielectric

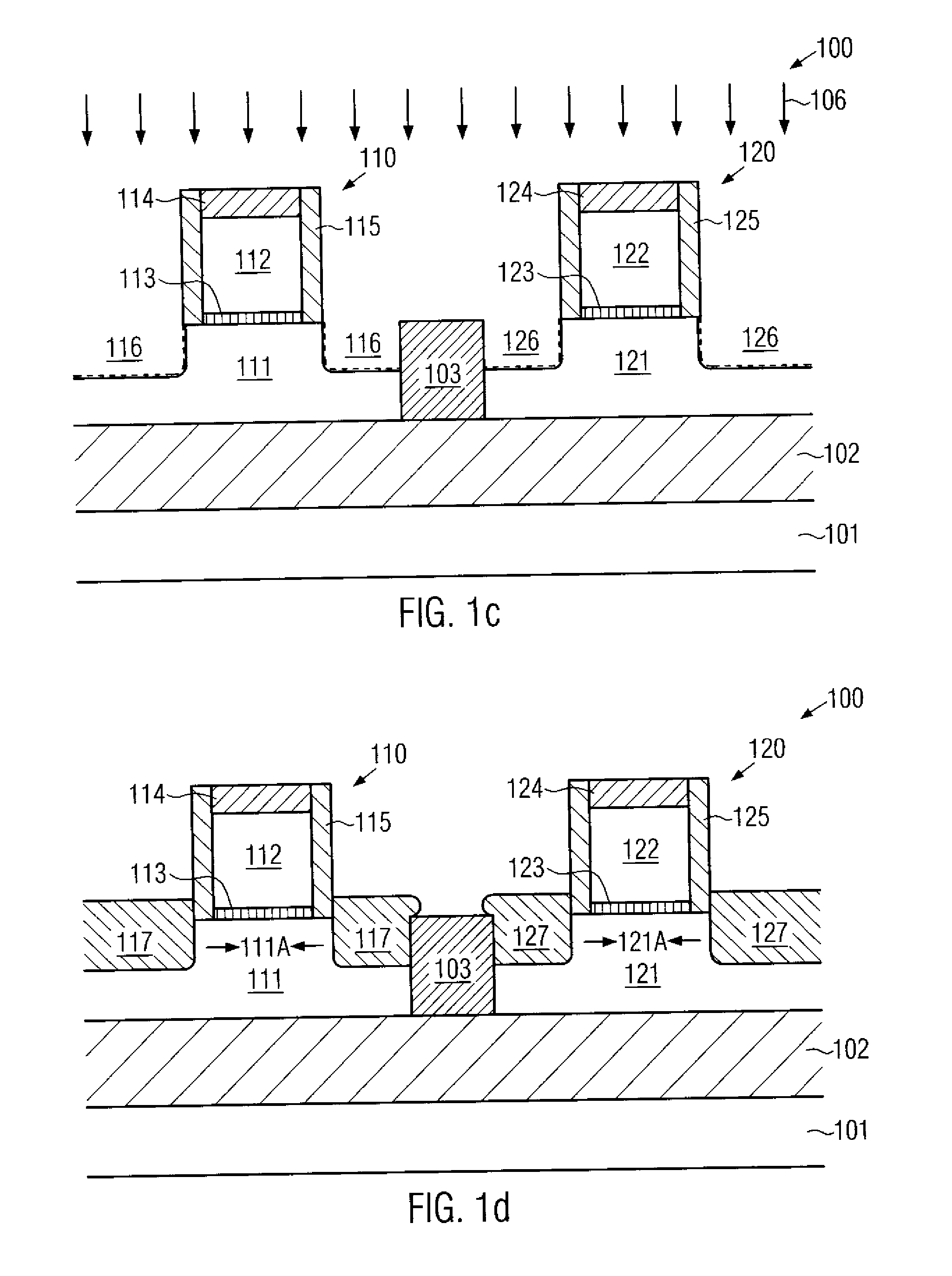

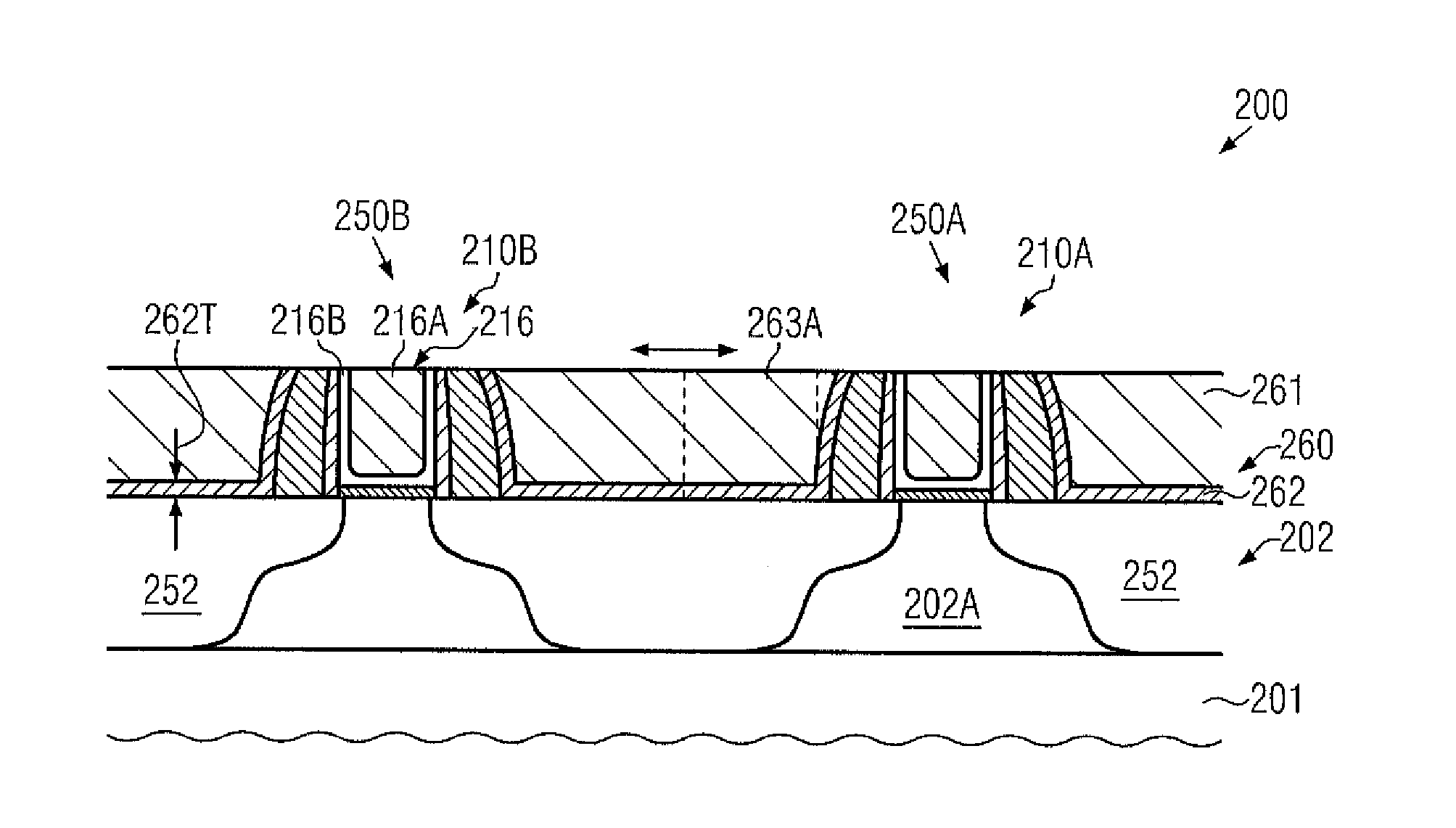

In replacement gate approaches for forming sophisticated high-k metal gate electrode structures in a late manufacturing stage, the exposing of the placeholder material may be accomplished on the basis of a substantially uniform interlayer dielectric material, for instance in the form of a silicon nitride material, which may have a similar removal rate compared to the dielectric cap material, the spacer elements and the like of the gate electrode structures. Consequently, a pronounced degree of recessing of the interlayer dielectric material may be avoided, thereby reducing the risk of forming metal residues upon removing any excess material of the gate metal.

Owner:GLOBALFOUNDRIES INC

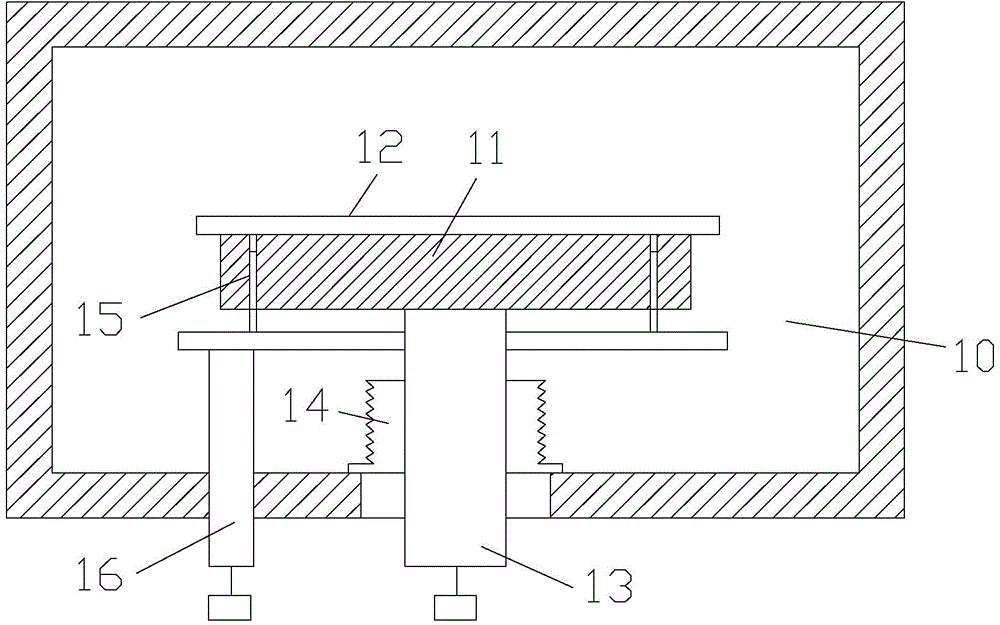

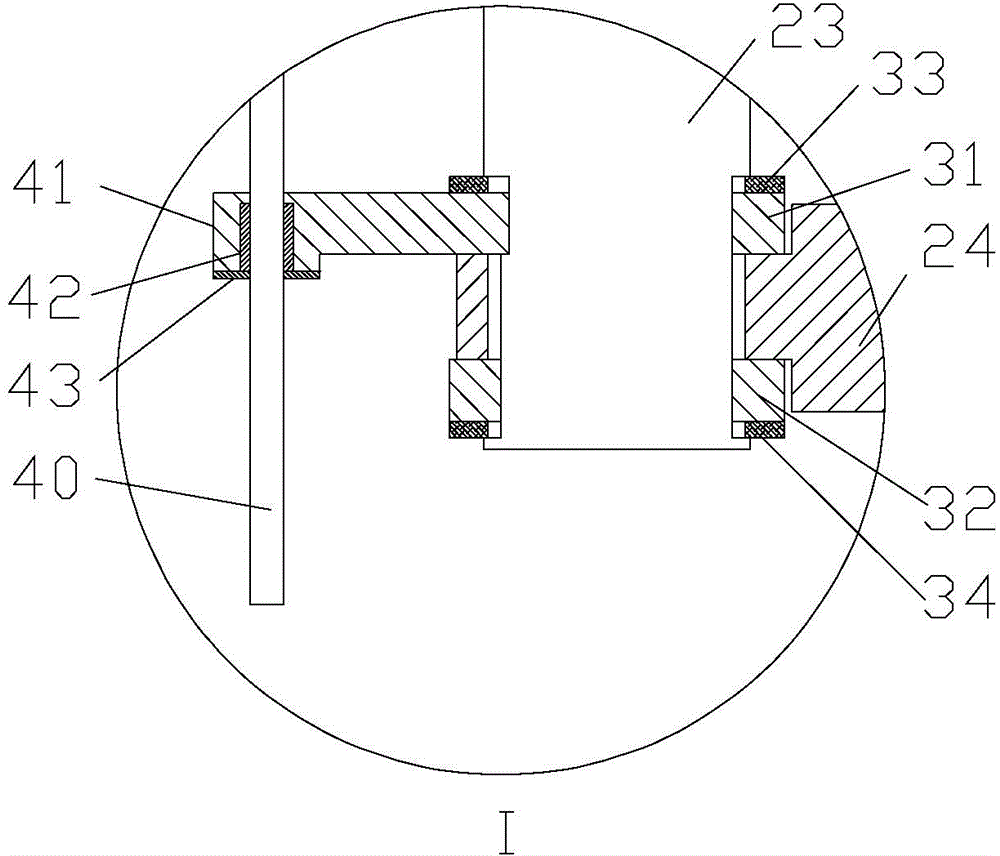

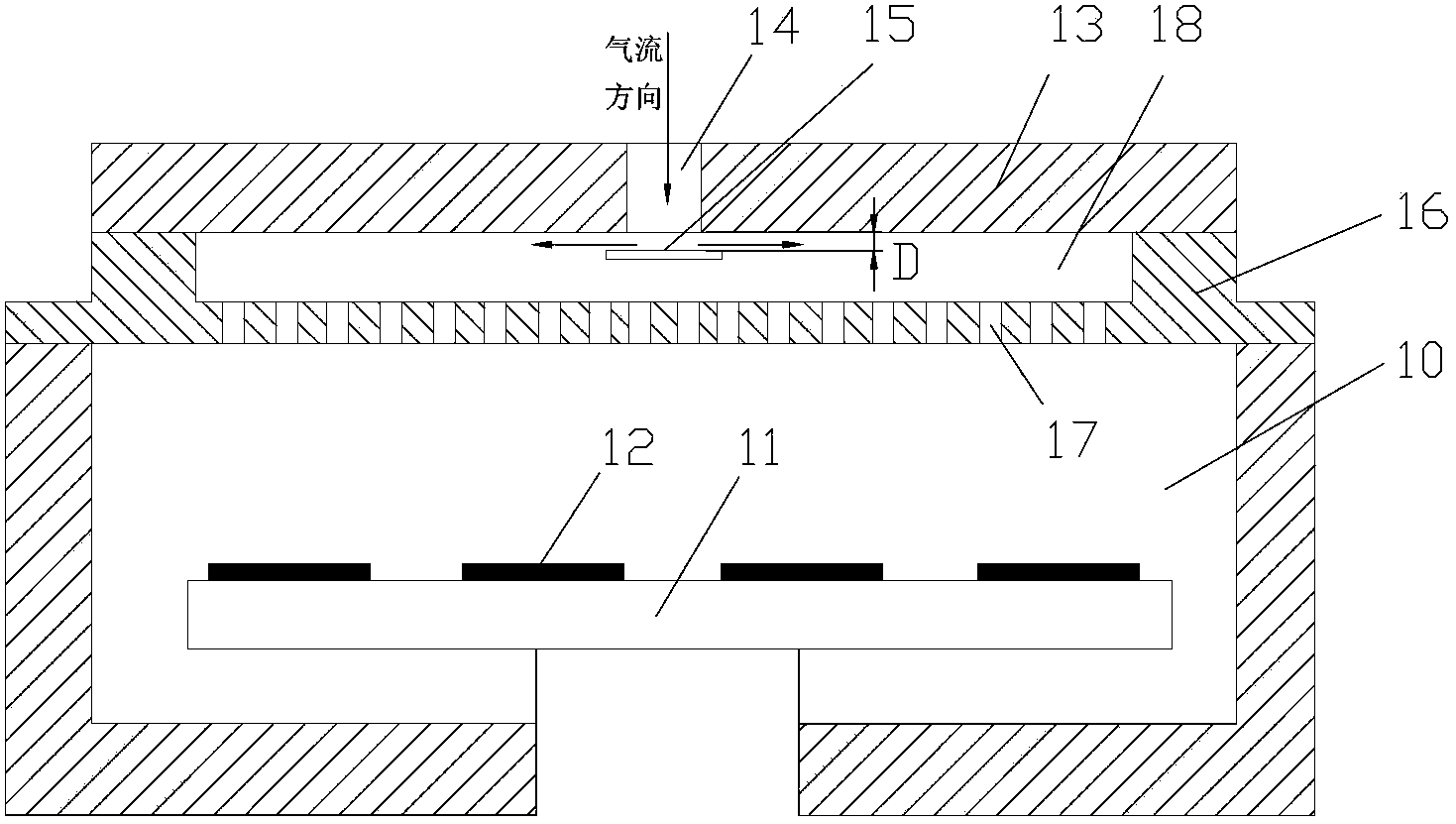

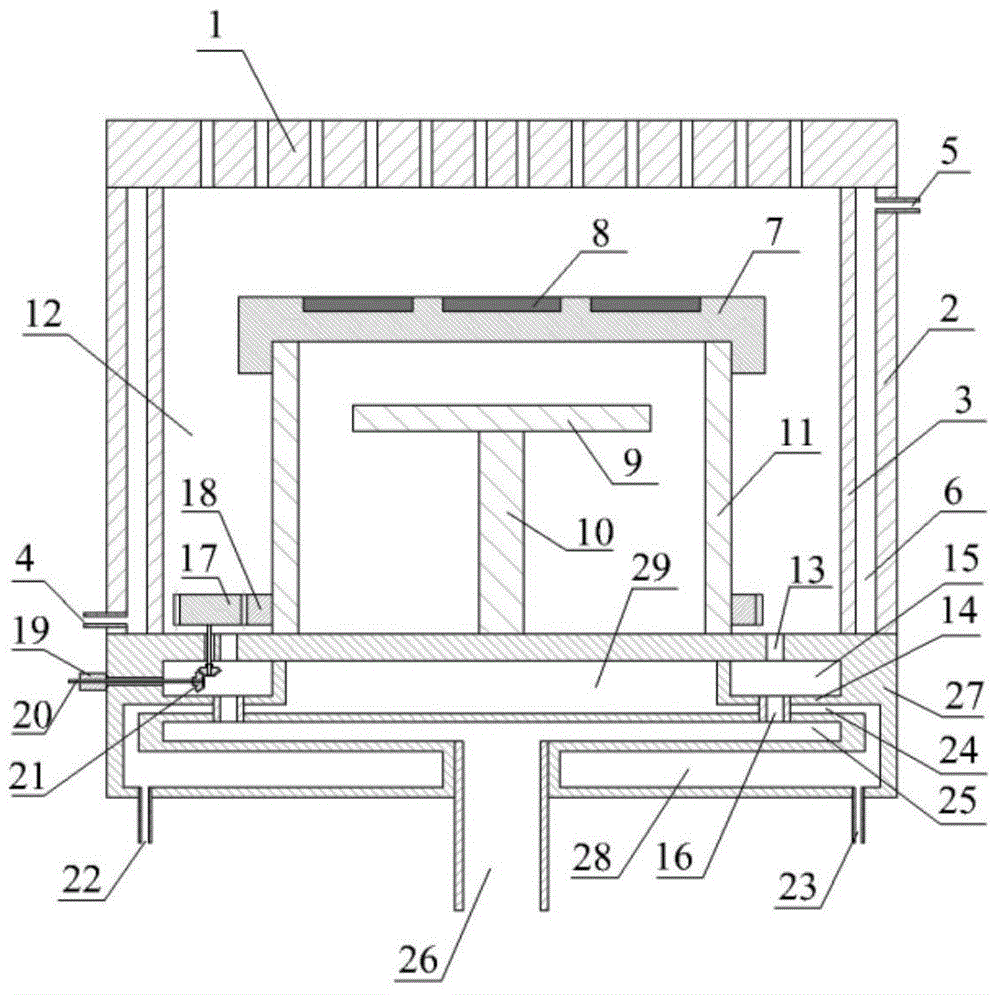

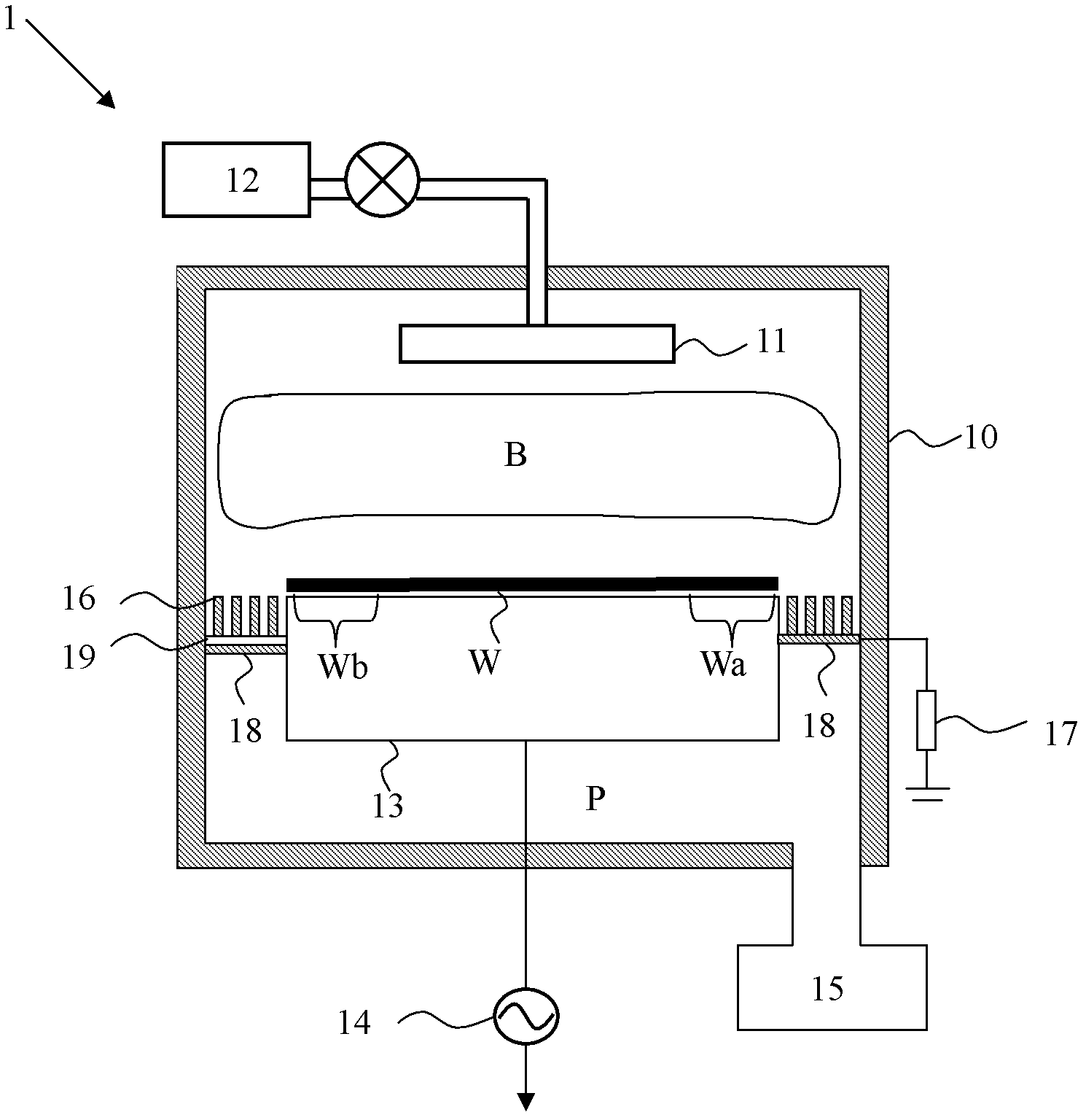

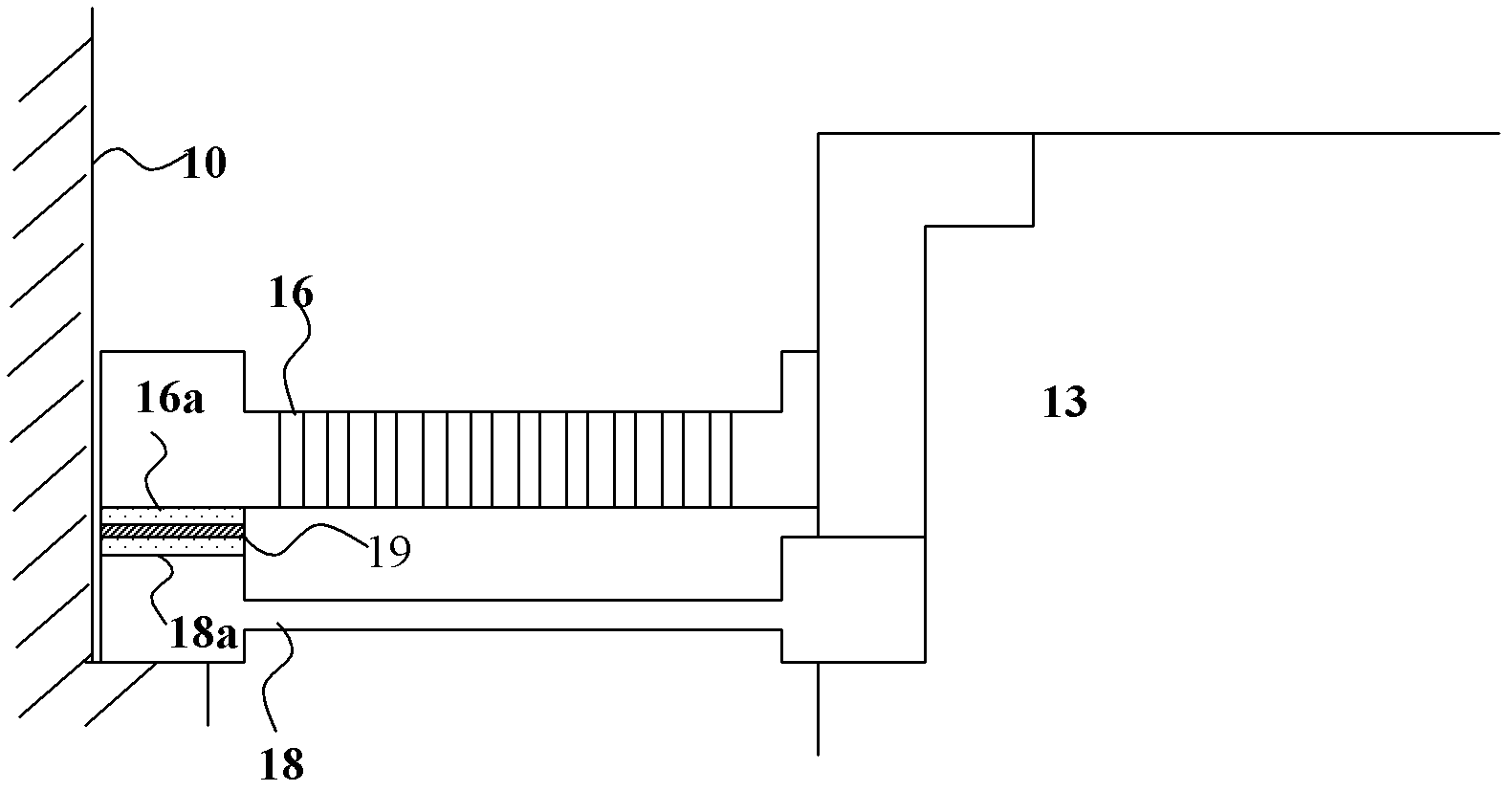

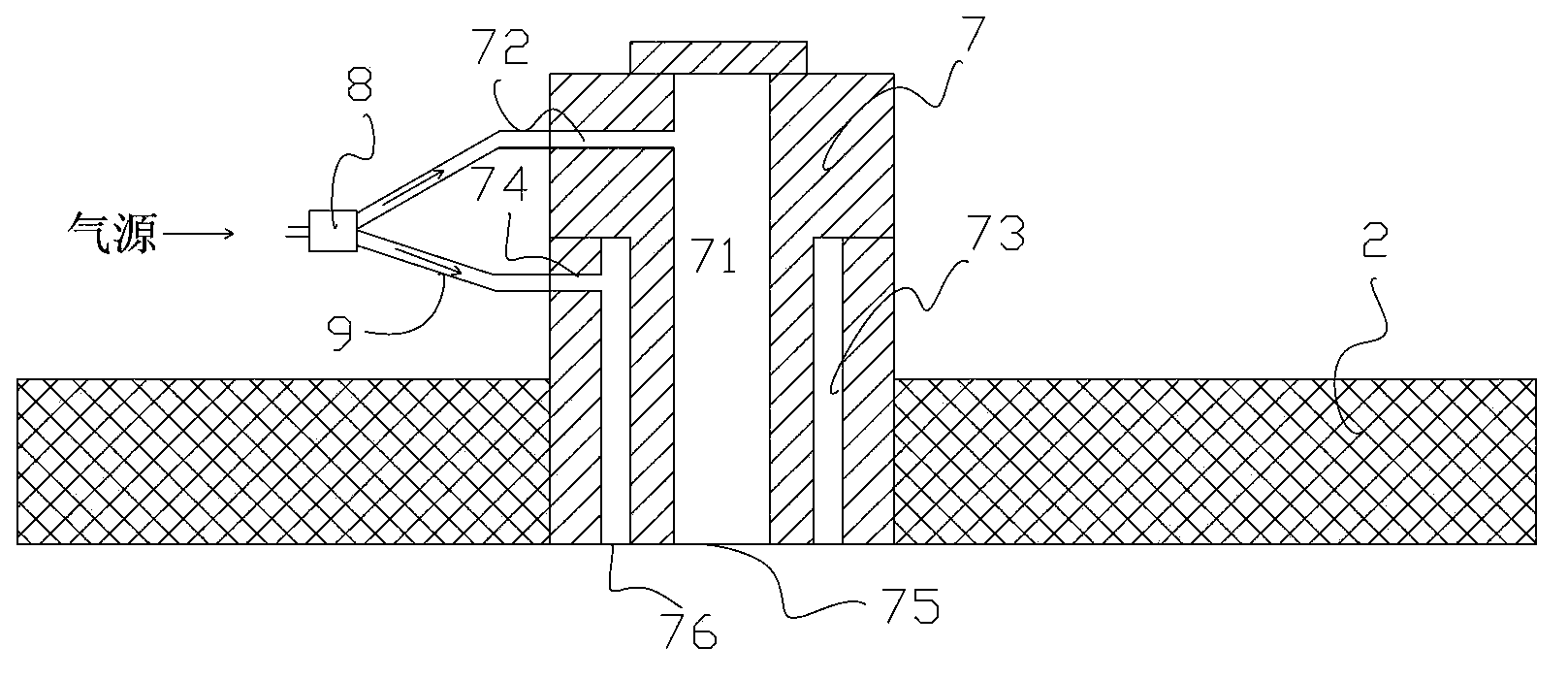

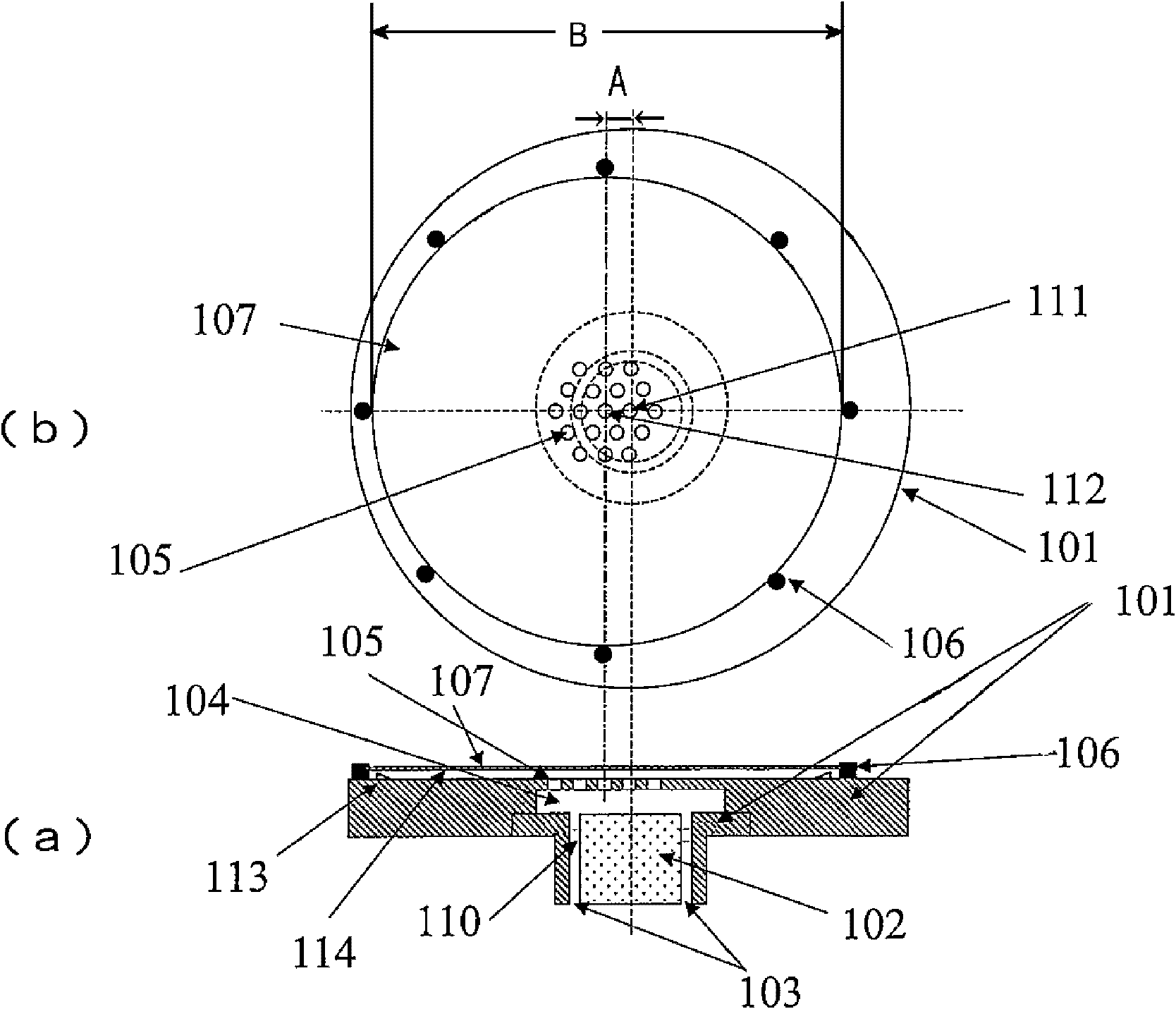

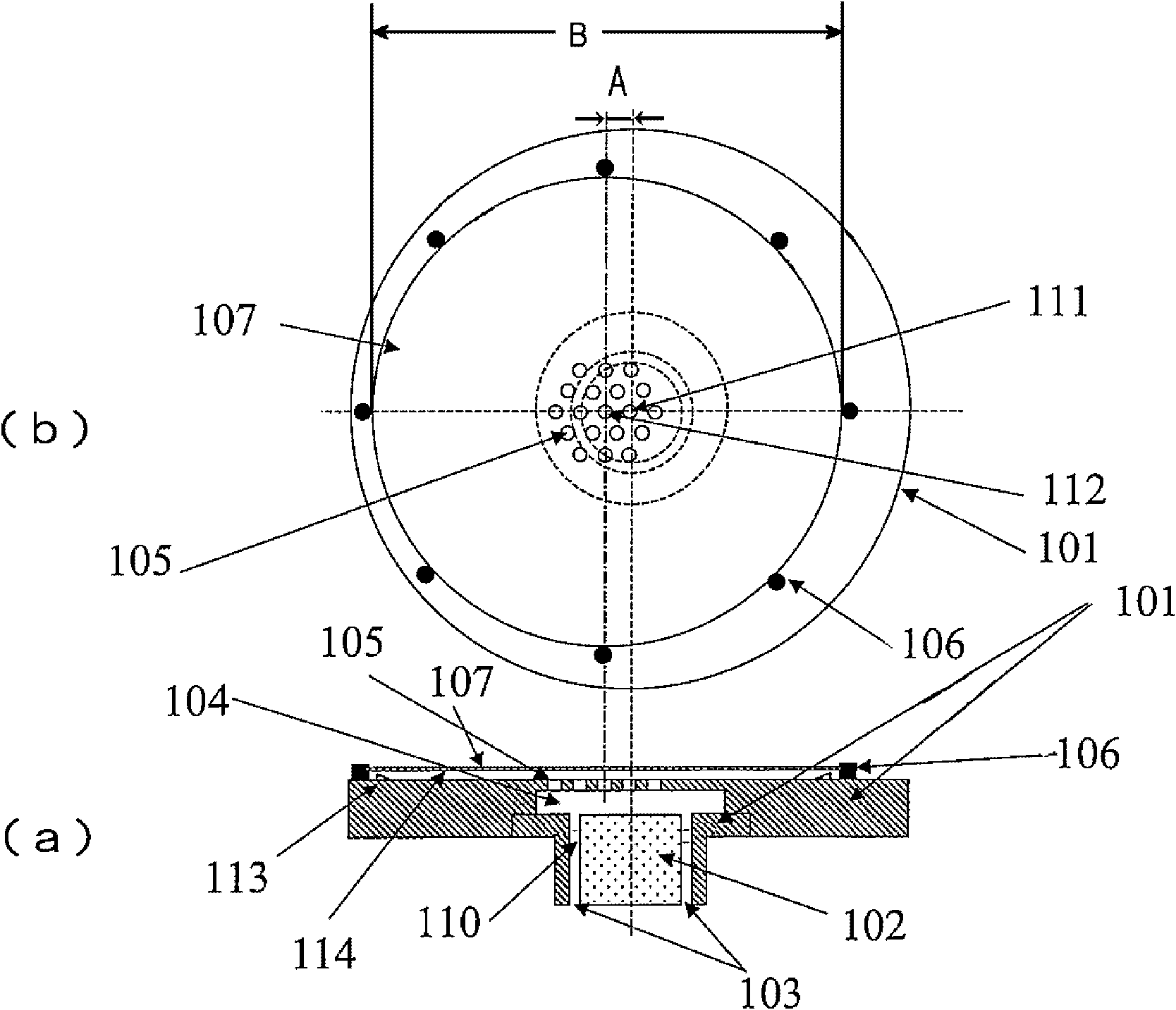

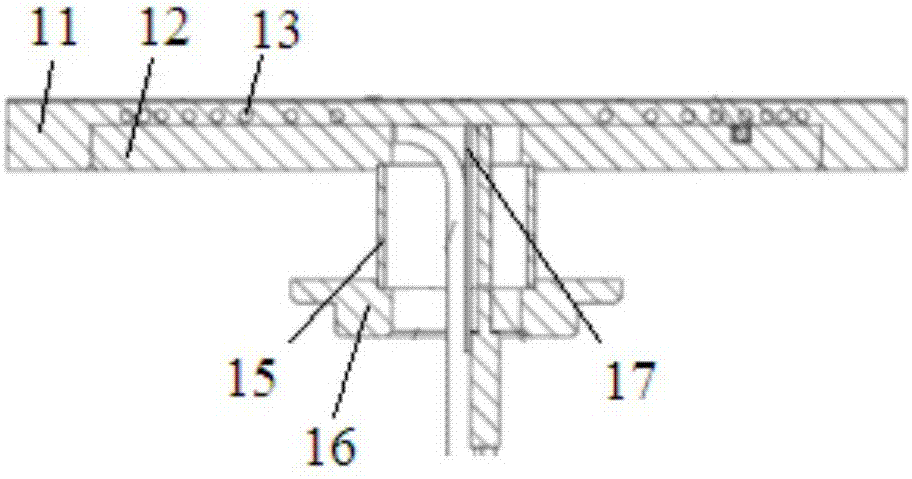

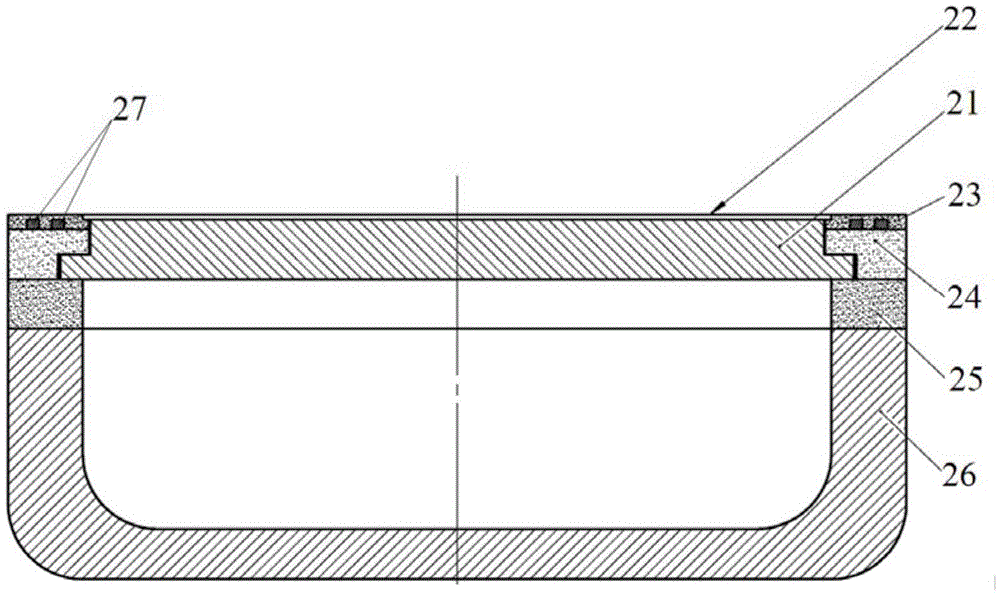

Carrying platform elevating gear, reaction cavity, and plasma processing device

ActiveCN104465447AGuaranteed levelnessEliminate redundant constraintsElectric discharge tubesVacuum evaporation coatingRotational degrees of freedomEngineering

The invention provides a carrying platform elevating gear, a reaction cavity, and a plasma processing device. A bracket driving source drives a shaft lifting bracket to do lifting motion. A bellows shaft passes through the shaft lifting bracket and is fixedly connected with the shaft lifting bracket, so as to do lifting motion with the shaft lifting bracket in a linear bearing, thereby realizing lifting motion of the carrying platform which is fixed on the bellows shaft. In the carrying platform elevating gear, a guiding mechanism is used to limit axial rotation of the bellows shaft in a lifting process. The bellows shaft passes through the linear bearing, a guiding shaft installing assembly, and a shaft lifting bracket in sequence. The guiding shaft installing assembly tightly holds the bellows shaft. The upper end of the guiding shaft is fixed on the cavity wall of the reaction cavity. The lower end of the guiding shaft passes through the guiding shaft installing assembly, so that the guiding shaft installing assembly does lifting motion with the shaft lifting bracket along the guiding shaft. The carrying platform elevating gear can limit rotation degree of freedom of a connecting rod, so as to ensure a carrying device from deflecting.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

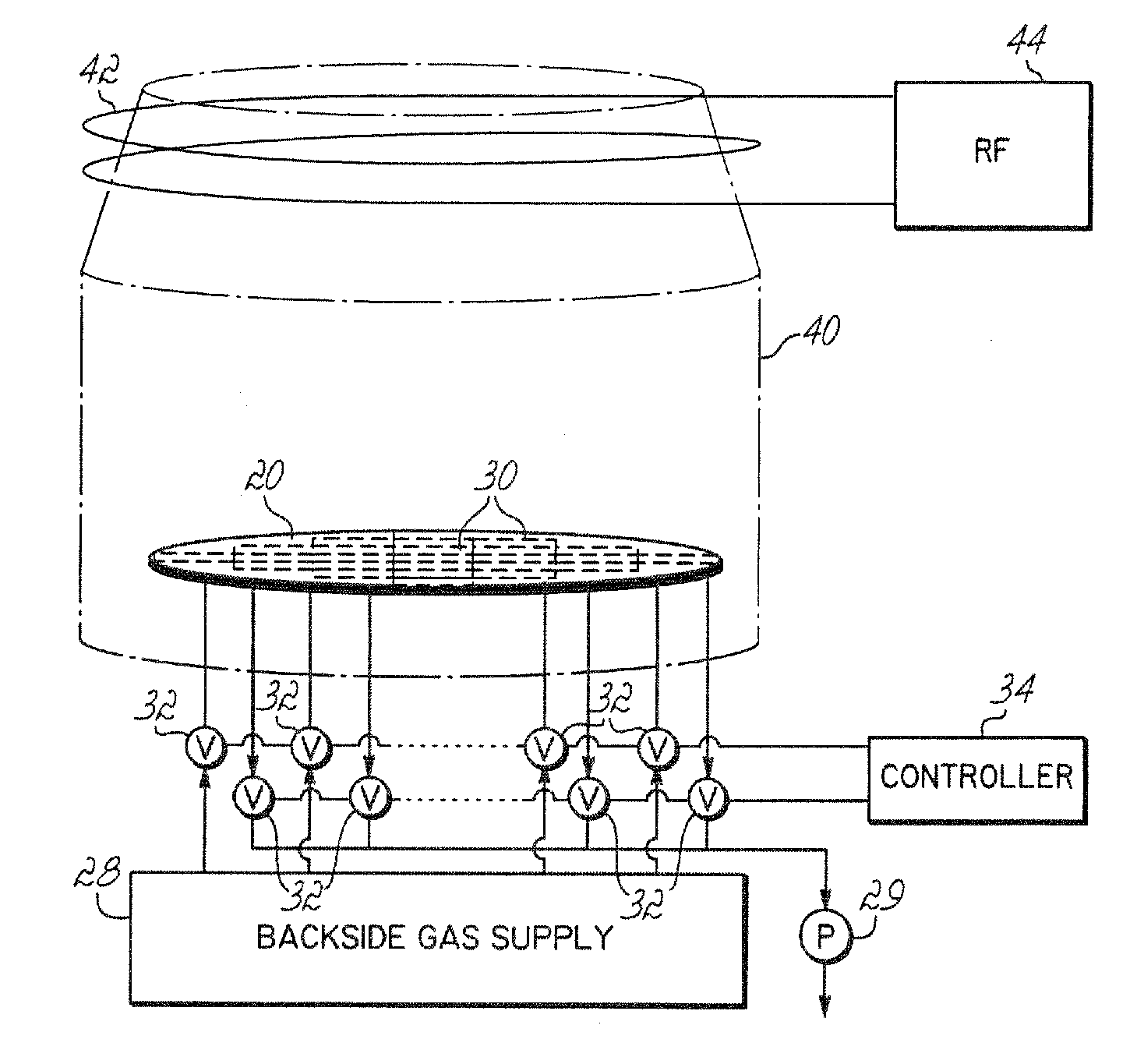

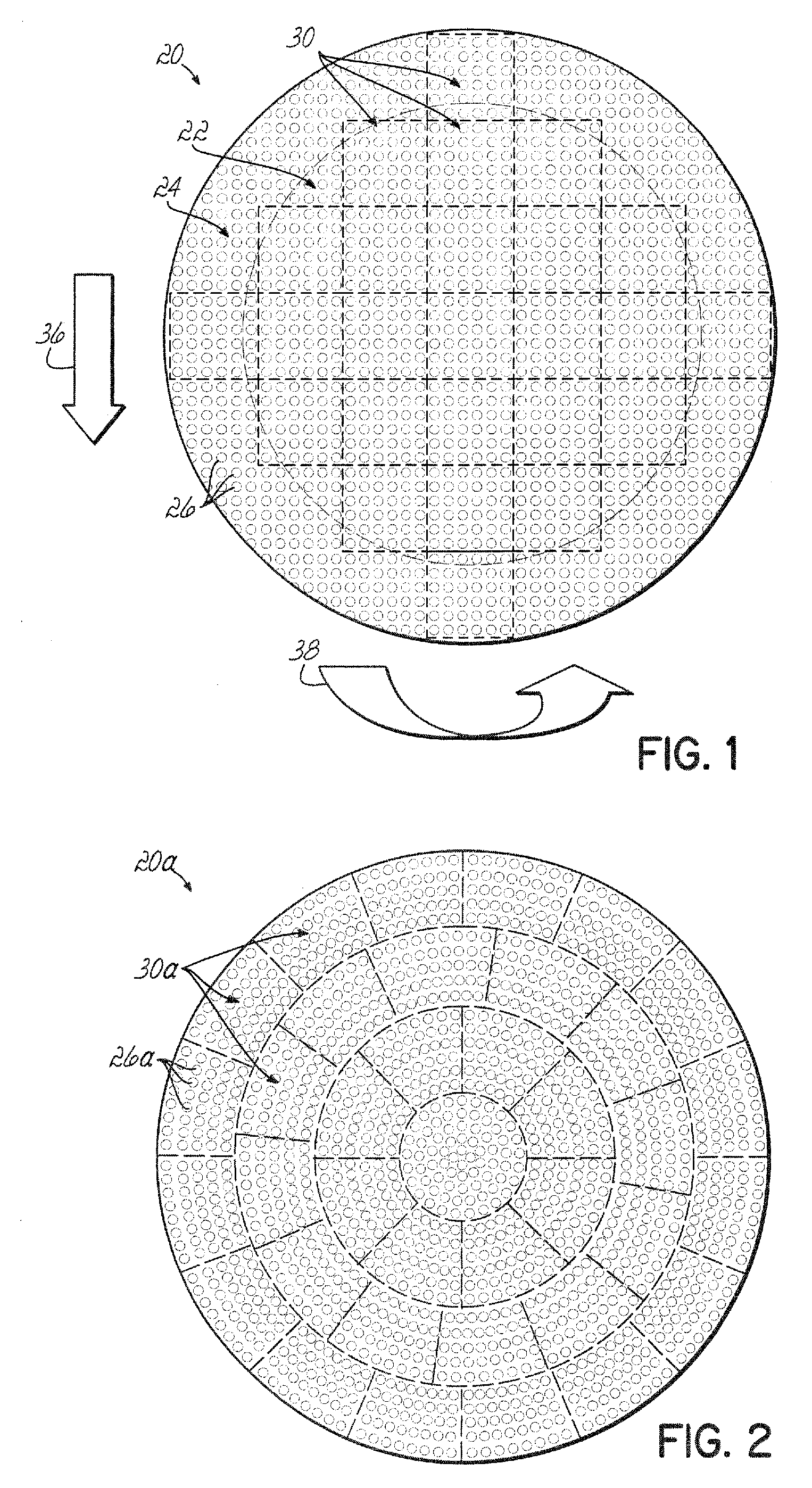

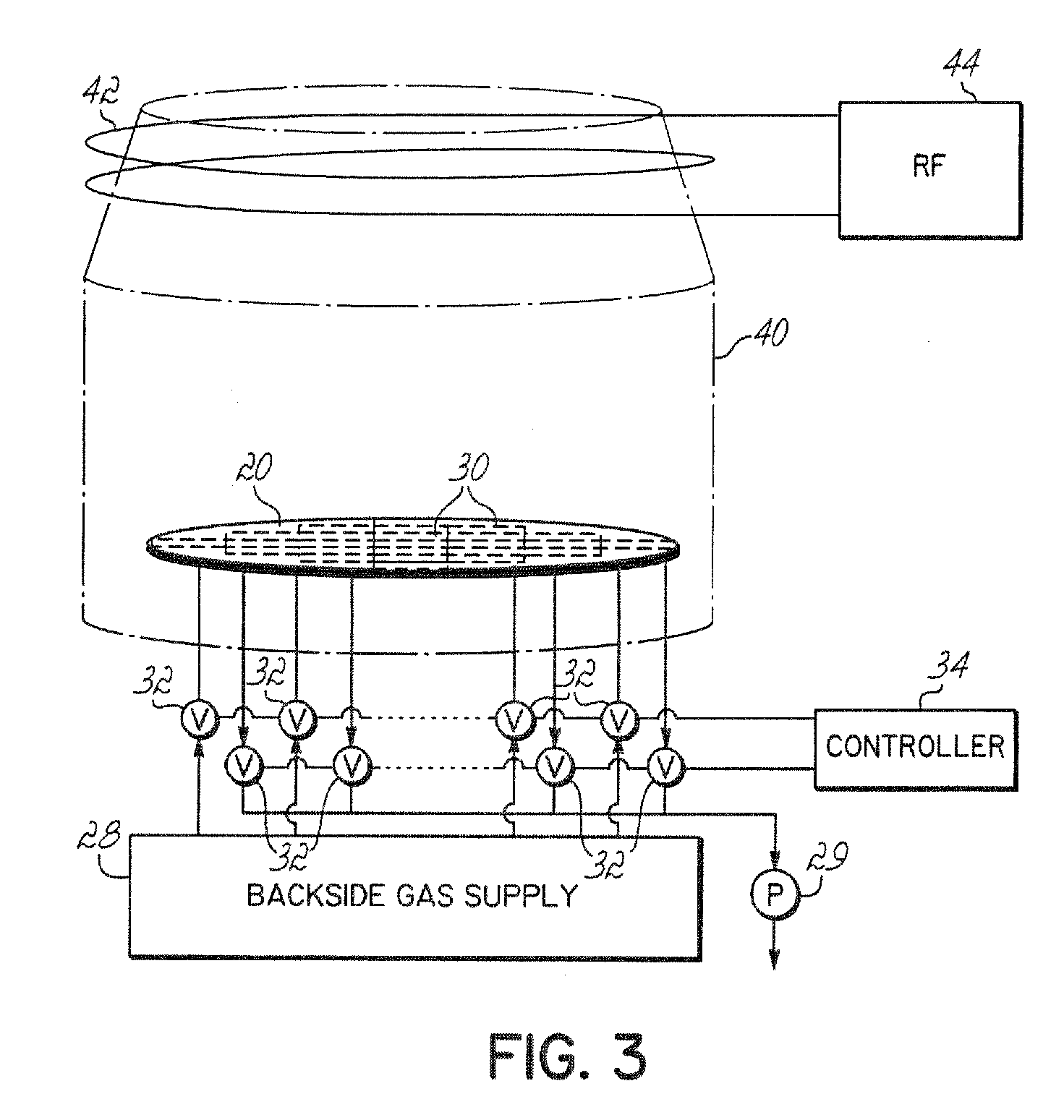

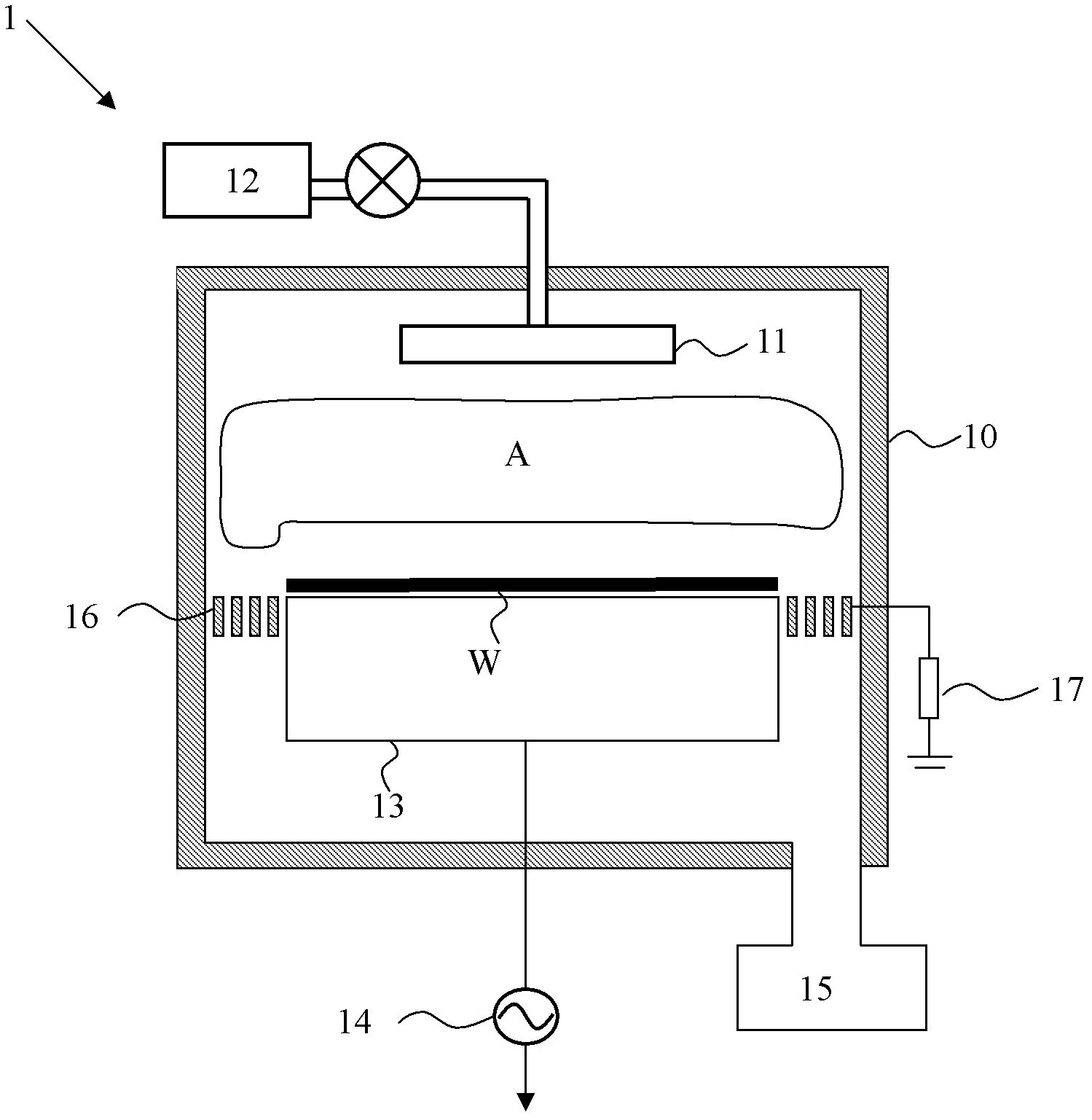

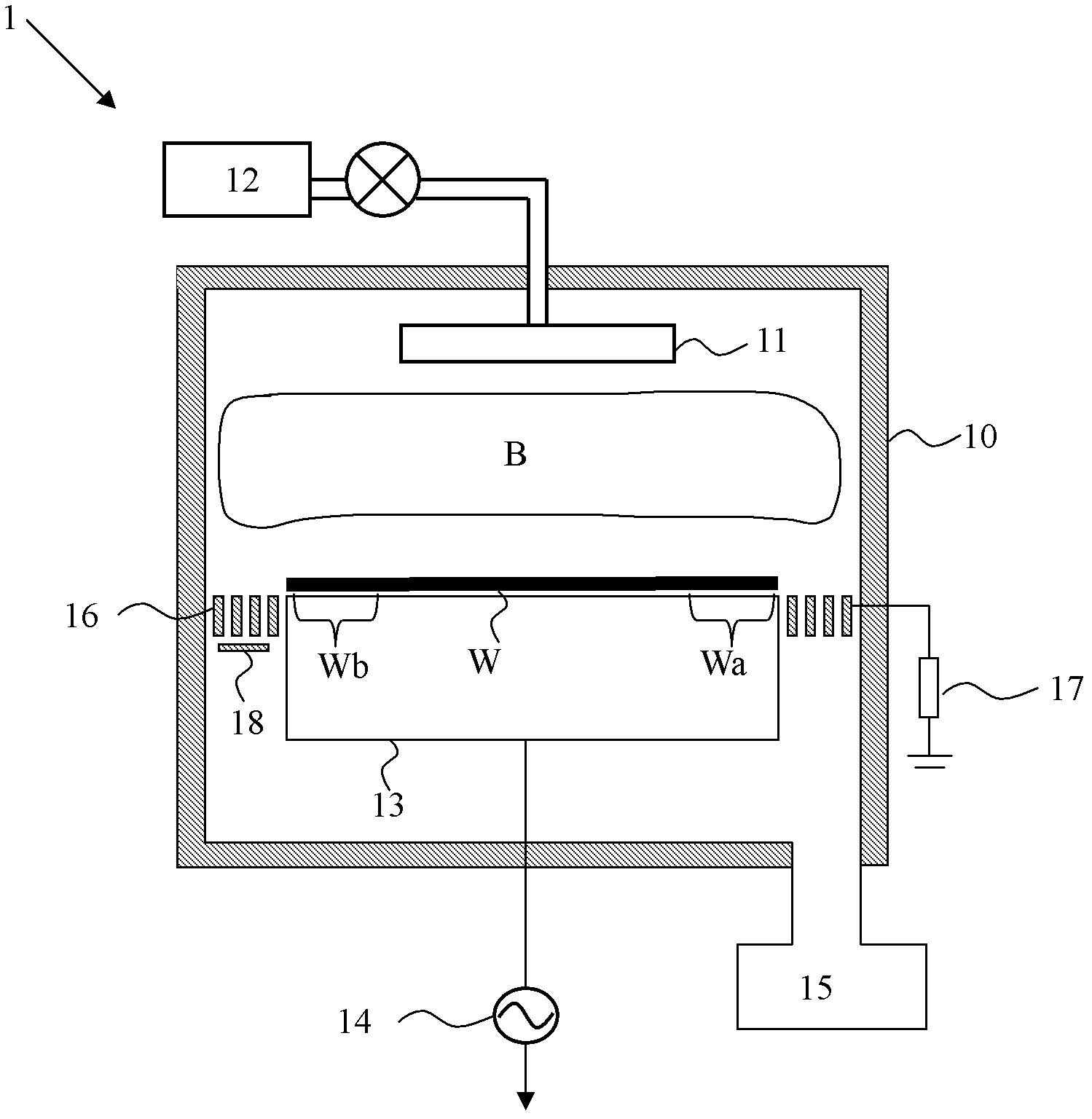

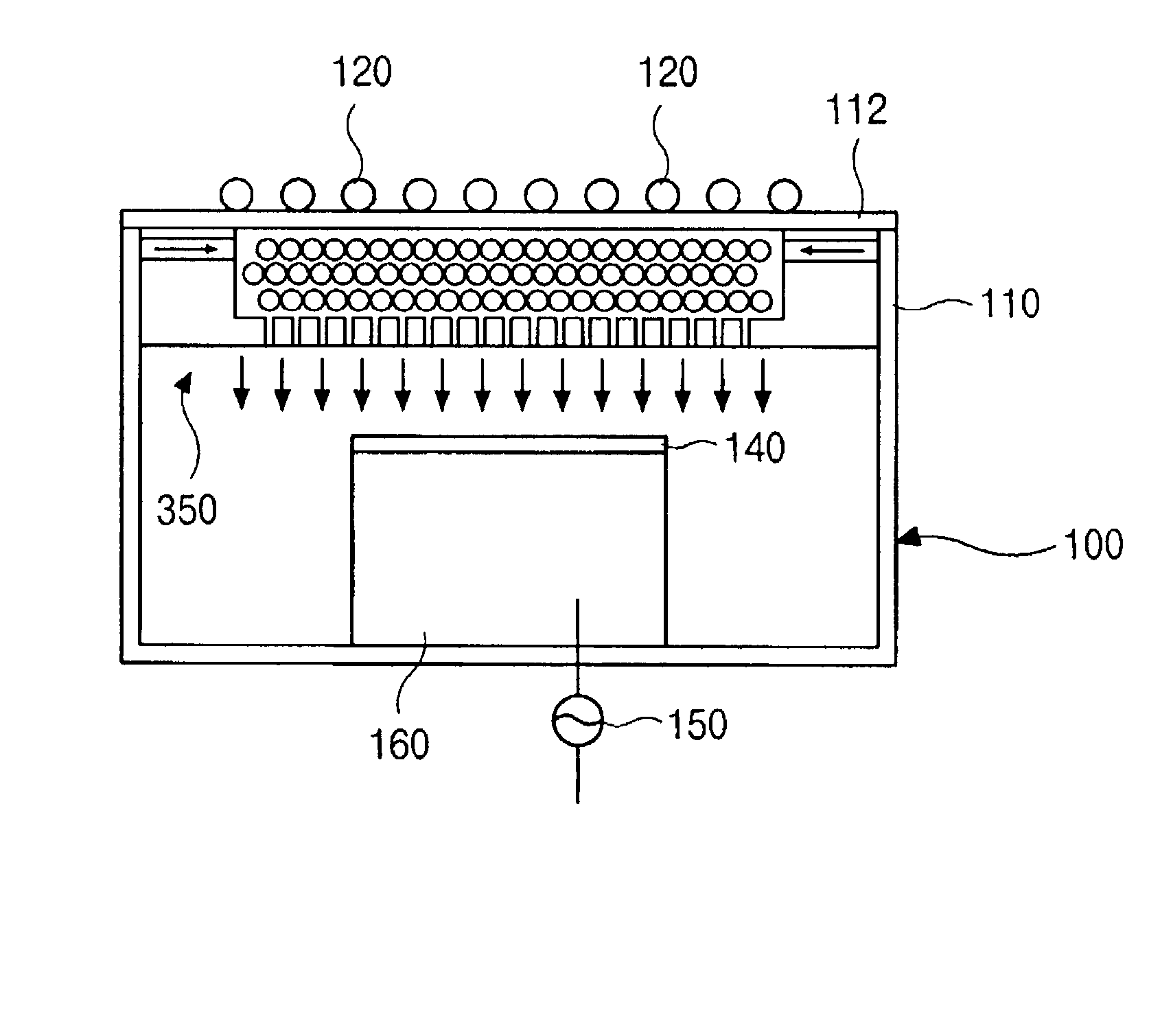

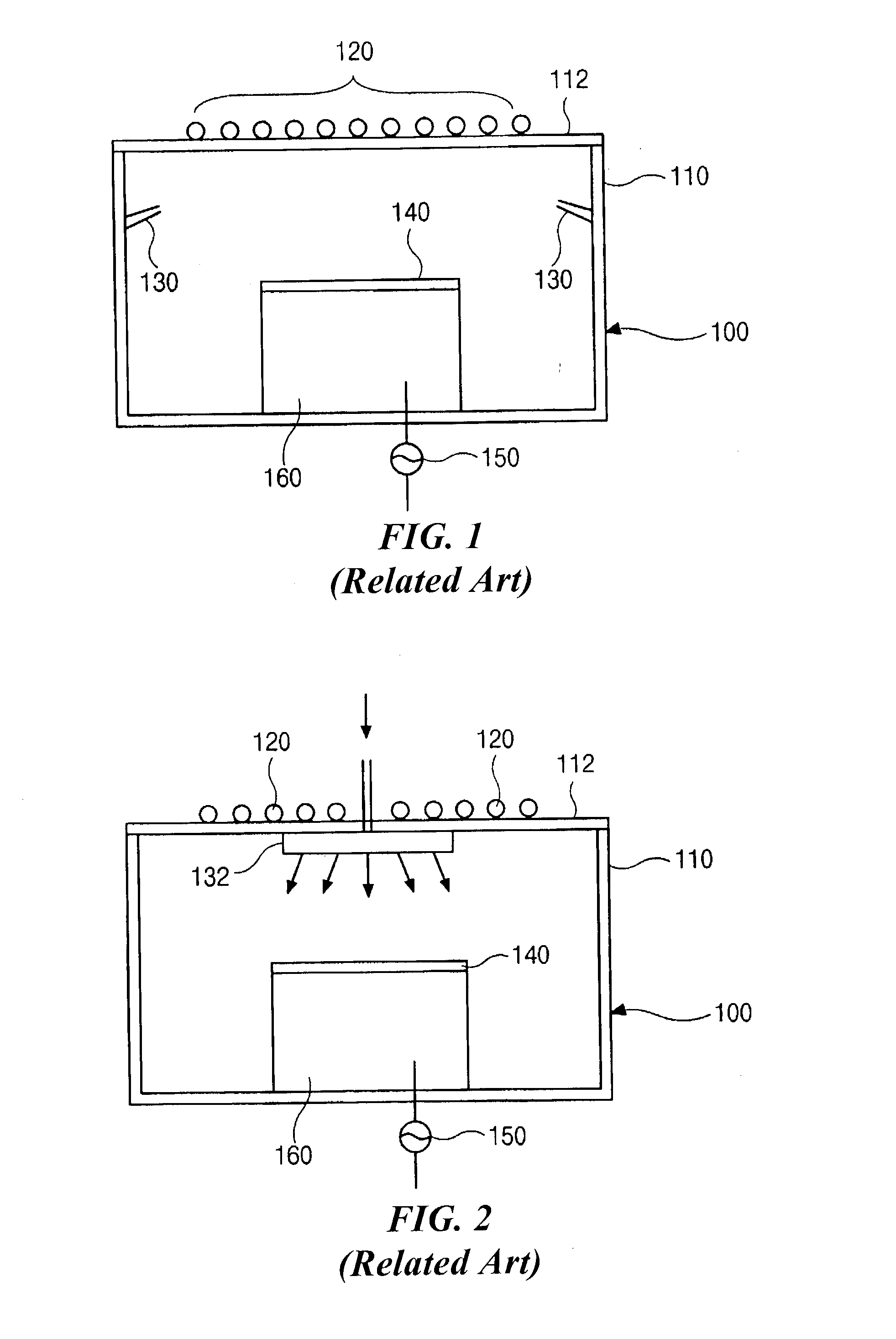

Dynamic temperature backside gas control for improved within-substrate process uniformity

ActiveUS20080227227A1Improve uniformityImprove process uniformitySemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingProcess engineeringHelium

A method and apparatus are provided to control the radial or non-radial temperature distribution across a substrate during processing to compensate for non-uniform effects, including radial and angular non-uniformities arising from system variations, or process variations, or both. The temperature is controlled, preferably dynamically, by flowing backside gas differently across different areas on a wafer supporting chuck to vary heat conduction across the wafer. Backside gas flow, of helium, for example, is dynamically varied across the chuck to control the uniformity of processing of the wafer. Ports in the support are grouped, and gas to or from the groups is separately controlled by different valves responsive to a controller that controls gas pressure in each of the areas to spatially and preferably dynamically control wafer temperature to compensate for system and process non-uniformities.

Owner:TOKYO ELECTRON LTD +1

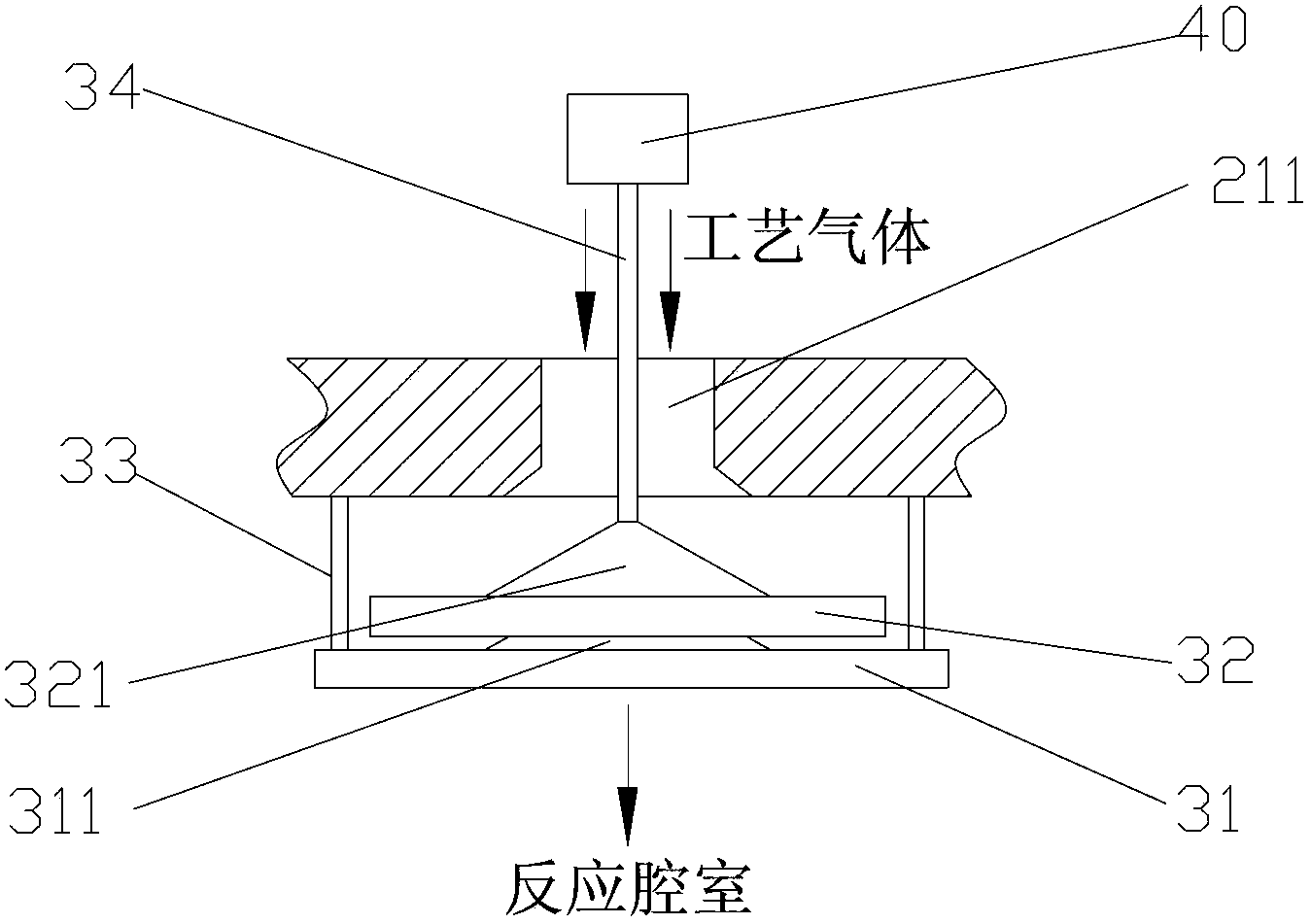

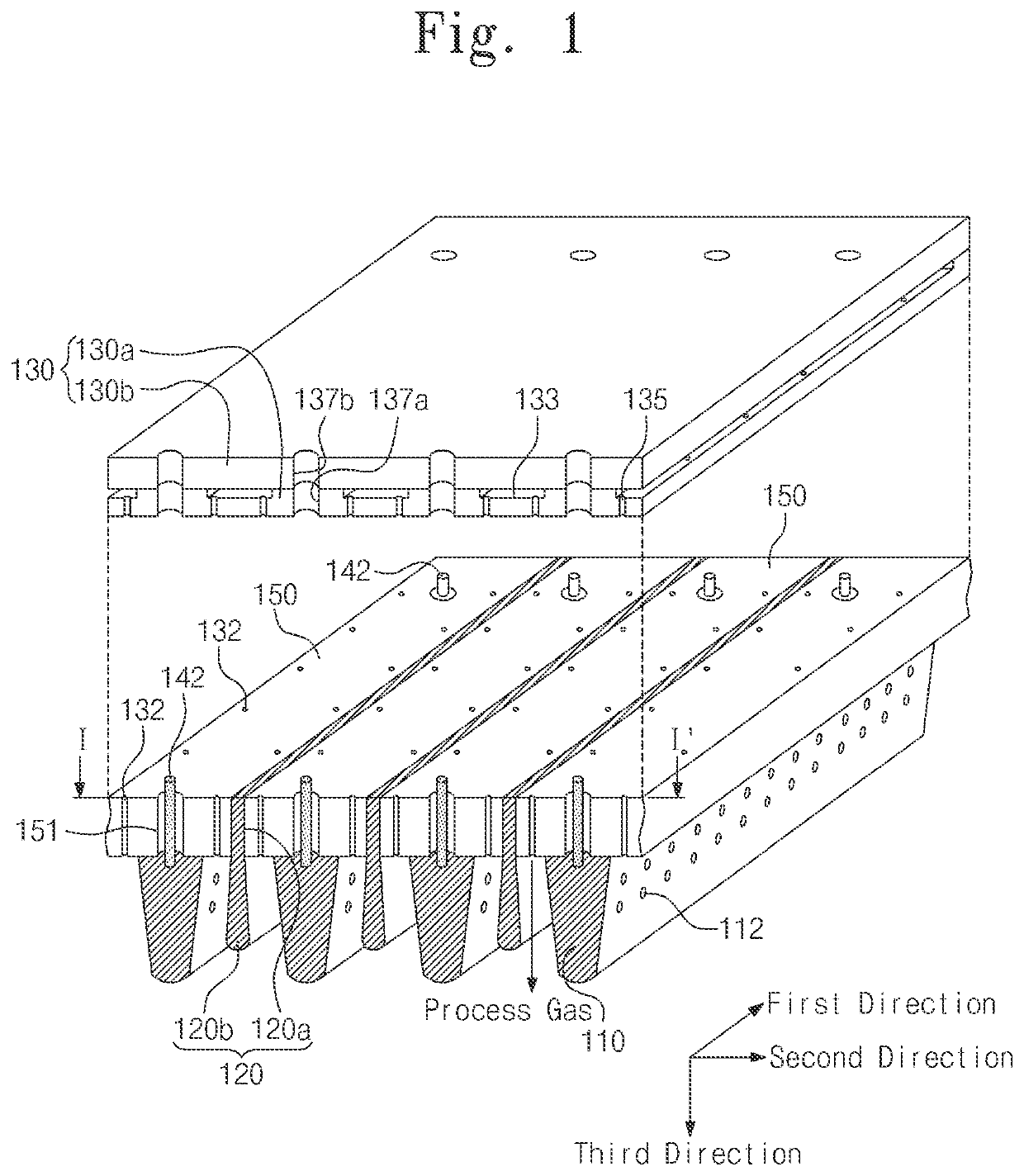

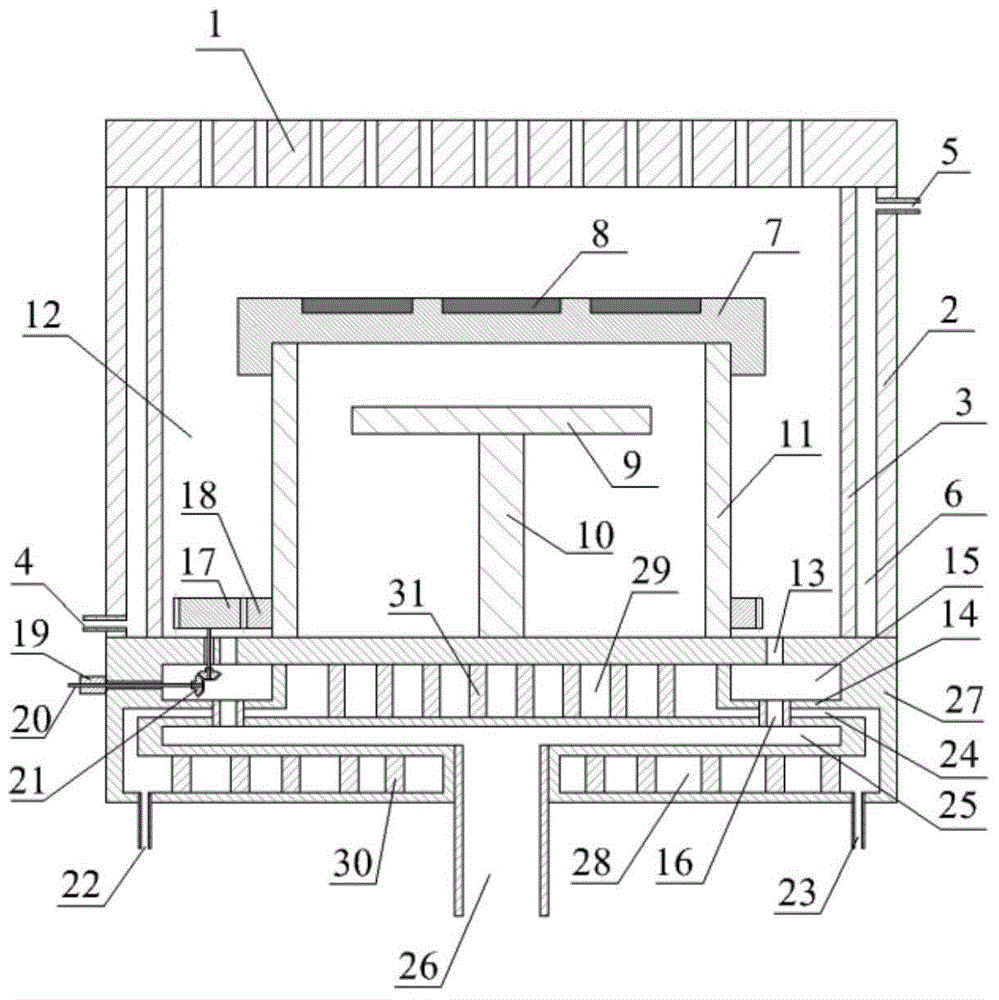

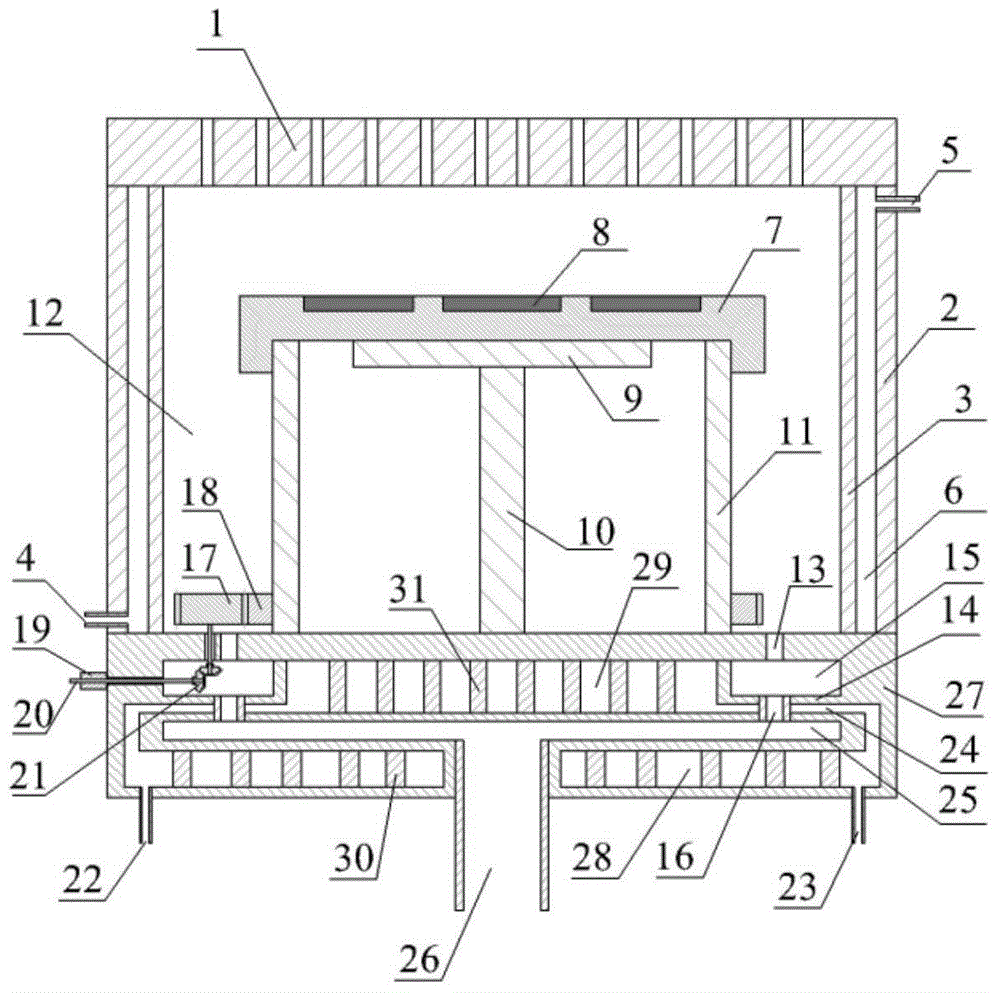

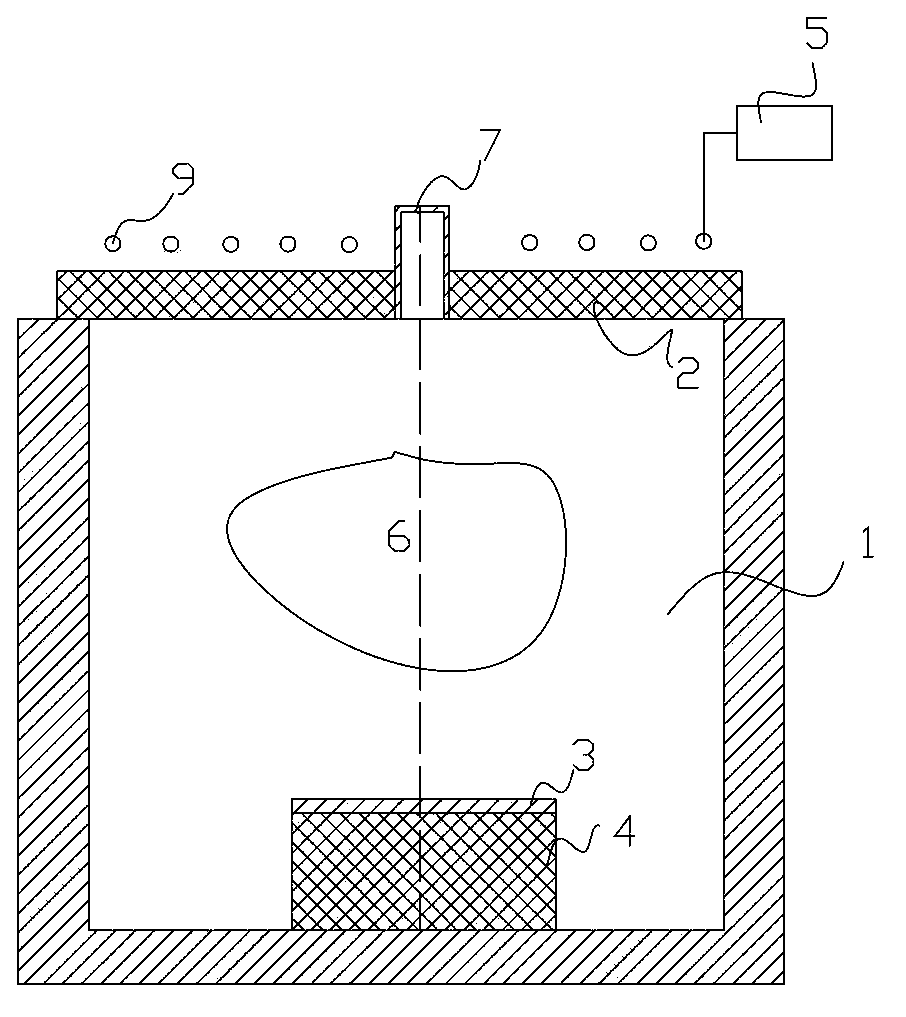

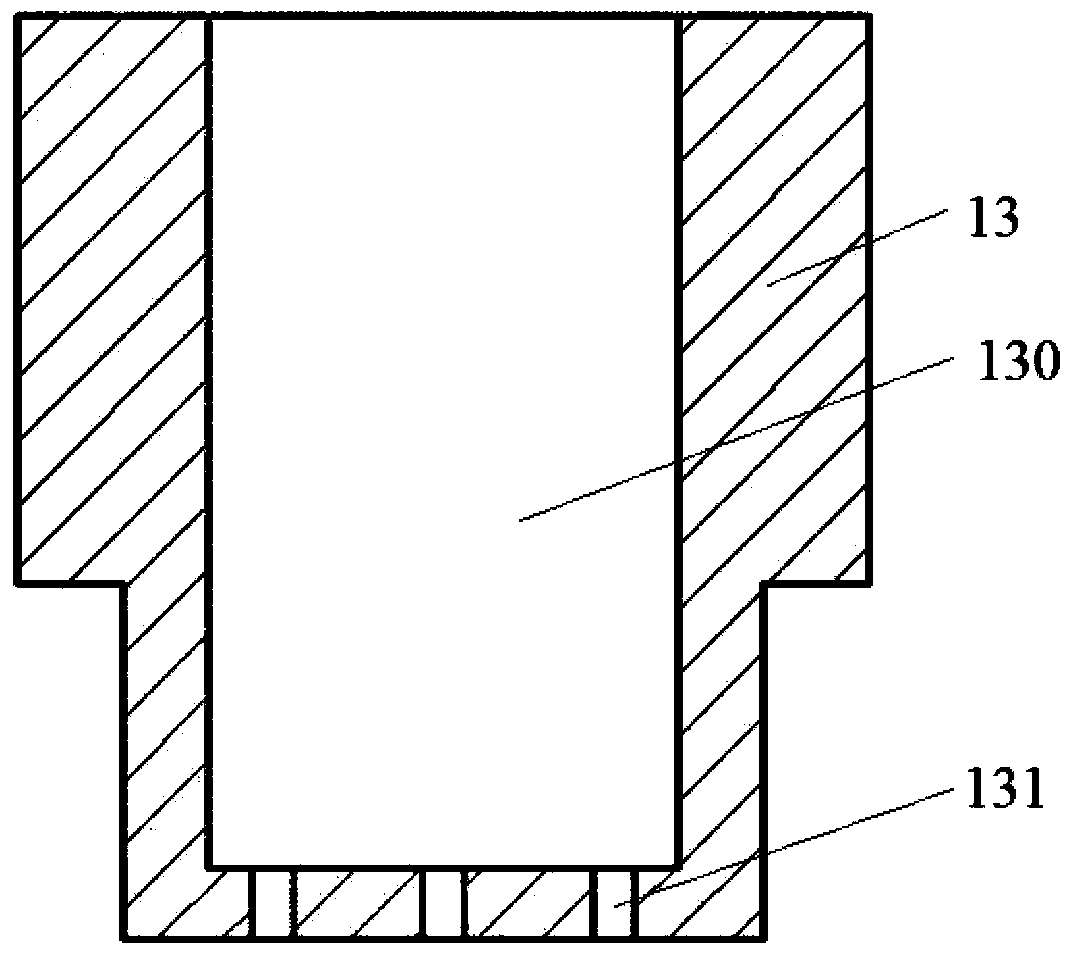

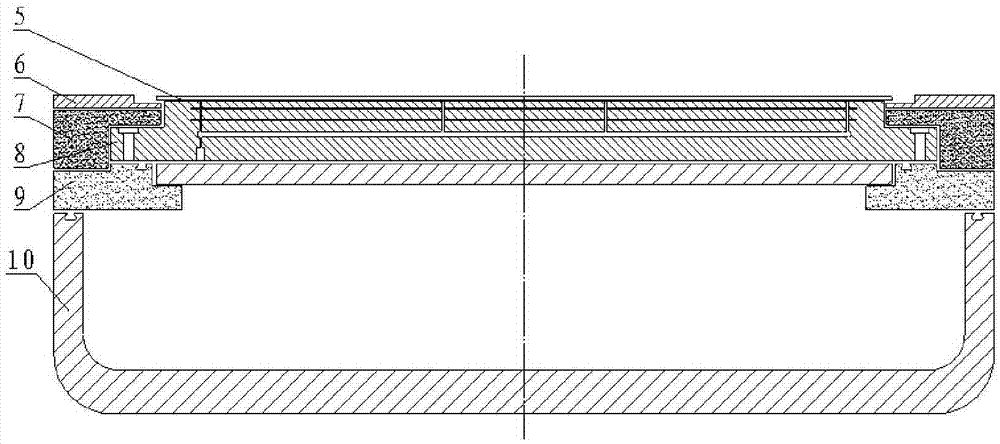

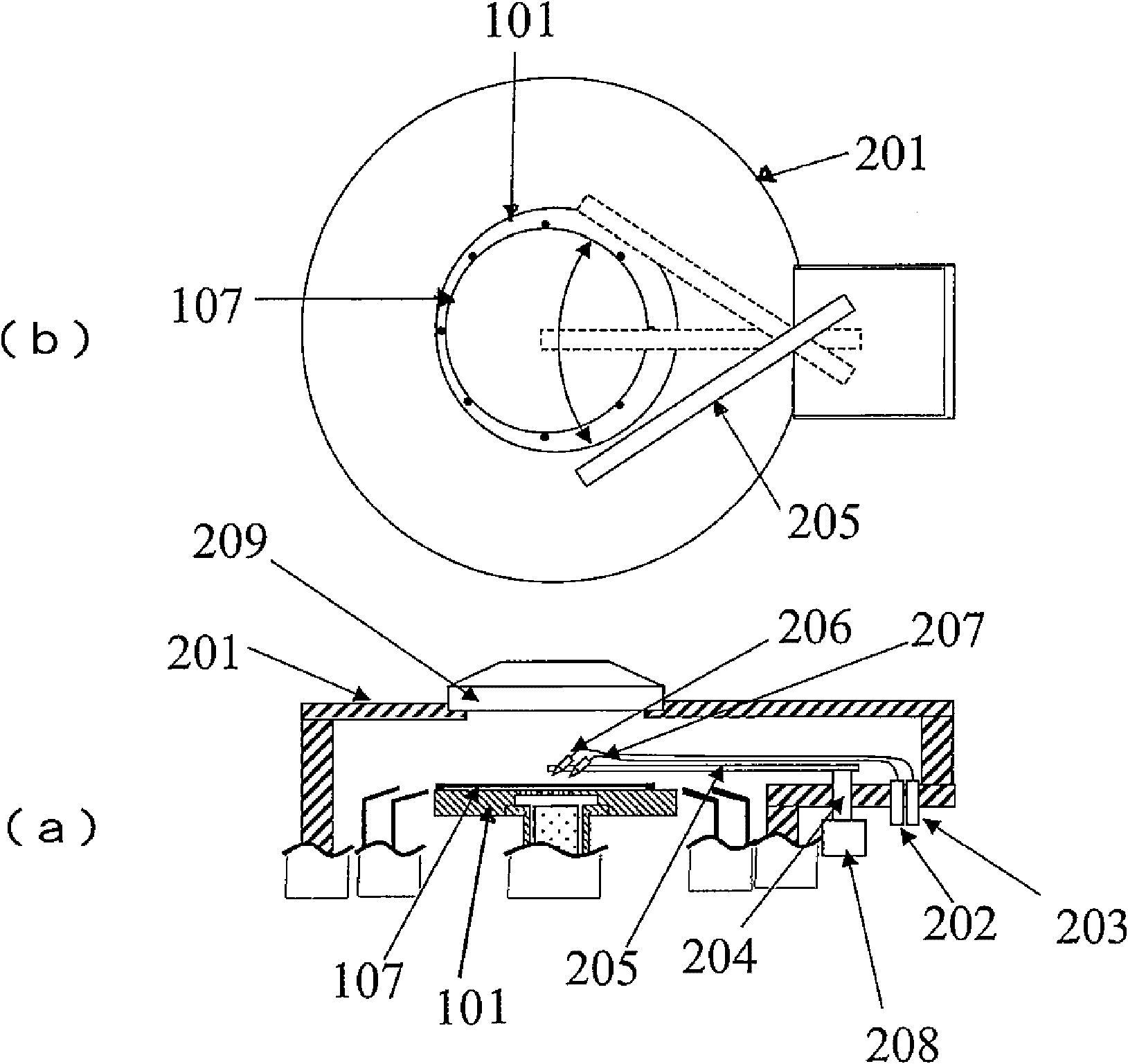

Gas feeding device, reaction cavity, and plasma processing equipment

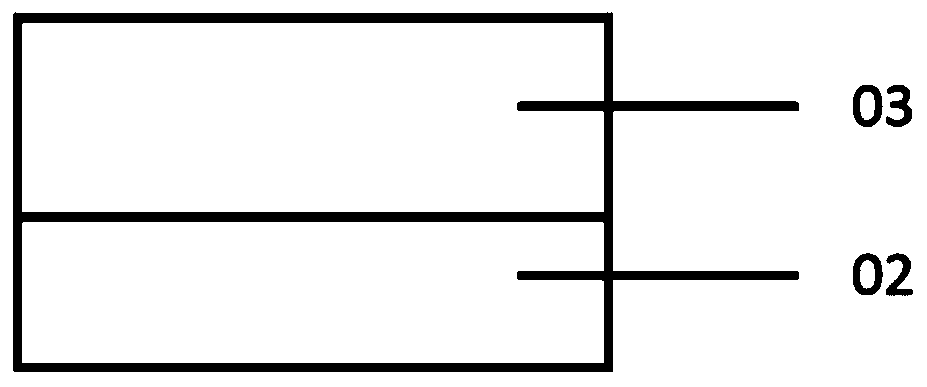

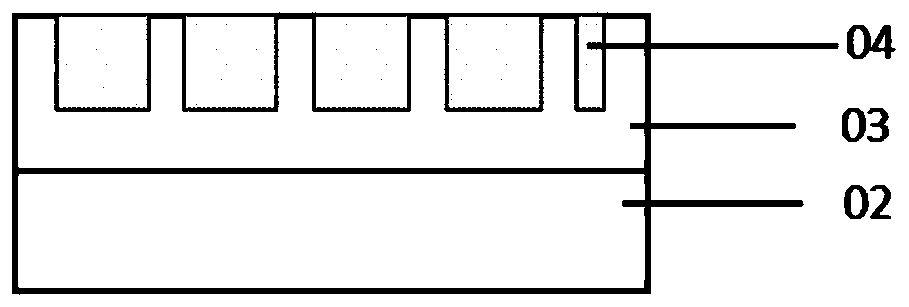

InactiveCN104073782AEvenly distributedUniform thicknessChemical vapor deposition coatingEngineeringPlasma processing

The invention provides a gas feeding device, a reaction cavity, and plasma processing equipment; wherein the gas feeding device comprises a central gas inlet, a diffusion plate unit, and a first driving source, the lower end of the central gas inlet is communicated with the inner of the reaction cavity; the diffusion plate unit and the lower end of the central gas inlet form a horizontal gas inlet, the diffusion plate unit comprises an upper diffusion plate and lower diffusion plate, the upper diffusion plate and the lower diffusion plate are laminated together and are both provided with a plurality of through holes which are used to form a vertical gas inlet that allows the process gas to go through; and the first driving source is used to solely drive the upper diffusion plate to rotate or horizontally move relative to the lower diffusion plate so as to adjust the cross section area of the vertical gas inlet. The gas feeding device can adjust the gas flow of different areas in the reaction cavity, thus the films that are deposited on each processed tools have a uniform thickness, and the technology uniformity is improved.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

Superior fill conditions in a replacement gate approach by corner rounding prior to completely removing a placeholder material

InactiveUS8048792B2Efficient removalIncrease of a gate openingSemiconductor/solid-state device manufacturingSemiconductor devicesMaterial ErosionIntermediate state

In a replacement gate approach, a superior cross-sectional shape of the gate opening may be achieved by performing a material erosion process in an intermediate state of removing the placeholder material. Consequently, the remaining portion of the placeholder material may efficiently protect the underlying sensitive materials, such as a high-k dielectric material, when performing the corner rounding process sequence.

Owner:GLOBALFOUNDRIES INC

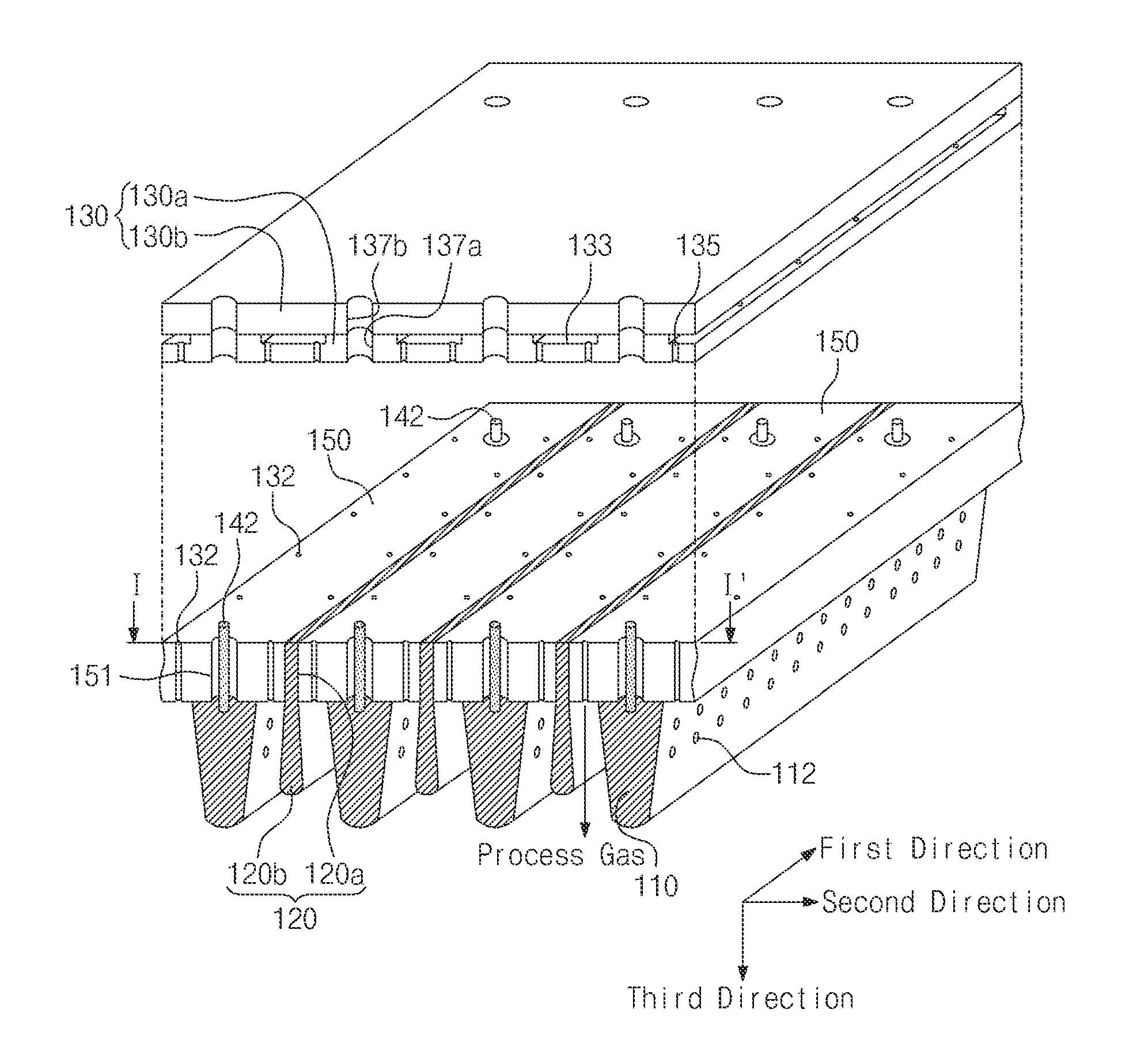

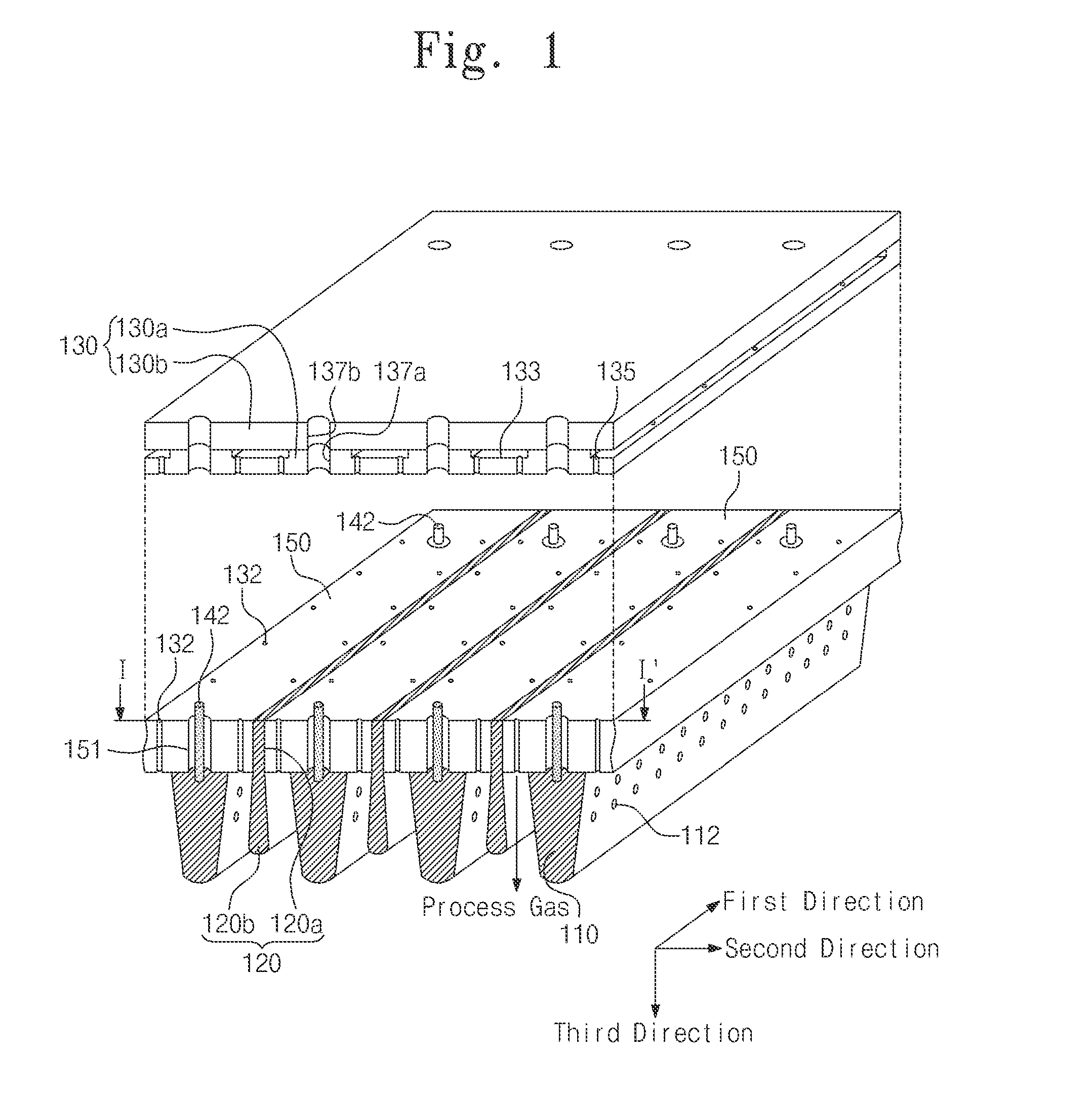

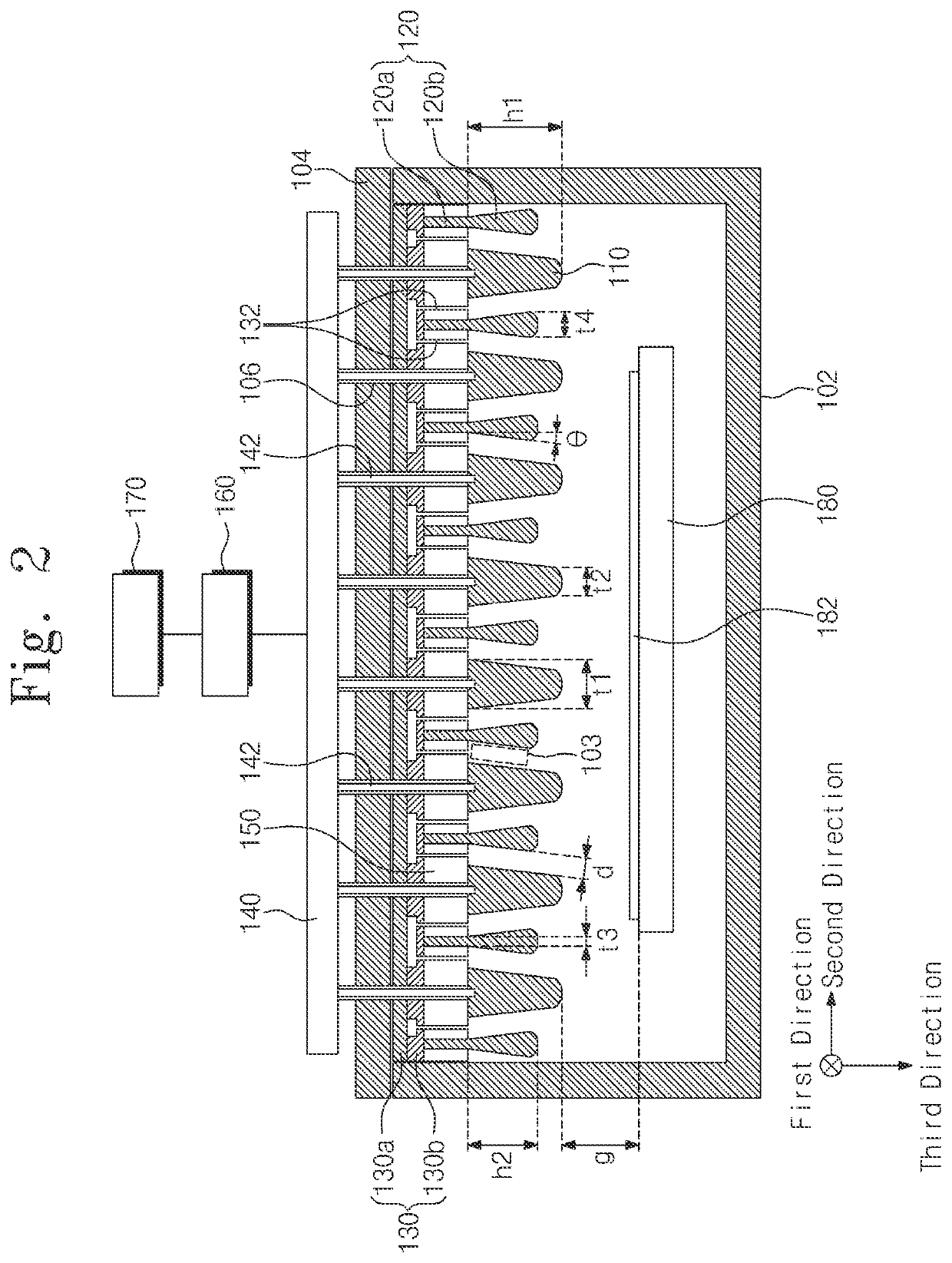

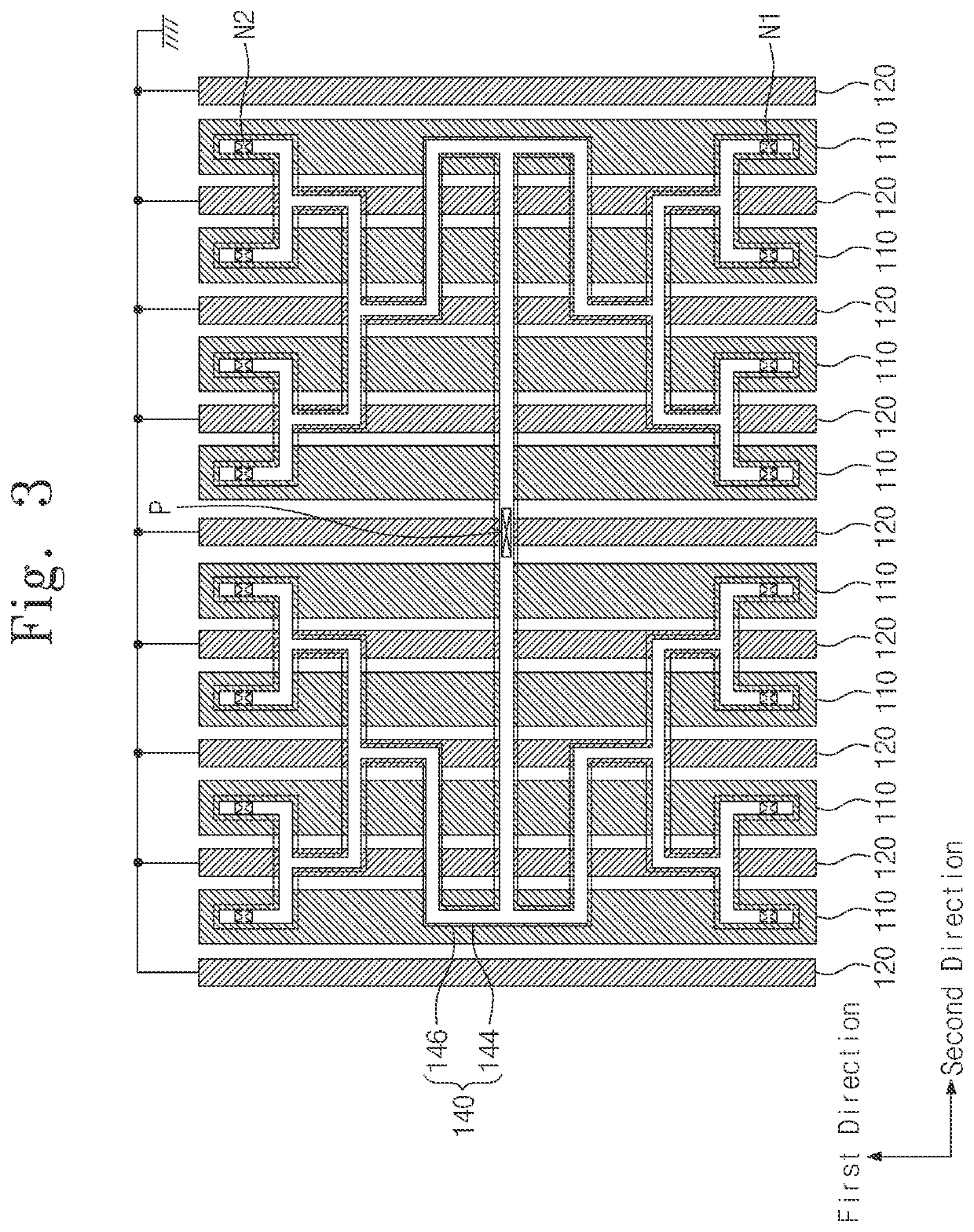

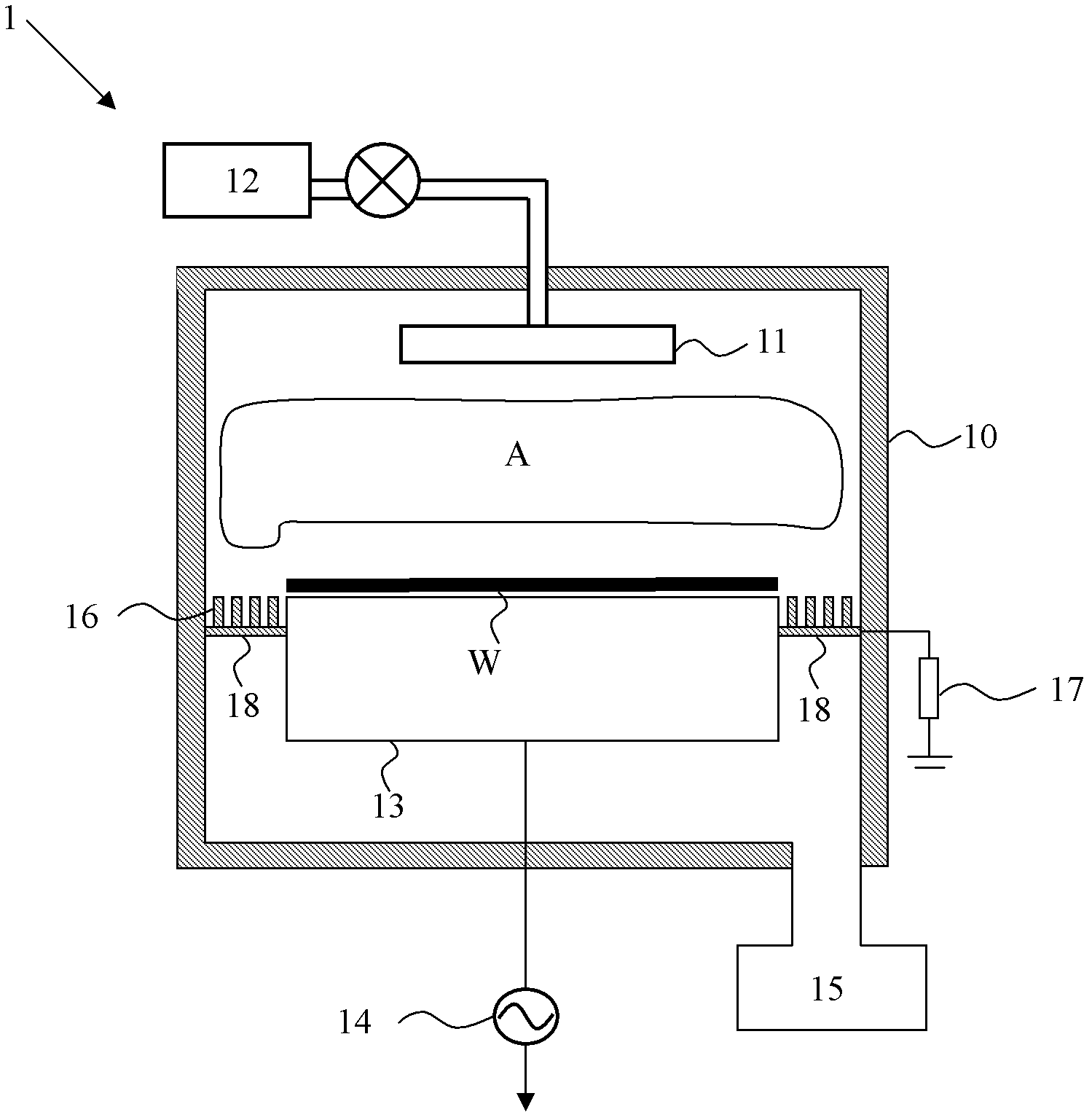

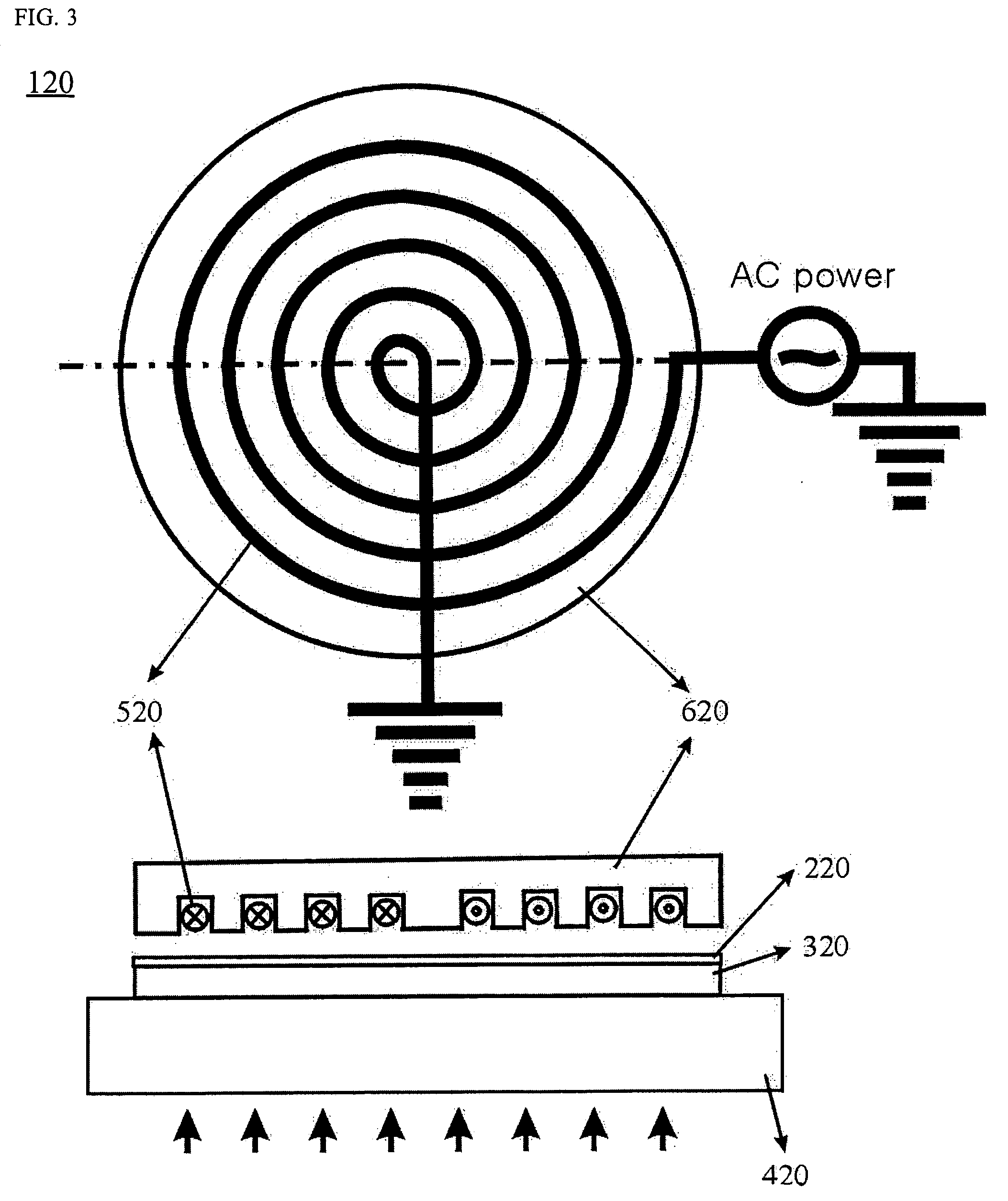

Plasma generating apparatus and substrate processing apparatus

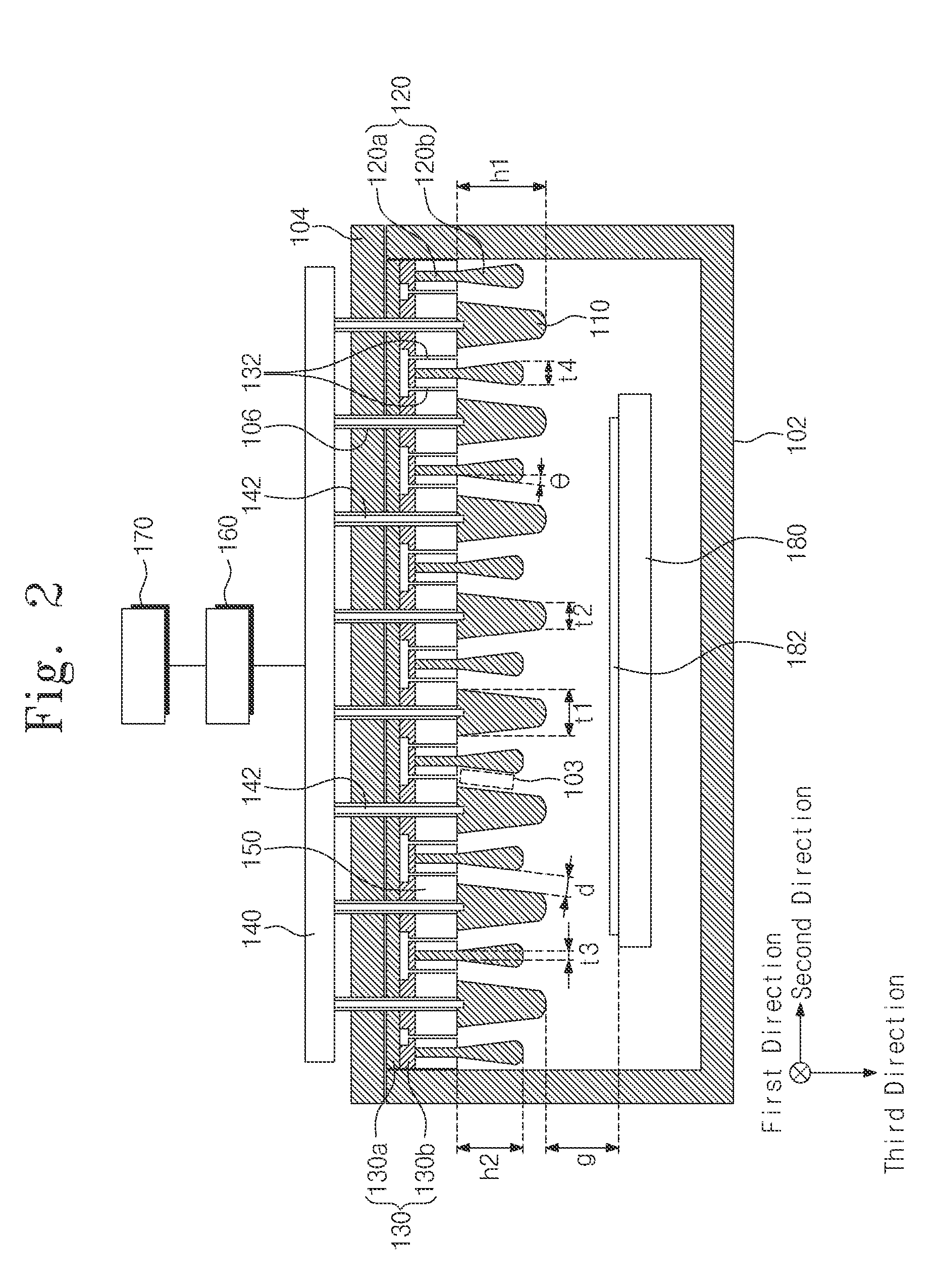

ActiveUS20140007812A1Improve process uniformityFast processingElectric discharge tubesElectric arc lampsEngineeringElectrical and Electronics engineering

Provided are a plasma generating apparatus and a substrate treating apparatus. The plasma generating apparatus includes a plurality of ground electrodes arranged inside a vacuum container and extending parallel to each other and power electrodes arranged between the ground electrodes. An area where a distance between the ground electrode and the power electrode is constant exists, and the power electrodes are tapered in a direction facing the substrate. The power electrodes are connected to an RF power source, and height of the power electrode is greater than that of the ground electrode in the direction facing the substrate.

Owner:JUSUNG ENG +1

Chemical mechanical grinding method

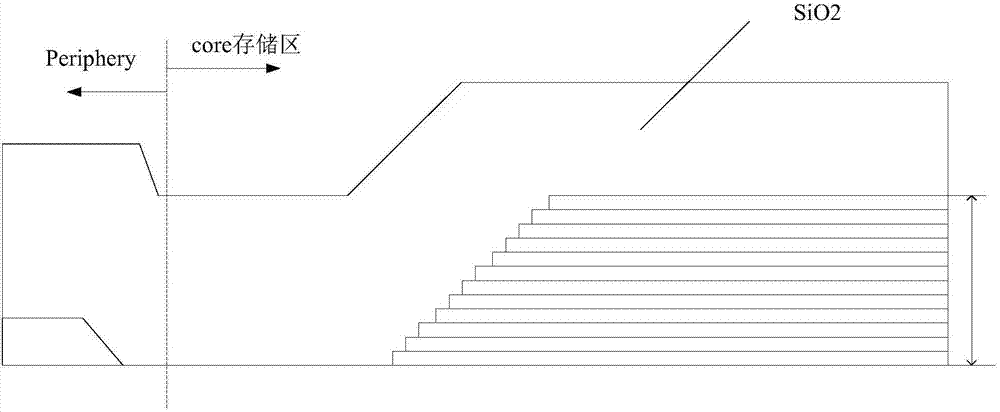

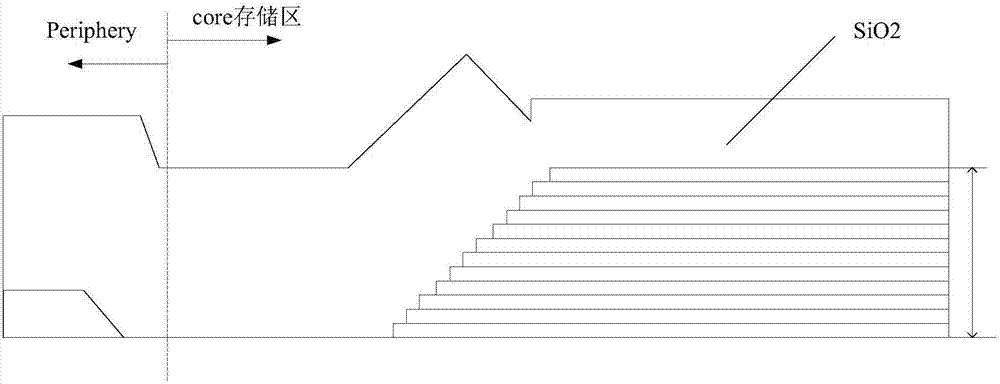

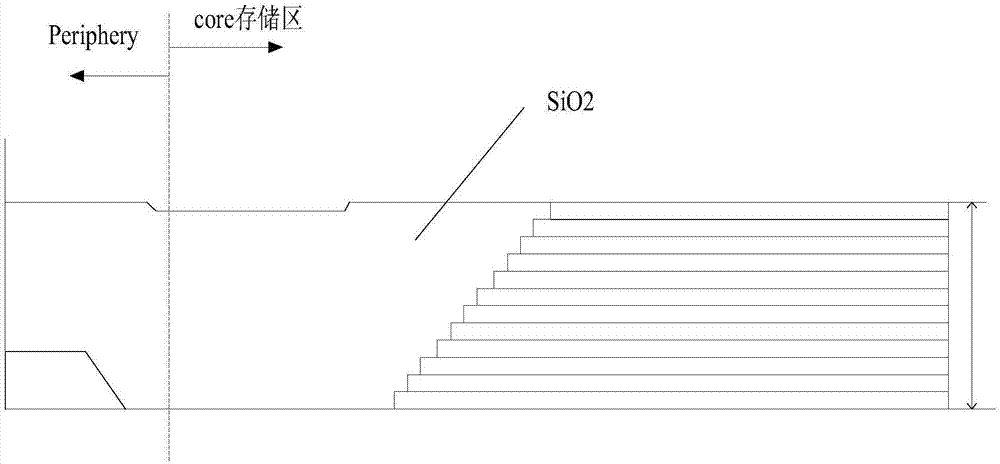

InactiveCN106876263AImprove process uniformityImprove yieldSemiconductor/solid-state device manufacturingMaterials sciencePeripheral

The scheme provides a chemical mechanical grinding method. After an oxide layer is deposited in a peripheral circuit region and a storage region of a three-dimensional storage, the peripheral circuit region is subjected to etching for the first time to enable the lowest height of the oxide layer in the peripheral circuit region to be equivalent to the highest height of the stage in the storage region; a barrier layer is formed on the oxide layer of the three-dimensional storage; then the storage region is subjected to etching for the second time, and the barrier layer and the oxide layer in the three-dimensional storage are subjected to chemical and mechanical grinding at the same time until the lowest height of the oxide layer, corresponding to the stage region, in the storage region is equivalent to the highest height of the stage; and next, the residual barrier layer in the three-dimensional storage is removed. Therefore, the barrier layer is formed on the surface of the oxide layer; and in addition, the removing speed of the barrier layer is slower than that of the oxide layer, so that the additional barrier layer can protect the structure of the storage region, Dishing defect influence in the prior art can be avoided, the overall technological uniformity of the three-dimensional storage can be improved, and the yield is improved.

Owner:YANGTZE MEMORY TECH CO LTD

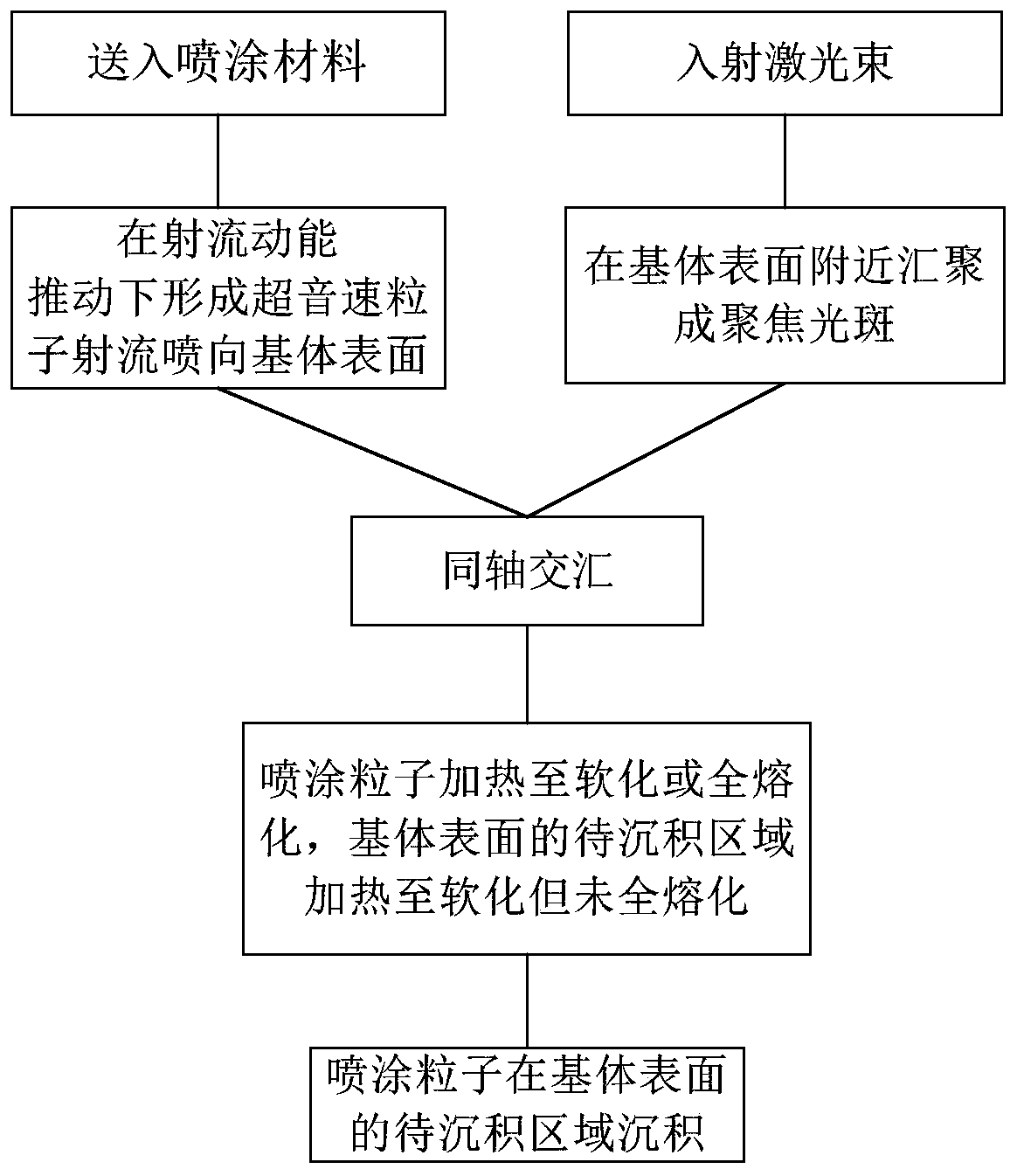

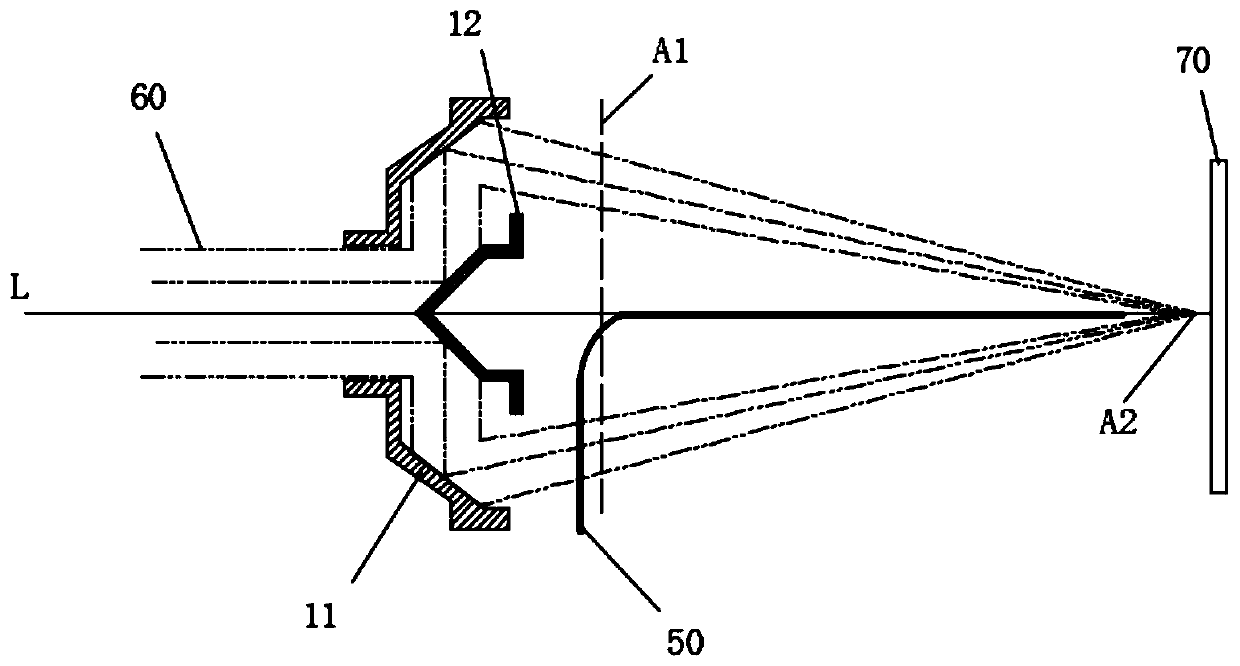

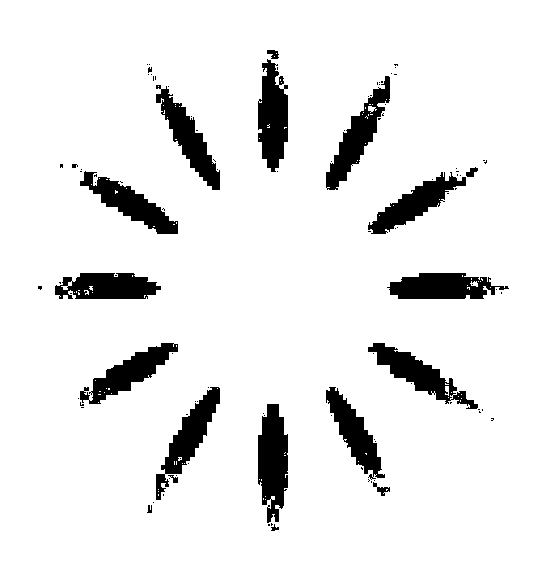

Central coaxial powder feeding type supersonic laser spraying method

ActiveCN109837497AReduce splashAchieve the purpose of supersonic laser sprayingAdditive manufacturing apparatusMolten spray coatingOptoelectronicsLaser beams

The invention discloses a central coaxial powder feeding type supersonic laser spraying method. The central coaxial powder feeding type supersonic laser spraying method comprises the steps that incident one or more laser beams are converged into one or more focusing light spots near the surface of a substrate through optical transformations; spraying materials are input into hollow regions of thelaser beams to be transmitted and form a bunch of supersonic particle jet flow driven by jet flow kinetic energy and the jet flow is sprayed to the surface of the substrate; when the particle jet flowintersects with the coaxial focusing light spots, laser energy is absorbed by sprayed particles and the sprayed particles are heated to soften or melt completely, meanwhile, a part of the laser energy is absorbed by the surface of the substrate, and the surface of the substrate is heated to soften but not melt completely; and a large number of the sprayed particles is subjected to supersonic collision in a to-be-deposited area on the surface of the substrate, and deposition is realized. According to the processes, the particle jet flow and the focusing light spots move continuously together relative to the surface of the substrate, and the sprayed particles deposit and superimpose continuously to form a coating. According to the central coaxial powder feeding type supersonic laser spraying method, by means of a series of the optical transformations, the incident laser beams are transformed and converged into annular or annular-like tiny focusing light spots, and the purpose of the supersonic laser spraying with central coaxial powder feeding is realized.

Owner:NAT INNOVATION INST OF DEFENSE TECH PLA ACAD OF MILITARY SCI

Plasma generating apparatus and substrate processing apparatus

ActiveUS10553406B2Improve process uniformityFast processingElectric discharge tubesEngineeringMaterials science

Owner:JUSUNG ENG +1

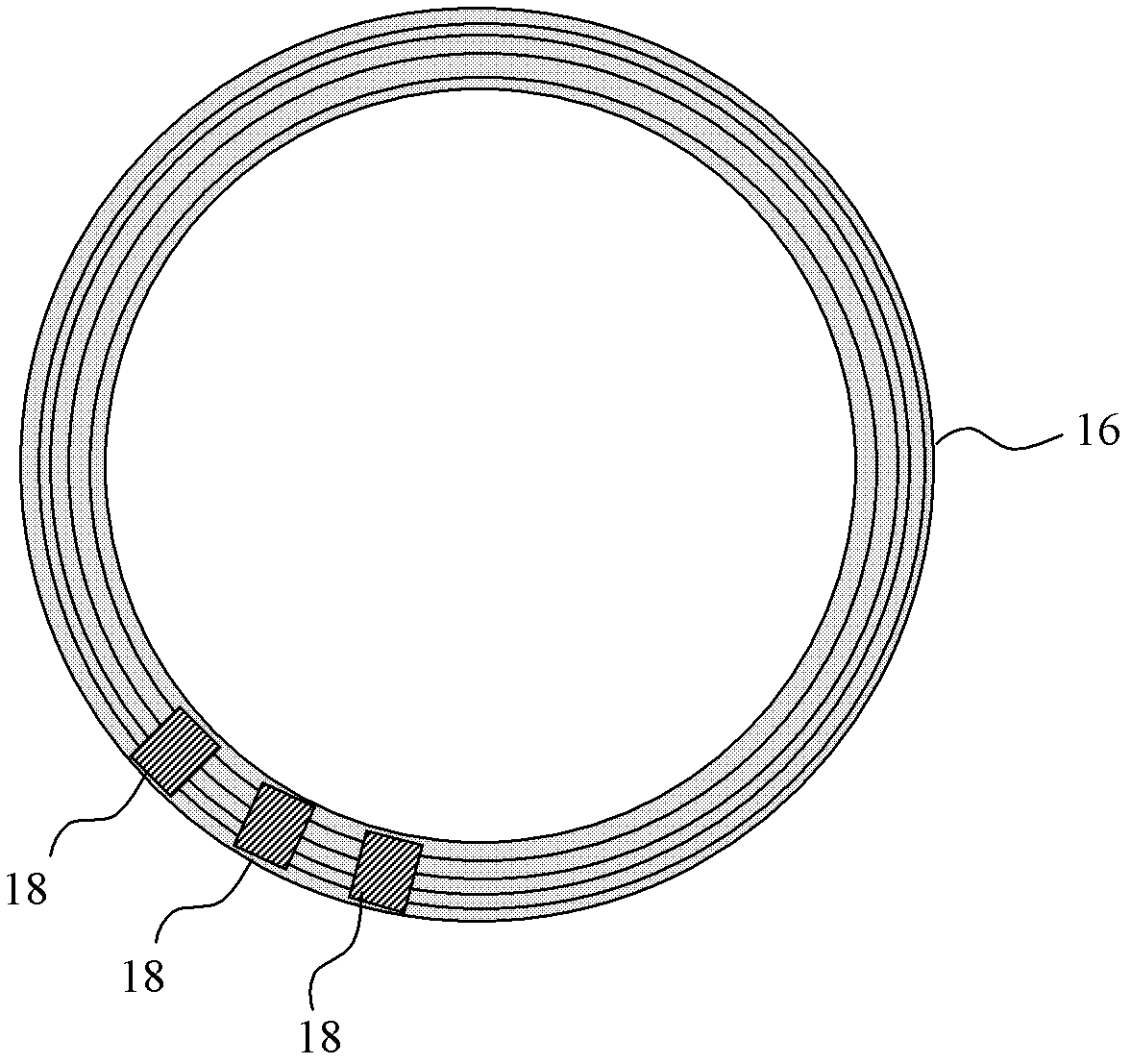

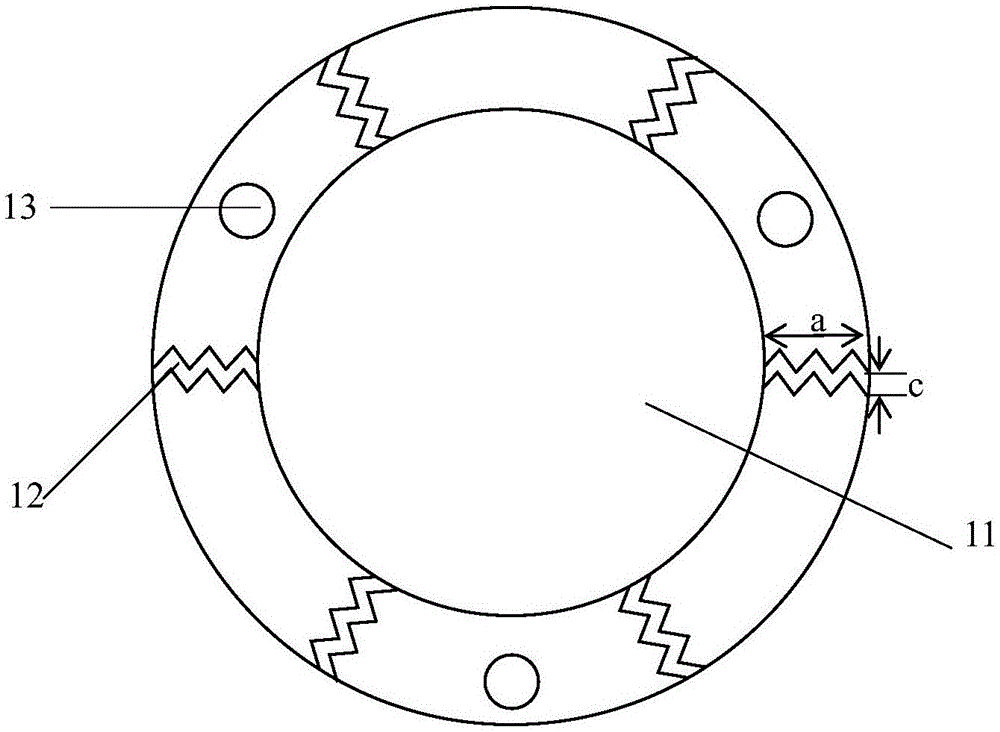

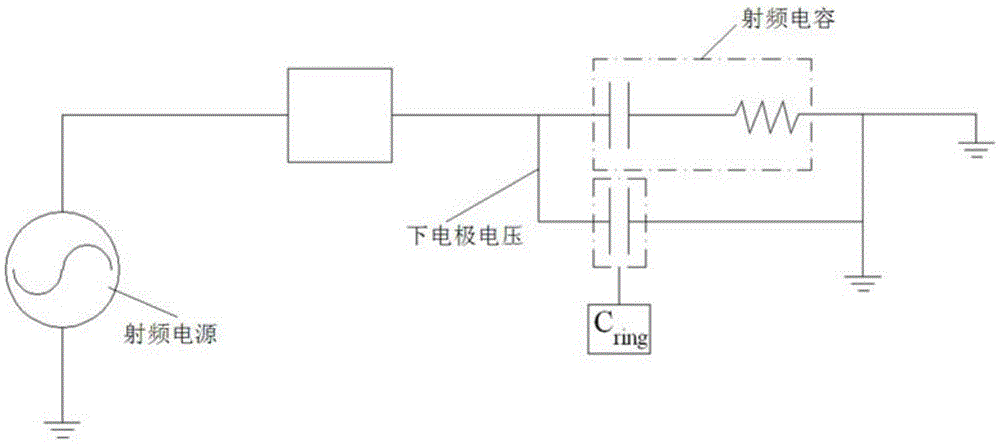

Adjustable limiting ring used for plasma processing device

ActiveCN103177925AImprove process uniformityImprove the problem of asymmetry in the process areaElectric discharge tubesEngineeringPlasma processing

The invention provides an adjustable limiting ring used for a plasma processing device. The limiting ring is used for controlling discharge of redundant gas in a manufacturing process and neutralizing redundant charged particles; at least a baffle is arranged below the limiting ring; the baffle is parallel with the limiting ring and is at least partially overlapped with the limiting ring in the vertical direction; and the baffle is provided with a plurality of discharge channels. The adjustable limiting ring used for the plasma processing device can improve regional asymmetry in the plasma manufacturing process, and further improve non-uniformity of the manufacturing process of substrates.

Owner:ADVANCED MICRO FAB EQUIP INC CHINA

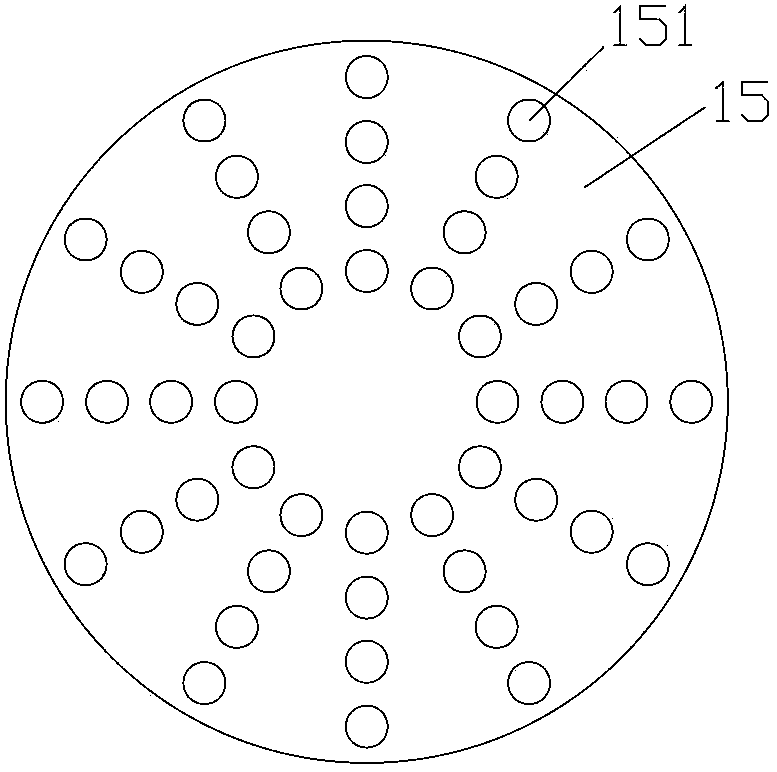

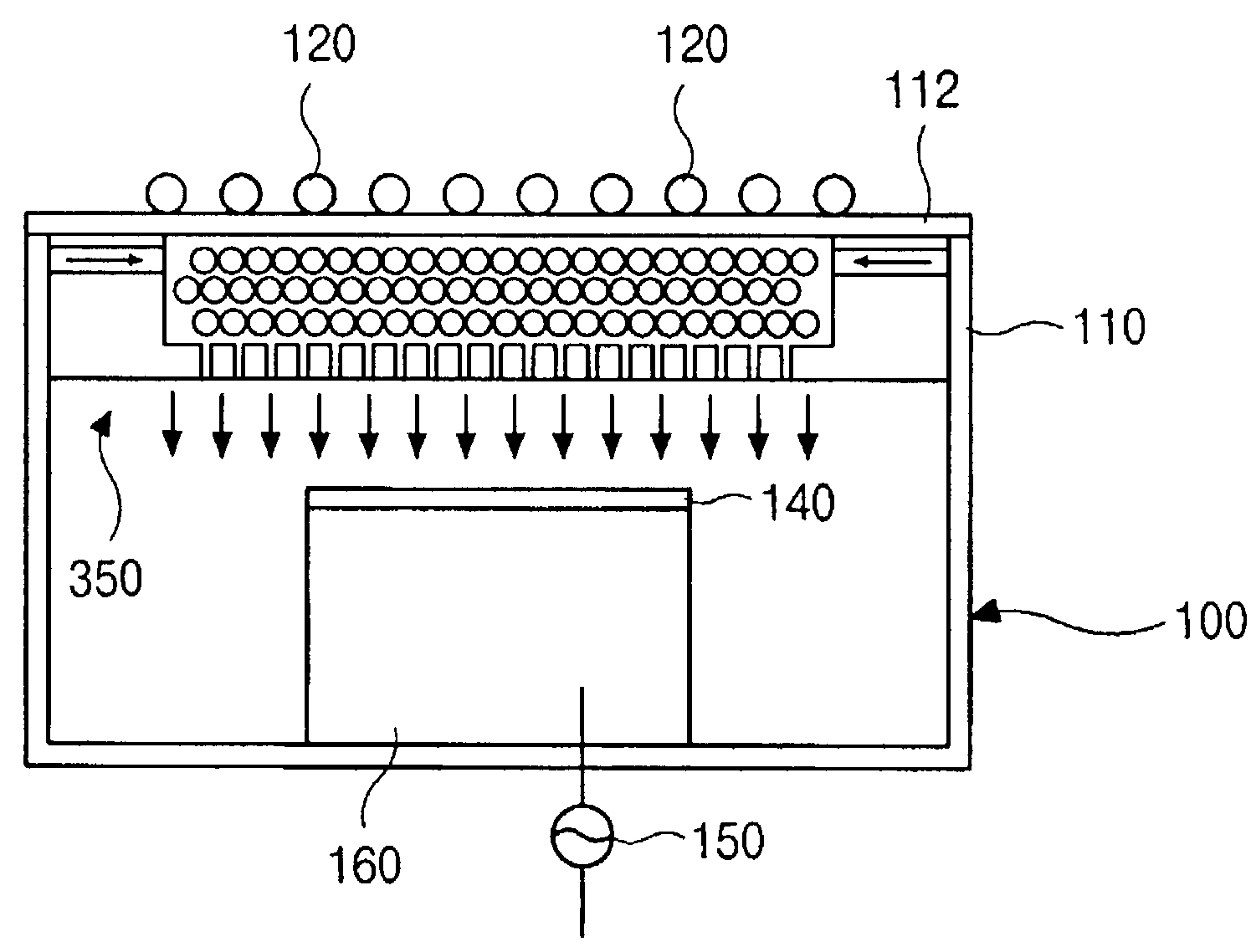

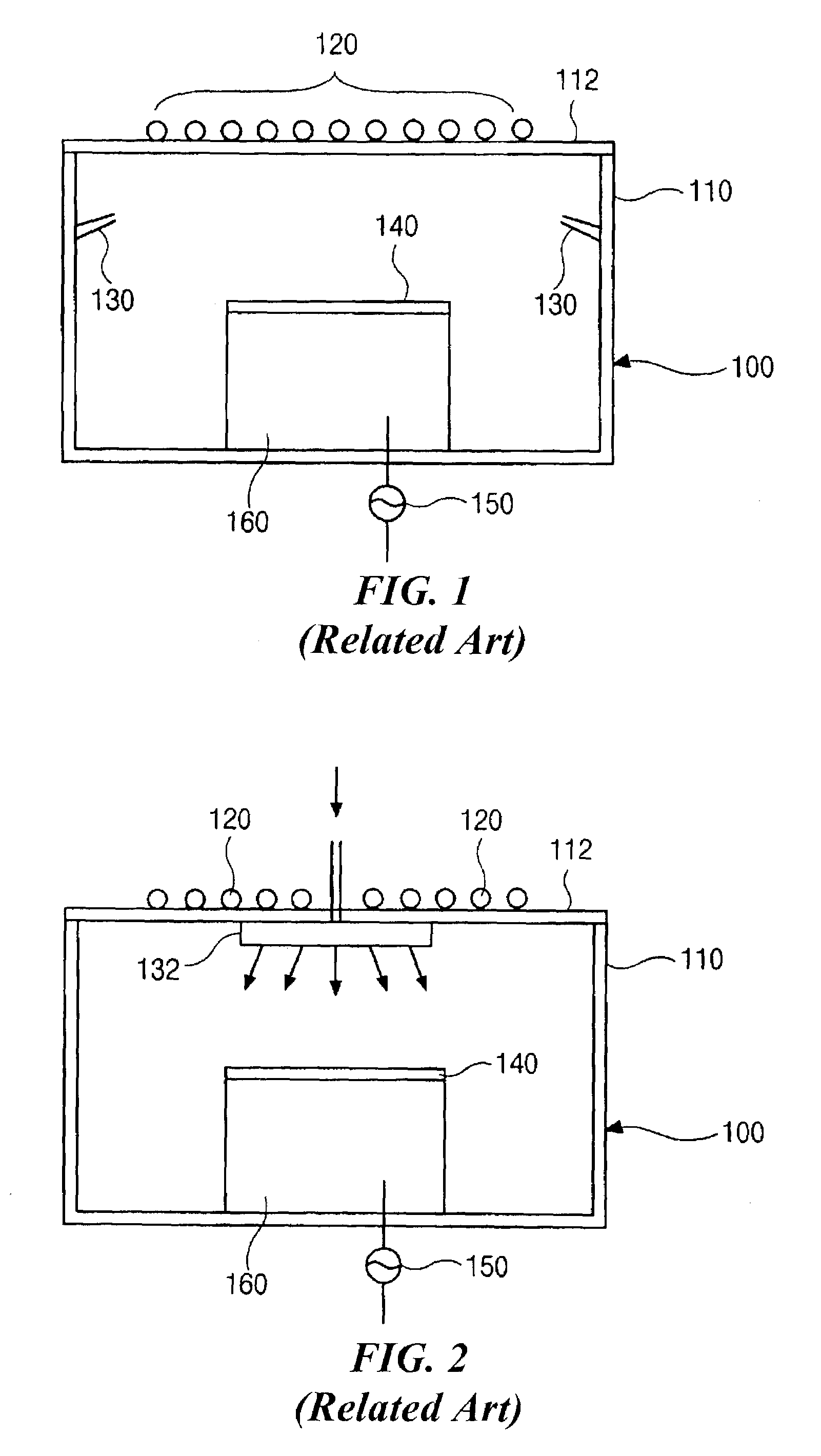

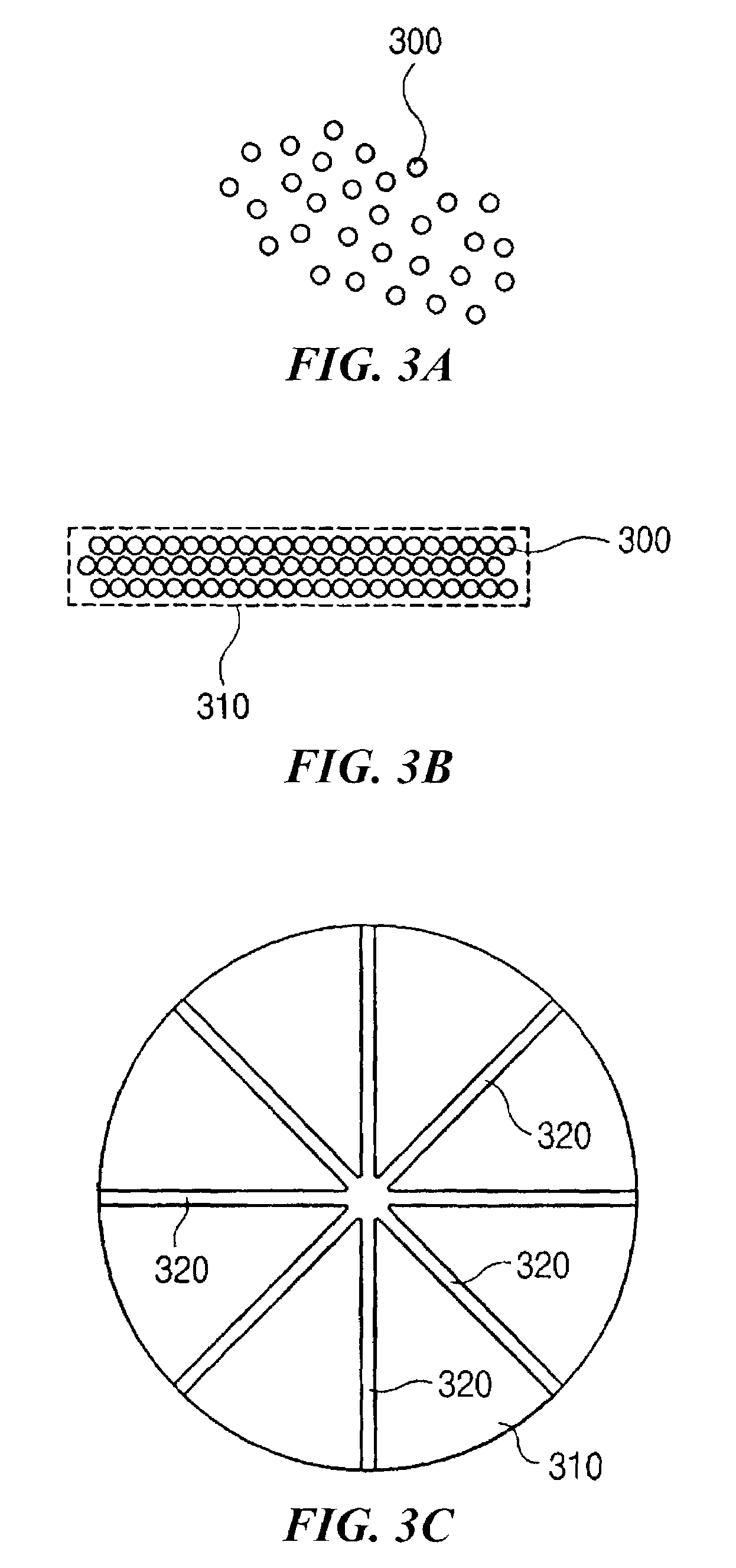

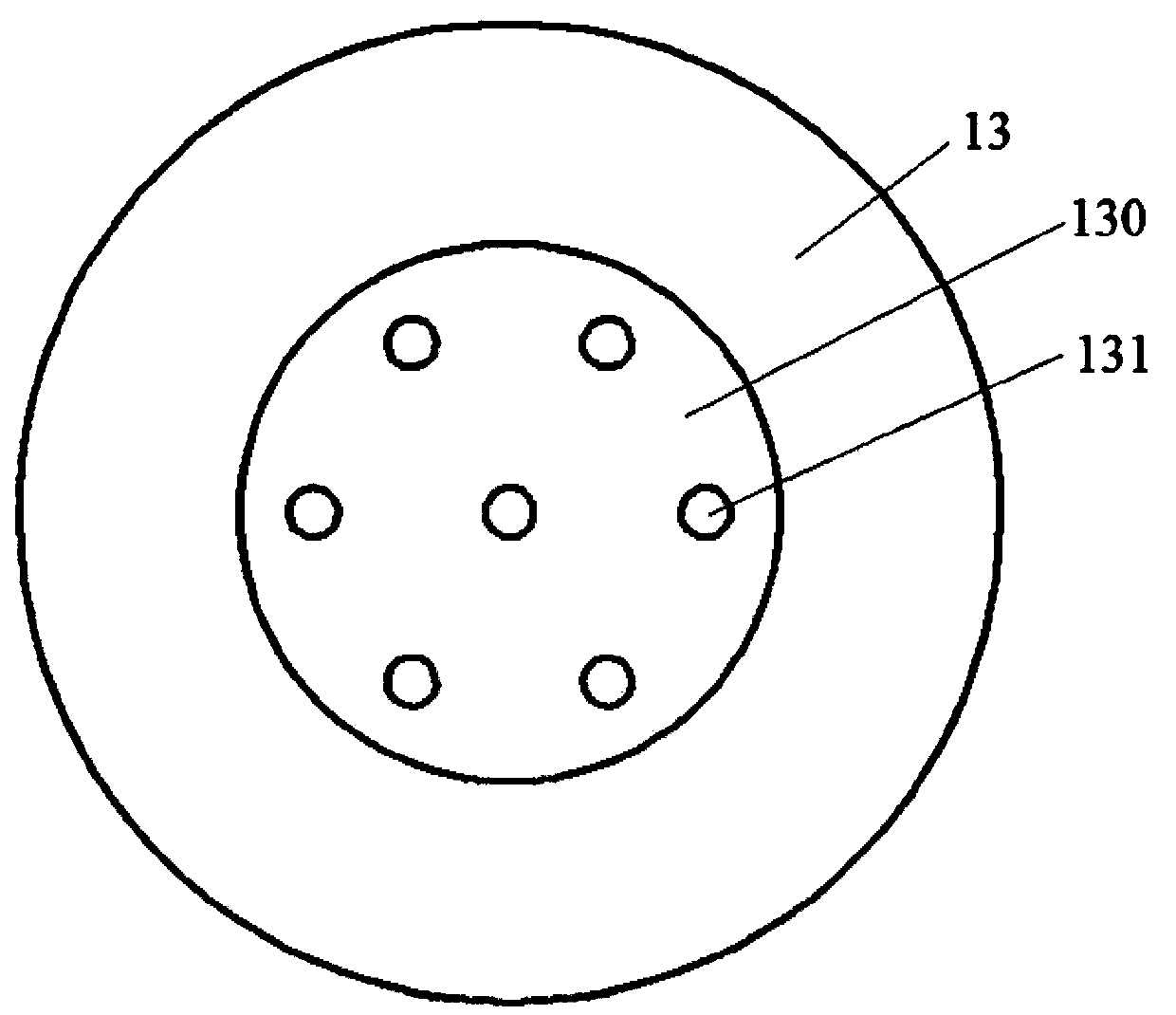

Gas diffussion plate for use in ICP etcher

InactiveUS20030136516A1Improve process uniformityElectric discharge tubesSemiconductor/solid-state device manufacturingDiffusionInductively coupled plasma

A gas diffusion plate supplying process gases into a chamber of an ICP (inductively coupled plasma) etcher is provided in the present invention. The gas diffusion plate includes a porous plate comprised of a plurality of balls and formed by compressing and curing the plurality of balls, the porous plate having a circular planar shape; a plurality of gas flow grooves formed on an upper surface of the porous plate; and a gas distribution plate having a plurality of gas-feed holes at the bottom thereof and a plurality of gas-feed passages in the side portion thereof, the gas distribution plate surrounding lower and side portions of the porous plate.

Owner:JUSUNG ENG

Symmetrical vapor deposition equipment reaction cavity

ActiveCN104862667AEasy to cleanReduce depositionChemical vapor deposition coatingCooling chamberProduct gas

The invention discloses a symmetrical vapor deposition equipment reaction cavity. The reaction cavity mainly comprises a gas input body, a heater, a slide carrying disc, a slide carrying disc support, a reaction cavity housing, a heater, a heater support, a reaction gas channel, a cavity pedestal and a tail gas outlet. The reaction cavity is characterized in that the tail gas outlet is arranged at the center of the cavity pedestal, a gas chamber is arranged in the middle of the cavity pedestal and a cooling chamber is arranged around the gas chamber. The tail gas outlet is arranged at the center of the cavity pedestal so that gas inlet and outlet symmetrical distribution is realized and uniformity of gas flowing distribution in the reaction cavity is guaranteed and improved. Tail gas goes through the gas chamber of the cavity pedestal and cooling surfaces of the gas chamber of the cavity pedestal cool the reaction tail gas so that the reaction tail gas is uniformly cooled, precipitates are reduced and tail gas treatment system damage caused by a high reaction tail gas temperature is avoided.

Owner:甘志银

Adjustable constraint device used for plasma processing device

ActiveCN103187234AImprove process uniformityImprove the problem of asymmetry in the process areaElectric discharge tubesEngineeringMechanical engineering

The invention discloses an adjustable plasma constraint device applied to a plasma processing device, wherein the plasma constraint device is arranged between a processing area and an exhaust area, and comprises electric grounding elements, conducting elements and spacing elements. The conducting elements are arranged on the electric grounding elements, the conducting elements and the electric grounding elements are mutually insulated, and a plurality of exhaust channels are arranged on the conducting elements. Each spacing element is arranged between the electric grounding element and the conducting element, wherein the spacing elements are made of insulation materials. According to the adjustable plasma constraint device applied to the plasma processing device, the asymmetry of the plasma processing area can be improved, and processing non-uniformity of substrates is further improved.

Owner:ADVANCED MICRO FAB EQUIP INC CHINA

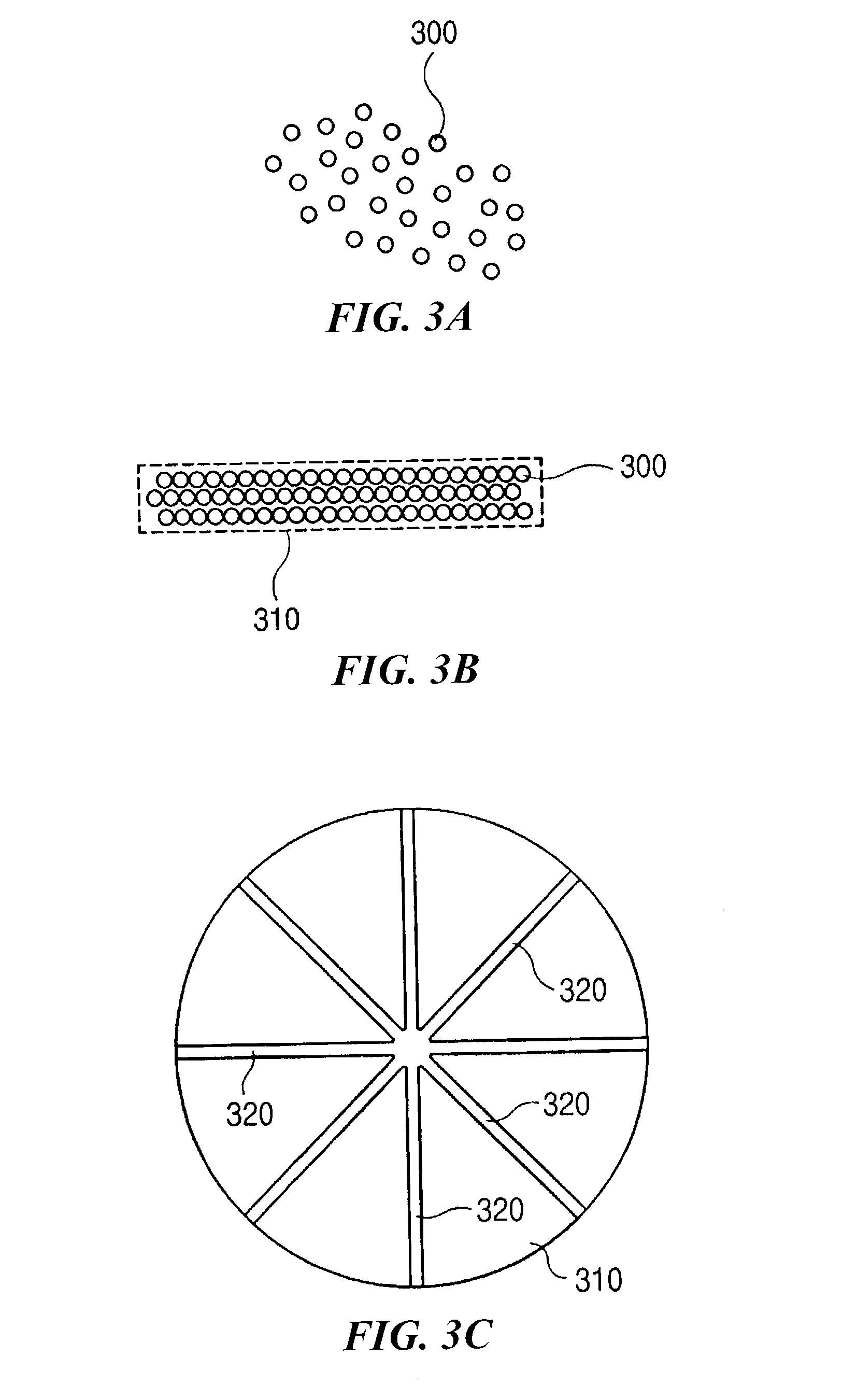

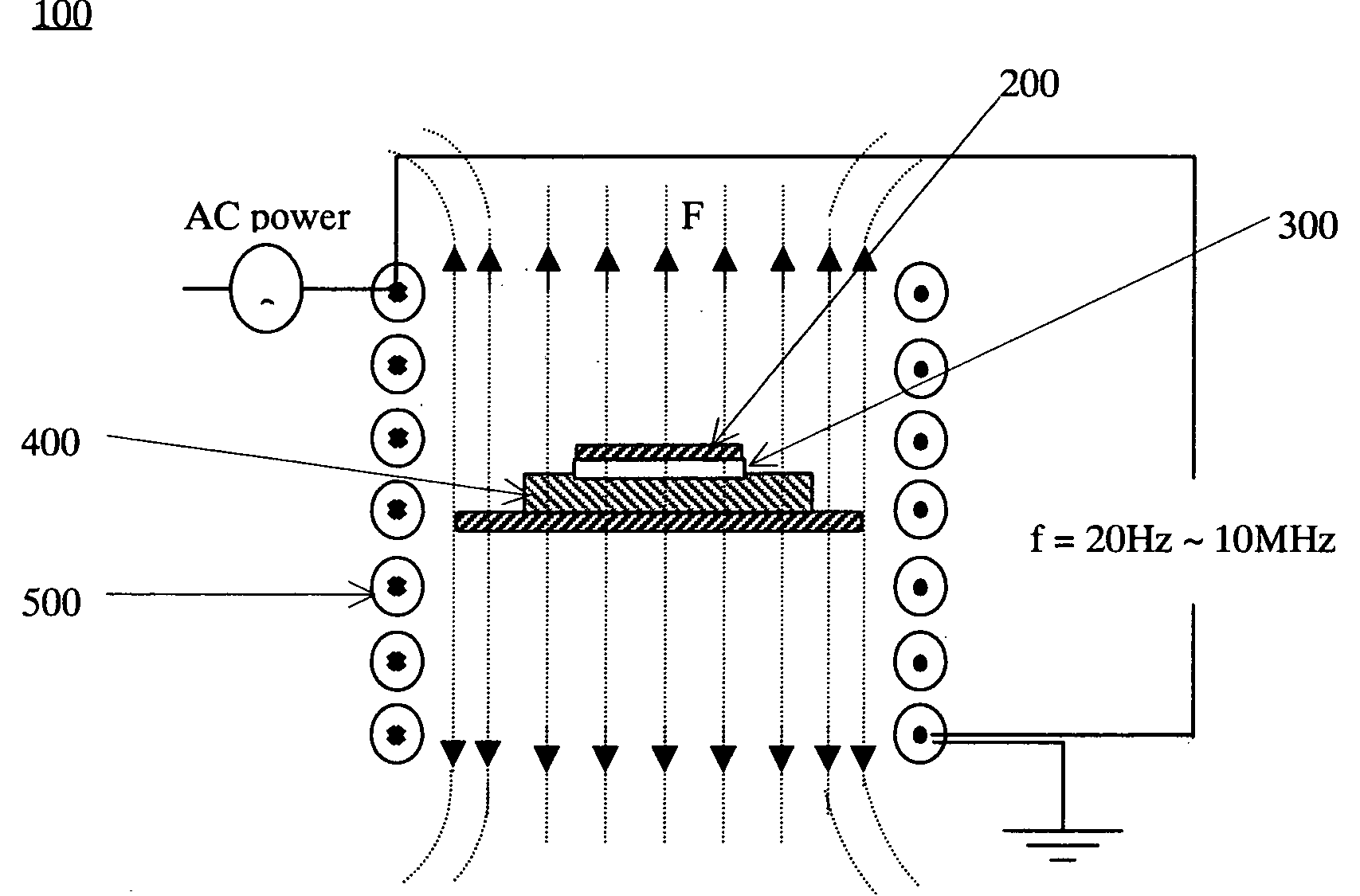

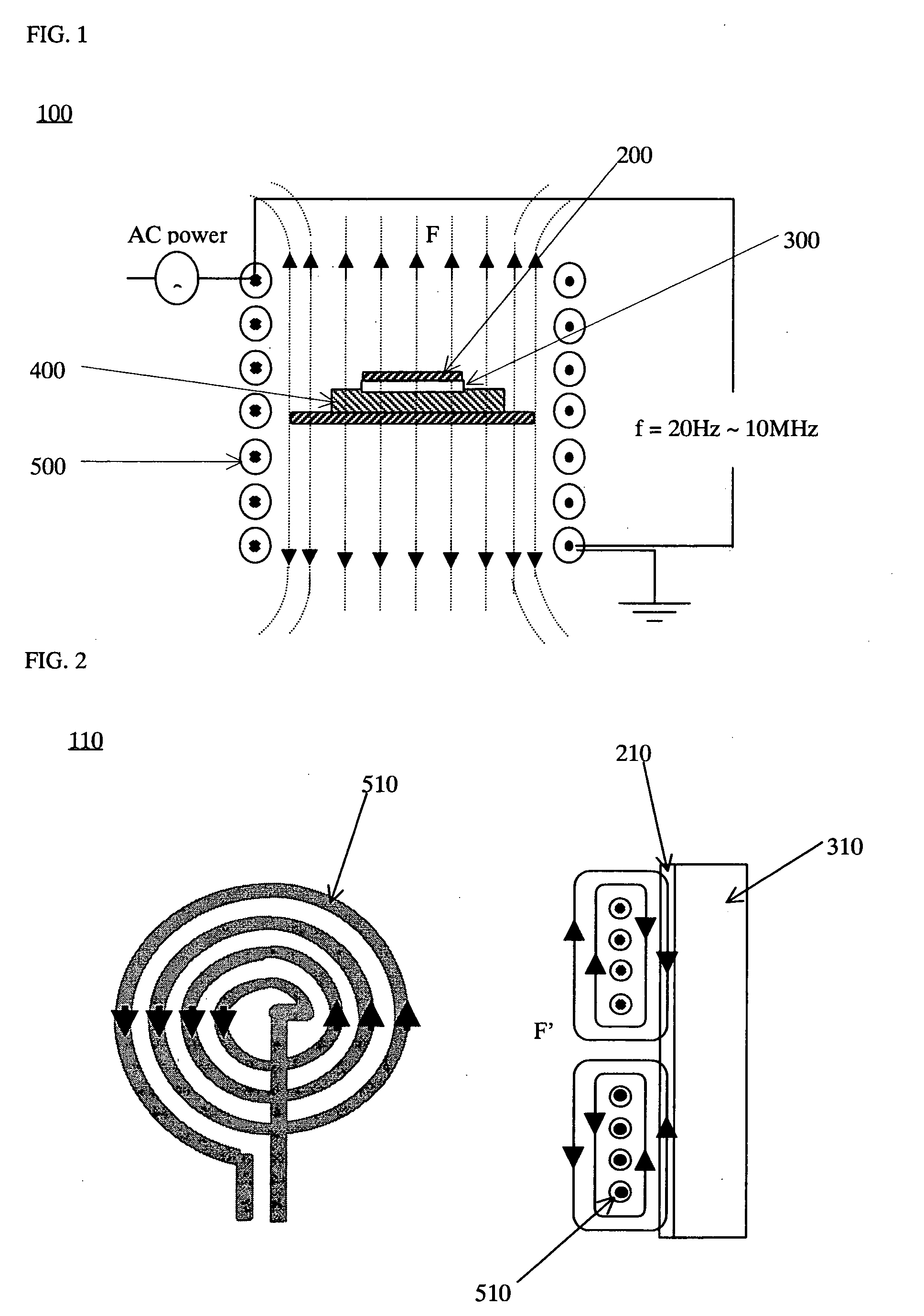

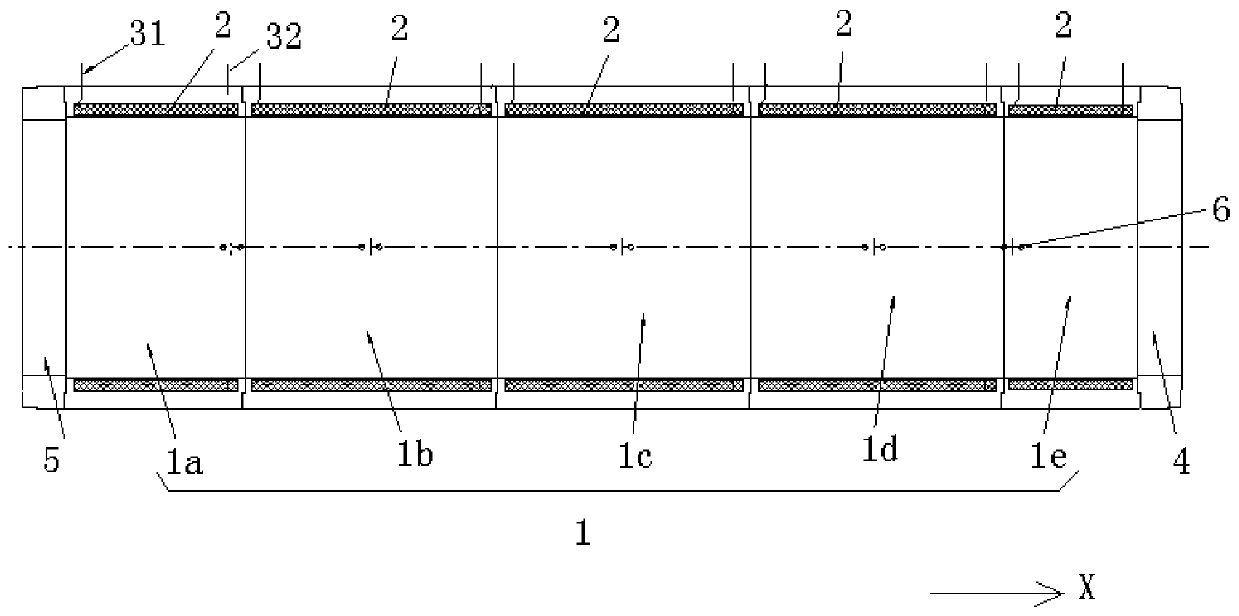

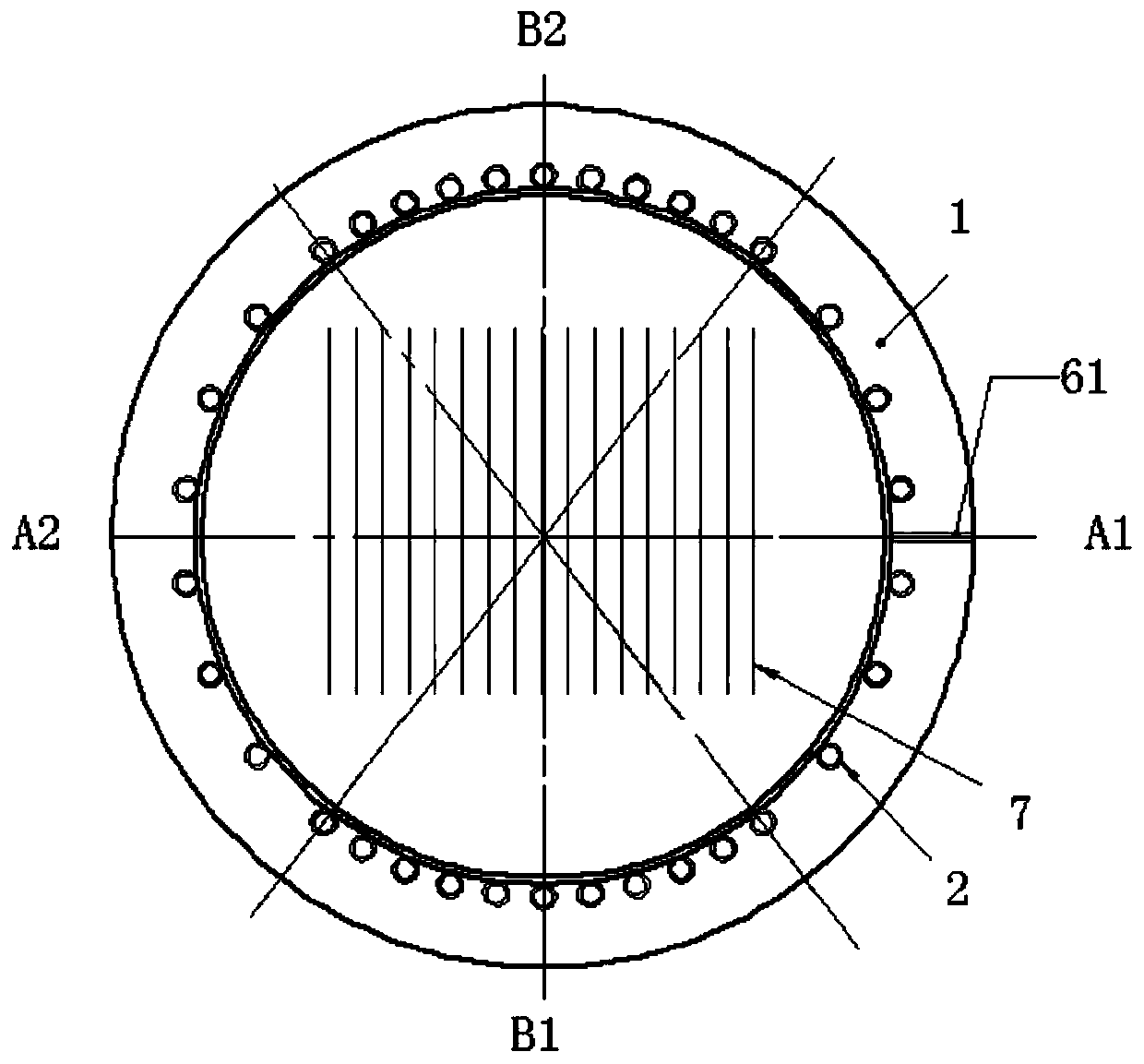

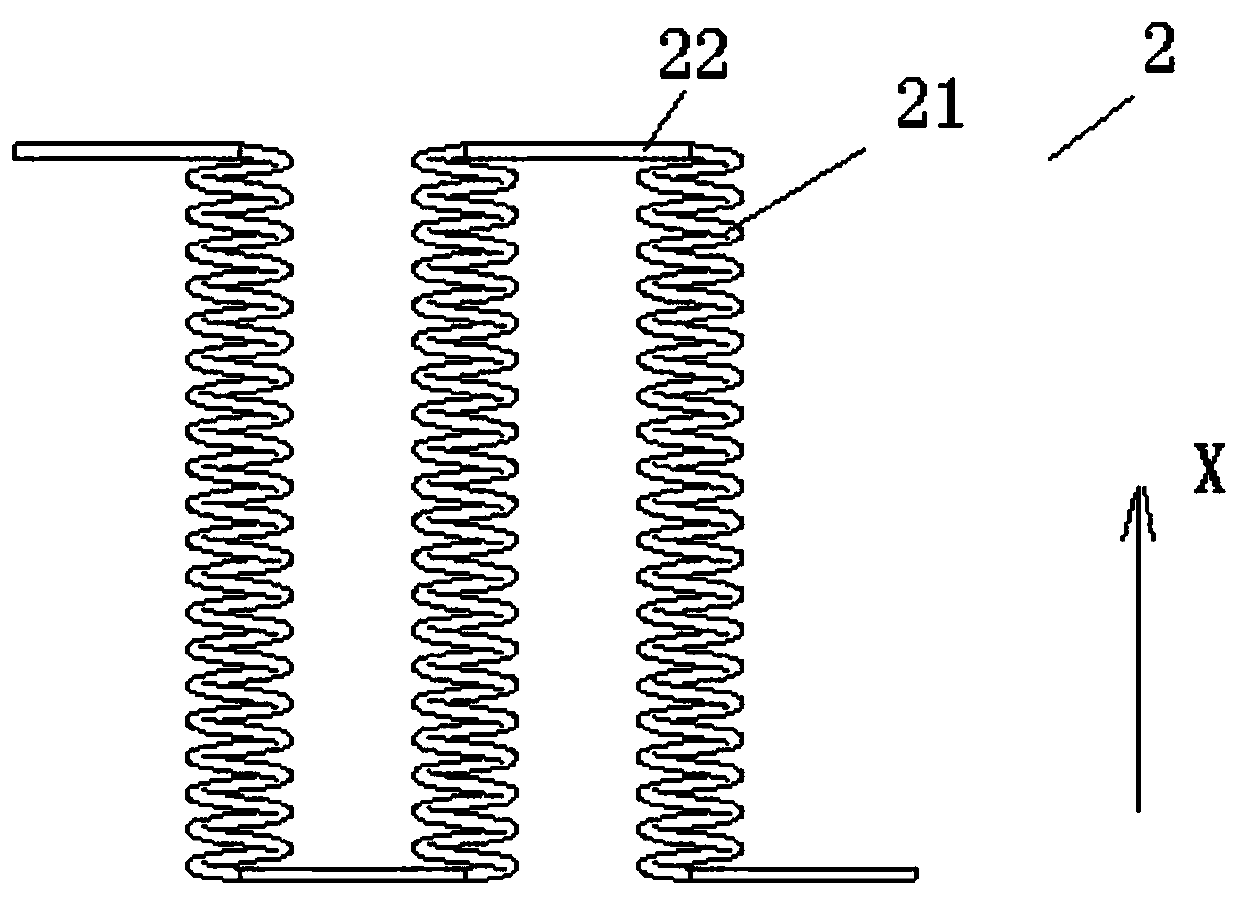

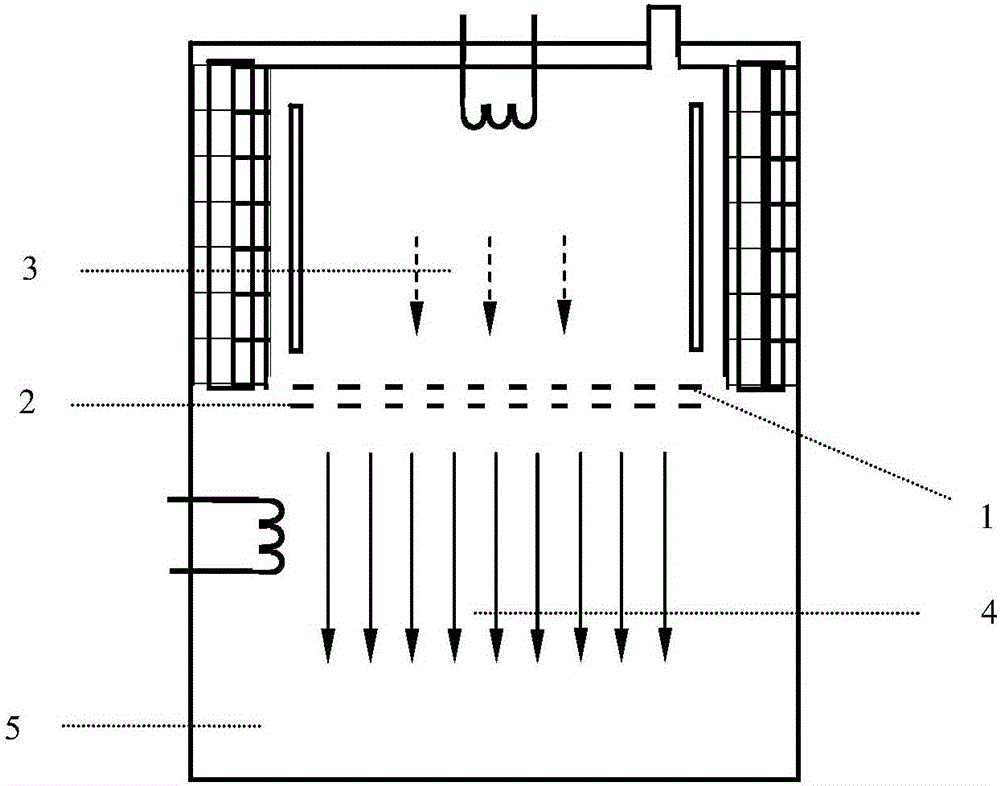

Methods and apparatuses for heat treatment of semiconductor films upon thermally susceptible non-conducting substrates

InactiveUS20050186723A1Maximize goalImprove process uniformitySemiconductor/solid-state device manufacturingIn planeSusceptor

In a method for crystallization or dopant activation heat treatment of a semiconductor film upon a thermally susceptible non-conducting substrate lying onto a susceptor, an induction coil is disposed in close proximity of the semiconductor film and disposed with the electrical current direction of the coil aligned parallel to the in-plane direction of the semiconductor film, a magnetic core is disposed around the coil to strengthen and concentrate a magnetic field generated by the coil onto the semiconductor film, and an alternating electrical current is introduced in the induction coil to generate an alternating magnetic field through the semiconductor film heated by the susceptor to the extent that the semiconductor film can be induction-heated.

Owner:VIATRON TECH INC

Gas diffusion plate for use in ICP etcher

InactiveUS7156950B2Improve process uniformityElectric discharge tubesSemiconductor/solid-state device manufacturingDiffusionEngineering

A gas diffusion plate supplying process gases into a chamber of an ICP (inductively coupled plasma) etcher is provided in the present invention. The gas diffusion plate includes a porous plate comprised of a plurality of balls and formed by compressing and curing the plurality of balls, the porous plate having a circular planar shape; a plurality of gas flow grooves formed on an upper surface of the porous plate; and a gas distribution plate having a plurality of gas-feed holes at the bottom thereof and a plurality of gas-feed passages in the side portion thereof, the gas distribution plate surrounding lower and side portions of the porous plate.

Owner:JUSUNG ENG

Heating furnace body and semiconductor device

ActiveCN110527984ARealize partition independent controlCompensate for temperature differencesFinal product manufactureElectric heating for furnacesPower semiconductor deviceHeating time

The invention provides a heating furnace body and semiconductor device. The heating furnace body comprises an annular heat preservation body; and heating structures which are independent of one another and are sequentially arranged on the inner side of the annular heat preservation body in the axial direction of the annular heat preservation body; moreover, at least one heating structure comprisesa plurality of heating subsections which are in one-to-one correspondence with a plurality of subareas divided in the circumferential direction of the annular heat preservation body, and heat radiated by at least two heating subsections at the same time is different. According to the heating furnace body provided by the invention, the heating efficiency can be improved, the heating time can be shortened and the process uniformity can be improved under the condition of the same or less heating power.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

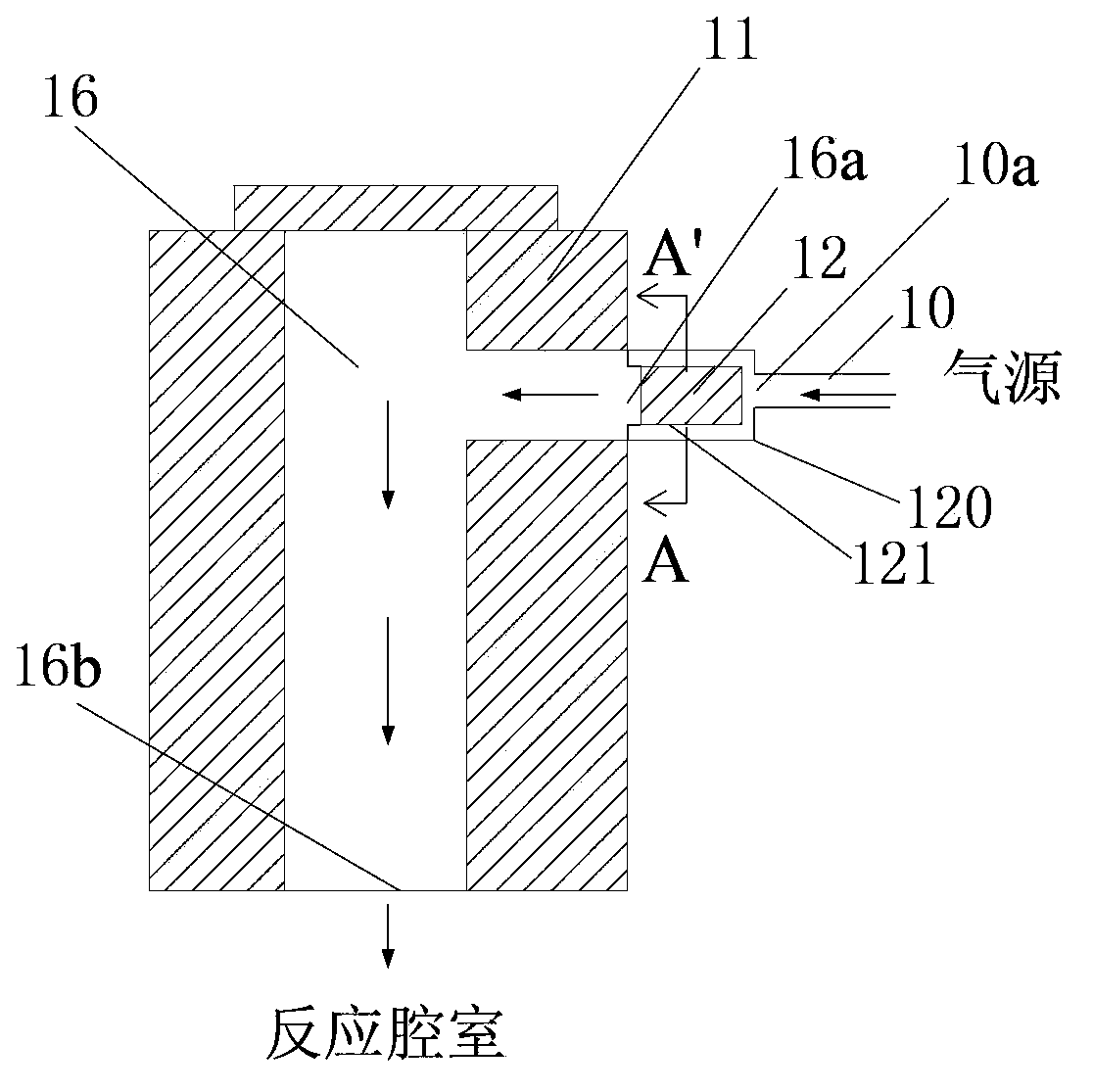

Air inlet system and plasma processing device

InactiveCN104112637ASmooth diffusionImprove process uniformityElectric discharge tubesInlet channelEngineering

The invention provides an air inlet system and a plasma processing device. The air inlet system is used for conveying process gas to a reaction chamber and comprises an air inlet pipeline and an air inlet channel. The air inlet of the air inlet channel is communicated with the air inlet pipeline. The air outlet of the air inlet channel is communicated with the interior of the reaction chamber. The process gas flows into the reaction chamber from the air inlet pipeline and the air inlet channel. An air flow stabilizing assembly is also arranged between the air inlet of the air inlet channel and the air inlet pipeline and is used for enabling the flow state of the process gas flowing into the air inlet channel to tend to a laminar flow state. The air inlet system may enable the flow state of the process gas flowing into the air inlet channel to tend to the laminar flow state such that the process gas flowing into the reaction chamber tends to a uniform state. Thus, the process uniformity of the plasma processing device can be further improved.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

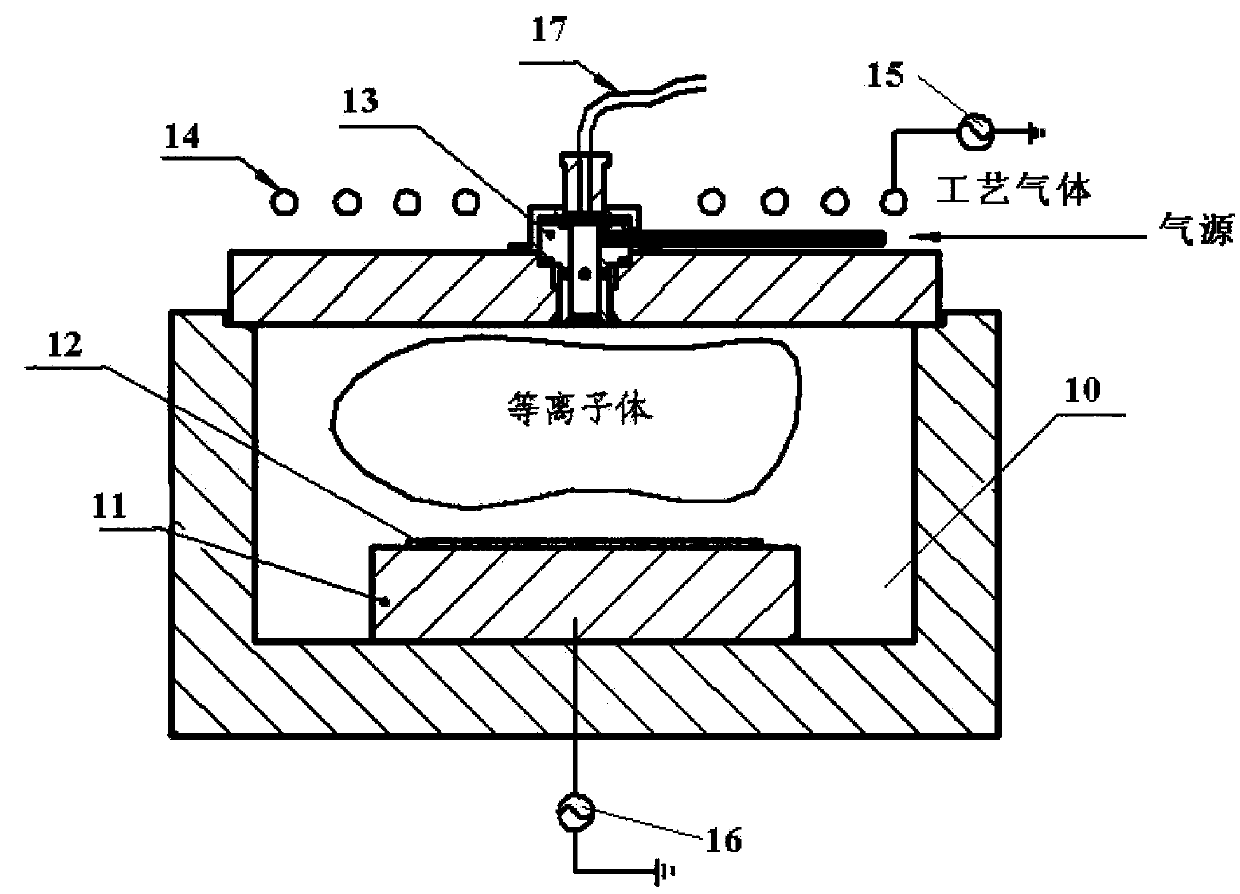

Air inlet device and plasma processing equipment

InactiveCN104233229AImprove distribution uniformityImprove process uniformityChemical vapor deposition coatingPlasma processingProduct gas

The invention provides an air inlet device and plasma processing equipment. The air inlet device comprises an air inlet unit and an air source, wherein the air source supplies process gas into a reaction chamber by virtue of the air inlet unit; the air inlet unit comprises a central air inlet nozzle arranged at the top of the reaction chamber and an edge air inlet nozzle group arranged on the side wall of the reaction chamber, and the central air inlet nozzle is respectively communicated with the air source and the reaction chamber and used for spraying the process gas to a central area of the reaction chamber; and the edge air inlet nozzle group comprises at least two edge air inlet nozzles which are arranged along the circumferential direction of the reaction chamber and are independent of each other; the edge air inlet nozzle group is used for spraying the process gas to an edge area of the reaction chamber. By adopting the air inlet device provided by the invention, the flow of the process gas flowing towards the edge area of the reaction chamber can be further increased so as to ensure that distribution of the process gas in the edge area and the central area of the reaction chamber tends to be uniform, so that the process uniformity of the plasma processing equipment can be improved.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

Static chuck mechanism and semiconductor processing equipment

InactiveCN106898574AAchieve fixationSpeed up heat transferElectric discharge tubesSemiconductor/solid-state device manufacturingEngineeringTemperature difference

The invention provides a static chuck mechanism and semiconductor processing equipment. The mechanism comprises a substrate, an edge assembly, a main static heating layer and an edge static heating layer. The substrate comprises a bearing surface for bearing a wafer, a stepped surface which surrounds the periphery of the bearing surface and is located at the edge of the wafer and is lower than the bearing surface. The edge assembly comprises a focusing ring, a base ring and an insulating ring, wherein the focusing ring is disposed on the stepped surface in a surrounding manner. The insulating ring is disposed at the bottom of the substrate, and supports the substrate. The main static heating layer is disposed on the bearing surface, and is used for the electrostatic absorption of the wafer, and the adjustment of the temperature of the wafer. The edge static heating layer is disposed on the stepped surface, and is used for the electrostatic absorption of the focusing ring and the adjustment of the temperature of the focusing ring. The mechanism provided by the invention can independently adjust the temperature of the central region and edge region of the wafer, can achieve the compensation for the temperature difference between the edge region and the central region of the wafer, and can improve the technological uniformity.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

Wet treatment device and wet treatment method

InactiveCN102473626AImprove process uniformitySemiconductor/solid-state device manufacturingEngineeringGas supply

A wet treatment device retains a substrate to be treated on a stage and rotates the stage, to perform a wet treatment. The substrate to be treated, the center of which is moved away from the rotation center of the stage, is retained in the stage using a Verneuil chuck which blows an inert gas onto the reverse side of the substrate to be treated, so that the substrate to be treated rotates eccentrically in conjunction with the rotation of the stage. A first gas supply route used for the Verneuil chuck is provided in a rotary shaft portion within the stage. Further, in the stage, second gas supply routes which communicate with the first gas supply route to introduce an inert gas onto the reverse side of the substrate to be treated are axisymmetrically placed with respect to the center axis of the substrate to be treated.

Owner:TOHOKU UNIV +1

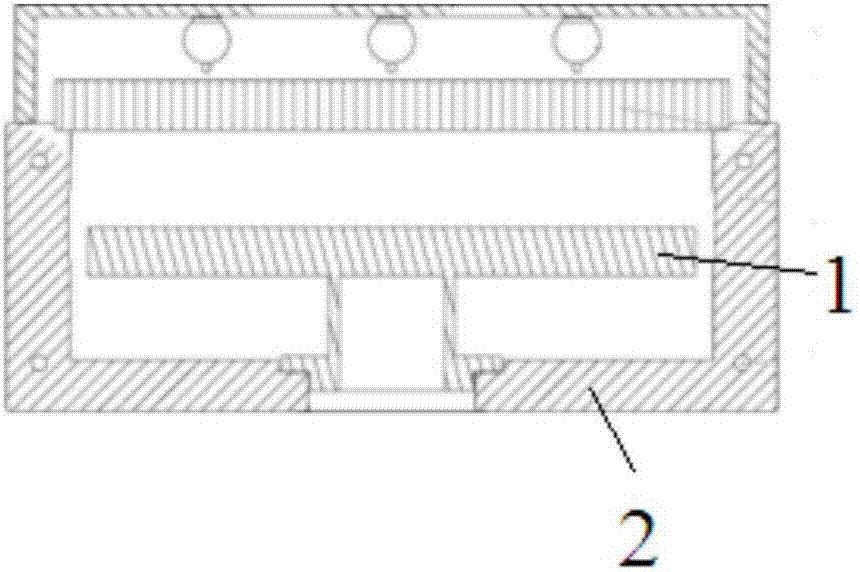

Heating chamber and semiconductor processing apparatus

InactiveCN107546147AReduce deliveryReduce cooling rateVacuum evaporation coatingSemiconductor/solid-state device manufacturingEngineeringSemiconductor

The present invention provides a heating chamber and a semiconductor processing apparatus. The heating chamber includes a heating device and a heat insulating member. The heating device includes a base, a connecting cylinder, and a fixing base. The base is configured to support a heated member. A heating element is arranged in the base; the connecting cylinder is respectively connected with the base and the fixing base, and is located in the central area of the base; and the fixing base is connected with the wall of the bottom chamber of the heating chamber. The heat insulating element is arranged between the fixing base and the wall of the bottom chamber to cut off the heat transfer between them. The present invention provides the heating chamber that can reduce the temperature differencebetween the edge region and the central region of the base so that the uniformity of heating can be improved.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

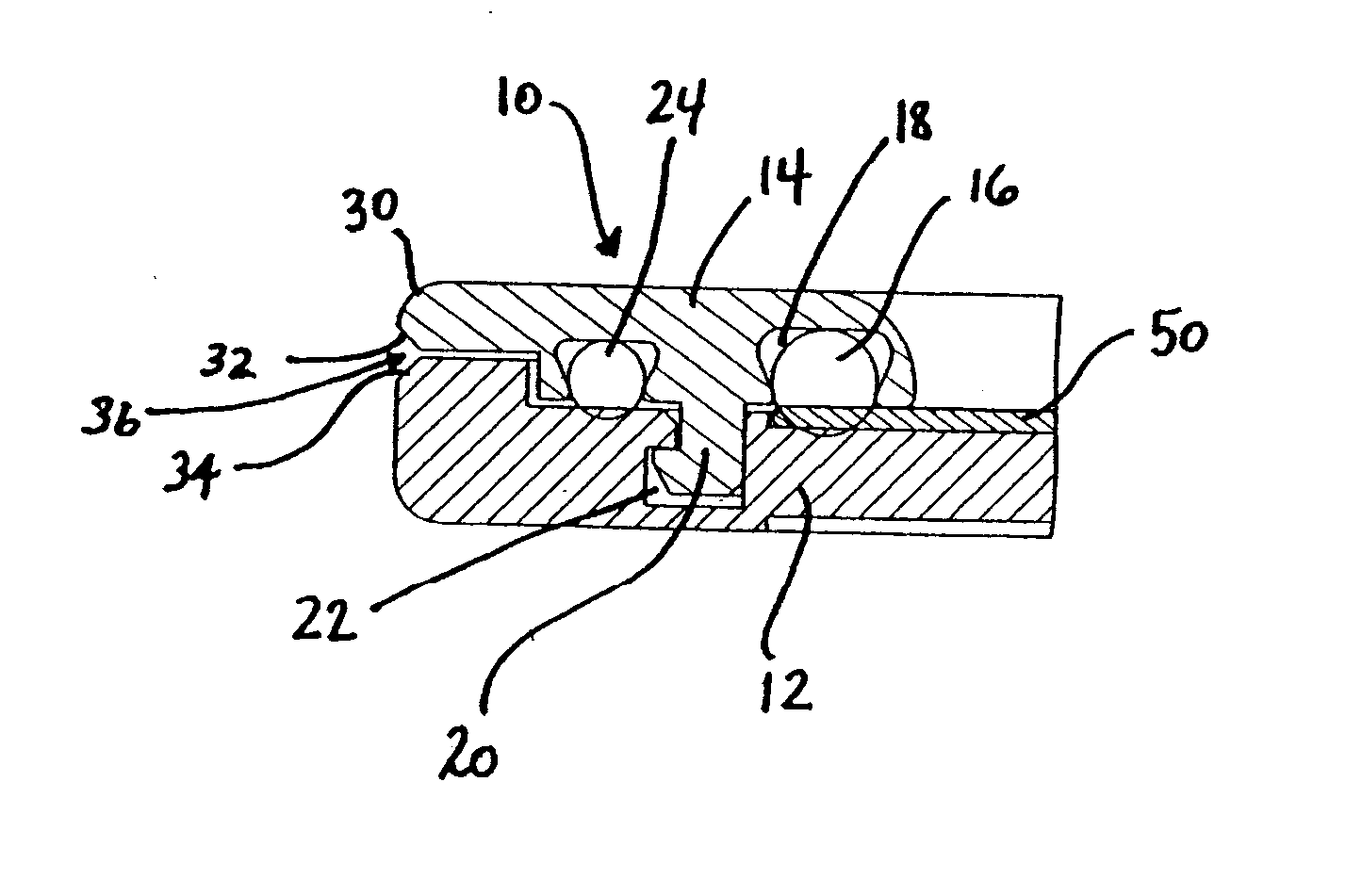

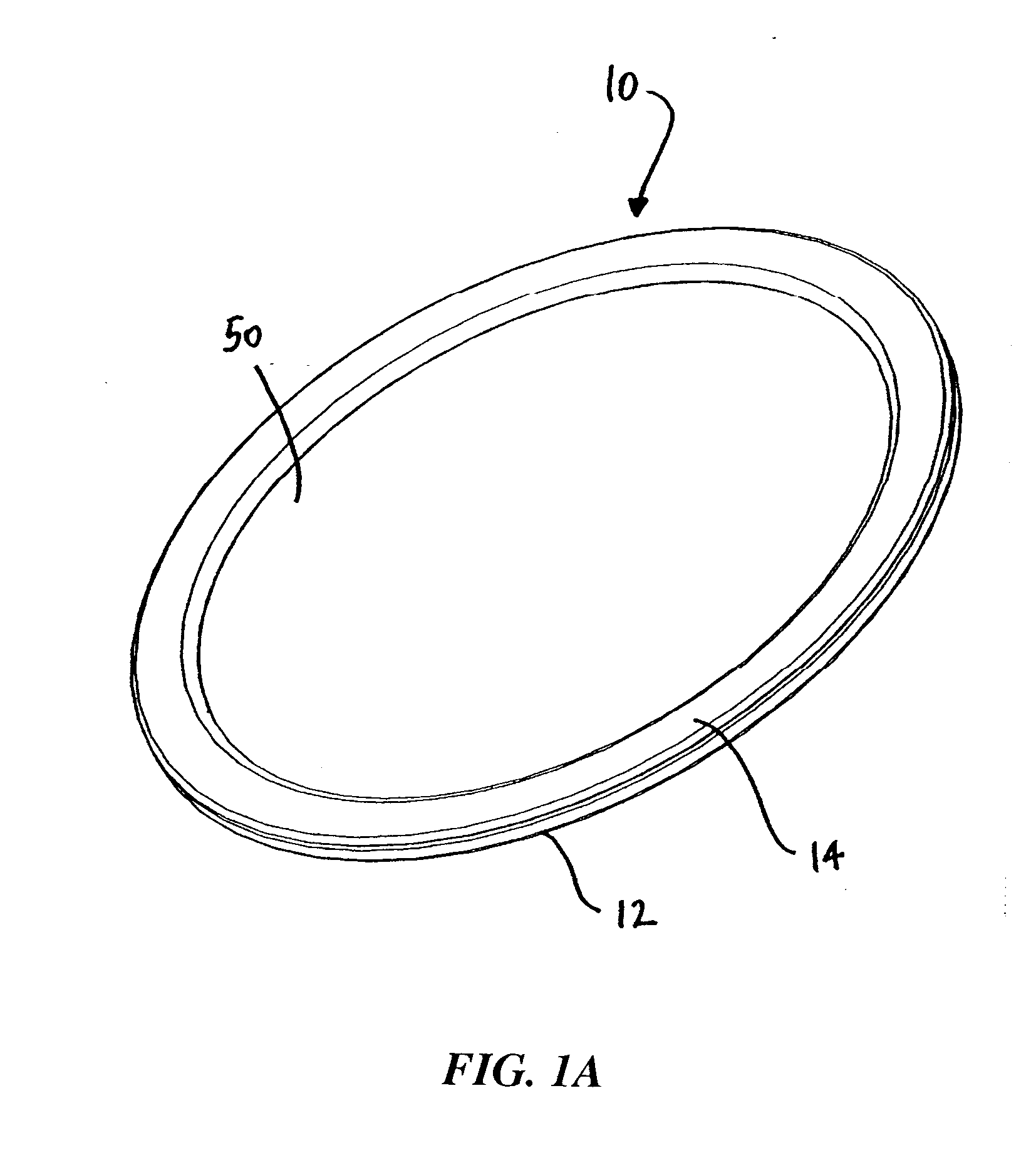

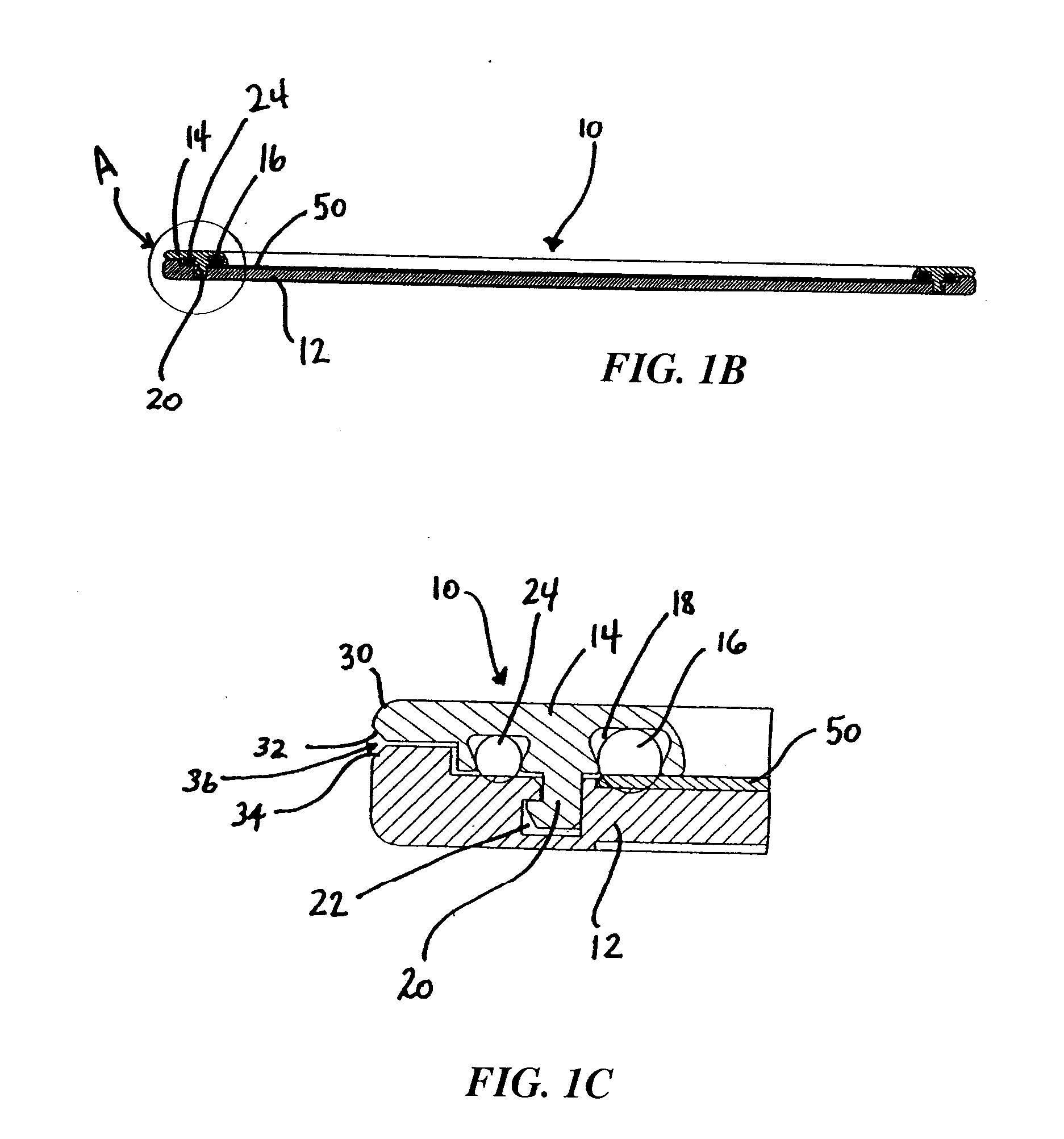

Apparatus for use in thinning a semiconductor workpiece

InactiveUS20060220329A1Avoid breakingSimple product structureSleeve/socket jointsTurning machine accessoriesSemiconductor materialsCompound (substance)

The present invention provides an apparatus and method for use in processing semiconductor workpieces. The new apparatus and method allows for the production of thinner workpieces that at the same time remain strong. Particularly, a chuck is provided that includes a body, a retainer removeably attached to the body and a seal forming member. When a workpiece is placed on the chuck body and the retainer is engaged to the body, a peripheral portion of the back side of the workpiece is covered by the retainer while an interior region of the back side of the workpiece is exposed. The exposed back side of the workpiece is then subjected to a wet chemical etching process to thin the workpiece and form a relatively thick rim comprised of semiconductor material at the periphery of the workpiece. The thick rim or hoop imparts strength to the otherwise fragile, thinned semiconductor workpiece. Semiconductor workpieces made according to the present invention offer an improved structure for handling thinned wafers in conventional automated equipment. This results in improved yields and improved process efficiency.

Owner:SEMITOOL INC

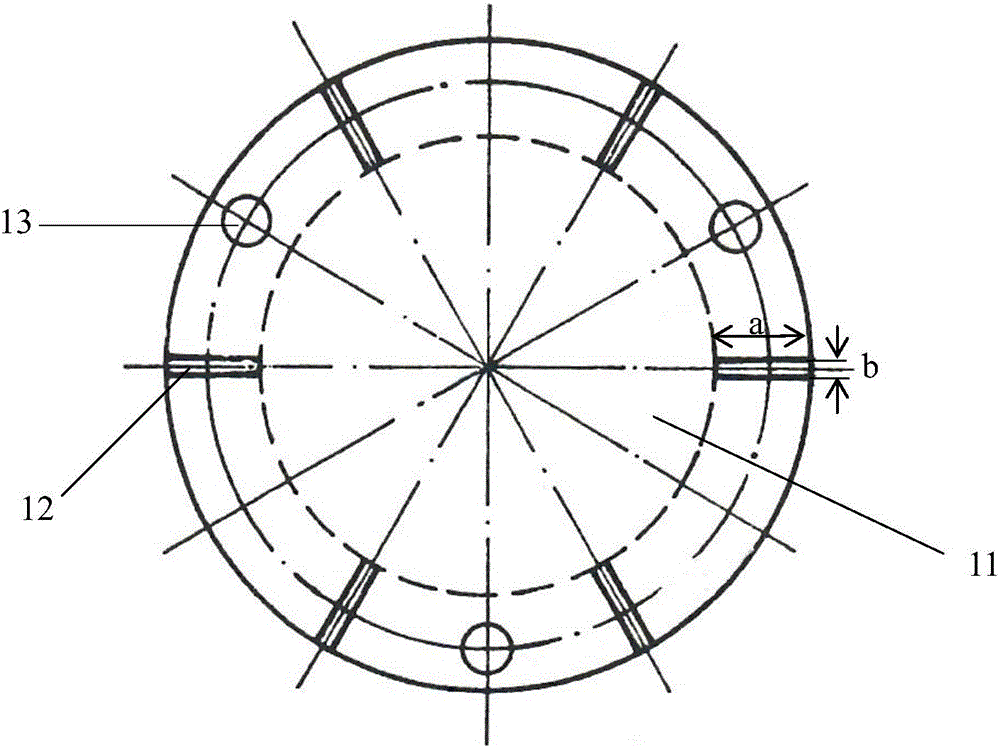

Grid mesh and ionic source

ActiveCN106158565AGood repeatabilityImprove process uniformityElectric discharge tubesIon beam processingThermal deformation

The invention relates to a grid mesh, which is used for an ionic optical system of an ionic source. The grid mesh is provided with a grid hole area with grid holes, a plurality of thermal stress slots are formed in the grid mesh from the edge of the grid hole area in an outward radiation manner, and the thermal stress slots penetrate through the upper surface and the lower surface of the grid mesh. The invention further provides an ionic source using the grid mesh. The radiating thermal stress slots are formed in the grid mesh, so that the thermal deformation problem of the melting-resistant metal plane grid mesh can be thoroughly solved, the uniformness and stability of the ion beam stream can also be maintained, the long-term and repeated ionic source working under high-temperature environment can be met, and the ionic source performance repeatability and the ion beam processing technique uniformness can be improved.

Owner:北京埃德万斯离子束技术研究所股份有限公司

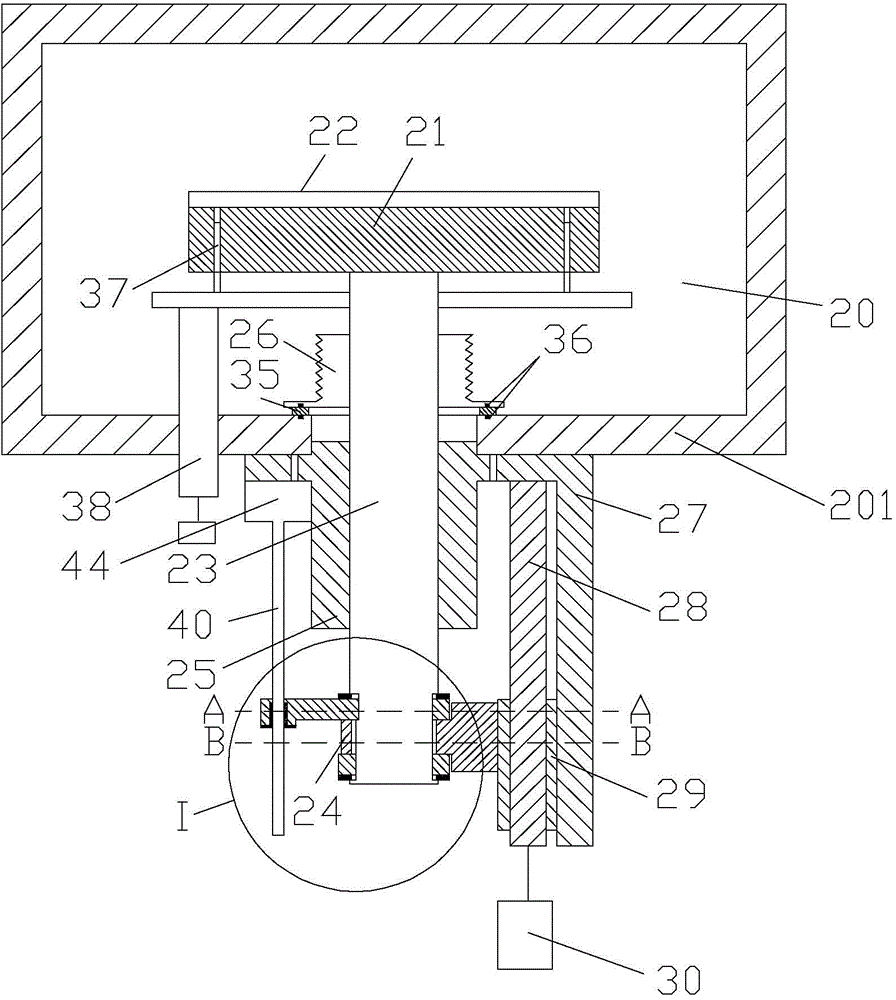

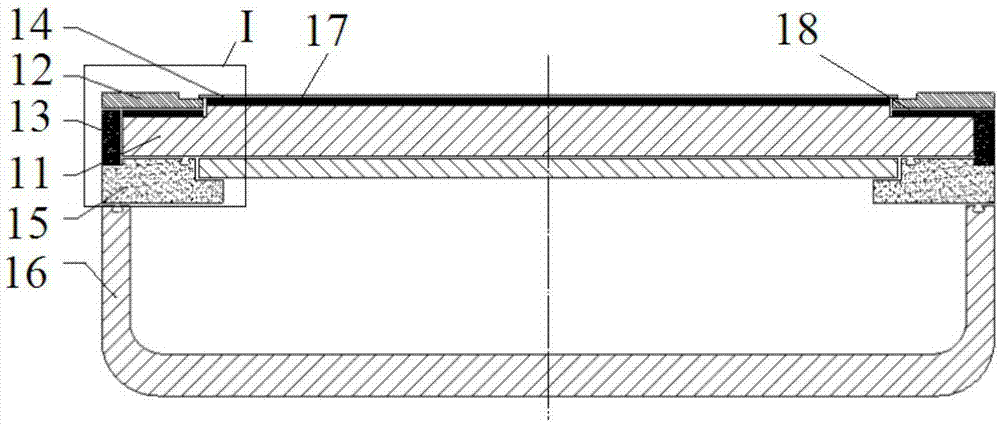

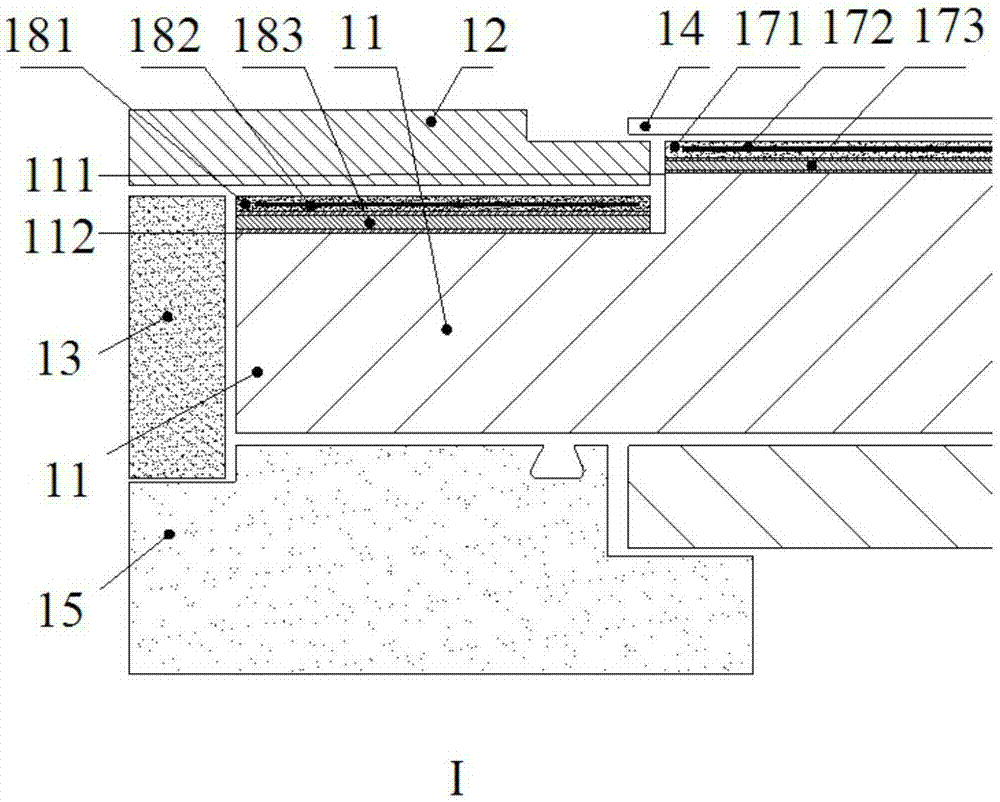

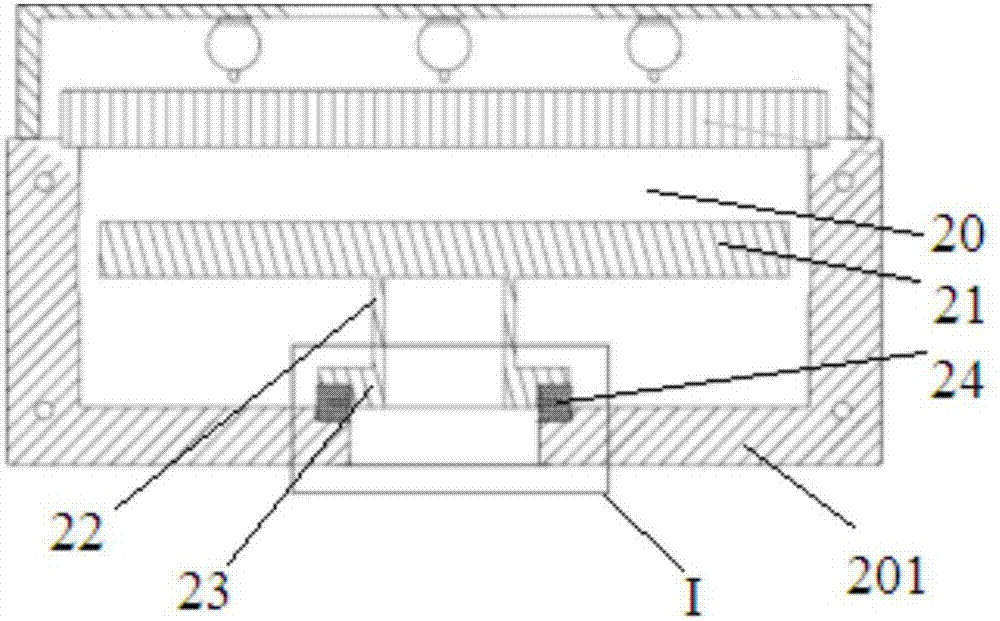

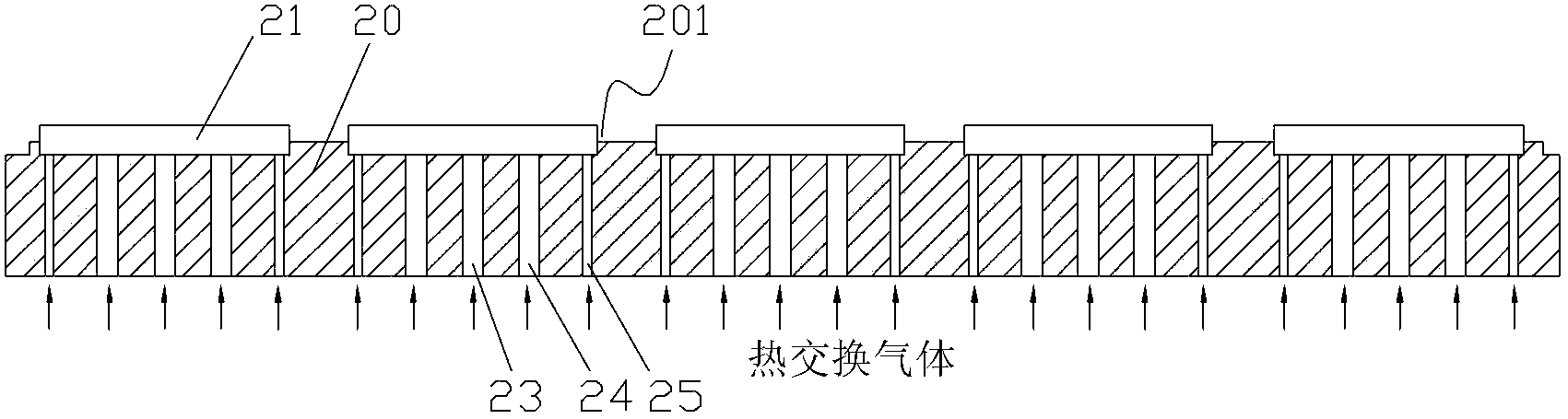

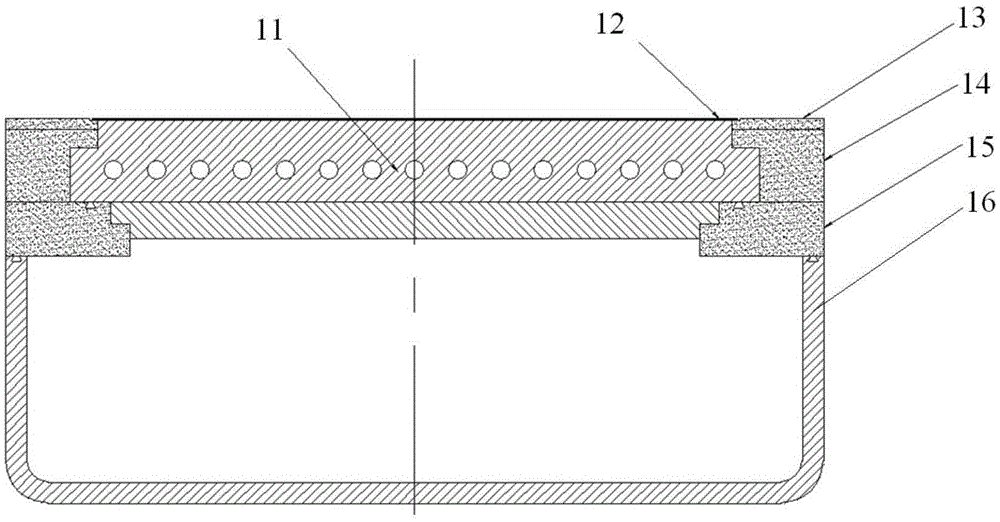

Tray and plasma processing equipment

ActiveCN104134624AImprove heat exchange effectUniform temperatureElectric discharge tubesSemiconductor/solid-state device manufacturingEngineeringPlasma processing

Disclosed are a substrate bearing device (20) and plasma processing equipment. An upper surface of the substrate bearing device (20) is provided with a plurality of substrate mounting locations (201), and heat-exchange gas inlet passages (23, 24, 25) are arranged in the substrate bearing device (20) corresponding to each substrate mounting location (201), so as to guide a heat exchange gas to the upper surface of the substrate mounting location (201). The heat-exchange gas inlet passages comprise peripheral inlet passages and a middle inlet passage, wherein gas inlets (23, 24, 25) of the peripheral inlet passages and the middle inlet passage are all in communication with an external gas source; gas outlets of the peripheral inlet passages are arranged in the peripheral region of the upper surface of the substrate mounting location (201); and a gas outlet of the middle inlet passage is arranged in the middle region of the upper surface of the substrate mounting location (201). The substrate bearing device (20) and the plasma processing equipment can improve the heat exchange effect of the peripheral region of a processed workpiece (21), so that the temperature of the peripheral region and the middle region of the processed workpiece (21) can be enabled to tend to be uniform, and then the uniformity of the plasma processing technology can be improved.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

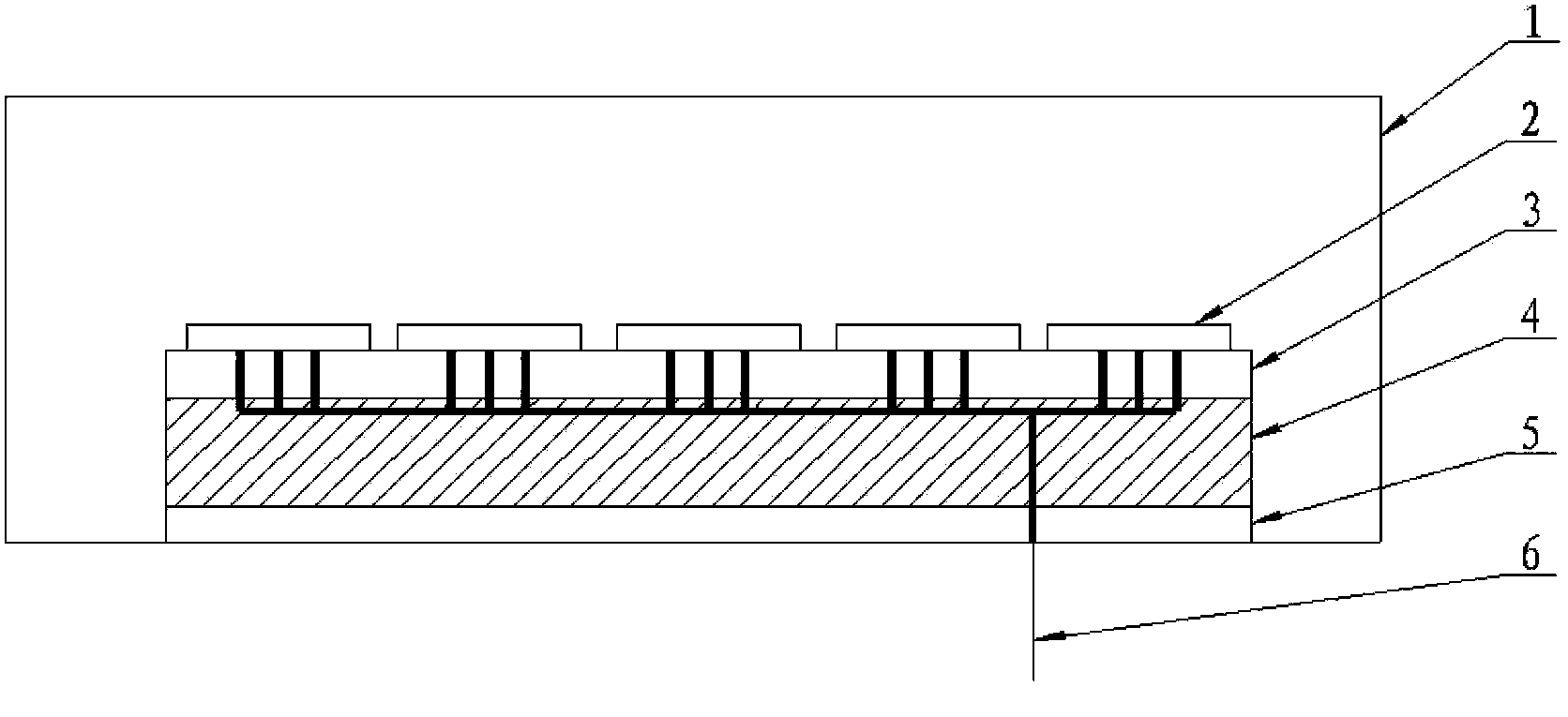

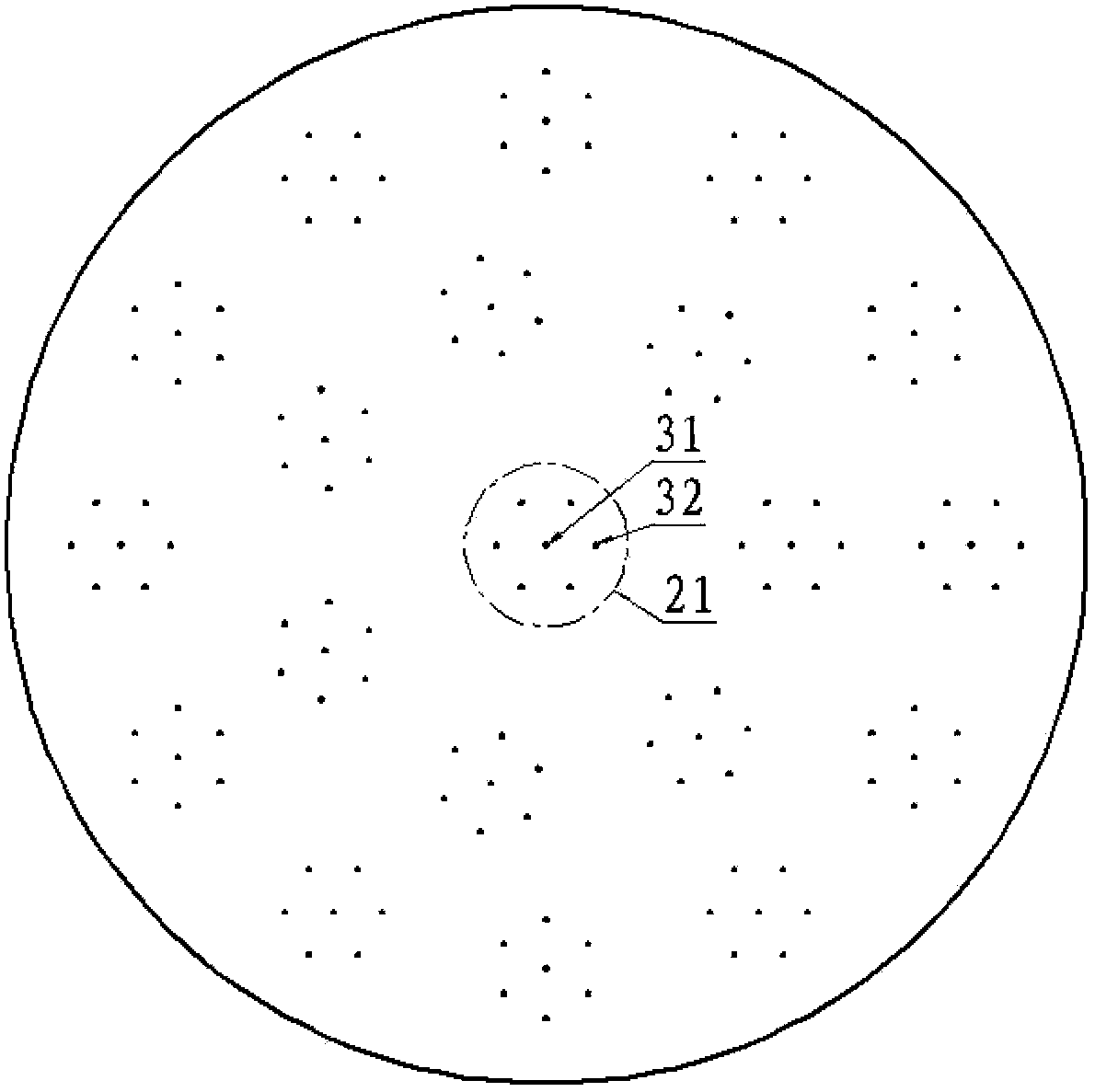

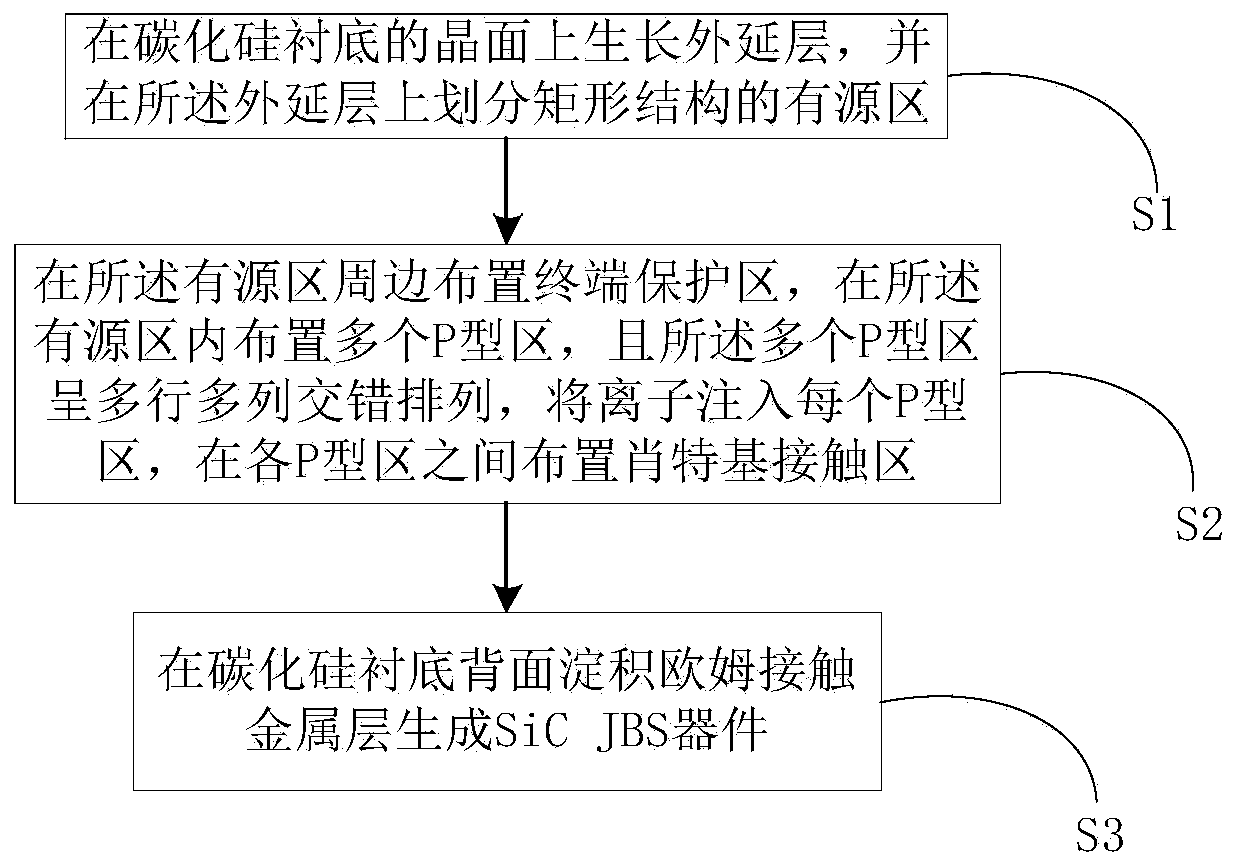

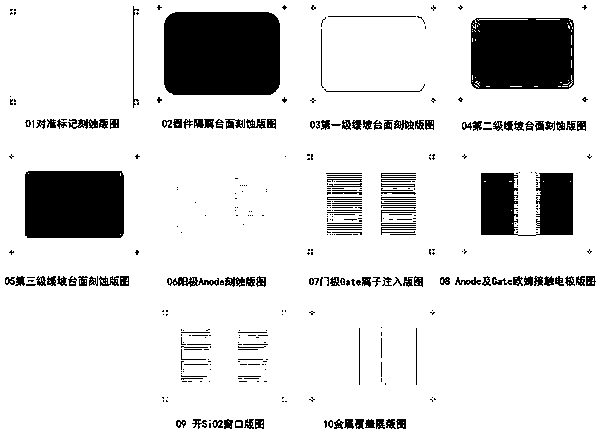

Layout method of SiC JBS device

PendingCN111261724AIncrease the area of the barrier regionGuaranteed reverse breakdown characteristicsSolid-state devicesSemiconductor/solid-state device manufacturingCarbide siliconSchottky barrier

The invention provides a layout method of a SiC JBS device, which comprises the following steps of: growing an epitaxial layer on the crystal surface of a silicon carbide substrate, and dividing an active region with a rectangular structure on the epitaxial layer, arranging a terminal protection region at the periphery of the active region, arranging a plurality of P-type regions in the active region, arranging the plurality of P-type regions in a multi-row and multi-column staggered manner, implanting ions into each P-type region, and arranging Schottky contact regions between the P-type regions, and depositing an ohmic contact metal layer on the back surface of the silicon carbide substrate to generate the SiC JBS device. The plurality of P-type regions are arranged in the SiC JBS devicein a multi-row and multi-column staggered manner, so that the reverse breakdown characteristic of the SiC JBS device is ensured, the Schottky barrier region area is increased, and the conduction capability is improved.

Owner:GLOBAL ENERGY INTERCONNECTION RES INST CO LTD

Carrying device and semiconductor processing equipment

ActiveCN106548967AUniform etch rateImprove process uniformitySemiconductor/solid-state device manufacturingSemiconductorPhysics

The invention provides a carrying device and semiconductor processing equipment. The carrying device comprises a chuck and a focusing ring, wherein the upper surface of the chuck is used for carrying a processed workpiece; the focusing ring encircles the periphery of the chuck; and moreover, the dielectric constant values of the focusing ring at different areas in the peripheral direction are different, so that the etching rate of the edge of the processed workpiece everywhere tends to be uniform. According to the carrying device provided by the invention, the etching rate of the edge of the processed workpiece everywhere can tend to be uniform, so that the technological uniformity can be improved.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

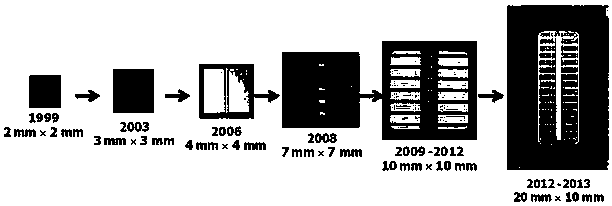

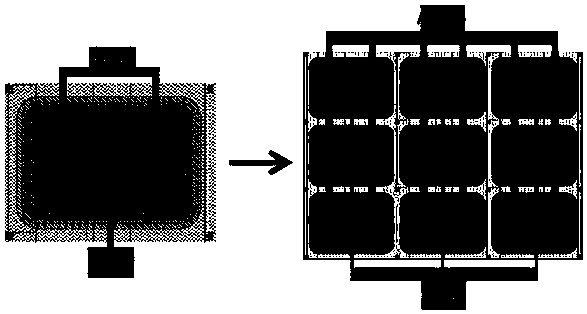

Device array of silicon carbide gate turn-off thyristor GTO and preparation method thereof

PendingCN108550572AIncrease the effective working areaSlow performanceSemiconductor/solid-state device detailsSolid-state devicesGate turn-off thyristorMachining

The invention provides a device array of a silicon carbide gate turn-off thyristor GTO and a preparation method thereof, wherein each single device is relatively small in size. The device array is formed by photoetching according to a corresponding photoetching layout and comprises at least two array structures of silicon carbide gate turn-off thyristors. The gate electrode of a GTO device unit islocated in the center of the table surface of the device unit. The gate electrode of the GTO device unit forms an interdigital structure together with anodes located on the two sides of the table surface of the device unit. A cathode is located on the back surface of the substrate of the device unit. During the packaging process, the gate electrodes of all device units are led down to a packagingstructure according to the layout design. Meanwhile, all anodes are led out in the opposite directions of the gate electrodes. According to the device array scheme adopted by the invention, the effective working area of a whole packaging chip can be remarkably improved. The condition that the performance of the whole packaging chip is reduced due to the defects of local materials can be avoided.Moreover, the process difficulty of device machining can be reduced, and the process stability and the process uniformity can be improved. The yield of prepared devices can be remarkably improved.

Owner:INST OF ELECTRONICS ENG CHINA ACAD OF ENG PHYSICS

High-temperature-resistant oxidation coating nickel-based alloy powder for laser cladding

InactiveCN110331397AImprove performanceLow melting pointMetallic material coating processesRare-earth elementCrack resistance

The invention discloses a high-temperature-resistant oxidation coating nickel-based alloy powder for laser cladding, and the powder mainly comprises the following chemical components: Ni, Cr, Mo, W, Co, V, Fe, Si, Mn, and at least two of rare earth elements Y2O3 3, La2O3 3, Ce and Hf in proper amount. The invention fundamentally solves and improves the crack resistance, the formability, the process stability and the component uniformity of the alloy powder in a laser cladding layer, and meets the comprehensive performance requirements of a repair part on the cladding layer, such as oxidation resistance, corrosion resistance, wear resistance, fatigue resistance, moderate hardness and strength, certain conductivity and the like. The powder material can be used for laser cladding of the conductive roller part of the key equipment of a electrogalvanizing unit, solves the repairing problem of the conductive roller after corrosion and abrasion, and provides an effective and convenient methodfor successfully repairing the invalid conductive roller part in the metallurgical industry.

Owner:扬州安泰威合金硬面科技有限公司