Device array of silicon carbide gate turn-off thyristor GTO and preparation method thereof

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

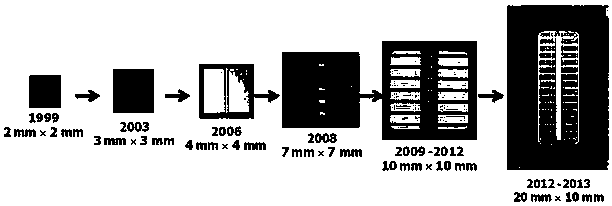

Problems solved by technology

Method used

Image

Examples

Embodiment 1

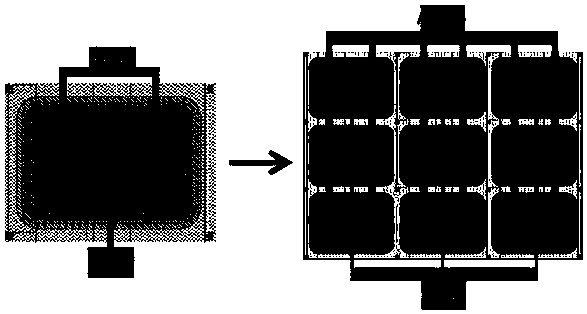

[0039] A silicon carbide gate turn-off thyristor device array (SiC GTO Array), the epitaxial structure of the SiC material is the P+ / N / P- / P / N+ structure in the SiC GTO device from top to bottom, from top to bottom Each epitaxial layer is a P+ contact layer in turn (doping concentration 2×10 19 cm -3 , thickness 2μm), N base layer (doping concentration 2.3×10 17 cm -3 , thickness 2μm), P-drift layer (doping concentration 2×10 14 cm -3 , thickness 60μm), P buffer layer (doping concentration 2×10 17 cm -3 , thickness 2μm), N+ field stop layer (doping concentration 2×10 18 cm -3 , thickness 1μm), the bottom is N+ 4H-SiC intrinsic substrate. The device unit mesa size of the SiC GTO device array is 3.52mm*2.52mm; the device array is an area array with 3 columns and 4 rows, which contains a total of 12 GTO devices, and the overall design size of the array is 11.46mm*11.28mm.

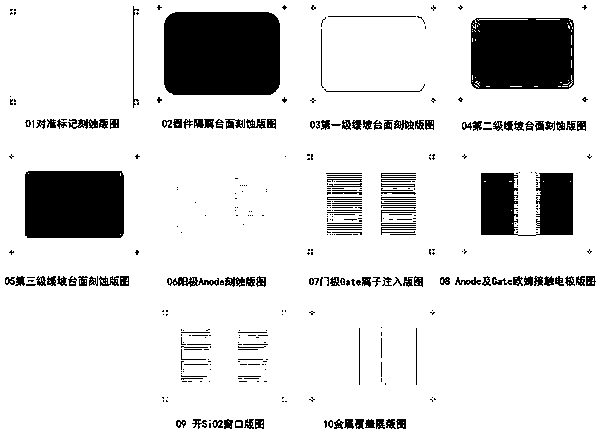

[0040] according to image 3 The photolithographic layout design in the present embodiment, the pr...

Embodiment 2

[0055] Another silicon carbide gate turn-off thyristor device array (SiC GTO Array), the epitaxial structure of its SiC material is a typical P+ / N / P- / P / N+ structure in SiC GTO devices from top to bottom, from top to bottom Each epitaxial layer to the next is the P+ contact layer (doping concentration 2×10 19 cm -3 , thickness 2μm), N base layer (doping concentration 2.3×10 17 cm -3 , thickness 2μm), P-drift layer (doping concentration 2×10 14 cm -3 , thickness 90μm), P buffer layer (doping concentration 2×10 17 cm -3 , thickness 2μm), N+ field stop layer (doping concentration 2×10 18 cm -3 , thickness 1μm), the bottom is N+ 4H-SiC intrinsic substrate. The device unit mesa size of the SiC GTO device array is 3.52mm*5.04mm; the device array is an area array with 6 columns and 4 rows, which contains a total of 24 GTO devices, and the overall design size of the array is 22.92mm*21.36mm.

[0056] The device array process preparation flow in embodiment 2 is similar to the p...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Area | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More