Patents

Literature

56 results about "Gate turn-off thyristor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A gate turn-off thyristor (GTO) is a special type of thyristor, which is a high-power semiconductor device. It was invented by General Electric. GTOs, as opposed to normal thyristors, are fully controllable switches which can be turned on and off by their third lead, the gate lead.

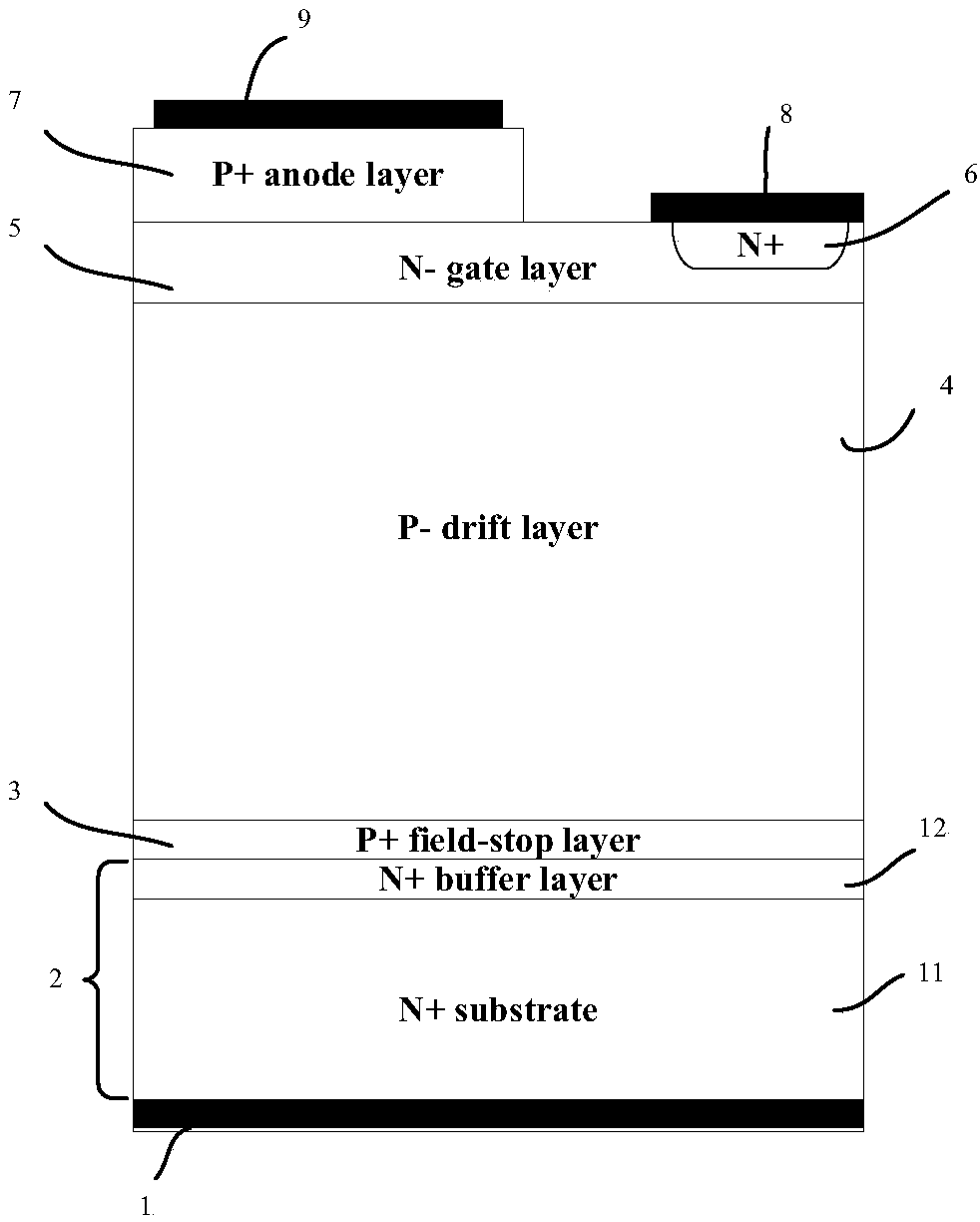

Processing technique to improve the turn-off gain of a silicon carbide gate turn-off thyristor

ActiveUS7851274B1Increased turnLow mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesGate turn-off thyristorNanosecond

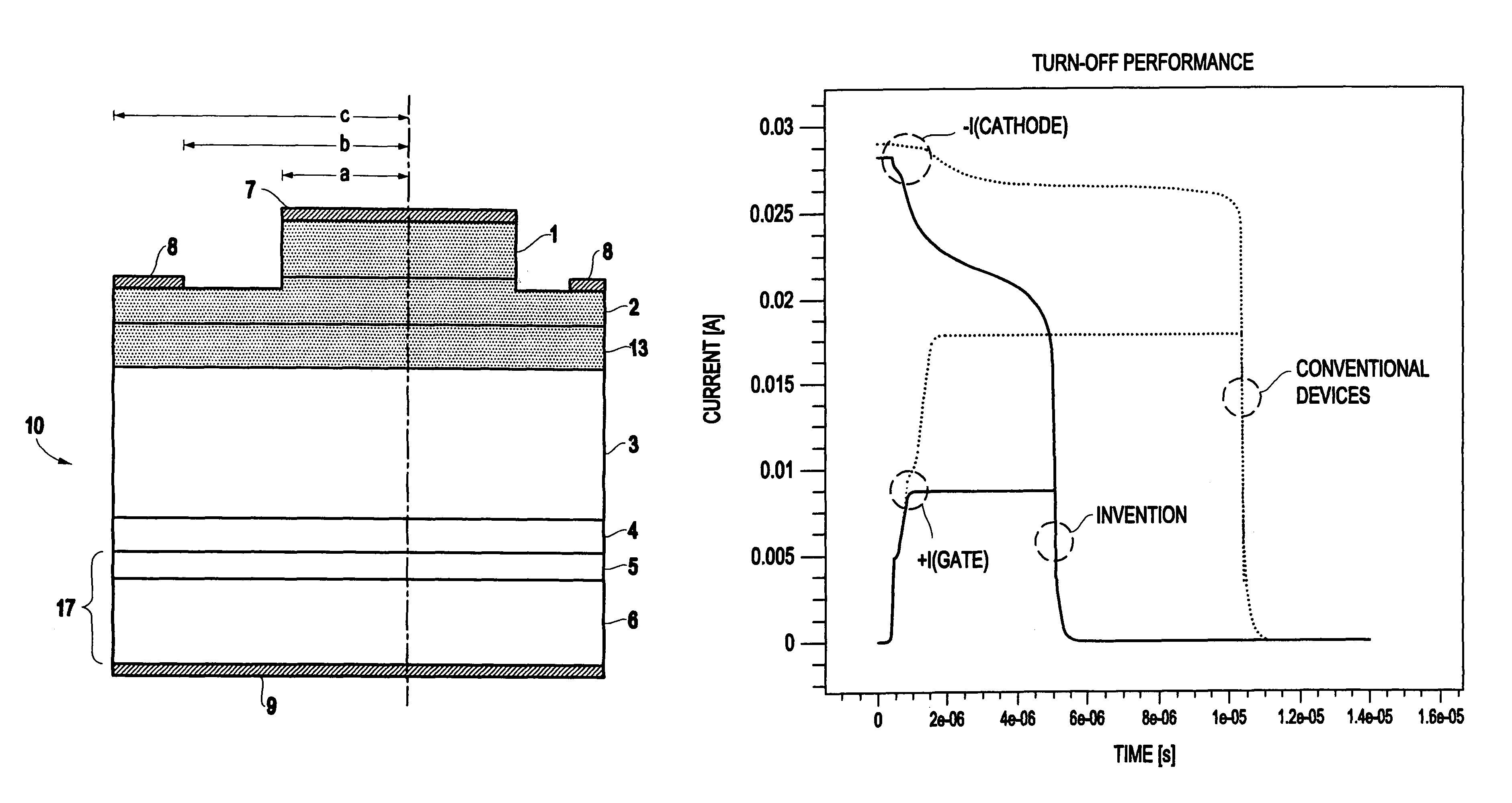

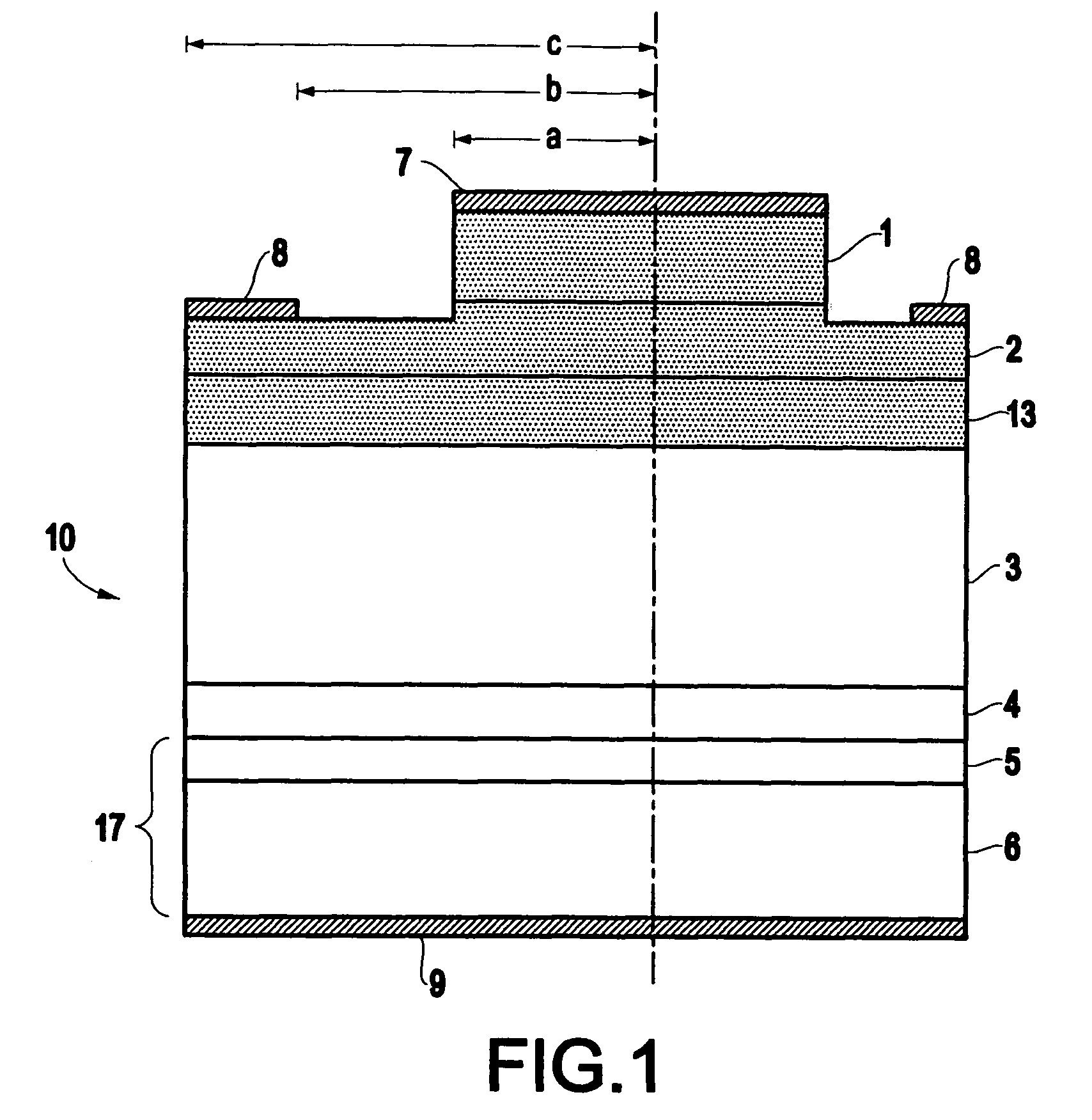

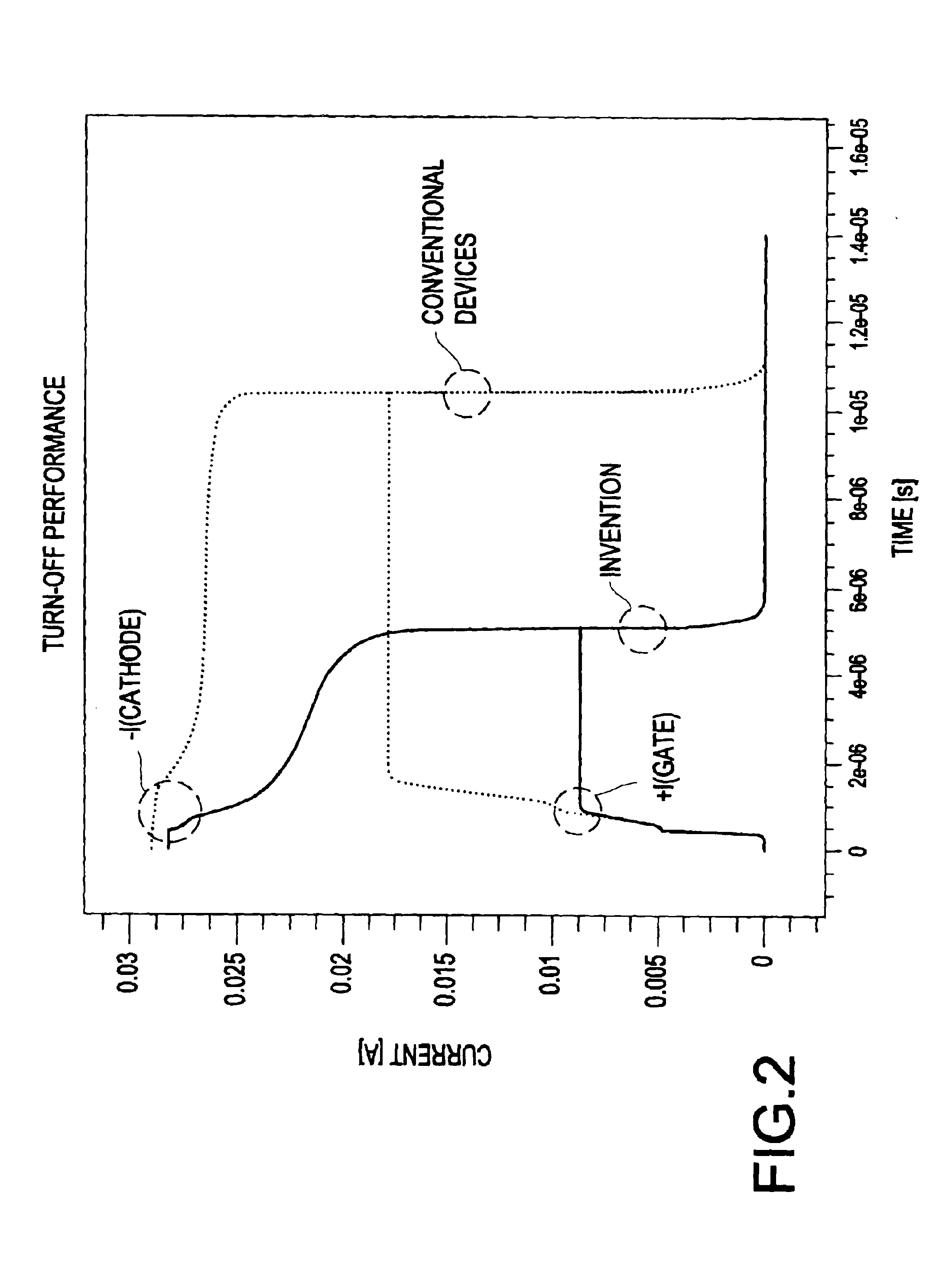

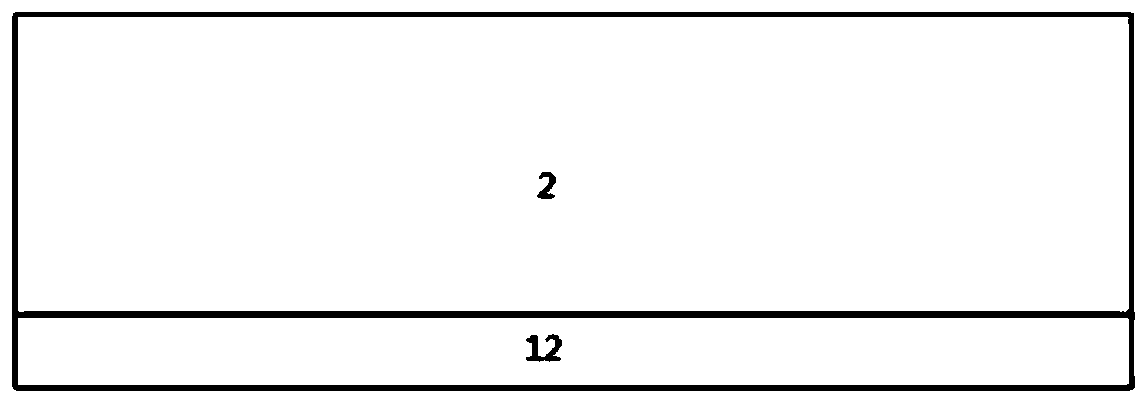

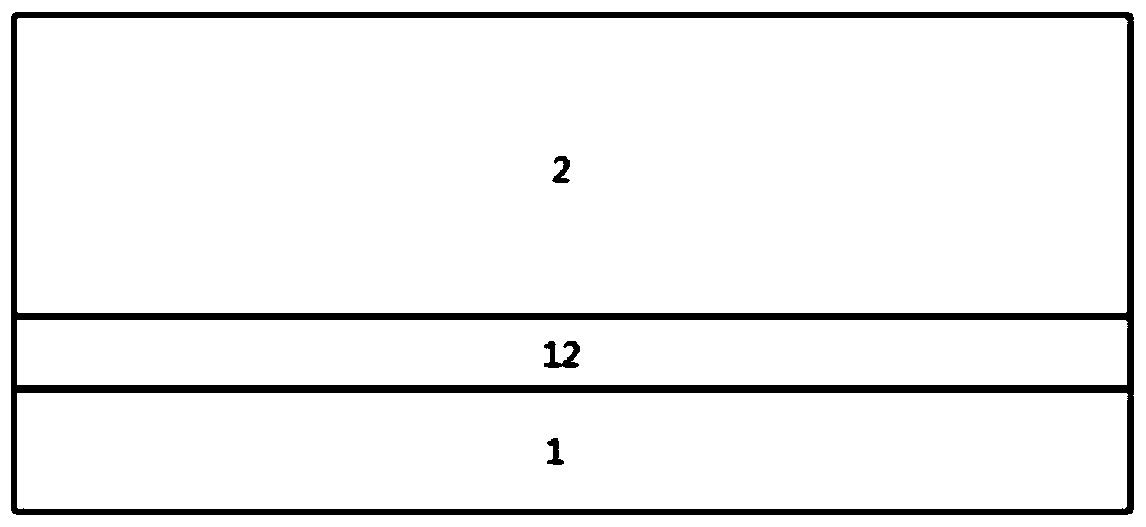

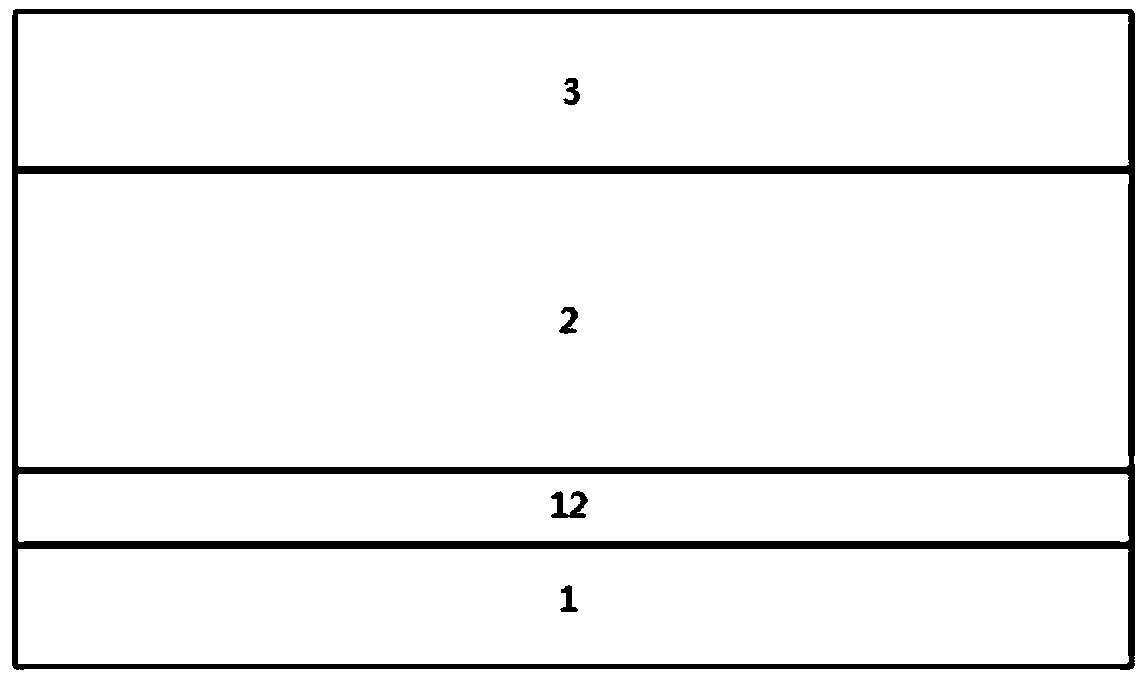

A structure and method for a silicon carbide (SiC) gate turn-off (GTO) thyristor device operable to provide an increased turn-off gain comprises a cathode region, a drift region having an upper portion and a lower portion, wherein the drift region overlies the cathode region, a gate region overlying the drift region, an anode region overlying the gate, and at least one ohmic contact positioned on each of the gate region, anode region, and cathode region, wherein the upper portion of the drift region, the gate region, and the anode region have a free carrier lifetime and mobility lower than a comparable SiC GTO thyristor for providing the device with an increased turn-off gain, wherein the free carrier lifetime is approximately 10 nanoseconds. The reduced free carrier lifetime and mobility are affected by altering the growth conditions, such as temperature under which epitaxy occurs.

Owner:ARMY US SEC THE

Voltage space vector control device and control method for soft start

ActiveCN103633910ASmall starting currentNo reduction in starting torqueElectronic commutation motor controlAC motor controlMicrocontrollerFrequency changer

The invention relates to a voltage space vector control device and a voltage space vector control method for soft start. At present, a soft start technology has the problems of high starting current and low starting torque, and frequency converter soft start has the shortcoming of difficulty in the implementation of power frequency switching. A three-phase alternating current power supply is used for supplying power, six electric GTOs (gate-turn-off thyristors) can be reversely connected in parallel, an IGBT (insulated gate bipolar transistor) is adopted for a continuous current circuit, a voltage space vector control circuit is formed under the control of a microcontroller, and a current transformer is used for transmitting a three-phase current signal to the microcontroller for current limiting start and current monitoring. The phases A, B and C of the power supply of a three-phase alternating current asynchronous motor are subjected to alternating current voltage regulation and frequency modulation control under the control of the microcontroller, a voltage space vector control strategy is used for realizing hexagonal flux linkage track control over the alternating current motor, the voltage / frequency ratio is relatively stable, and the stability of main magnetic flux of the motor is ensured.

Owner:SHAANXI UNIV OF SCI & TECH +1

Method for manufacturnig silicon high-speed semiconductor switch device

InactiveCN1471146AExcellent electrical performanceDensity Spatial Distribution OptimizationSemiconductor/solid-state device manufacturingGate turn-off thyristorPlatinum

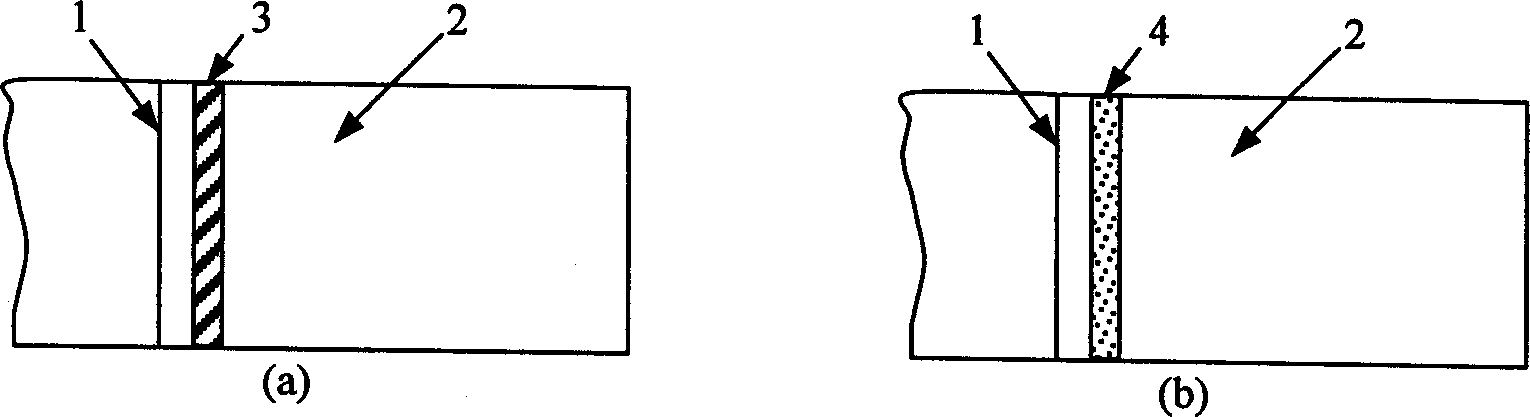

The method is applicable to manufacture silicon semiconductor binistor with at least one PN junction such as GTO, IGBT etc. General manufacturing steps is carried out till the step of making metalized electrode. Platinum-silicon alloy is made on surface of silicon. Using proton or particle injection forms local high density defect area. Heating and annealing makes the defect area absorb platinum to convert to platinum impurity range. Then, General manufacturing steps is carried out till manufacturing completion. The performances of the invention are better than present life control technique. The parts made by the invention possesses higher switching speed and backward recovery speed, but the forward voltage drop and reverse leakage are not increased visibly.

Owner:BEIJING UNIV OF TECH

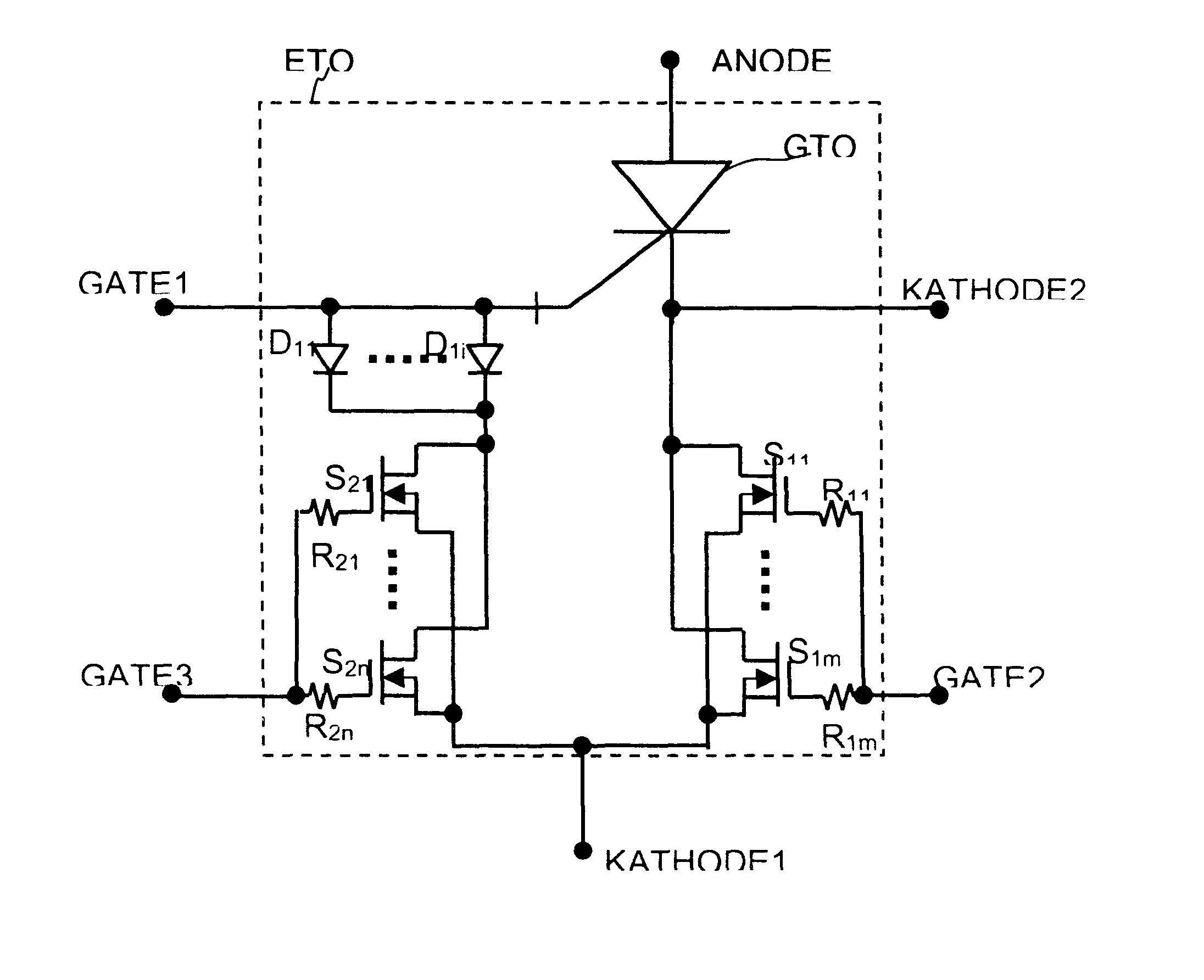

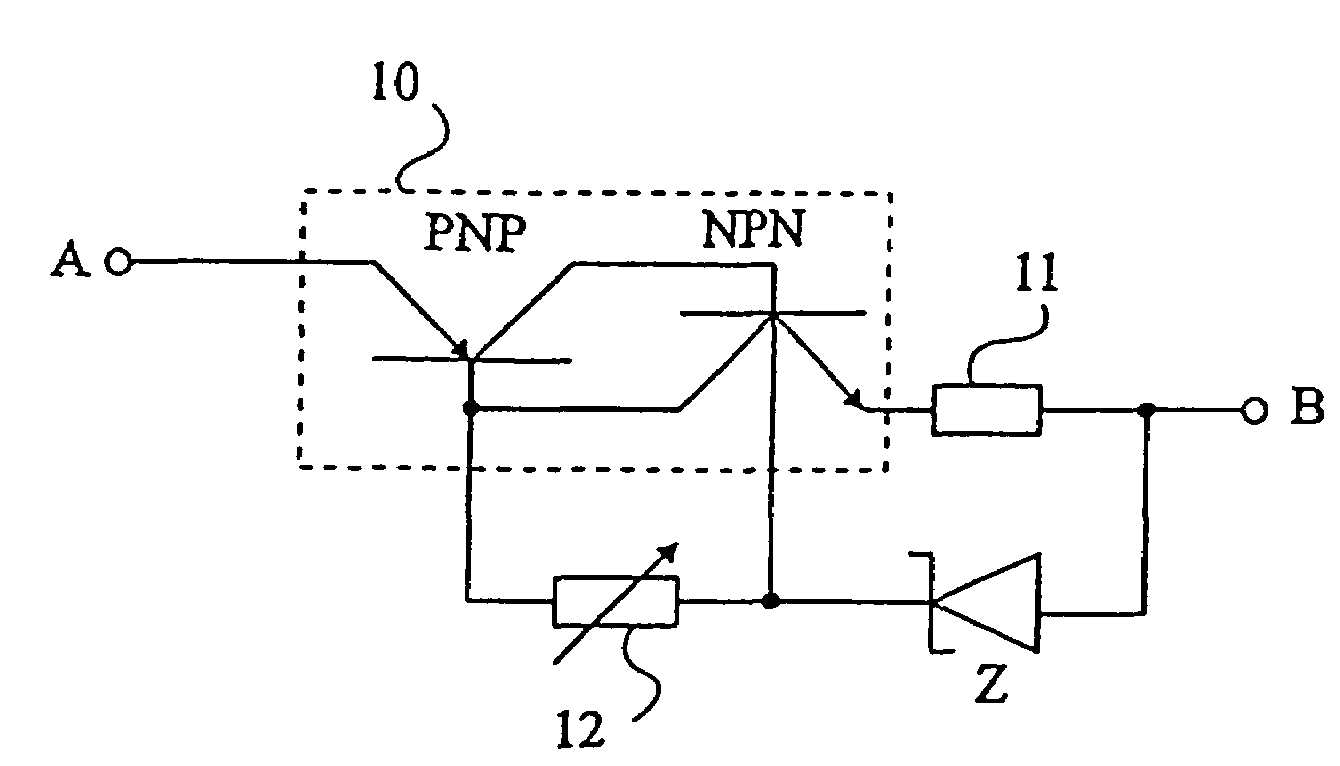

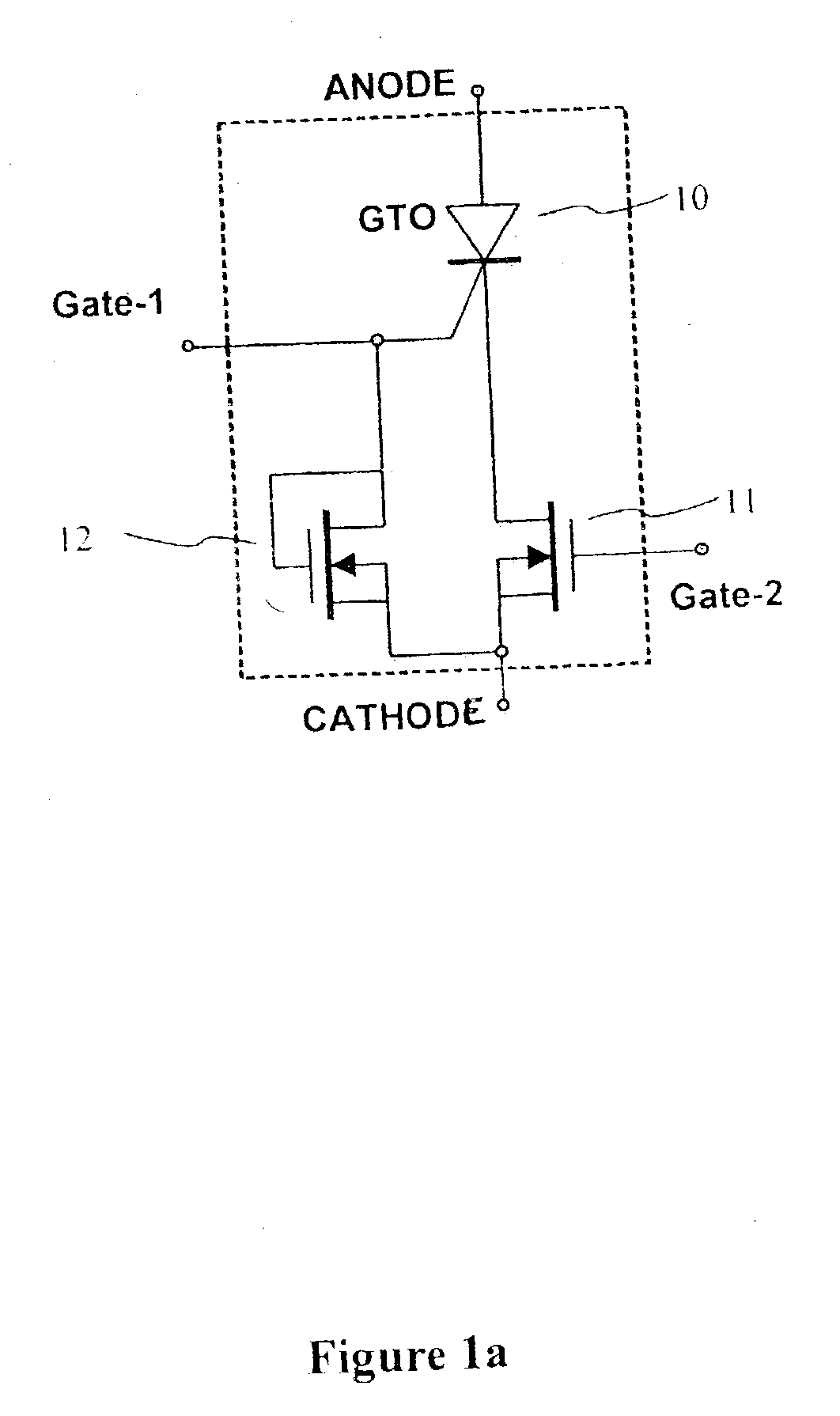

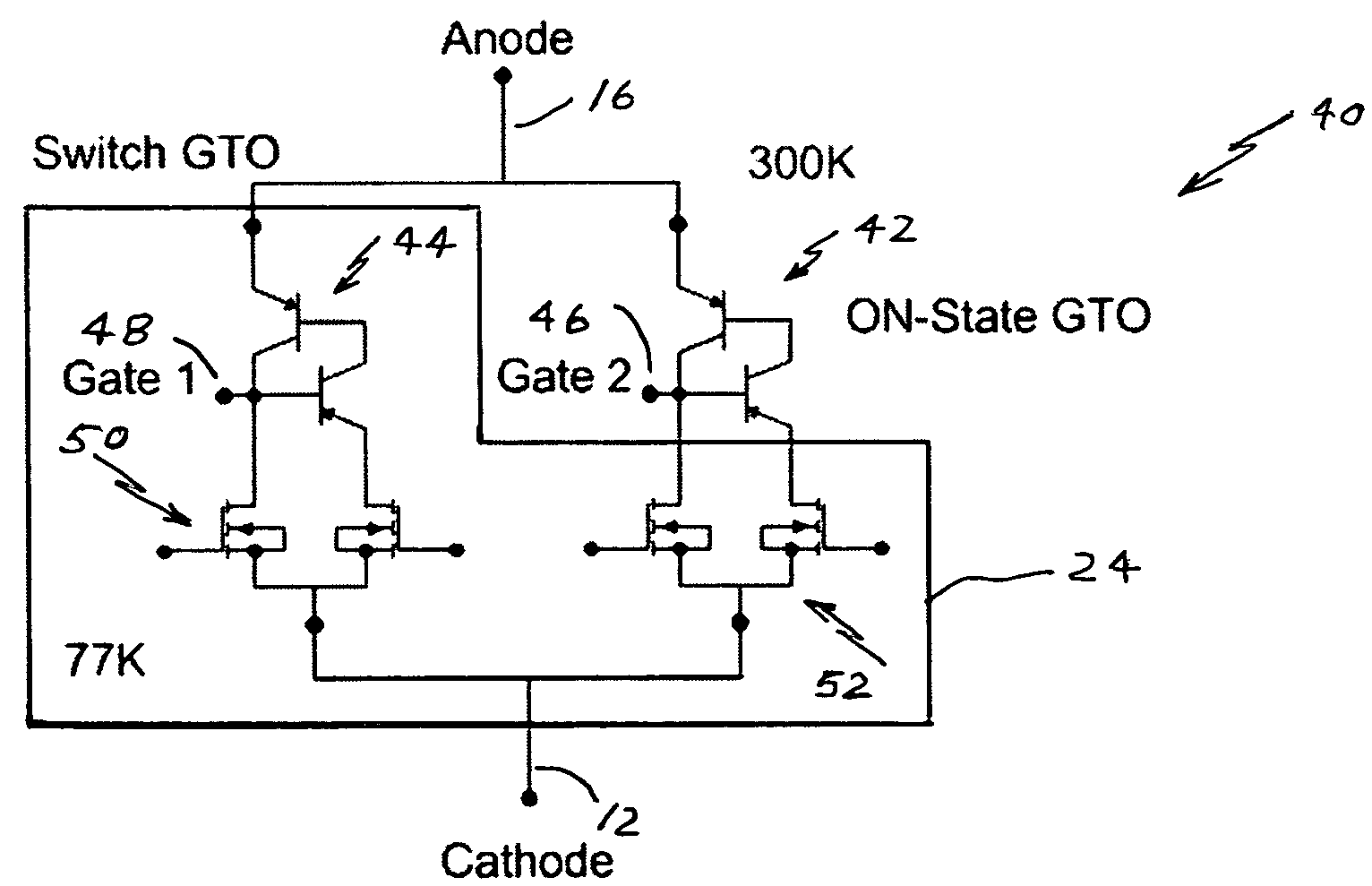

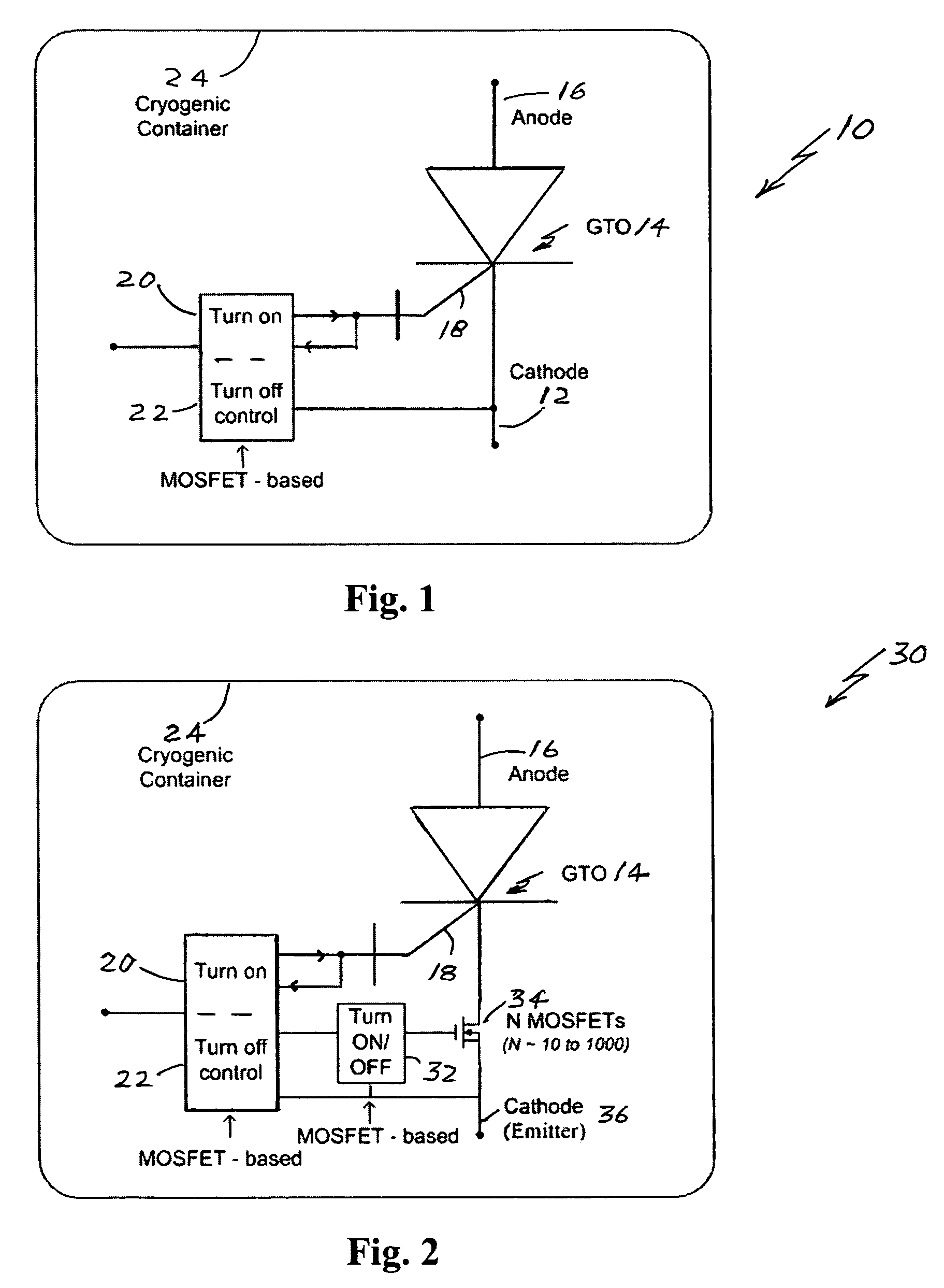

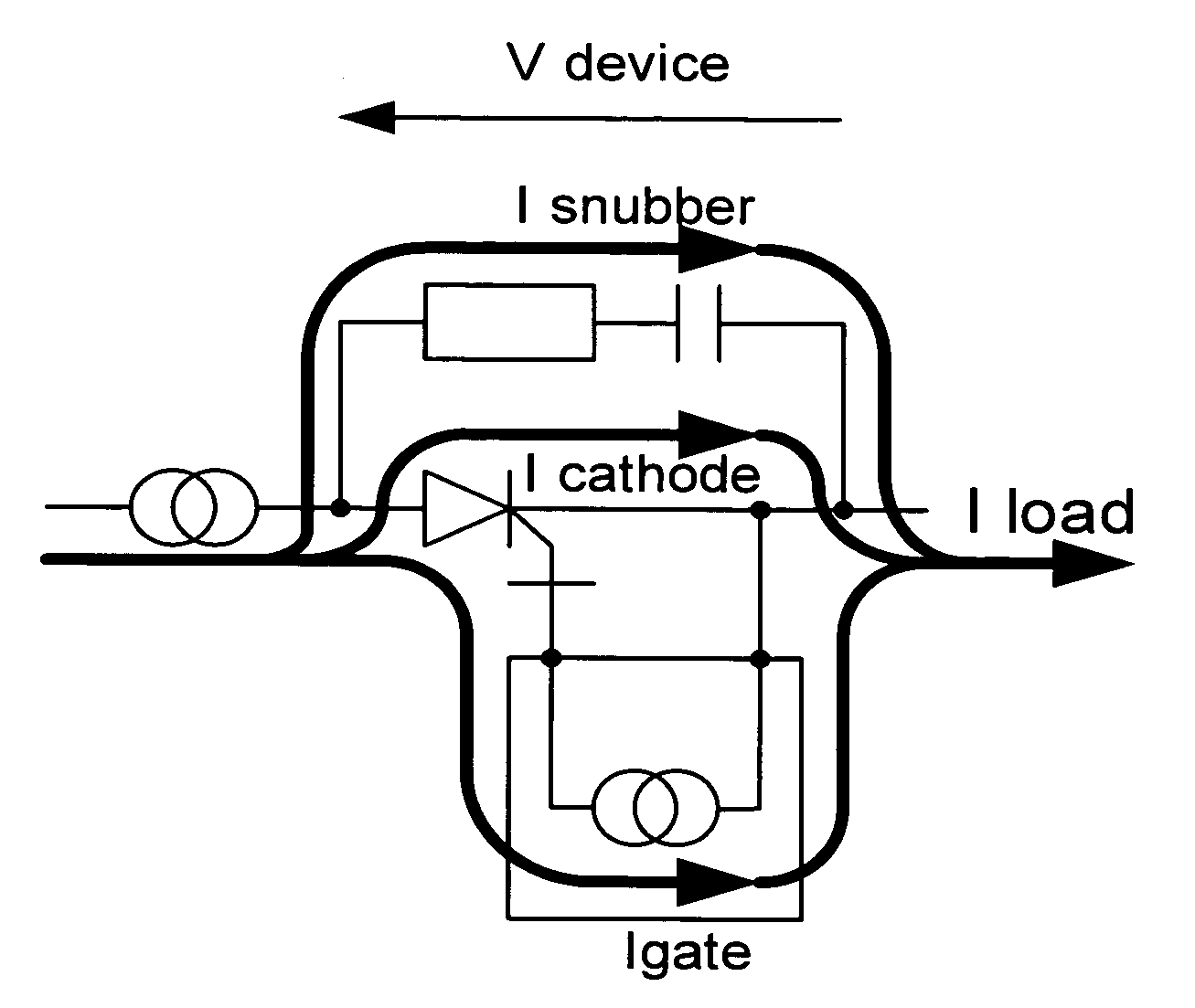

Emitter turn-off thyristors and their drive circuits

A family of emitter turn-off thyristors and their drive circuit comprise a gate turn-on (GTO) thyristor, a first switch, the drain of the first switch being connected to the cathode of the GTO thyristor, and a second switch connected between the gate of the GTO thyristor and the source of the first switch. The first switch consists of many paralleled metal oxide semiconductor field effect transistors (MOSFETs). The anode of the GTO thyristor and the source of the first switch serve as the annode and the cathode, respective, of the emitter turn-off thyristor. The emitter turn-off thyristor has four control electrodes: the gate of the GTO thyristor, the control electrode of the second switch, the gate of the first switch, and the cathode of the GTO thyristor. The drive circuit comprises a current source circuit, a voltage clamp circuit, a current direction detector, and a control circuit. The ETO thyristor further comprises a current sensing and over-current detector circuit. The first switch is packaged in a printed circuit board.

Owner:VIRGINIA TECH INTPROP INC

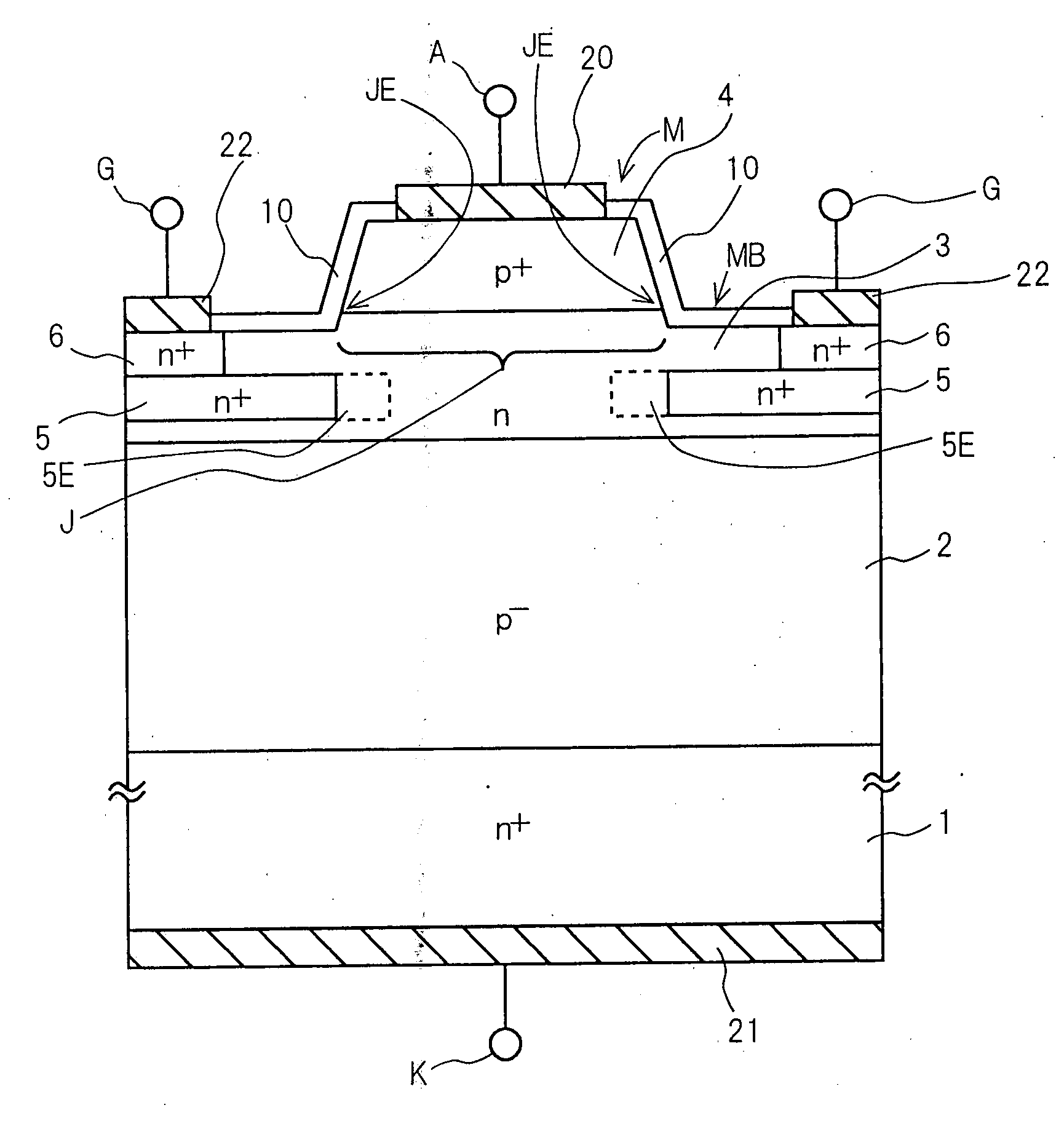

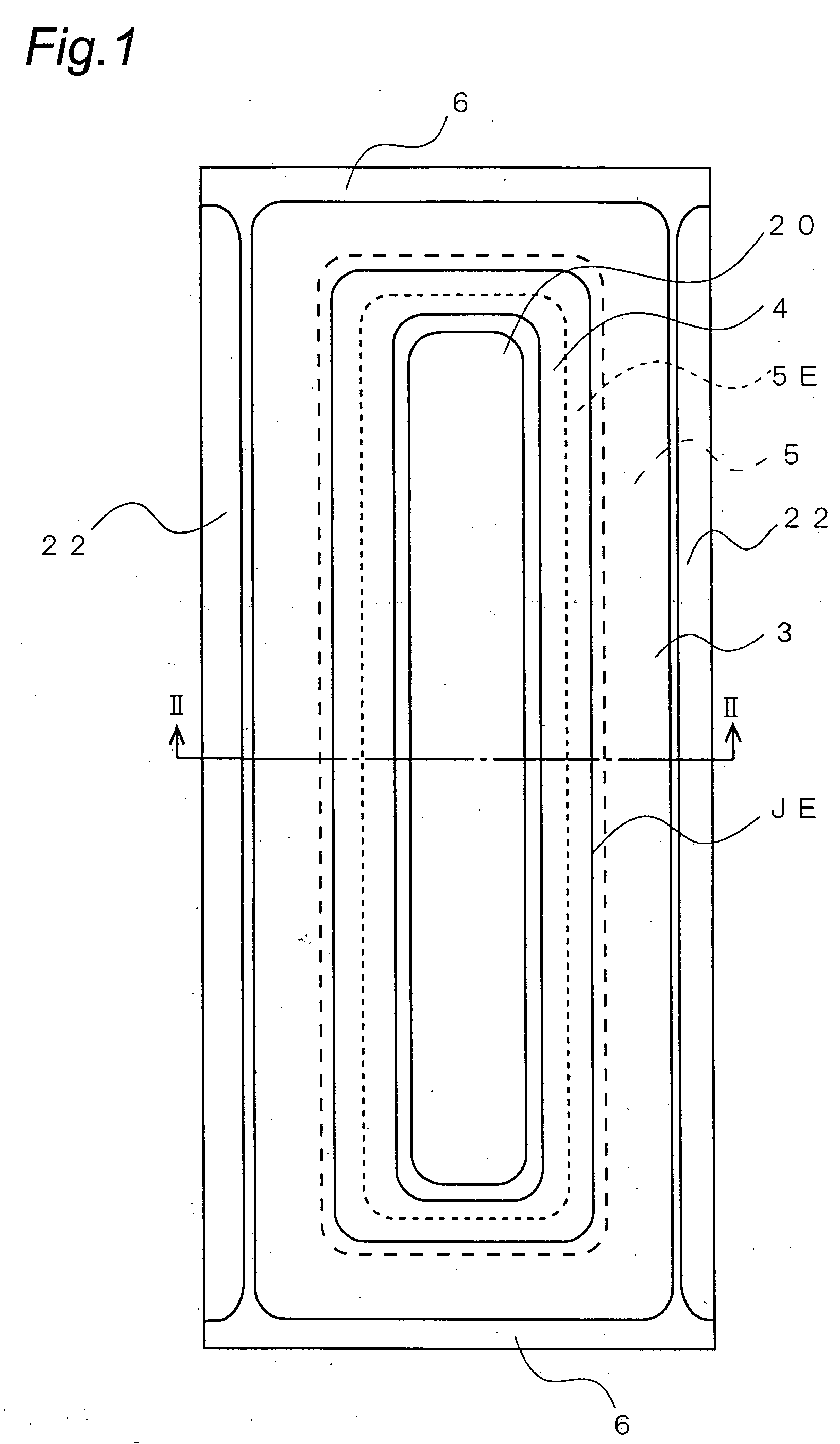

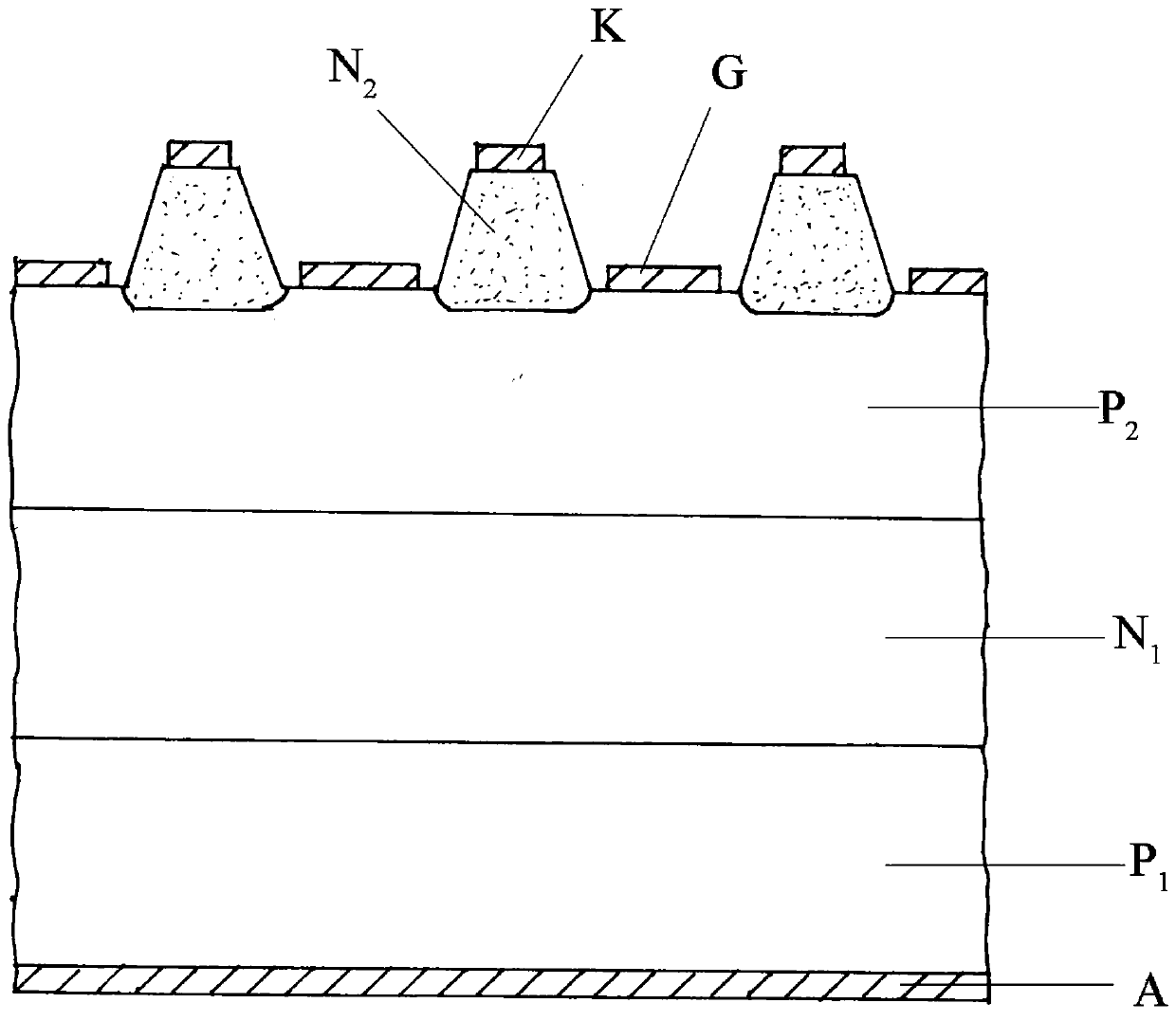

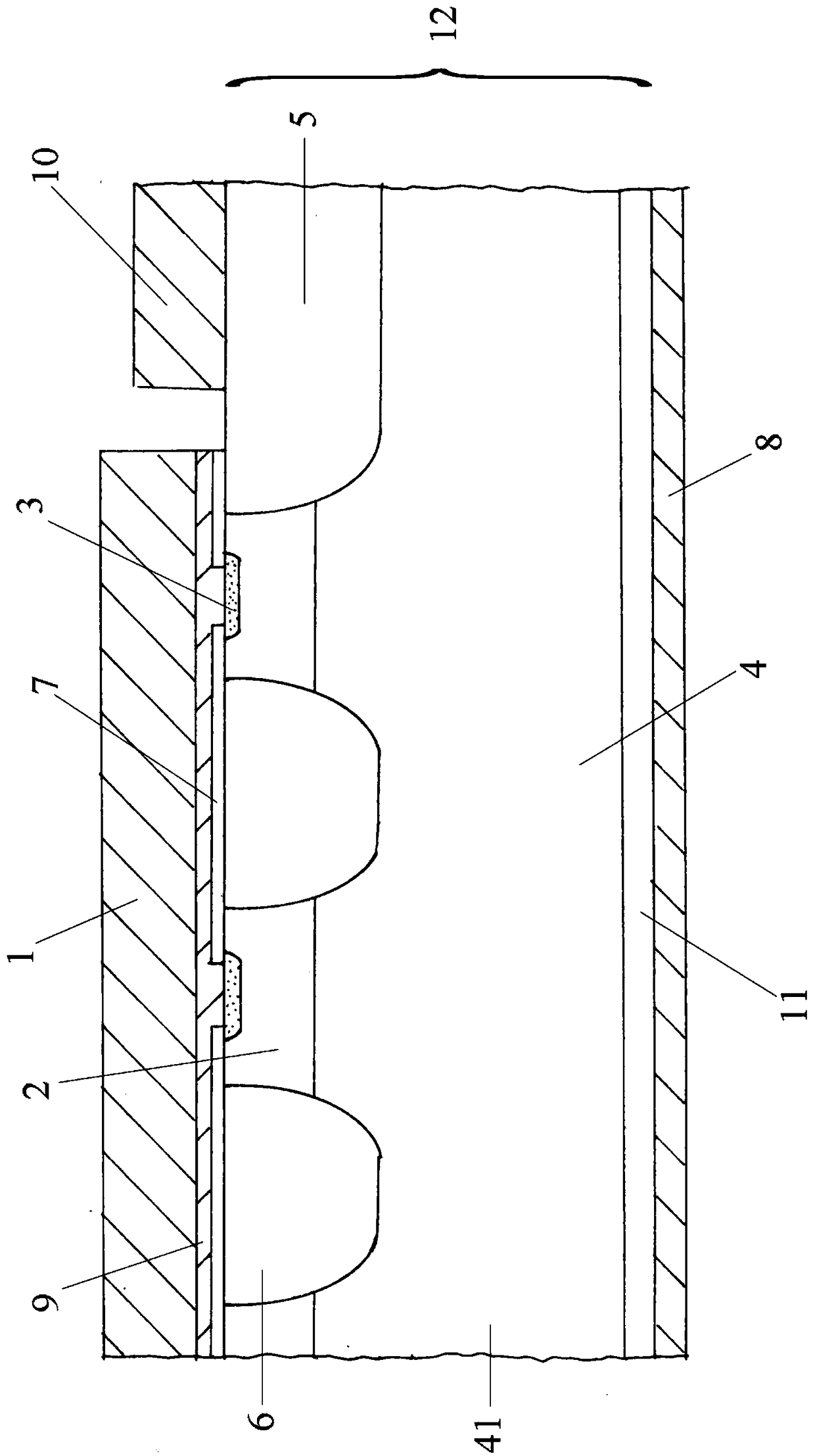

Gate turn-off thyristor

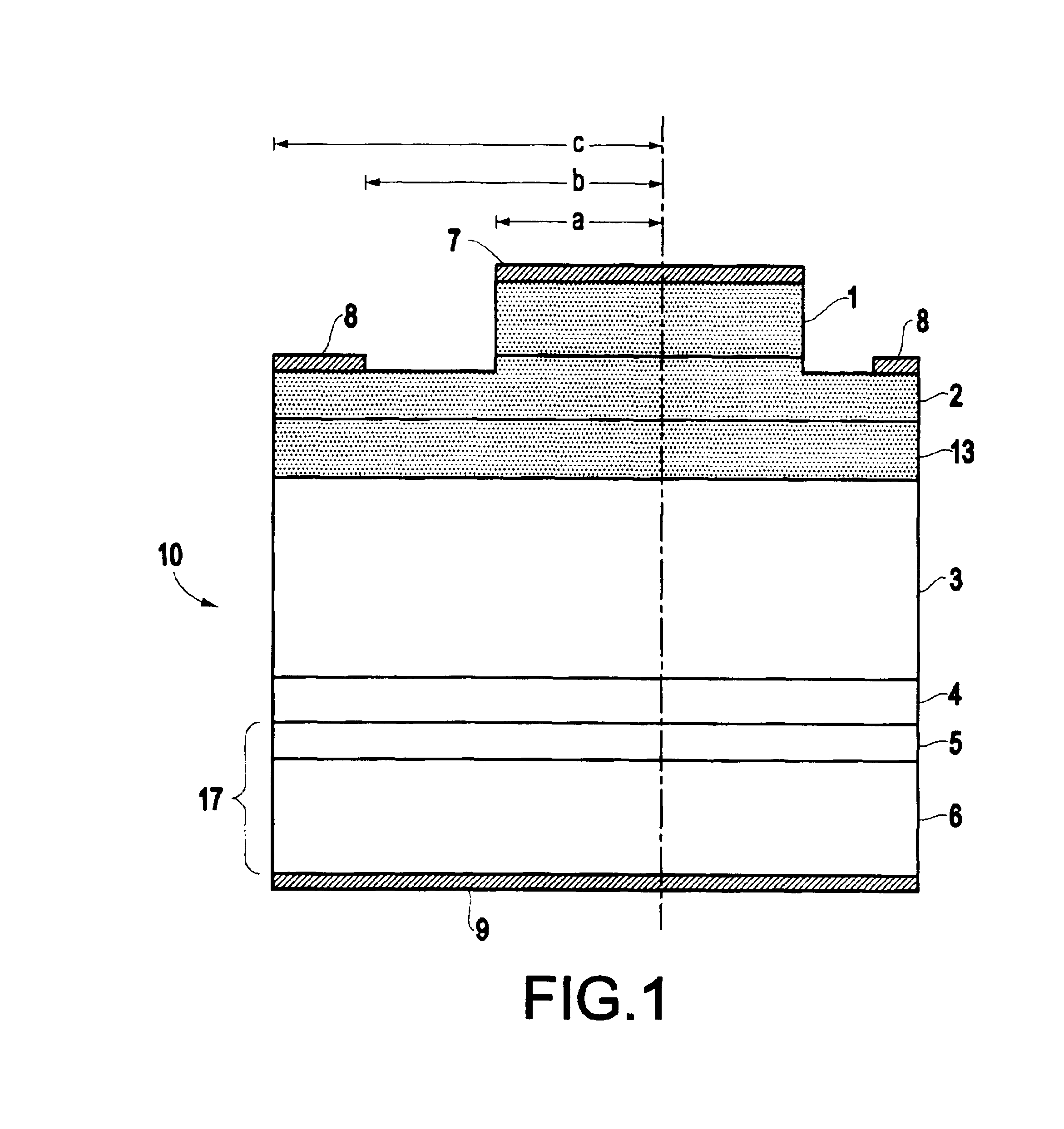

A mesa-type wide-gap semiconductor gate turn-off thyristor has a low gate withstand voltage and a large leakage current. Since the ionization rate of P-type impurities greatly increases at high temperatures when compared with that at room temperature, the hole implantation amount increases and the minority carrier lifetime becomes longer. Consequently, the maximum controllable current is significantly lowered when compared with that at room temperature. To solve these problems, a p-type base layer is formed on an n-type SiC cathode emitter layer which has a cathode electrode on one surface, and a thin n-type base layer is formed on the p-type base layer. A mesa-shaped p-type anode emitter layer is formed in the central region of the n-type base layer. An n-type gate contact region is formed sufficiently apart from the junction between the p-type anode emitter layer and the n-type base layer, and an n-type low-resistance gate region is so formed in the n-type base layer that it surrounds the anode emitter layer.

Owner:THE KANSAI ELECTRIC POWER CO

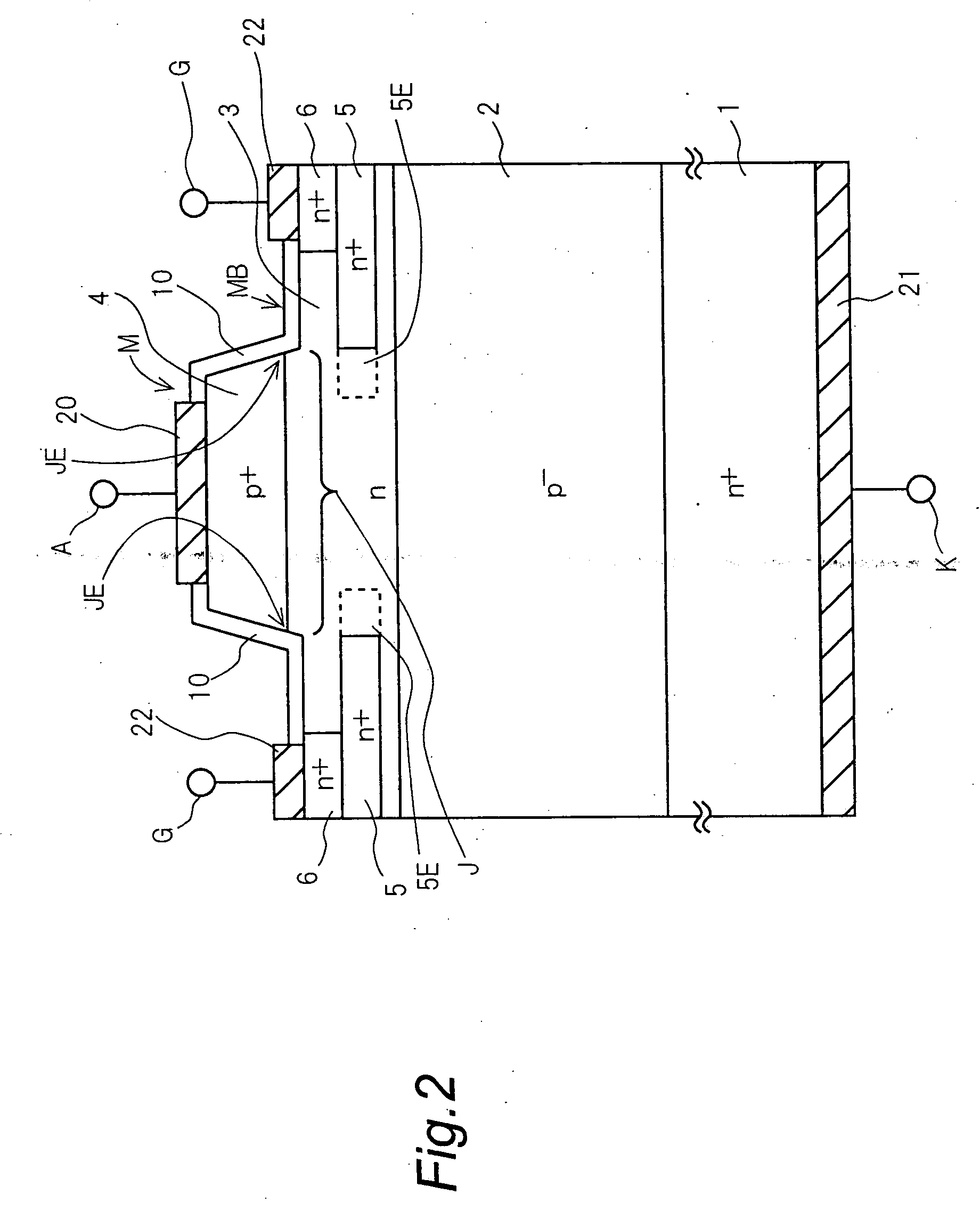

Processing technique to improve the turn-off gain of a silicon carbide gate turn-off thyristor and an article of manufacture

A structure and method for a silicon carbide (SiC) gate turn-off (GTO) thyristor device operable to provide an increased turn-off gain comprises a cathode region, a drift region having an upper portion and a lower portion, wherein the drift region overlies the cathode region, a gate region overlying the drift region, an anode region overlying the gate, and at least one ohmic contact positioned on each of the gate region, anode region, and cathode region, wherein the upper portion of the drift region, the gate region, and the anode region have a free carrier lifetime and mobility lower than a comparable SiC GTO thyristor for providing the device with an increased turn-off gain, wherein the free carrier lifetime is approximately 10 nanoseconds. The reduced free carrier lifetime and mobility are affected by altering the growth conditions, such as temperature under which epitaxy occurs.

Owner:ARMY US SEC THE

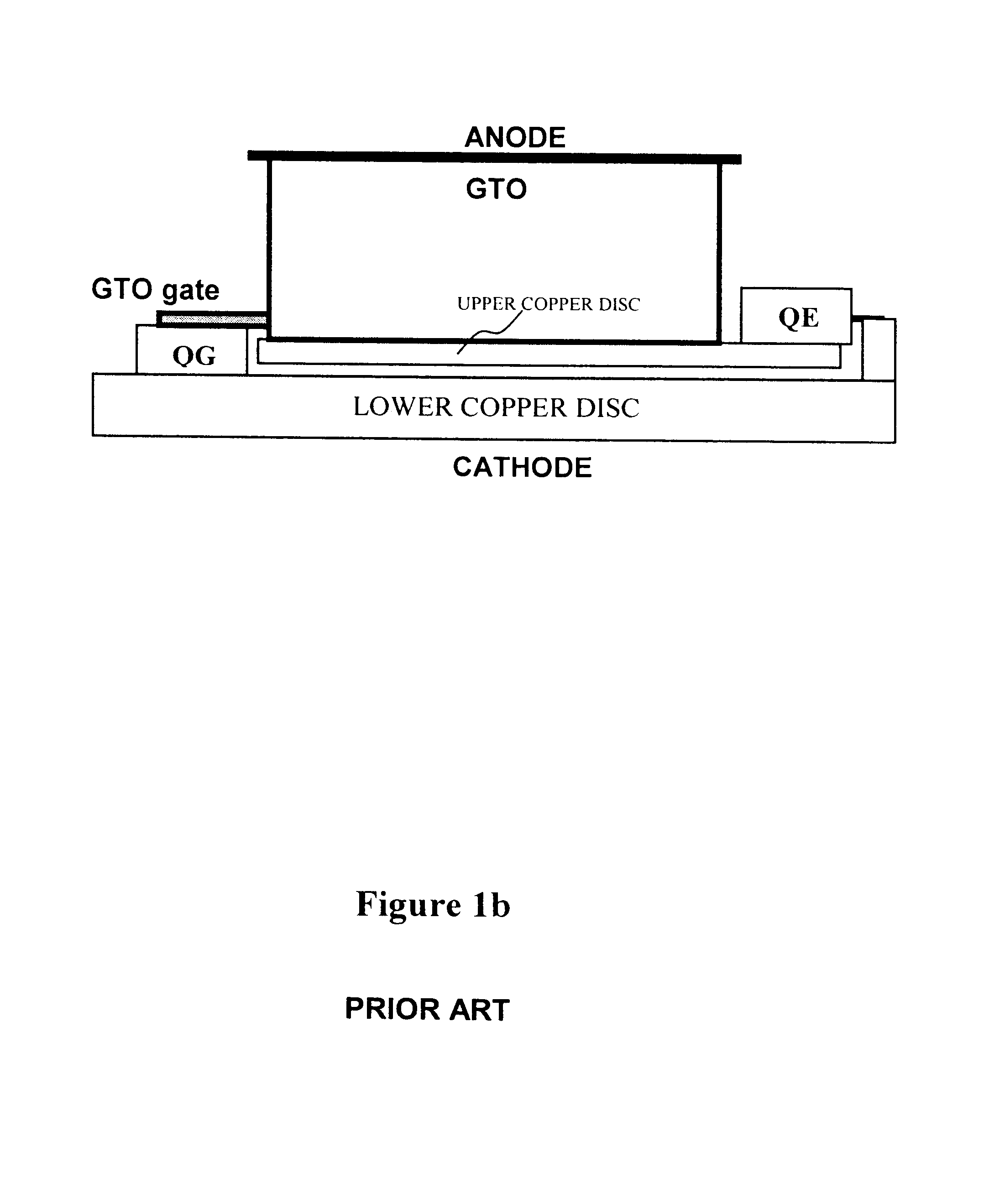

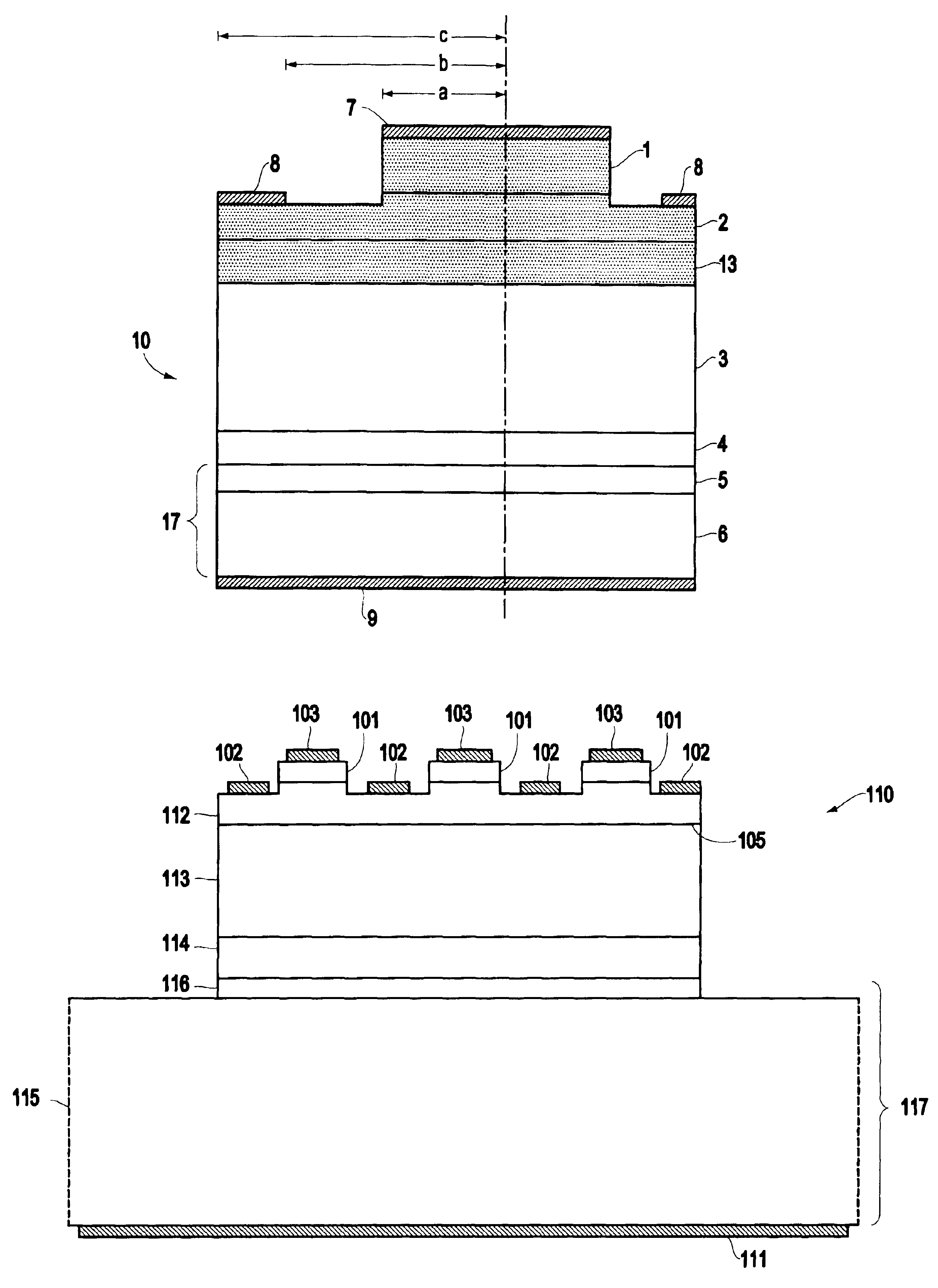

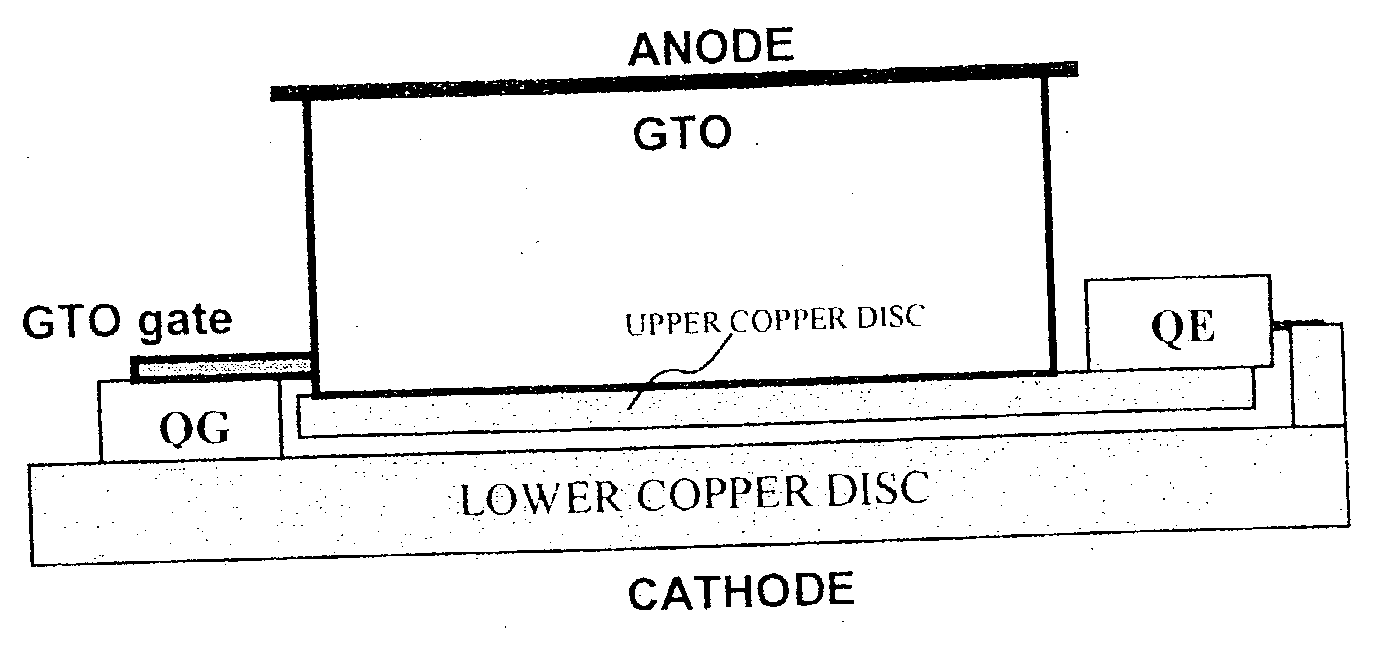

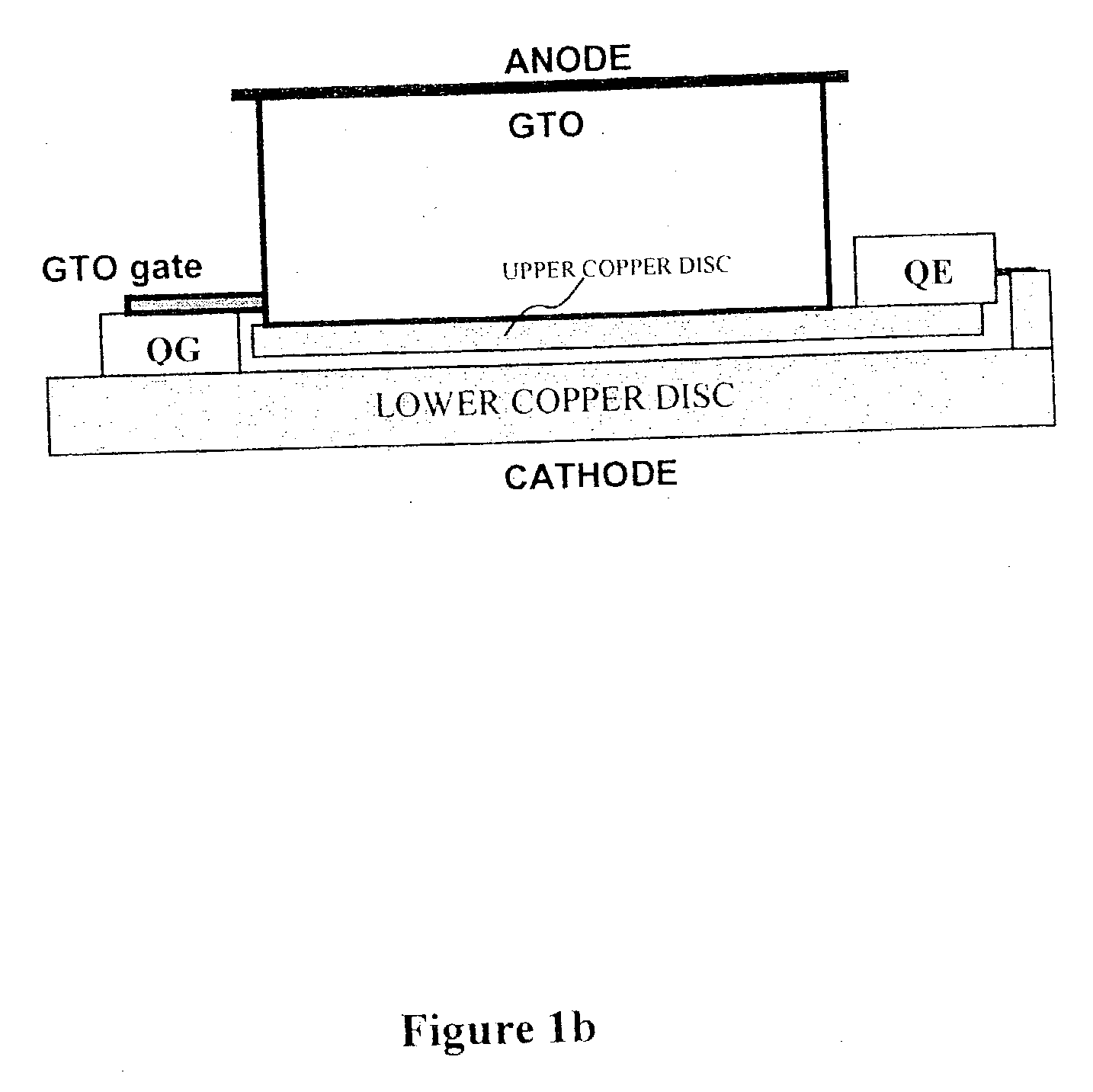

Super GTO-based power blocks

InactiveUS7692211B1Minimizes differential gate-cathode inductanceLower impedanceThyristorSemiconductor/solid-state device detailsGate turn-off thyristorEngineering

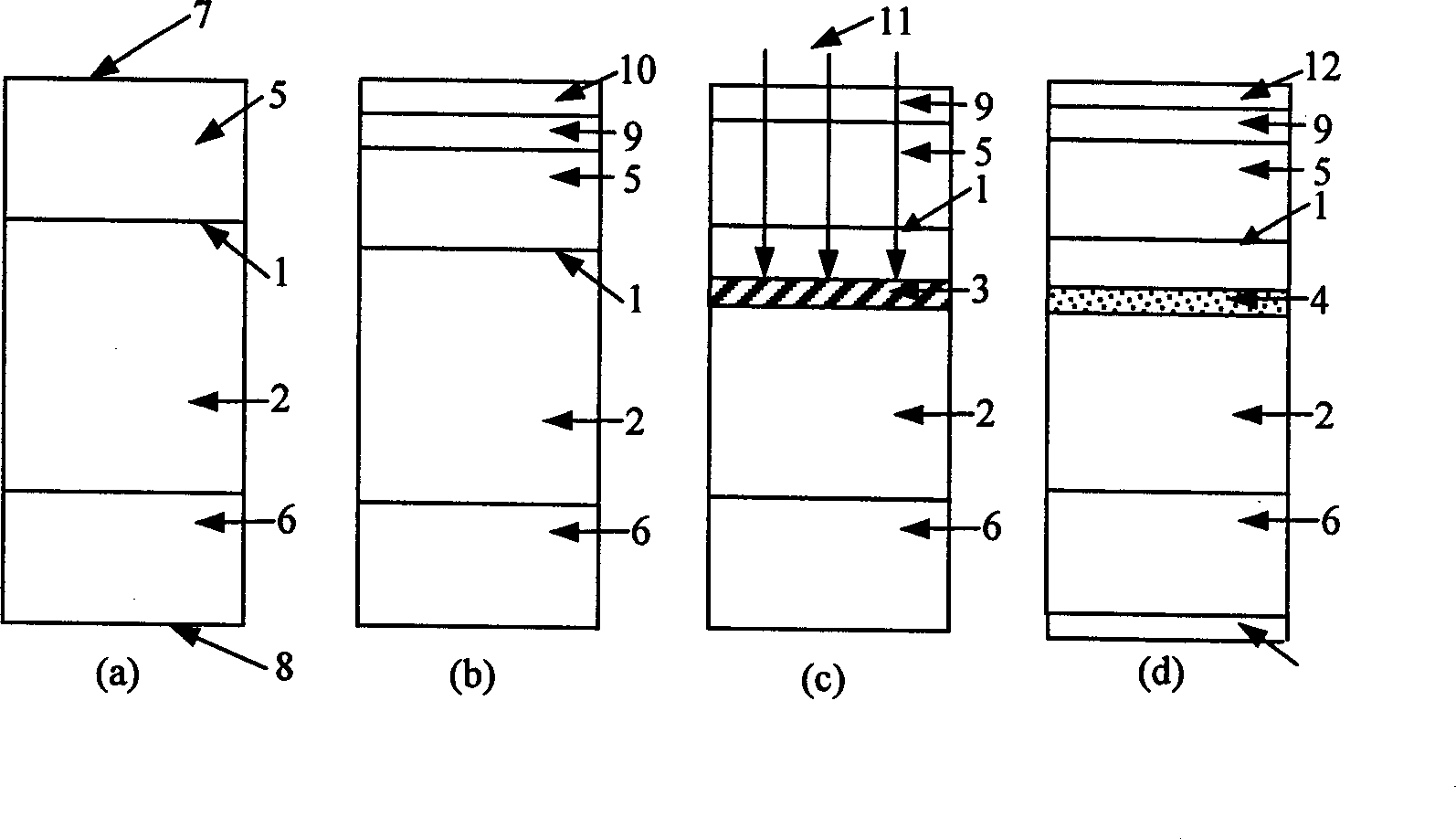

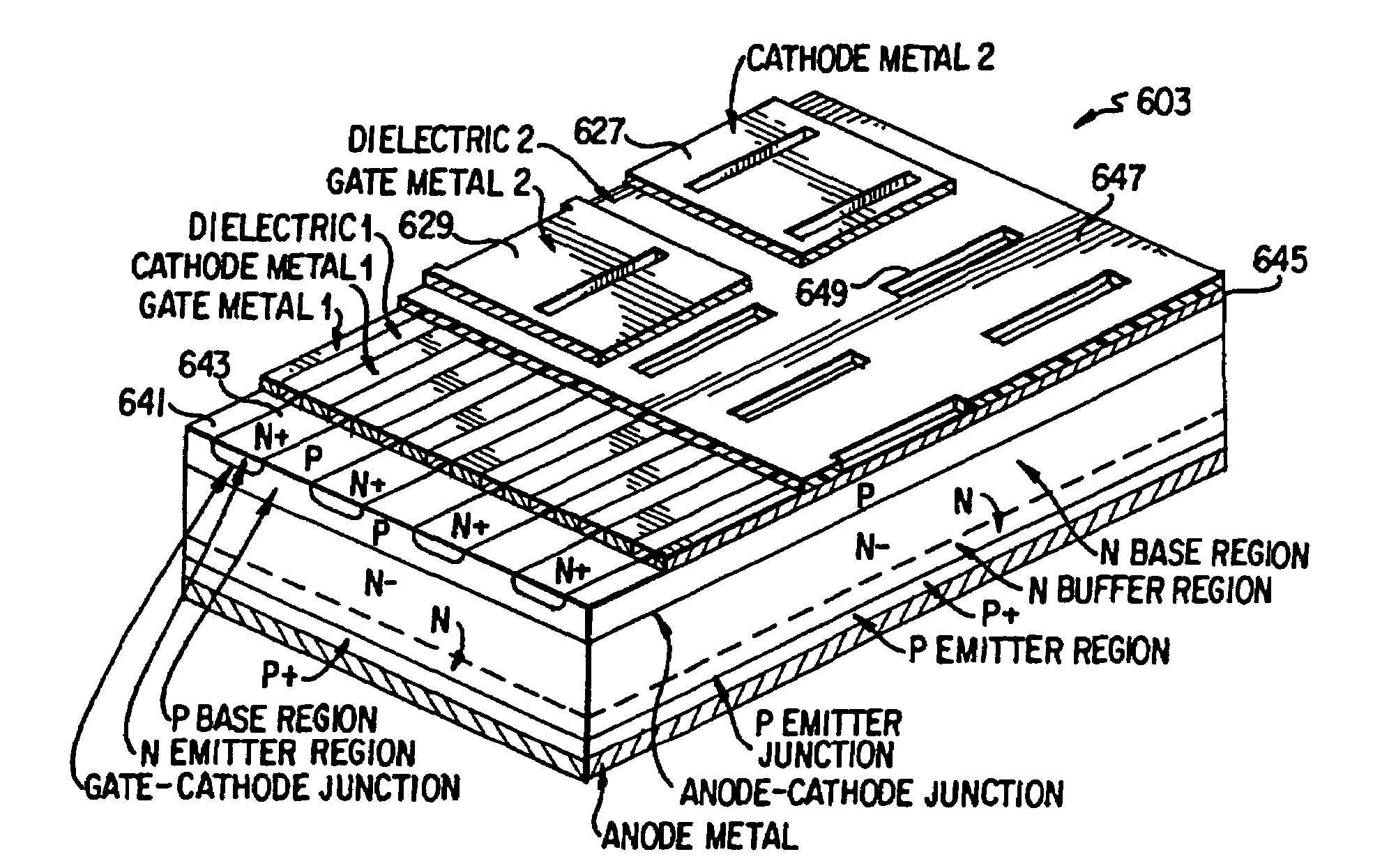

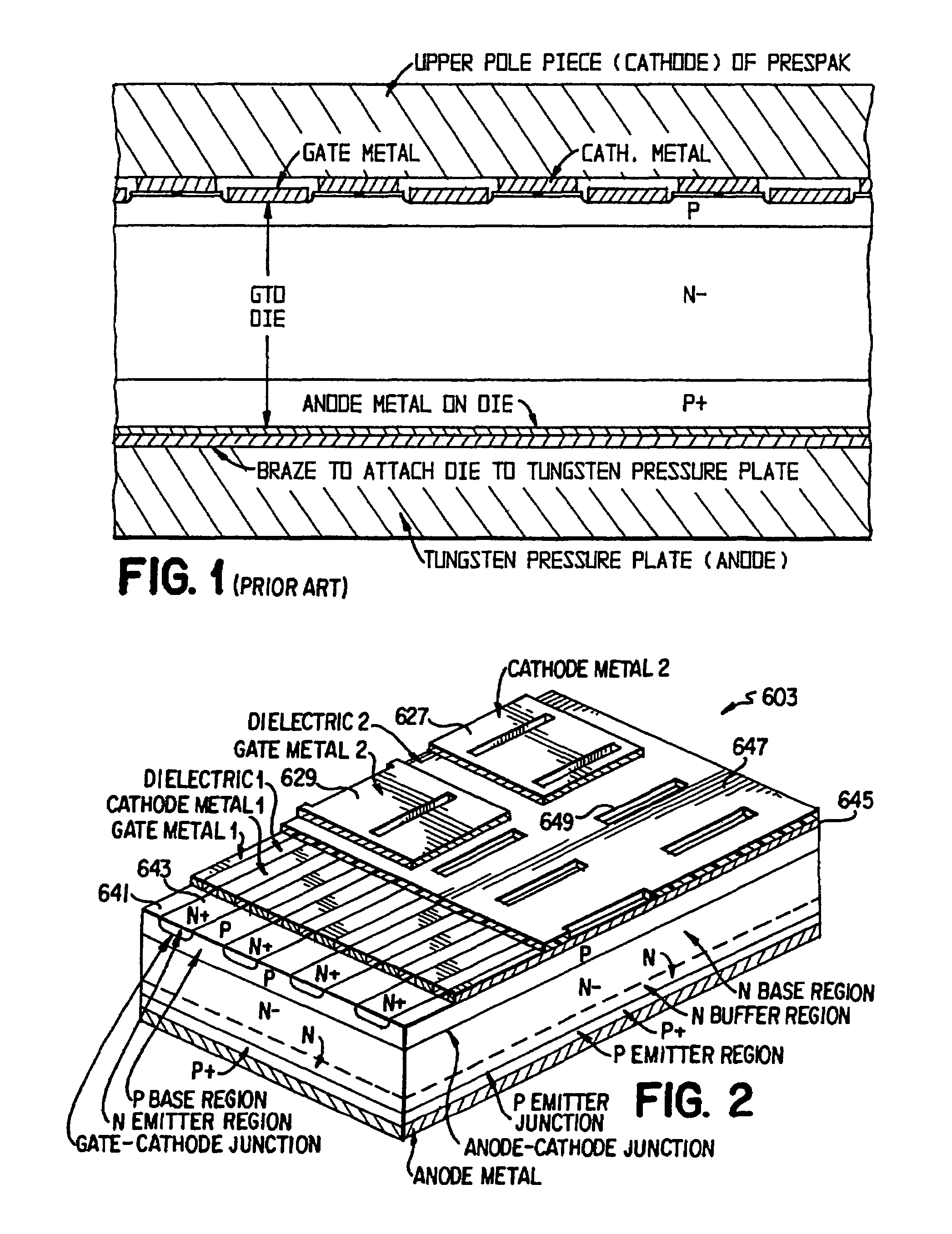

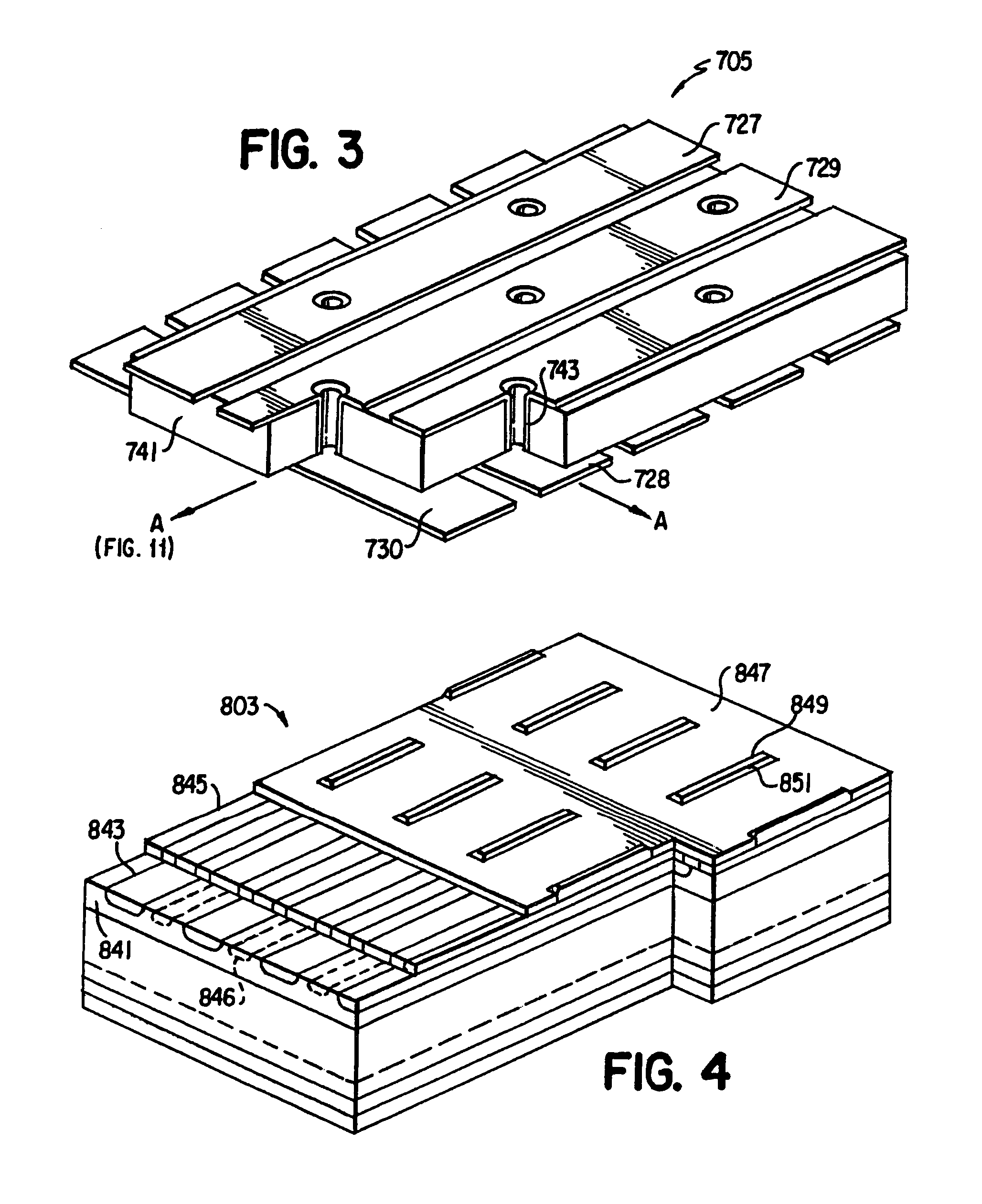

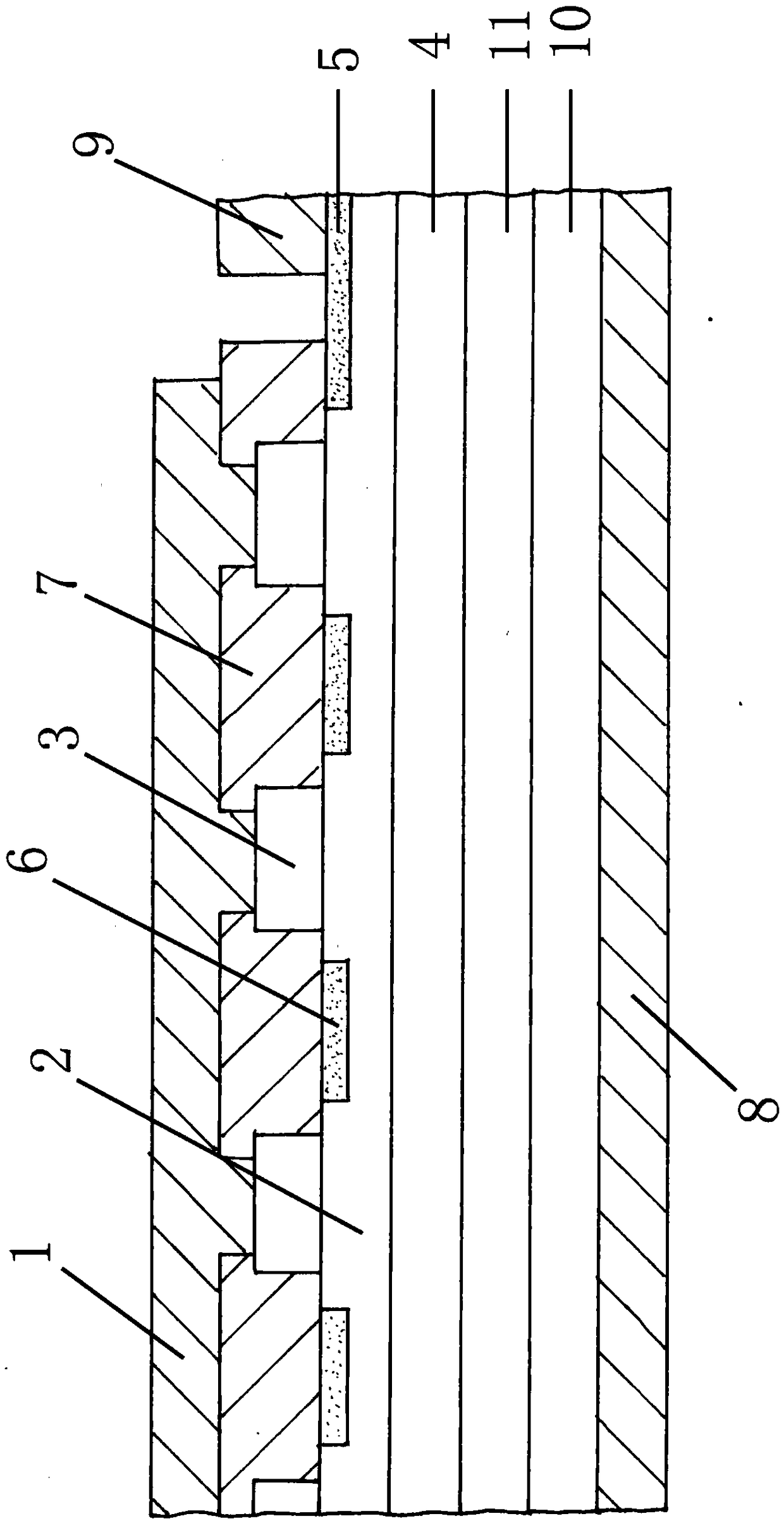

A gate turn-off thyristor (GTO) device has a lower portion, an upper portion and a lid. The lower portion has a lower base region of a first conductivity type, and a lower emitter region of a second conductivity type disposed at or from a lower surface of the lower base region. A lower junction is formed between the lower base region and the lower emitter region. The upper portion has an upper base region of the second conductivity type, and upper emitter regions of the first conductivity type disposed at or from an upper surface of the upper base region. An upper-lower junction is formed between the lower base region and the upper base region, and upper junctions are formed between the upper base region and the upper emitter regions. The upper base region and upper emitter regions form an upper base surface with first conductive contacts to the upper base region alternating with second conductive contacts to the upper emitter regions. The lid has a layer of insulator with upper and lower surfaces. Upper metal stripes extend along the upper surface of the insulator, and lower metal stripes extend along the lower surface of the insulator. The upper and lower metal stripes are connected together by vias that extend through the insulator. One set of the lower metal stripes contacts the first conductive contacts, but not the second conductive contacts. Another set of the lower metal stripes contacts the second conductive contacts, but not the first conductive contacts.

Owner:EXCELITAS TECH

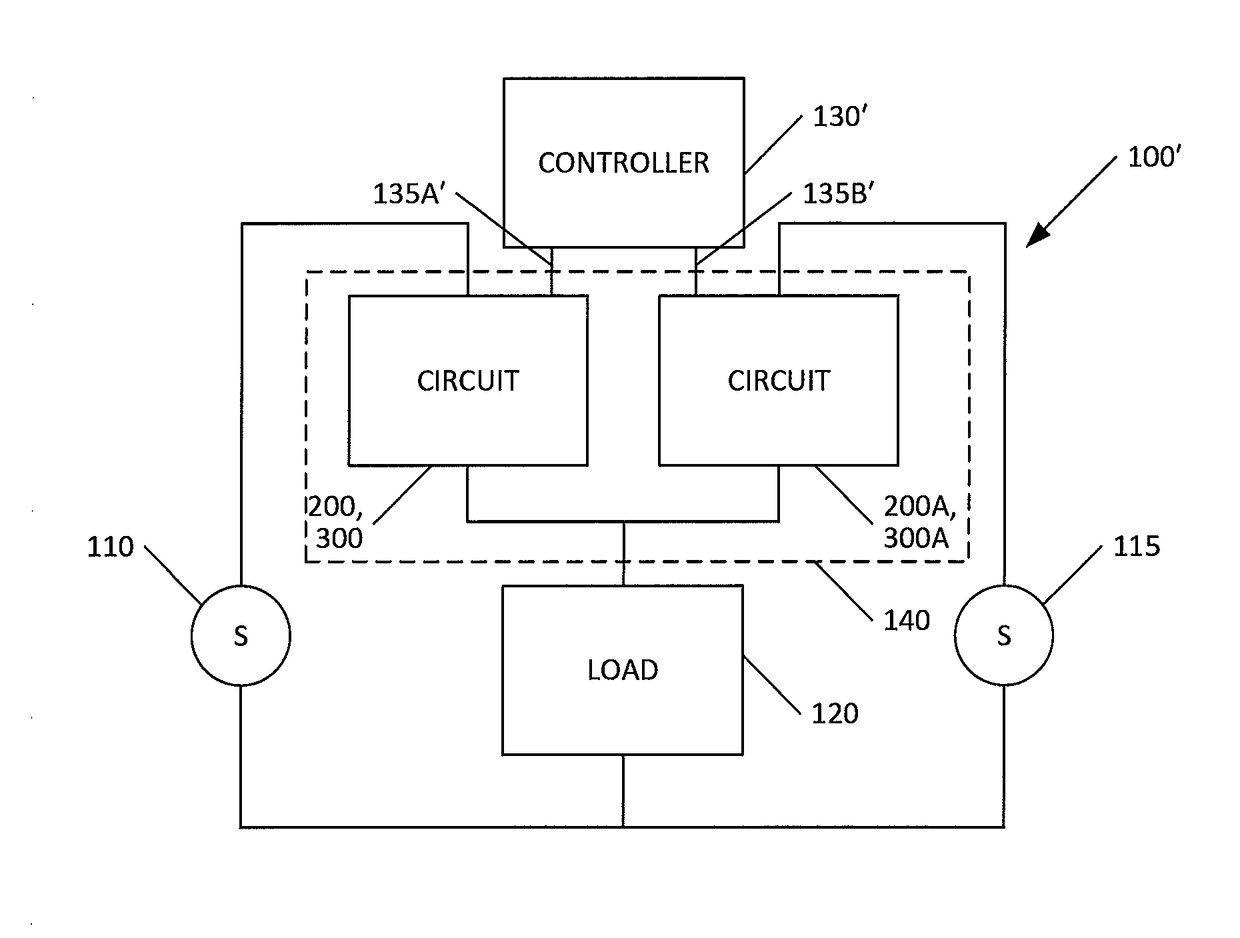

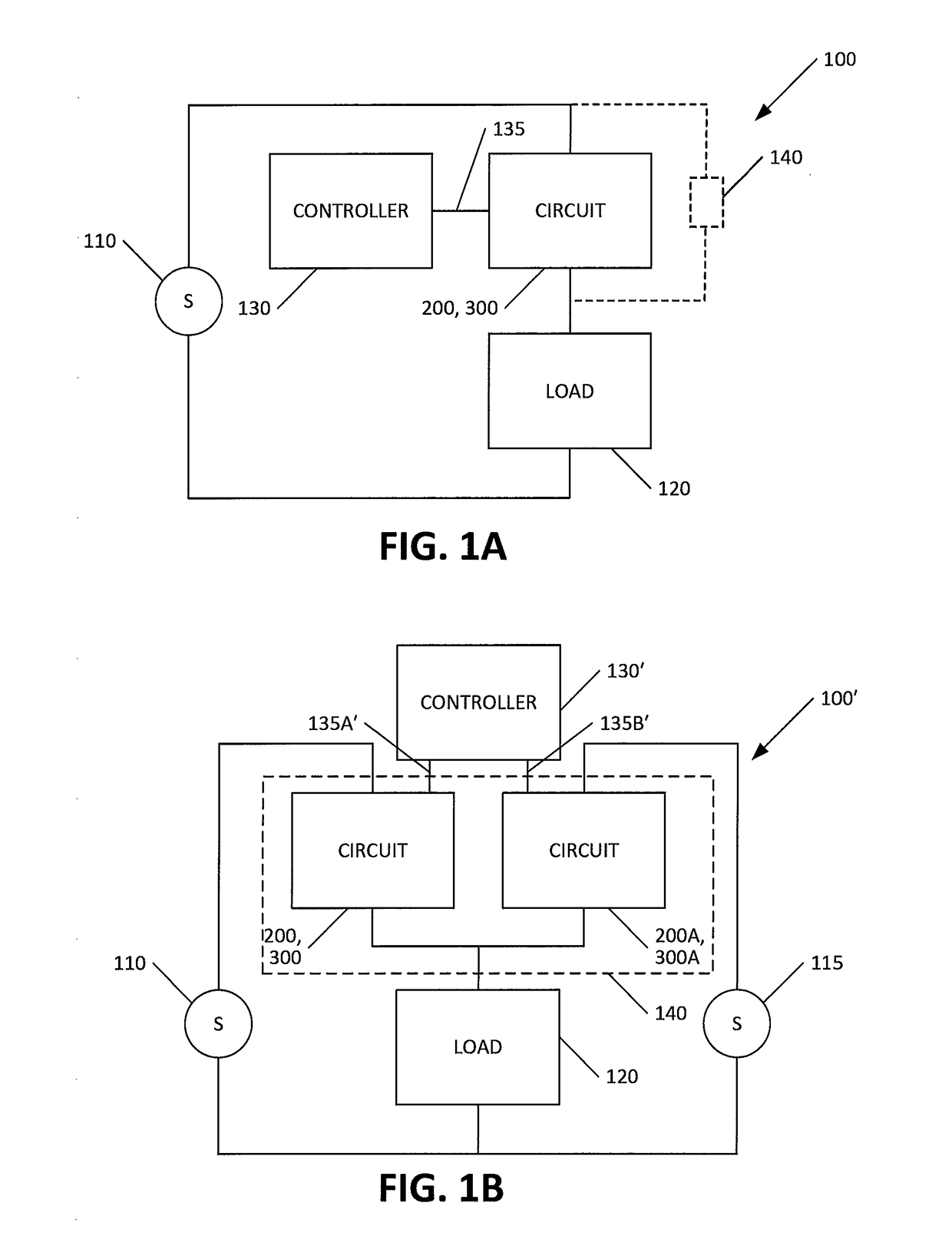

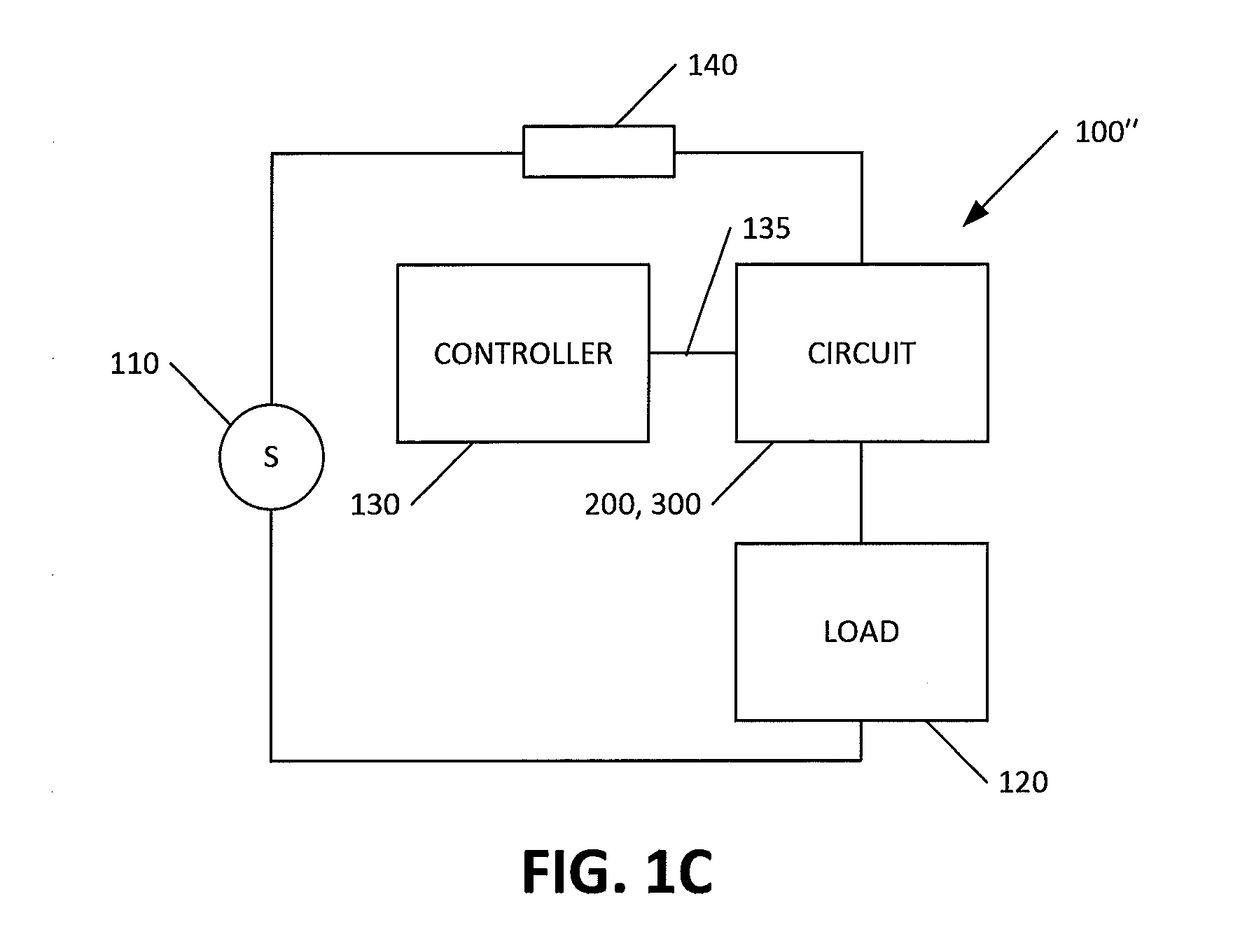

Low-loss and fast acting solid-state breaker

InactiveUS20170141558A1Electronic switchingArrangements responsive to excess currentGate turn-off thyristorIrradiation

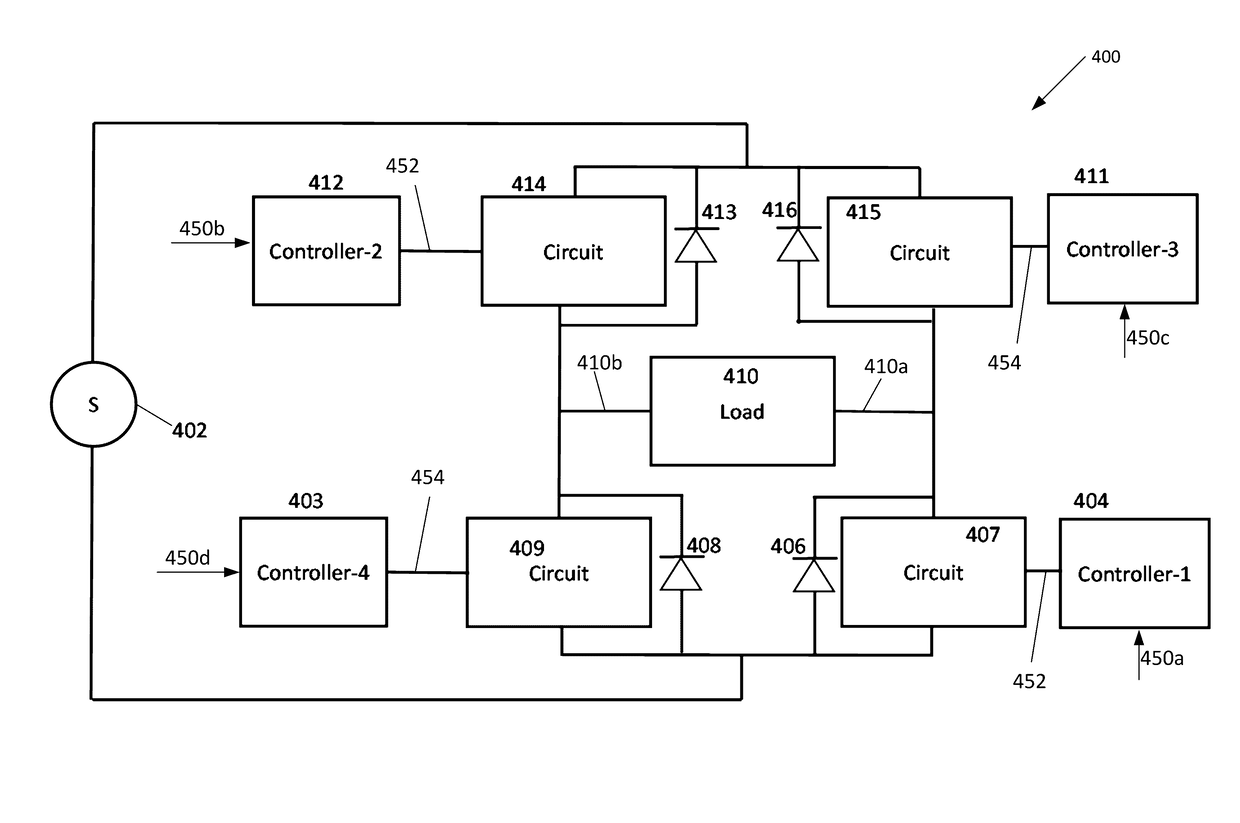

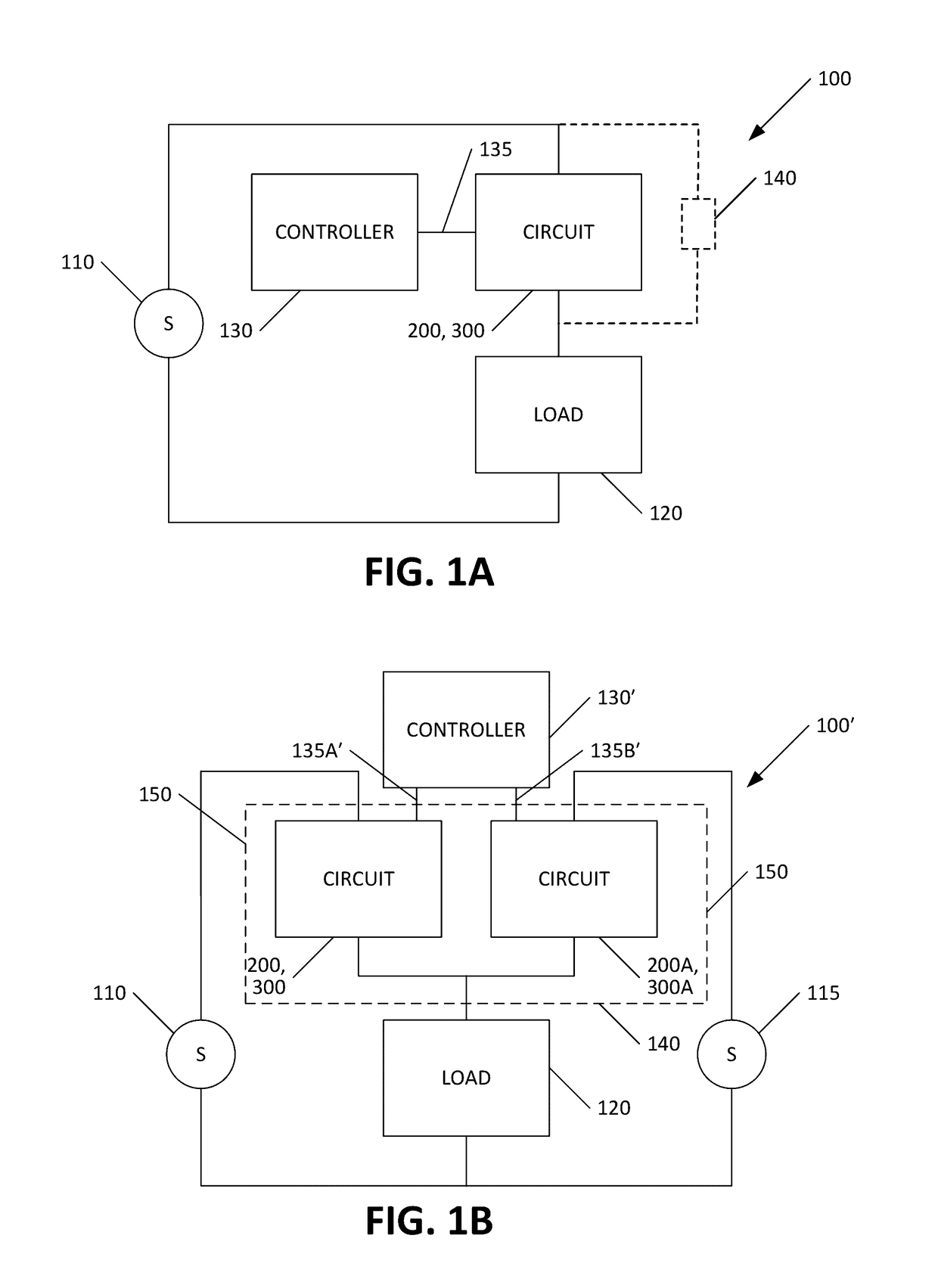

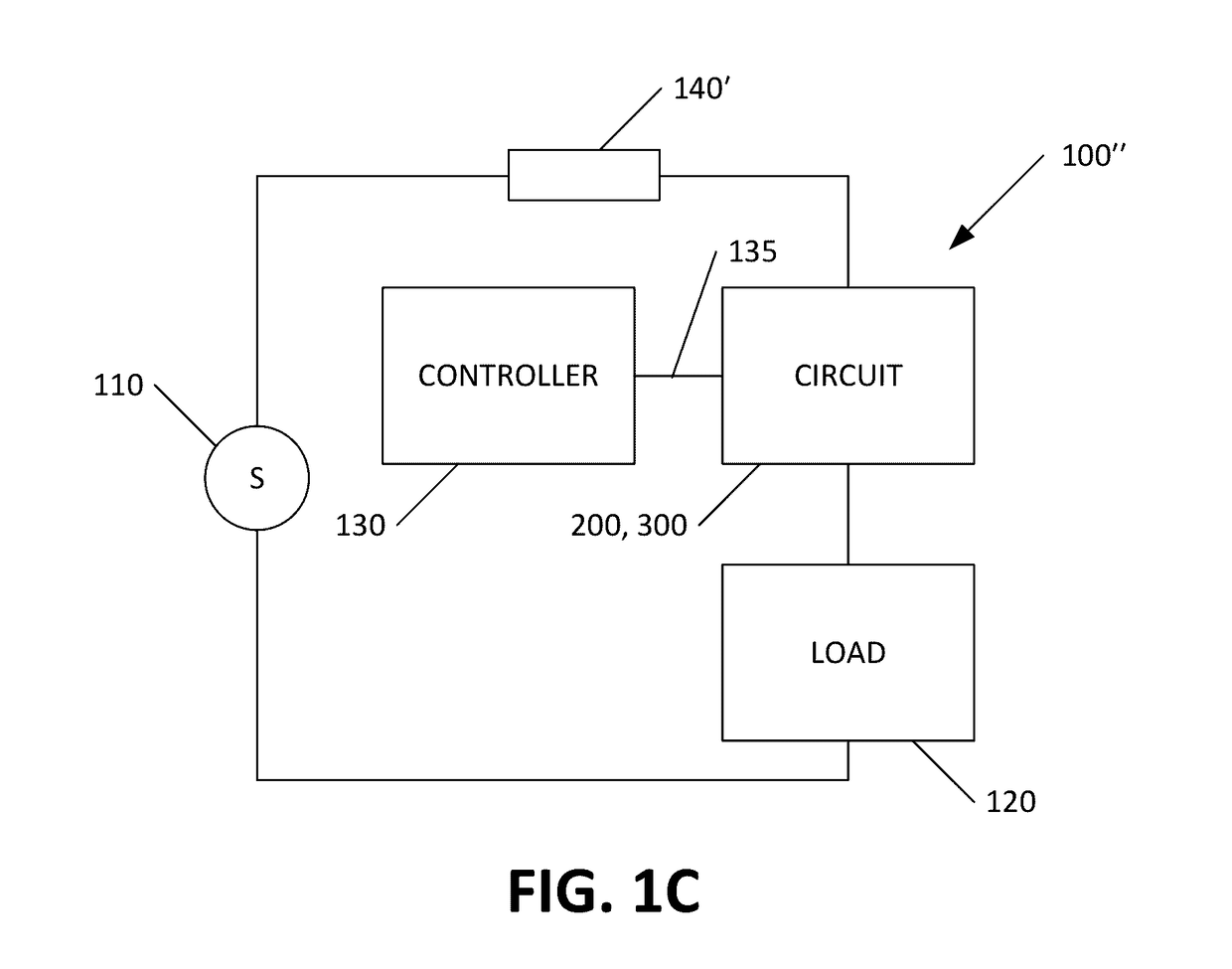

A circuit including a source, a load, and an isolation circuit for controllably isolating the load from the source. The isolation circuit is disposed between the source and the load. The isolation circuit includes at least one insulated-gate bipolar transistor (IGBT) and at least one gate turn-off thyristor (GTO) in parallel with the insulated-gate bipolar transistor. When no fault condition exists, the GTO is configured to be ON to couple the load to the source. When a fault condition exists, the at least one IGBT is configured to turn ON. After the at least one IGBT turns ON, the at least one GTO is configured to turn OFF. After a predetermined amount of time, reflecting the post fabrication alteration to the GTO's minority carrier lifetime (e.g. electron irradiation), after the at least one GTO turns OFF, the at least one IGBT is configured to turn OFF. Alternatively, the circuit is used as an inverter switch, where at the command to turn ON is supplied, the at least one IGBT is turned ON, followed by the at least one SGTO. When commanded to turn OFF the at least one SGTO is turned OFF followed by the at least one IGBT. This alternative configuration allows the robust, controllable switching speeds of IGBTs and the superior conduction efficiency of SGTOs. The two configurations mentioned above utilize a wide range of SGTO performance, thus the ability to control the SGTOs turn-off speed by reducing its minority carrier lifetime after the device is processed is of large importance. The efficiency of all uses of the circuit can be optimized with the judicious selection of SGTO minority carrier lifetime and the ratio of active area between the SGTO and IGBT devices. In all cases there is a balance between the time the circuit can achieve hard turn-off without current commutation, the conduction efficiency of the circuit and the maximum amount of controllable current. In all cases both the conduction efficiency of the circuit is higher than an IGBT-only based circuit, and the switching performance is higher than a GTO-only based circuit.

Owner:EXCELITAS TECH

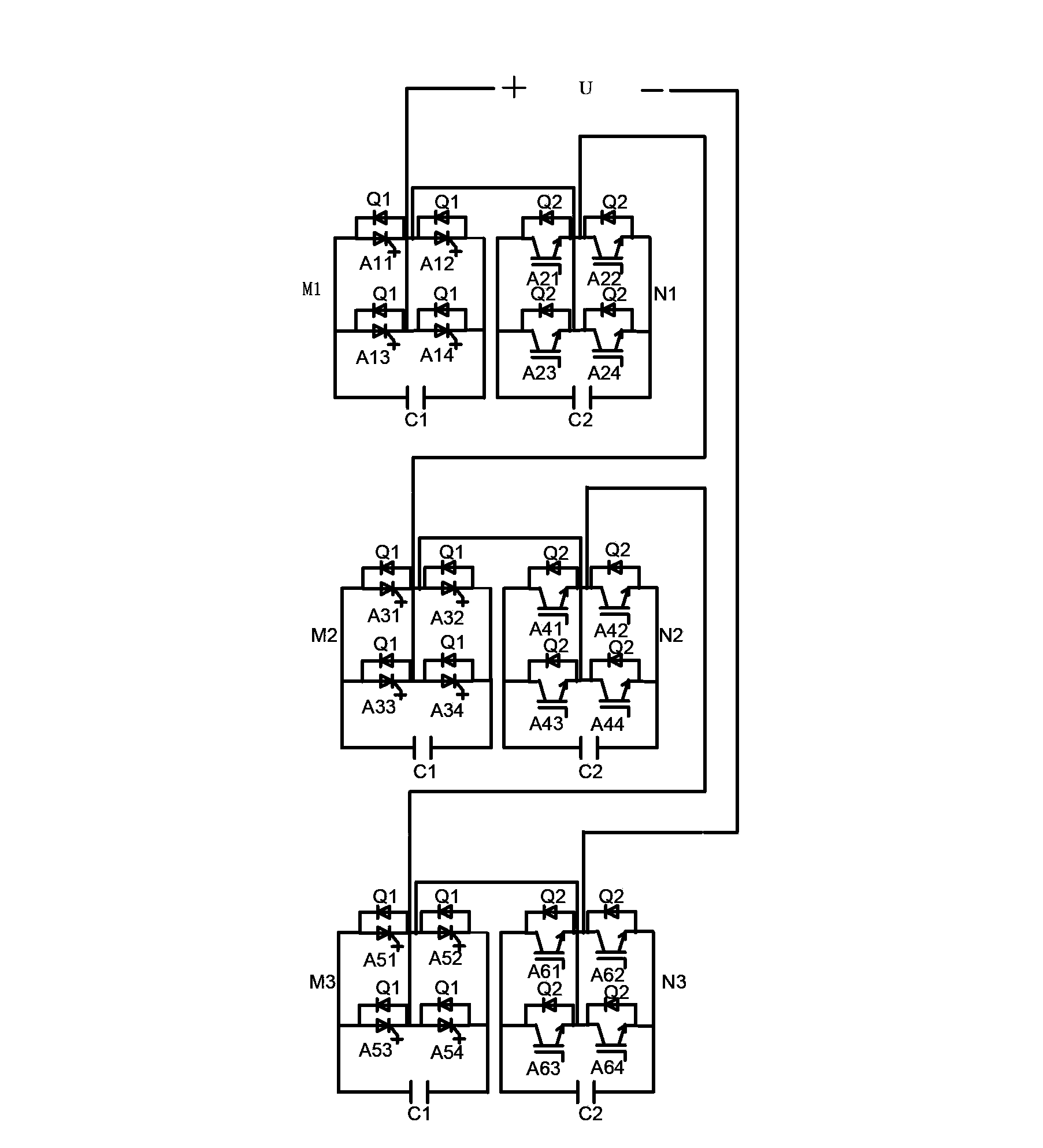

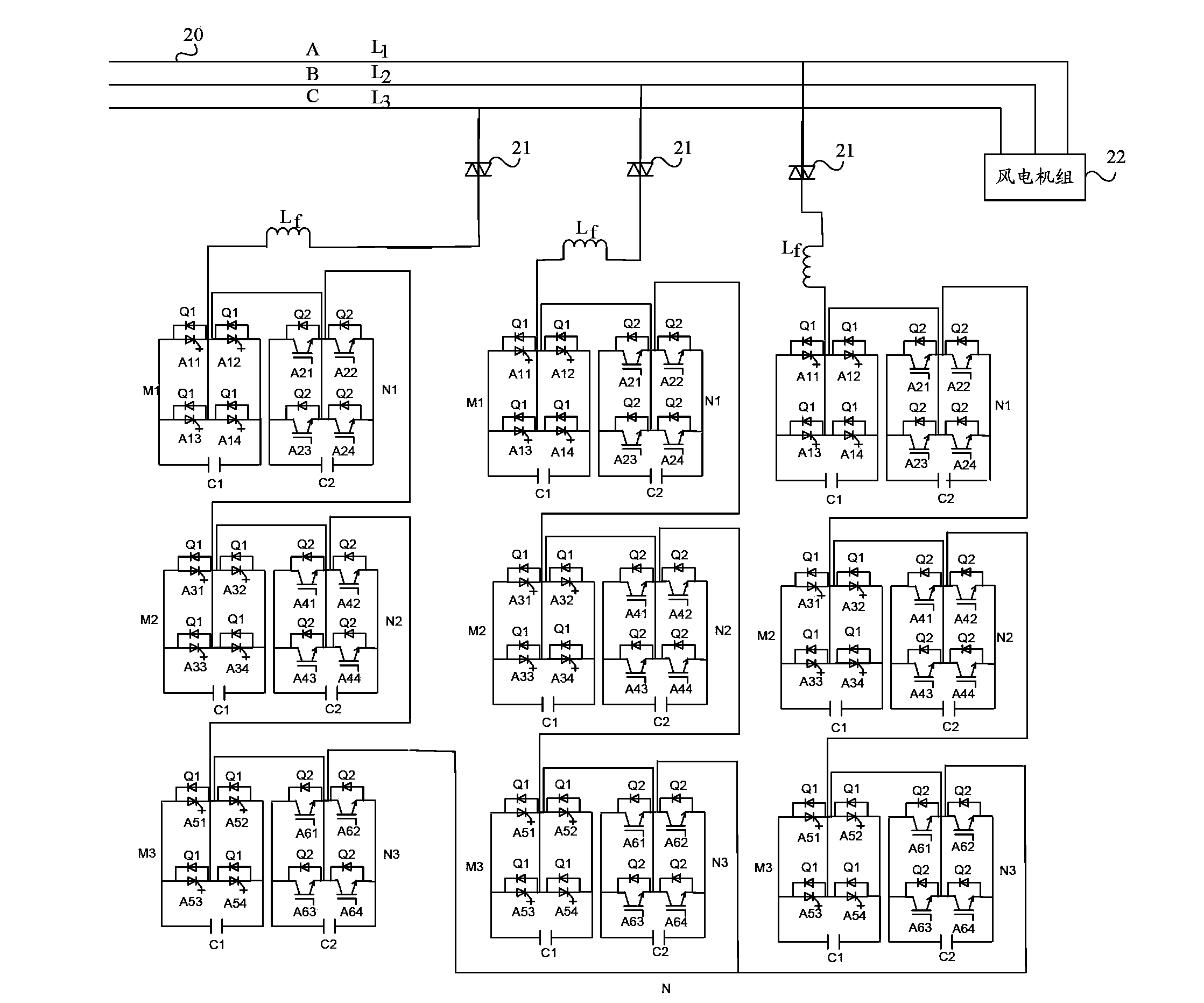

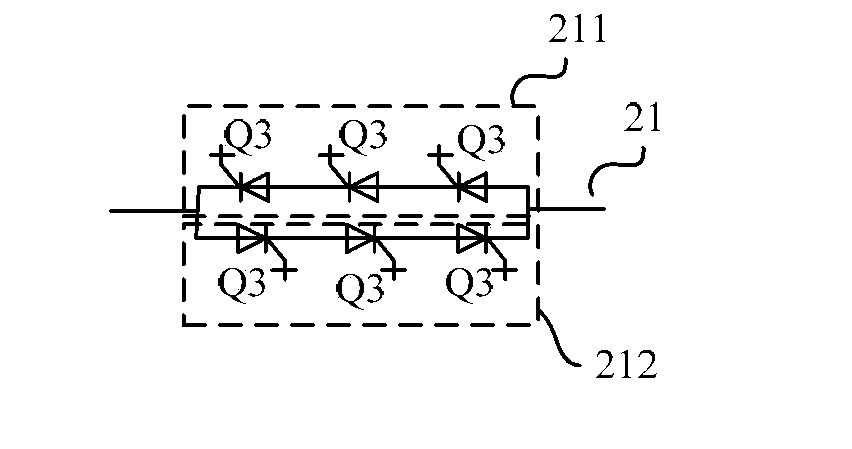

Hybrid cascading multi-level static synchronous compensation device and wind turbine generator set power supply system

ActiveCN103390896AReduce THDIncrease the switching frequencyFlexible AC transmissionReactive power adjustment/elimination/compensationGate turn-off thyristorElectricity

The invention provides a hybrid cascading multi-level static synchronous compensation device and a wind turbine generator set power supply system. The synchronous compensation device comprises a first H-bridge power unit and a second H-bridge power unit. The first H-bridge power unit comprises two parallel-connection bridge arms, wherein each bridge arm comprises two series-connection gate pole turn-off thyristors. The second H-bridge power unit comprises two parallel-connection bridge arms, wherein each bridge arm comprises two series-connection insulated gate bipolar transistors. The characteristics of power devices in the first H-bridge power unit in the synchronous compensation device and the characteristics of power devices in the second H-bridge power unit in the synchronous compensation device are complementary to form a hybrid cascading circuit structure, the aims that the switching frequency of the power devices is reduced and the capacity of the synchronous compensation device is improved can be well achieved, and the synchronous compensation device can be applied in power supply systems of various types, and particularly suitable for the power supply system of a wind turbine generator set with the high megawatt power so as to meet the application requirements of the high-power wind turbine generator set.

Owner:SINOVEL WIND GRP

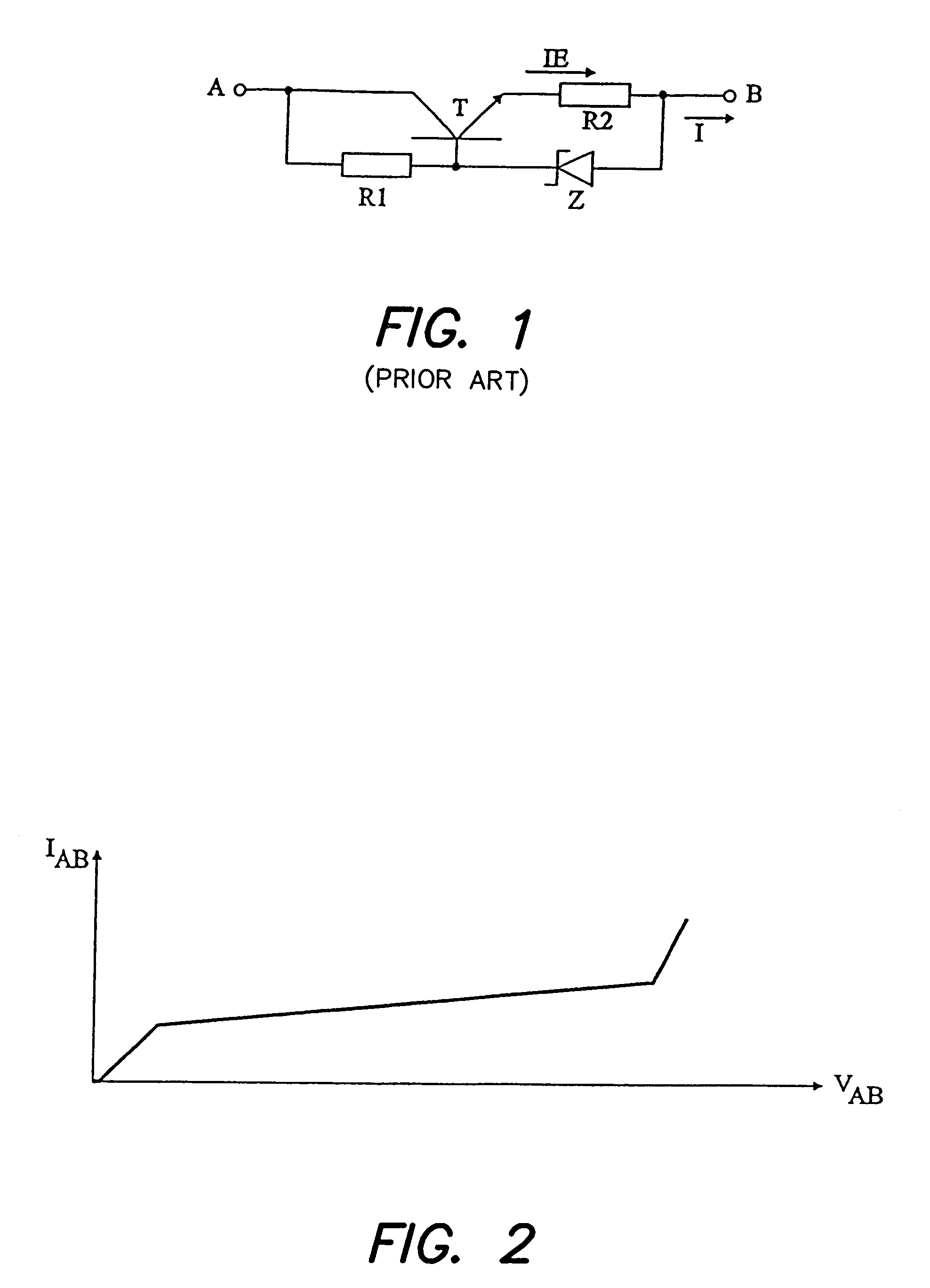

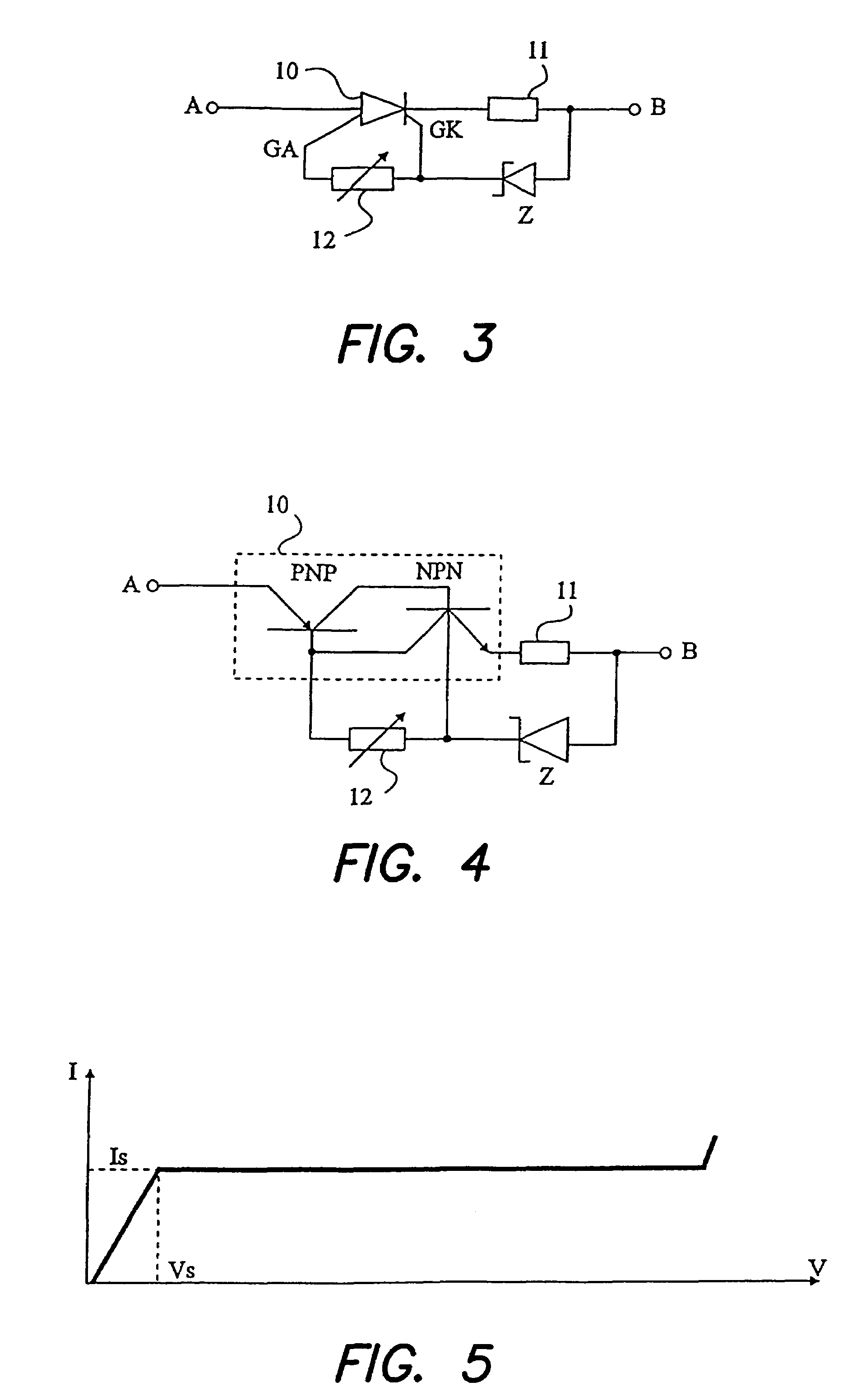

Constant current generator

InactiveUS7433166B1ThyristorEmergency protective arrangement detailsGate turn-off thyristorCurrent limiting

A constant current generator connected between first and second terminals includes a gate turn-off thyristor in series with a resistor; a current limiting component connected between the anode gate and the cathode gate of the thyristor; and a voltage reference connected between the cathode and the cathode gate of the thyristor.

Owner:STMICROELECTRONICS SRL

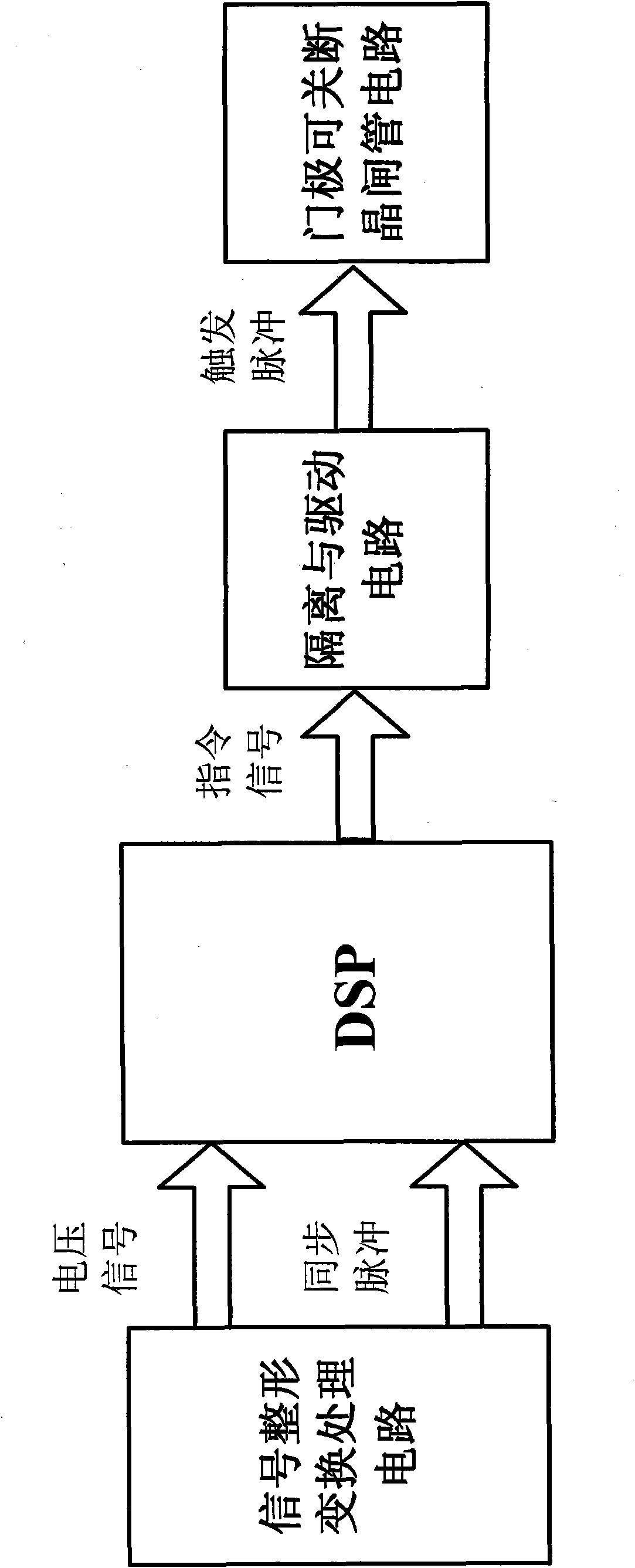

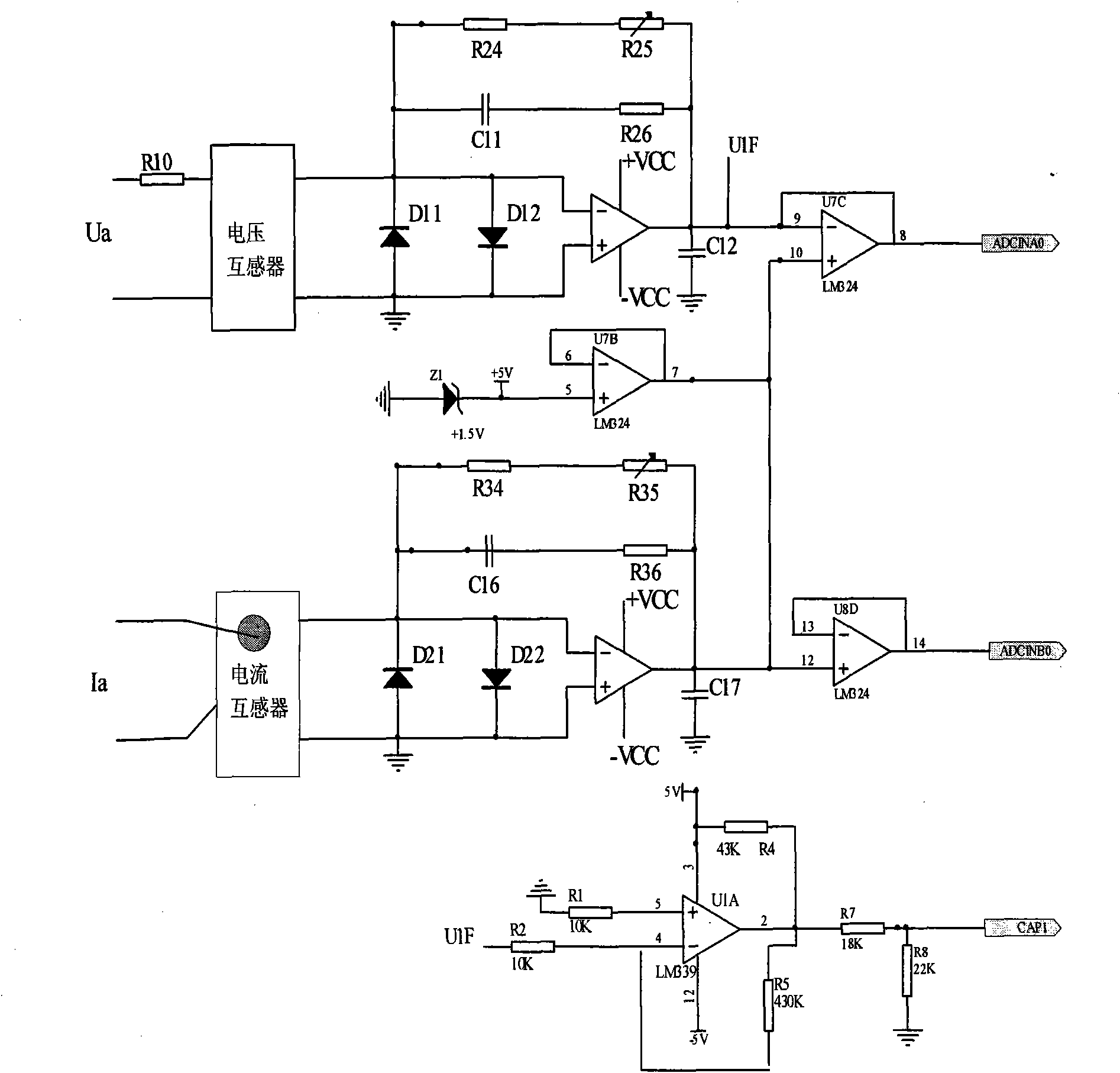

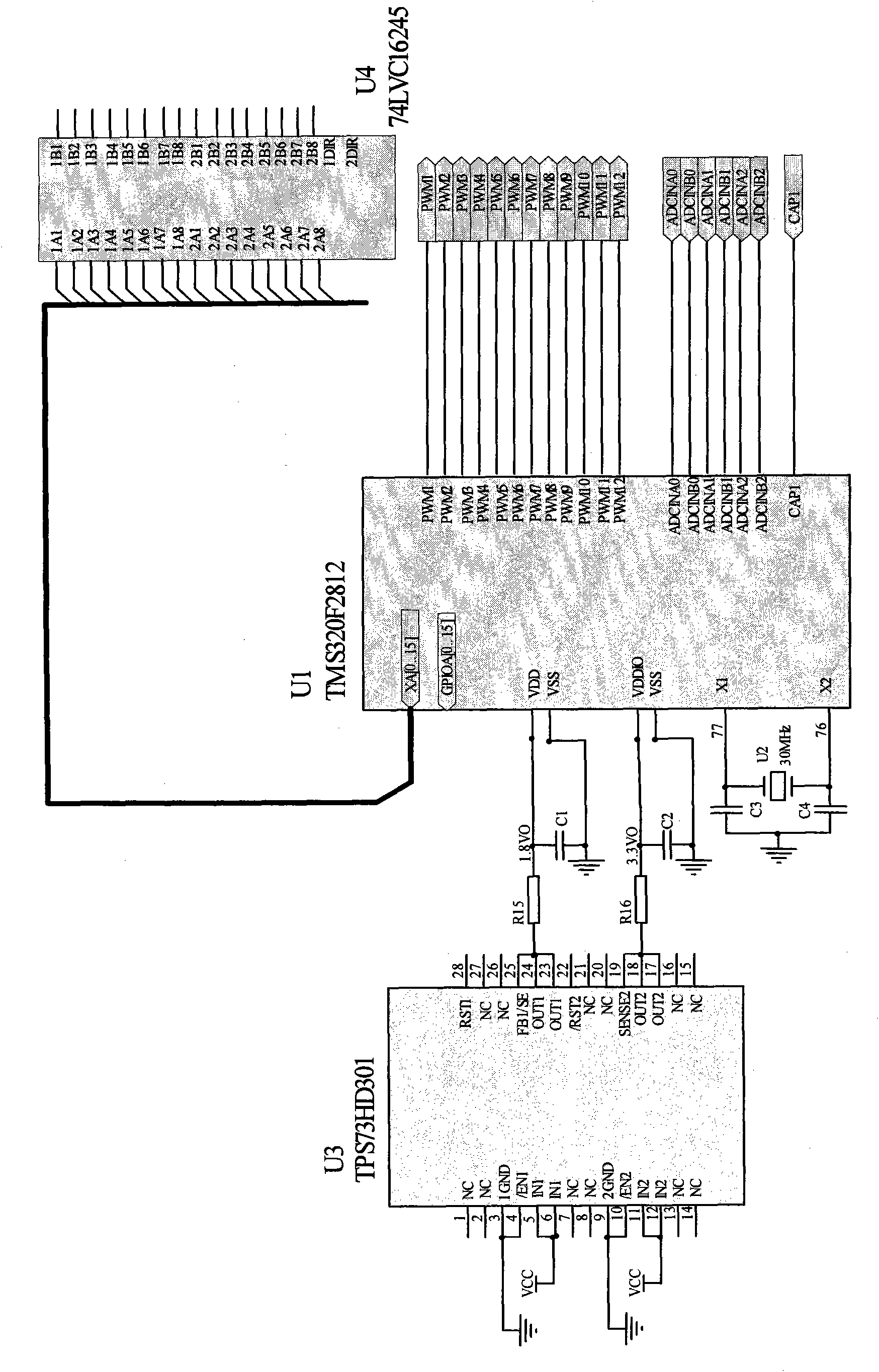

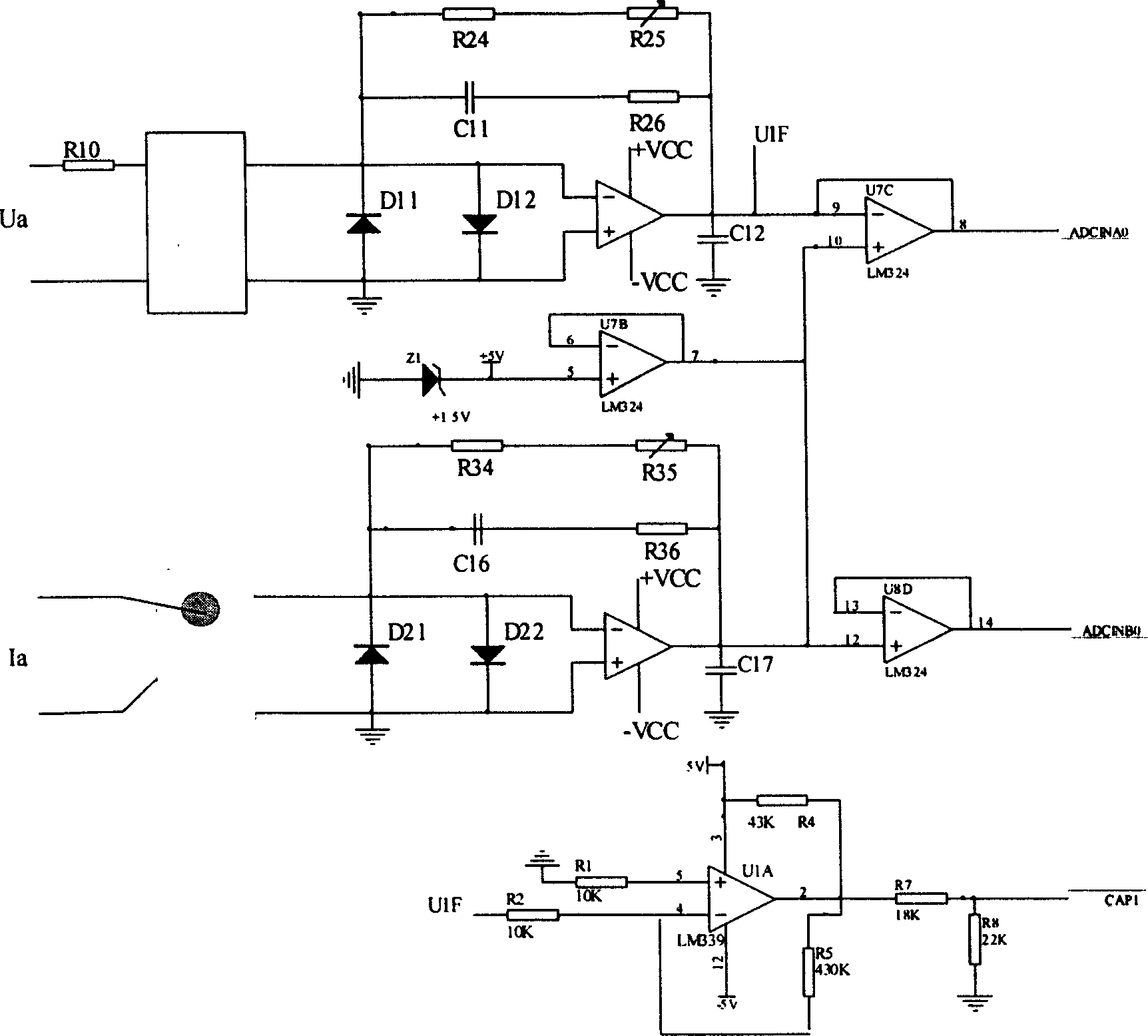

DSP (Digital Signal Processor) based improved instantaneous detection and control system of cascaded active power filter

InactiveCN101964529AEasy to adjustImprove reliabilityActive power filteringHarmonic reduction arrangementDigital signal processingHarmonic pollution

The invention relates to a DSP (Digital Signal Processor) based improved instantaneous detection and control system of a cascaded active power filter. The system comprises a signal shaping and transformation processing circuit, a central data processing circuit, an insulating and driving circuit and a gate turn off thyristor circuit. The system proposes an improved instantaneous detection method based on a dq transformational theory, and fundamental wave positive-sequence components of voltage and current are synchronously extracted through dq transformation; and through coordinate transformation and projection, a current fundamental wave positive-sequence active component is obtained, and three-phase voltage distortion and fundamental wave positive-sequence active current while asymmetry can be detected in real time. In the invention, a high-performance digital signal processing chip is utilized to control a cascaded multi-level active power compensator, thereby the control speed and precision are greatly improved, the device capacity and the voltage class are improved, the stability of the grid is enhanced, and the influence on the running of whole system due to harmonic pollution is avoided.

Owner:TIANJIN UNIVERSITY OF TECHNOLOGY

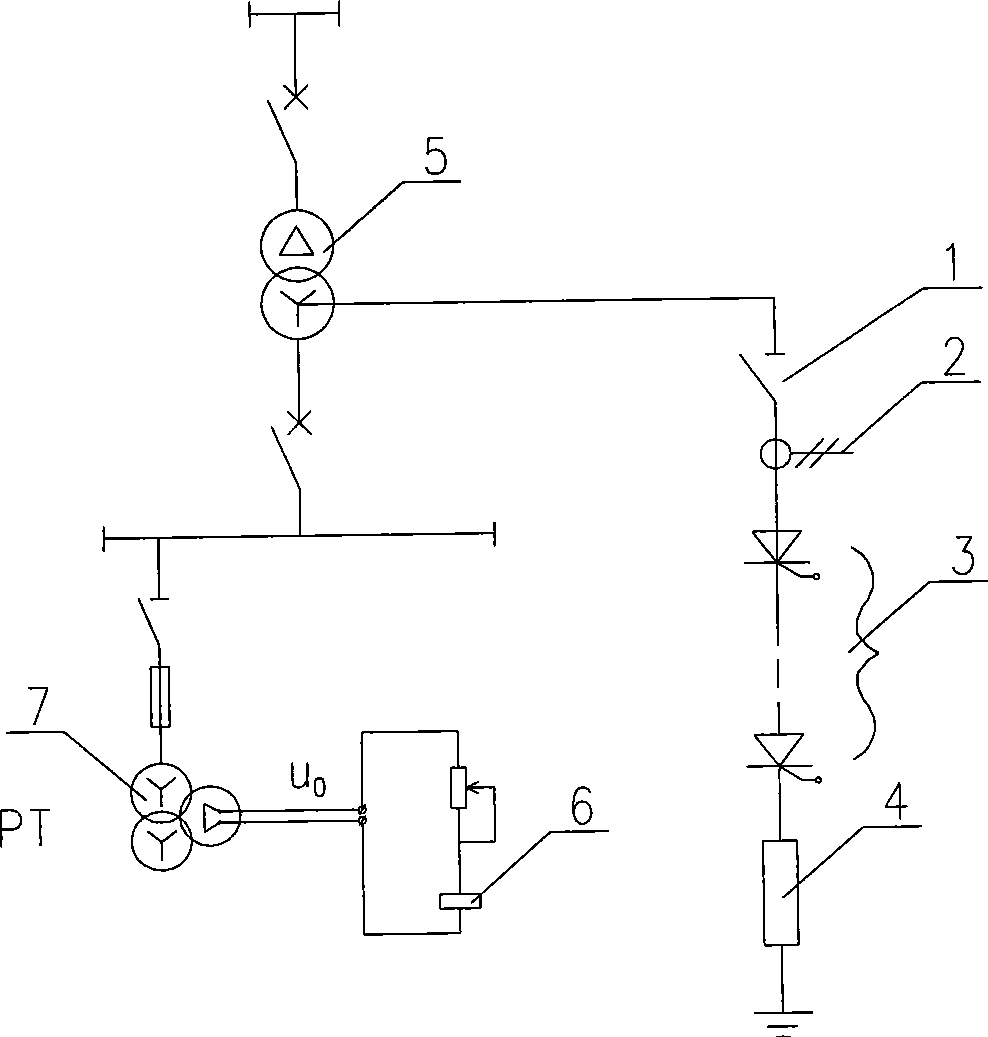

Resistance-grounded system

InactiveCN101378192AOvercome shortcomingsImprove reliabilityEmergency protective arrangements for limiting excess voltage/currentAutomatic controlEngineering

The invention belongs to the technical field of electricity, discloses a resistance grounding system, and particularly relates to an automatic control resistance grounding system. One end of a neutral-point isolating switch is connected with one end of a neutral-point current transformer, the other end of the neutral-point isolating switch is connected with one end of a power transformer, the other end of the neutral-point current transformer is connected with one end of a thyristor which can be opened and closed, the other end of the thyristor which can be closed is connected with a neutral-point grounding resistance, the other end of the power transformer is connected with a voltage transformer, and two triangle ends of a secondary opening of the voltage transformer is connected with the relay for controlling the opening and closing of the neutral-point thyristor. The automatic control resistance grounding system improves the reliability of medium-voltage power distribution, prevents the occurrence of cable fires, and can be widely applied in 3 to 35kV industrial enterprises and city network power distribution systems.

Owner:CISDI ENG CO LTD

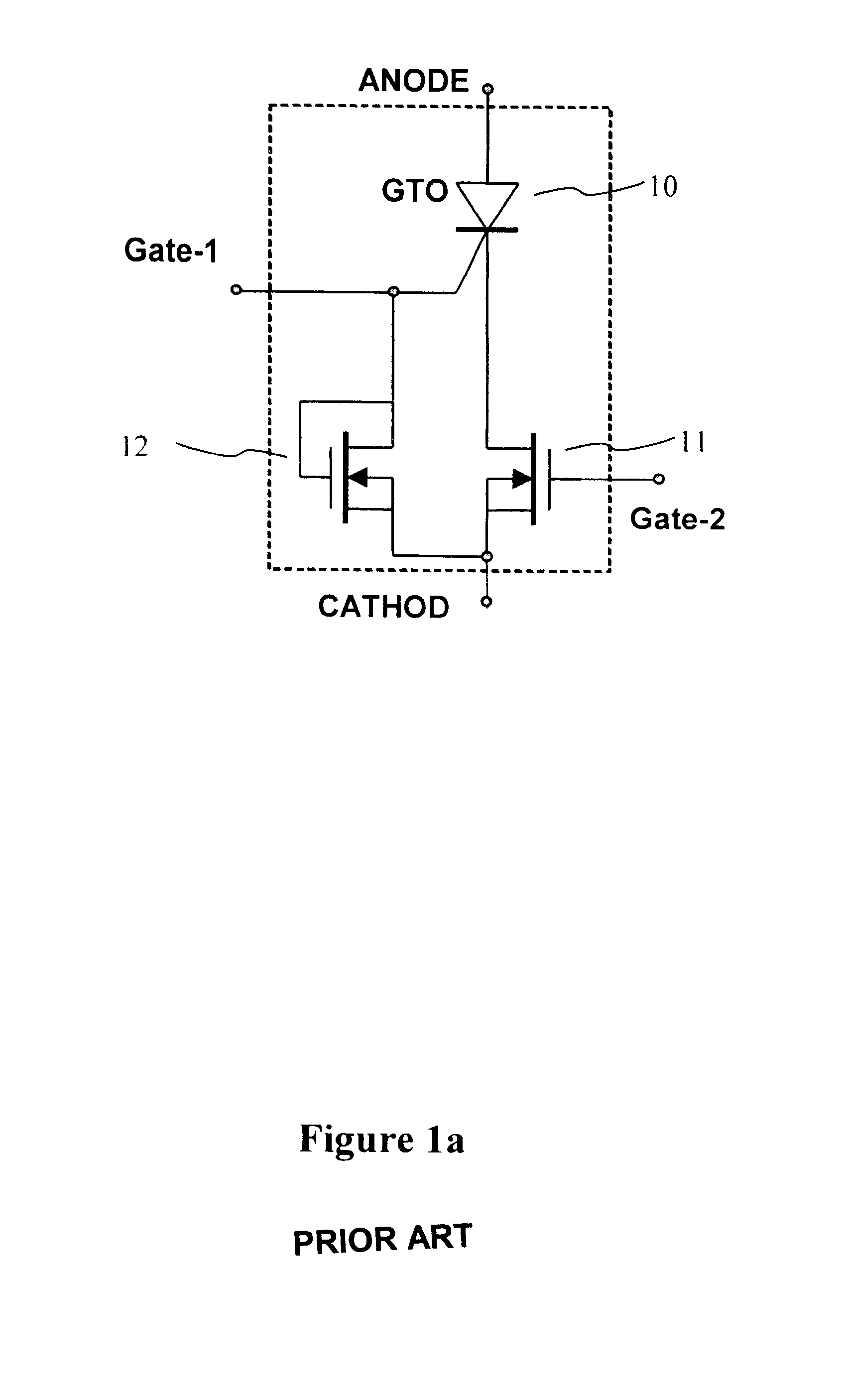

Emitter turn-off thyristors and their drive circuits

InactiveUS20030168671A1Save energyImprove reliabilityTransistorThyristorGate turn-off thyristorEmitter turn off thyristor

A family of emitter turn-off thyristors compres a gate turn-on (GTO) thyristor, a first switch, the drain of the first switch being connected to the cathode of the GTO thyristor, and a second switch connected between the gate of the GTO thyristor and the source of the first switch. The first switch consists of a number of paralleled metal oxide semiconductor field effect transistors (MOSFETs). The anode of the GTO thyristor and the source of the first switch serve as the annode and the cathode, respective, of the emitter turn-off thyristor. The emitter turn-off thyristor has four control electrodes; the gate of the GTO thyristor, the control electrode of the second switch, the gate of the first switch, and the cathode of the GTO thyristor.

Owner:VIRGINIA TECH INTPROP INC

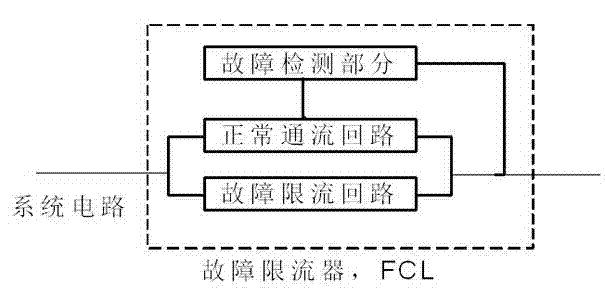

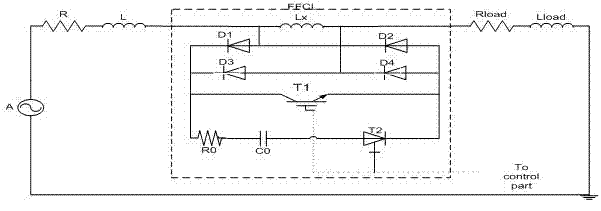

SSCB-based coal mine power grid fast fault current limiter

InactiveCN104852348AReduce short circuit current levelsGuaranteed normal opening and closingArrangements responsive to excess currentCapacitanceDiode bridge rectifier

Owner:HENAN POLYTECHNIC UNIV

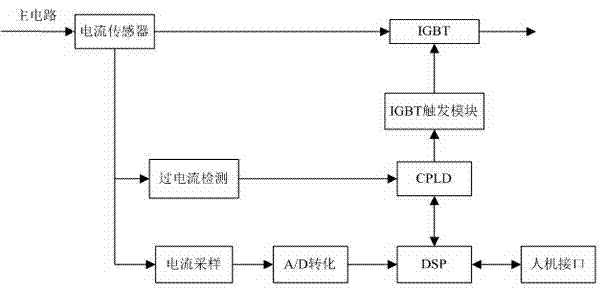

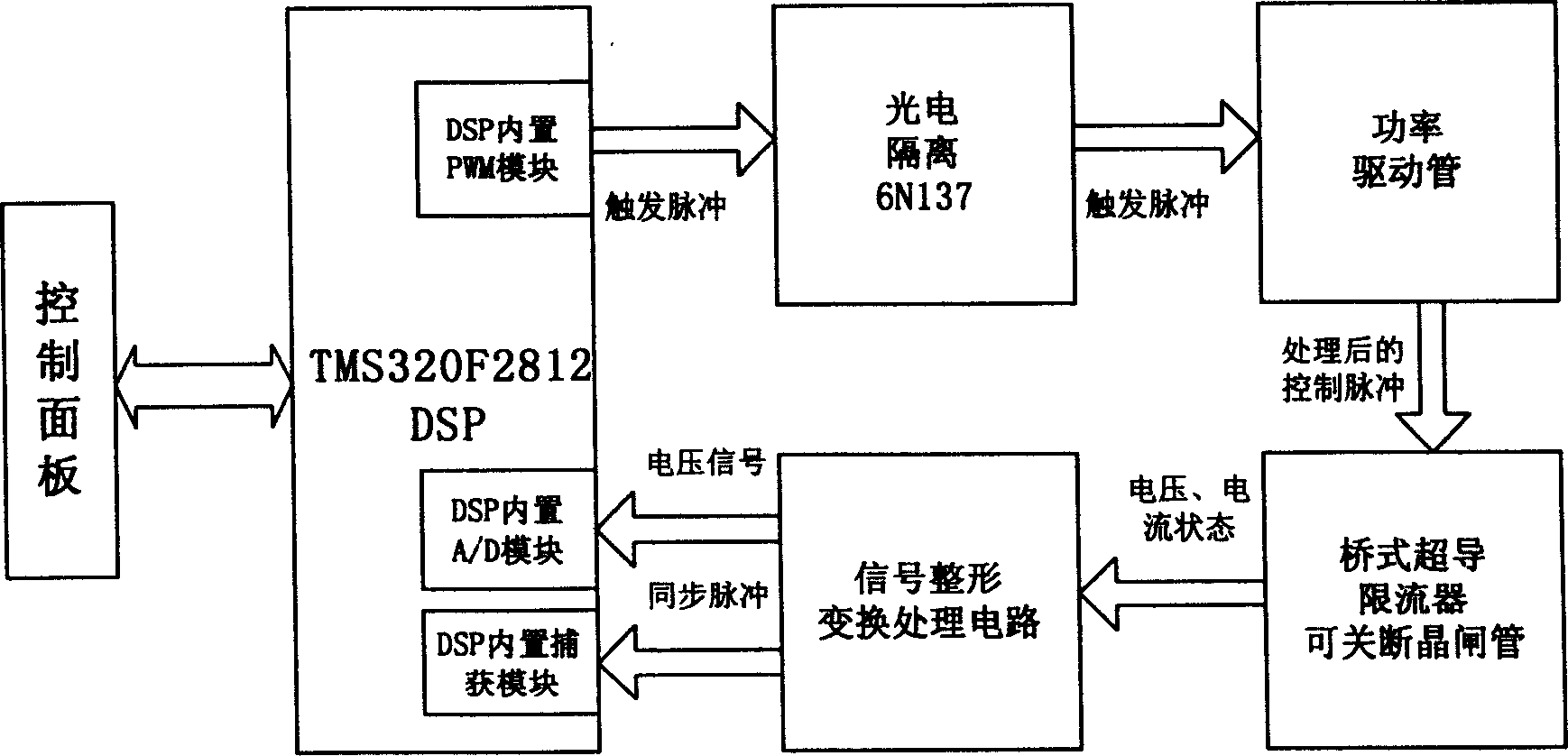

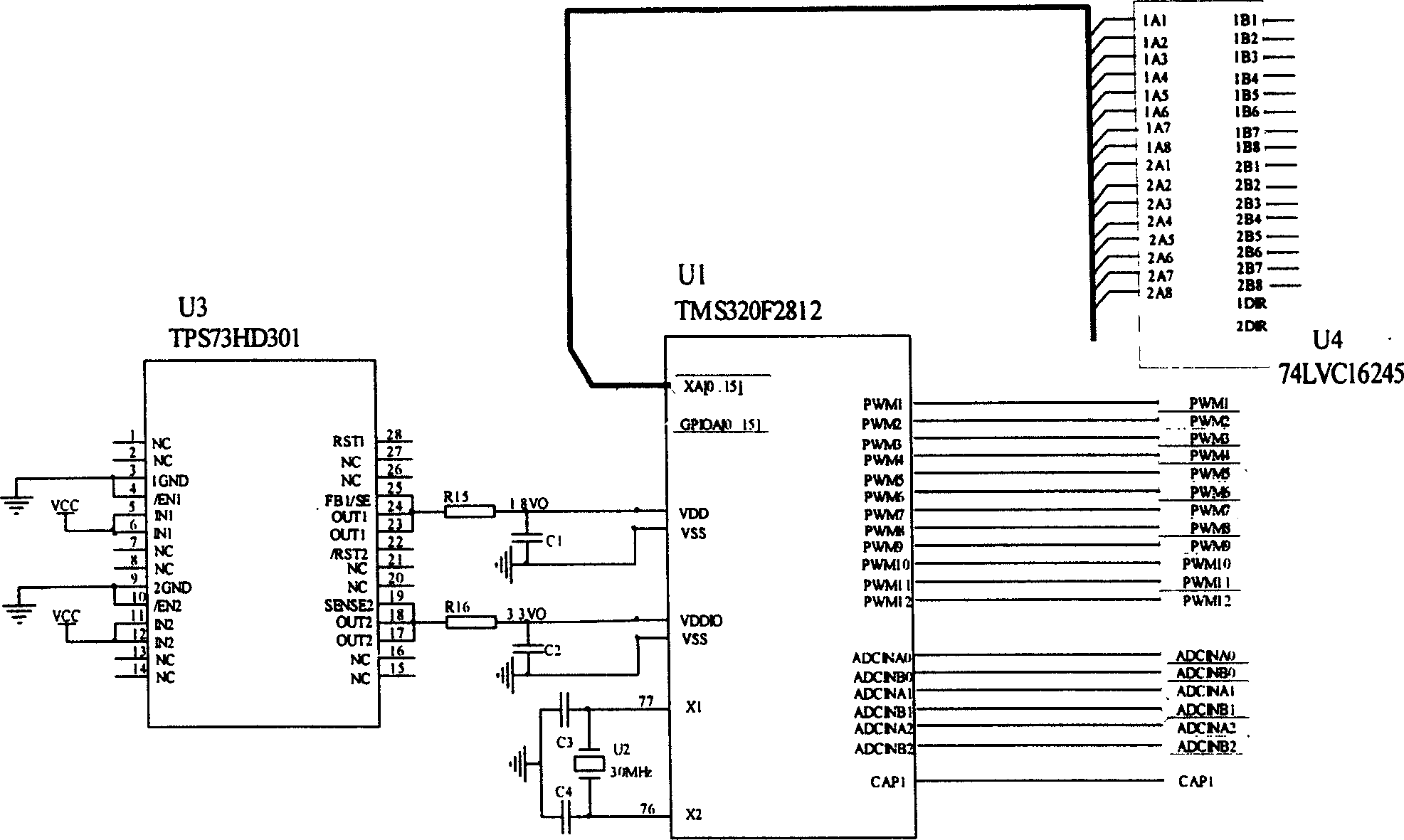

Bridge superconducting current limitter control system based on DSP

InactiveCN1599183AGive full play to high-speed data computing capabilitiesImprove stabilityArrangements responsive to excess currentEmergency protective arrangements for limiting excess voltage/currentElectronic switchClosed loop

The invention relates to a control system of the bridge type superconducting current limiter bases on the DSP. It treats the circuit through the signal reshaping transformation to collect the electrical signals, send the signal to the power driving tube circuit after being treated by the central data processing circuit, then control the gate-controlled switch element circuit of the bridge type superconducting current limiter and reach the aim to controll the system. The advantages and the technological effects of the invention lie in the following aspects: adopting the DSP to form the control system, simple hardware circuit, highly precise real time control, increased stability and reliability of the system. Appling the DSP to the bridge type superconducting current limiter and carrying out the closed loop control to the electronic switch composed of the GTO and other parts can reduce the loss caused by the short circuit of the electric power.

Owner:TIANJIN UNIVERSITY OF TECHNOLOGY

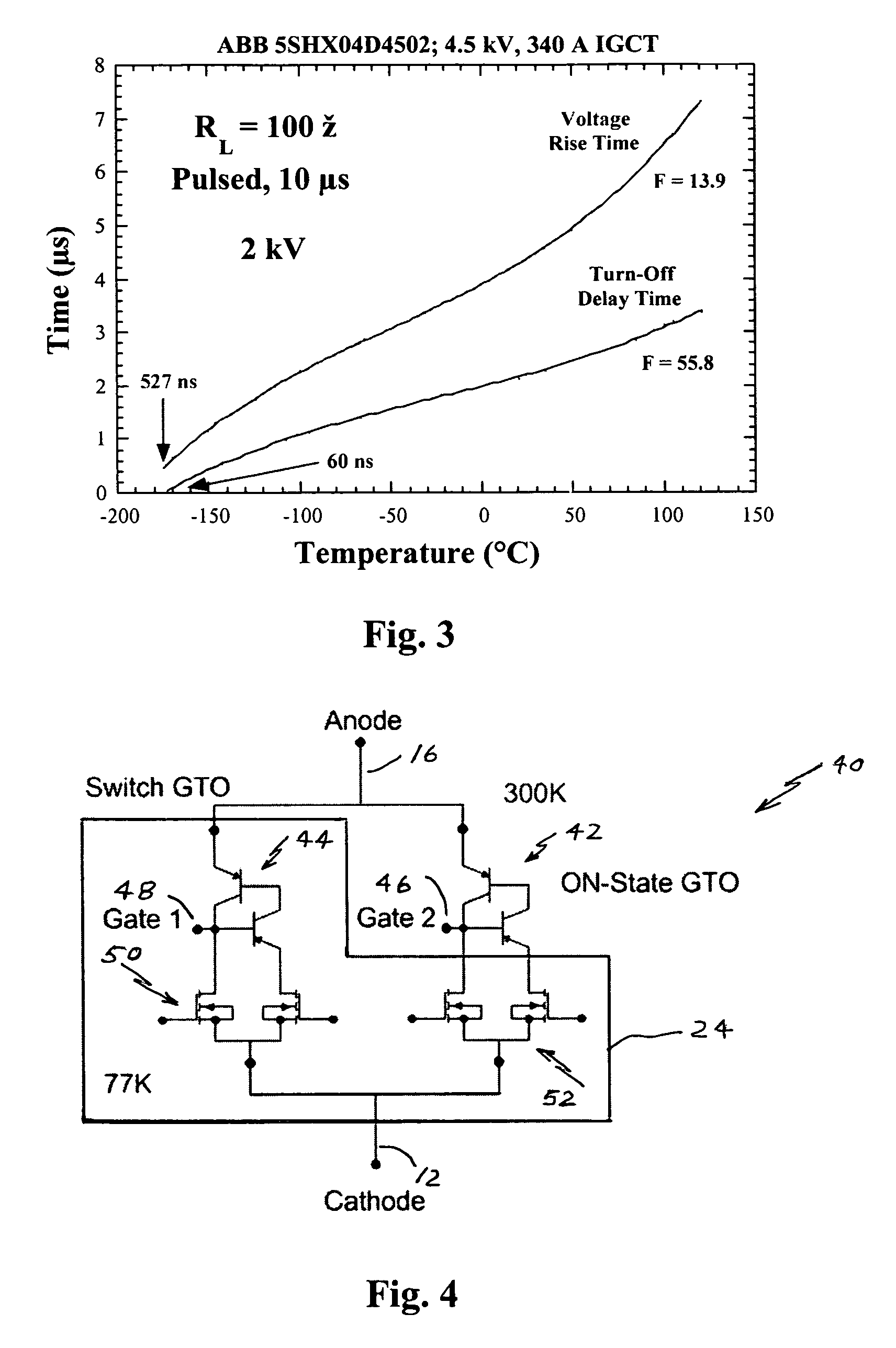

Efficient thyristor-type power switches

InactiveUS7352233B1Increased switching lossesFast switching speedElectronic switchingGate turn-off thyristorEmitter turn off thyristor

The highest-power switches now available are based on thyristor-type devices: GTOs (Gate turn-off thyristors), MTOs (MOS controlled turn-off thyristors), IGCTs (Integrated gate commutated thyristors), and the new ETOs (Emitter turn-off thyristors). These devices handle kilovolts and kiloamperes for megawatt inverters / converters. Measurements by the inventors show that conduction losses of MOSFETs and switching losses of IGCTs are drastically decreased by cryo-cooling. IGCTs, ETOs, and MTOs, together with many small, low voltage MOSFETs for gate and emitter turn-off circuitry, are cryo-cooled to attain much higher switching speeds and a reduction in size, weight and cost of high-power (megawatt range) equipment.

Owner:MTECH LAB

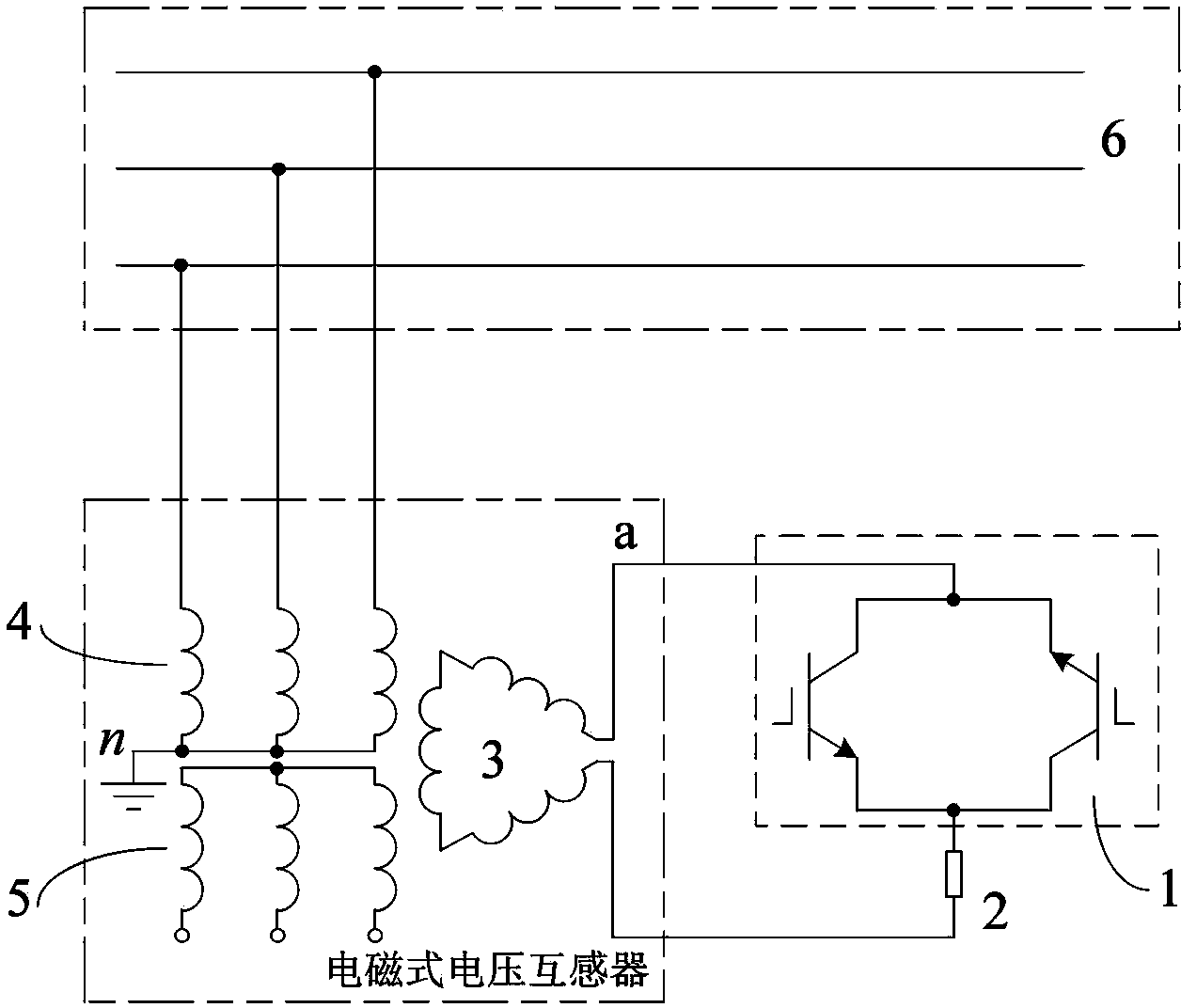

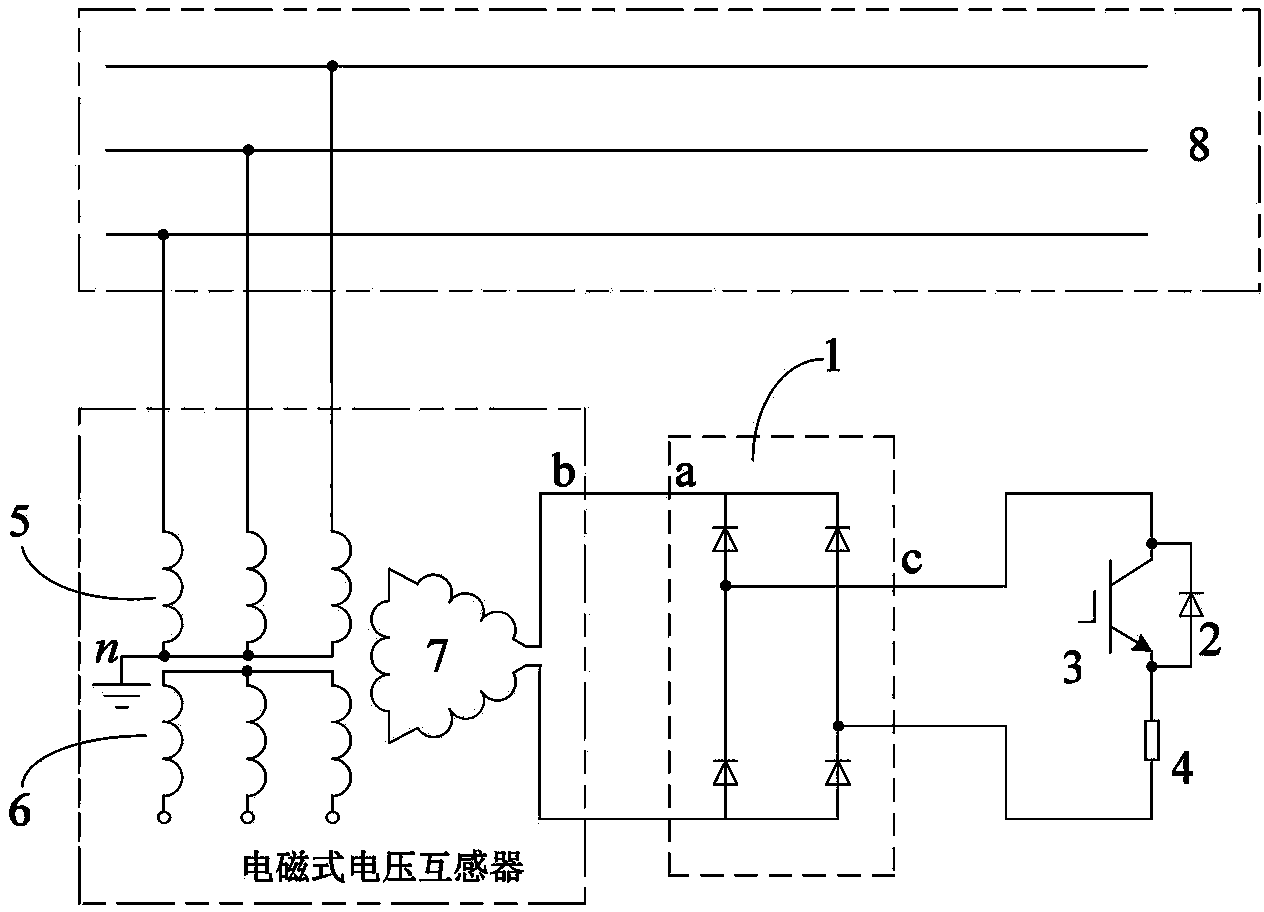

Secondary alternating-current resonance elimination device used for electromagnetic type voltage transformer

InactiveCN104377680AImprove stability and securitySimple structureEmergency protective arrangements for limiting excess voltage/currentOvervoltageTransformer

The invention discloses a secondary alternating-current resonance elimination device used for an electromagnetic type voltage transformer. The device comprises a fully-controlled switch unit (1) and a discharging resistor (2), and the fully-controlled switch unit (1) and the discharging resistor (2) are connected with the two ends of an open delta winding (3) of the electromagnetic type voltage transformer after being connected in series to form a circuit; the fully-controlled switch unit (1) is composed of two fully-controlled switch devices reversely connected in parallel; each fully-controlled switch device is one of an insulated gate bipolar transistor (IGBT), an integrated gate commutated thyristor (IGCT) and a gate turn-off thyristor (GTO). The secondary alternating-current resonance elimination device is simple in structure, can quickly and effectively suppress ferromagnetic resonance overvoltage generated by the electromagnetic type voltage transformer and does not influence normal and asymmetric operation modes of a system, and accordingly safety and stability of power system operation are effectively improved.

Owner:STATE GRID CORP OF CHINA +2

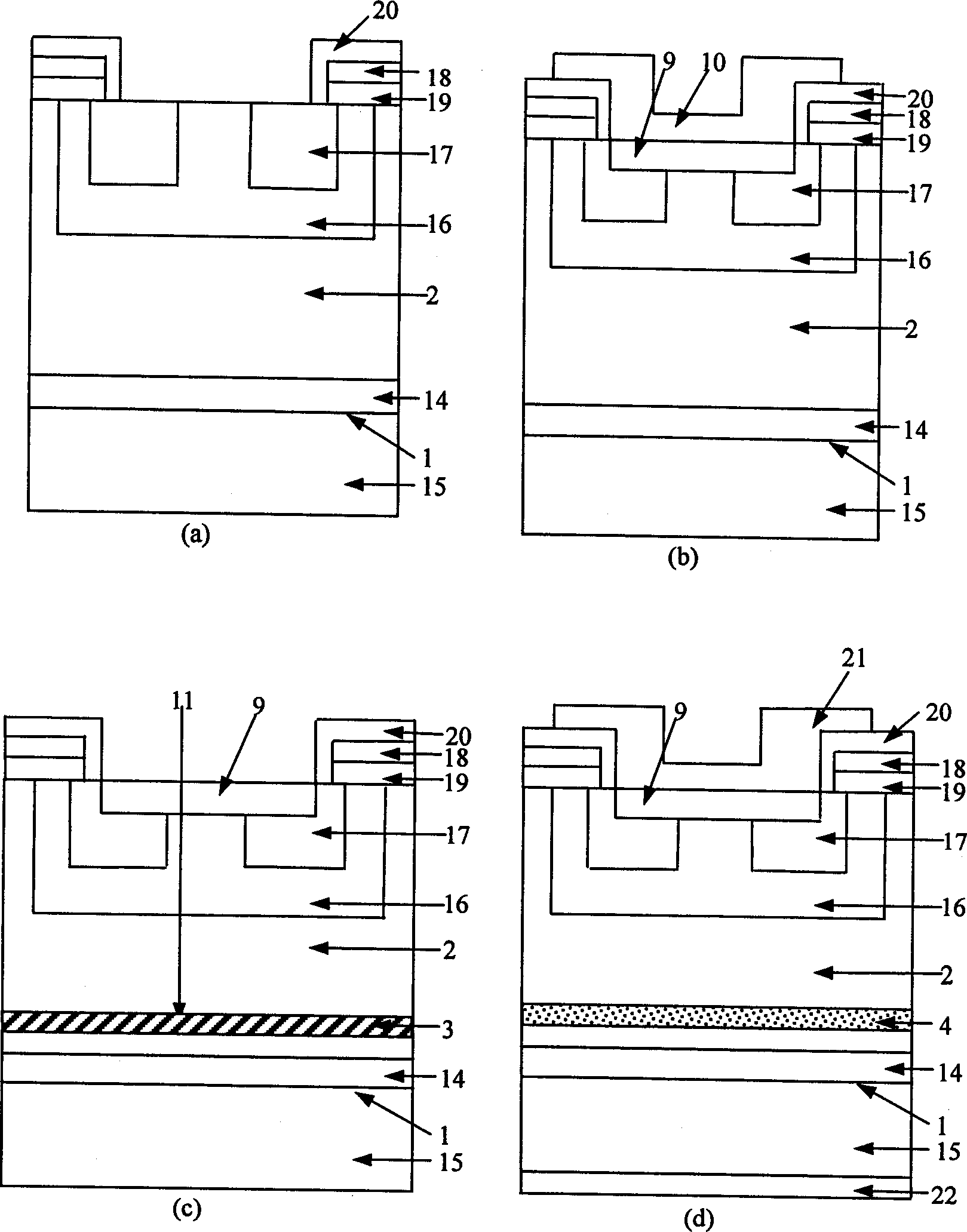

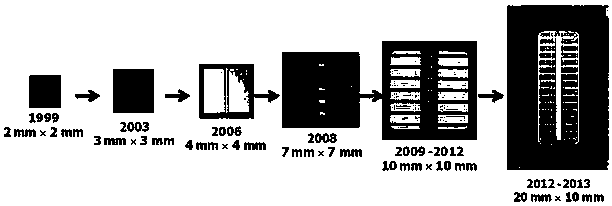

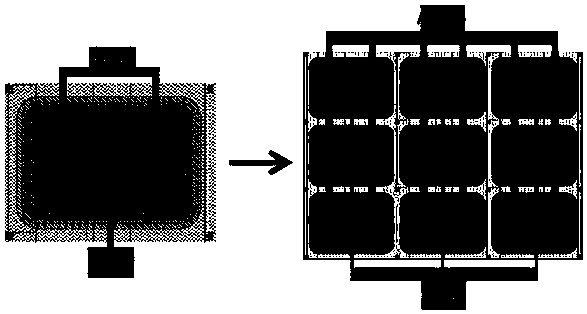

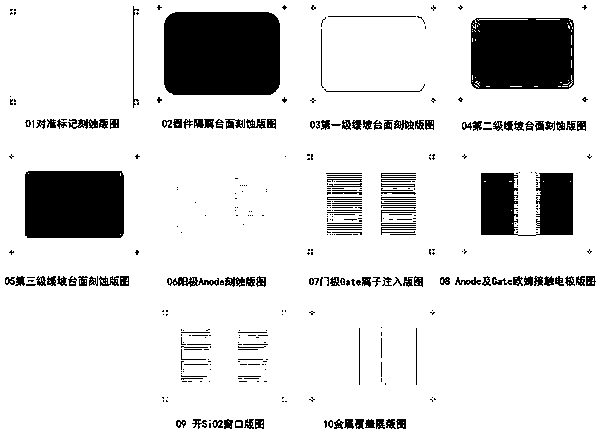

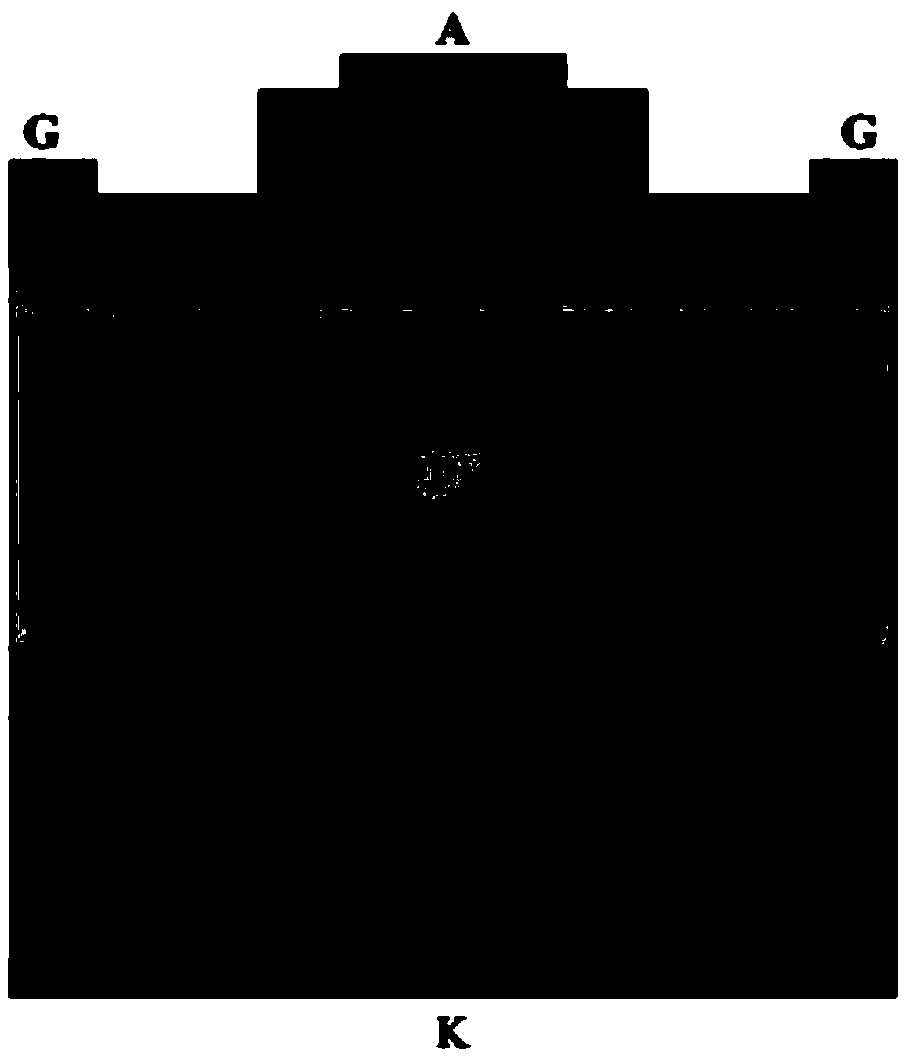

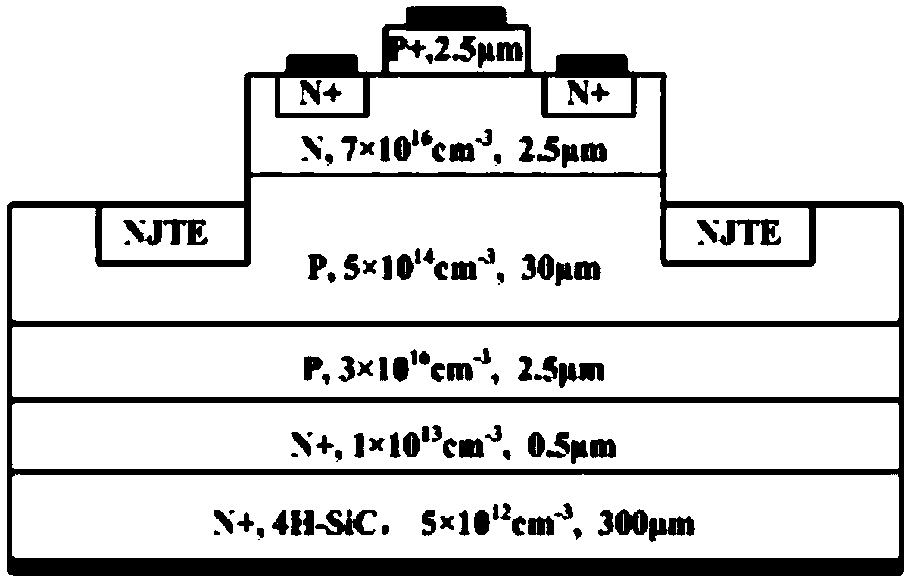

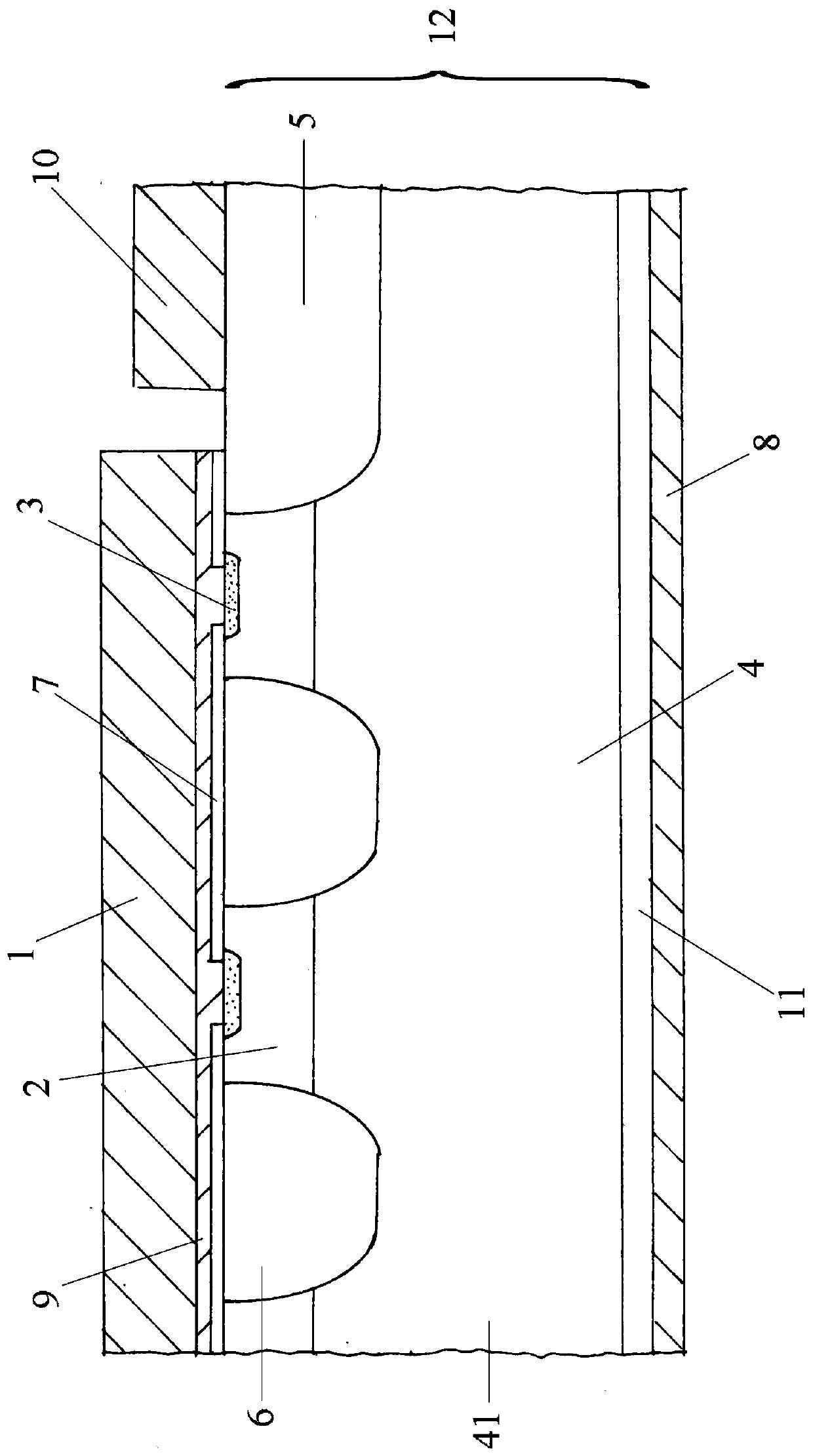

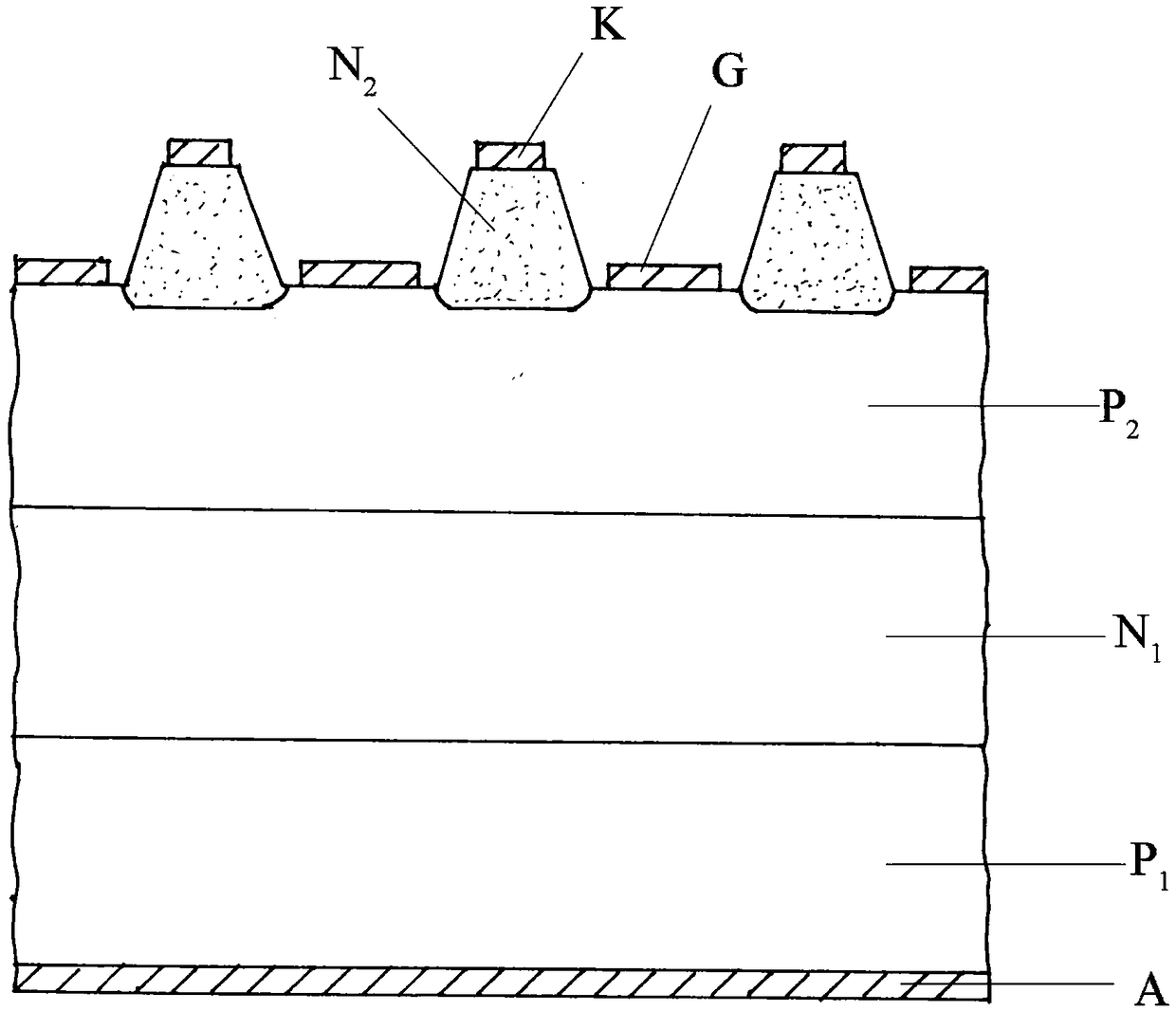

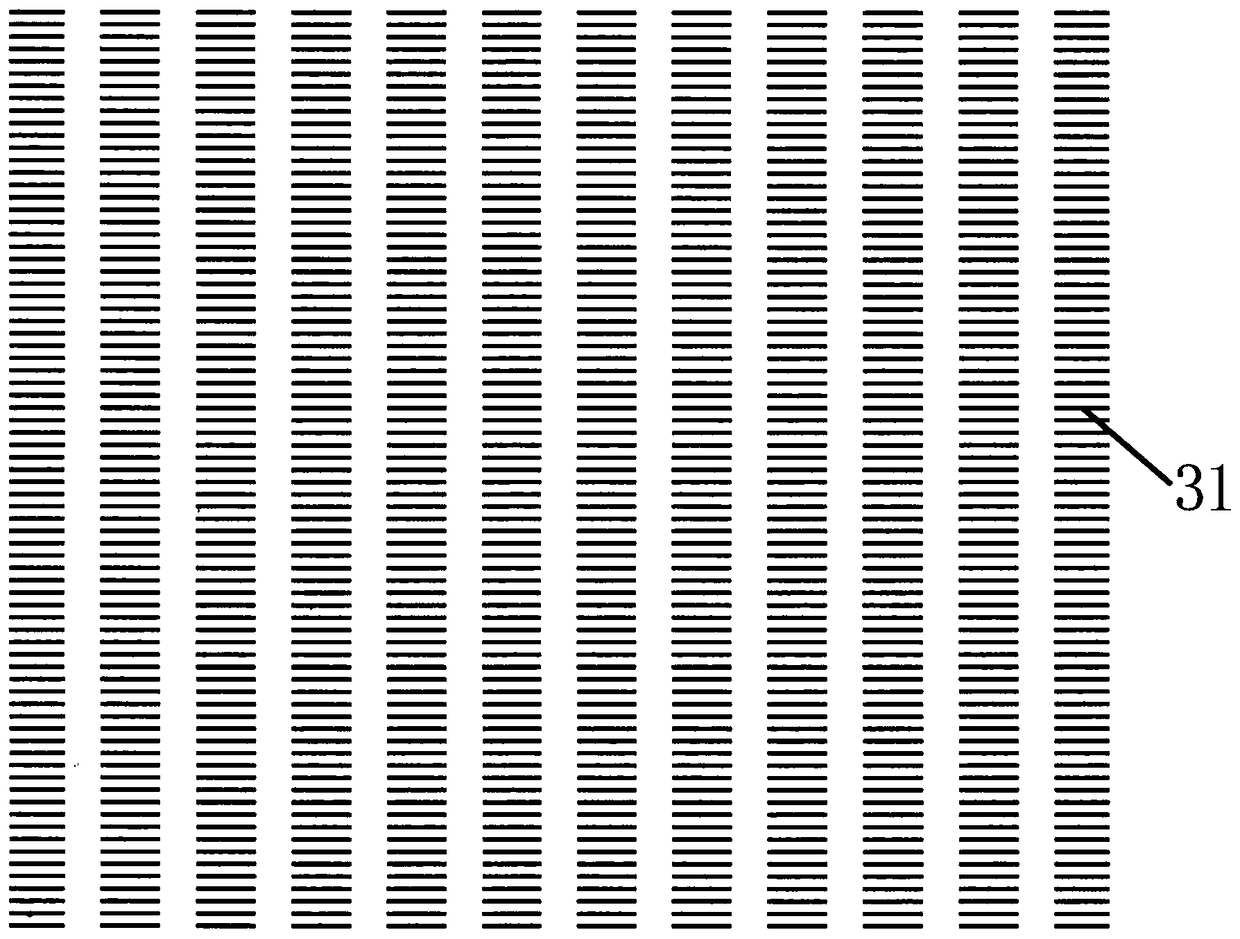

Device array of silicon carbide gate turn-off thyristor GTO and preparation method thereof

PendingCN108550572AIncrease the effective working areaSlow performanceSemiconductor/solid-state device detailsSolid-state devicesGate turn-off thyristorMachining

The invention provides a device array of a silicon carbide gate turn-off thyristor GTO and a preparation method thereof, wherein each single device is relatively small in size. The device array is formed by photoetching according to a corresponding photoetching layout and comprises at least two array structures of silicon carbide gate turn-off thyristors. The gate electrode of a GTO device unit islocated in the center of the table surface of the device unit. The gate electrode of the GTO device unit forms an interdigital structure together with anodes located on the two sides of the table surface of the device unit. A cathode is located on the back surface of the substrate of the device unit. During the packaging process, the gate electrodes of all device units are led down to a packagingstructure according to the layout design. Meanwhile, all anodes are led out in the opposite directions of the gate electrodes. According to the device array scheme adopted by the invention, the effective working area of a whole packaging chip can be remarkably improved. The condition that the performance of the whole packaging chip is reduced due to the defects of local materials can be avoided.Moreover, the process difficulty of device machining can be reduced, and the process stability and the process uniformity can be improved. The yield of prepared devices can be remarkably improved.

Owner:INST OF ELECTRONICS ENG CHINA ACAD OF ENG PHYSICS

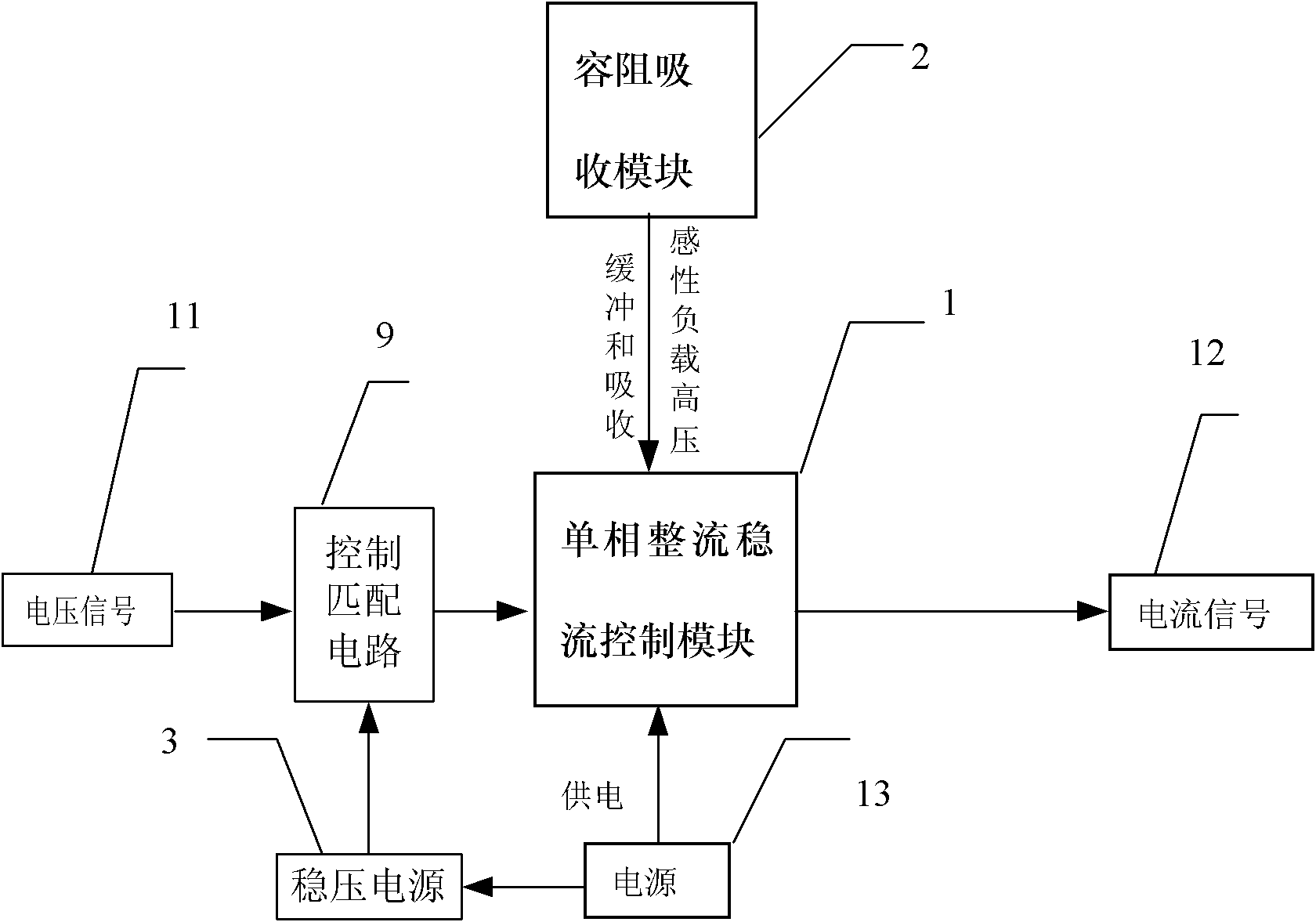

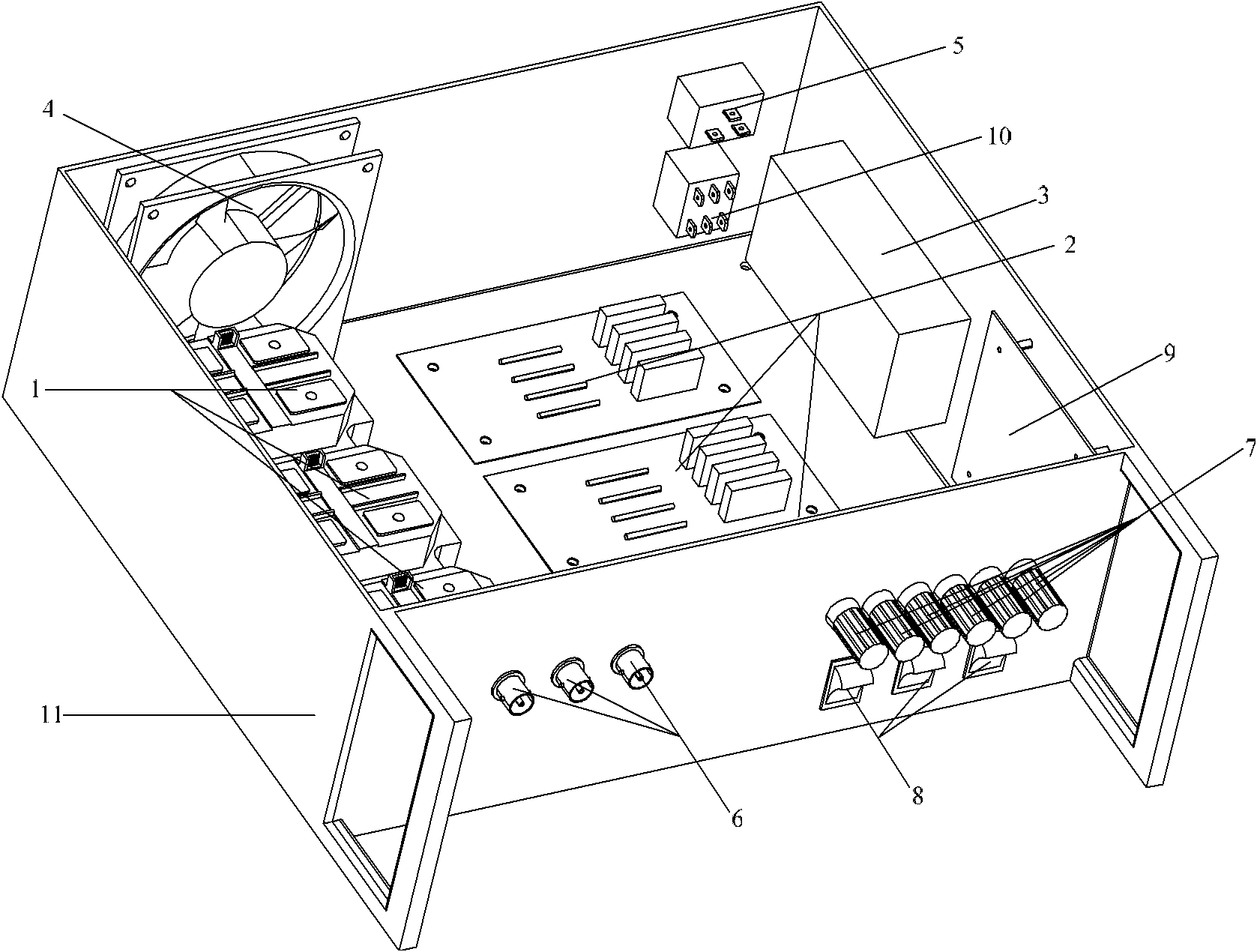

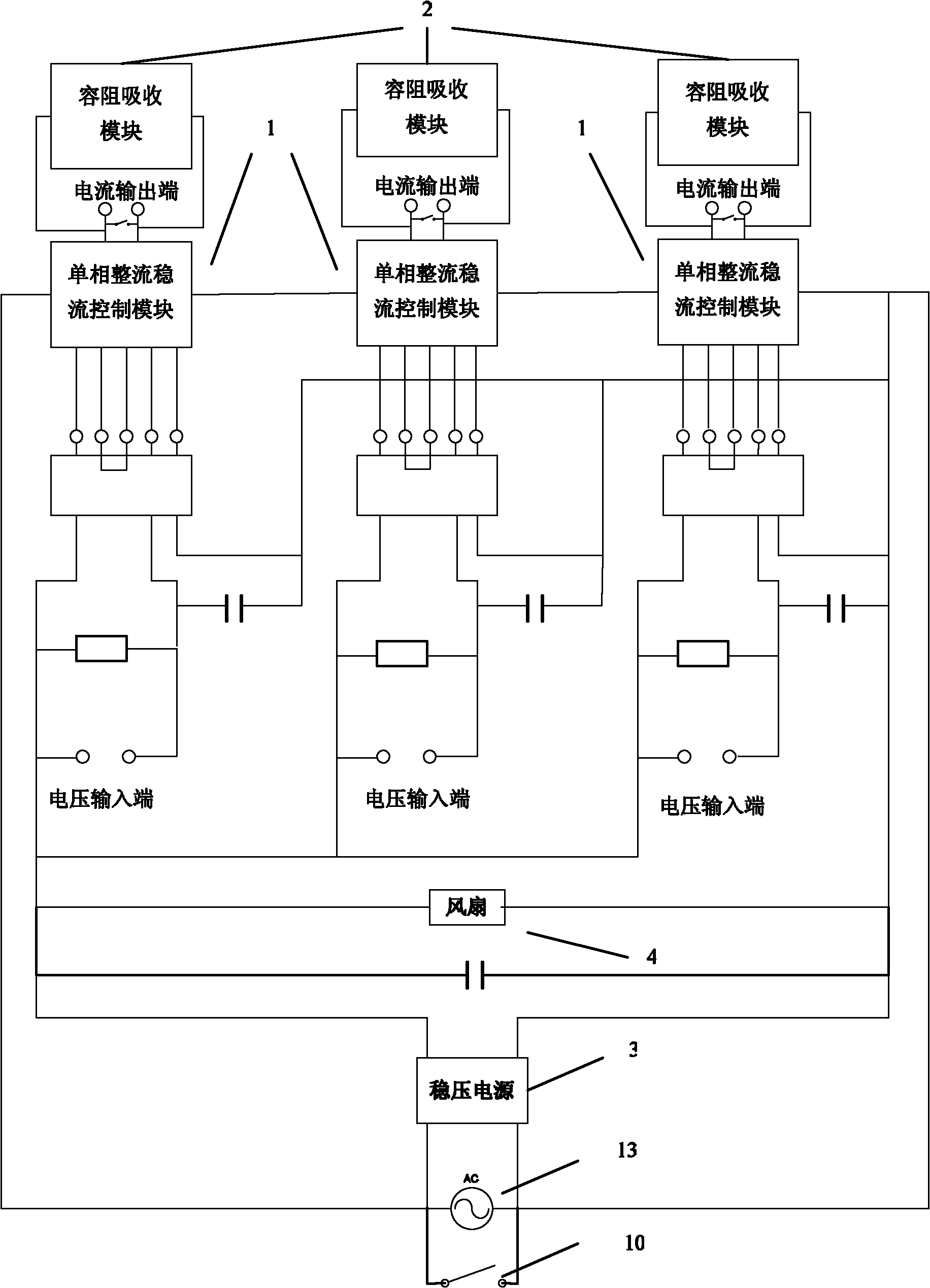

Active control drive power supply for shape memory alloy

InactiveCN102111079AReduce volumeIncrease output powerAc-dc conversionMachines/enginesCapacitanceCurrent sensor

The invention provides an active control drive power supply for a shape memory alloy. The drive power supply uses a closed loop control system consisting of a current stabilized regulating controller, a gate turn-off thyristor and a current sensor; the current which is output to the shape memory alloy is controlled via continuously sampling weak voltage signals which are output by a digital-modulus converting card at a computer end so that the voltage signals at the computer end are in one-to-one correspondence with the output current intensity. Each case of the drive power supply is provided with three passages which can simultaneously and independently drive three shape memory alloy wires; in order to enable the power supply to adapt to an inductive load, each passage is provided with a capacitance and resistance absorbing module to prevent the gate turn-off thyristor from being punctured by the high voltage generated by the inductive load. The shape memory alloy active control drive power supply is simple in structure, convenient and fast in use, high in drive power, convenient in operation and wide in regulating range.

Owner:BEIHANG UNIV

Secondary direct-current resonance elimination device used for electromagnetic type voltage transformer

InactiveCN104377679AImprove stability and securityFerroresonance is quickly eliminatedTransformersInductancesOvervoltageElectric power system

The invention discloses a secondary direct-current resonance elimination device used for an electromagnetic type voltage transformer. The device comprises a rectifier circuit, a fully-controlled switch device and a discharging resistor. The alternating-current side connection end of the rectifier circuit is connected with the connection end of an open delta winding of the electromagnetic type voltage transformer, and the direct-current side connection end of the rectifier circuit, the fully-controlled switch device and the discharging resistor are connected in series to form a circuit; the fully-controlled switch device is one of an insulated gate bipolar transistor (IGBT), an integrated gate commutated thyristor (IGCT) and a gate turn-off thyristor (GTO); the rectifier circuit is a single-phase uncontrolled rectifier bridge composed of four rectifier diodes. The secondary direct-current resonance elimination device can quickly and effectively suppress ferromagnetic resonance overvoltage generated by the electromagnetic type voltage transformer and does not influence normal and asymmetric operation modes of a system, and accordingly safety and stability of power system operation are effectively improved and the structure is simple.

Owner:STATE GRID CORP OF CHINA +2

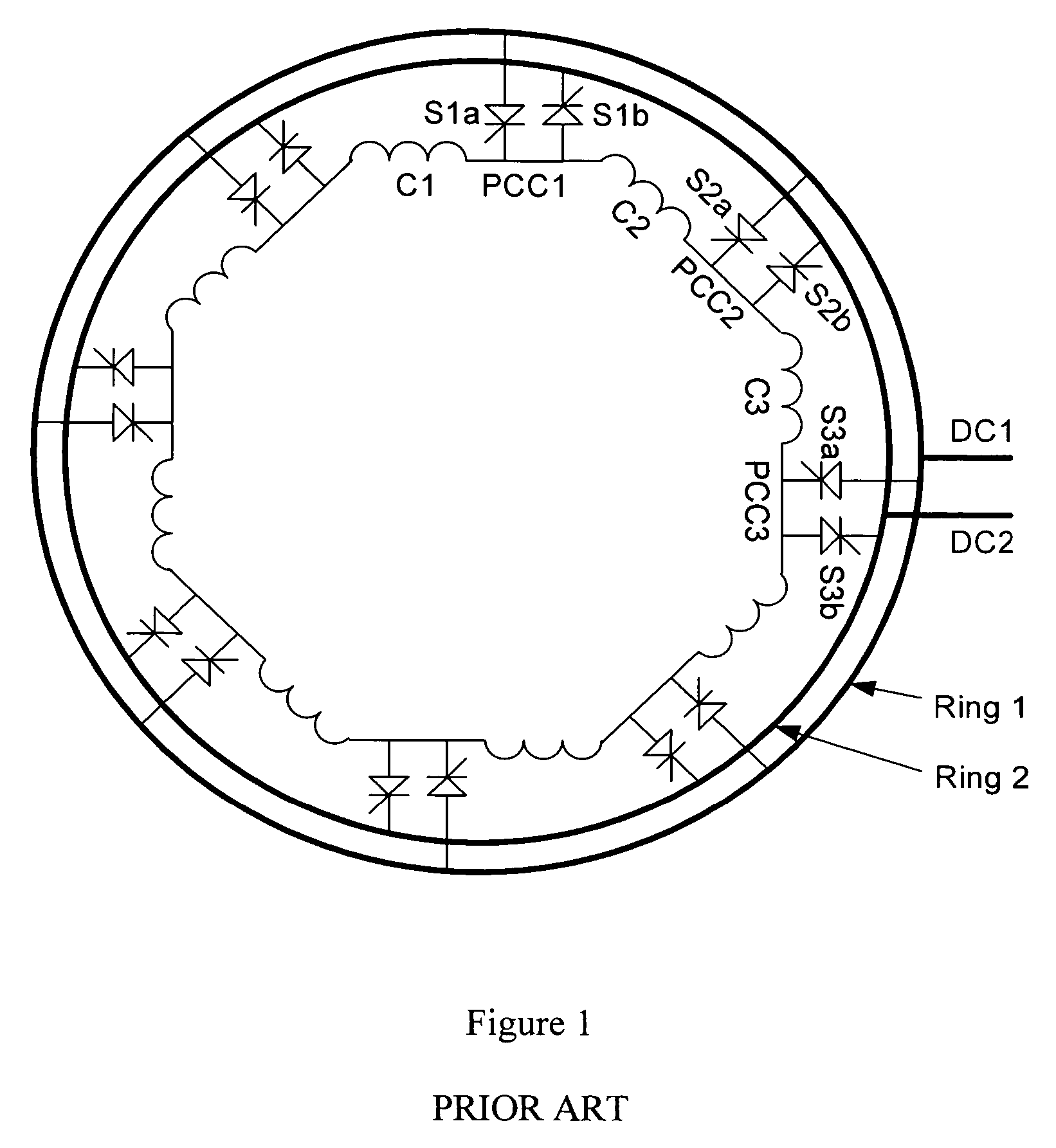

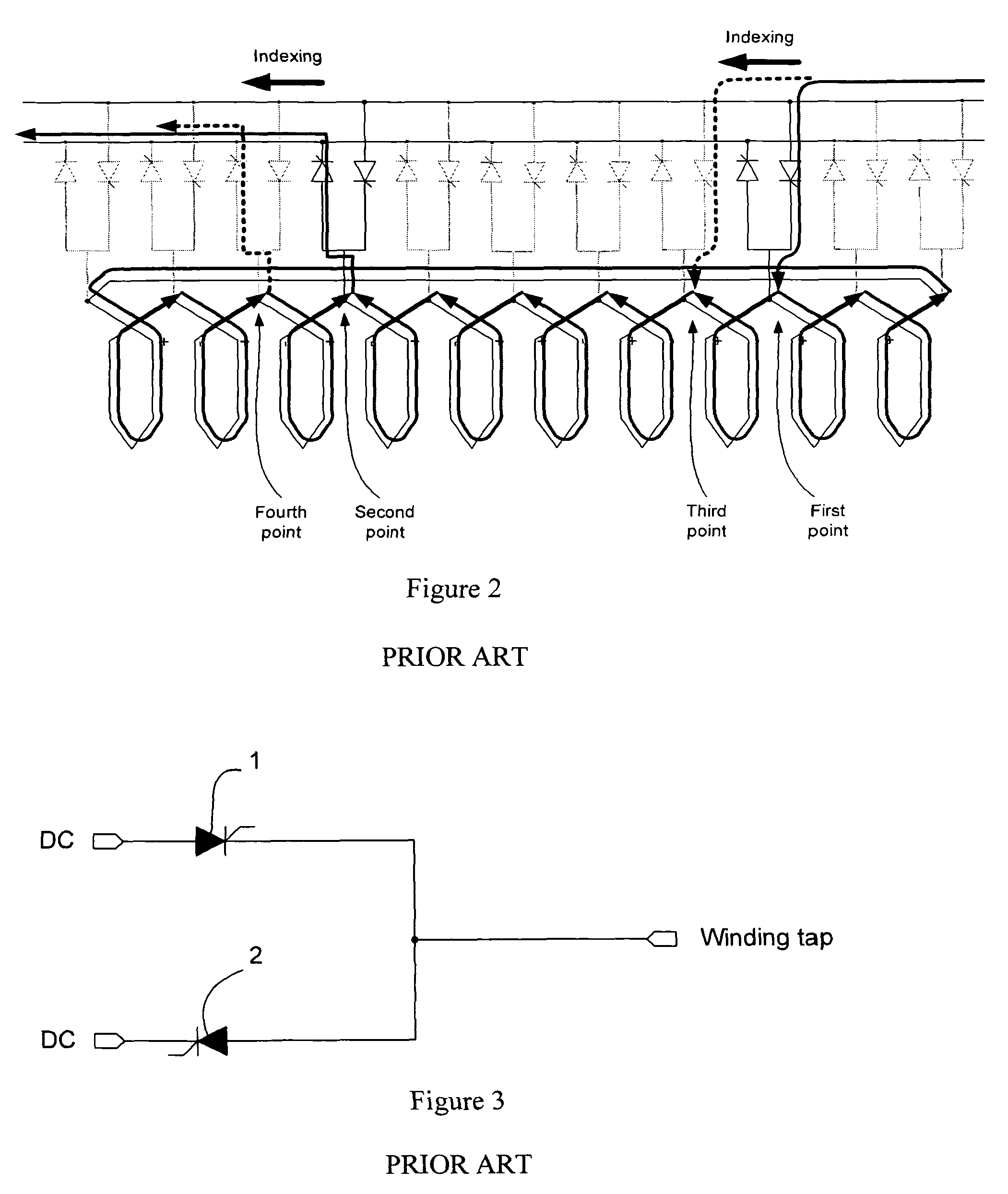

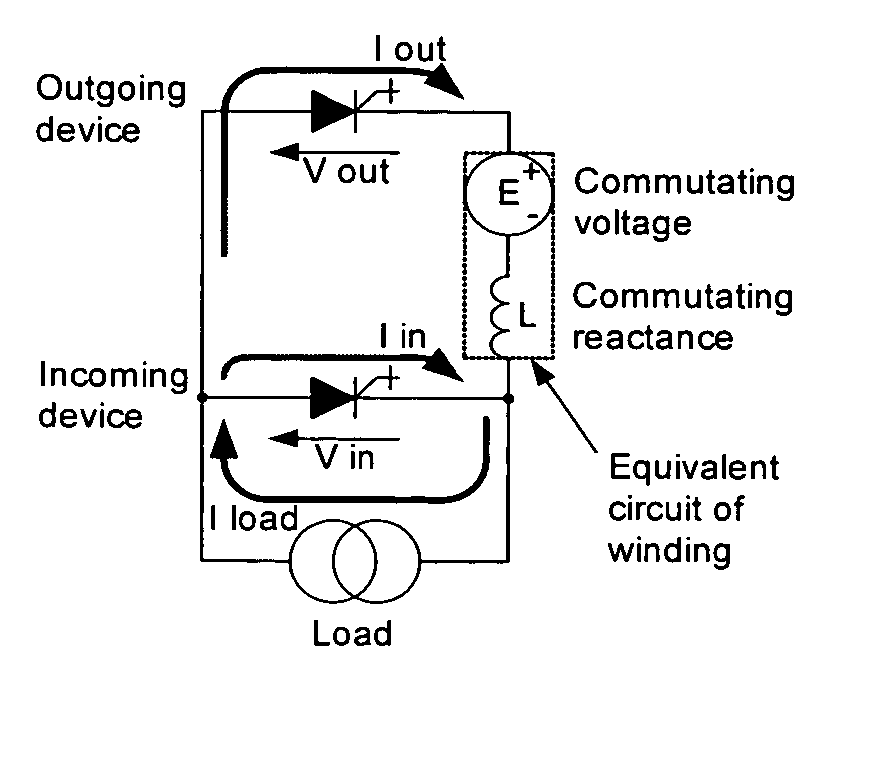

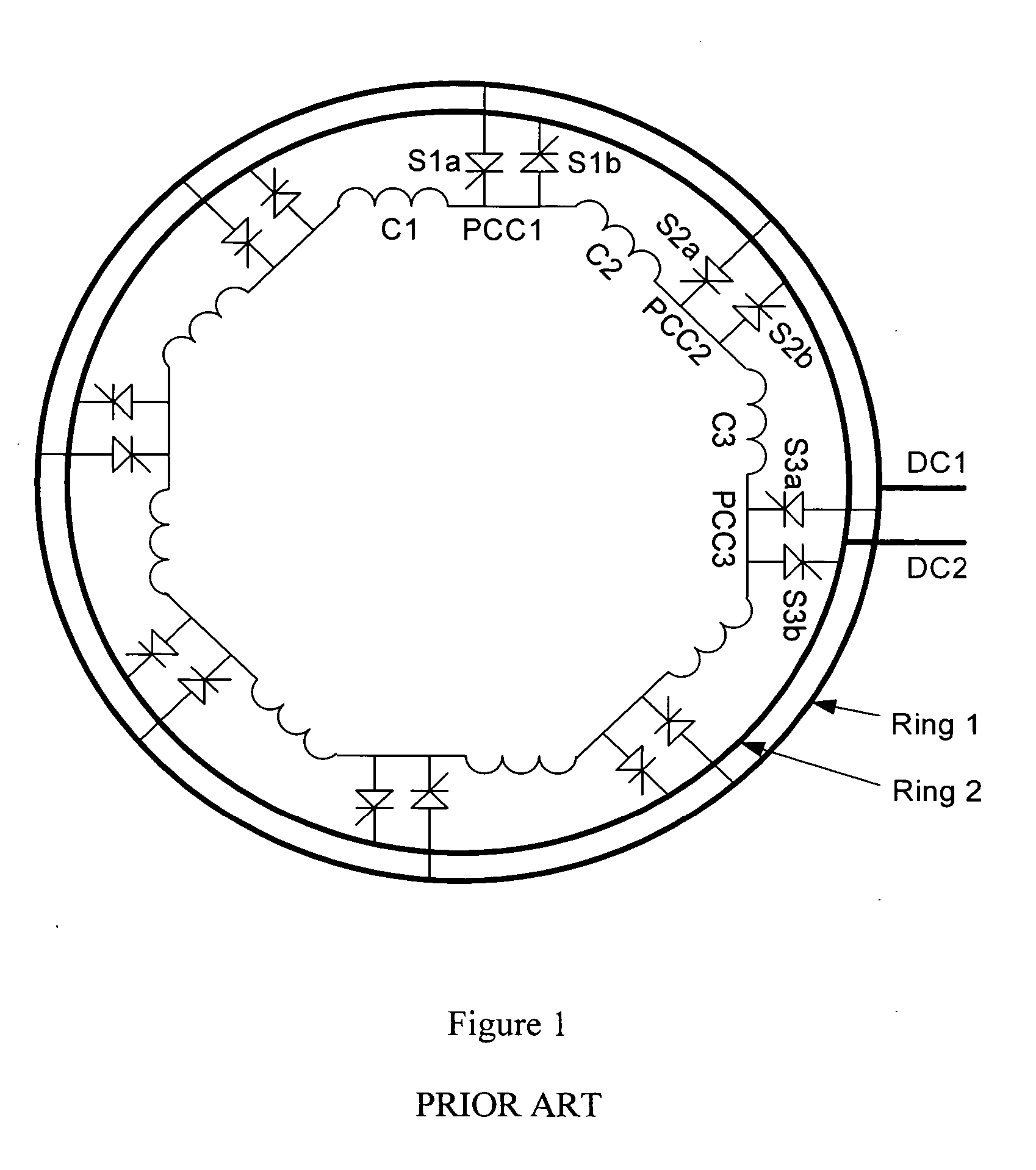

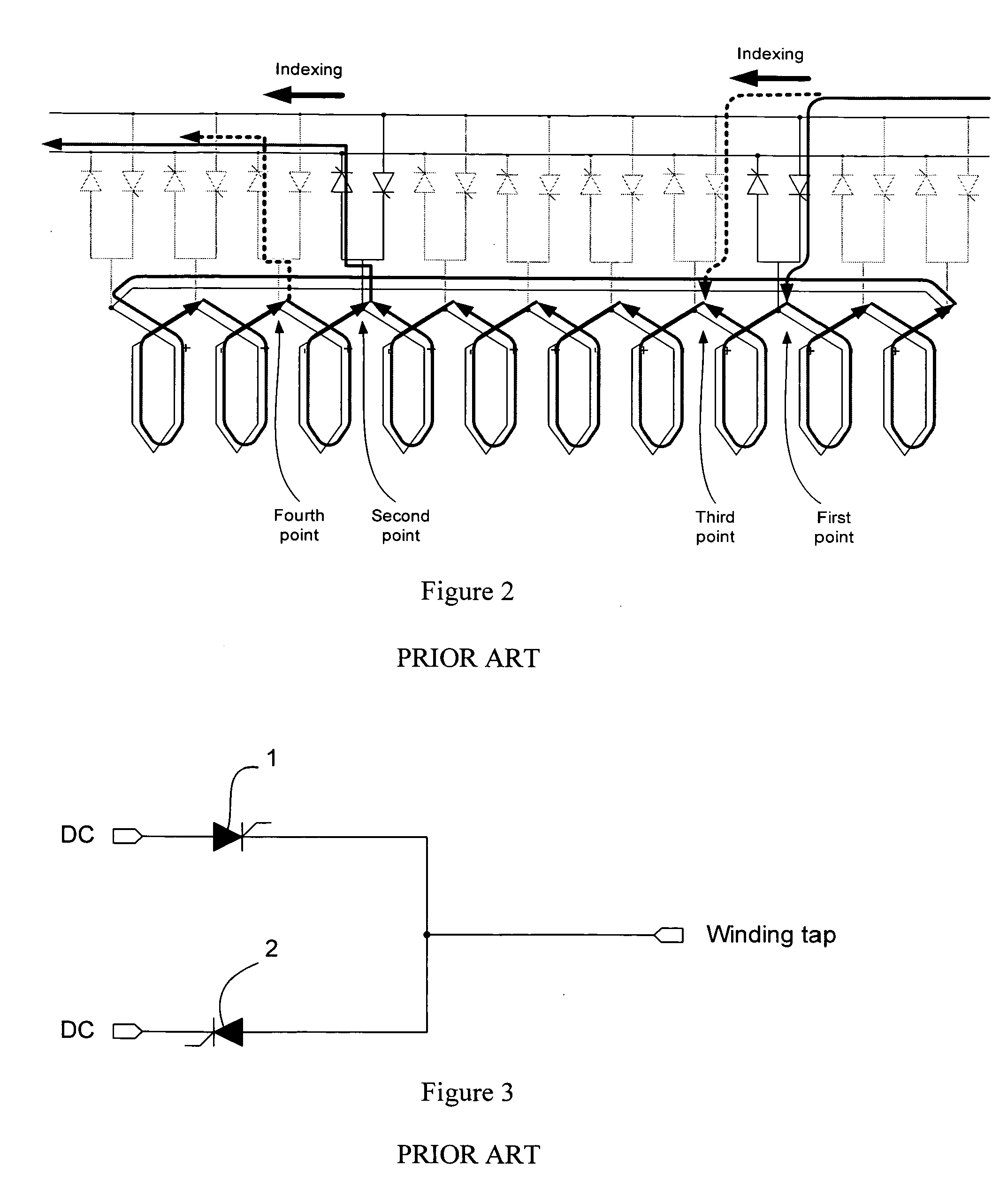

Electronic commutator circuits

InactiveUS7852025B2Reduce conduction lossRaise the ratioMotor/generator/converter stoppersAC motor controlGate turn-off thyristorHemt circuits

The present invention provides an electronic commutator circuit for use with a stator winding of an electrical machine. The stator winding of the electrical machine includes a number of coils linked by the same number of points of common coupling. The electronic commutator circuit comprising the same number of switching stages, each switching stage being connected between a respective one of the points of common coupling and first and second dc terminals. Each switching stage further includes a first reverse blocking semiconductor power device (such as a Reverse Blocking Gate Turn Off Thyristor (RB-GTO 1) capable of being turned on and off by gate control having its anode connected to the first dc terminal, and a second reverse blocking semiconductor power device (RB-GTO 2) capable of being turned on and off by gate control having its cathode connected to the second dc terminal.

Owner:GE POWER CONVERSION

Electronic commutator circuits

InactiveUS20070145928A1Reduce conduction lossRaise the ratioMotor/generator/converter stoppersAC motor controlGate turn-off thyristorCoupling

The present invention provides an electronic commutator circuit for use with a stator winding of an electrical machine. The stator winding of the electrical machine includes a number of coils linked by the same number of points of common coupling. The electronic commutator circuit comprising the same number of switching stages, each switching stage being connected between a respective one of the points of common coupling and first and second dc terminals. Each switching stage further includes a first reverse blocking semiconductor power device (such as a Reverse Blocking Gate Turn Off Thyristor (RB-GTO 1) capable of being turned on and off by gate control having its anode connected to the first dc terminal, and a second reverse blocking semiconductor power device (RB-GTO 2) capable of being turned on and off by gate control having its cathode connected to the second dc terminal.

Owner:GE POWER CONVERSION

Low-Loss and Fast Acting Solid-State Breaker

InactiveUS20170141560A1Electronic switchingArrangements responsive to excess currentGate turn-off thyristorEngineering

A circuit including a source, a load, and an isolation circuit for controllably isolating the load from the source. The isolation circuit is disposed between the source and the load. The isolation circuit includes at least one insulated-gate bipolar transistor (IGBT) and at least one gate turn-off thyristor (GTO) in parallel with the insulated-gate bipolar transistor. When no fault condition exists, the GTO is configured to be on to couple the load to the source. When a fault condition exists, the at least one IGBT is configured to turn on. After the at least one IGBT turns on, the at least one GTO is configured to turn off. After a predetermined amount of time after the at least one GTO turns off, the at least one IGBT is configured to turn off.

Owner:EXCELITAS TECH

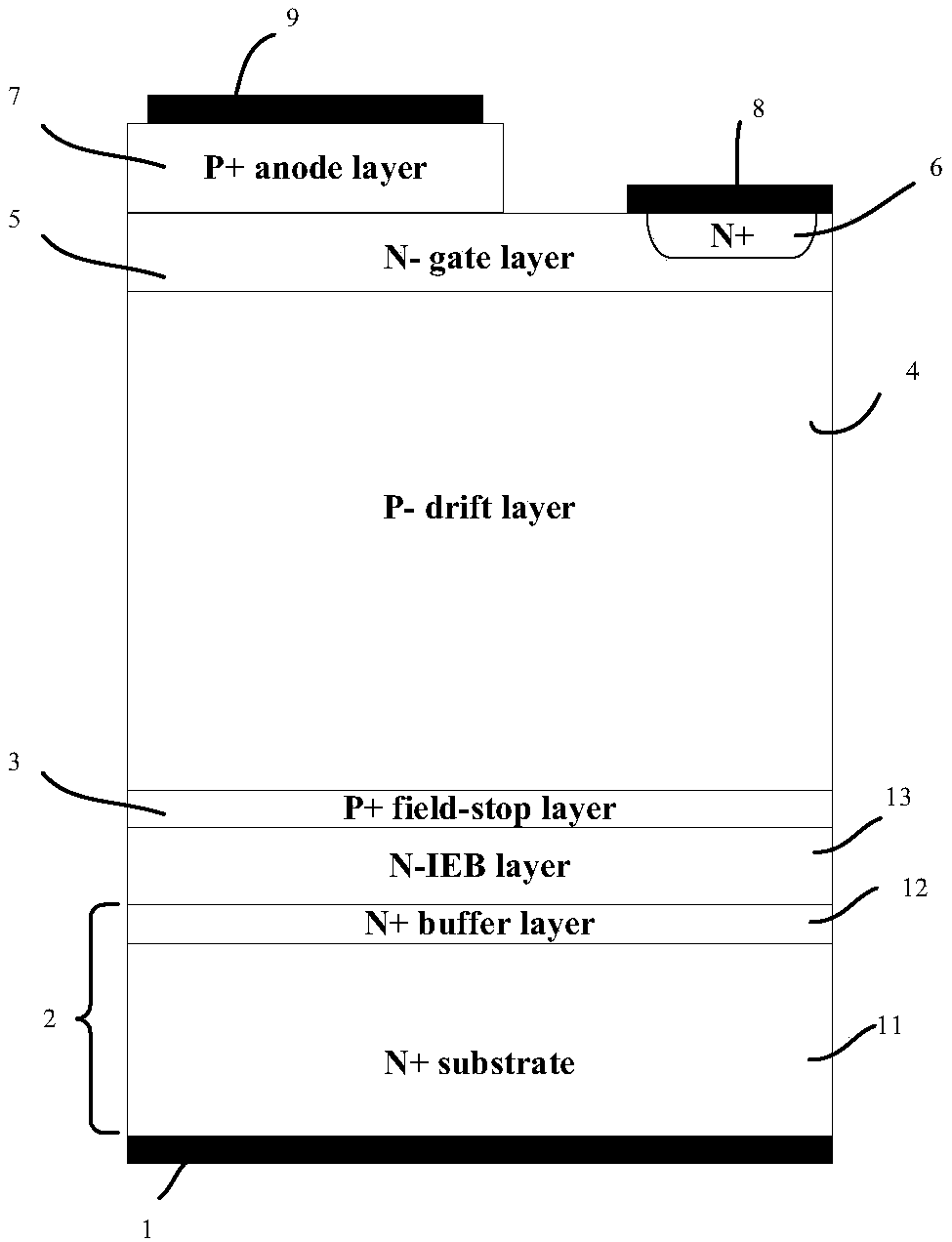

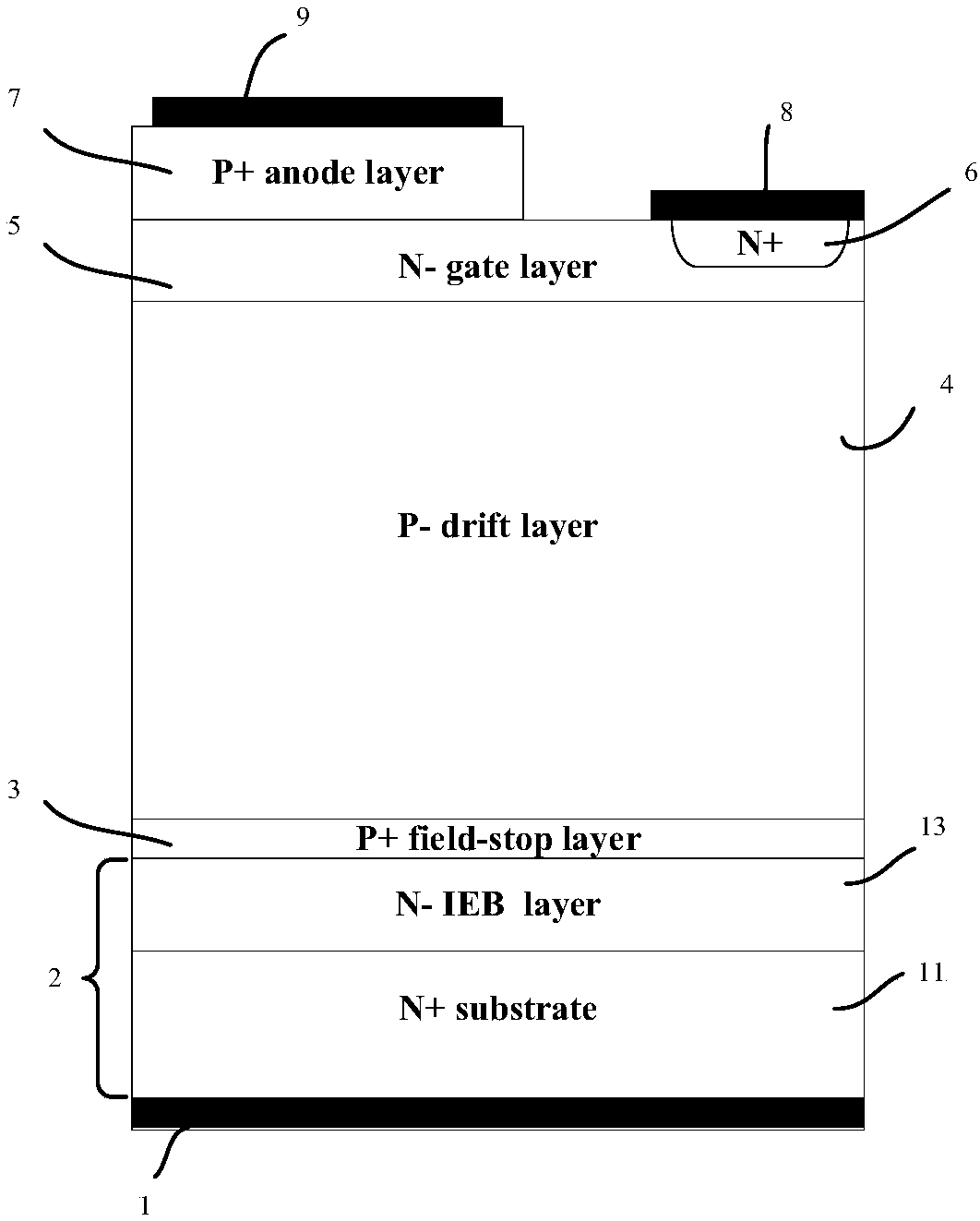

A silicon carbide gate can turn off a thyristor

InactiveCN109065614ALower on-resistanceReduce power consumptionThyristorSemiconductor/solid-state device manufacturingGate turn-off thyristorDiffusion current

The invention relates to a power semiconductor technology, in particular to a silicon carbide gate turn-off thyristor. The invention modifies the cathode region of the conventional silicon carbide GTOby adding a layer of N-IEB layer (N-type Injection Enhanced Buffer Layer). As the doping concentration of the IEB layer 13 is low, the lifetime and mobility of minority carriers in the region are improved, and the diffusion length of minority carriers in the cathode structure is increased, thereby increasing the injection efficiency of the cathode. As a built-in electric field is generated between the N-type substrate 2 and the IEB layer 13 as a result of the concentration difference, , and the direction thereof is pointed from the N-type substrate 2 to the N-type substrate 3-IEB layer 13, which prevents minority hole from diffusing from N-IEB layer 13 to the N-type substrate 2, thereby reducing the minority hole diffusion current and further increasing the cathode injection efficiency.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Silicon carbide gate-turn-off thyristor and manufacturing method thereof

ActiveCN108878523AWeaken edge current densityIncrease dtSemiconductor/solid-state device manufacturingSemiconductor devicesGate turn-off thyristorPower flow

The invention provides a silicon carbide gate-turn-off thyristor. The thyristor is of a PNPN four-layer SiC structure which is arranged on an N+ type SiC substrate; the upper layer is a strip composedof a plurality of repeatedly-arranged upper tube P-type emission regions; the middle layer is composed of an upper tube N-type base region, an upper tube N type thick base region and an upper tube Ntype thick base region bus bar; the upper tube N type thick base region and the upper tube N type thick base region bus bar are crossed or parallel; and the upper surface of the upper tube N-shaped bus bar is connected with a gate pole metal layer. By virtue of the silicon carbide gate-turn-off thyristor provided by the invention, the current density of the periphery can be reduced, and the anti-dI / dt and anti-dV / dt capability can be improved.

Owner:HANGZHOU UG MIN SEMICON TECH CO LTD

Thyristor with gate capable of being turned off and manufacturing method thereof

ActiveCN110047913AImprove reliabilityLower requirementThyristorSemiconductor/solid-state device manufacturingGate turn-off thyristorEngineering

The invention provides a thyristor with a gate capable of being turned off. A plurality of strips formed by repeatedly arranging a plurality of high-doping-concentration upper tube N-type emitting regions are arranged on the upper surface of an N-type silicon substrate sheet; an upper tube P-type concentrated base region bus bar surrounds the periphery of each strip; a cathode metal layer is arranged on the upper surface of each upper tube N-type emitting region; an upper tube P-type base region is arranged below each upper tube N-type emitting region; the side surface of each upper tube P-type base region is connected with an upper tube P-type concentrated base region or an upper tube P-type concentrated base region bus bar; an upper tube N-type collector region is arranged below the upper tube P-type base region, the upper tube P-type concentrated base region and the upper tube P-type concentrated base region bus bar; a lower tube P-type emitting region is arranged below the upper tube N-type collector region; the lower surface of the lower tube P-type emitting region is connected with an anode metal layer; and a gate metal layer is arranged above the silicon substrate sheet. According to the thyristor with the gate capable of being turned off, the dI / dt resistance and the dV / dt resistance are remarkably enhanced, and the breakdown voltage and the current capacity have a wideapplication range.

Owner:HANGZHOU UG MIN SEMICON TECH CO LTD

Gate pole turn-off thyristor and manufacturing method thereof

InactiveCN109786451AIncrease working frequencyLower bulk resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesGate turn-off thyristorVoltage drop

The invention discloses a gate pole turn-off thyristor and a manufacturing method thereof. The gate pole turn-off thyristor comprises a first base region, a second base region, a third base region anda fourth base region which are sequentially formed from bottom to top and also comprises positive electrode metal, negative electrode metal and two gate pole metals, wherein the positive electrode metal is formed on a lower surface of the first base region, the negative electrode metal is formed on an upper surface of the fourth base region, the two gate pole metals are formed on an upper surfaceof the fourth base region and are respectively arranged at two sides of the negative electrode metal, the gate pole turn-off thyristor also comprises a first conductive type of heavy-doped buried layers and a first conductive type of heavy-doped injection regions, the injection regions are respectively formed below the two negative electrode metals, the buried layers are formed below the injection regions, the buried layers extend to the third base region from the upper surface of the third base region, and the injection regions penetrate through the fourth base region from the upper surfaceof the four base region. The invention also discloses a manufacturing method of the gate pole turn-off thyristor. The gate pole-turn-off thyristor has the advantages of small conduction voltage drop and specially short turn-off time.

Owner:泉州臻美智能科技有限公司

Gate-turn-off thyristor and manufacturing method thereof

InactiveCN108899358AEnhanced anti-dIEnhanced dtThyristorSemiconductor/solid-state device manufacturingGate turn-off thyristorEngineering

The invention provides a gate-turn-off thyristor. A plurality of strips formed by repeatedly arraying a plurality of high-doping-concentration upper tube N type emission regions are arranged on an upper surface of an N type silicon substrate chip; an upper tube P-type concentrated basic region bus bar is arranged around the periphery of each strip; a cathode metal layer is arranged on the upper surface of one upper tube N type emission region, an upper tube P-type basic region is arranged below the upper tube N type emission region, and a side face of the upper tube P-type basic region is connected with an upper tube P-type concentrated basic region or the upper tube P-type concentrated basic region bus bar; an upper tube N-type current collection region is arranged below the upper tube P-type basic region, the upper tube P-type concentrated basic region and the upper tube P-type concentrated basic region bus bar; a lower tube P-type emission region is arranged below the upper tube N-type current collection region; a lower surface of the lower tube P-type emission region is connected with an anode metal layer; a gate metal layer is arranged above the silicon substrate chip. According to the gate-turn-off thyristor provided by the invention, anti-dI / dt ad anti-dV / dt capabilities of turn-off thyristor are remarkably enhanced, and breakdown voltage and a current capacity have a wide application range.

Owner:HANGZHOU UG MIN SEMICON TECH CO LTD

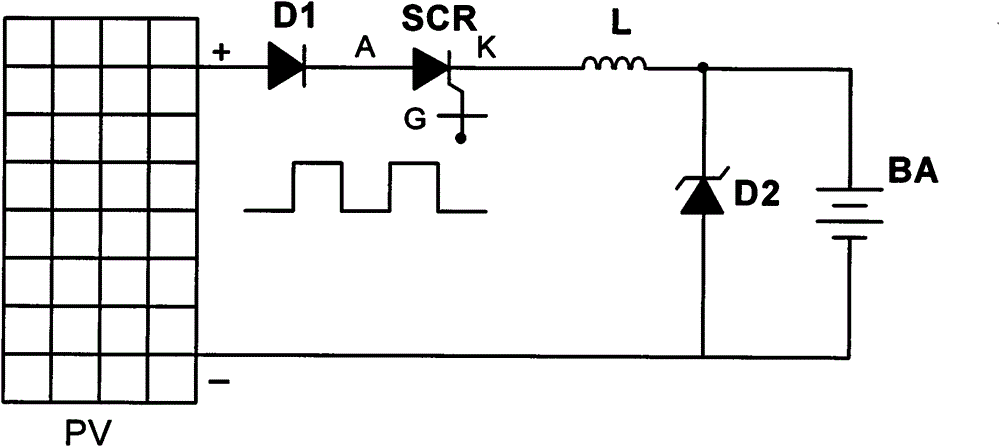

Storage battery charging control circuit in photovoltaic power generation system

InactiveCN104467052ASimple structureEasy maintenanceBatteries circuit arrangementsPhotovoltaicsGate turn-off thyristorBattery charge

The invention relates to a storage battery charging control circuit in a photovoltaic power generation system. The positive electrode of a solar cell panel is connected with the anode of a diode. The cathode of the diode is connected with the anode of a thyristor capable of being turned off. The cathode of the thyristor capable of being turned off is connected with the cathode of a voltage stabilizing diode and then connected with one end of an inductor. The other end of the inductor is connected to the anode of a storage battery. The cathode of the storage battery is connected with the anode of the voltage stabilizing diode and then connected with the negative electrode of the solar cell panel. When positive and negative trigger signals are added to the gate pole of the thyristor capable of being turned off, the thyristor capable of being turned off can be automatically turned off, and the charging voltage of the storage battery is adjusted. The storage battery charging control circuit is simple in structure, low in cost and high in reliability.

Owner:TIANJIN UNIV OF TECH & EDUCATION TEACHER DEV CENT OF CHINA VOCATIONAL TRAINING & GUIDANCE

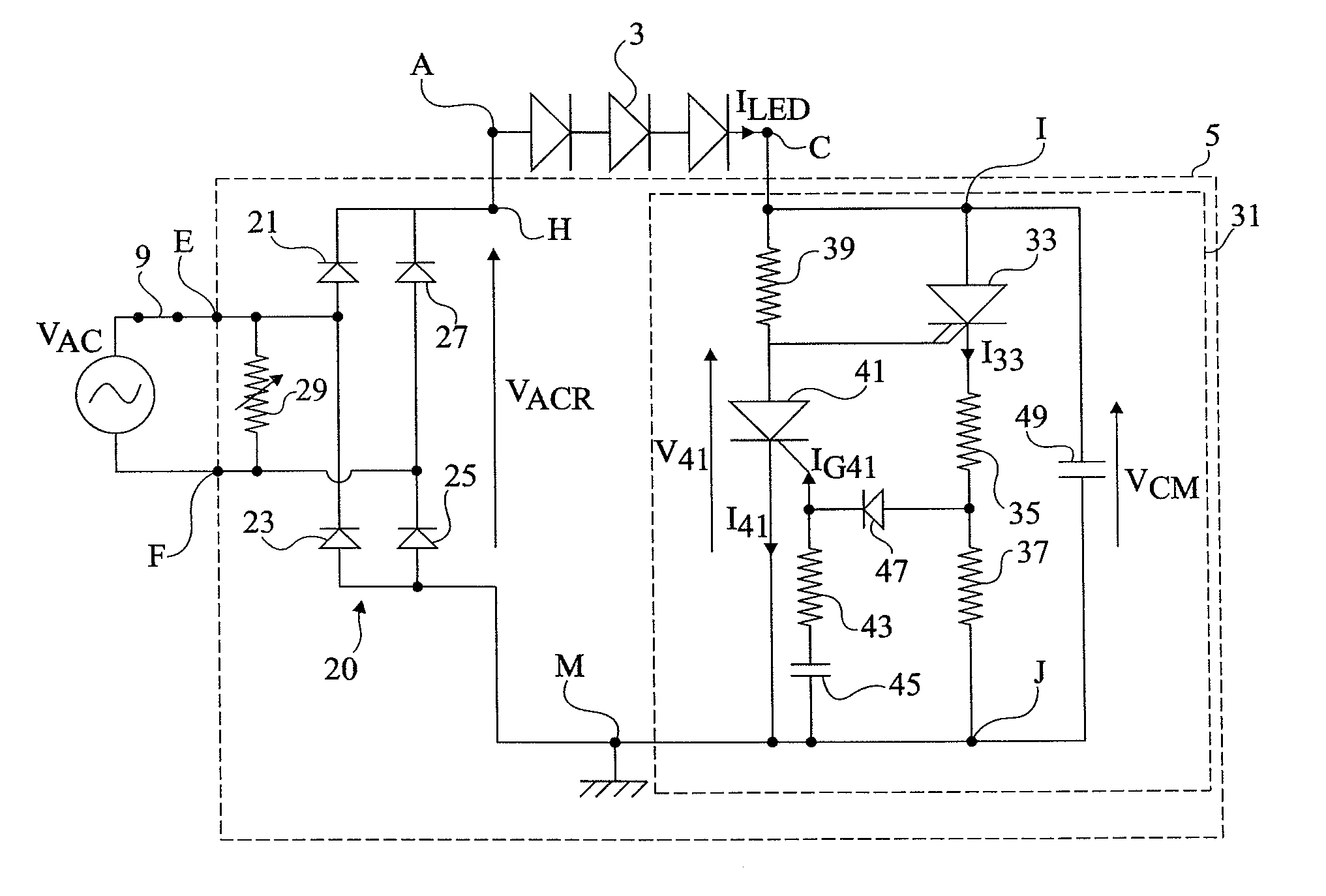

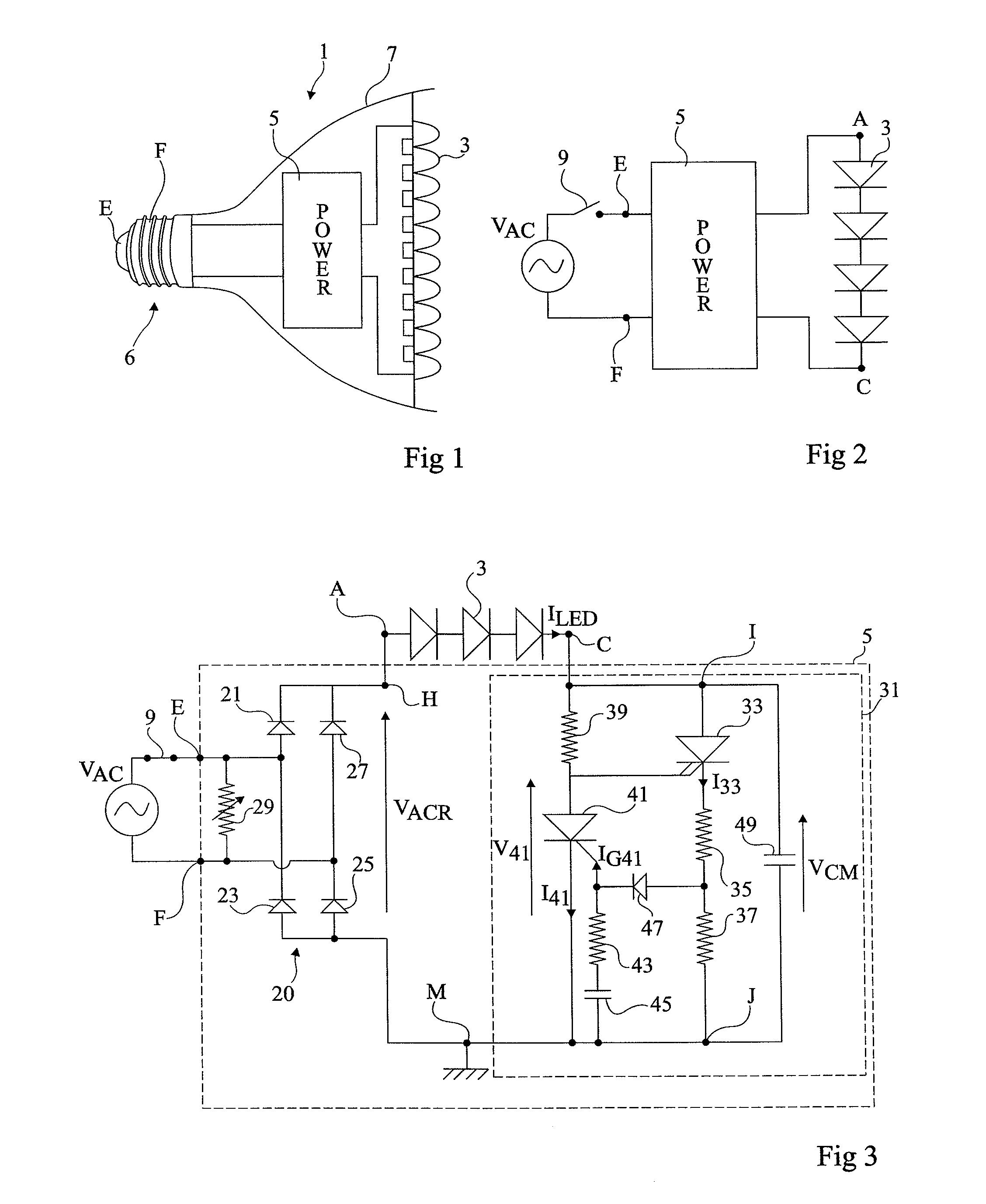

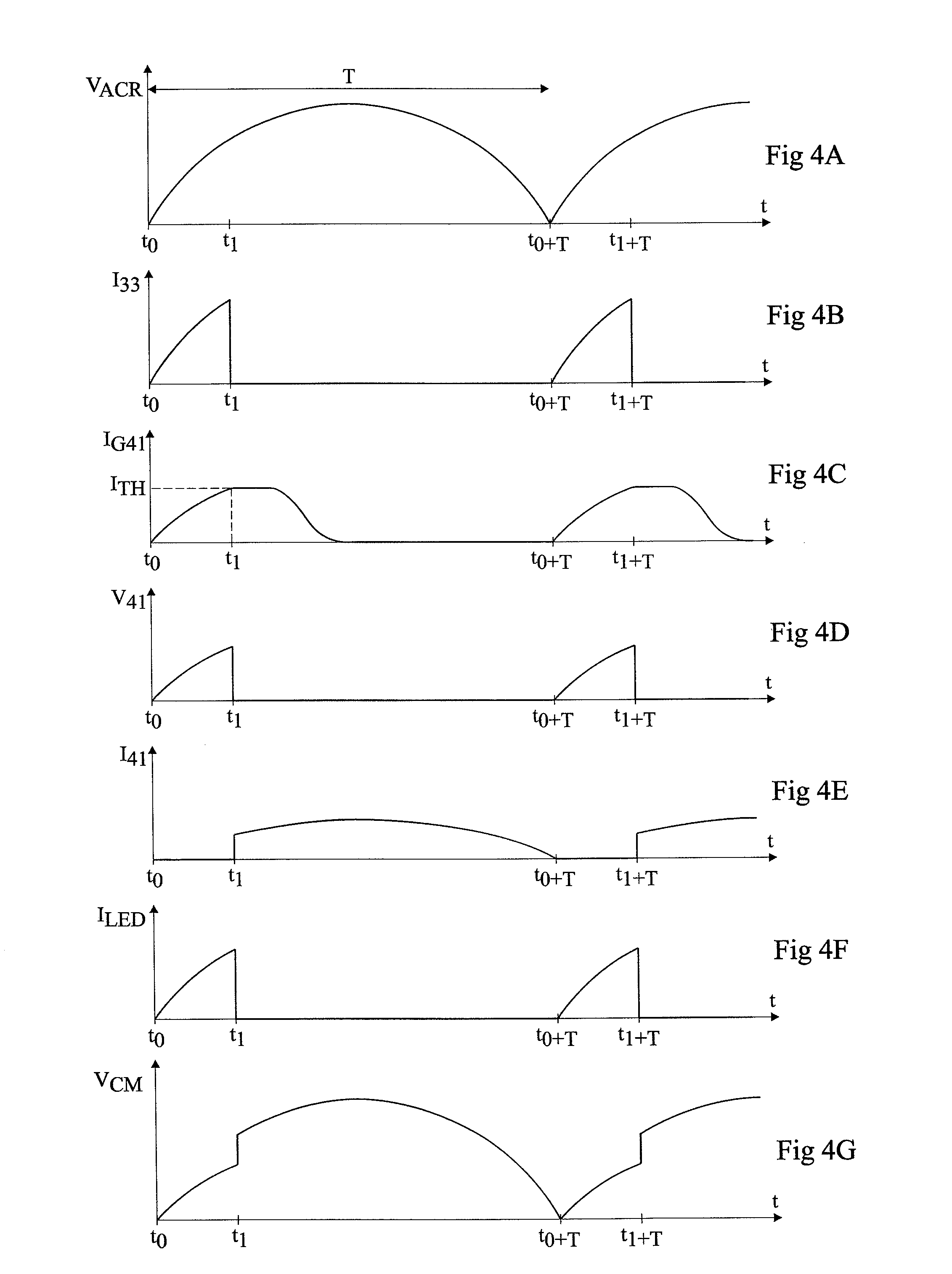

Circuit for controlling a lighting unit with light-emitting diodes

InactiveUS20100315006A1Extended service lifeLow costElectrical apparatusElectroluminescent light sourcesGate turn-off thyristorEffect light

A circuit capable of receiving, in series with at least one light-emitting diode, a rectified A.C. voltage, comprising: a first gate turn-off thyristor connected to first and second terminals of the circuit; and a control circuit for turning off the first thyristor when the voltage between the first and second terminals exceeds a threshold.

Owner:STMICROELECTRONICS (TOURS) SAS