Patents

Literature

107results about How to "Lower bulk resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Composite oxide sintered body and sputtering target comprising same

InactiveUS20110260121A1Reduce rateLower bulk resistanceConductive materialVacuum evaporation coatingBulk resistanceComposite oxide

A composite oxide sintered body includes In, Zn, and Sn, and has a relative density of 90% or more, an average crystal grain size of 10 μm or less, and a bulk resistance of 30 mΩcm or less, the number of tin oxide aggregate particles having a diameter of 10 μm or more being 2.5 or less per mm2 of the composite oxide sintered body.

Owner:IDEMITSU KOSAN CO LTD

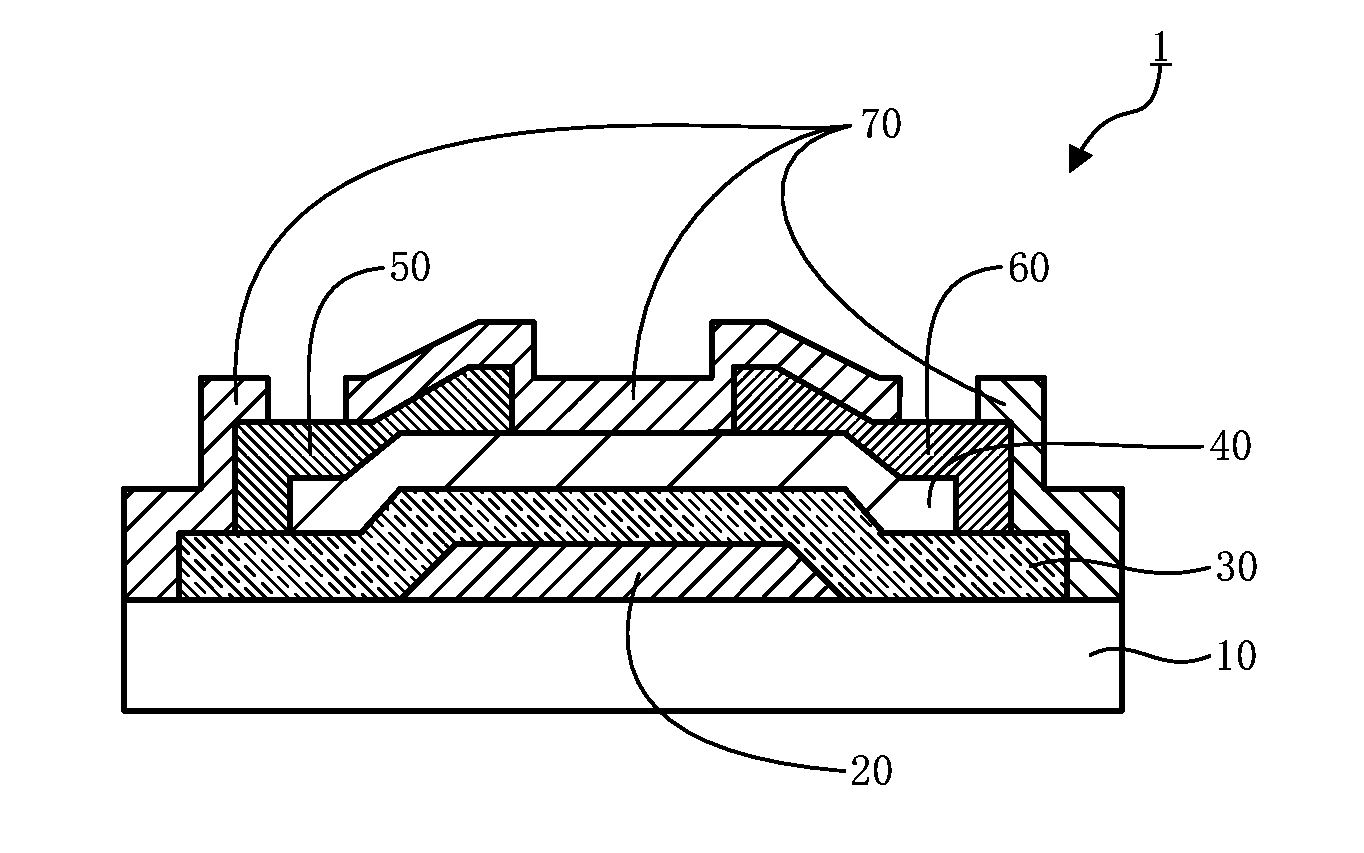

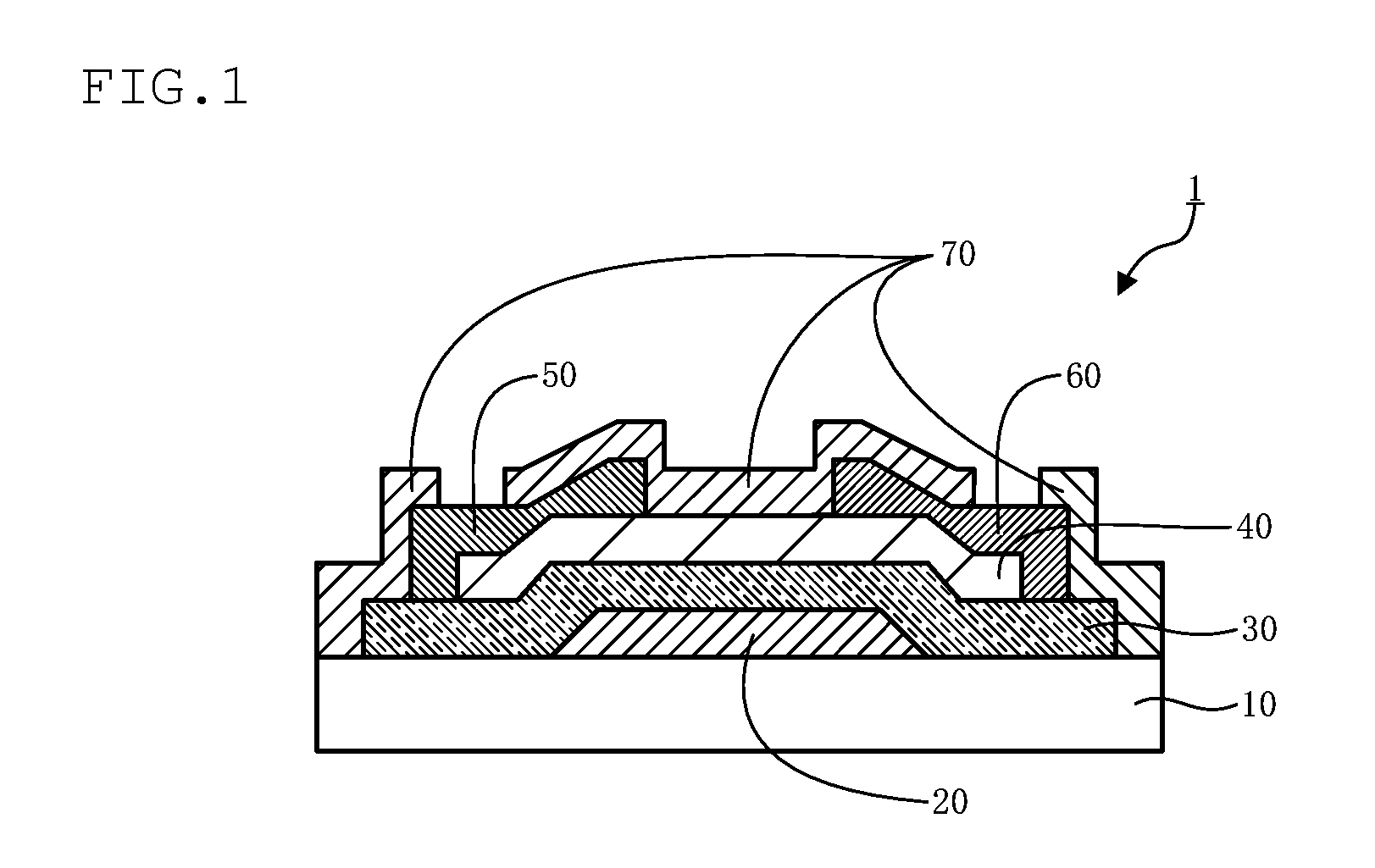

Organic light-emitting diode and flat display device including the same

ActiveUS20120326137A1Improve performanceReduce interface resistanceSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceCompound (substance)

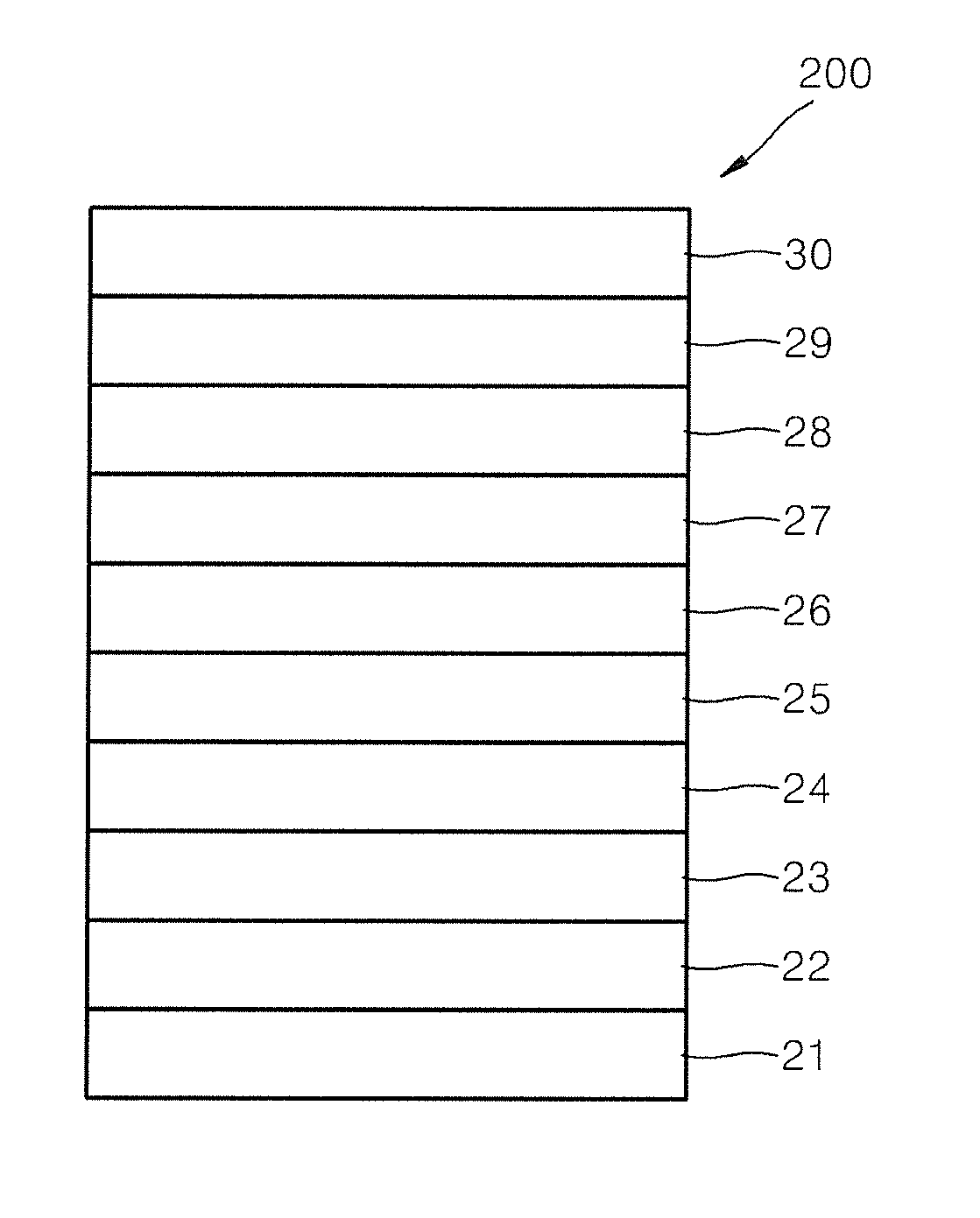

An organic light-emitting diode including a first electrode; a second electrode facing the first electrode; an emission layer interposed between the first electrode and the second electrode; a first hole transport layer including a first hole transporting compound; a second hole transport layer including a second hole transporting compound, the first and second hole transport layers being interposed between the first electrode and the emission layer; an electron transport layer interposed between the emission layer and the second electrode; a first mixing layer interposed between the first electrode and the first hole transport layer, contacting the first hole transport layer, and including the first hole transporting compound and a first cyano group-containing compound; and a second mixing layer interposed between the first electrode and the second hole transport layer, contacting the second hole transport layer, and including the second hole transporting compound and a second cyano group-containing compound.

Owner:SAMSUNG DISPLAY CO LTD

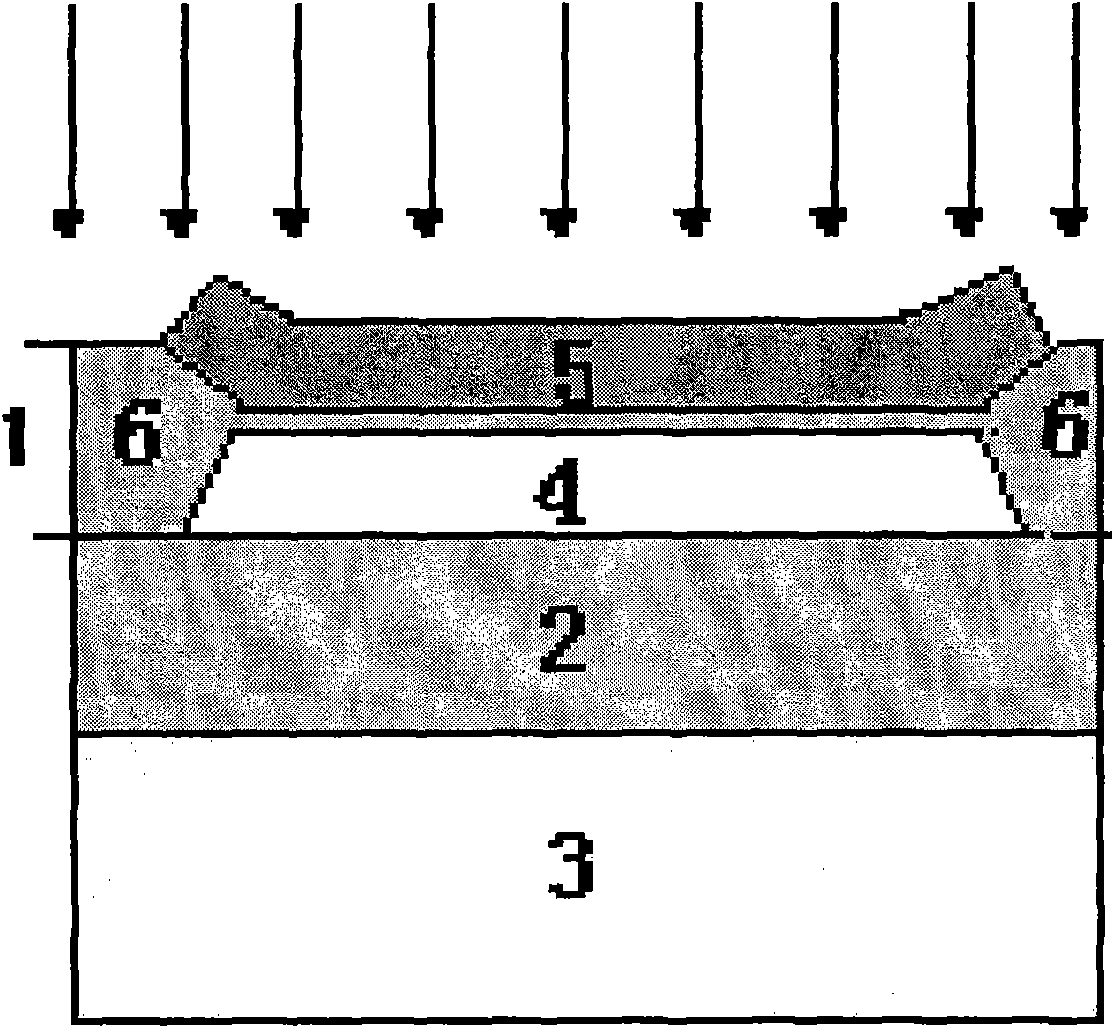

Technology for manufacturing selective emitter junction solar cell by printed phosphorous source one-step diffusion method

ActiveCN101937940ARealize the structureGood diffusion uniformity controlFinal product manufactureSemiconductor devicesDiffusion methodsScreen printing

The invention relates to technology for manufacturing a selective emitter junction solar cell by a printed phosphorous source one-step diffusion method. The method comprises the following steps of: cleaning and texturing a silicon wafer, performing screen printing of phosphorous-containing nano Si slurry, drying at the temperature of between 200 and 350 DEG C for about 20 minutes, and removing the solvent to obtain a phosphorous-containing oxidation layer with the thickness of 30 to 100nm; implementing BOE and RCA cleaning to remove 70 percent of surface phosphorous slurry before diffusion; putting the silicon wafer into a diffusion furnace, adding a POCL3 air source, heating to between 800 and 1,000 DEG C, forming re-diffusion at a grid line of the phosphorous-containing nano slurry on the silicon wafer to form a higher surface concentration-heavily doped region, and forming a shallow diffusion region in other areas. By adopting the screen printing of the phosphorous-containing nano slurry, the phosphorous-containing nano slurry is heated at high temperature for diffusion, forms the heavily doped region at a contact position with the grid line and forms a lightly doped region in other areas. The technology has the efficiency of over 18.5 percent on the premise of better controlling the diffusion uniformity.

Owner:TRINA SOLAR CO LTD

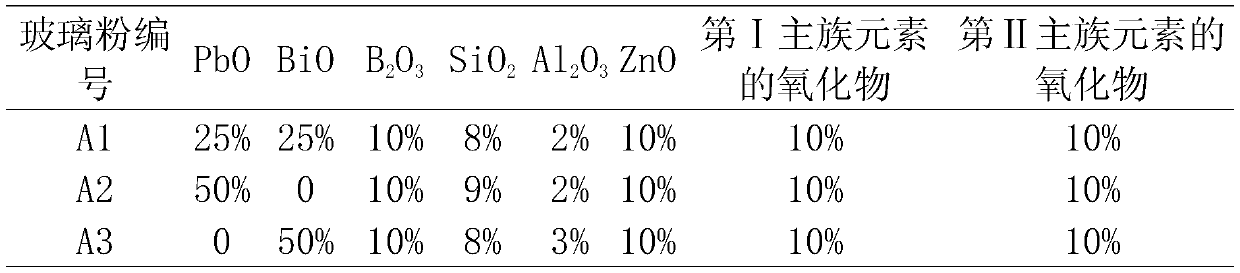

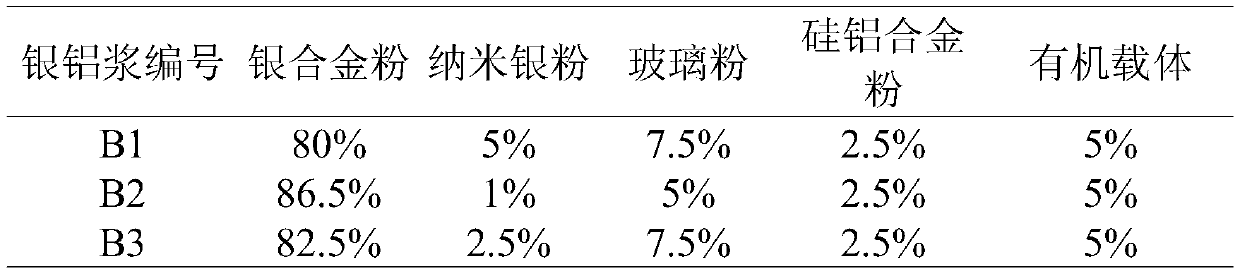

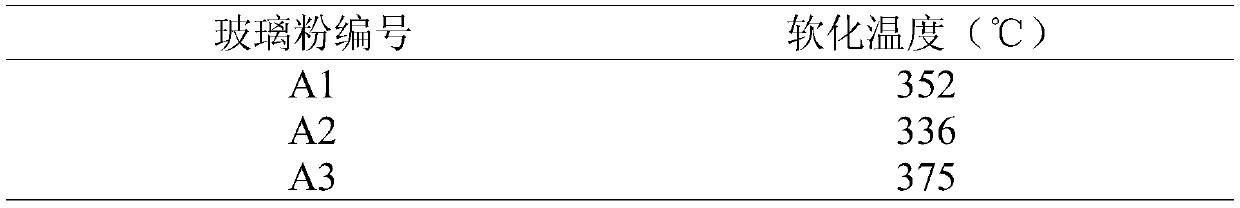

Glass powder and silver aluminum paste comprising glass powder and used on positive side of N-type double-sided solar cell

PendingCN110040968ALow softening temperatureIncrease the degree of vitrificationTransportation and packagingMetal-working apparatusMass ratioSilicon solar cell

The invention discloses glass powder and silver aluminum paste which comprises the glass powder and used on the positive side of an N-type double-sided solar cell. The silver aluminum paste comprisesconductive silver powder, silicon aluminum alloy powder, the glass powder and an organic carrier, wherein the glass powder is prepared from the following components in percentage by weight: 0-50% of PbO, 0-50% of BiO, 5-15% B2O3, 8-9% of SiO2, 2-3% of Al2O3 and 5-15% of ZnO; the mass ratio of silicon to aluminum in the glass powder is (4-5) to 1; the content of the conductive silver powder is 80wt% to 90wt%; the conductive silver powder comprises nano silver powder and silver alloy powder in a mass ratio of 1 to (18-90). The glass powder not only guarantees the corrosiveness of SiNx, but alsodoes not cause relatively strong metallized composition. The silver aluminum paste prepared by using the glass powder solves the problem of the contradiction between contact resistance and open circuit voltage when the silver aluminum paste is printed on the positive side of an N-type crystalline silicon solar cell.

Owner:NANTONG T SUN NEW ENERGY CO LTD

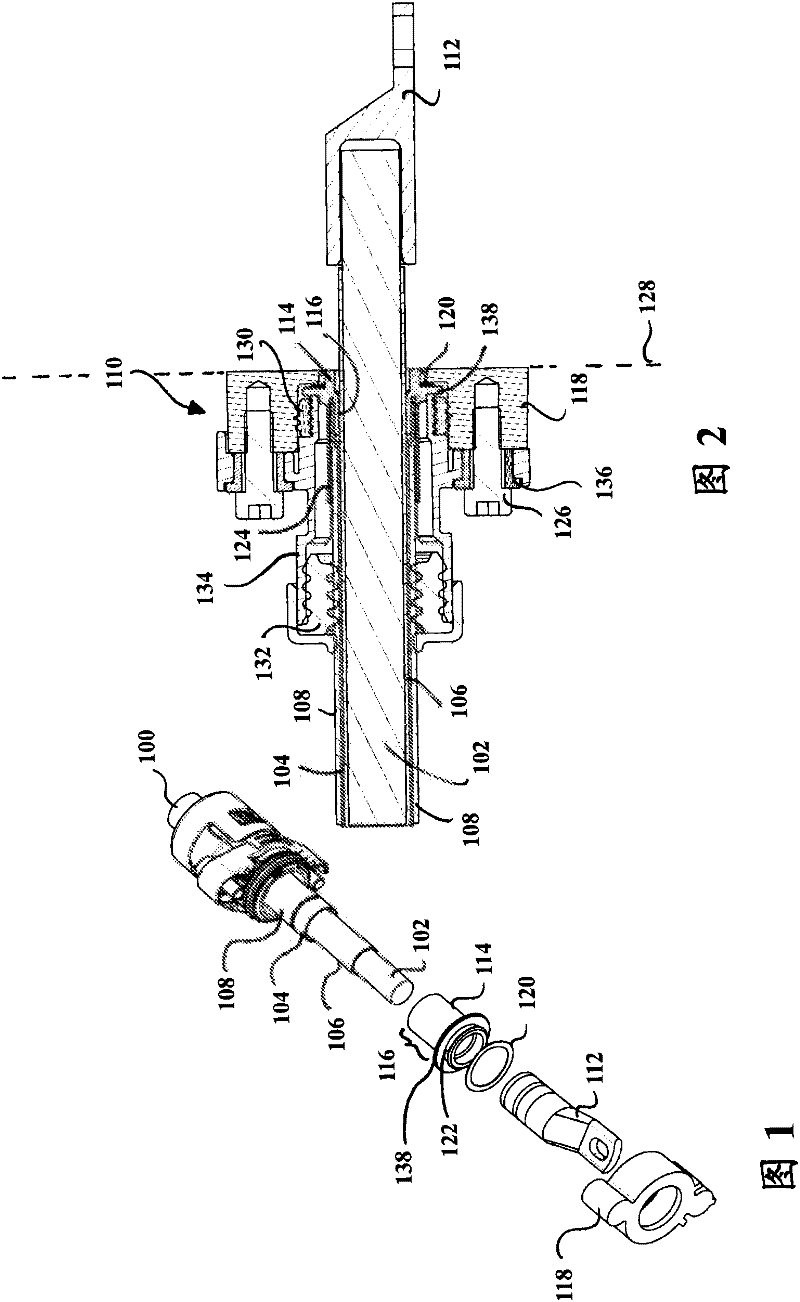

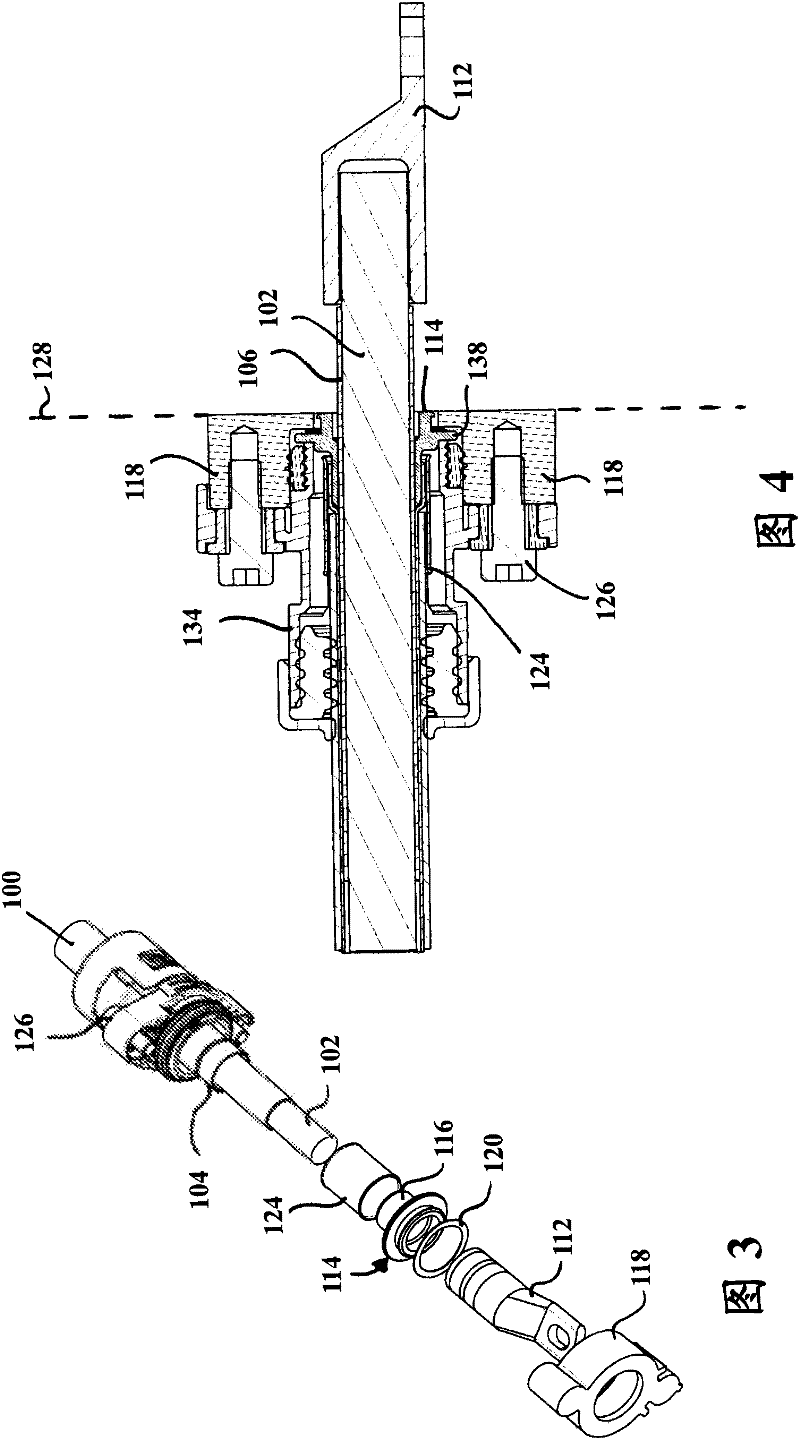

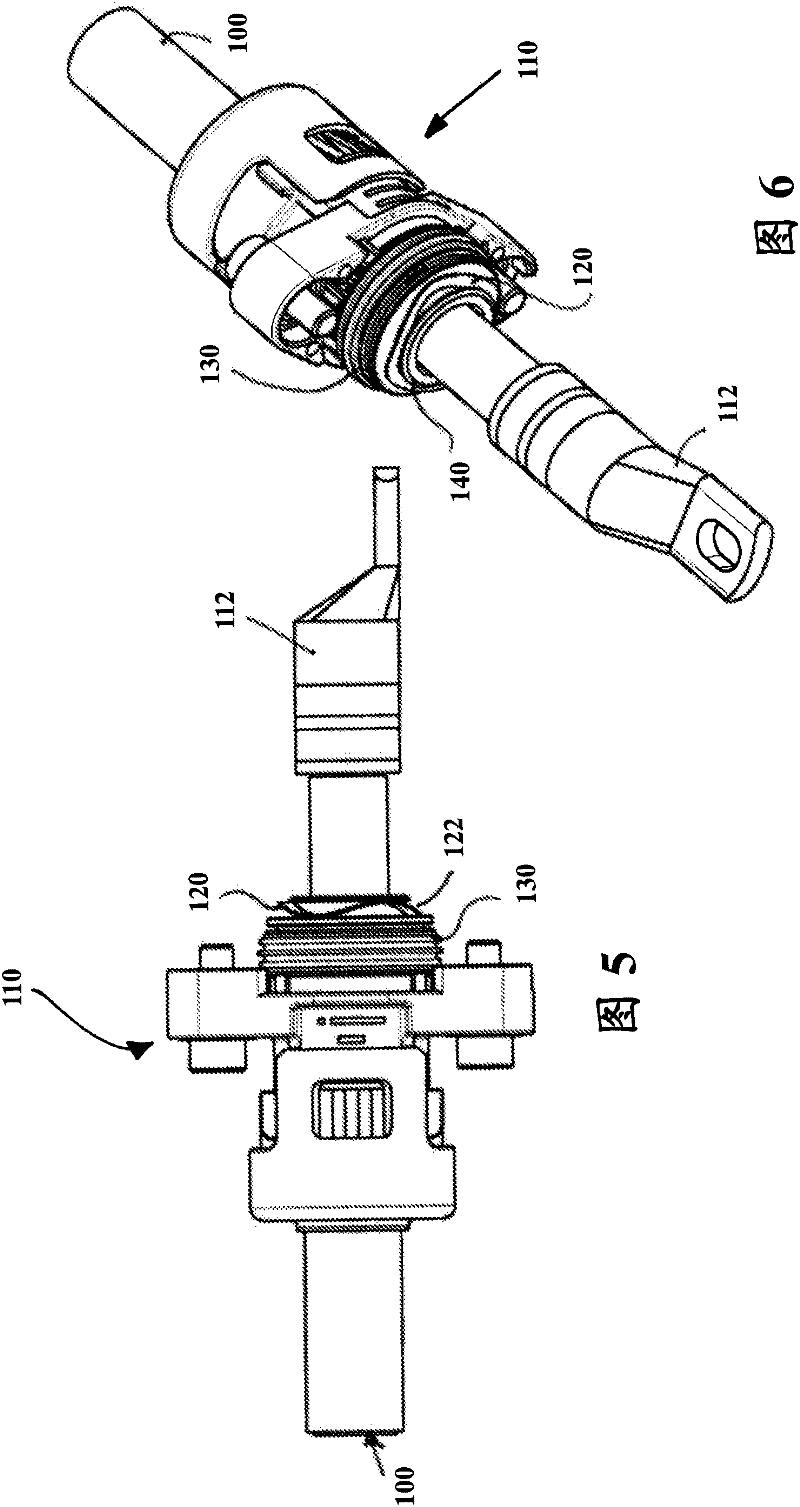

Shielding braid termination for shielded electrical connector

ActiveCN102341965ALower bulk resistanceReduce manufacturing costVehicle connectorsElectrically conductive connectionsShielded cableElectrical conductor

The present invention relates to shielded electrical cables and shielded electrical connectors to be affixed thereto, and in particular to the termination of the shielding braid provided at the electrical cable. According to the present invention, a shielding termination structure for engaging a shielding (104) of a shielded cable (100) having an insulated conductor (102) that is encompassed by said shielding is provided, said shielding termination structure (110) comprising: an electrically conductive shield body (114) for establishing an electrical connection between said shielding (104) and an electrically conductive interface (118), fixing means (126) for securing said shield body (114) at the interface (118); an electrically conductive spring element (120) that is arranged between said shield body (114) and the interface (118) for establishing the electric contact in a compressed state of the spring element (120).

Owner:TYCO ELECTRONICS (UK) LTD

Sputtering target containing zinc sulfide as major component, optical recording medium on which phase change optical disk protective film containing zinc sulfide as major component is formed by using the target, and method for manufacturing the sputtering target

ActiveUS7279211B2Reduce the impact of heatIncrease speedPigmenting treatmentCellsTectorial membraneRefractive index

Provided is a sputtering target and an optical recording medium having formed thereon a phase change optical disc protective film having zinc sulfide as its principal component employing such a target, as well as the manufacturing method thereof, characterized in that the sputtering target has zinc sulfide as its principal component, and is capable of adjusting the refractive index of a film containing conductive oxide in the range of 2.0 to 2.6. This sputtering target, and an optical recording medium having formed thereon a phase change optical disc protective film having zinc sulfide as its principal component employing such a target, is capable of reducing particles (dust emission) and nodules that arise during sputtering, has minimal variation in quality and is capable of improving mass productiveness, and in which the crystal grain is fine and has a high density of 90% or more.

Owner:JX NIPPON MINING & METALS CORP

Method for preparing antistatic filter material

InactiveCN103276532ALower surfaceLower bulk resistanceFibre treatmentFiltration separationDetonationGraphite

The invention discloses a method for preparing an antistatic filter material. The method includes the steps: preparing a plain felt; preparing treatment agents; treating after dipping; and drying to obtain the antistatic filter material. According to the method, the plain felt of the filter material is dipped in glue liquor with nano graphite powder, so that low resistance is formed inside the filter material and on the surface of the filter material. The antistatic filter material is low in surface and body resistance and fine in temperature and corrosion resistance, and the application condition of the filter material is greatly expanded. Electrostatic accumulation of the filter material in the use process can be effectively reduced, and the risk of detonation and even explosion of flammable and explosive products such as pulverized coal and coal gas in the filtering process due to electrostatic discharge sparking is avoided.

Owner:南京际华三五二一环保科技有限公司

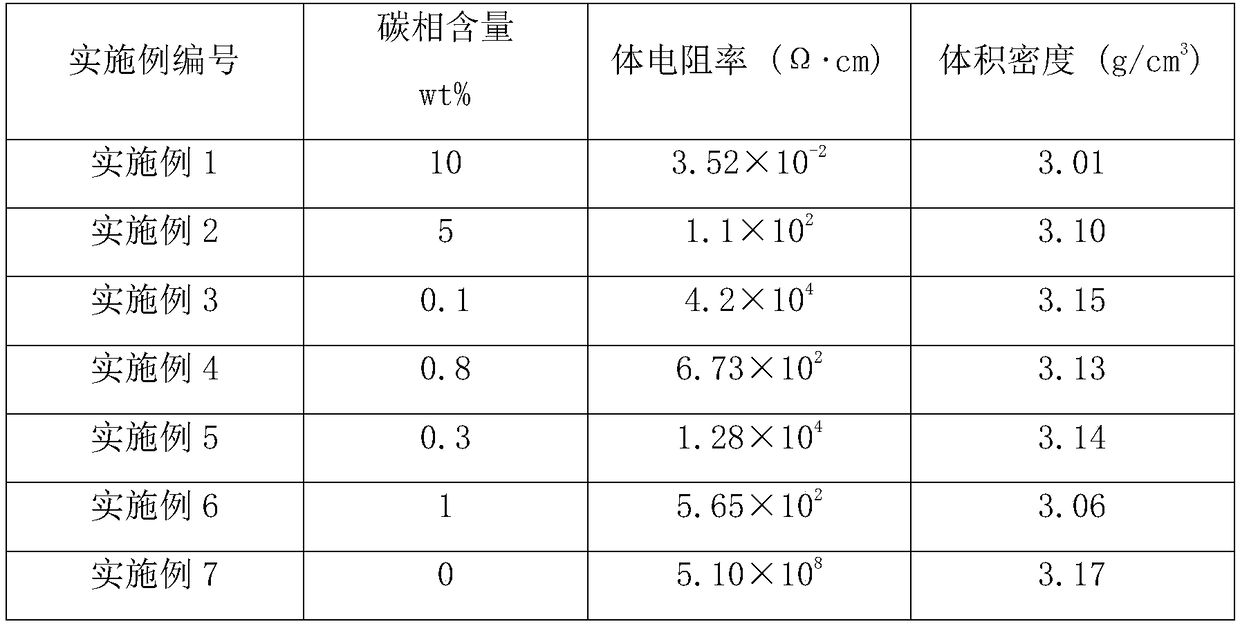

Silicon carbide ceramic with adjustable resistance and preparation method thereof

InactiveCN108911756ALower grain boundary resistanceLower bulk resistanceElectrical resistance and conductanceBoron carbide

The invention discloses silicon carbide ceramic with adjustable resistance and a preparation method thereof. The ceramic material mainly comprises a silicon carbide phase as a main phase, boron carbide as a sintering aid phase, and a carbon phase as a conductive phase, and the ceramic material can be prepared and has the bulk resistivity adjustable from 10<-2> to 10<8> Omega.cm. The silicon carbide ceramic has a density of 3.00 to 3.20 g / cm<3>. The core of the method is to coat the surface of silicon carbide raw material powder with a graphene-based material layer, and to adjust the content ofthe conductive phase in the silicon carbide ceramic to obtain the silicon carbide ceramic with adjustable bulk resistivity.

Owner:NINGBO VULCAN TECH CO LTD

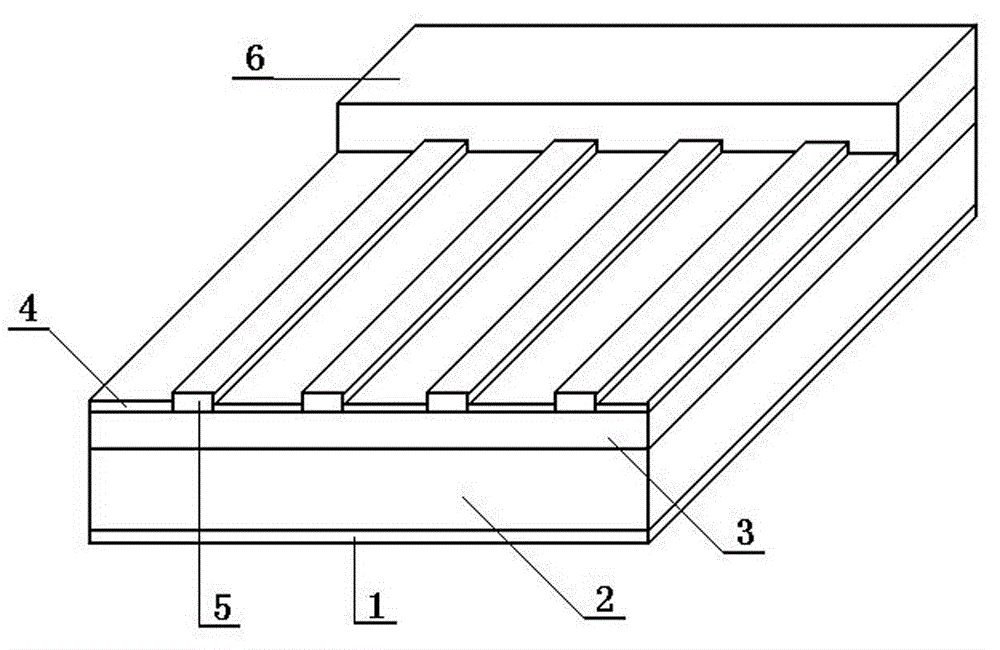

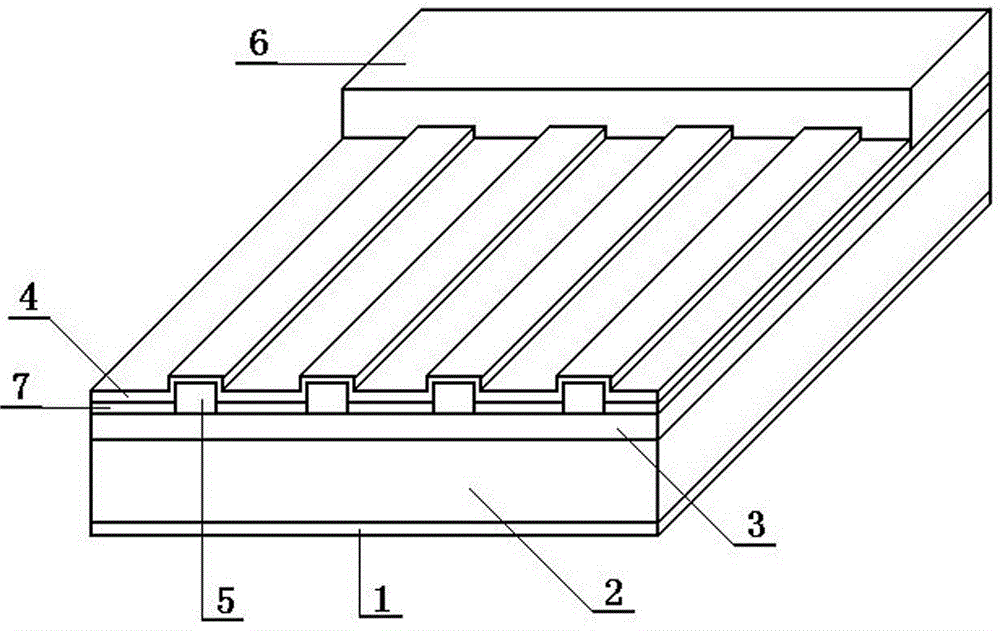

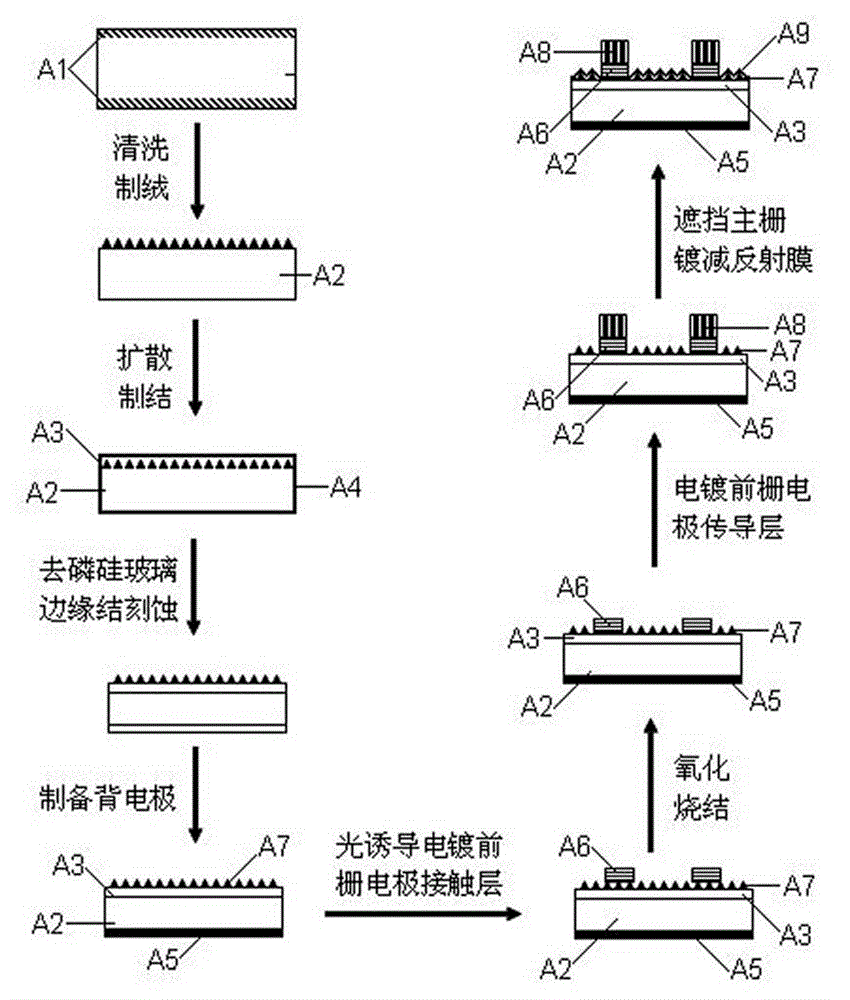

Crystalline silicon solar cell with high-photoelectric conversion efficiency and manufacturing method thereof

InactiveCN102881732AReduce shadow lossTightly boundFinal product manufactureSemiconductor devicesOhmic contactCrystalline silicon

The invention discloses a crystalline silicon solar cell with high-photoelectric conversion efficiency and a manufacturing method thereof. The cell comprises a crystalline silicon P-N node substrate, a back electrode and a front gate electrode, wherein the back electrode is in ohmic contact with the P area of the crystalline silicon P-N node substrate; the front gate electrode is in ohmic contact with the N area of the crystalline silicon P-N node substrate; the front gate electrode is wrapped under the antireflection layer and comprises a SiO2 layer and an antireflection layer; the SiO2 layer is positioned on the surface of the N area of the crystalline silicon P-N node substrate; and the antireflection layer is arranged on the SiO2 layer. The manufacturing method comprises a cleaning and flocking step, a diffusing and knotting step, a phosphorus-washing and etching step, a back electrode-preparing step, a photoinduced front gate electrode electroplating step, an oxidizing and sintering step, a front gate electrode electroplating step and an antireflection layer preparing step. The photoinduced front gate electrode electroplating step and the oxidizing and sintering step are adopted, so that the cell has the characteristics of simple production process, high efficiency, low cost, low front gate electrode shade loss of the solar cell, low contact resistance and body resistance, uneasiness in line breaking of the thin front gate electrode, low cell surface reflectivity and high photoelectric conversion efficiency.

Owner:YUNNAN UNIV

Lead-free electrocondution slurry used for crystalline silicon solar cell back electrode and preparation method thereof

ActiveCN103400633AImprove solder resistanceImprove adhesionNon-conductive material with dispersed conductive materialCable/conductor manufactureSlurrySolvent

The invention relates to lead-free electrocondution slurry used for a crystalline silicon solar cell back electrode. The lead-free electrocondution slurry used for the crystalline silicon solar cell back electrode consists of the following components in percentage by weight: 40-70wt% of silver plating copper powder, 2-10wt% of inorganic lead-free glass powder and 25-50wt% of organic carrier, wherein the organic carrier is the mixture of solvent, thickening agent and additive, and the prepared electrocondution slurry printing back electrode has the advantages of big thickness, small bulk resistance, excellent soldering resistance, strong welding adhesive force and silver ion migration resistance. Meanwhile, after cell pieces are subjected to series welding, an assembly has the advantages of higher stability and stronger anti-aging capability.

Owner:SHANGHAI BONA ELECTRONICS TECH

Composite oxide sintered body and sputtering target comprising same

ActiveUS20130112971A1Reduce rateLower bulk resistanceTransistorVacuum evaporation coatingBulk resistanceComposite oxide

Owner:IDEMITSU KOSAN CO LTD

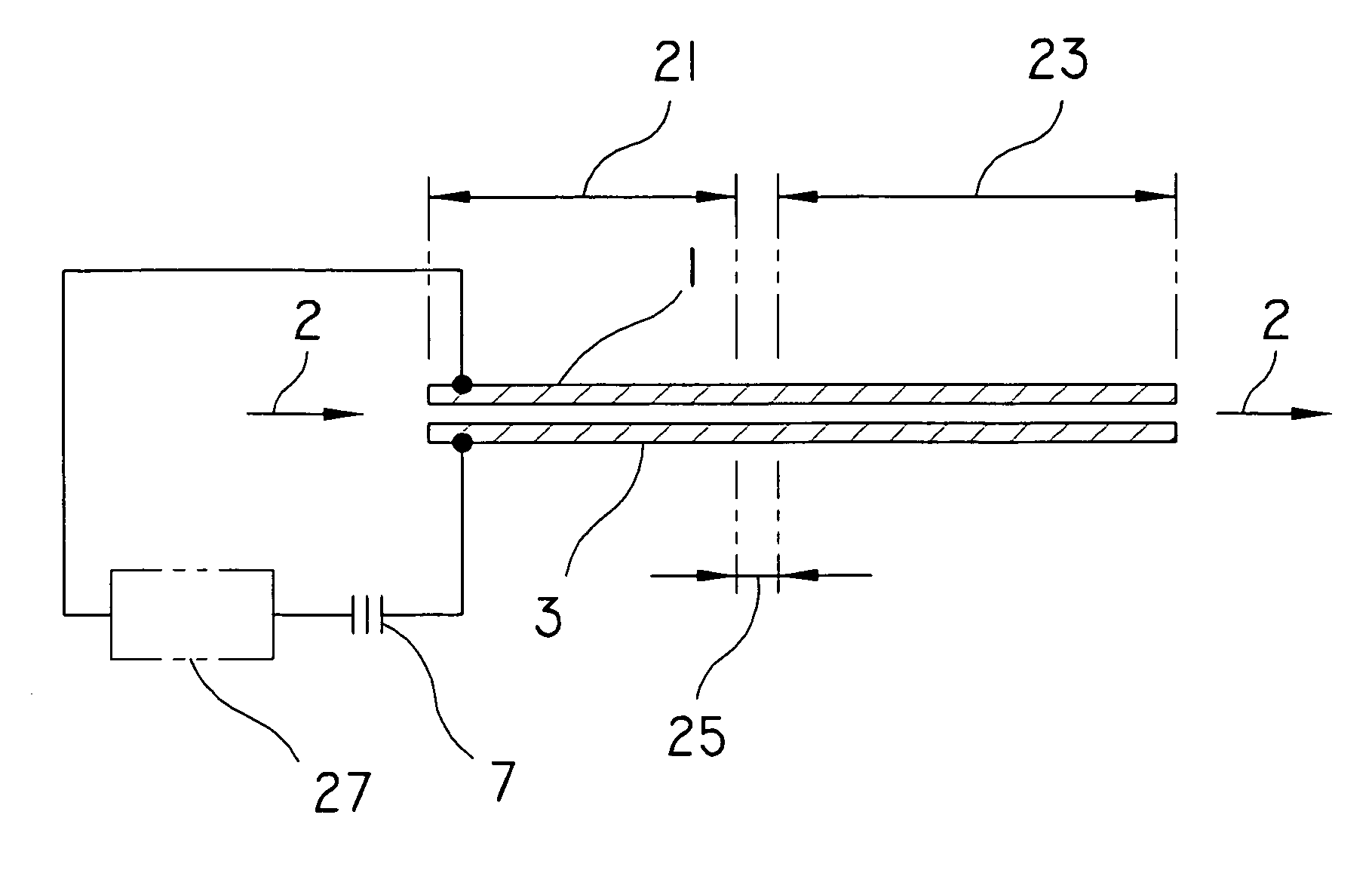

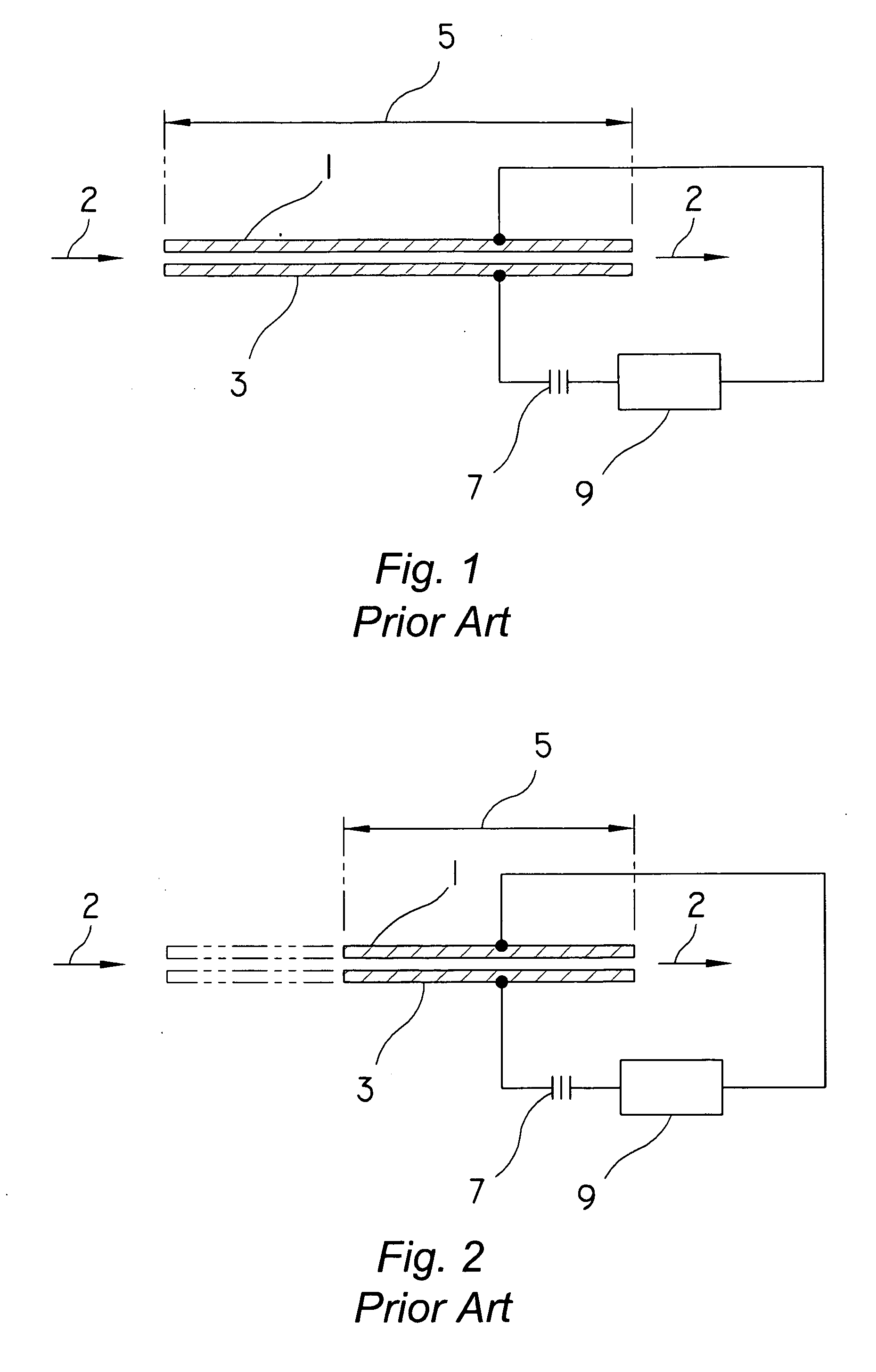

Instant water heater with PTC plastic conductive electrodes

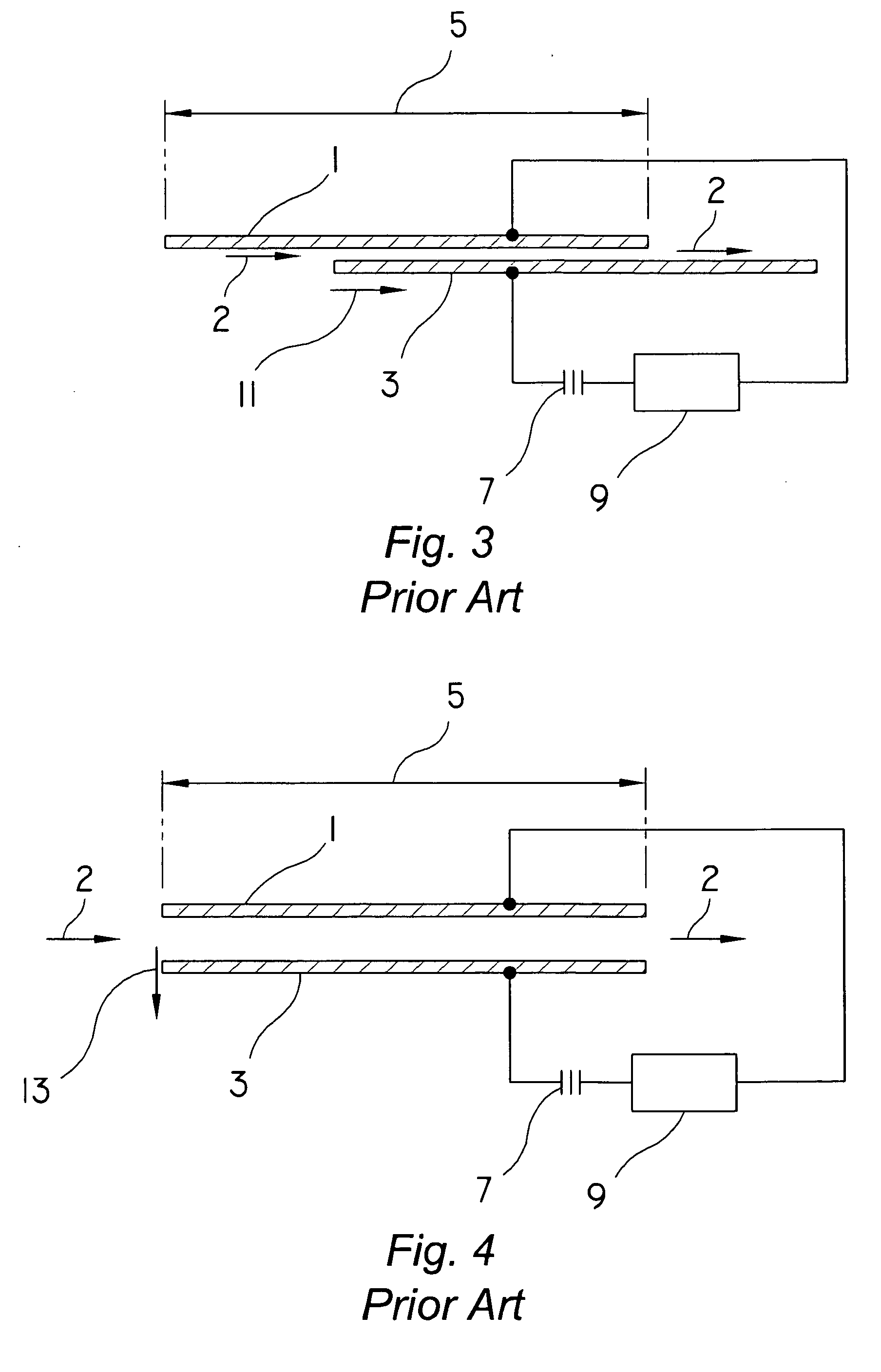

InactiveUS20060239664A1Lower bulk resistanceSuitable conductivitySteam generation heating methodsCooking vesselsEngineeringConductive materials

An instant water heater utilizing positive temperature coefficient plastic electrically conductive material structures for electrodes. The heating of the water is not generated by the electrodes, but instead by the resistance of the water to the electrical current flowing between them. The material of the electrodes undergoes a phase change at certain temperatures when whereby it converts from electrically conductive to electrically non-conductive at a predetermined temperature. The output temperature of the water is determined by a combination of the area of the electrodes that confront one another, the water's conductivity, the flow rate of the water and the current limiting capability of the conductive electrode materials positive temperature coefficient, which reduces or stops the heating of the water when the intended water temperature is achieved.

Owner:CHAPUT IVANHOE

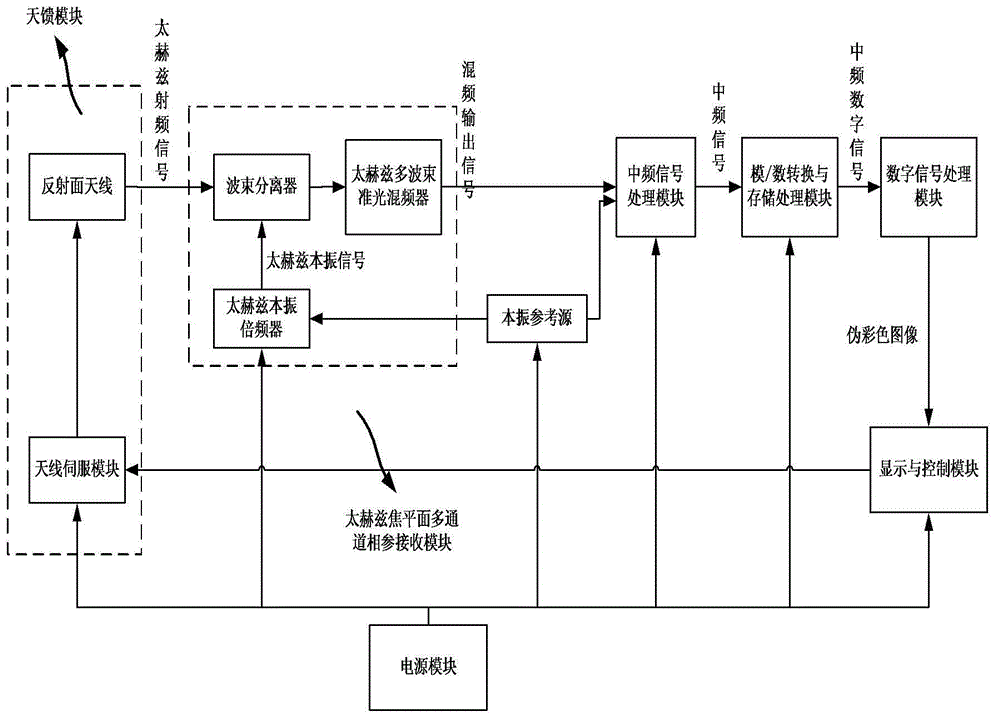

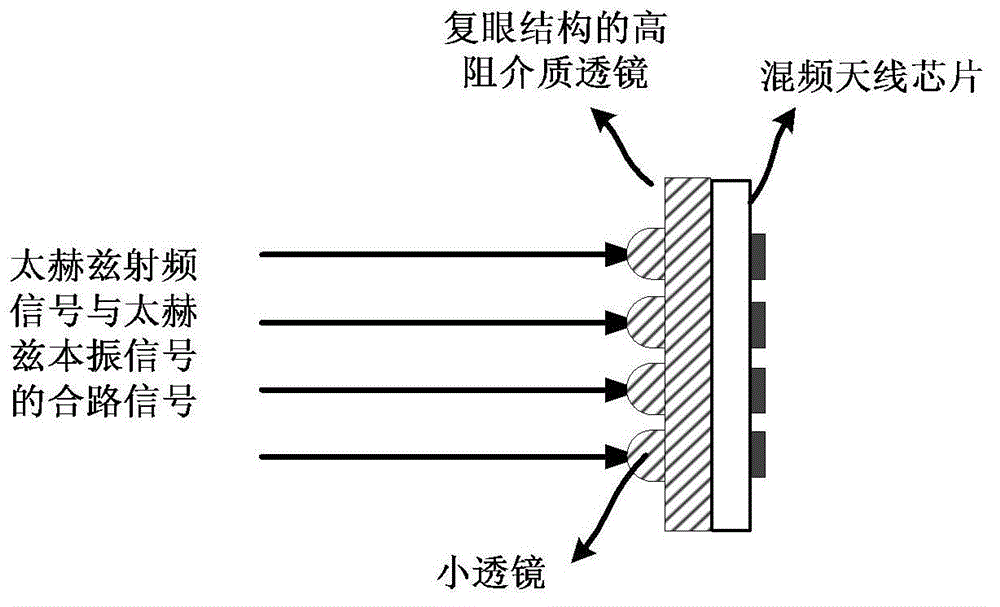

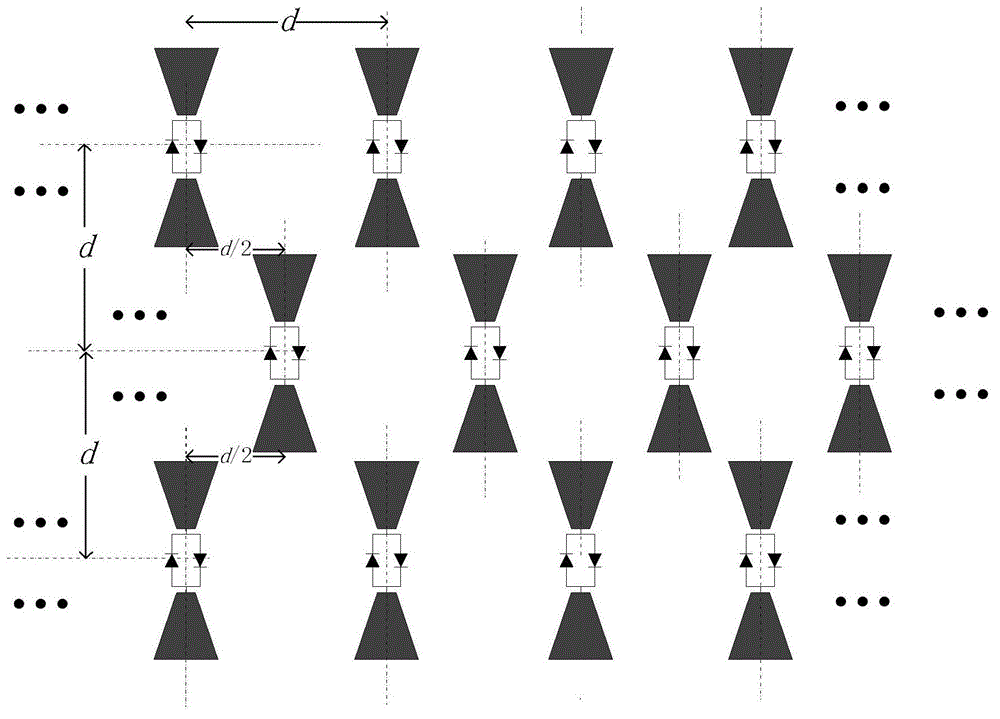

Portable terahertz passive type color camera

InactiveCN104038707AHighly integratedImprove machining accuracyTelevision system detailsAntenna arraysFrequency conversionImage resolution

Provided in the invention is a portable terahertz passive type color camera comprising a terahertz type multi-beam quasi-optical mixer having N1*N2 pixels. The terahertz type multi-beam quasi-optical mixer carries out frequency mixing on a received terahertz radio frequency signal and a terahertz type oscillator signal to generate N1*N2-path mixing output signals, wherein the N1 and N2 are natural numbers larger than or equal to 1; and each path of mixing output signal corresponds to one pixel. According to the invention, the terahertz type multi-beam quasi-optical mixer is used as the main receiving and frequency conversion element and the integration level is high; and the two-dimensional large-scale array can be realized well. The size of the whole receiving machine is small and the weight is light. The target identification capability can be improved in a complex background environment; and real-time imaging can be realized. The good resolution ratio and the high sensitivity are realized.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

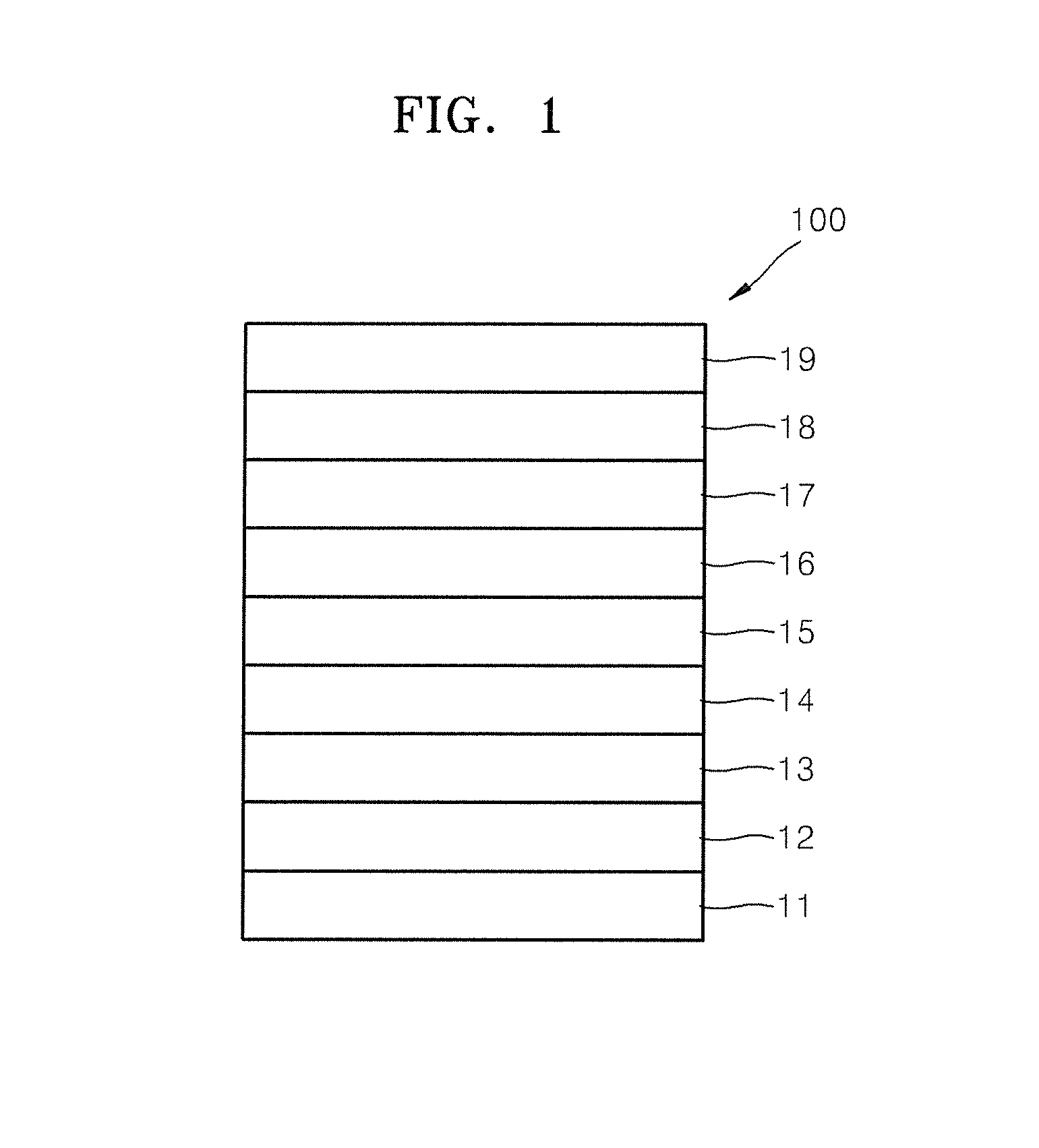

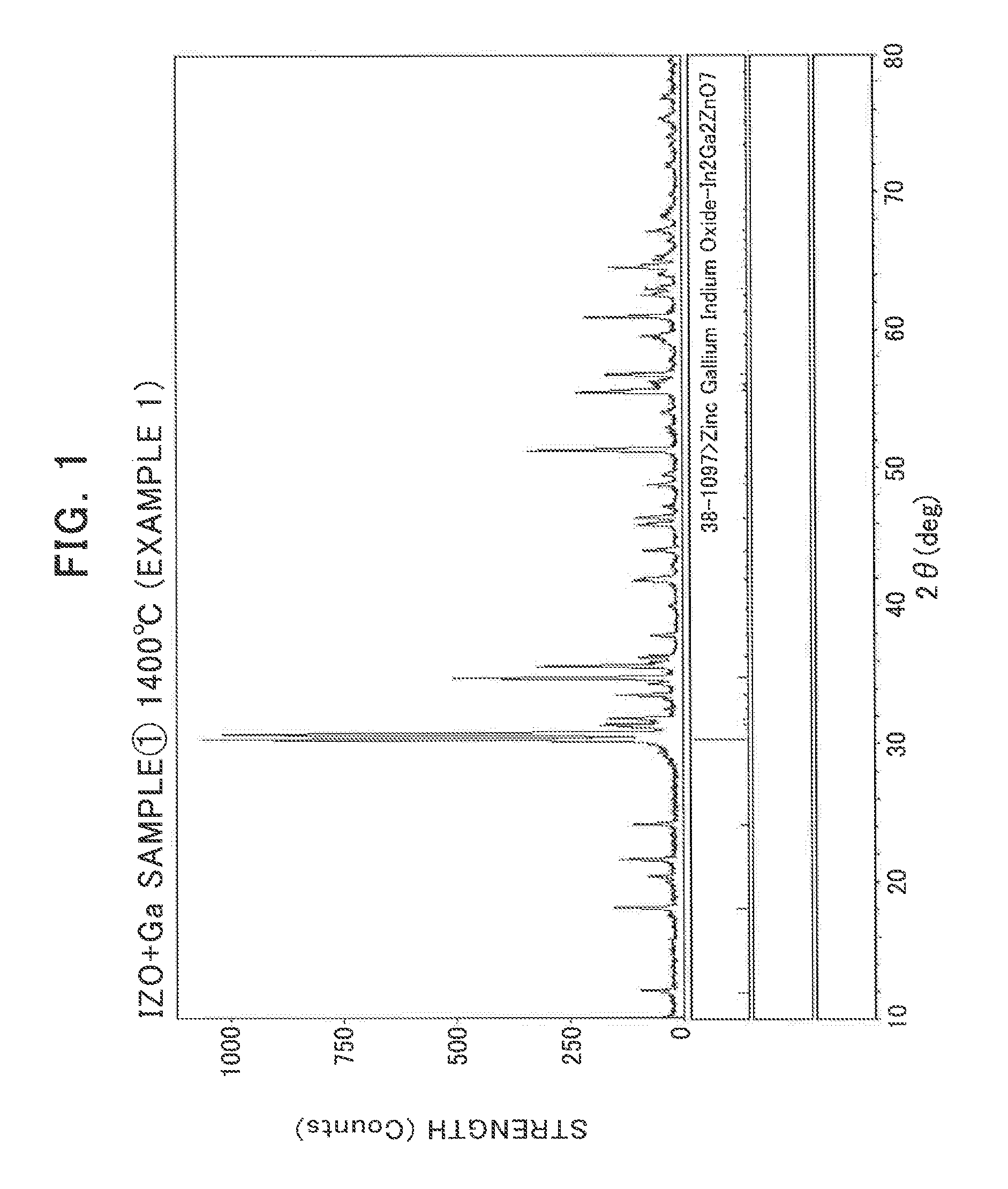

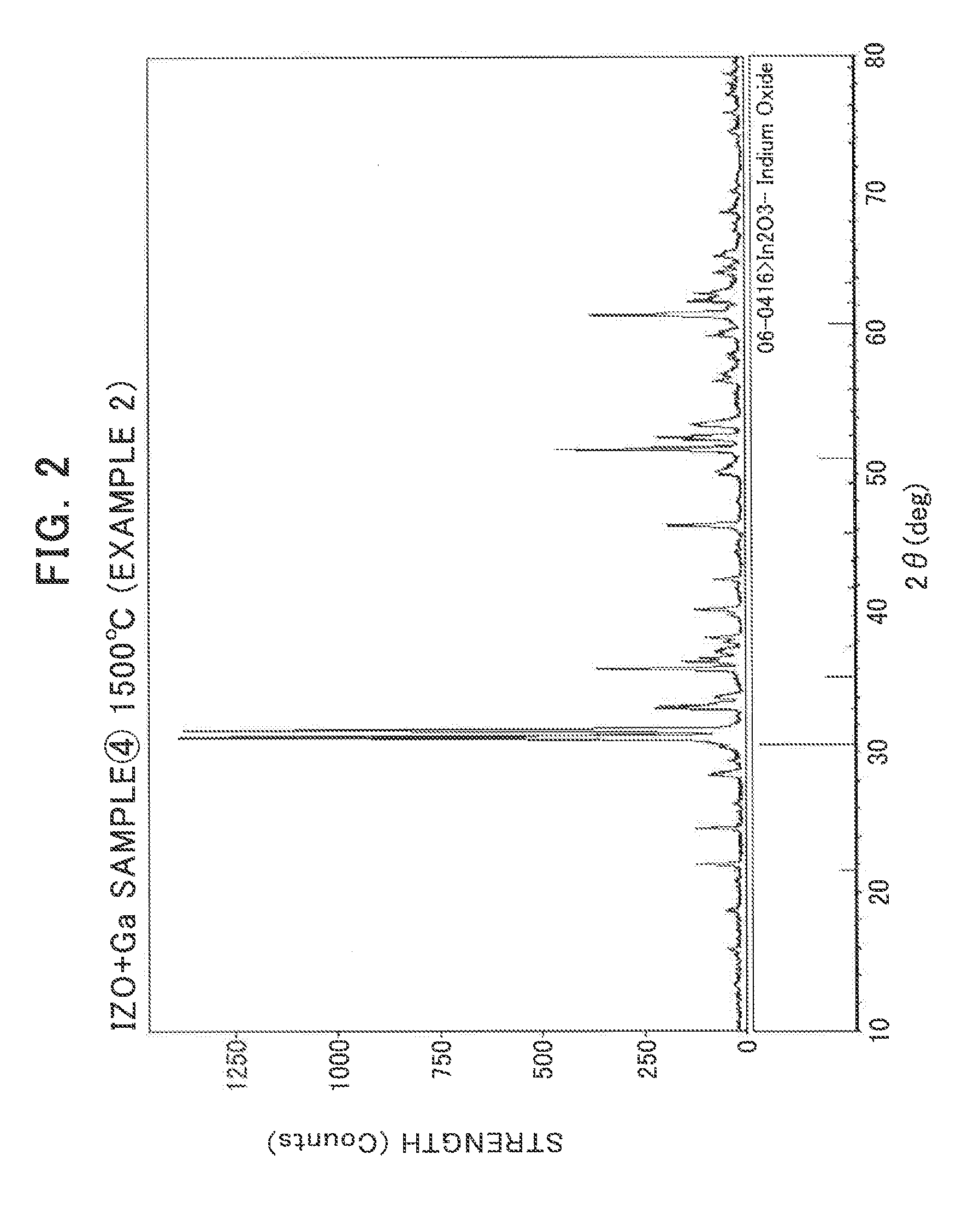

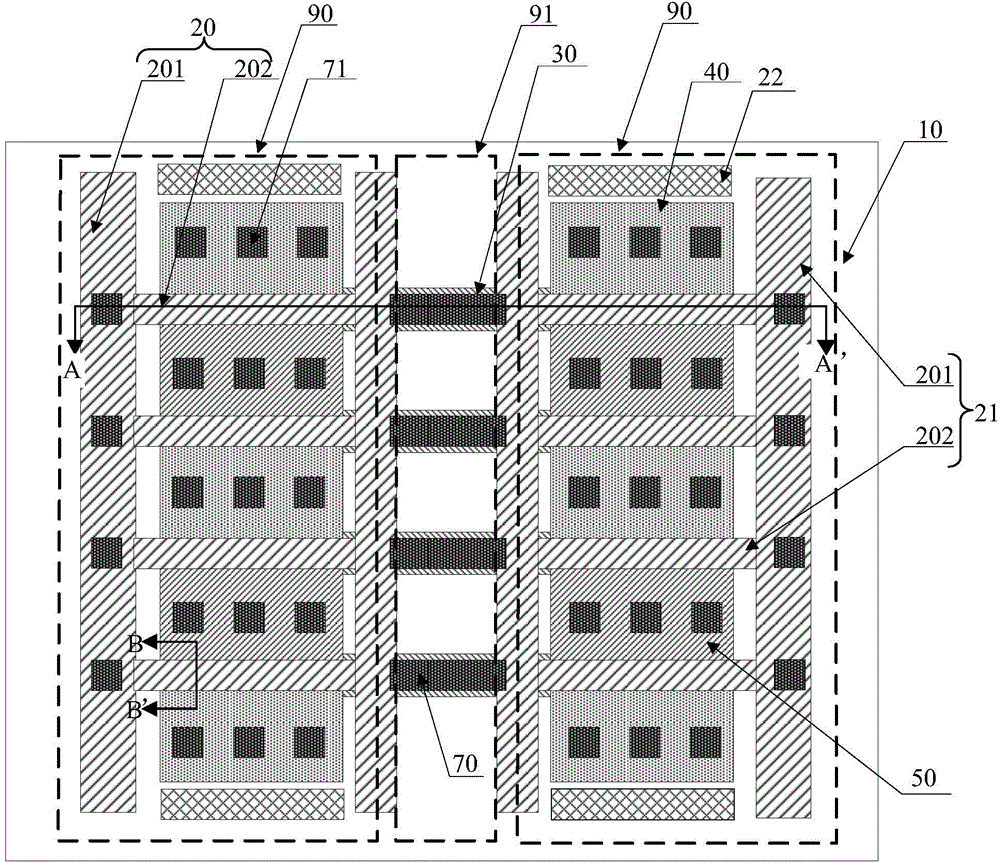

Sputtering Target for Oxide Thin Film and Process for Producing the Sputtering Target

Disclosed is a sputtering target that can suppress the occurrence of anomalous discharge in the formation of an oxide semiconductor film by sputtering method and can continuously and stably form a film. Also disclosed is an oxide for a sputtering target that has a rare earth oxide C-type crystal structure and has a surface free from white spots (a poor appearance such as concaves and convexes formed on the surface of the sputtering target). Further disclosed is an oxide sintered compact that has a bixbyite structure and contains indium oxide, gallium oxide, and zinc oxide. The composition amounts (atomic %) of indium (In), gallium (Ga), and zinc (Zn) fall within a composition range satisfying the following formula: In / (In+Ga+Zn)<0.75

Owner:IDEMITSU KOSAN CO LTD

SOI dynamic threshold transistor

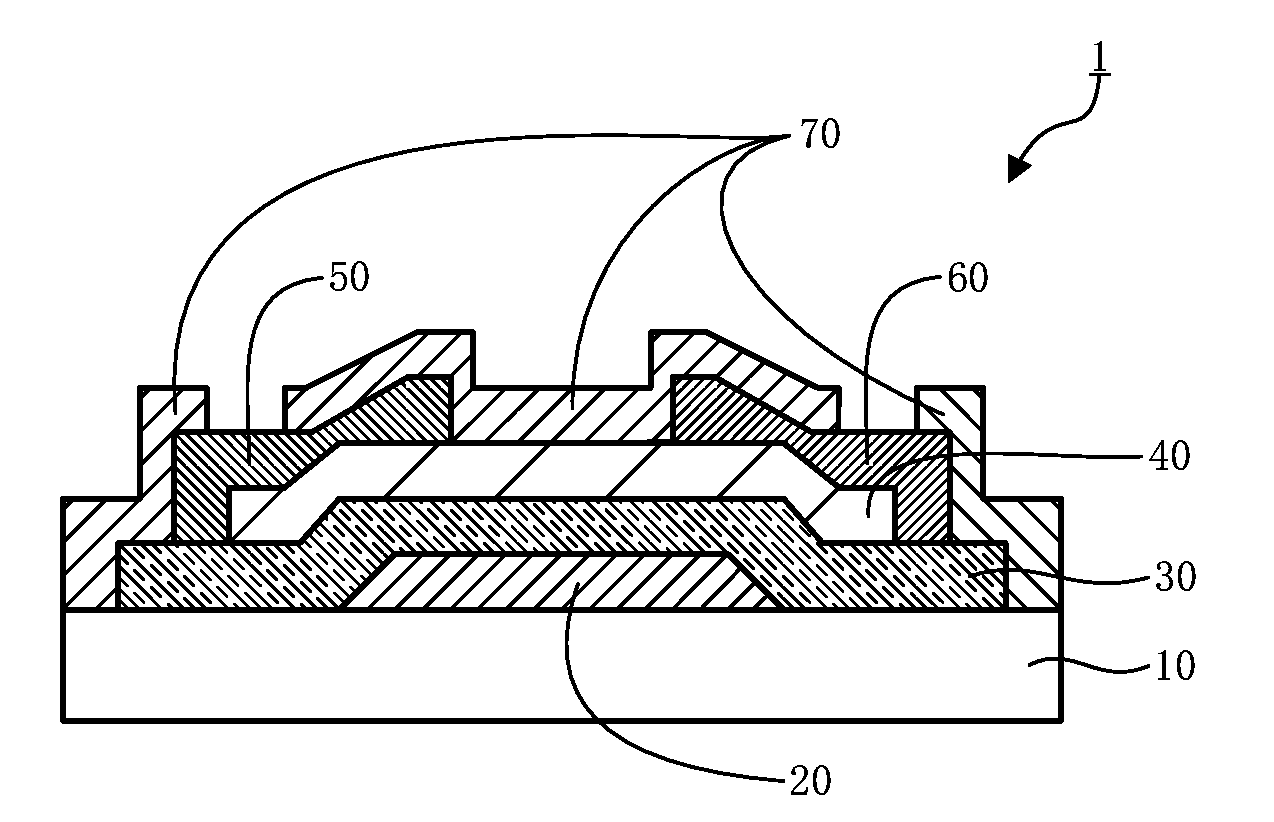

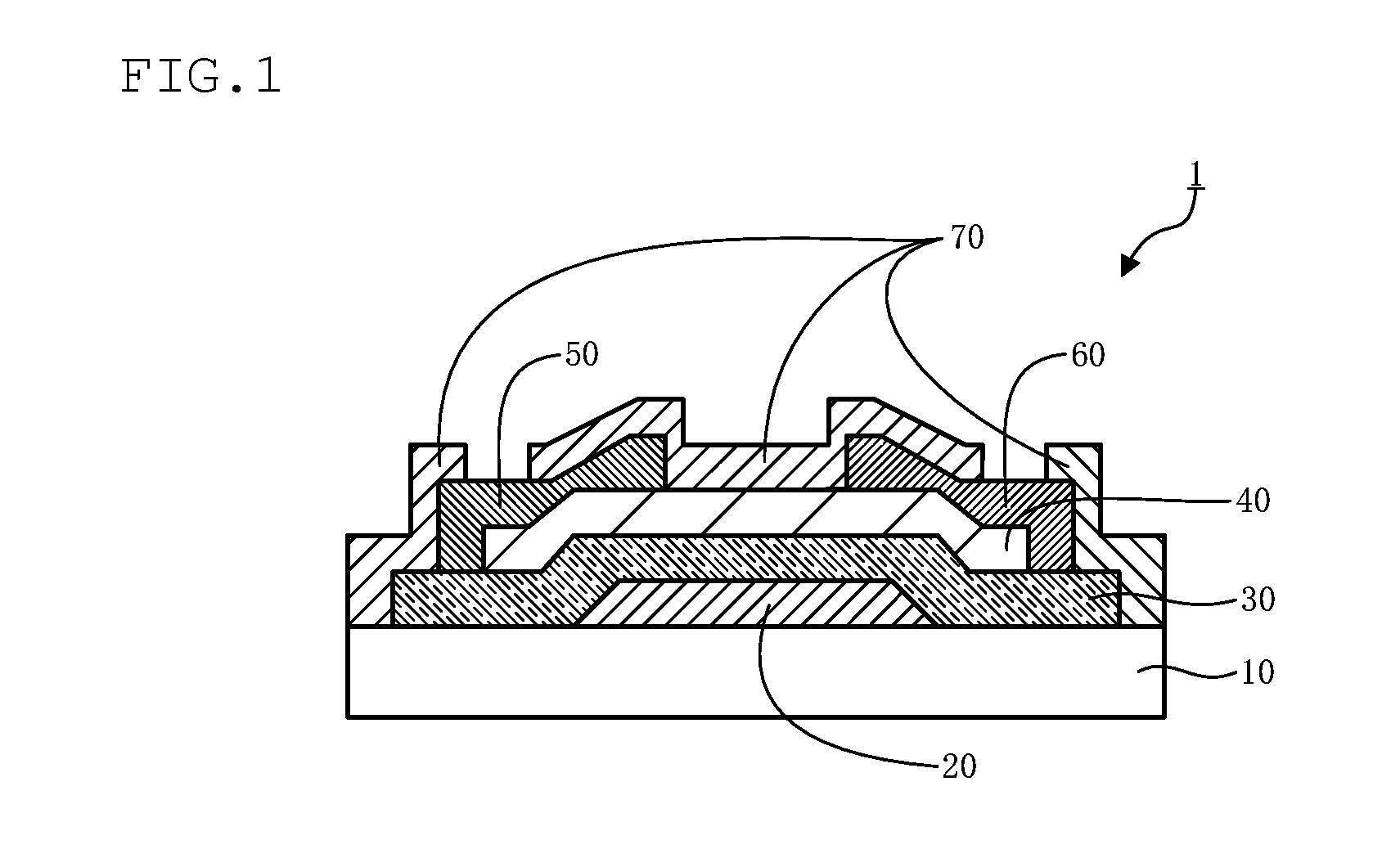

ActiveCN104362174AImprove RF performanceReduce areaSemiconductor devicesParasitic capacitorCapacitance

The invention provides an SOI dynamic threshold transistor which comprises a semiconductor substrate, a first multi-interdigital gate structure, a second multi-interdigital gate structure, a body contact region, a source region, a drain region and a first contact hole. A grid electrode is connected with the body contact region through the first contact hole. By the adoption of a body contact region sharing method, the utilization rate of the body contact region can be increased, and parasitic capacitance can be lowered; meanwhile, by the adoption of a multilateral connection mode, low gate resistance can be obtained. When a device is in a cut-off state, the threshold of the device is high, and the leaked current is low; when the device is in an on state, the threshold voltage of the device is lowered and the current is increased under the influence of the bulk effect. As a result, the device can have a steep sub-threshold slope and a large saturation current; meanwhile, the working voltage of the device is low, and the device is quite suitable for application at low power consumption. By the adoption of the design method, a parasitic resistor and a parasitic capacitor can be improved, and the SOI dynamic threshold transistor has certain application value in the radio frequency application field.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

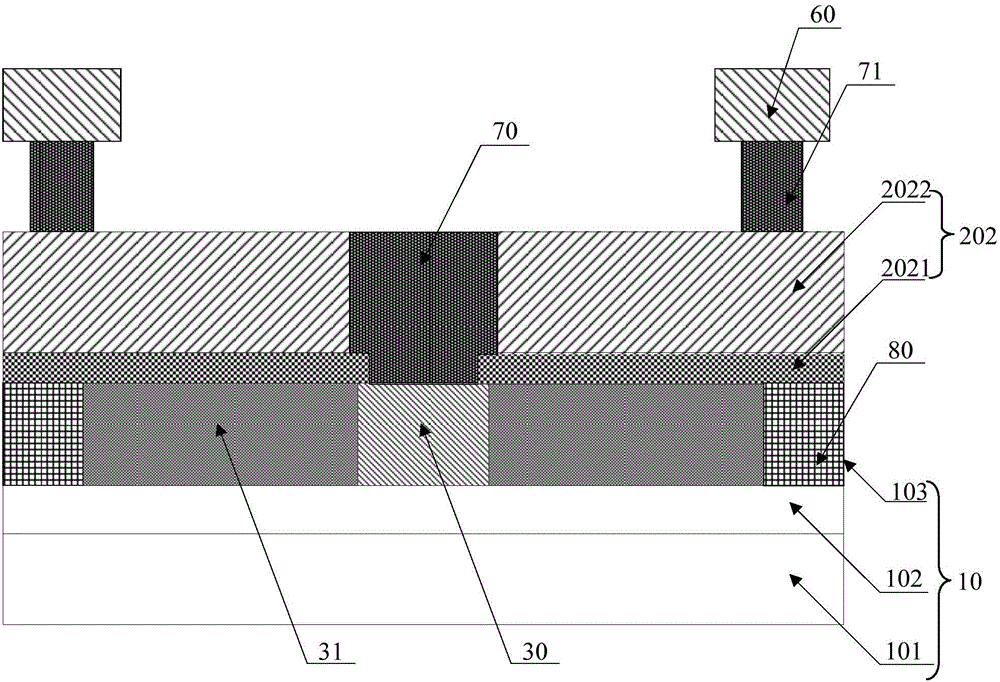

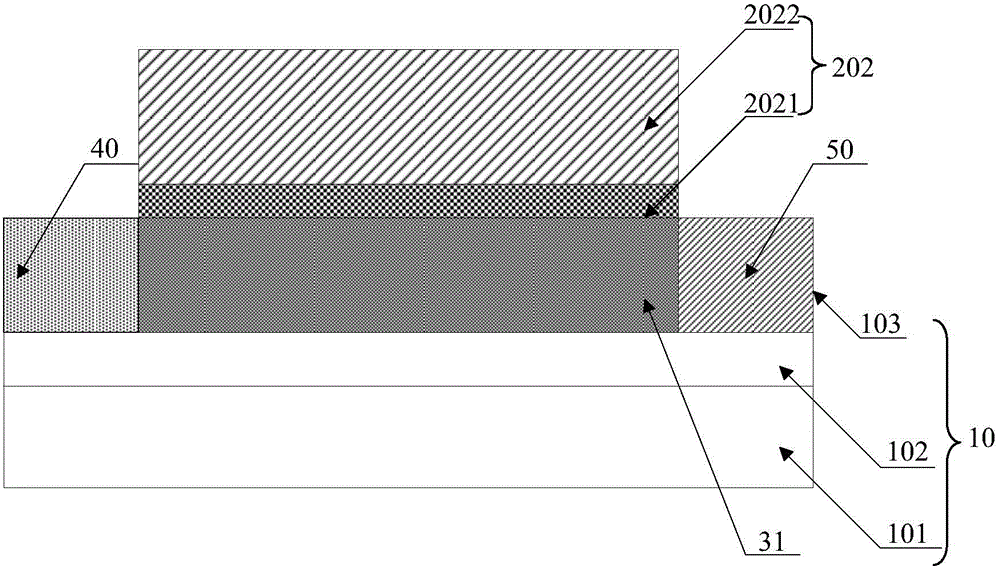

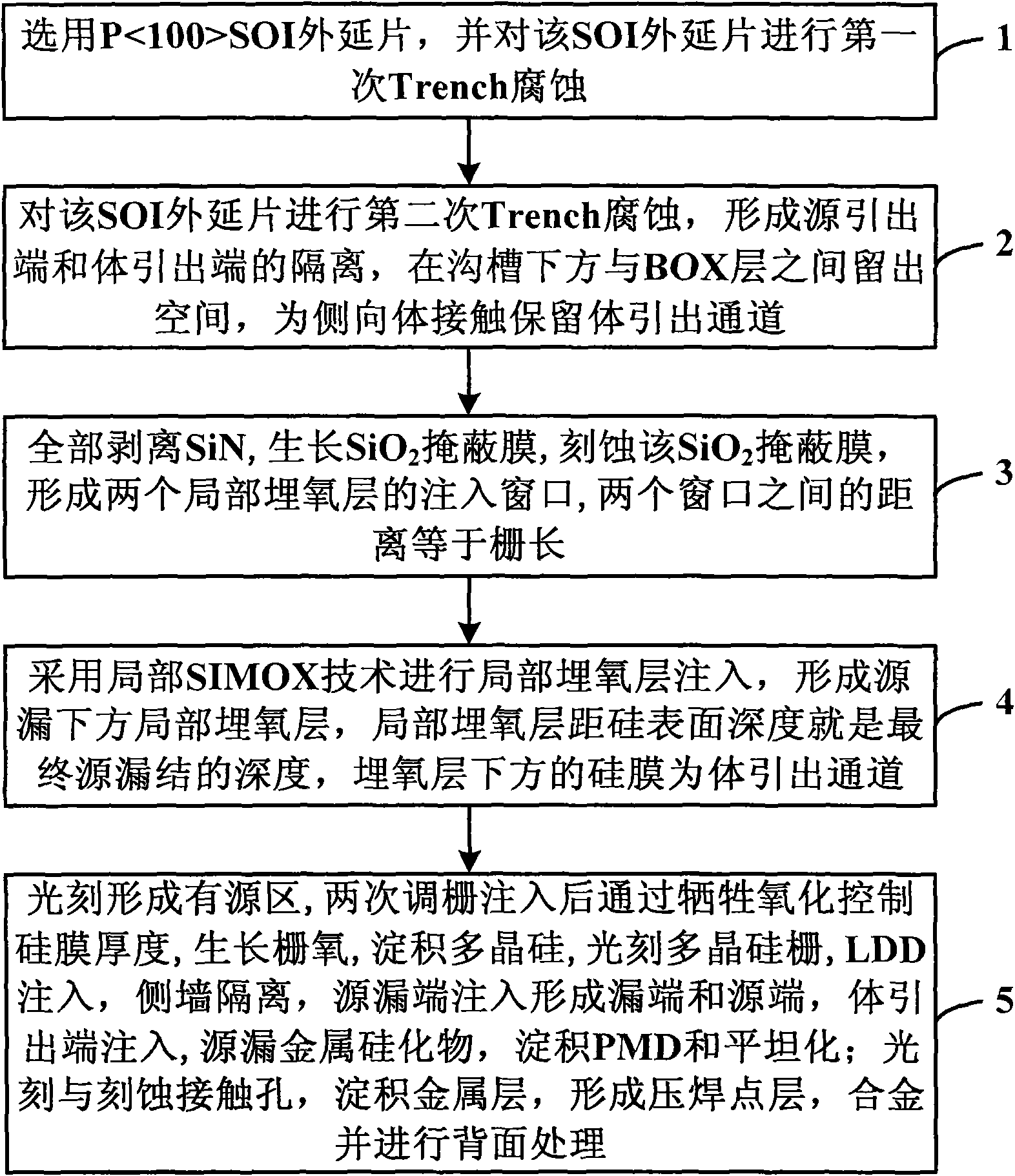

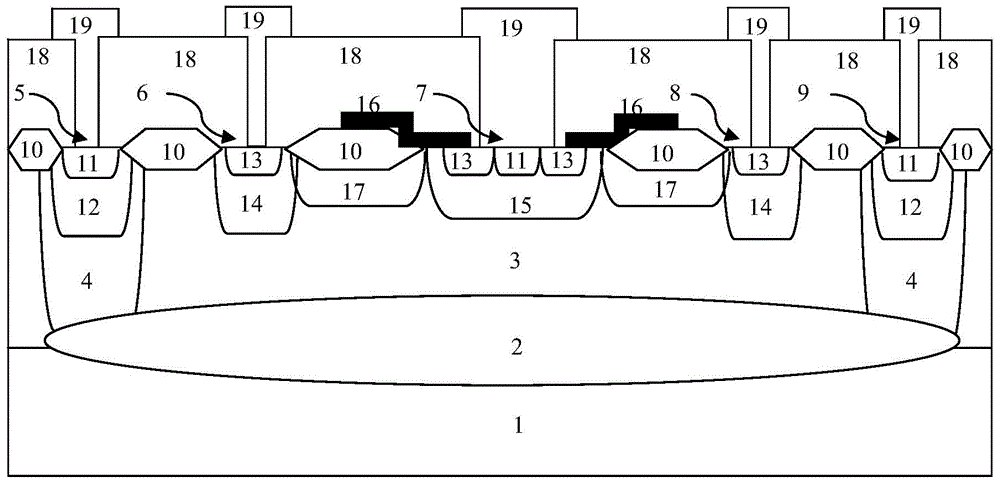

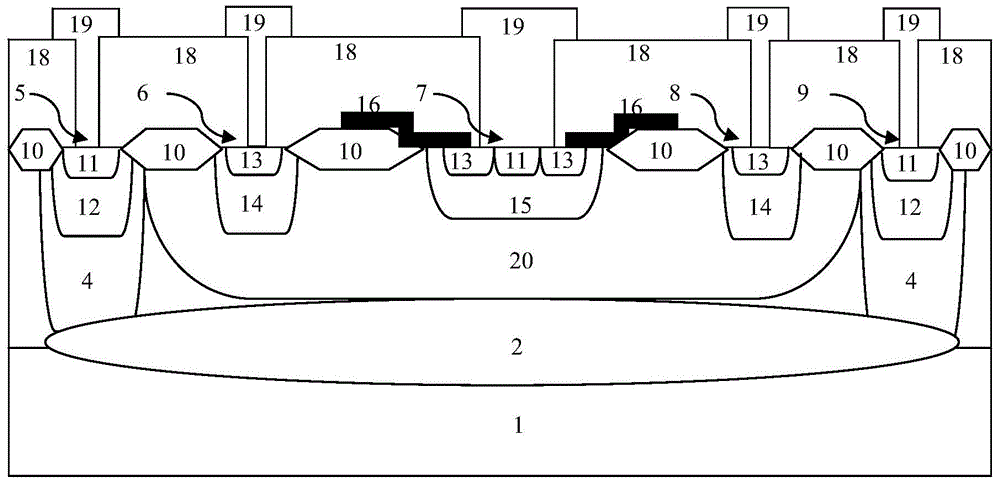

Method for manufacturing body-contact structure of partially depleted SOI MOSFET

ActiveCN101621009AReduce possession effectInhibition of possession effectSemiconductor/solid-state device manufacturingMOSFETBody contact

The invention discloses a method for manufacturing a body-contact structure of a partially depleted SOI MOSFET, which comprises the following steps: selecting a P<100>SOI epitaxial wafer and subjecting the SOI epitaxial wafer to primary Trench corrosion; performing secondary Trench corrosion to form an isolation layer between a source leading-out end and a body leading-out end and preserving a space between the bottom of a trench and a BOX layer to preserve a body leading-out channel for lateral body contact; stripping SiN completely, growing a SiO2 mask film and etching the SiO2 mask film to form injection windows of two local buried oxide layers; injecting the local buried oxide layers to form local buried oxide layers under source and drain regions; forming an active region by photoetching, performing tuned grid injection twice, controlling the thickness of a silicon film by sacrificial oxidation, growing gate oxide, depositing polysilicon, etching a polysilicon gate, performing LDD injection and side wall isolation, performing source and drain end injection to form a drain end and a source end, performing body leading-out end injection, growing source and drain silicide and performing PMD and planarization; and photoetching and etching contact holes, depositing a metal layer to form a pad layer and alloy, and performing back treatment.

Owner:BEIJING ZHONGKE XINWEITE SCI & TECH DEV

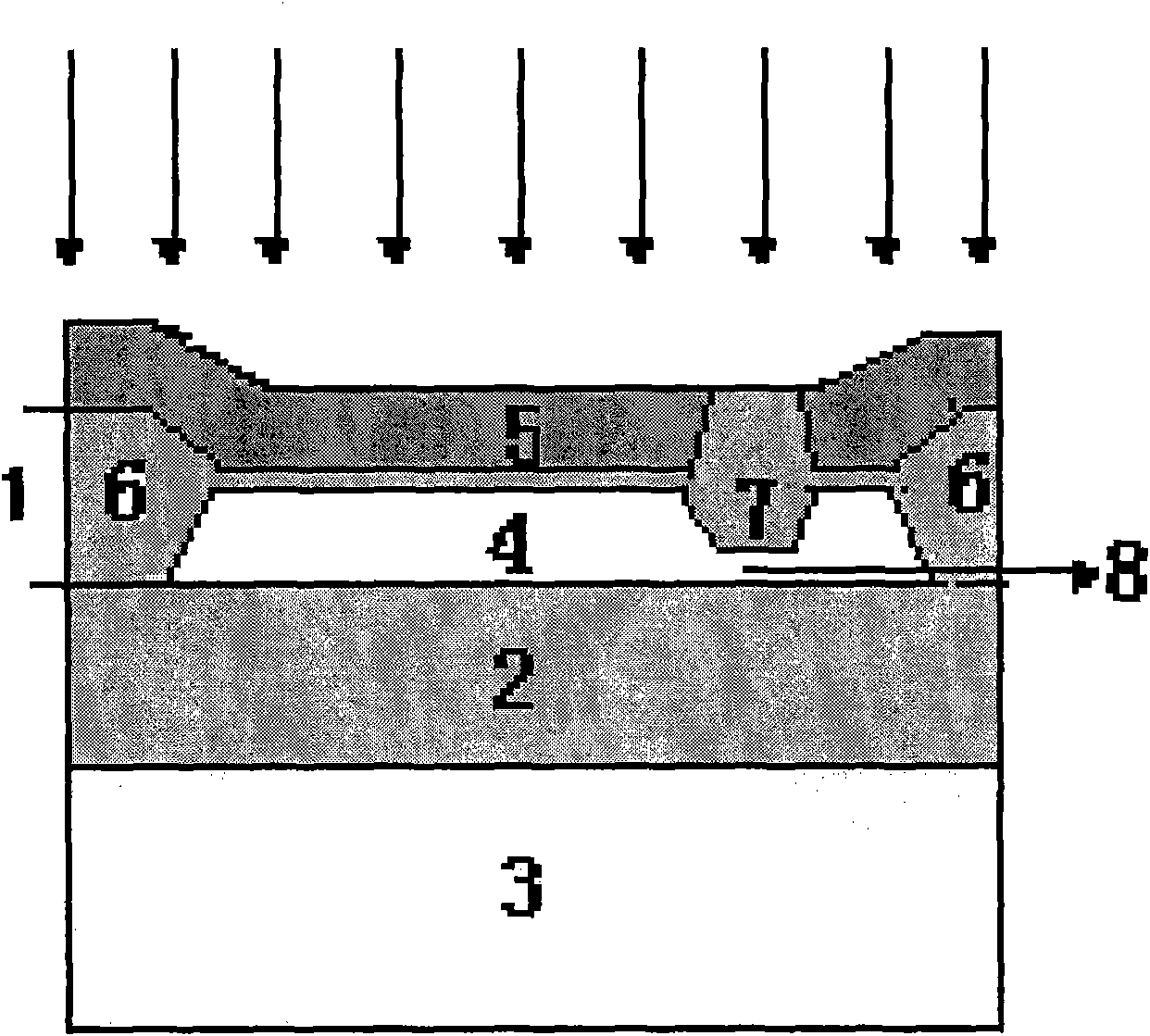

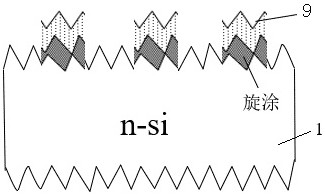

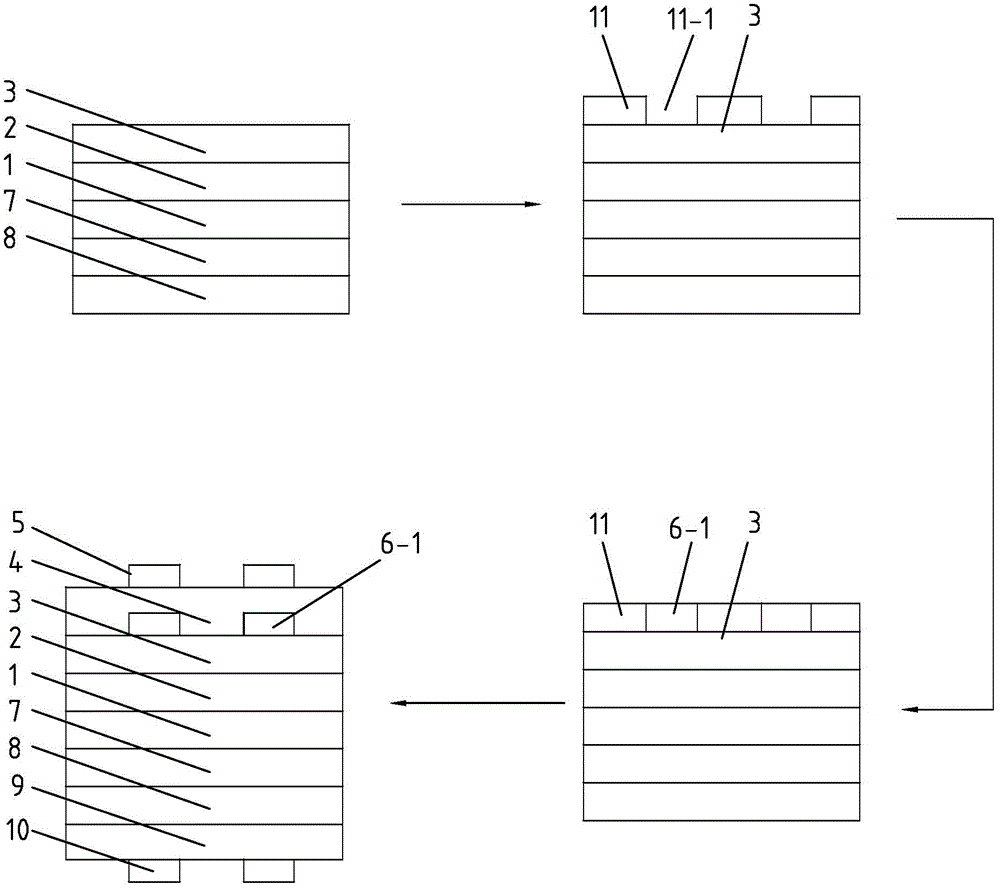

Manufacturing method of N-type TOPCon solar cell

ActiveCN111628047AReduce the amount of investmentAvoid damageFinal product manufacturePhotovoltaic energy generationPhysical chemistrySilicon oxide

The invention relates to a manufacturing method of an N-type TOPCon solar cell. The manufacturing method comprises the following steps: a, double-sided texturing; b, single-sided spin coating; c, single-sided oxidation: forming a boron-containing silicon oxide layer on a spin coating surface; d, forming a heavily doped region substrate and a lightly doped region substrate: forming an organic masklayer for protecting a heavily doped region at a position corresponding to the metal gate line by using a mask mode, completely removing the boron-containing silicon oxide layer and the boron source outside the coverage area of the organic mask layer by using HF, and then removing the organic mask layer; and e, heavy doping and light doping: specifically, completely pushing the spin-coated boron source into the silicon substrate through a tubular low-pressure diffusion method, forming a heavy doping region is formed, carrying out whole-surface source-through deposition to form a lightly dopedregion, and finally, carrying out high-temperature oxidation to form a BSG layer with the thickness of 80-100nm, and then carrying out normal subsequent processes. According to the invention, a boronselective emitter can obtain higher photoelectric conversion efficiency, so that the conversion efficiency of the solar cell is improved.

Owner:常州顺风太阳能科技有限公司

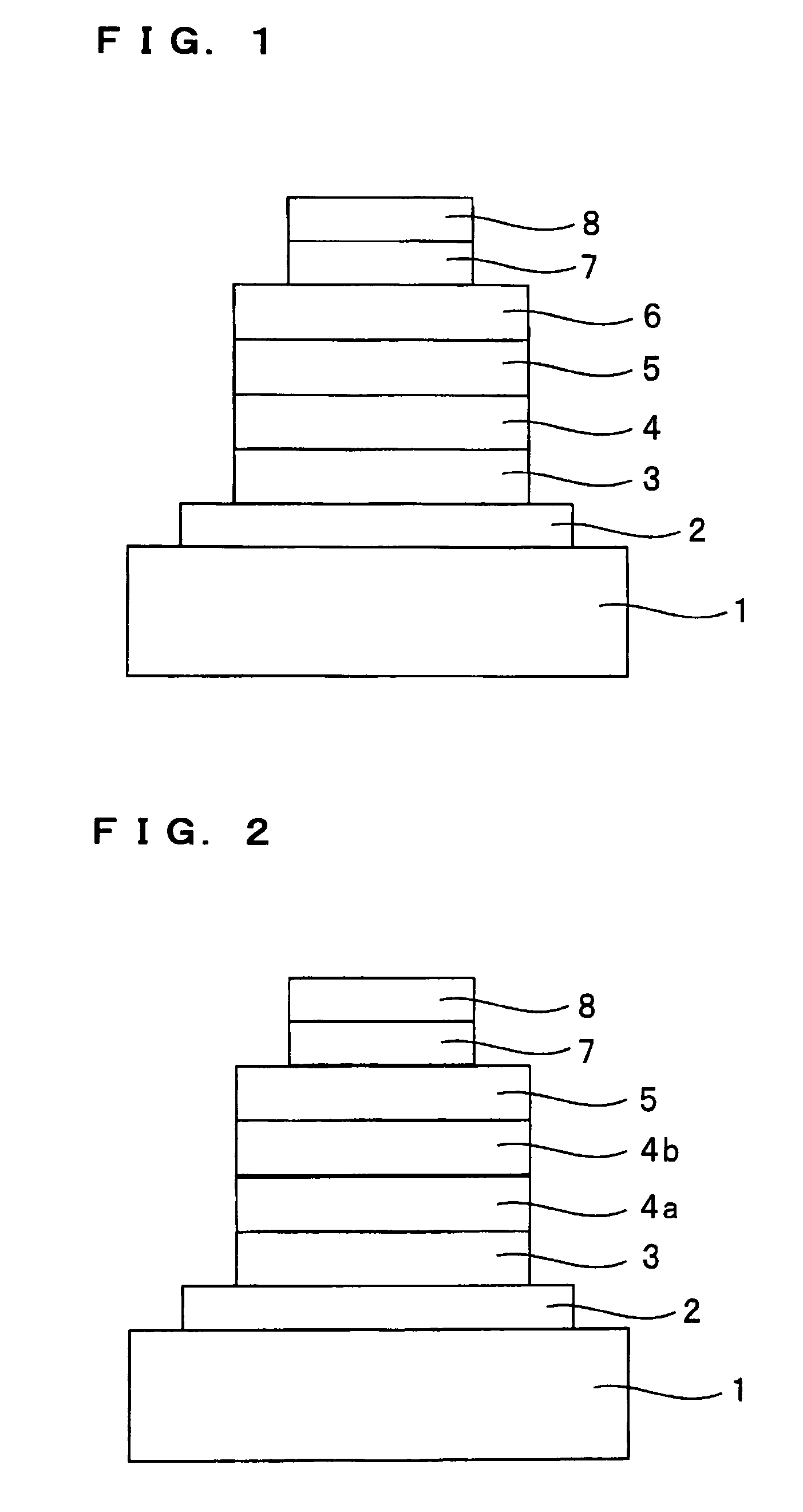

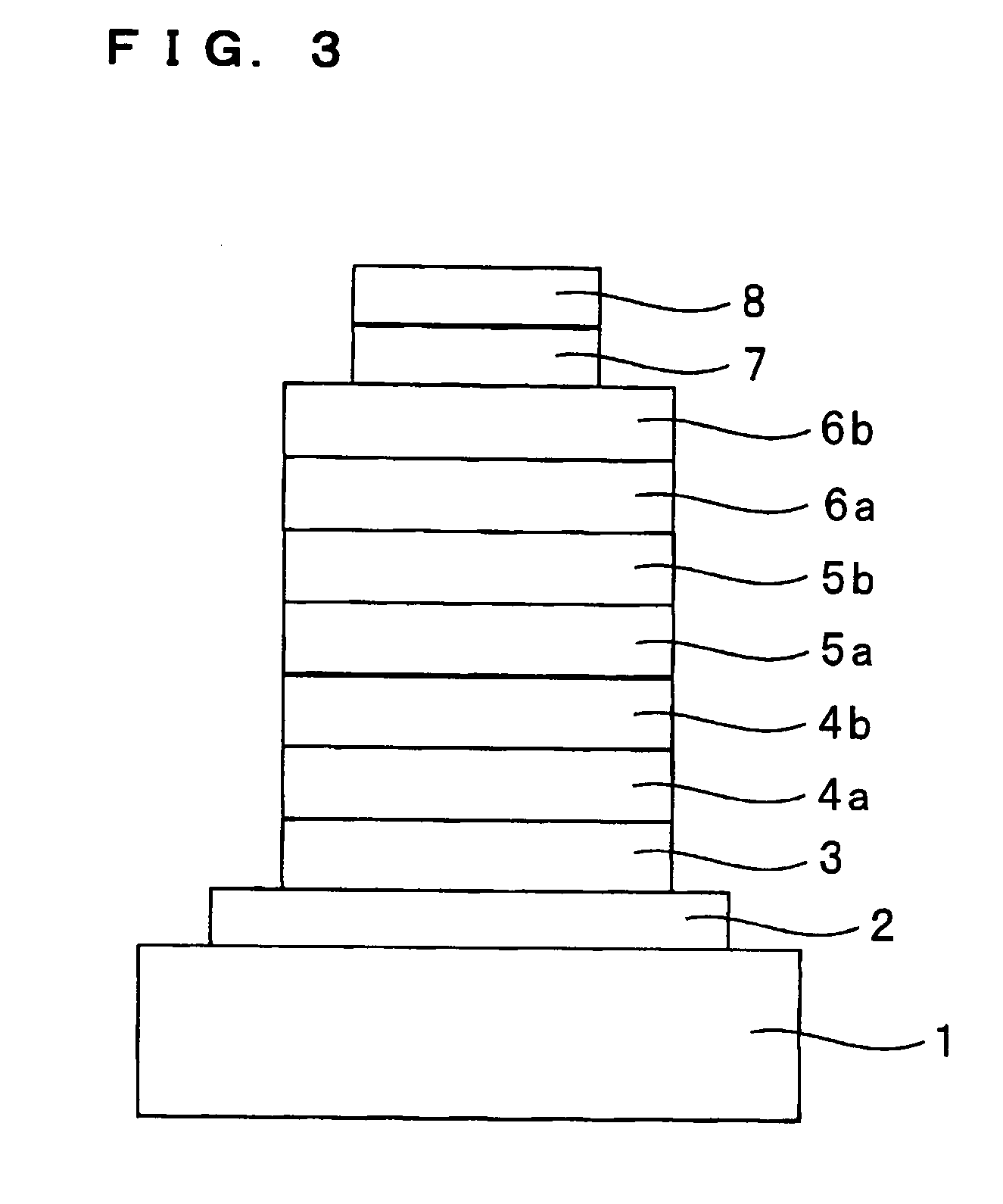

Hole transport material for organic electroluminescence devices and organic electroluminescence device using the same

InactiveUS20070009761A1Reduce resistanceImprove conductivityDischarge tube luminescnet screensElectroluminescent light sourcesCompound (substance)Thiophene derivatives

A hole transport material for organic electroluminescence devices, characterized by consisting of a copolymer having a first unit consisting of a heterocyclic compound containing a sulfur atom and a second unit consisting of a secondary or tertiary amine compound, wherein the above-mentioned hole transport material preferably further includes a third unit having a conjugated structure, preferably uses a thiophene derivative as the heterocyclic compound of the first unit, preferably uses a diphenylamine derivative and a triphenylamine derivative as the secondary or tertiary amine compound of the second unit, and includes a structure of a fluorene derivative or a structure of a phenylene derivative as the third unit, and an organic electroluminescence device using the same.

Owner:SANYO ELECTRIC CO LTD

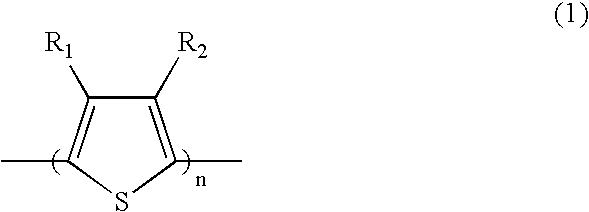

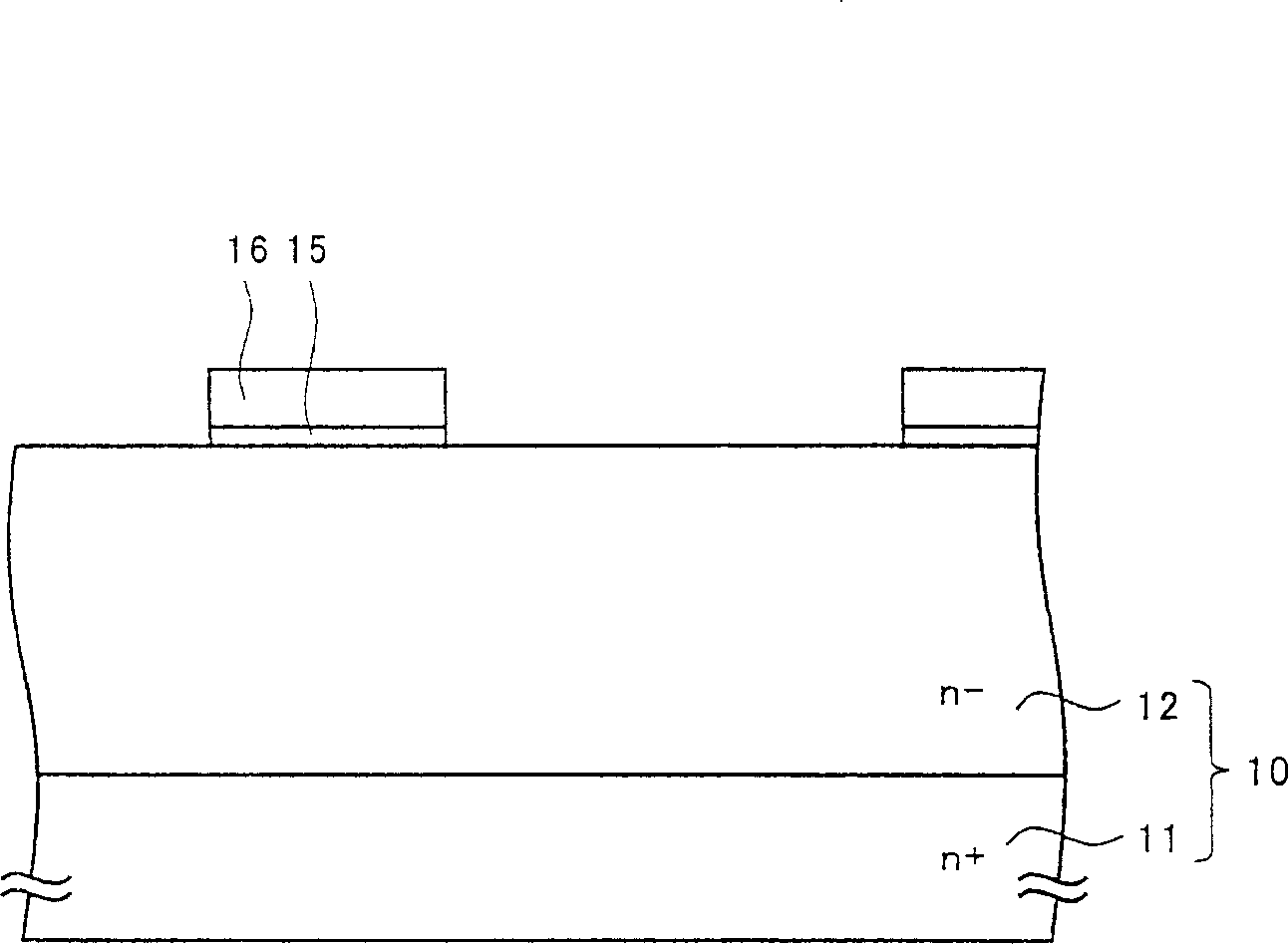

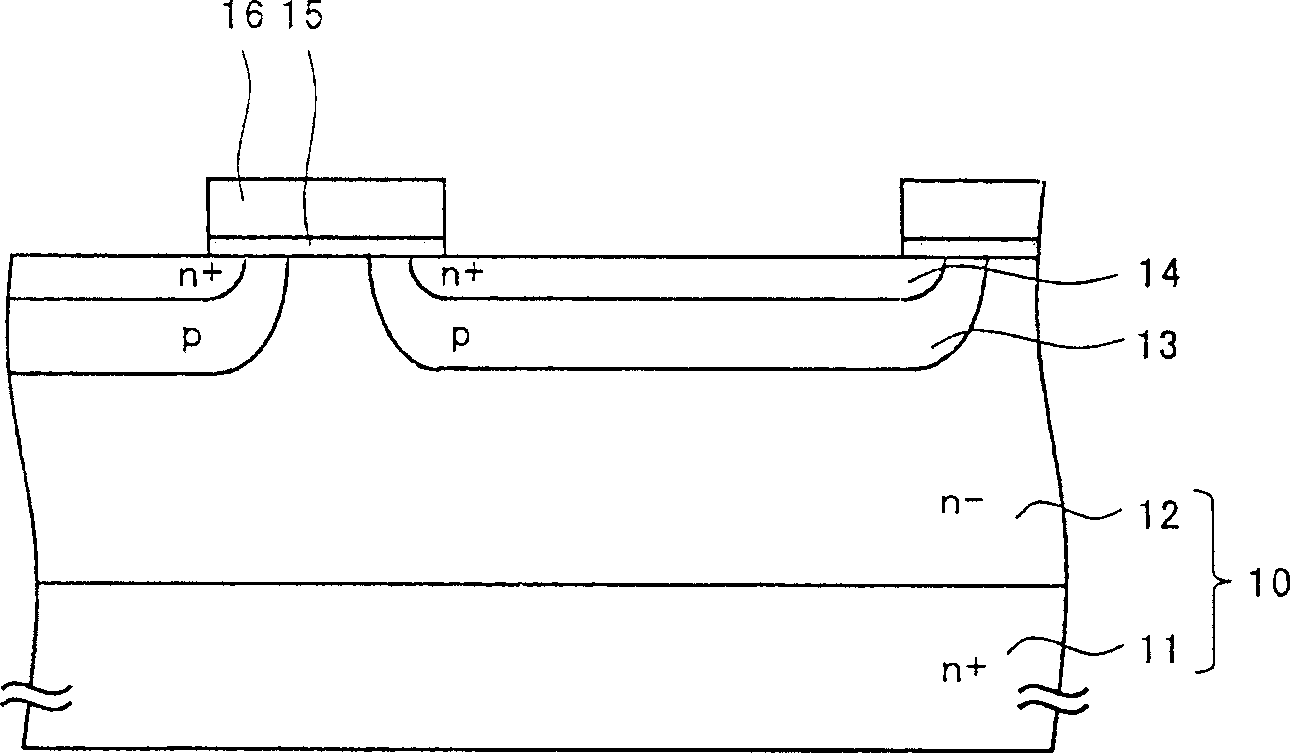

Semiconductor device manufacturing method thereof

InactiveCN1677687AShort reverse recovery timeImprove efficiencyTransistorSolid-state devicesMOSFETSchottky barrier

The invention solves the problem that a device becomes large in size and the number of components increases because a Schottky barrier diode is provided externally, in the case that the MOSFET includes a parasitic pn diode between the source and drain for use as Fast Recovery Diode (FRD), and a pn junction diode becomes a factor for preventing high speed switching operation and low power consumption. A groove is provided through a channel layer between adjacent gate electrodes of the MOSFET and a Schottky metal layer is also provided within the groove. Accordingly, since the bottom of groove is formed with the Schottky barrier diode, the Schottky barrier diode can be comprised within a diffusing region of the MOSFET. Cosequently, reduction in size of device and reduction in the number of components can be realized simultaneously.

Owner:SANYO ELECTRIC CO LTD

P type transverse double-dispersion MOS pipe capable of reducing conduction resistance

InactiveCN104617143AReduce areaLight concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSemiconductor

The invention discloses a P type transverse double-dispersion MOS pipe capable of reducing conduction resistance, and belongs to the technical field of semiconductor devices. The P type transverse double-dispersion MOS pipe capable of reducing conduction resistance comprises a P type substrate, an N embedded layer, a P type epitaxial layer, a first active area, a second active area, a third active area, a fourth active area, a fifth active area, field areas arranged between the active areas, a deep N trap, a shallow P trap, an N+ injection diffusion area, a shallow N trap, P+ injection diffusion area, and a P type injection layer which is between the shallow P trap and a back gate N trap area. With the adoption of the P type transverse double-dispersion MOS pipe, the conduction resistance is reduced while pressure resistance is ensured, and moreover, the area of a device is reduced.

Owner:WUXI YOUDA ELECTRONICS

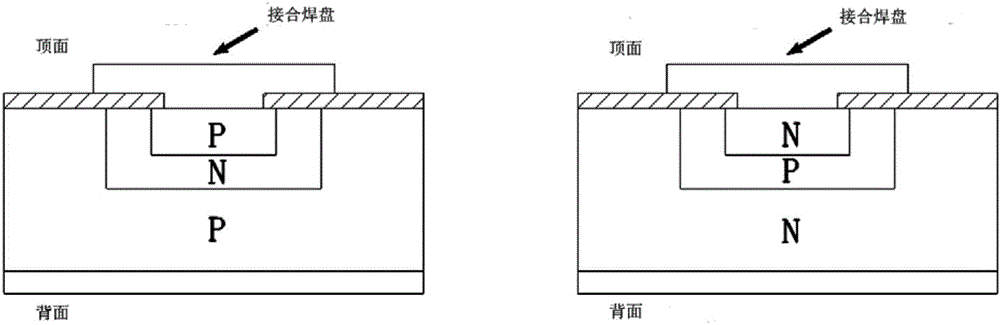

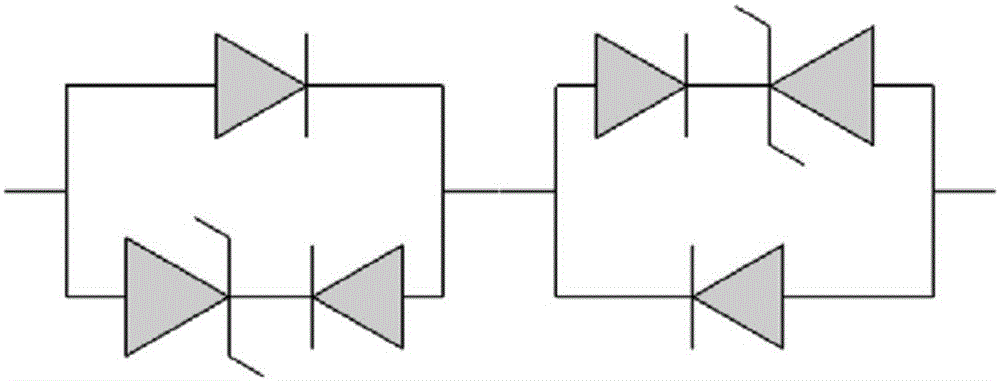

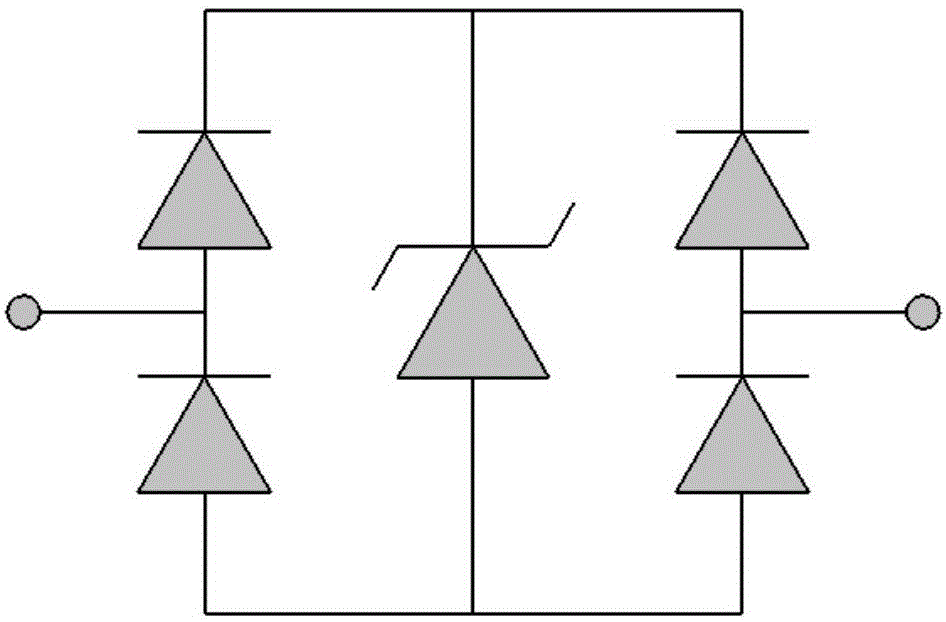

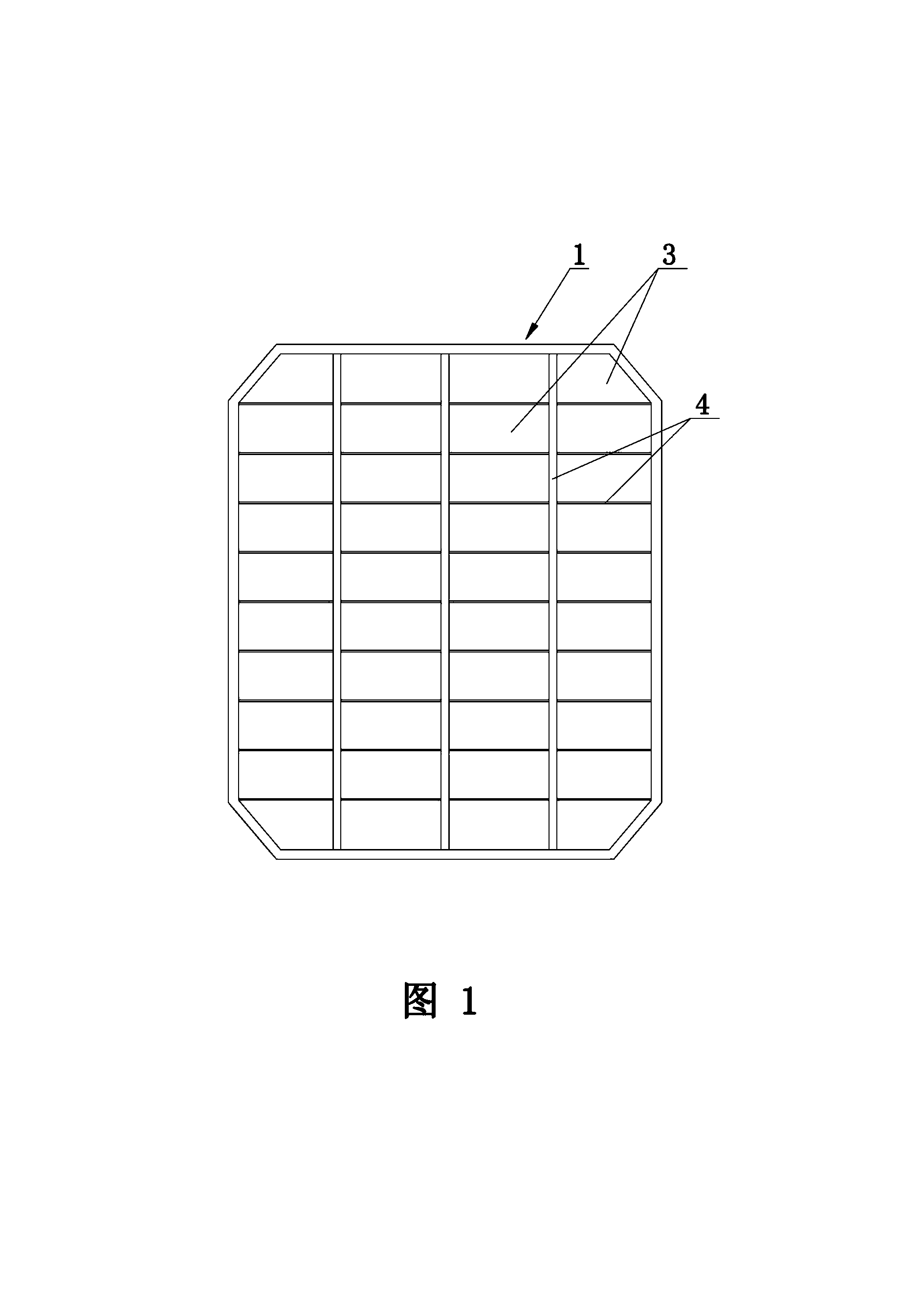

Two-way ultralow capacitance transient voltage suppressor and production method thereof

ActiveCN106158851AReduce packaging costsMeet application needsSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceTransient voltage suppressor

The invention relates to a two-way ultralow capacitance TVS (Transient Voltage Suppressor) and a production method thereof. The TVS comprises a semiconductor substrate of a first conductive type, a first epitaxial layer of a second conductive type, a third epitaxial layer of the first conductive type, a first buried layer of the second conductive type, a first doped region of the second conductive type, a second doped region of the first conductive type, a first groove, a second groove, a first insulating medium, a third groove and an active region, wherein the first buried layer is formed between the first epitaxial layer and the third epitaxial layer; the first doped region is formed by being opposite to the first buried layer in the third epitaxial layer; the second doped region is formed in the third epitaxial layer and is not opposite to the first buried layer; the first groove extends to the inside of the semiconductor substrate from the surface of the third epitaxial layer; the second groove extends from the surface of the third epitaxial layer and penetrates through the third epitaxial layer; the first groove and the second groove are filled with the first insulating medium; the third groove extends from the surface of the third epitaxial layer and penetrates through the first buried layer to the inside of the first epitaxial layer; the active region is formed by annealing in-situ polycrystalline silicon loaded in the third groove.

Owner:BEIJING YANDONG MICROELECTRONICS

Solar cell and method for producing grid line electrode of solar cell

ActiveCN102800763ALower bulk resistanceControl thicknessFinal product manufactureSemiconductor devicesEtchingLaser scribing

The invention discloses a solar cell and a method for producing a grid line electrode of the solar cell. The method for producing the grid line electrode is that a layer of transparent insulation material is coated or settled on a cell surface; the transparent insulation material on grid lines is removed through using a laser scribing method, a die pressing method, a dry / wet etching method and the like, and the grid lines are exposed; and a conducting material which is used as a grid line electrode is plated on the grid line through using a plating method. The method for producing the grid line electrode can form a circuit pattern of the grid line electrode at one time, so that the production efficiency is effectively improved, moreover, the production temperature can be indoor temperature, and the performance of a current generation body cannot be influenced; the method for producing the grid line electrode is relatively simple, does not have unnecessary steps, and the arranged transparent insulation material can well protect the cell, so that the product service life is prolonged; and the method for producing the grid line electrode can also relatively accurately control the thickness and the width of the grid line electrode, the material utilization rate is also high, and the production cost is relatively low.

Owner:福建钜能电力有限公司 +1

Method for preparing antistatic filter material with graphite powder

InactiveCN103272435AReduce static build-upLow surface and bulk resistanceFiltration separationFilter materialCoal dust

The invention discloses a method for preparing an antistatic filter material with graphite powder. The method comprises the steps of preparing a plain felt, preparing a treatment agent: as for the plain felt steeped with the treatment agent, attaching nanoscale graphite powder onto the surface of the filter material in a spraying manner, drying: allowing the filter felt with the surface attached with the nanoscale graphite powder to enter an oven for preliminary drying and baking by the action of traction of the oven, drying the surface of the filter felt, removing redundant water in the filter felt, and obtaining the antistatic filter material. According to the method, the nanoscale graphite powder is sprayed onto the filter material plain felt, so that low resistance is formed in and on the surface of the filter material, the electrostatic accumulation of the filter material during use can be reduced effectively, and the risks of deflagration and even explosion of flammable and explosive products such as coal dust and coal gas during filter due to electrostatic discharge and sparking are avoided.

Owner:南京际华三五二一环保科技有限公司

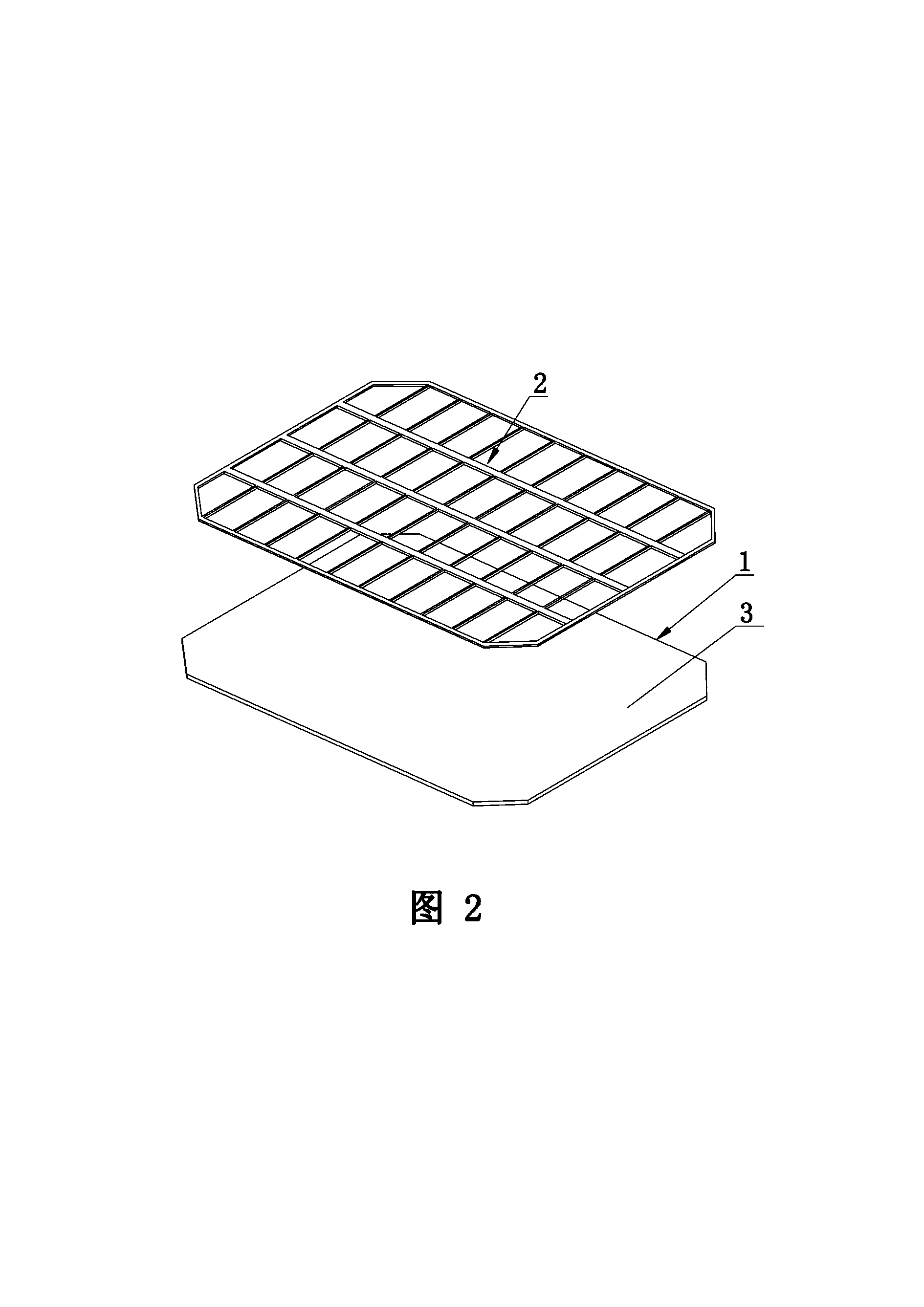

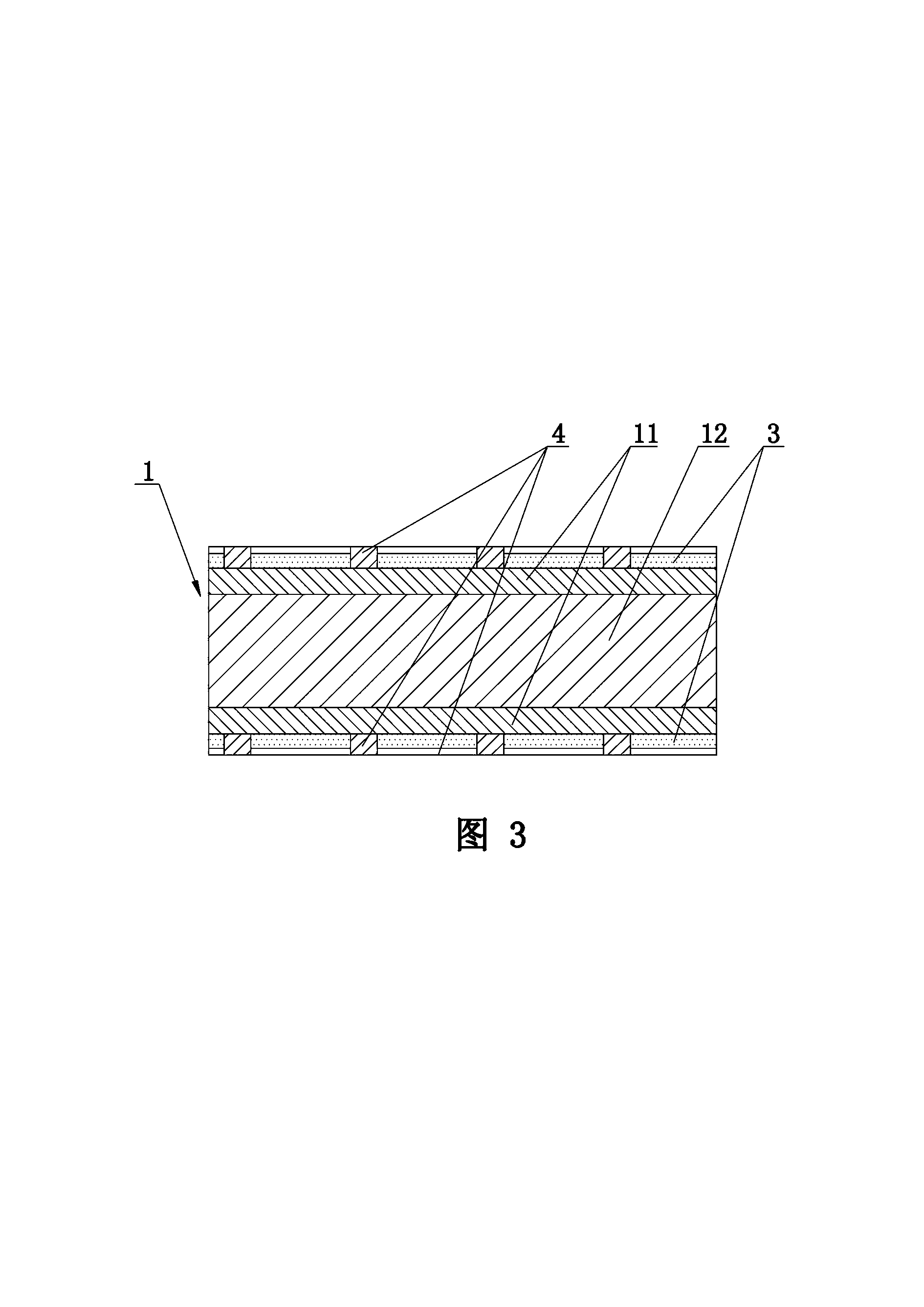

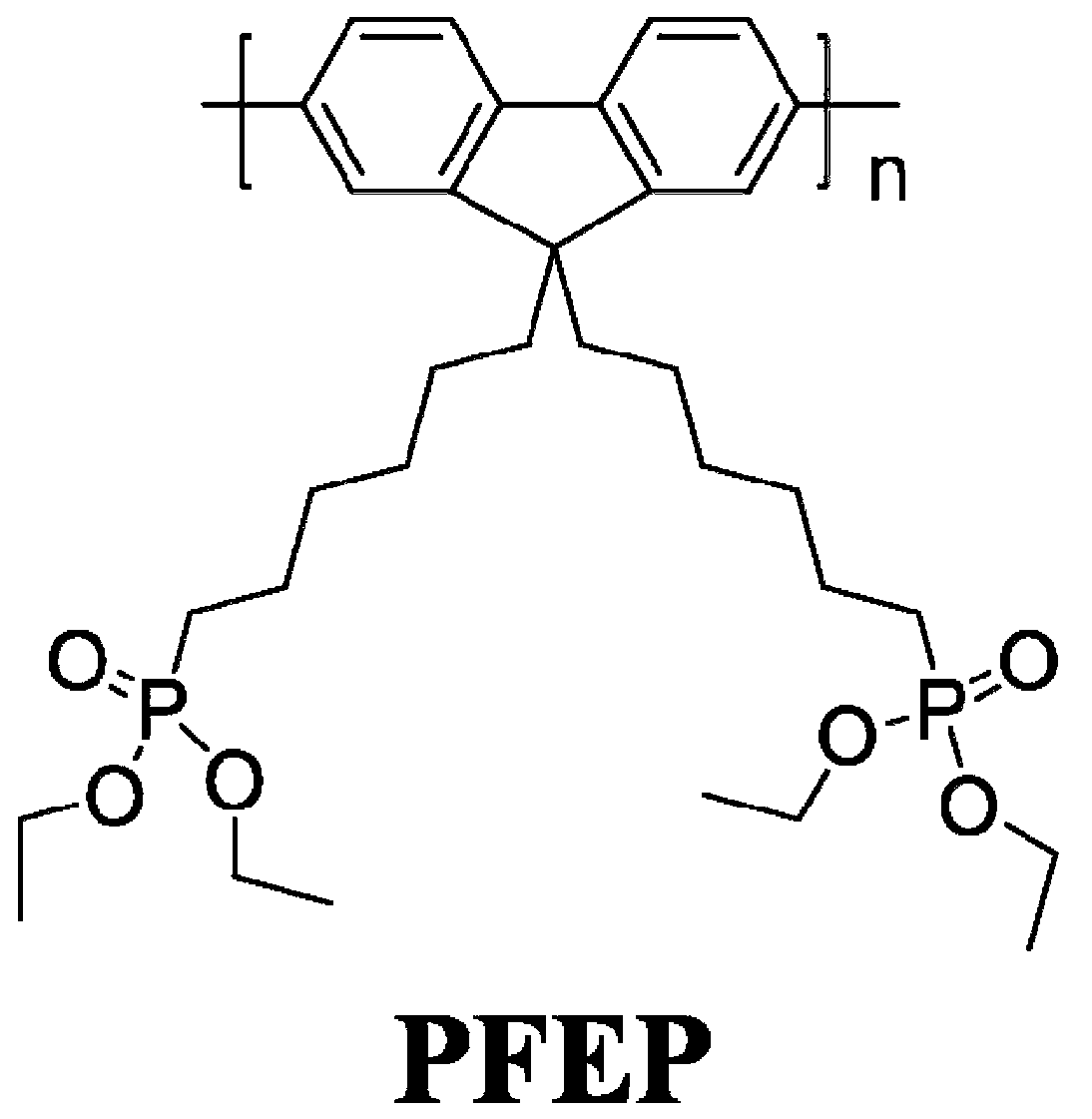

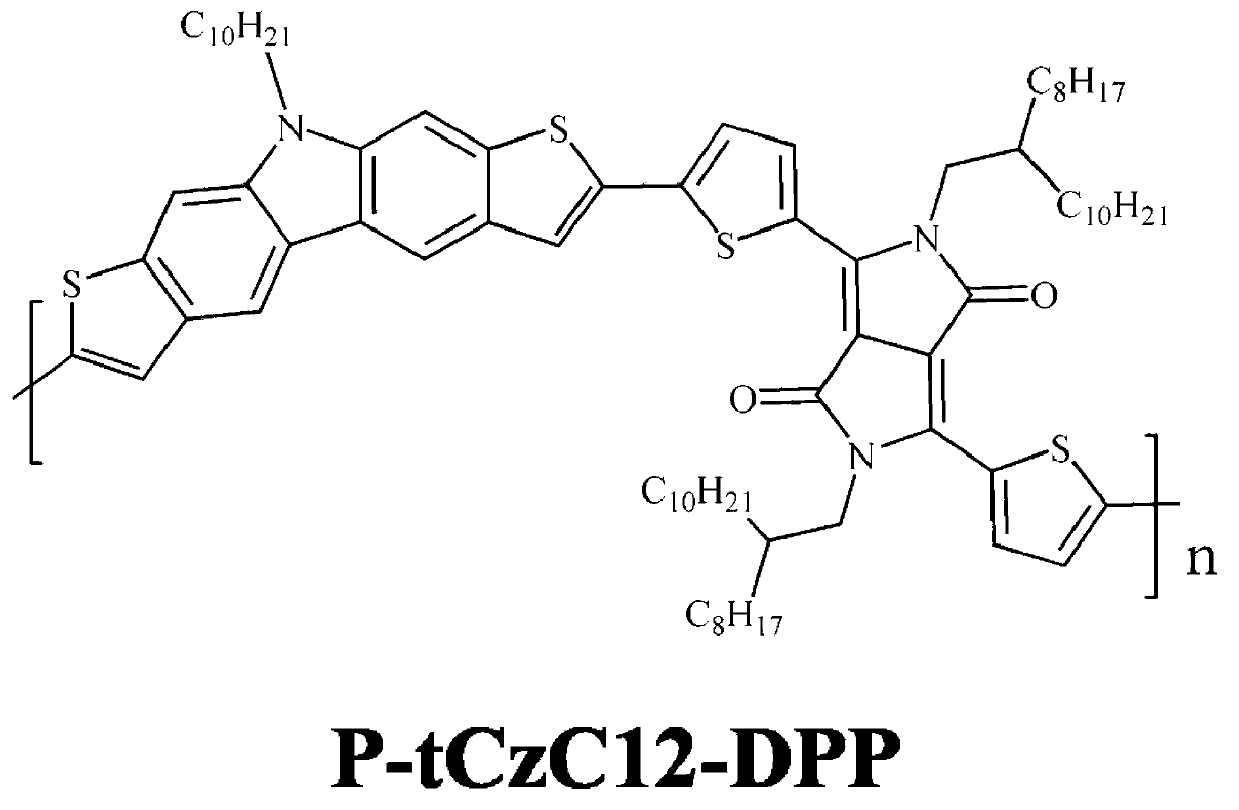

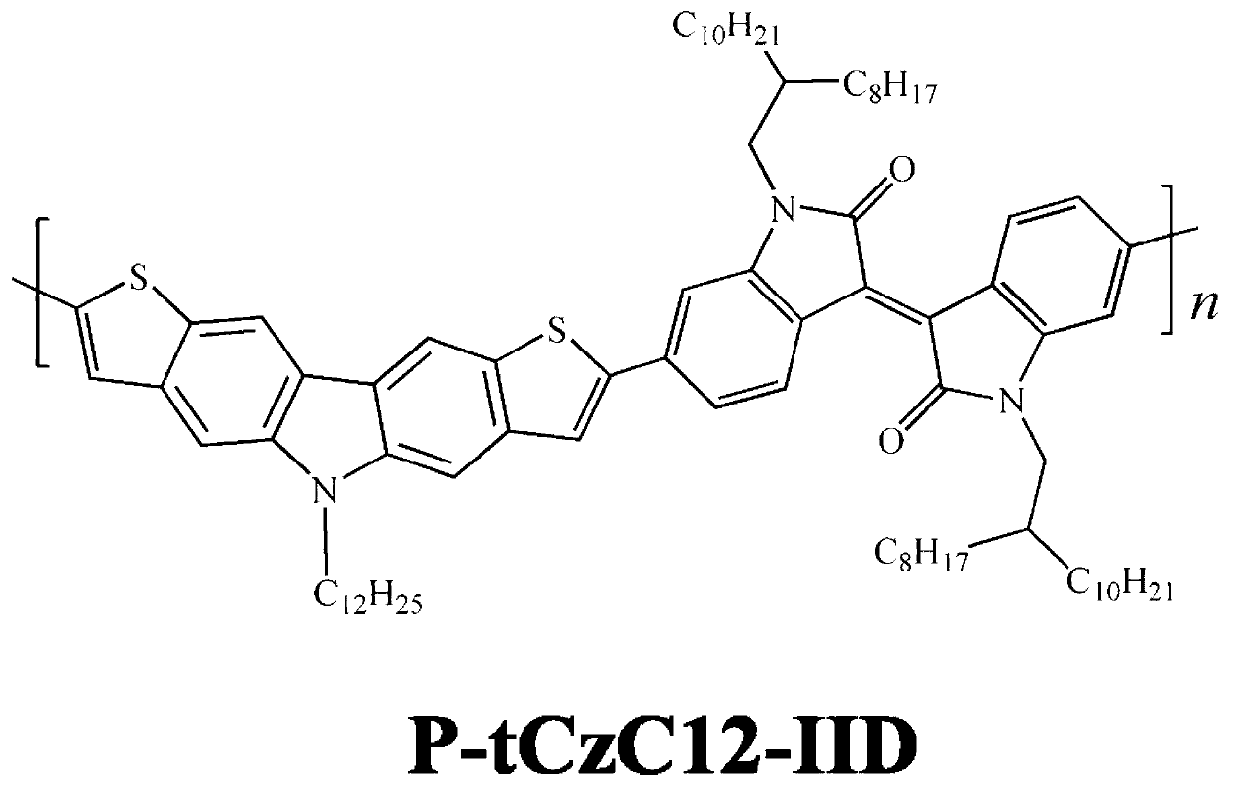

Polymer solar cell

ActiveCN103280528AImprove conductivityLower bulk resistanceSolid-state devicesSemiconductor/solid-state device manufacturingComposite cathodeFill factor

The invention relates to a polymer solar cell. The polymer solar cell sequentially comprises a cathode layer, a cathode interface layer, a photosensitive layer, an anode interface layer and an anode layer, wherein the cathode interface layer is an inorganic semiconductor nanocrystalline-conjugated polymer composite material layer. The cathode interface layer is specifically a ZnO-PFEP (phosphate ester polyfluorene) composite material layer. According to the polymer solar cell, the ZnO-PFEP composite cathode interface layer is arranged between the cathode layer and the photosensitive layer, and the mass ratio of ZnO to PFEP in the interface layer is controlled, so that the electrical conductivity of the cathode interface layer can be effectively increased, the bulk resistance of the cathode interface layer is reduced, the electron output resistance is decreased, furthermore, the short-circuit current, open-circuit voltage, fill factor and energy conversion efficiency of the cell are improved, and the electron transportation and collection are benefited.

Owner:CHANGCHUN INST OF APPLIED CHEMISTRY - CHINESE ACAD OF SCI

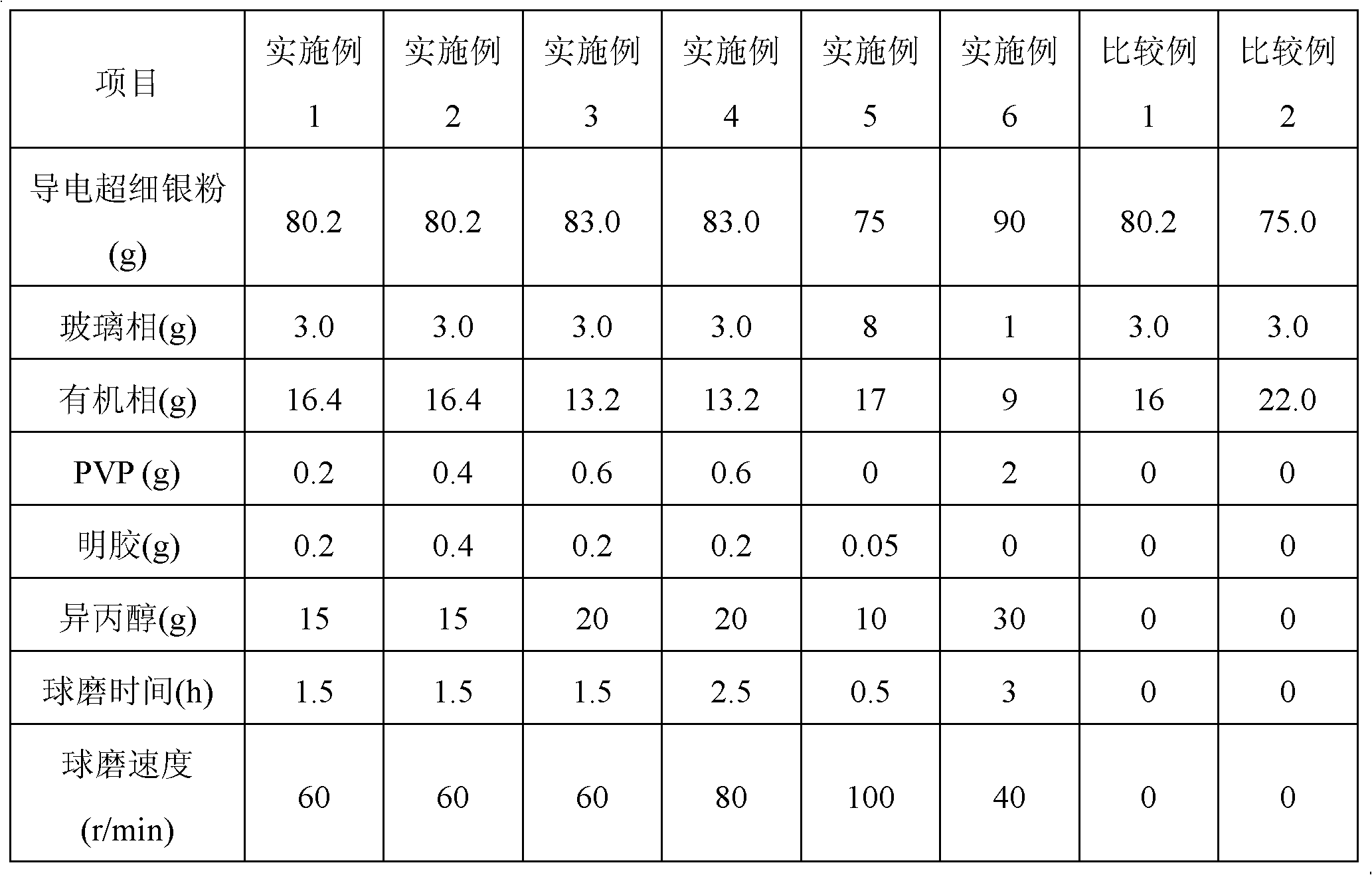

Modified silver thick film sizing agent for crystalline silicon solar cell and preparation method thereof

ActiveCN102543257AImprove the reunion situationImprove electrical performanceNon-conductive material with dispersed conductive materialCable/conductor manufactureElectricityFill factor

The invention discloses a modified silver thick film sizing agent for a crystalline silicon solar cell and a preparation method thereof. The modified silver thick film sizing agent comprises the following ingredients by weight percentage: conductive superfine silver powders accounting for 75 to 90 percent, glass powders accounting for 1 to 8 percent, and organic phases accounting for 9 to 17 percent; in addition, the modified silver thick film sizing agent also comprises surface active agents accounting for 0.05 to 2 percent of the total weight of the conductive superfine silver powders and the glass powders. According to the invention, the surfaces of the powders are coated with a layer of surface active agents, so that the aggregation condition of the powders can be improved, the powders can be dispersed in the organic phases better so as to form a more stable sizing agent system, at the same time, the scraper fineness of the sizing agent can be reduced, and the service life of the sizing agent can be prolonged. An electrode printed through the modified silver thick film sizing agent achieves great height, low body resistance and higher mechanical strength after being sintered. Therefore, not only the modified silver thick film sizing agent disclosed by the invention improves the mechanical strength of the electrode of the cell, but also fill factors (FF) of the cell are increased, the series resistance is reduced, the optical conversion efficiency is improved, and the cell can be enabled to achieve good balance of comprehensive electrical property and mechanical performance.

Owner:上海太阳能工程技术研究中心有限公司

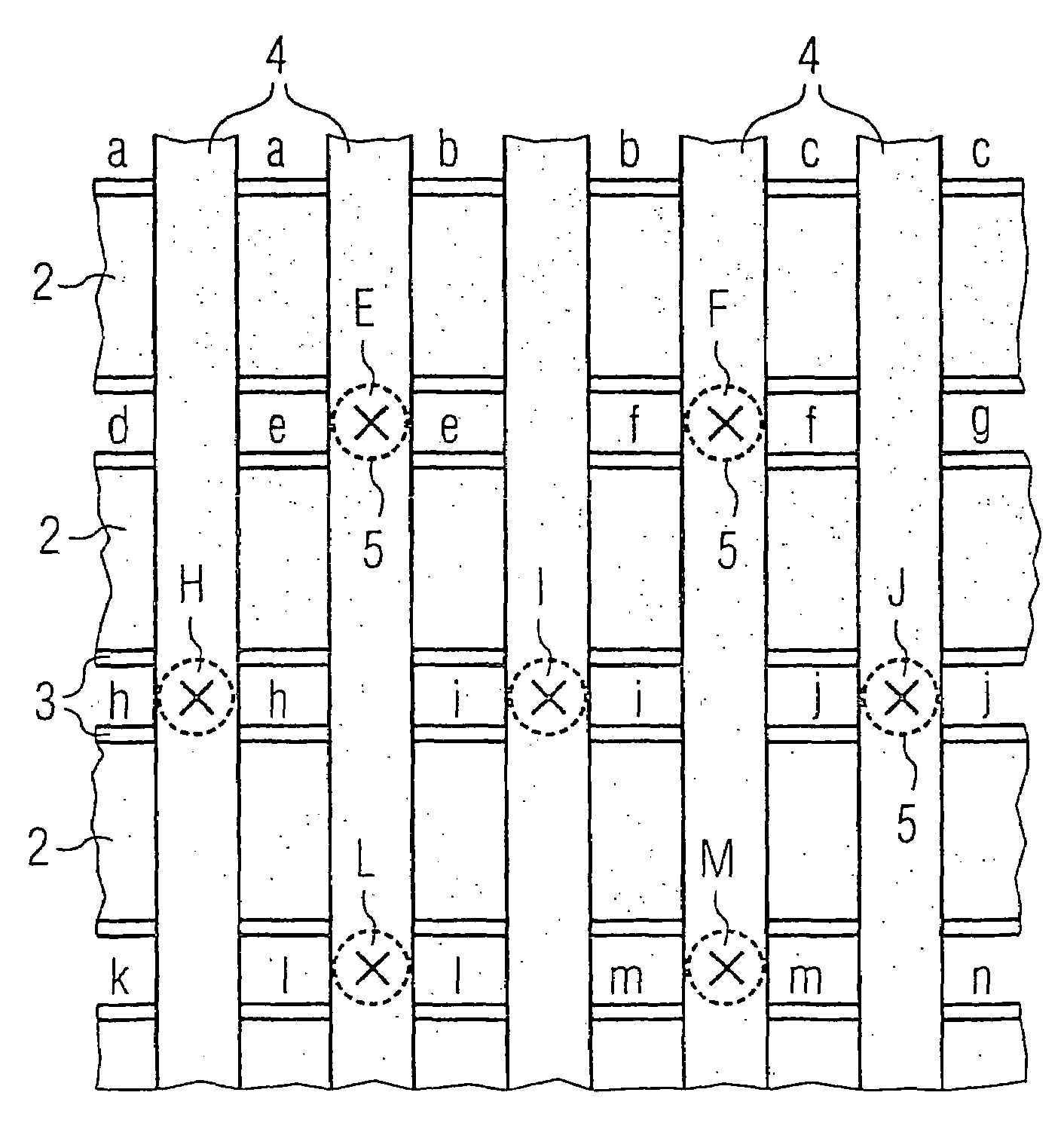

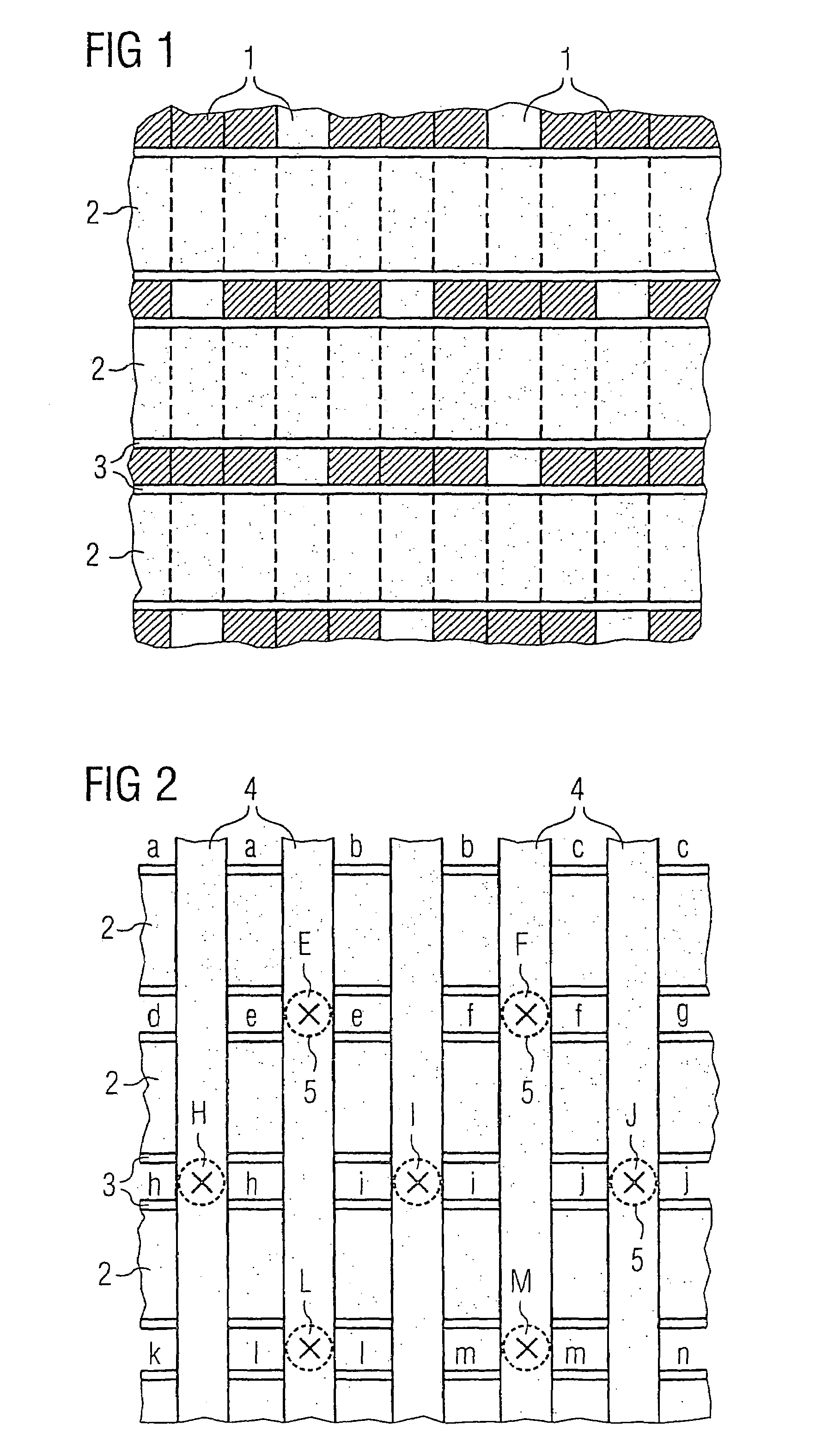

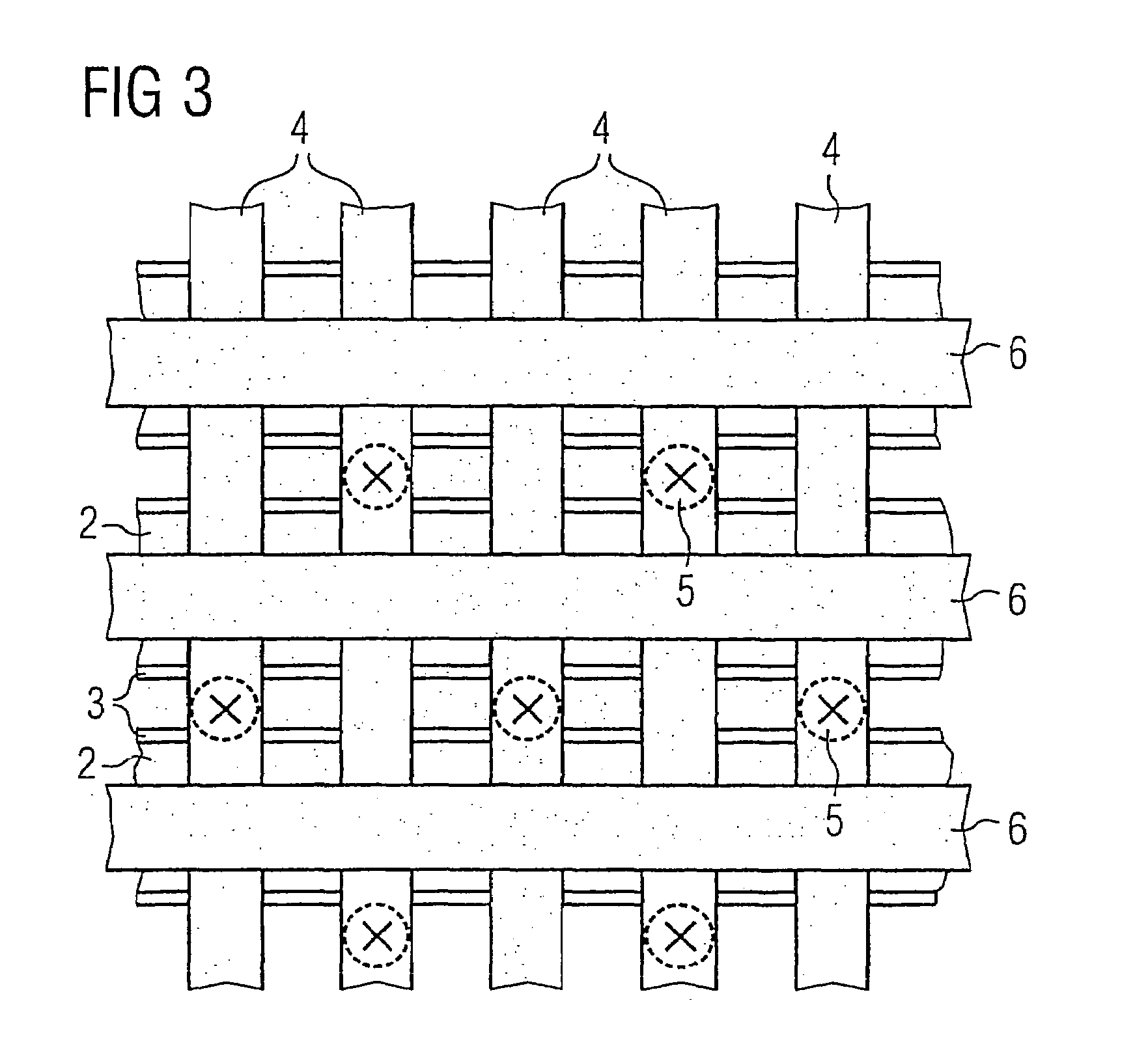

Semiconductor memory having charge trapping memory cells and fabrication method

InactiveUS7184291B2Lower bulk resistanceSolid-state devicesRead-only memoriesBit lineCross connection

In the case of this semiconductor memory having NROM cells, the channel regions of the memory transistors in each case run transversely with respect to the relevant word line, the bit lines are arranged on the top side of the word lines and in a manner electrically insulated from the latter, and electrically conductive cross-connections are present, which are arranged in sections in interspaces between the word lines and in a manner electrically insulated from the latter and are connected to the bit lines in each case in next but one sequence.

Owner:POLARIS INNOVATIONS LTD

All-aluminum back surface field aluminum paste for crystalline silicon solar cell and preparation method thereof

ActiveUS20170148936A1Increase contactLower bulk resistanceConductive materialInksSilver pasteOrganic solvent

The invention discloses an all-aluminum back surface field aluminum paste for a crystalline silicon solar cell and a preparation method thereof. The all-aluminum back surface field paste mainly comprises 60-70% aluminum powder, 5-10% nanometer metal oily solution, 1-10% inorganic binder, 10-20% organic binder, 5-30% organic solvent and 1-5% accessory ingredient. According to the aluminum paste prepared by the present invention, the back surface preparing process of an all-aluminum back surface field can be implemented preferably; moreover, the paste has great adhesive force, is easy to be better adhered to silver paste printed afterwards; meanwhile, the paste can be in good contact with a silicon chip through the nanometer metal oily solution added into the paste, the aluminum back surface is prevented from falling off, and good ohm contact can be formed, so that the photoelectric conversion efficiency is increased, and the economic benefits of enterprises are increased.

Owner:NANTONG T SUN NEW ENERGY CO LTD

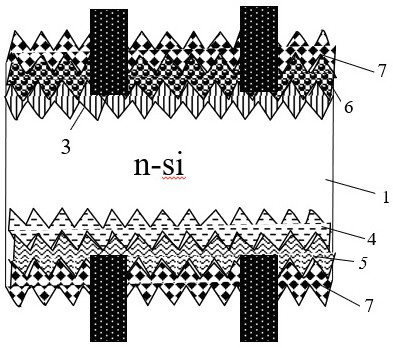

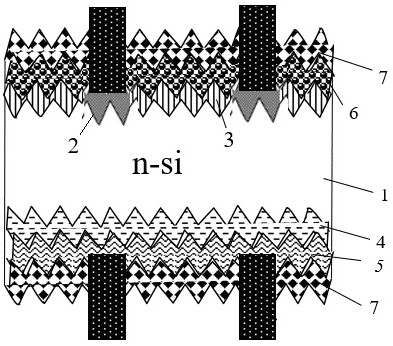

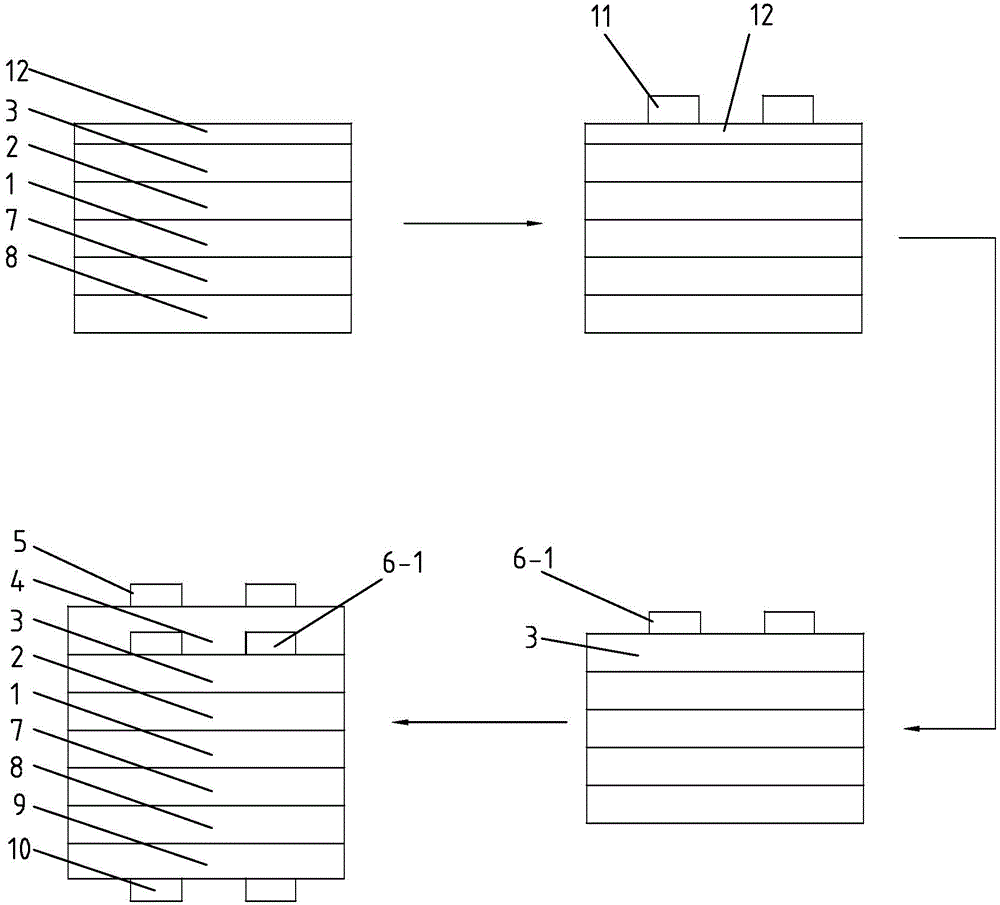

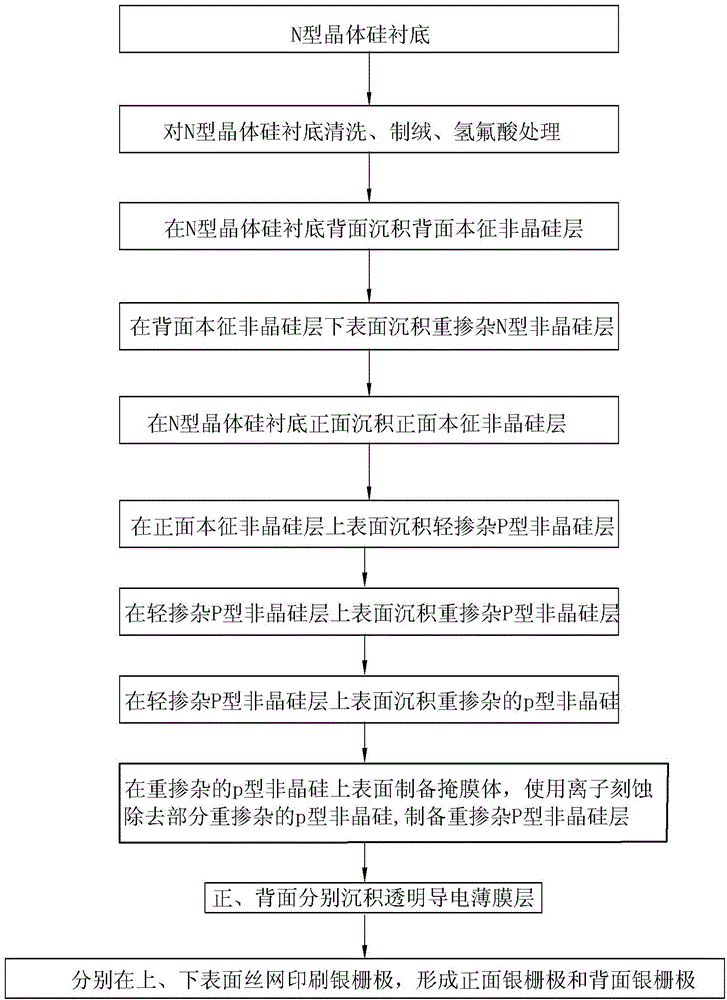

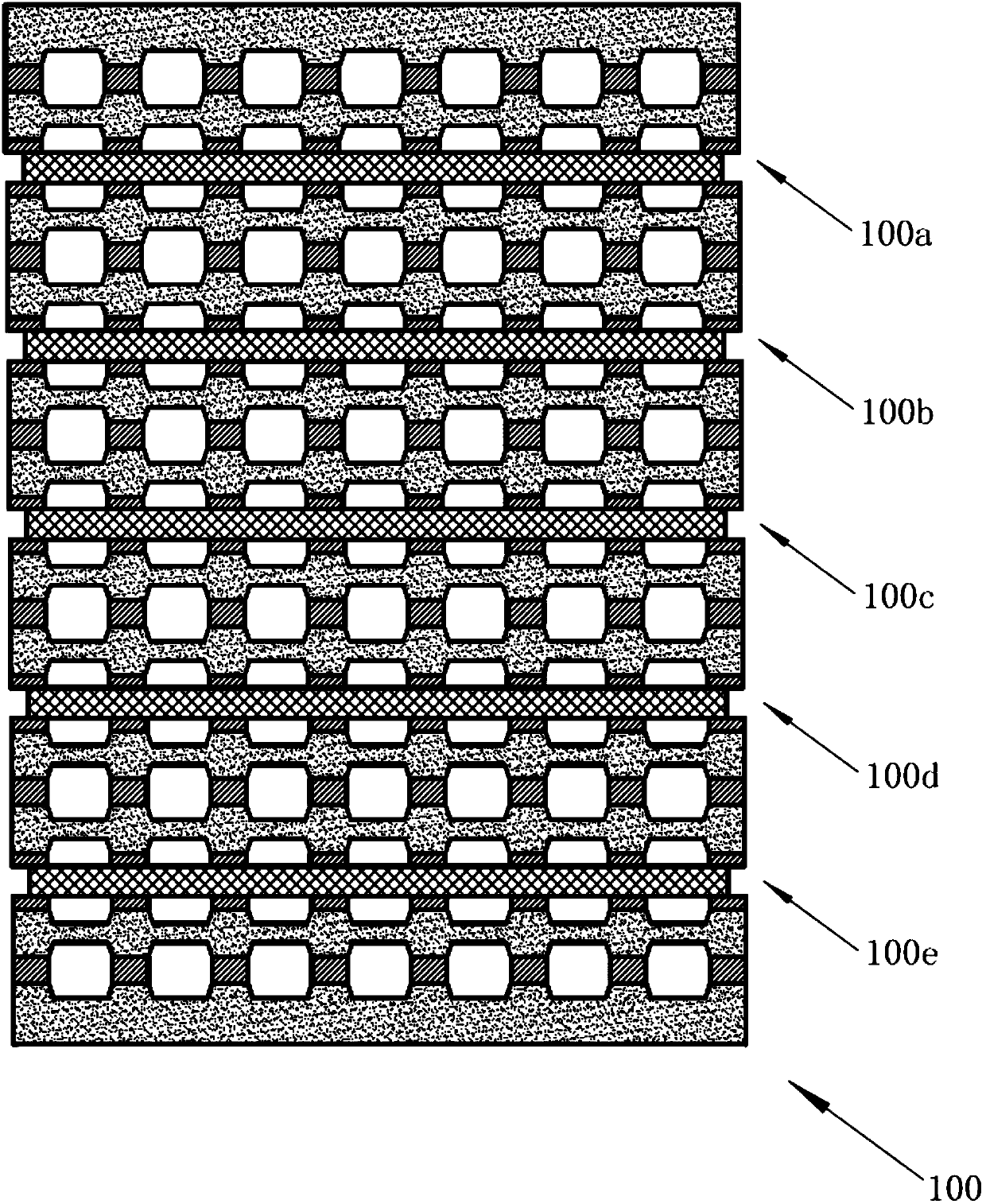

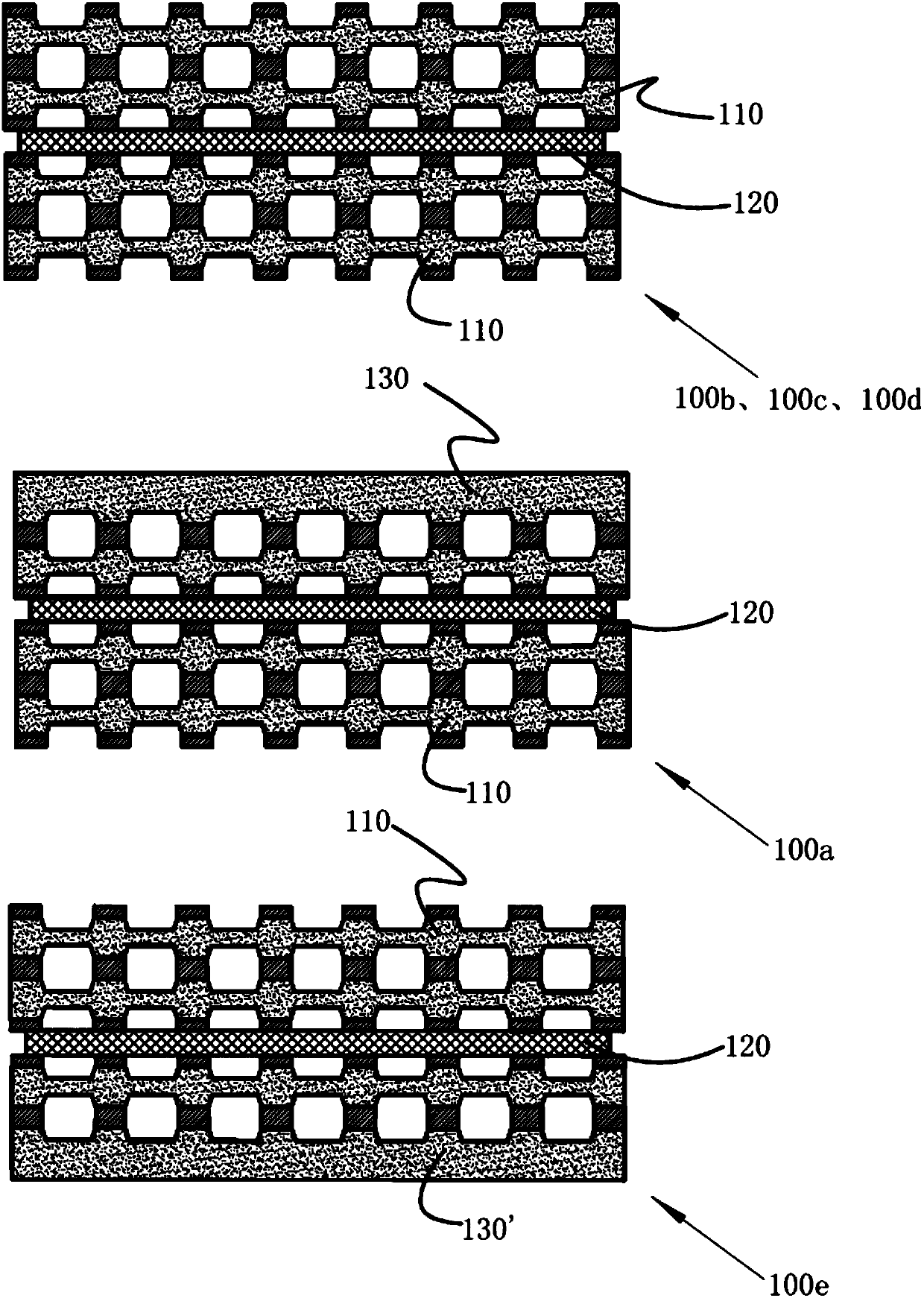

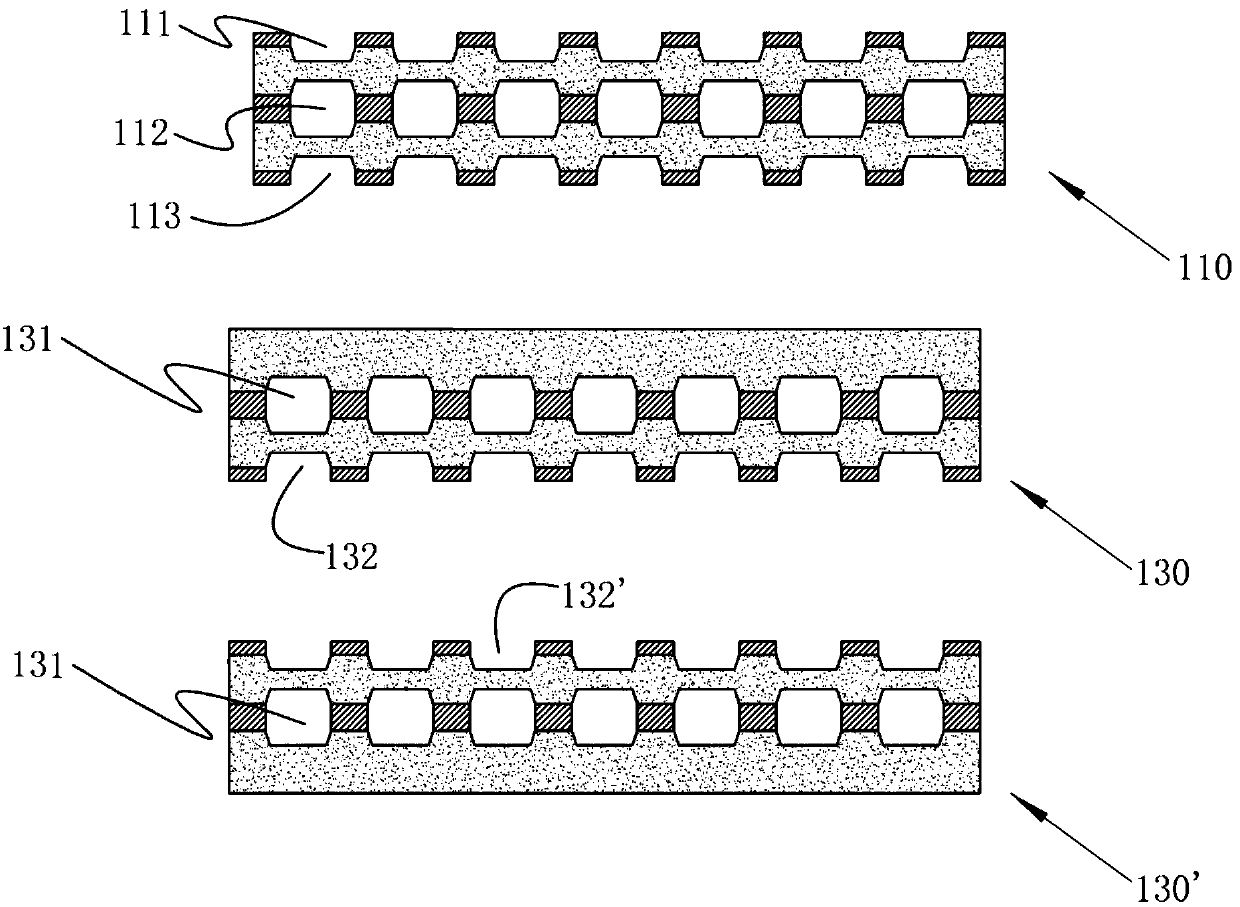

Heterojunction solar cell with selective emitting electrode and manufacturing method thereof

ActiveCN103985778AImprove efficiencyLower bulk resistanceFinal product manufacturePhotovoltaic energy generationHeterojunctionCharge carrier

The invention discloses a heterojunction solar cell with a selective emitting electrode and a manufacturing method of the heterojunction solar cell. The heterojunction solar cell comprises an N-type crystalline silicon substrate, a front-face intrinsic amorphous silicon layer, a light doped P-type amorphous silicon layer, a front-face transparent conducting film layer, a front-face silver grid electrode, a heavy doped P-type amorphous silicon layer, a back-face intrinsic amorphous silicon layer, a heavy doped N-type amorphous silicon layer, a back-face transparent conducting film layer and a back-face silver grid electrode, and the N-type crystalline silicon substrate is provided with a front face and a back face. The heavy doped P-type amorphous silicon layer is adopted as the selective emitting electrode, is arranged at the contact position of the front-face transparent conducting film layer and the light doped P-type amorphous silicon layer and is provided with a plurality of heavy doped P-type amorphous silicon monomers, and the heavy doped P-type amorphous silicon monomers correspond to grid wires of the front-face silver grid electrode one to one and are located under the corresponding grid wires respectively. The heavy doped N-type amorphous silicon layer is deposited on the lower surface of the back-face intrinsic amorphous silicon layer. According to the solar cell and the manufacturing method, recombination of current carriers can be reduced, absorption of the emitting electrode on the current carriers is reduced, and therefore open-circuit voltages and short-circuit currents are improved, and the efficiency of the heterojunction cell is improved.

Owner:TRINA SOLAR CO LTD

Silicon pole plate and preparation method thereof

The invention discloses a silicon pole plate and a preparation method thereof. The silicon pole plate is made of a doped conductive crystalline silicon material and is provided with an internal cooling medium flow channel, a front reducing agent flow channel and / or a back oxidizing agent flow channel, wherein the internal cooling medium flow channel, the front reducing agent flow channel and / or the back oxidizing agent flow channel are / is respectively provided with a silicon pole plate inlet and outlet combination communicated with the internal cooling medium flow channel, the front reducing agent flow channel and / or the back oxidizing agent flow channel. Compared with a metal pole plate, a graphite pole plate or a composite material pole plate in the prior art, the silicon pole plate provided by the invention has better advantages in the aspects of service life, cost, efficiency and power density, and undoubtedly has great significance and a core promotion effect on the large-batch industrialization process of fuel cells.

Owner:SUNLAND SHANGHAI INVESTMENT CO LTD

Preparation method of dacron fabric compound antistatic agent

The invention discloses a preparation method of a dacron fabric compound antistatic agent and belongs to the technical field of textile. The preparation method comprises the following steps: firstly, dropwise adding absolute ethyl alcohol and phosphorus pentoxide into a flask; mixing and stirring the mixture and heating and sealing the mixture for stirring reaction; after reaction, dropwise adding deionized water and stirring the mixture to obtain a reaction liquid 1; then adding dimethyl diallyl ammonium chloride and the like into the flask; dropwise adding normal butanol; adjusting the pH value by using sodium hydroxide to obtain a reaction liquid 2; then adding dimethyl diallyl ammonium chloride and the like into a three-mouth flask; stirring the mixture and adding ammonium persulfate to induce a reaction; then supplementing glycidyl acrylate and the like; after reaction, obtaining a reaction liquid 3; and mixing the reaction liquid 2 with the reaction liquid 3 to obtain the dacron fabric compound antistatic agent. The compound antistatic agent prepared by the method does not change color if being used at a high temperature, is stable in performance, and not only can remarkably improve the antistatic performance of the dacron fabric, is lasting in antistatic property, but also is non-irritant and healthy and safe.

Owner:揭阳市庆兴化纤实业有限公司