P type transverse double-dispersion MOS pipe capable of reducing conduction resistance

A technology of lateral double diffusion and on-resistance, applied in circuits, electrical components, semiconductor devices, etc., can solve the problem of being difficult to make small, and achieve the effect of reducing the area of the tube body

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The technical solution of the invention will be described in detail below in conjunction with the accompanying drawings.

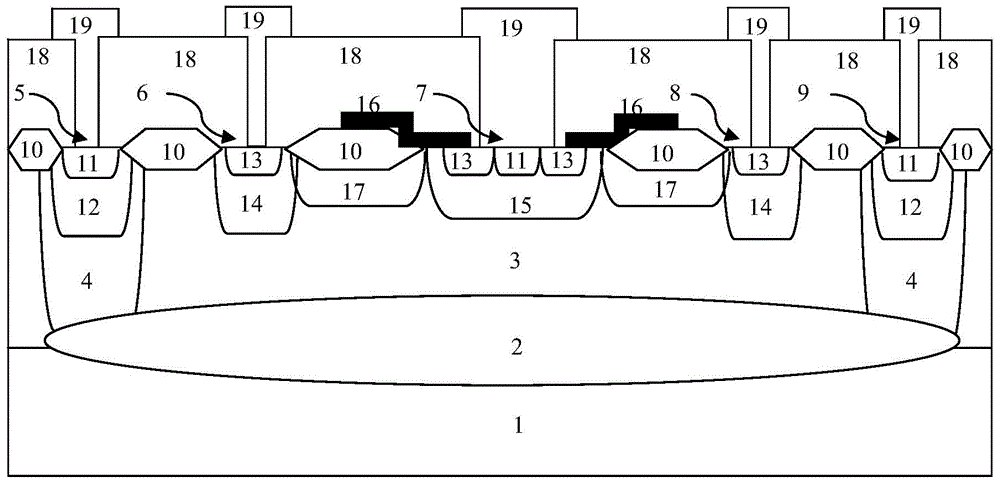

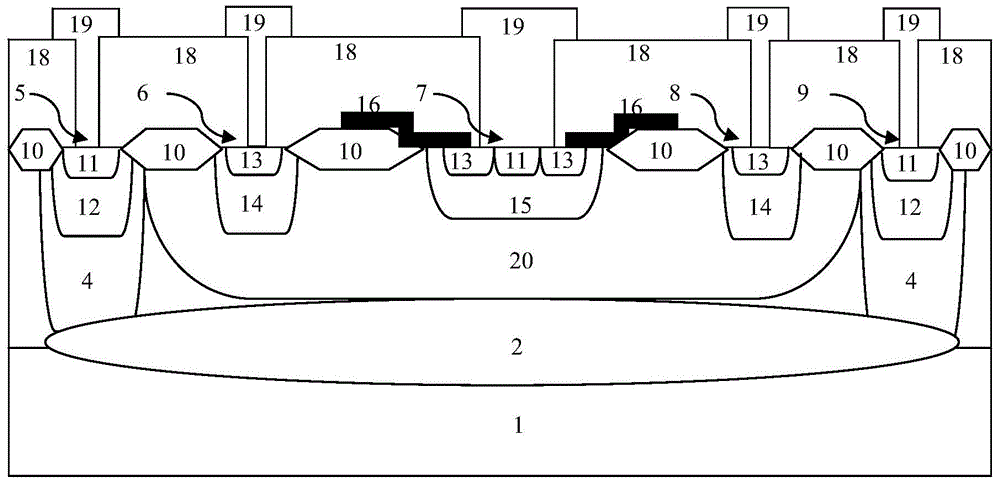

[0030] The P-type lateral double-diffused MOS transistor with reduced on-resistance involved in the present invention is as follows: figure 1 As shown, on a P-type substrate 1, a P-type epitaxial layer 3 is grown, and PLDMOS is formed in the epitaxial layer. Between the P-type substrate 1 and the P-type epitaxial layer 3 is an N-type buried layer 2 . At both ends of the N-type buried layer 2 are deep N wells 4 . The deep N well 4 diffuses 4~6um downward from the P-type epitaxial surface, communicates with the N-type buried layer, and isolates the inner P-type epitaxial layer from the outer P-type epitaxial layer to form an isolation structure. On the surface of the P-type epitaxial layer 3, a first active region 5, a second active region 6, a third active region 7, a fourth active region 8, and a fifth active region 9 are arranged in sequence. A ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More