Two-way ultralow capacitance transient voltage suppressor and production method thereof

A technology of transient voltage suppression and capacitance, which is applied in the direction of electric solid-state devices, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of increasing diebonding costs, increasing packaging defects, increasing overall size, etc., achieving low packaging costs and meeting The effect of application requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0089] In order to illustrate the present invention more clearly, the present invention will be further described in detail below in conjunction with preferred embodiments and accompanying drawings. The same parts in the drawings are denoted by the same symbols. Those skilled in the art should understand that the content specifically described below is illustrative rather than restrictive, and should not limit the protection scope of the present invention.

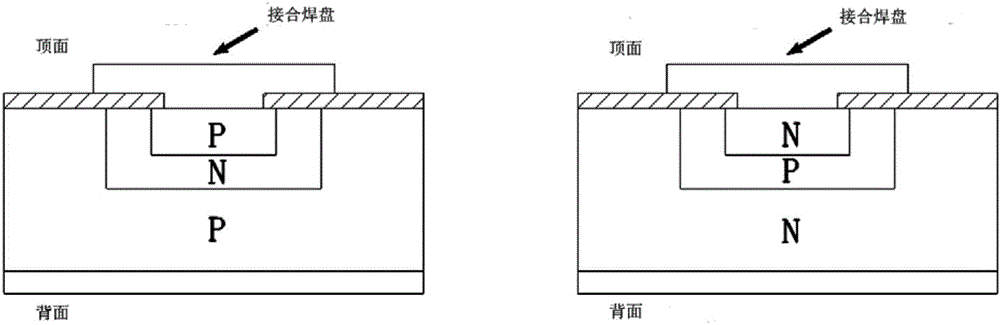

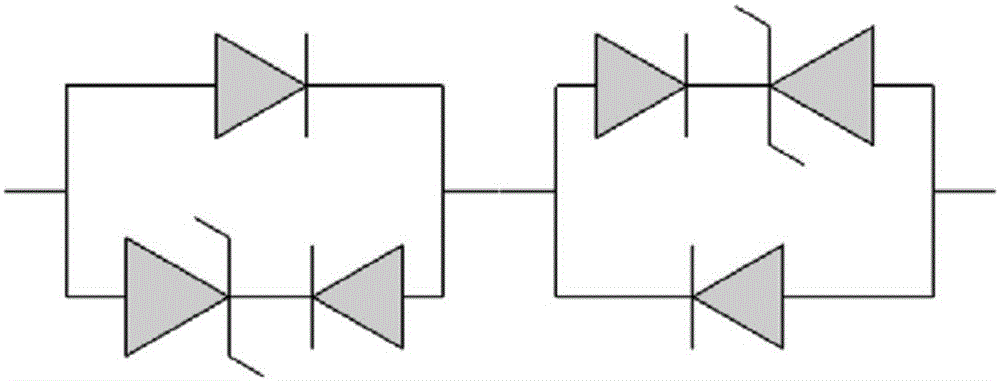

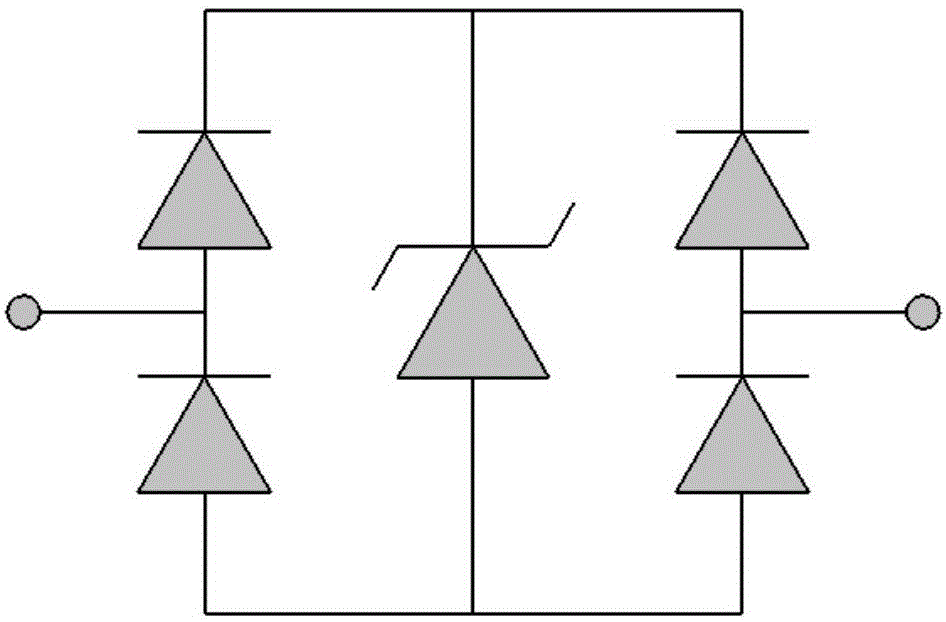

[0090] Such as Figure 5 As shown, the bidirectional ultra-low capacitance TVS of the present invention includes a first TVS transistor 15 , a second TVS transistor 16 , an upper rectifier diode 17 and a lower rectifier diode 18 . Wherein, the cathode of the first TVS tube 15 is connected with the cathode of the upper rectifying diode 17, the lower rectifying diode 18 shares the anode with the first TVS tube 15 and the second TVS16 tube, and the anode of the upper rectifying diode 17 is connected with the cathode of the l...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Resistivity | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Resistivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com