Manufacturing method of groove type super junction

A manufacturing method and super-junction technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., to achieve the effects of increasing doping concentration, reducing process difficulty, and reducing forward conduction resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

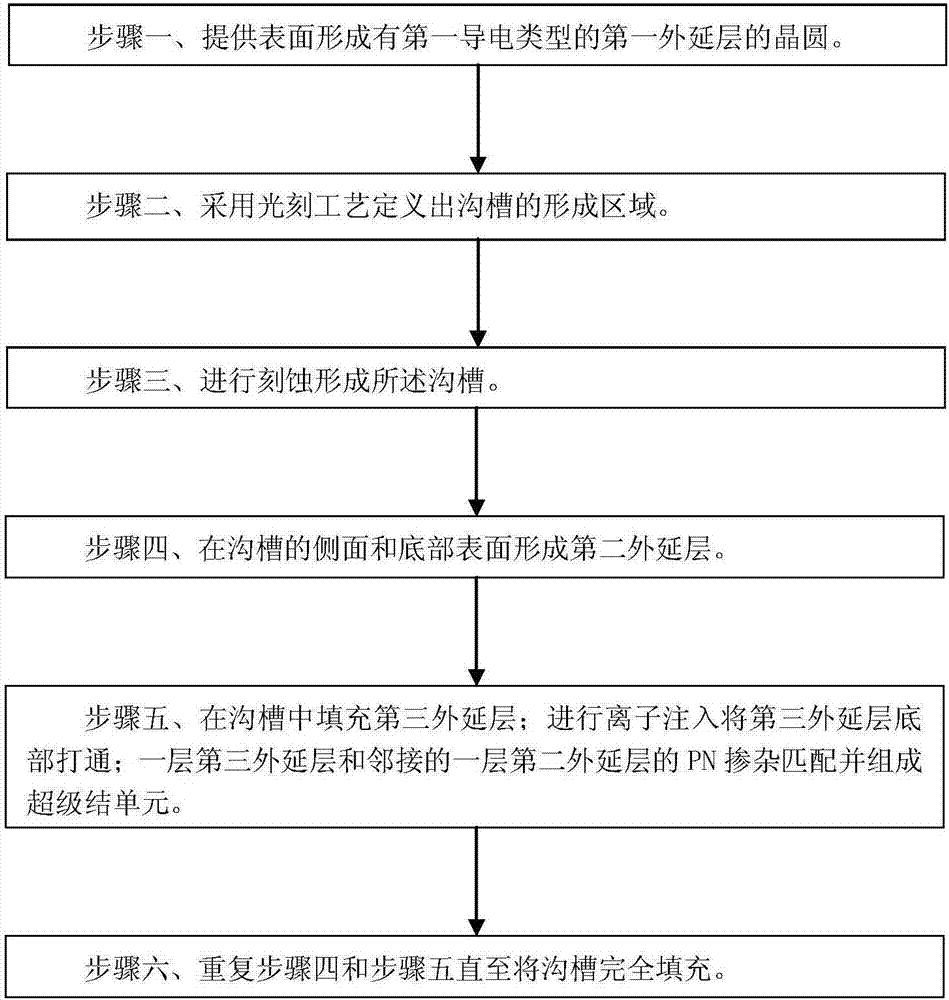

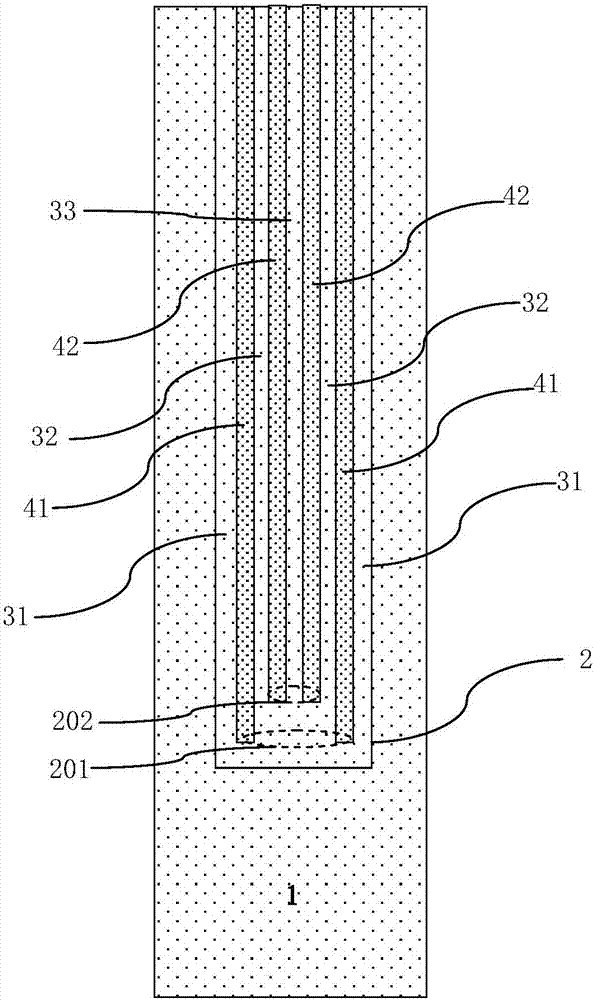

[0039] Such as figure 2 Shown is a flowchart of a method for manufacturing a Trench 2-type super junction according to an embodiment of the present invention; image 3 Shown is a schematic structural view of the super junction unit formed by the method of the embodiment of the present invention; the manufacturing method of the trench type 2 super junction in the embodiment of the present invention includes the following steps:

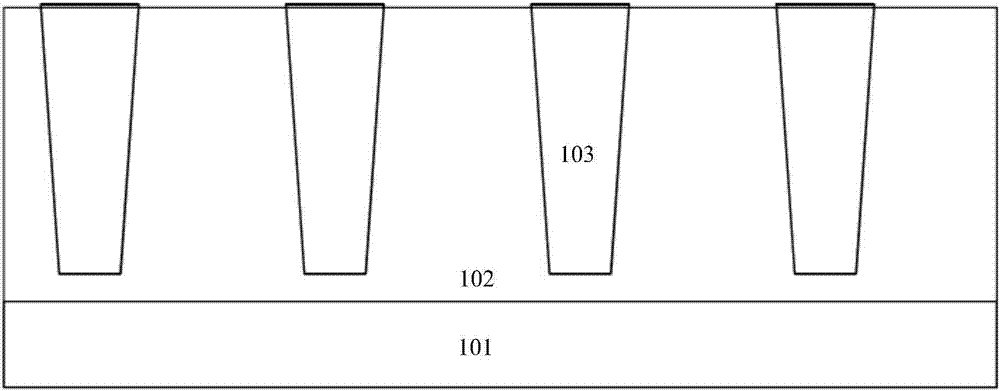

[0040] Step 1. A semiconductor substrate wafer is provided, and a first epitaxial layer 1 having a first conductivity type is formed on the surface of the semiconductor substrate wafer.

[0041] Preferably, the semiconductor substrate wafer is a silicon substrate wafer, the first epitaxial layer 1 is a silicon epitaxial layer, and the subsequently formed second epitaxial layers 31, 32 and 33 are all silicon epitaxial layers, and the third epitaxial layer 1 is a silicon epitaxial layer. Both epitaxial layers 41 and 42 are silicon epitaxial layers.

[0...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More