Patents

Literature

32results about How to "Suppress breakdown" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

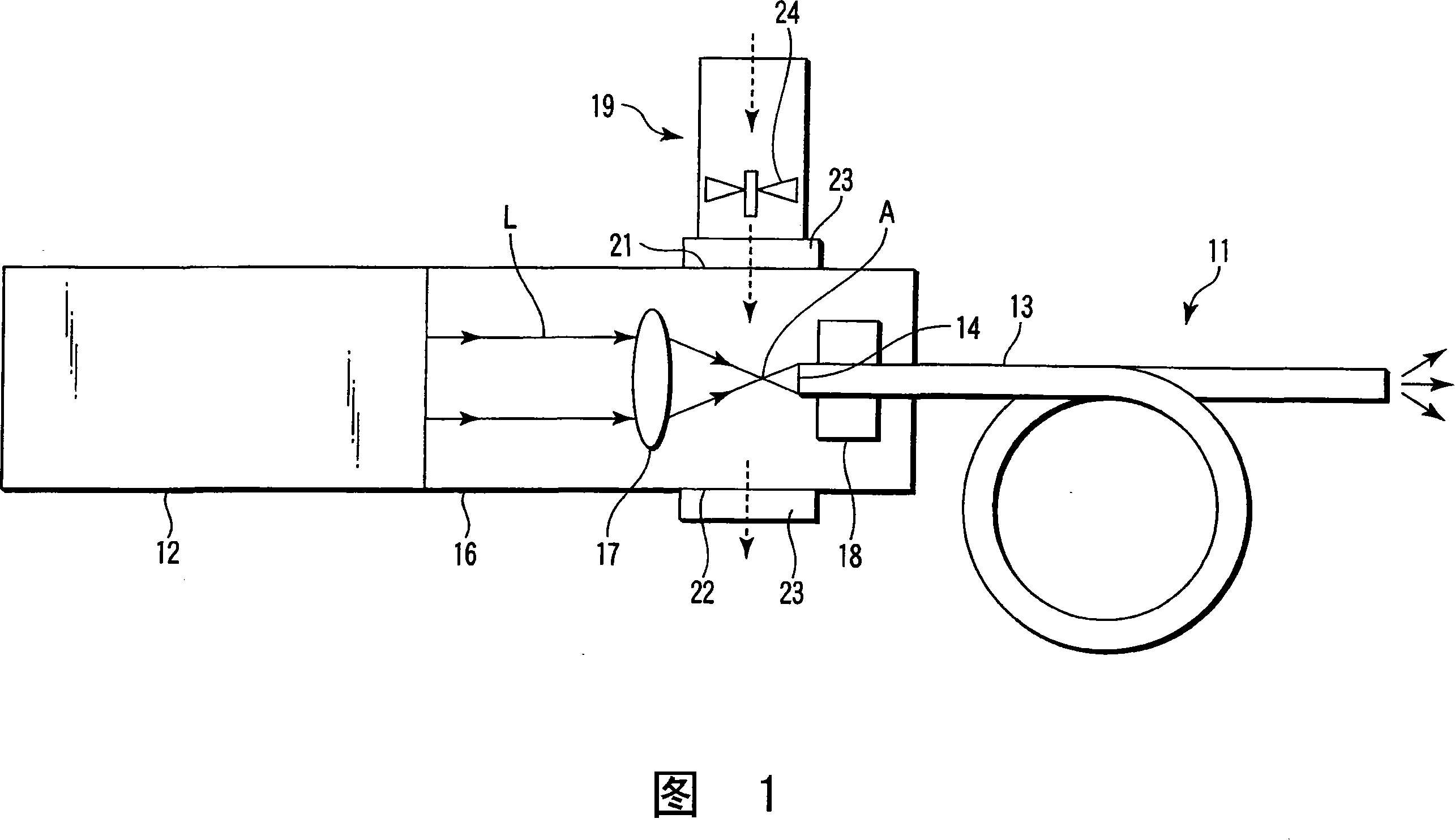

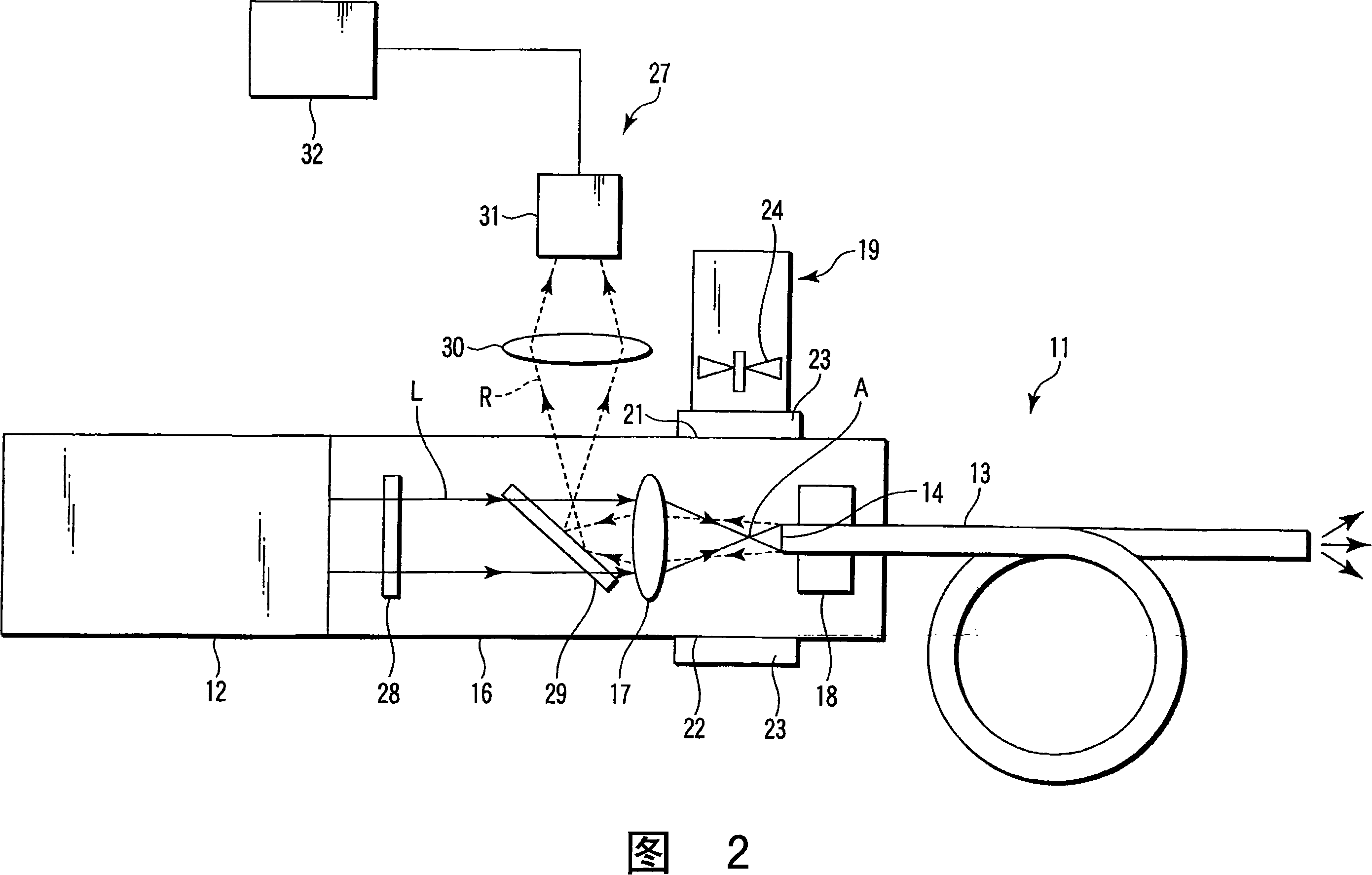

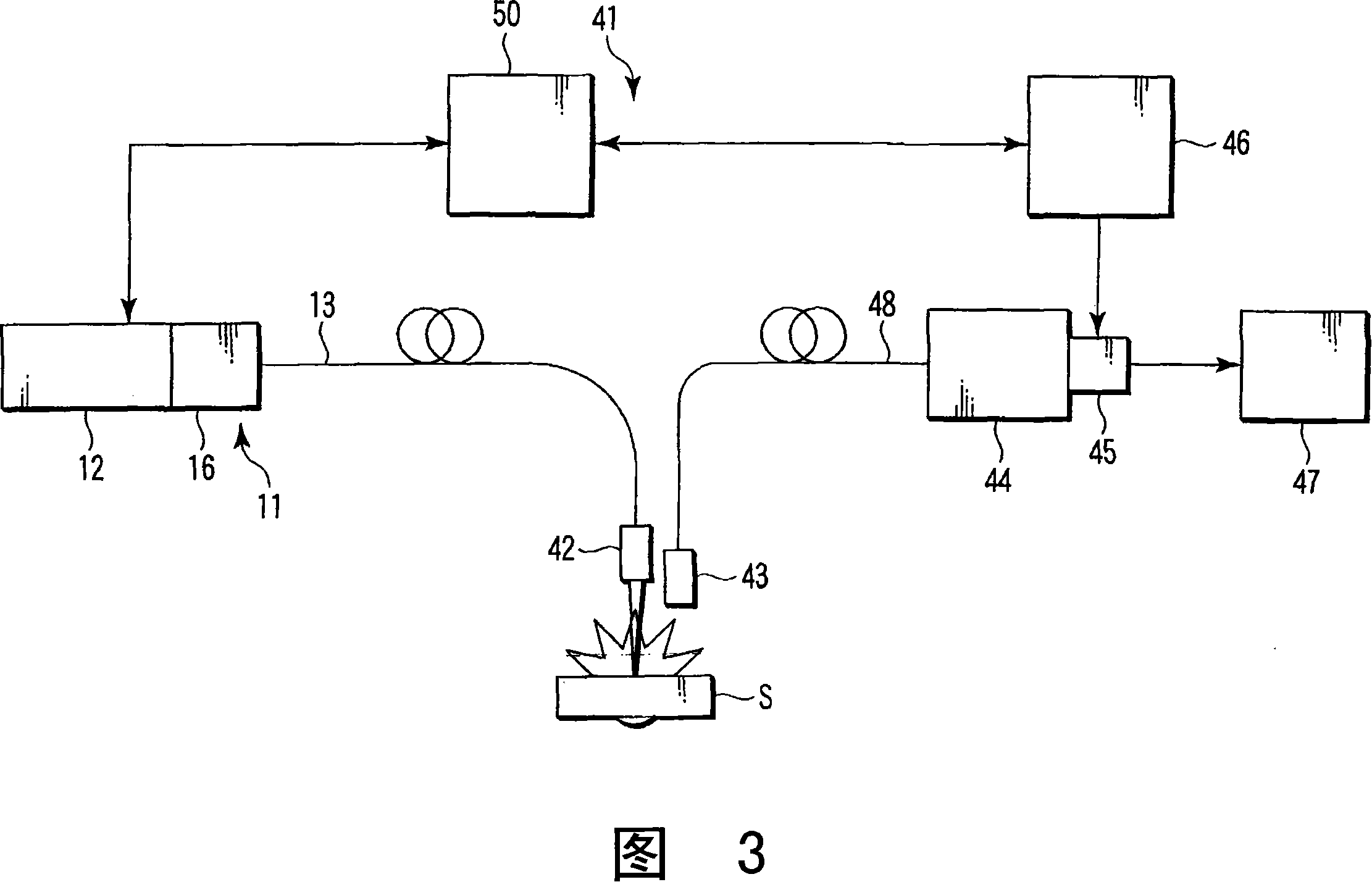

Laser beam injecting optical device for optical fiber

InactiveCN101109835ASuppress breakdownCoupling light guidesFluorescence/phosphorescenceIonizationLaser oscillator

In a shielding case, a condenser lens condenses a laser beam output by a laser oscillator to inject the laser beam into an entrance end face of an optical fiber disposed posterior to a focusing point of the laser beam. Ventilation of an ambient gas in the shielding case is carried out by ventilating means, and the ambient gas bringing about ionization in the vicinity of the focusing point of the laser beam is eliminated, thereby preventing the outbreak of air breakdown.

Owner:KK TOSHIBA +1

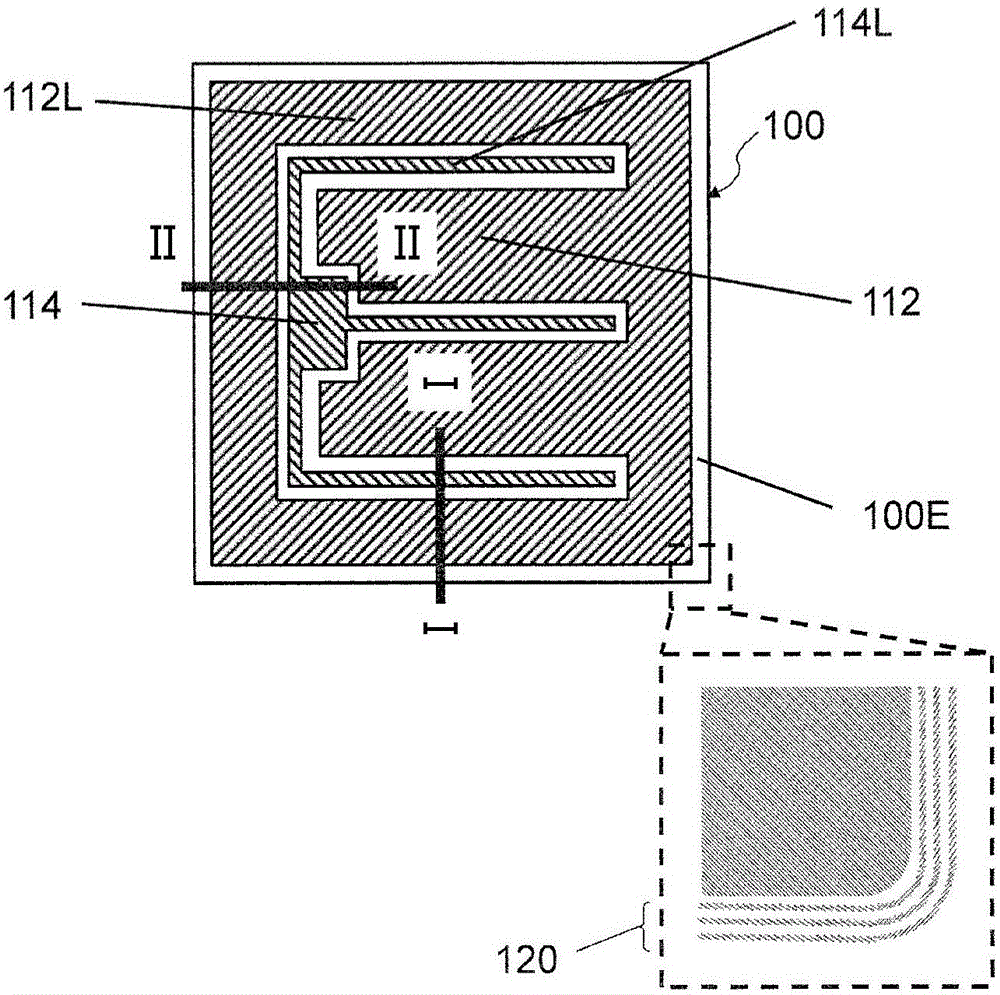

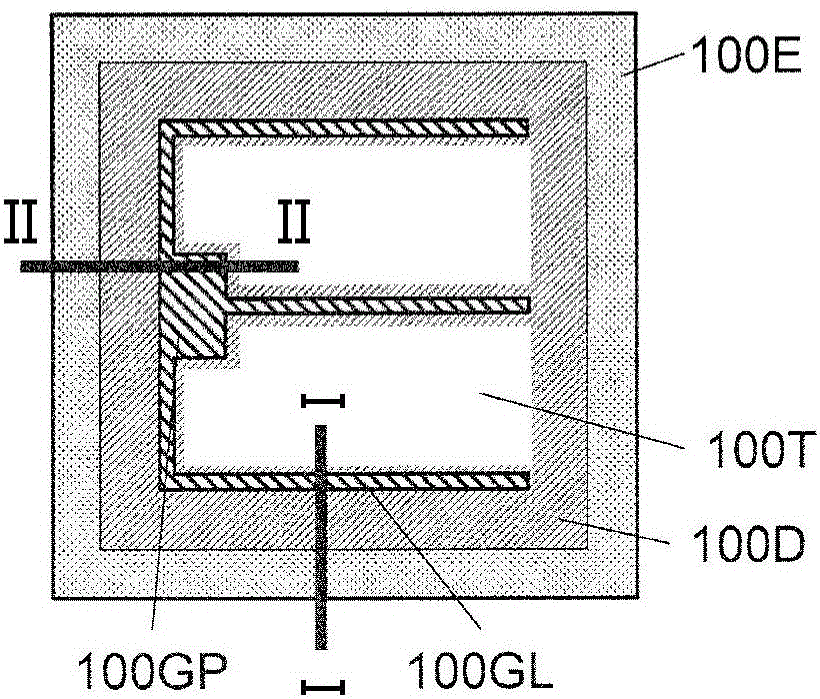

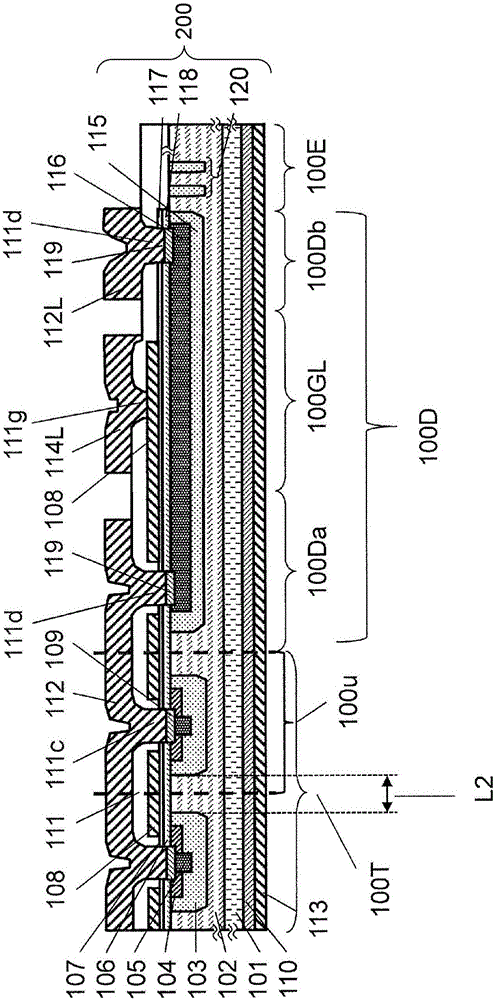

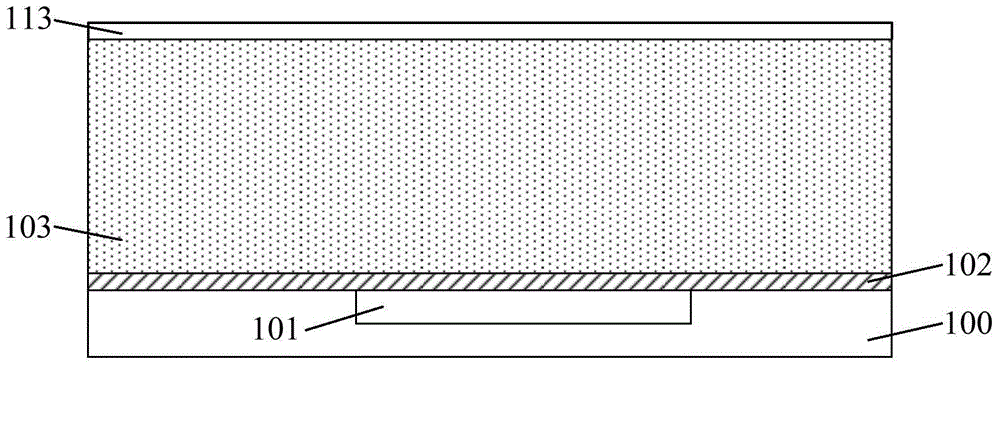

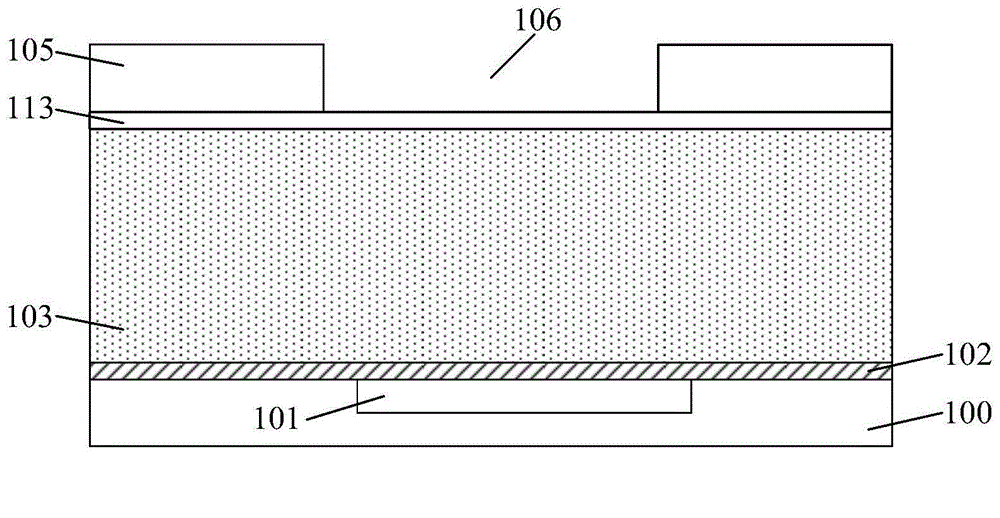

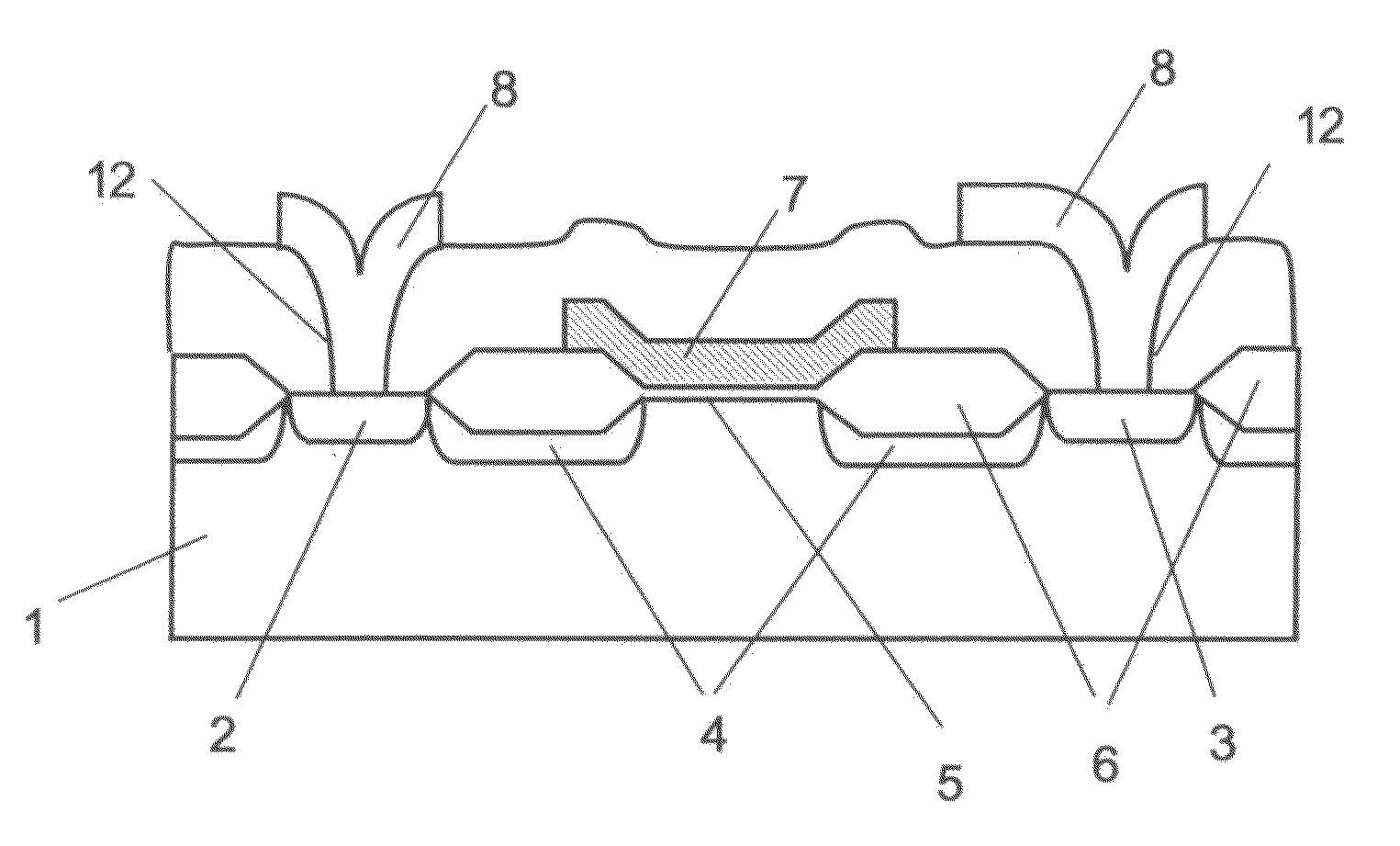

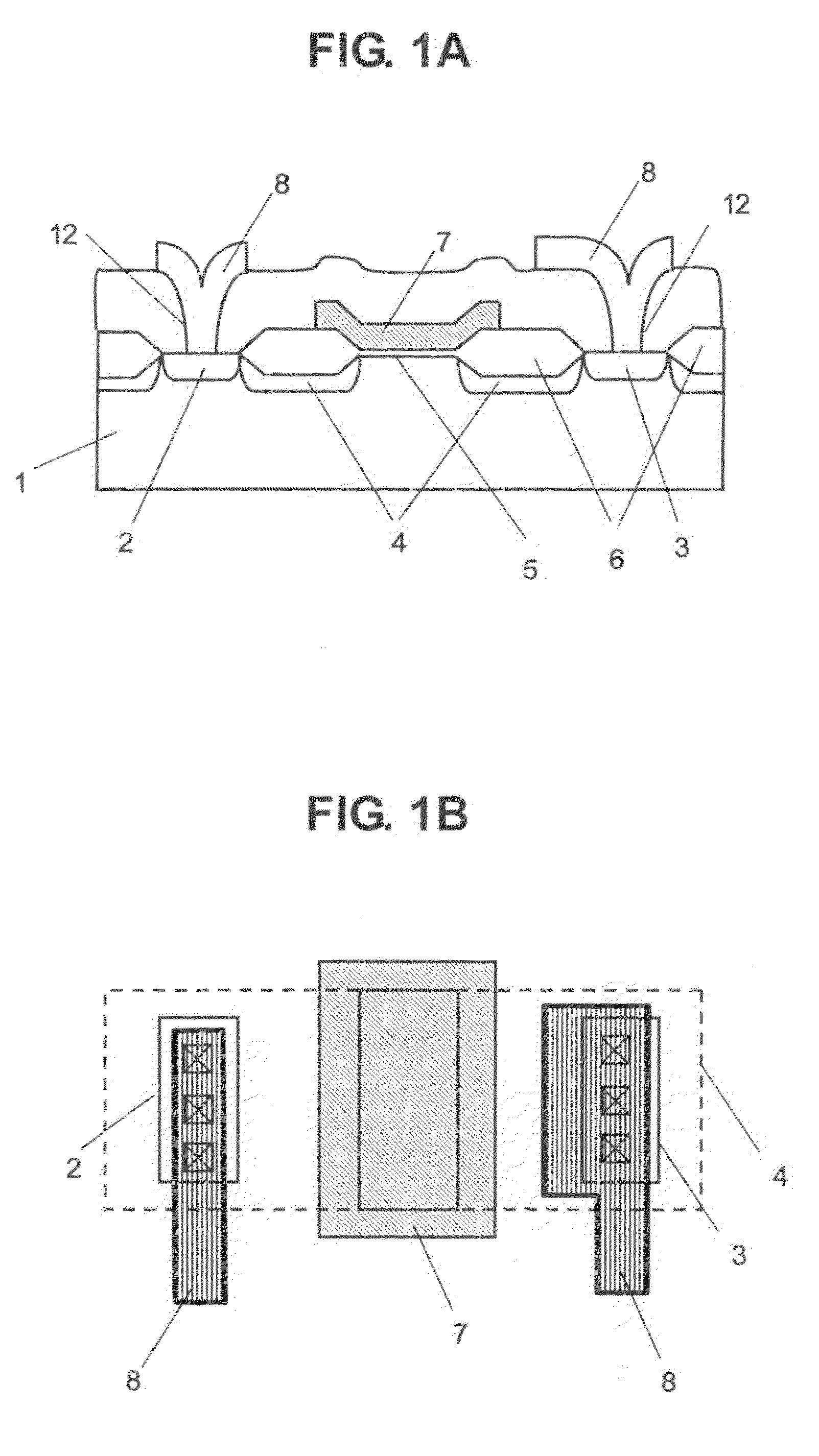

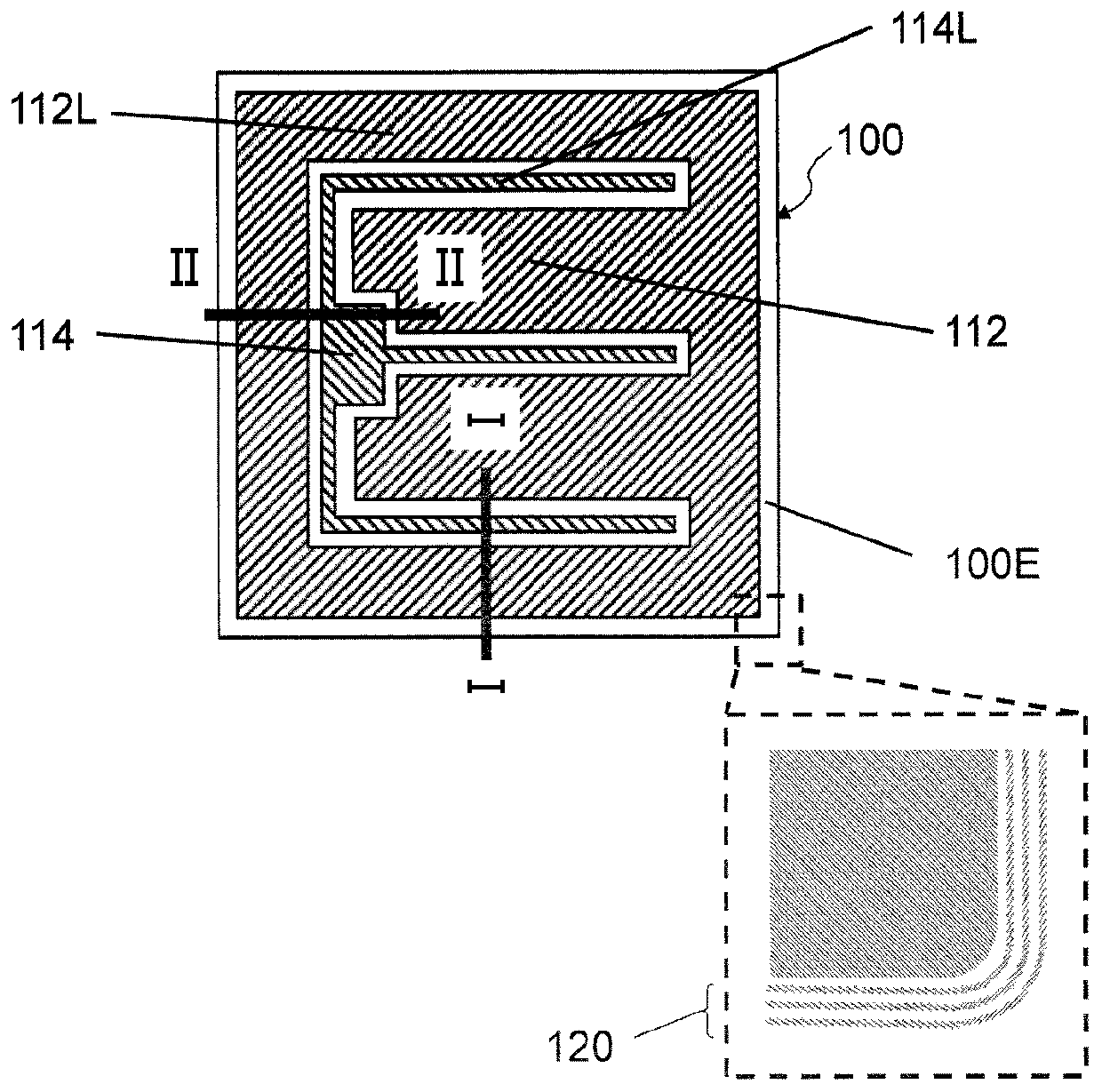

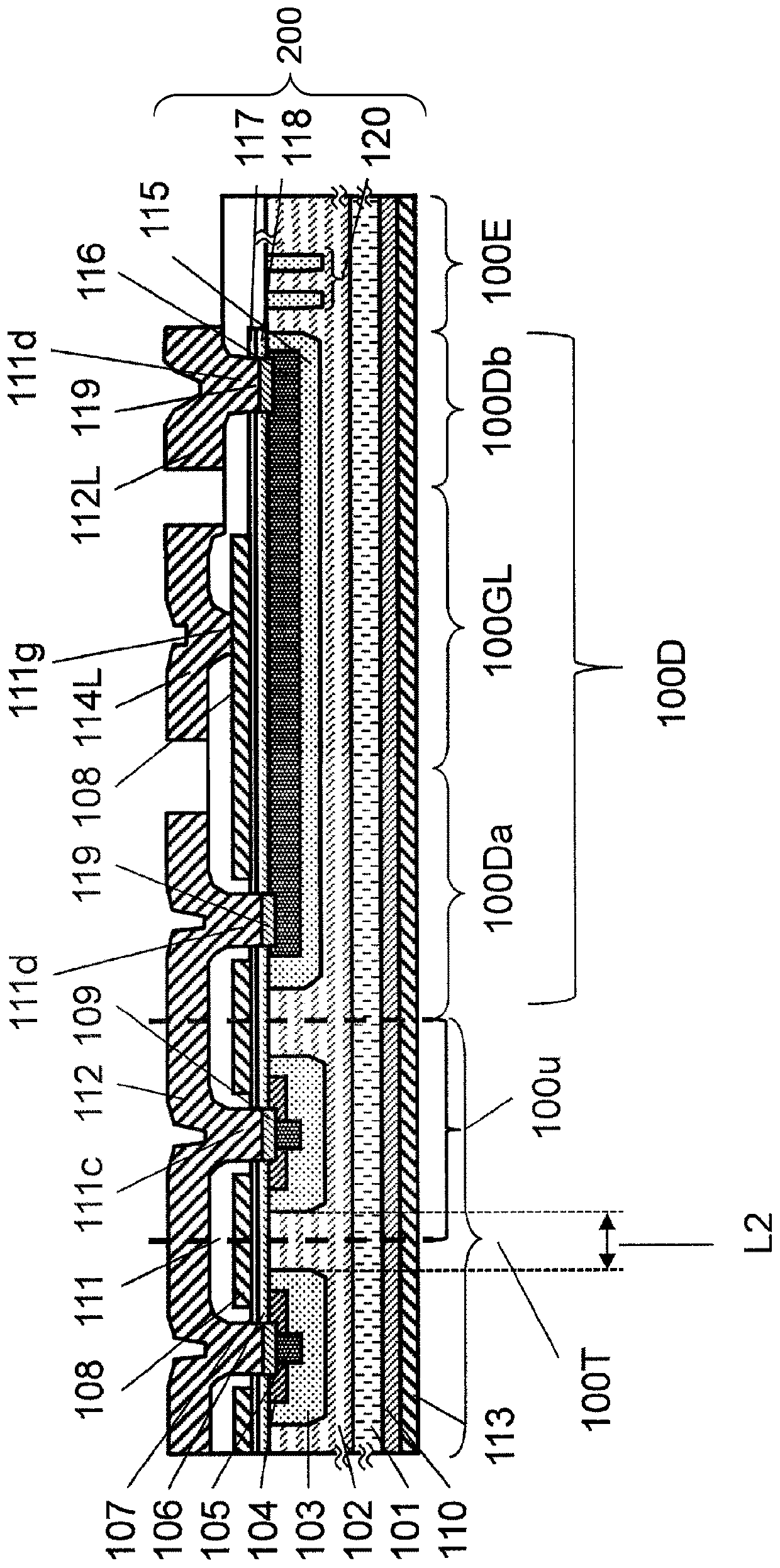

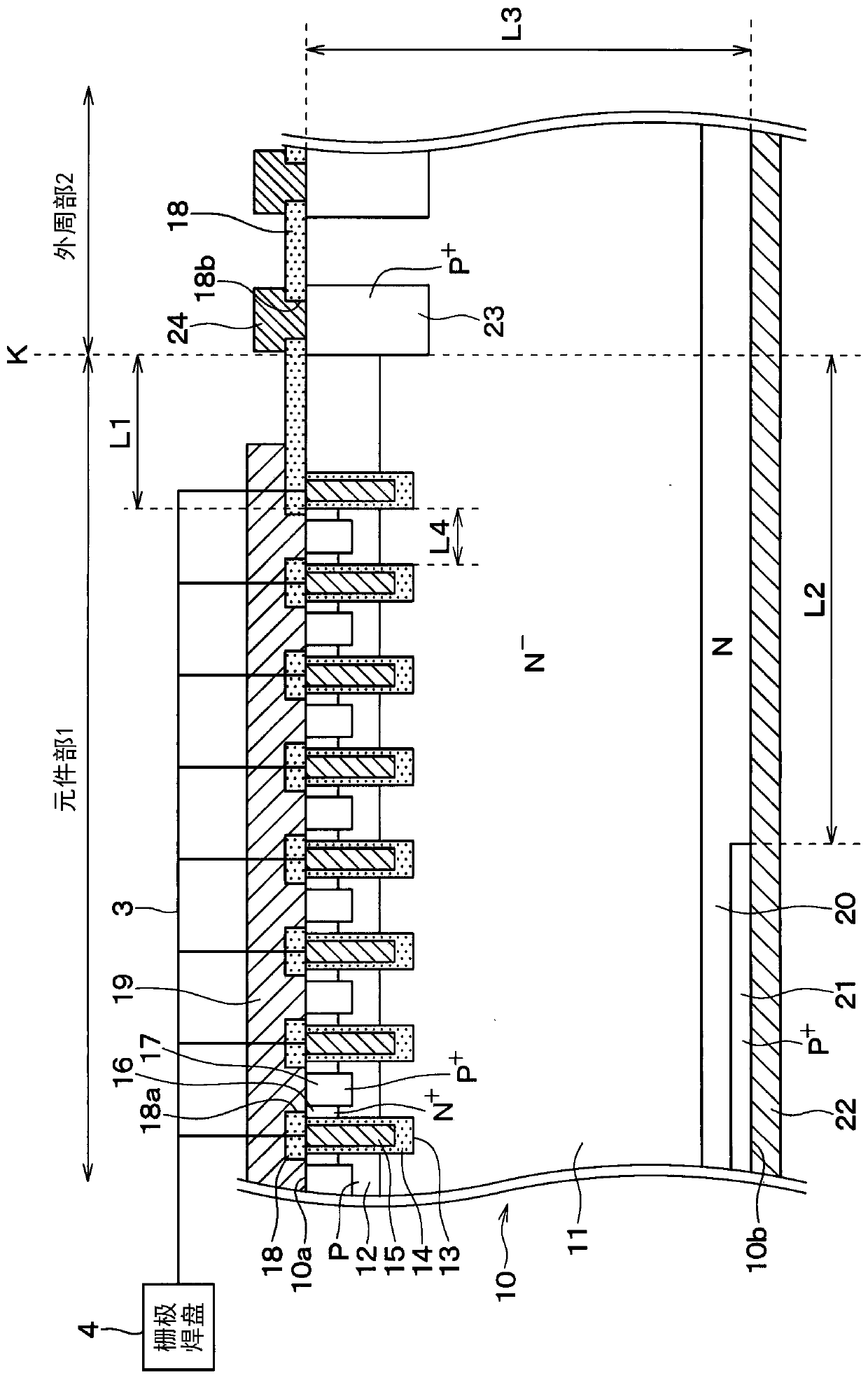

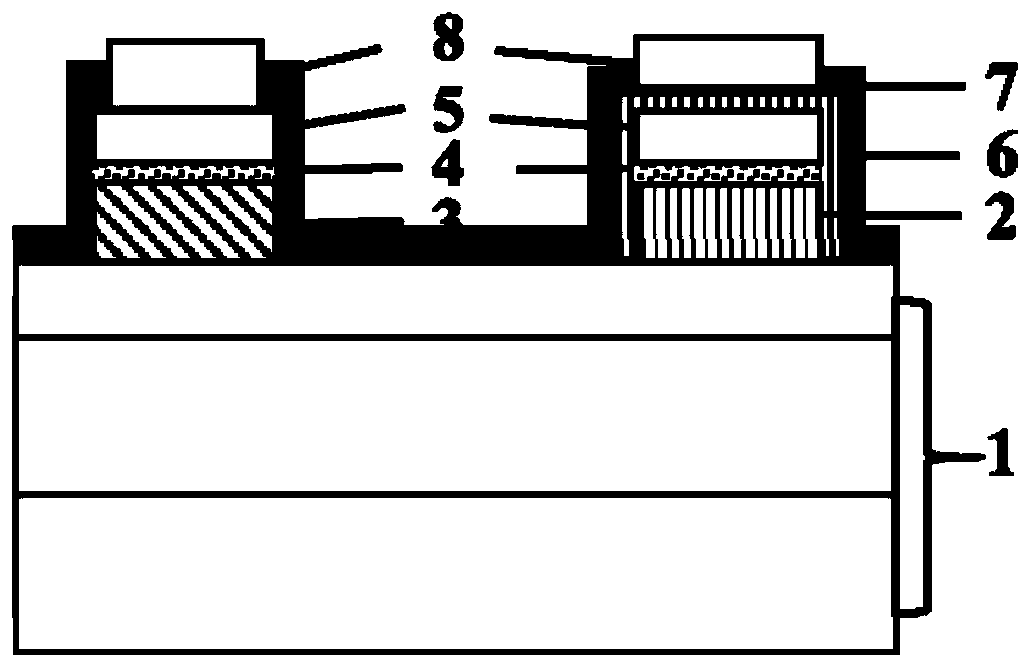

Silicon carbide semiconductor device

ActiveCN106463541ARaise the potentialSuppress breakdownSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductorTransistor

This silicon carbide semiconductor device comprises a transistor region, a diode region, a gate wiring region and a gate pad region. The gate pad region and the gate wiring region are respectively arranged so as to be sandwiched between the diode region that is adjacent to the transistor region and the diode region that is adjacent to a termination region. A gate electrode in the gate pad region and the gate wiring region is formed on an insulating film that is formed on an epitaxial layer. Consequently, dielectric breakdown of the insulating film in the gate region can be suppressed at the time of switching or avalanche breakdown without decreasing the quality of the gate insulating film.

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

Formation method of semiconductor structure

InactiveCN105702619AImprove hydrophobicityImprove corrosion resistanceSemiconductor/solid-state device manufacturingCorrosionSemiconductor structure

Provided is a formation method of a semiconductor structure. The method includes: a substrate and a dielectric layer positioned on the surface of the substrate are provided, and a bottom metal layer is arranged in the substrate; the dielectric layer is etched to form an opening penetrating through the dielectric layer, and the surface of the bottom metal layer is exposed at the bottom of the opening; pre-restoration irradiation processing of the dielectric layer at sidewalls of the opening is performed, and contact angles on the surface of the dielectric layer at the sidewalls of the opening are increased; after the pre-restoration irradiation processing, wet-process cleaning processing of the opening is performed; and a conductive layer filling the opening is formed. According to the method, the contact angles on the surface of the dielectric layer at the sidewalls of the opening are increased, the hydrophobicity capability of the surface of the dielectric layer at the sidewalls of the opening is improved, the corrosion of the dielectric layer at the sidewalls of the opening due to the wet-process cleaning processing is avoided, the breakdown voltage is increased, the problem of time dependent dielectric breakdown is suppressed, and the reliability and the electrical performance of the semiconductor structure are enhanced.

Owner:SEMICON MFG INT (SHANGHAI) CORP

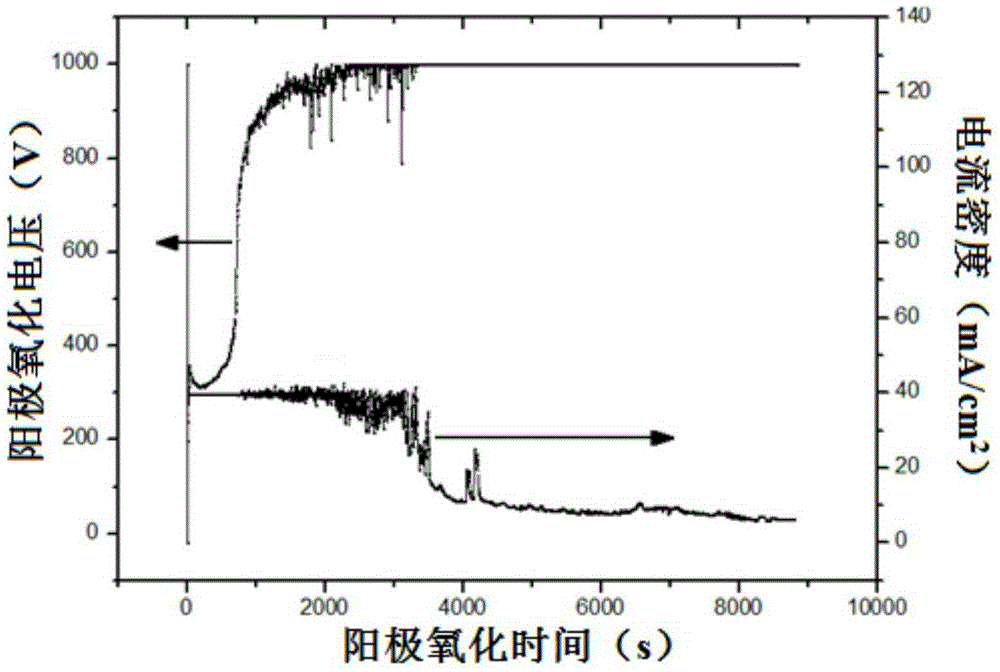

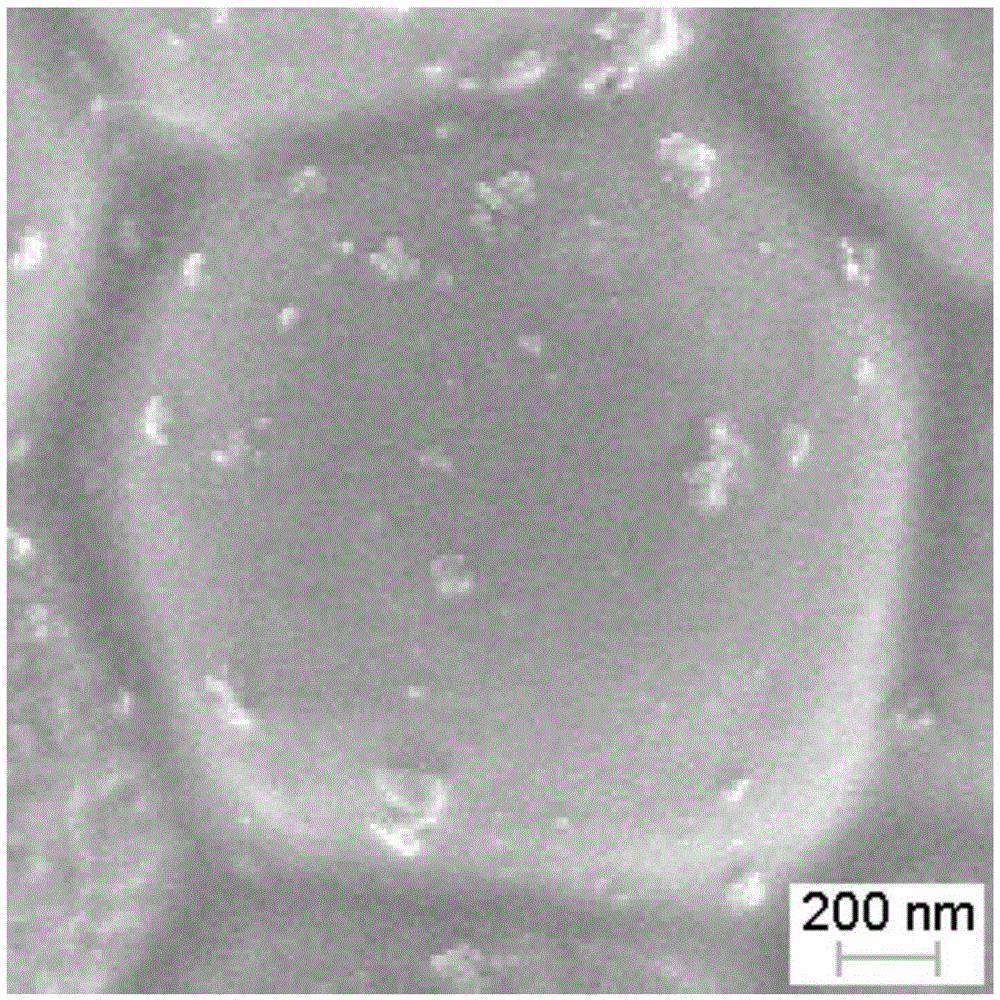

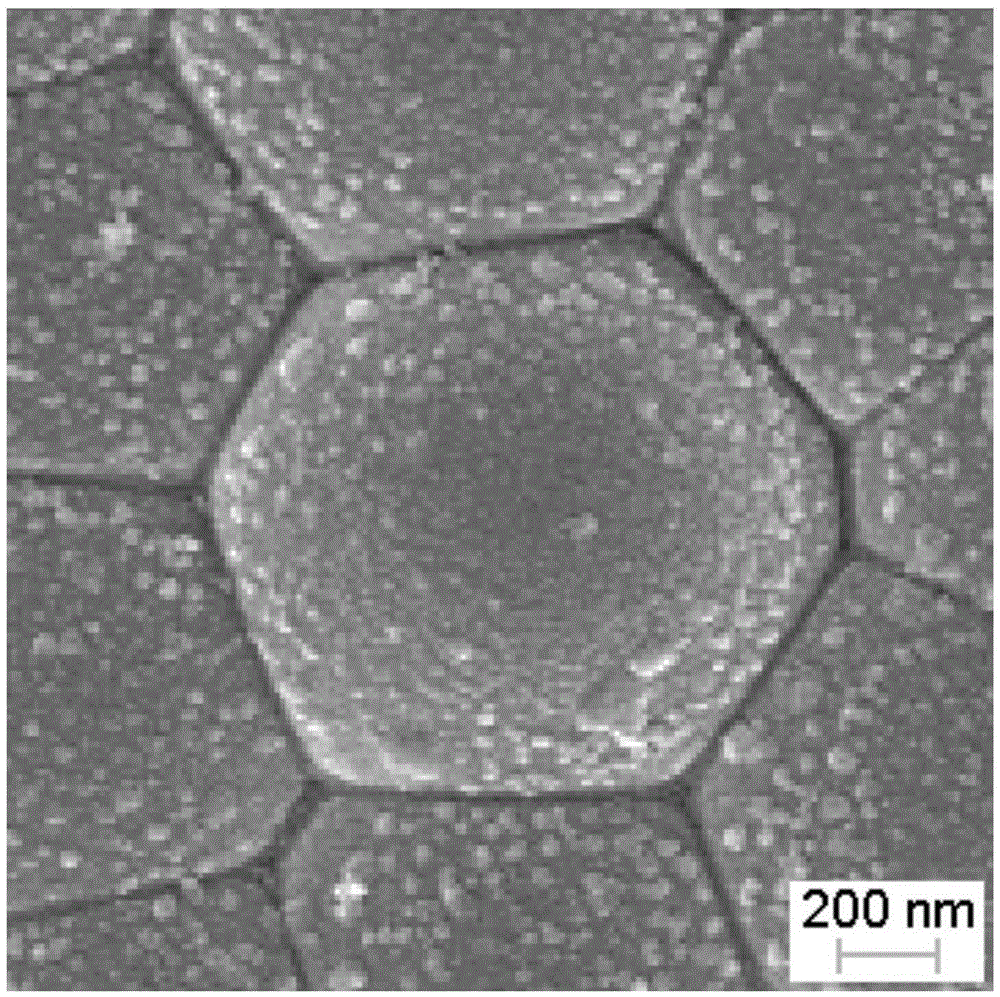

Method for preparing large-hole-interval porous anodic alumina membrane at high voltage

InactiveCN105297106ASuppress breakdownAchieving controllable equipmentSurface reaction electrolytic coatingConstant current densityHigh voltage

The invention discloses a method for preparing a large-hole-interval porous anodic alumina membrane at high voltage. The method includes the steps that a high pure aluminum sheet is subjected to electrochemical polishing after being washed; the polished aluminum sheet serves as an anode, graphite serves as a cathode, the anode oxidation process is performed while an oxalic acid-ethanol-water mixed solution serves as an electrolyte, and high anode oxidization voltage is obtained by performing self-adaption boosting under constant current density; a sample obtained through anode oxidization is soaked in a saturated copper chloride solution, then the large-hole-interval porous anodic alumina membrane is obtained, and the average hole interval of the prepared porous anodic alumina membrane is regulated and controlled by adjusting the ethanol adding proportion, the anode oxidization voltage and the current density. The large hole interval size of the prepared porous anodic alumina membrane is adjustable so that the porous anodic alumina membrane can serve as a template to synthesize various functional submicron and micron materials. Meanwhile, the large-hole-interval porous anodic alumina membrane has the advantages that raw materials are easy to obtain, operation is easy, cost is low, and repeatability is good, and feasibility is improved when the large-hole-interval porous anodic alumina membrane is applied to production.

Owner:SOUTH CHINA UNIV OF TECH

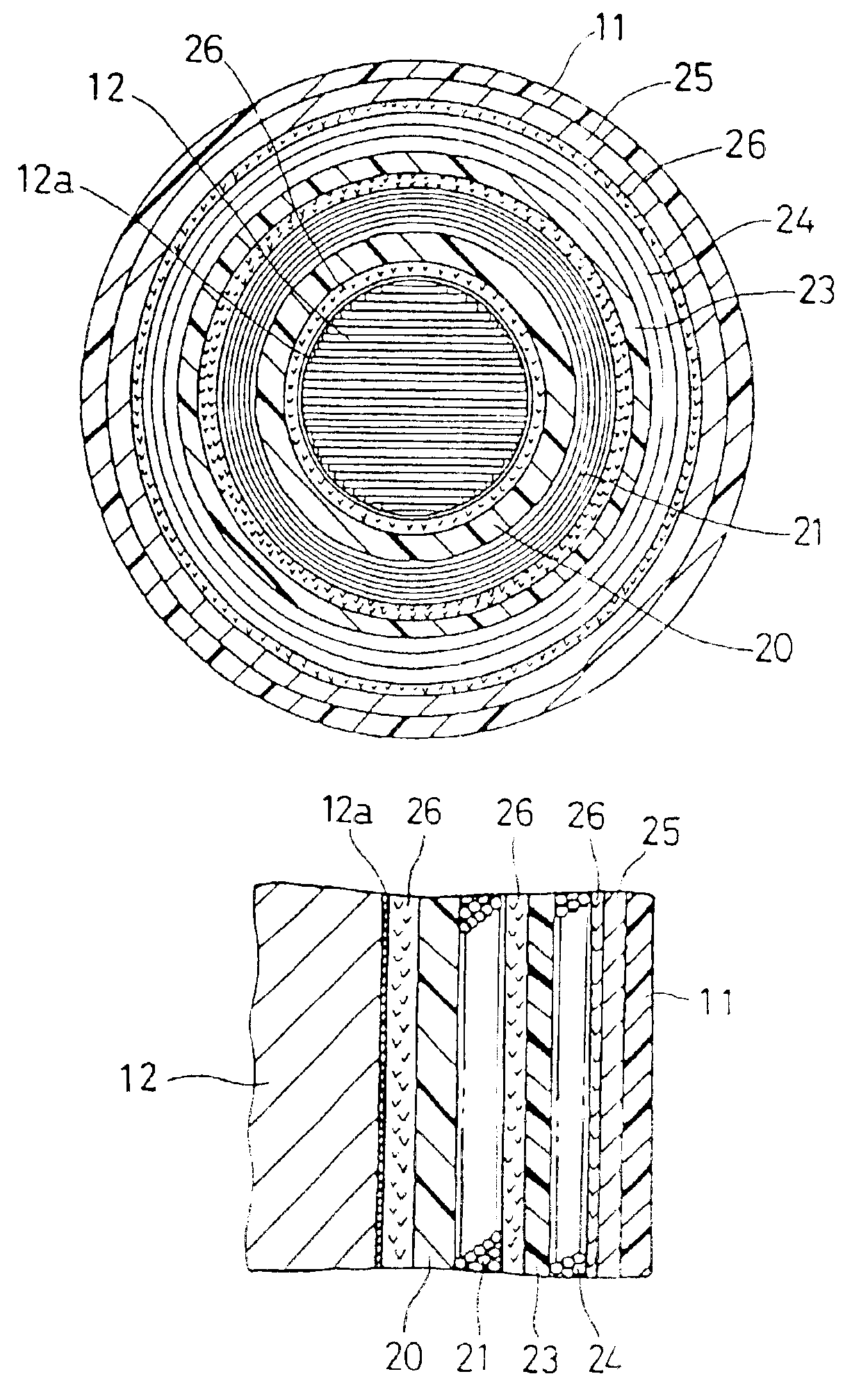

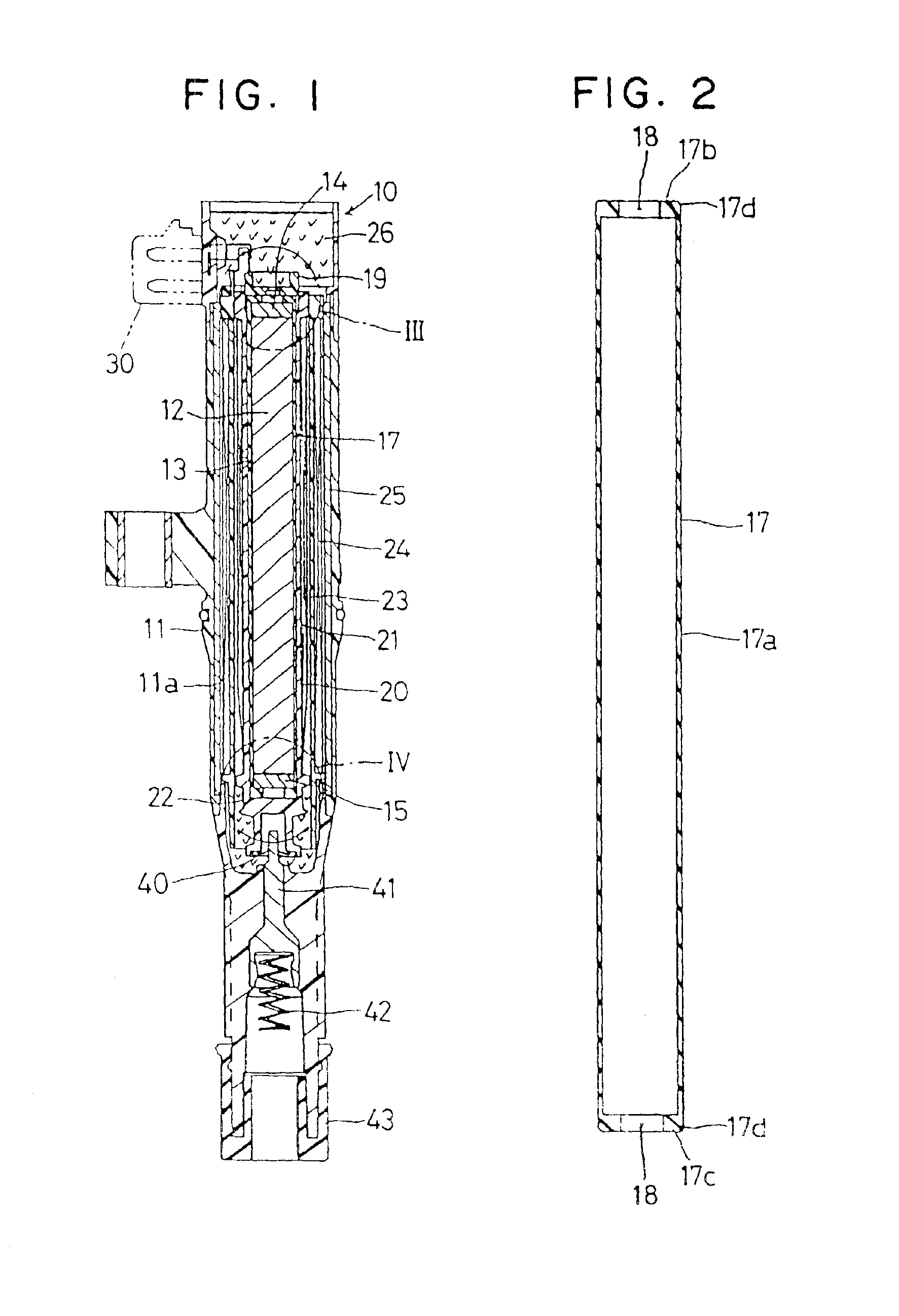

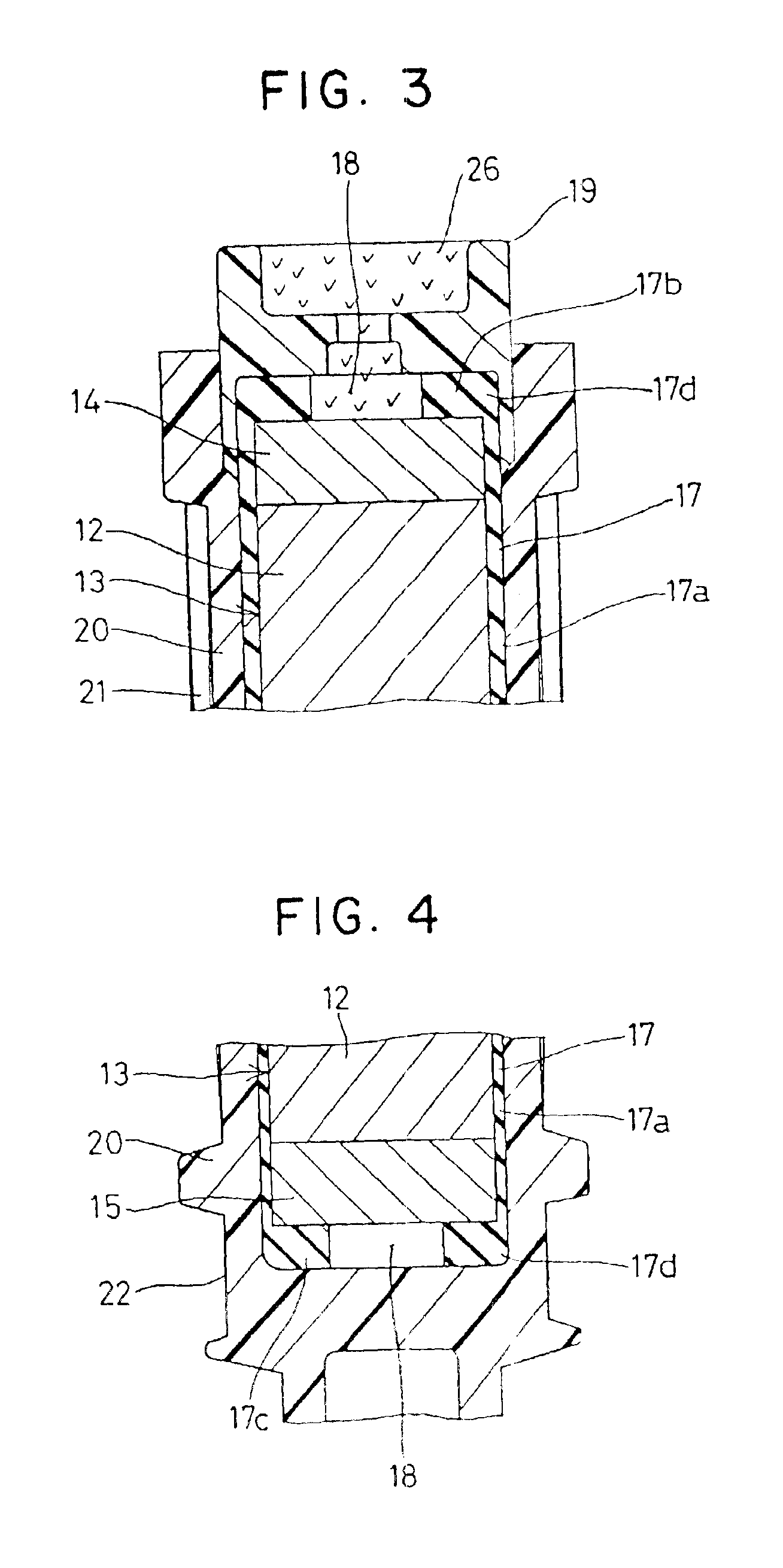

Stick-type ignition coil having improved structure against crack or dielectric discharge

InactiveUS7071804B2Suppress breakdownPrevent crackingTransformersTransformers/inductances casingsIgnition coilOuter core

A stick-type ignition coil have a central core, a cylindrical member, primary spool, primary coil, secondary spool, secondary coil, outer core and a resin insulator. The two longitudinal end corners and faces of the core are covered by respective buffer members. The inner circumferential corners of the outer core is supported by ring members. Some of the members disposed radially inside and other members disposed radially outside of the inside members are held slidably to each other in the ignition coil. The spools are made of resin containing a rubber in excess of 5 weight percent and reinforcing materials. The resin insulator contains a flexible material.

Owner:DENSO CORP

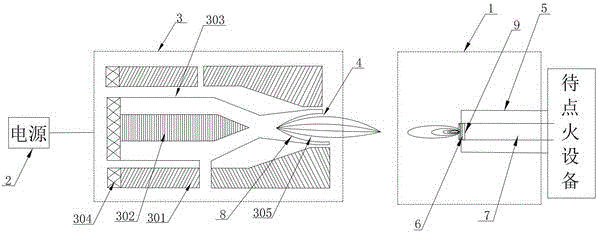

Non-impact self-adaptive trigger ignition device utilizing laminar flow plasma system

ActiveCN106304593AAchieve one ignitionAvoid arc breakingElectric spark ignitersPlasma techniquePlasma jetPlasma generator

The invention discloses a non-impact self-adaptive trigger ignition device utilizing a laminar flow plasma system, and belongs to the technical field of ignition equipment. The non-impact self-adaptive trigger ignition device comprises the laminar flow plasma system and an ignition nozzle. The laminar flow plasma system comprises a power supply, a laminar flow plasma generator and a jet nozzle, wherein the power supply is connected with the laminar flow plasma generator, and the jet nozzle and the laminar flow plasma generator are connected detachably. The ignition nozzle is arranged on equipment to be ignited, and comprises a shell, an ignition electrode and a guide tube, wherein the ignition electrode is arranged at the front end of the guide tube, the guide tube extends into the equipment to be ignited, and the shell is arranged outside the ignition electrode and the guide tube. The central axis of the jet nozzle coincides with the central axis of the ignition nozzle. The central axes of an electric arc channel, the jet nozzle and the ignition nozzle coincide, plasma is emitted along the central axis, an electric arc guidance effect is achieved through the design, the ignition steps are simplified, the ignition difficulty is reduced, ignition is achieved at a time with working gas, and meanwhile stability of laminar flow electric arc hot plasma jet is ensured.

Owner:四川金虹等离子技术有限公司

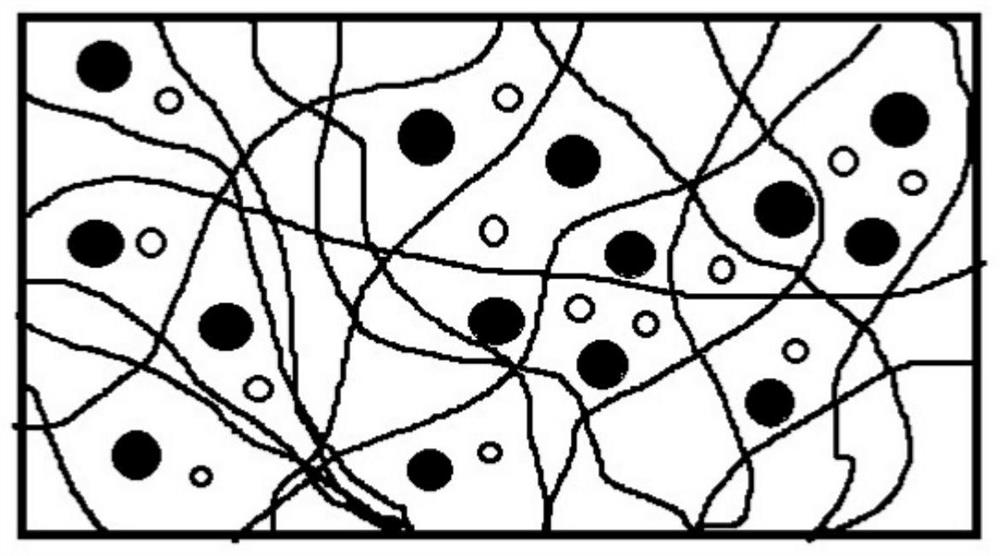

Junction barrier Schottky diode with a floating field ring terminal structure and a preparation method thereof

InactiveCN110364575AImprove featuresImprove leakage performanceSemiconductor/solid-state device manufacturingDiodeOhmic contactSchottky diode

The invention provides a junction barrier Schottky diode with a floating field ring terminal structure and a preparation method thereof, and belongs to the technical field of semiconductors. The diodecomprises a ohmic contact metal cathode, a substrate, a first epitaxial layer, a second epitaxial layer, a comb-shaped p region, a Schottky contact metal anode and an insulating layer from the bottomup, wherein the comb-shaped p region includes a plurality of PN junction p regions arranged at intervals and a plurality of floating field rings arranged at intervals on two sides of the outer side PN junction p regions. The invention further provides a preparation method of the junction barrier Schottky diode with the floating field ring terminal structure. The diode adjusts the electric field distribution through the comb-shaped PN junction structure, avoids the concentration of the electric field, disperses the electric field concentrated at the edge of the P-type region among a pluralityof field rings and reduces the maximum value of the electric field. In addition, the appropriate field ring width and gap are selected, and the electric field concentrated at the outmost field ring can be dispersed among the field rings, thereby avoiding the device breakdown caused by the excessively high local electric field.

Owner:CHANGCHUN INST OF OPTICS FINE MECHANICS & PHYSICS CHINESE ACAD OF SCI

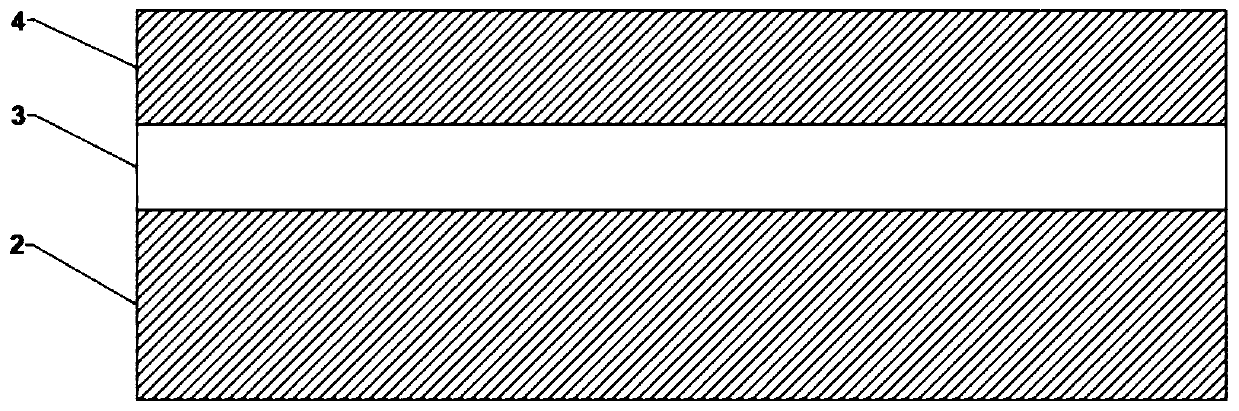

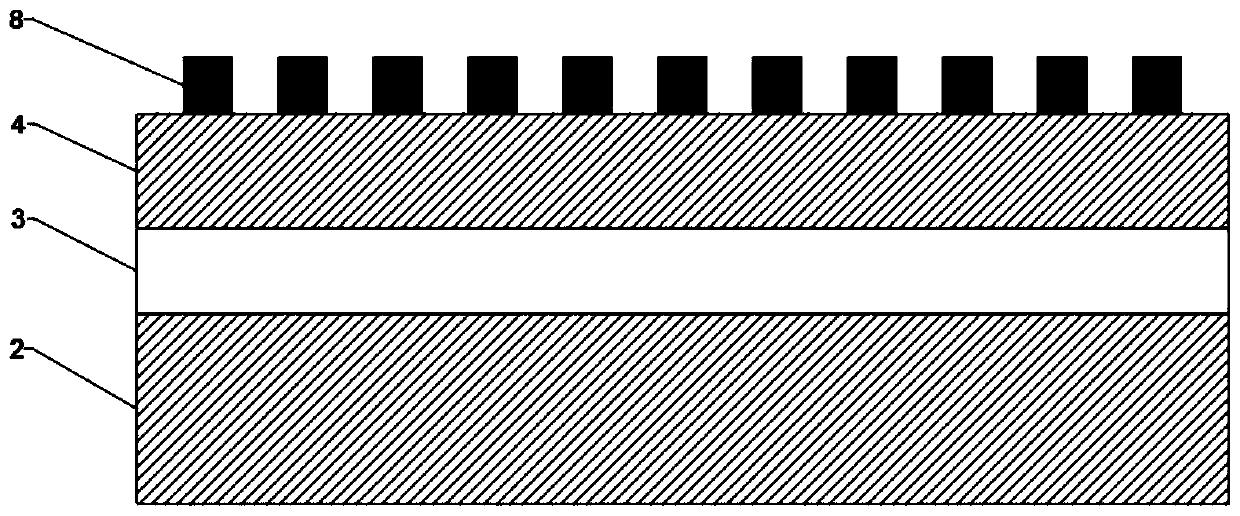

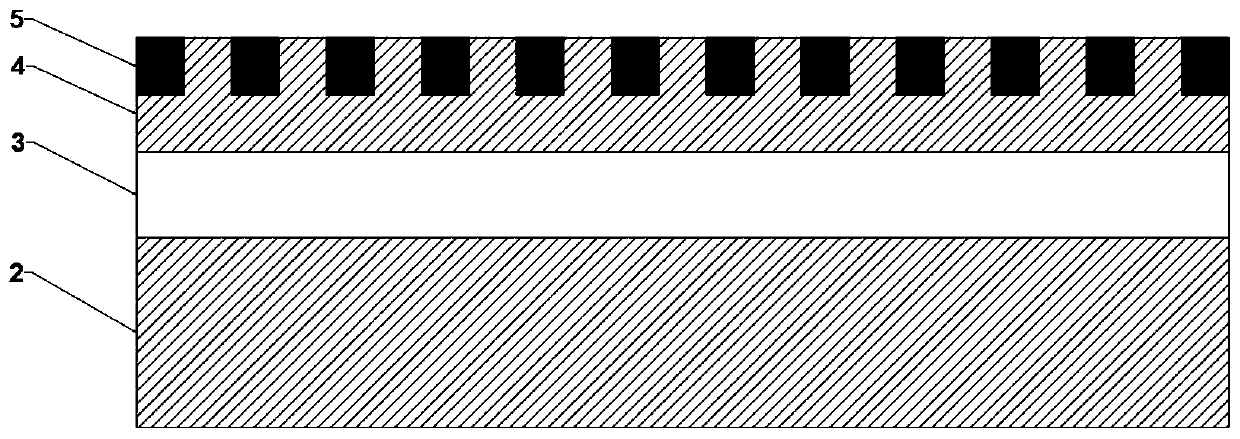

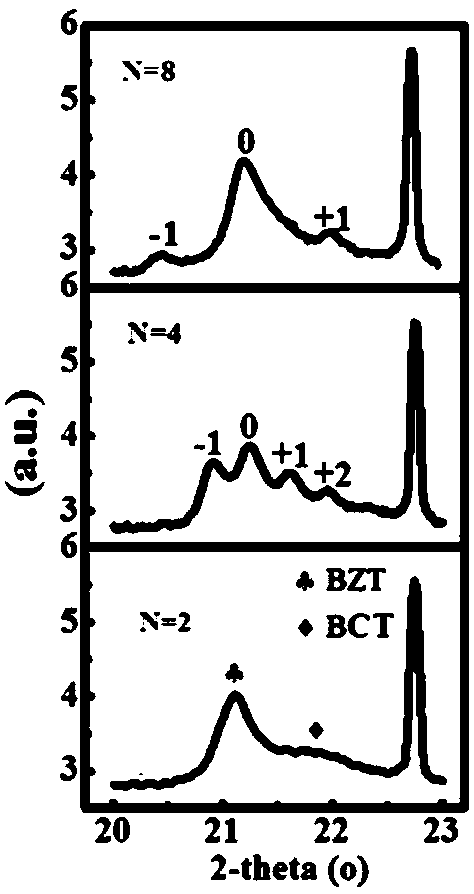

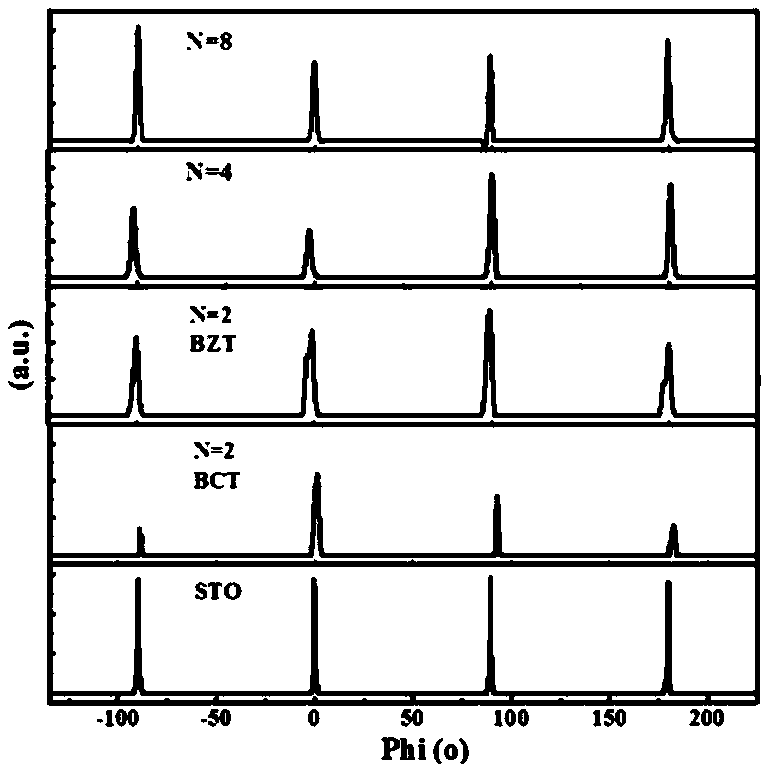

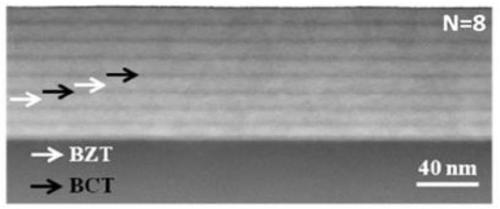

BCT/BZT-system lead-free monocrystal epitaxial multilayer energy storage film and preparation method thereof

InactiveCN109056068AImprove energy efficiencyIncreased hindrancePolycrystalline material growthFrom condensed vaporsHigh energyRadio frequency magnetron sputtering

The invention discloses a BCT / BZT-system lead-free monocrystal epitaxial multilayer energy storage film and a preparation method thereof. The preparation method has the advantages that the radio frequency magnetron sputtering technology is adopted, a BCT / BZT multilayer film is obtained on a substrate through plasma bombardment of target materials, films with different periods but same thicknessesare prepared through regulation of the sputtering time of the two target materials, the obtained films can have epitaxial multilayer heterostructures, part of the current paths can be stopped at the interfaces, and breakdown is effectively suppressed; as the interfaces increase, the hindrance effect of internal current branches on materials is enhanced, so that the energy storage film prepared bythe method has extremely high energy efficiency while the huge energy storage density is achieved; the energy efficiency of 8-cycle samples is more than 65%, most of them are more than 70%, and the efficiency of 4-cycle samples can be more than 80%.

Owner:XI AN JIAOTONG UNIV

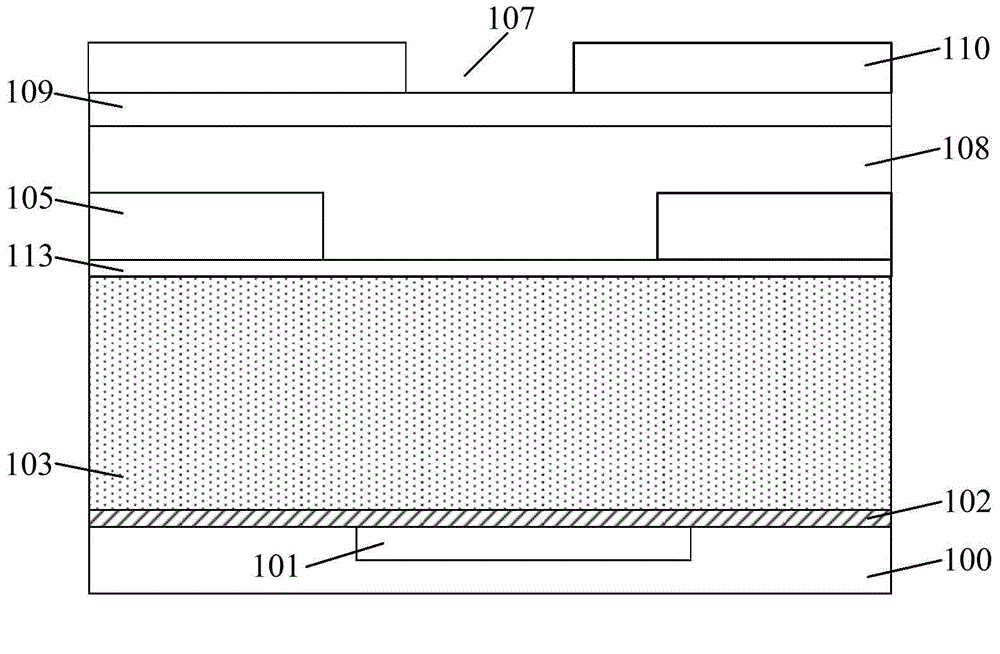

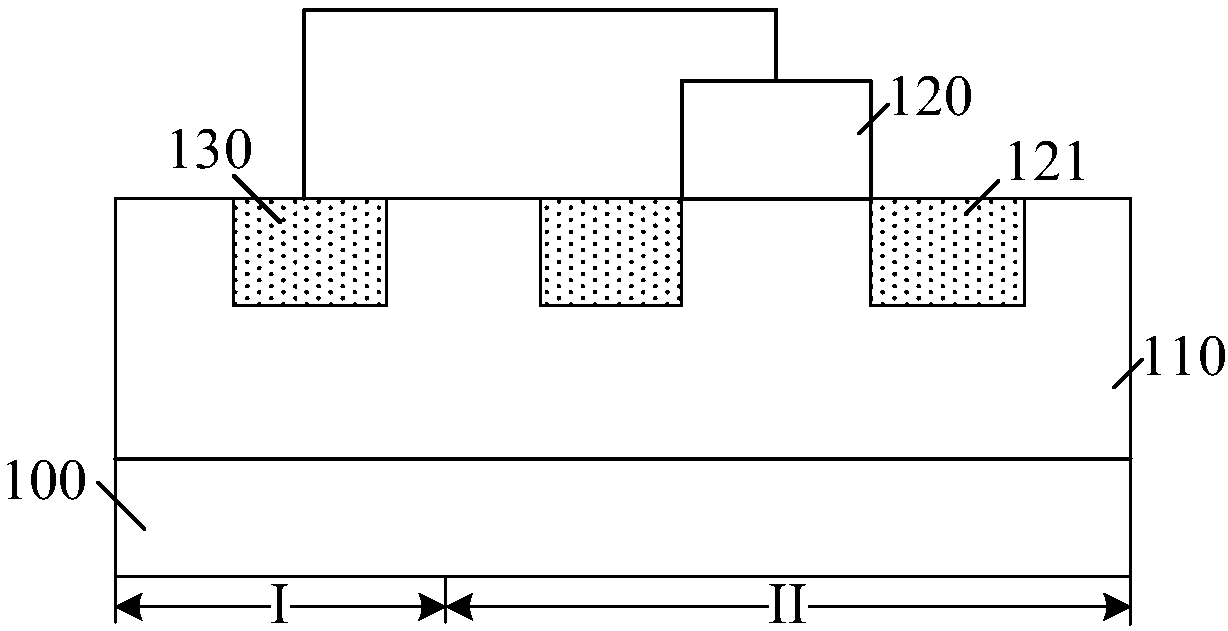

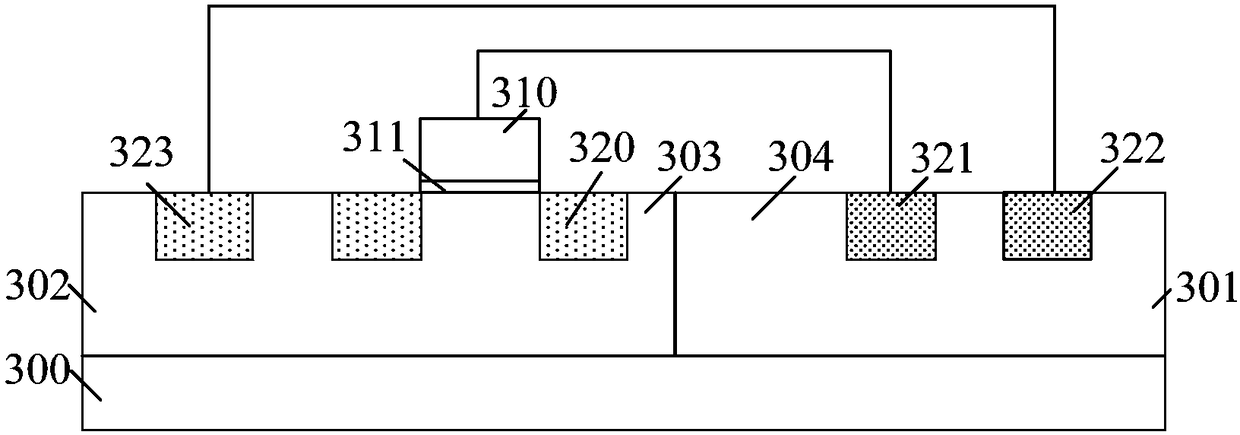

Semiconductor structure and forming method thereof

ActiveCN109037195AReduce the impactReduce voltageTransistorSemiconductor/solid-state device detailsSemiconductor structureTransistor

The invention provides a semiconductor structure and a forming method thereof, wherein, the method comprises the following steps: a substrate; a first well region, a second well region, a third well region and a fourth well region located between the third well region and the first well region which are located in the substrate, the third well region and the second well region being the same in conductivity type of doped ions and the fourth well region and the third well region being opposite in conductivity type of doped ions; a device structure located on the third well region; a first dopedregion and a second doped region located in the first well region, the first doped region and the second doped region being separate, the conductivity type of the doped ions in the first doped regionand the second doped region being opposite to that of the first well region, the first doped region being electrically connected to the device structure; a third doped region located in the second well region, the third doped region being electrically connected to the second doped region. The first doped region, the first well region and the second doped region form a transistor, which can improve the performance of the semiconductor structure.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Formation method for semiconductor structure

ActiveCN106206408AAvoid etch damageGood interface performanceSemiconductor/solid-state device manufacturingCorrosionSemiconductor structure

Disclosed is a formation method for a semiconductor structure. The formation method comprises the steps of providing a substrate and a dielectric layer which is positioned on the surface of the substrate, wherein a bottom layer metal layer is formed in the substrate; etching the dielectric layer to form an opening which runs through the dielectric layer, wherein the surface of the bottom layer metal layer is exposed out of the bottom of the opening; performing etching post-processing on the opening by adopting an H<2>-containing gas; forming a silicon layer on the surface of the side wall of the opening after the etching post-processing is carried out; after the silicon layer is formed, performing wet cleaning processing on the opening; and forming a conductive layer, wherein the opening is filled with the conductive layer. By adoption of the formation method, when the impurities in the opening are removed, corrosion to the dielectric layer on the side wall of the opening is avoided in the process of the wet cleaning processing, so that the breakdown voltage is increased; the time dependent dielectric breakdown problem is restrained; and the reliability and the electrical performance of the semiconductor structure are improved.

Owner:SEMICON MFG SOUTH CHINA CORP +1

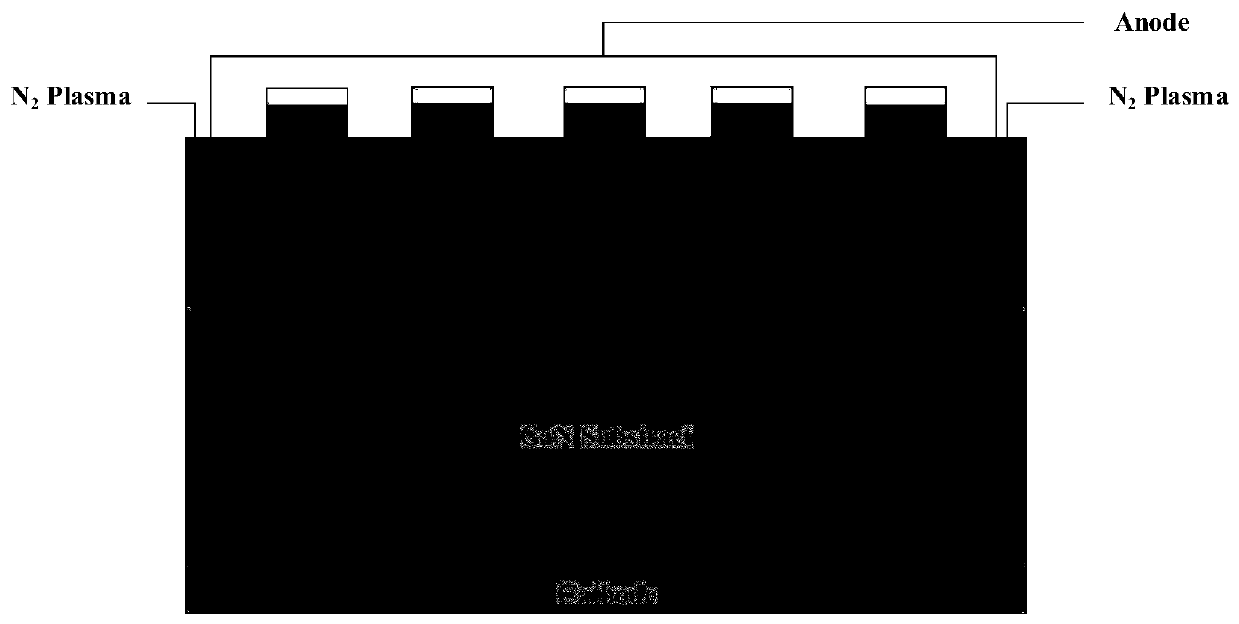

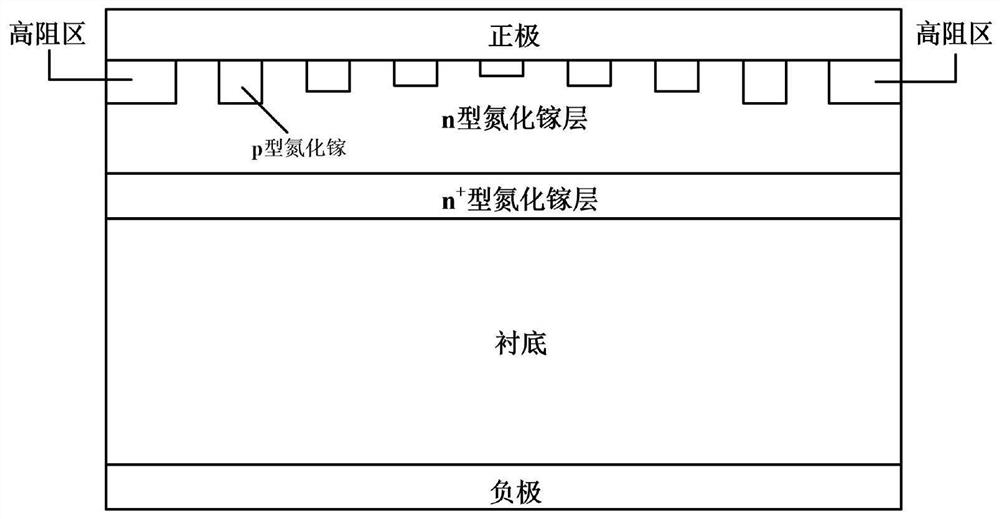

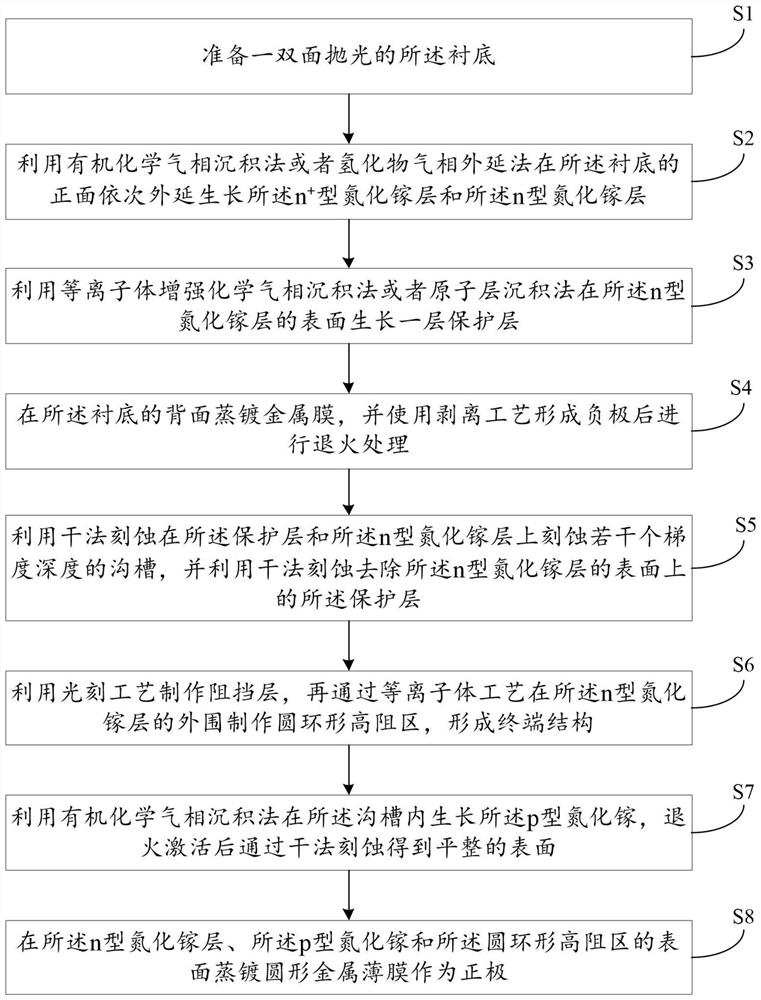

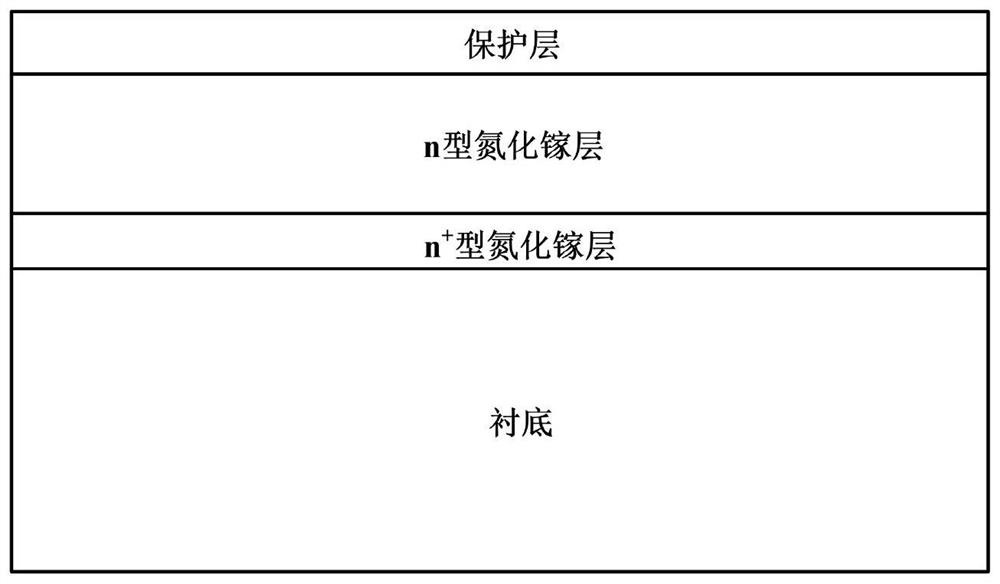

Novel GaN junction barrier Schottky diode and preparation method thereof

InactiveCN110752260AImprove performanceGood effectSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactSchottky diode

The invention discloses a novel GaN junction barrier Schottky diode and a preparation method thereof, which provides a new way for improving the performance of the Schottky diode by utilizing a noveldesign and a relatively simple and easily-achieved process. The novel GaN junction barrier Schottky diode sequentially comprises a cathode, a substrate, an n+ type GaN epitaxial layer, an n type GaN epitaxial layer, a high-resistance region, a comb-shaped p type GaN epitaxial layer, a comb-shaped p+ type GaN epitaxial layer and an anode from bottom to top, wherein plasmas are annularly injected into the outer edge of the n type GaN epitaxial layer to form the high-resistance region. According to the invention, p-type GaN does not need to be grown in the n-type GaN layer and a subsequent activation process is not needed, so that the process difficulty and the complexity are greatly reduced. Through the four layers of epitaxial GaN structures, good ohmic contact and better PN junctions can be formed, the forward on resistance is reduced, the reverse breakdown voltage is increased, and the performance of the device is effectively improved. In addition, the high-resistance region formed byN2 Plasma can effectively inhibit breakdown of the device at the edge of an electrode under high voltage, and the breakdown performance is enhanced.

Owner:CHANGCHUN INST OF OPTICS FINE MECHANICS & PHYSICS CHINESE ACAD OF SCI

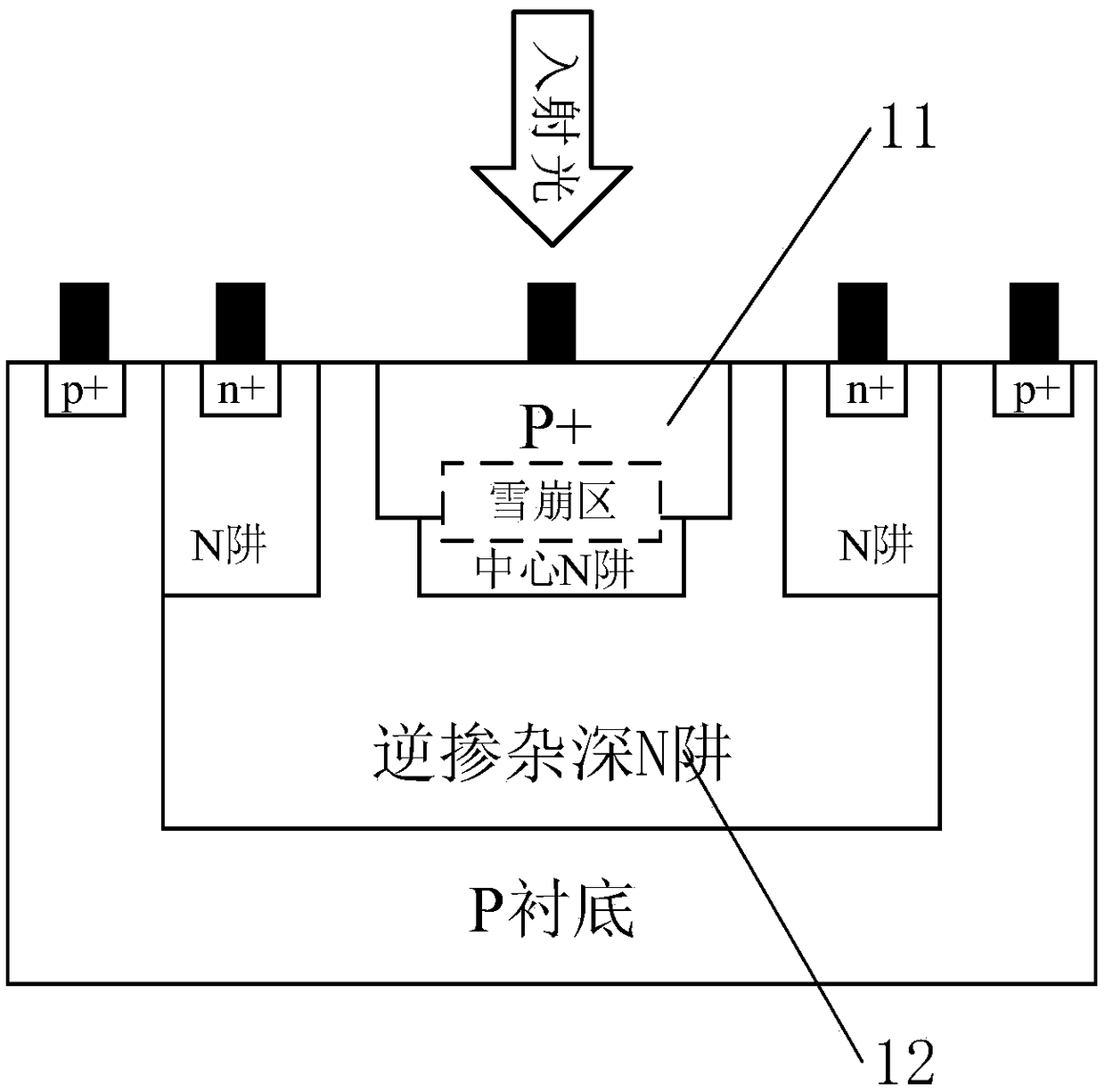

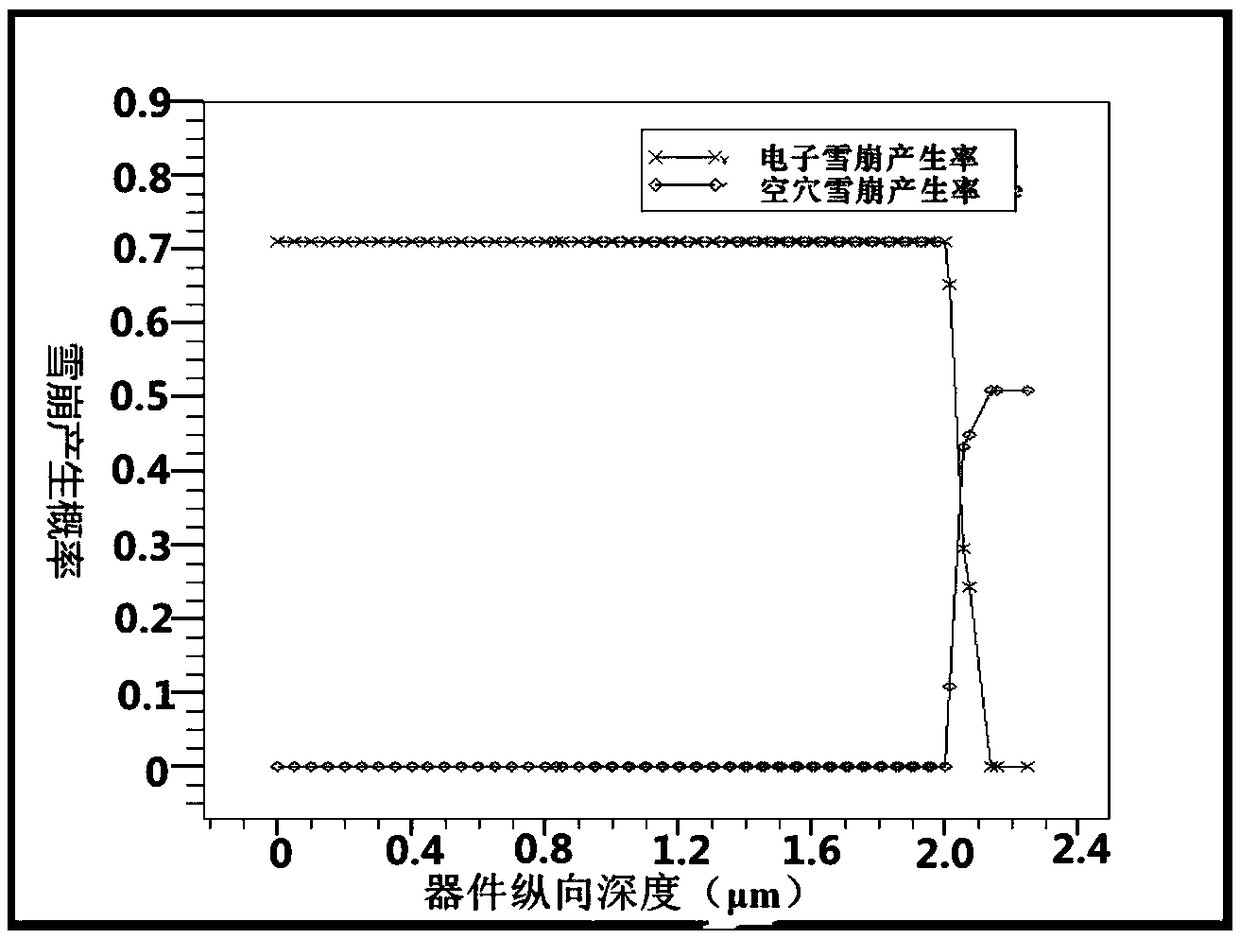

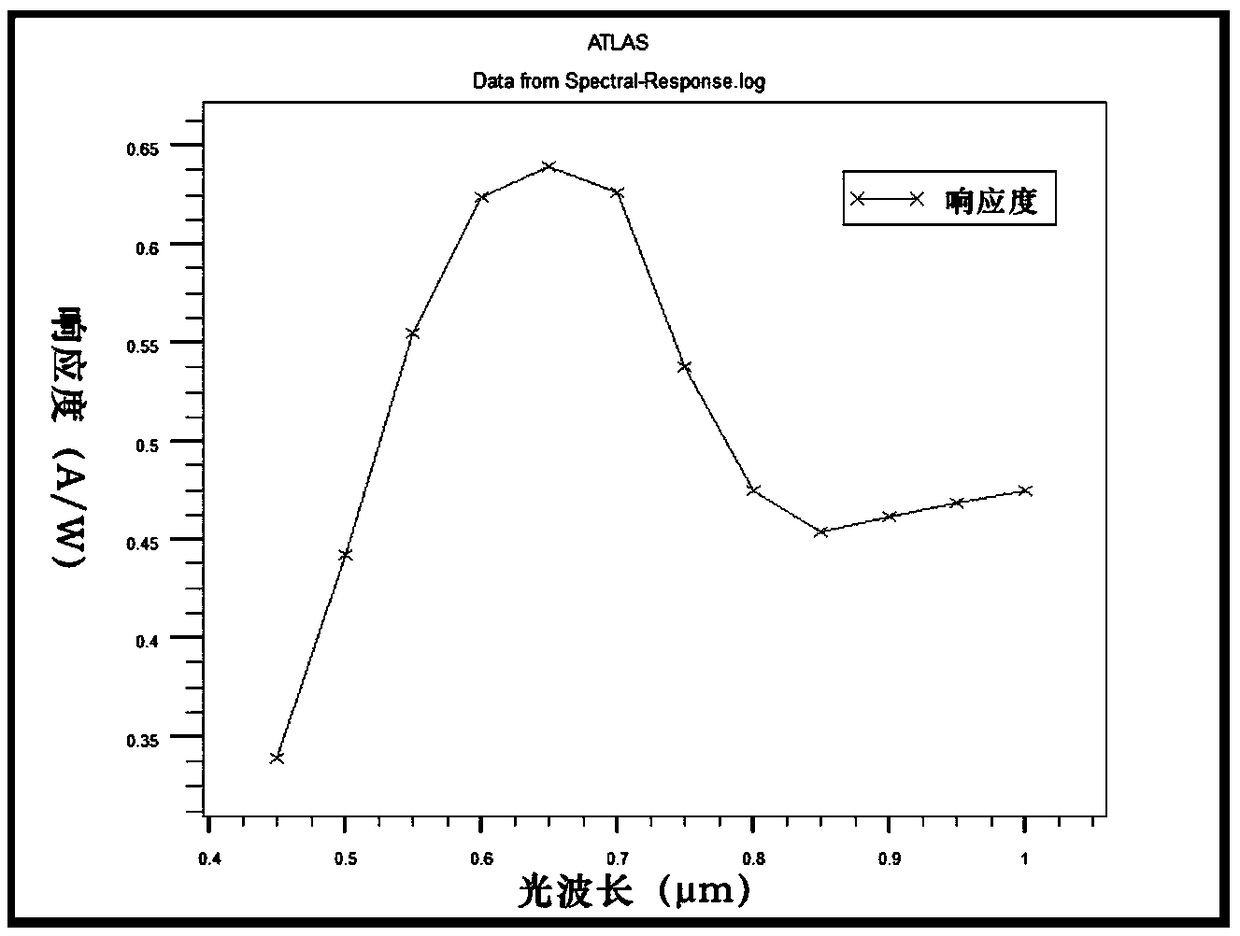

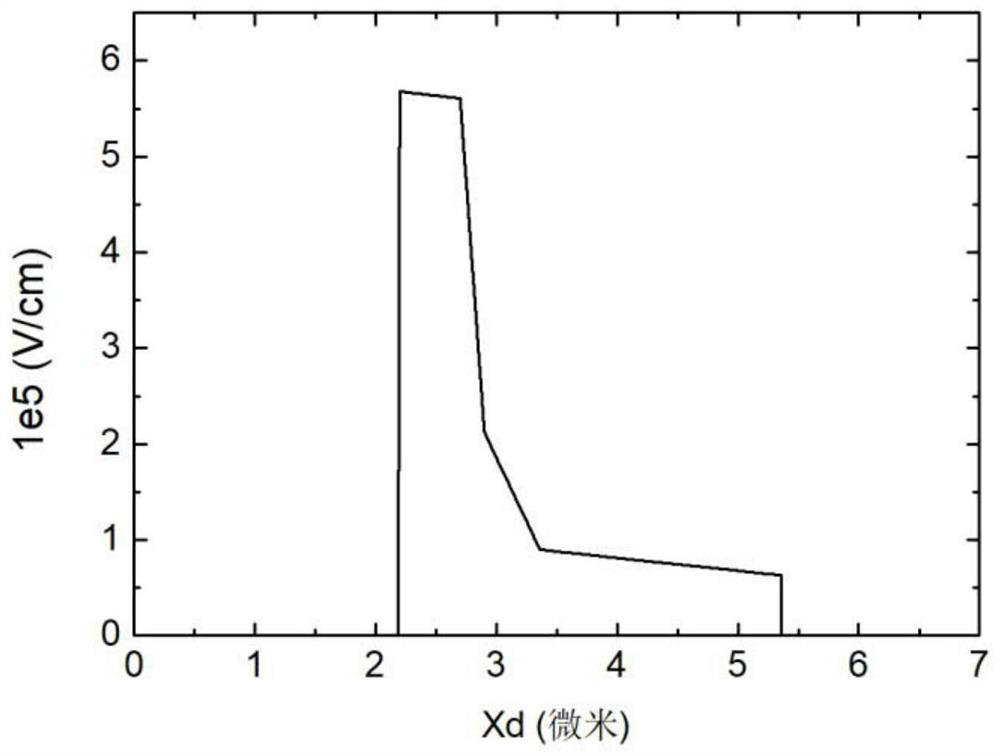

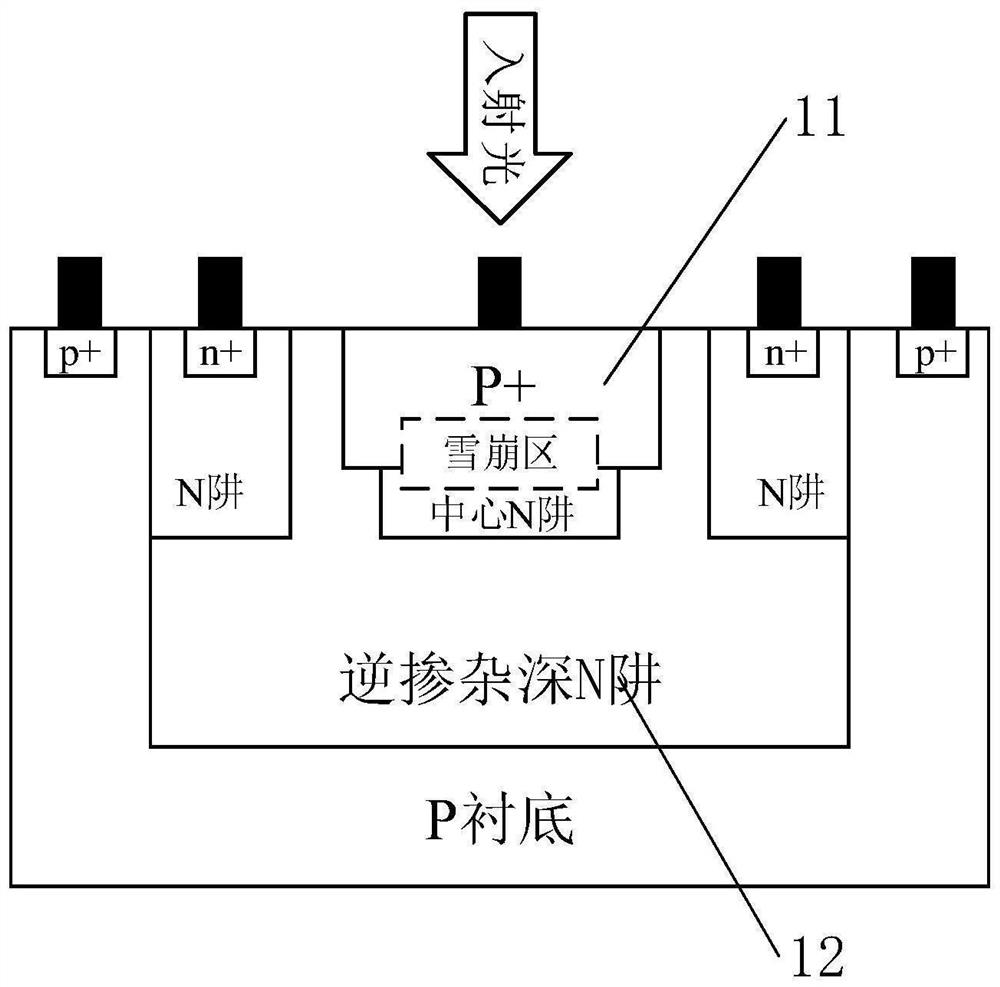

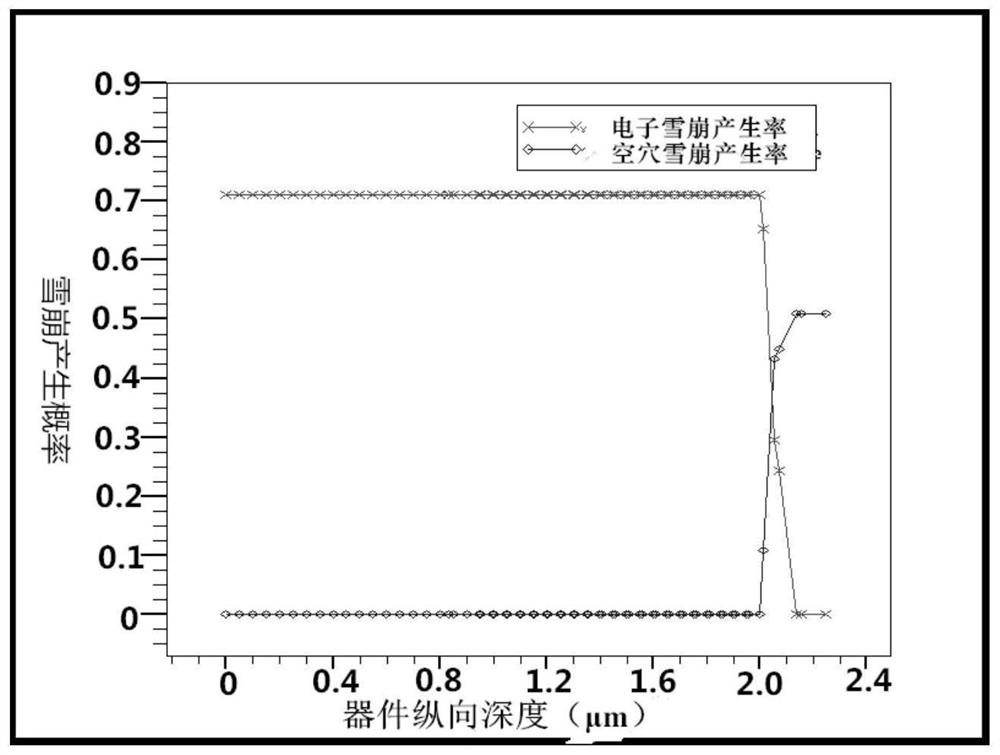

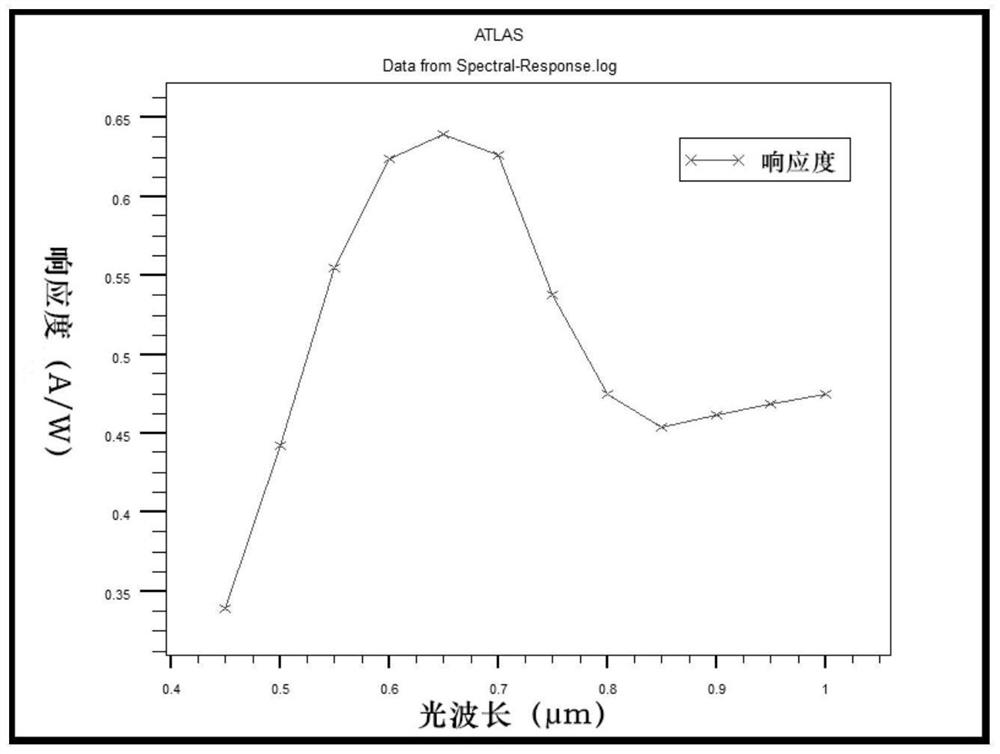

CMOS SPAD (Single Photon Avalanche Diode) photoelectric device with deep N well adopting inverse doping distribution

InactiveCN109285901AImprove detection efficiencyReduce utilizationSemiconductor devicesCMOSQuantum efficiency

The invention relates to a CMOS SPAD (Single Photon Avalanche Diode) photoelectric device with a deep N well adopting inverse doping distribution, which comprises a P substrate, wherein the P substrate is provided with a deep N well, a central N well and a P+ layer, two sides of the deep N well are provided with N wells, the deep N well adopts an inverse doping distribution structure, that is, thedeep N well close to the device surface is low in concentration and the concentration of the deep N well increases along the increase in vertical depth away from the device surface, the transverse diffusion exists between the two lateral N wells and the central N well in the deep N well, an n- virtual protection ring is formed at the edge of a PN junction, incident photons are mainly absorbed bythe deep N well when shooting to the internal part of the device, most of the photons can be utilized by the P+ layer / central N well junction to form photon-generated carriers, and only a few of the photons penetrate through the deep N well and form photon-generated carriers on the P substrate. The photon detection efficiency of the device is improved by mainly increasing the thickness of an absorption region of the device and optimizing the quantum efficiency of the device.

Owner:重庆亚川电器有限公司

4H-SiC metal semiconductor field effect transistor with lightly doped gate edge drain side portion

ActiveCN109524474AAlleviate the effect of electric field concentrationSuppress breakdownTransistorElectric fieldSemi insulating

The invention discloses a 4H-SiC metal semiconductor field effect transistor with a lightly doped gate edge drain side portion. The 4H-SiC metal semiconductor field effect transistor comprises a 4H-SiC semi-insulating substrate, a P-type buffer layer and an N-type channel layer from the bottom to top. Two sides of the upper surface of the N-type channel layer are provided with a source electrode cap layer and a drain cap layer, a source electrode is arranged on the upper surface of the source cap layer, a drain electrode is arranged on the upper surface of the drain cap layer, the bottom of the N-type channel layer is provided with a gate electrode at one side adjacent to the source cap layer, a lightly doped region is formed under the gate of partial gate electrode and partial gate drainon the N-type channel layer, and the lightly doped region is an axisymmetric structure of a vertical line of a gate edge of a gate electrode drain side. According to the 4H-SiC metal semiconductor field effect transistor, the electric field concentration effect on the drain side of the gate edge can be alleviated so as to optimize the electric field and current on the drain side of the gate edge,therefore, the breakdown is suppressed, a thermal electron charging effect can be alleviated so as to reduce an interface state, the degradation of the device performance is suppressed, and thereforethe life of the device is improved.

Owner:XIDIAN UNIV

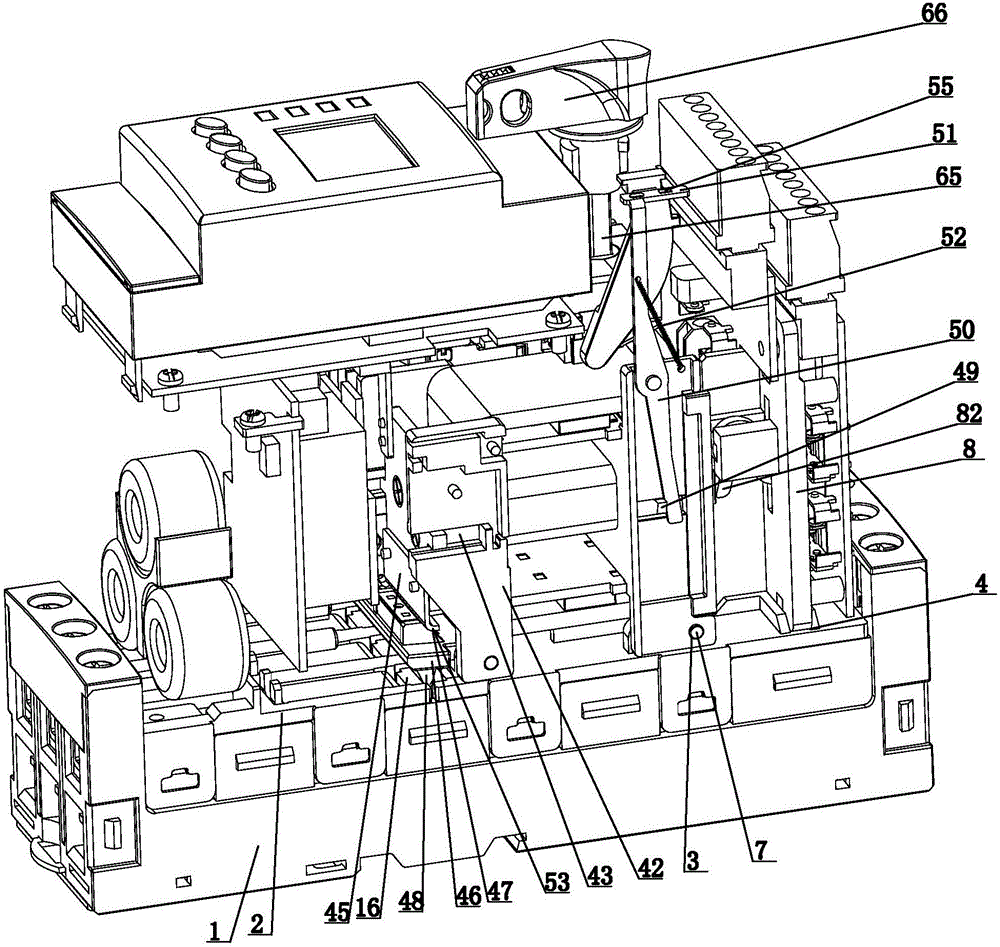

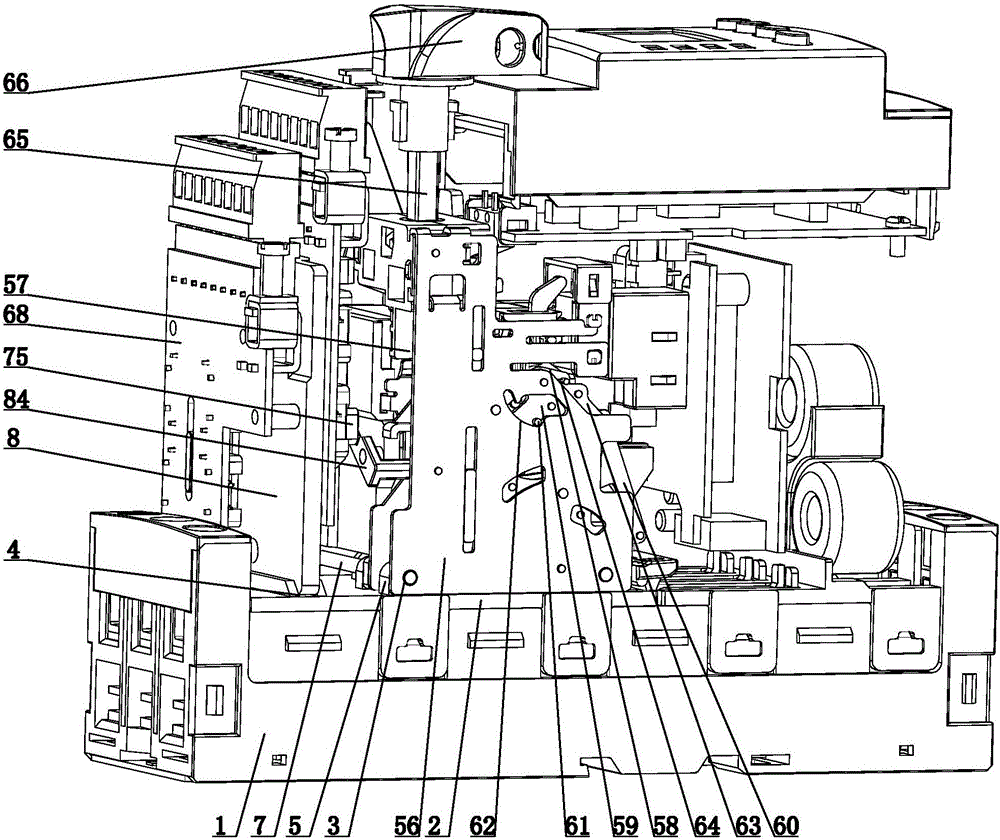

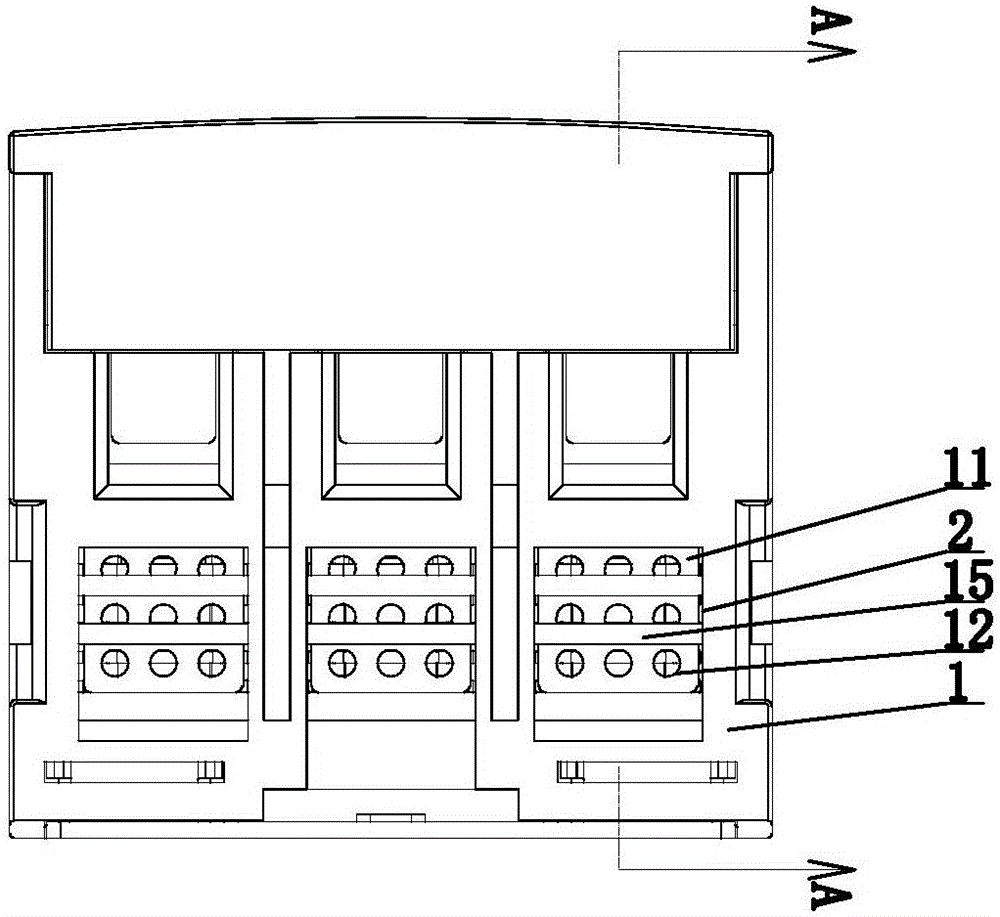

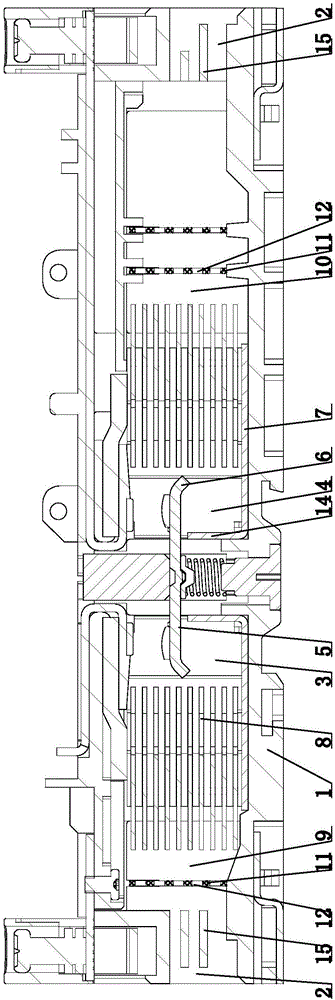

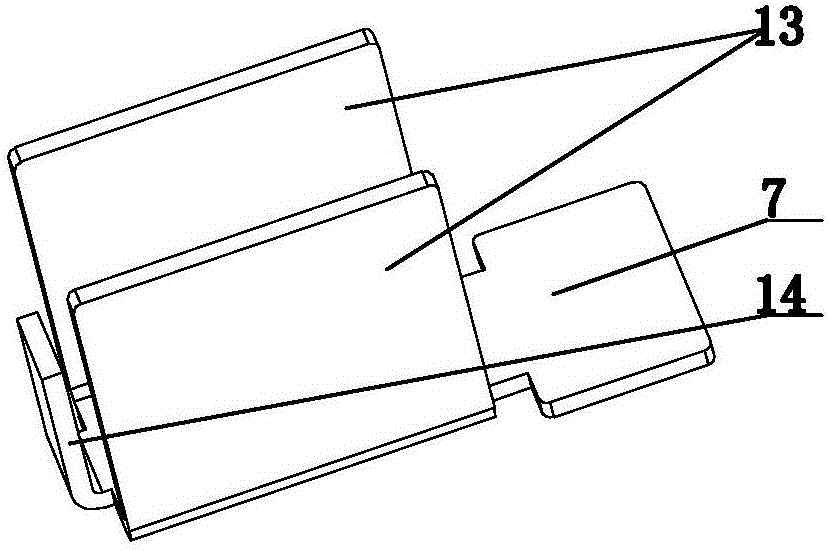

Control and protection switch electric appliance

ActiveCN106409620AStable structureEasy to assemble and disassembleCircuit-breaking switch detailsProtective switch operating/release mechanismsComputer moduleEngineering

The invention discloses a control and protection switch electric appliance. The electric appliance comprises a pedestal module, an electromagnet module, an operation module and an auxiliary module, wherein the electromagnet module, the operation module and the auxiliary module are arranged on the pedestal module. The electric appliance is characterized in that the pedestal module includes a pedestal and a cover plate which is detachably arranged on the pedestal; two sides of the electromagnet module and the operation module are provided with a plurality of first through holes which are coaxially arranged; the cover plate is provided with a slot and a plurality of installation seats which can be cooperated with the first through holes; the installation seats are provided with second through holes aligning at the first through hole; the first through hole and the second through holes are fixed through pins; the auxiliary module includes a support plate which can be inserted into the slot; peripheries of the electromagnet module, the operation module and the auxiliary module are provided with shells; and the shell is detachably arranged on the pedestal. By using the control and protection switch electric appliance provided in the invention, the structure is simple and compact, a three phase short circuit is not easy to generate, stability is good, assembling and maintenance are convenient and a service life is long.

Owner:浙江新控电气科技有限公司

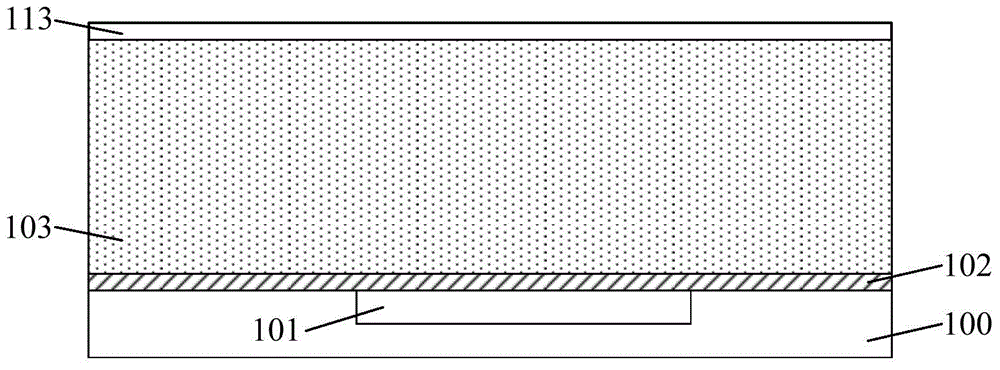

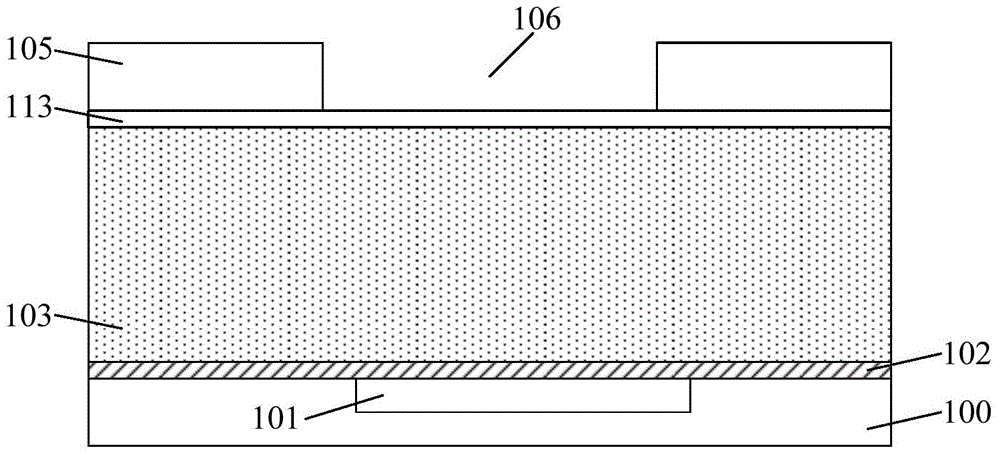

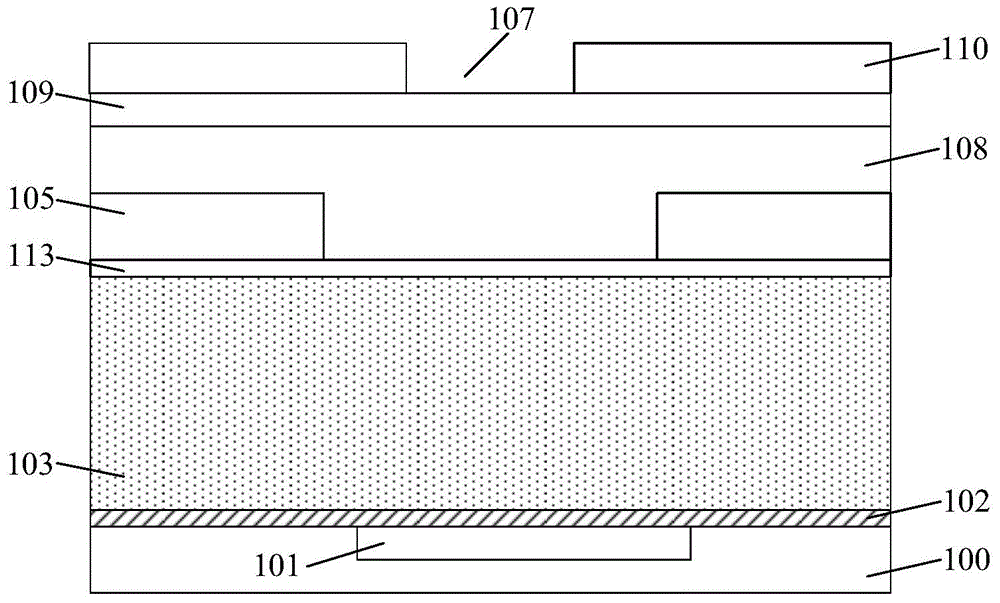

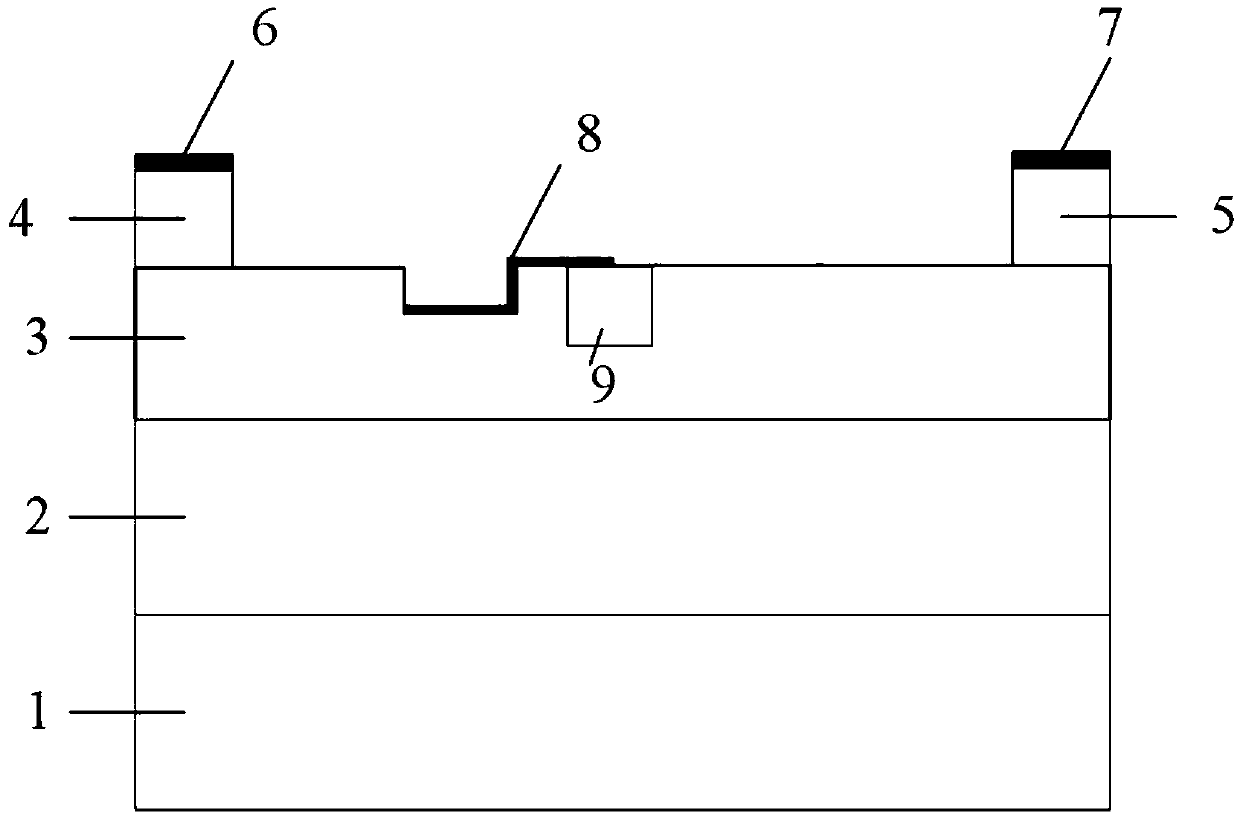

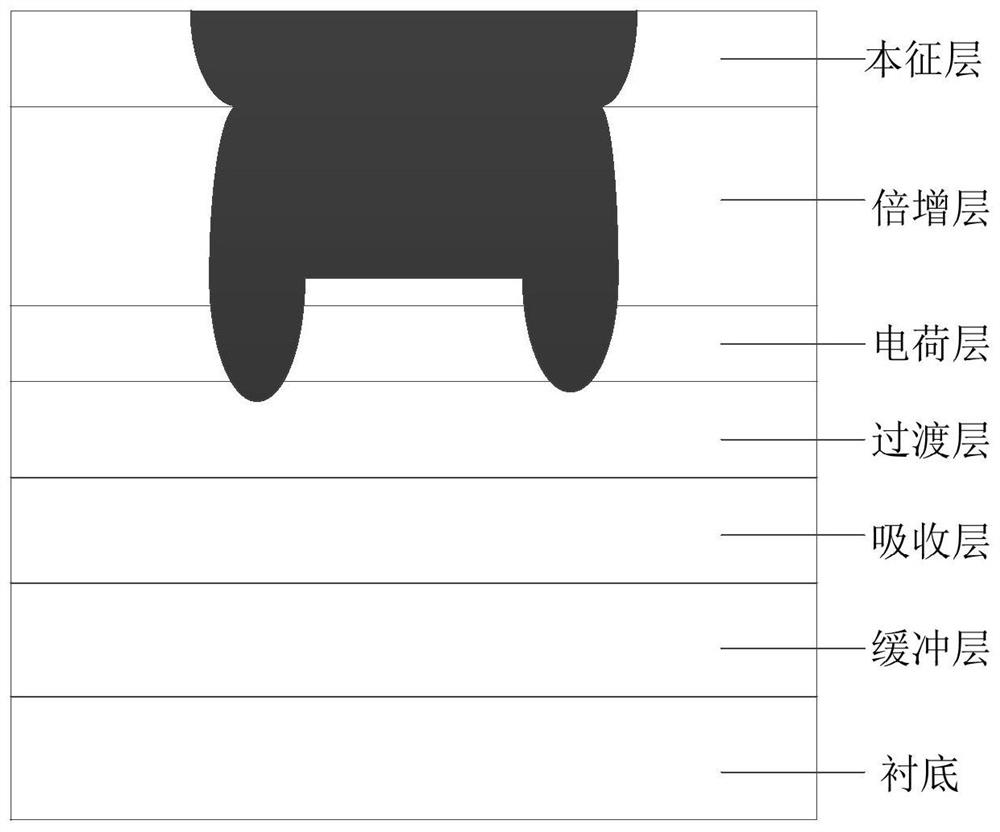

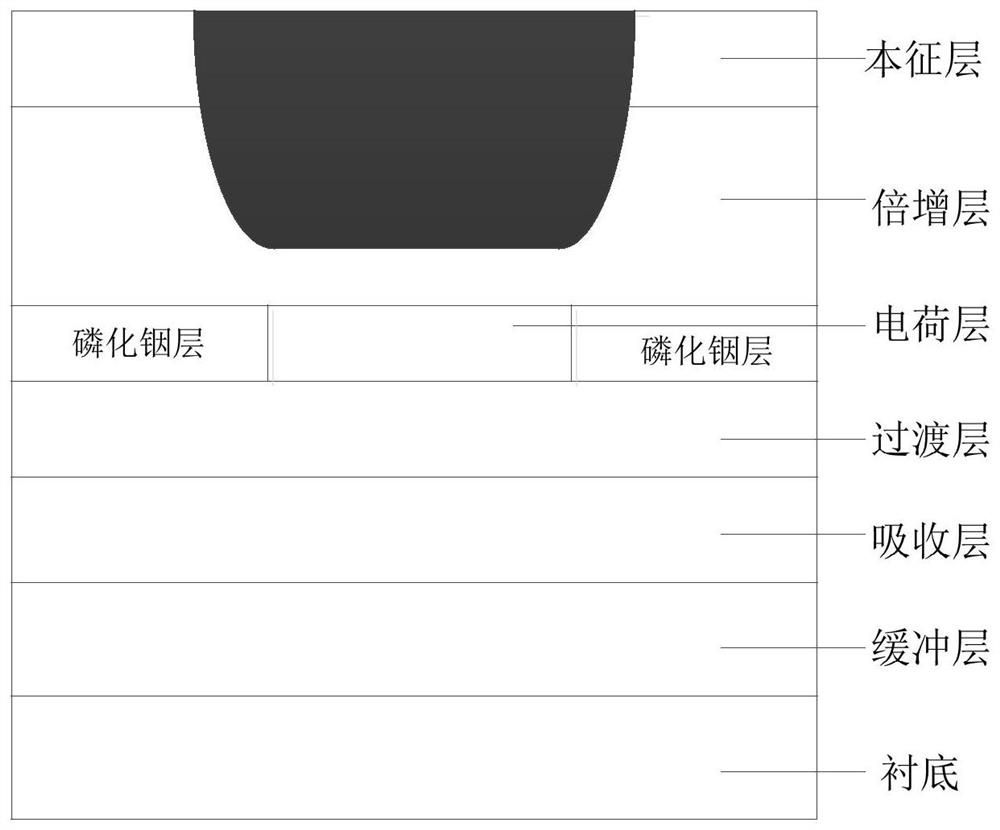

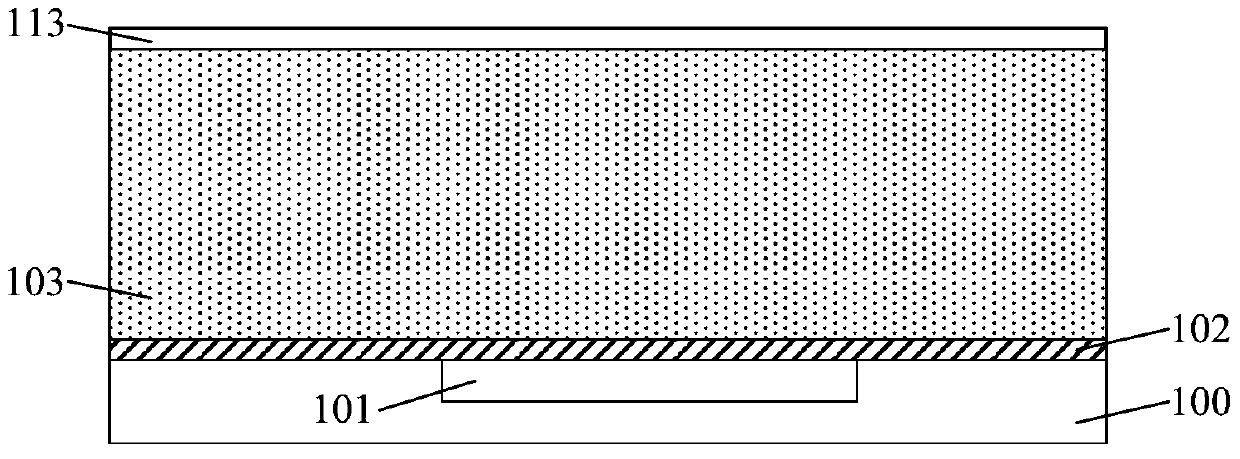

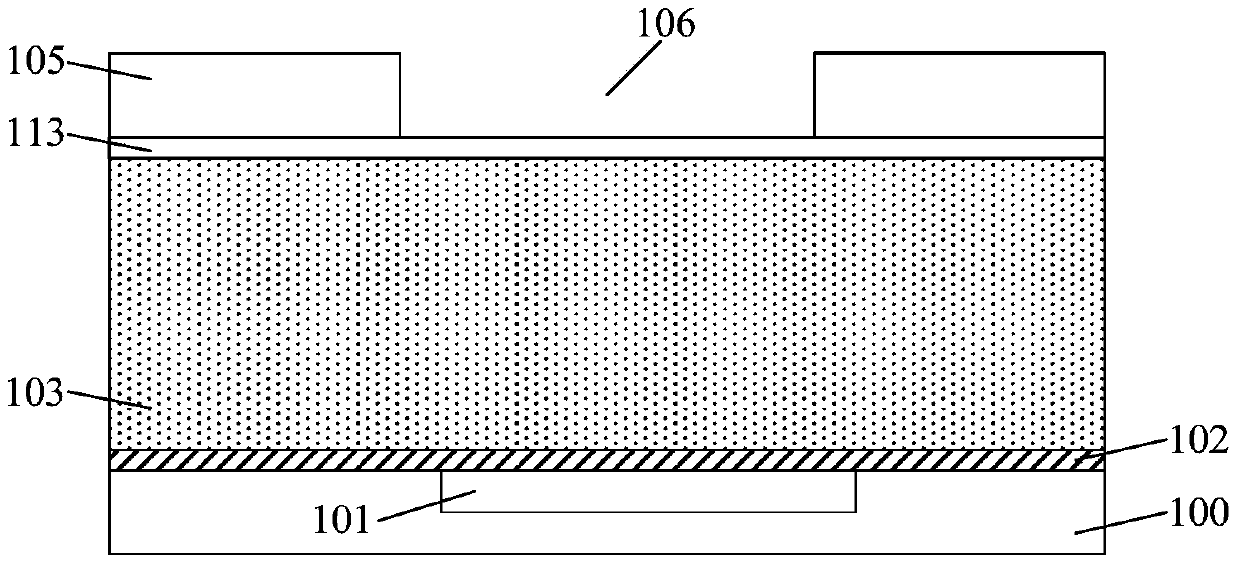

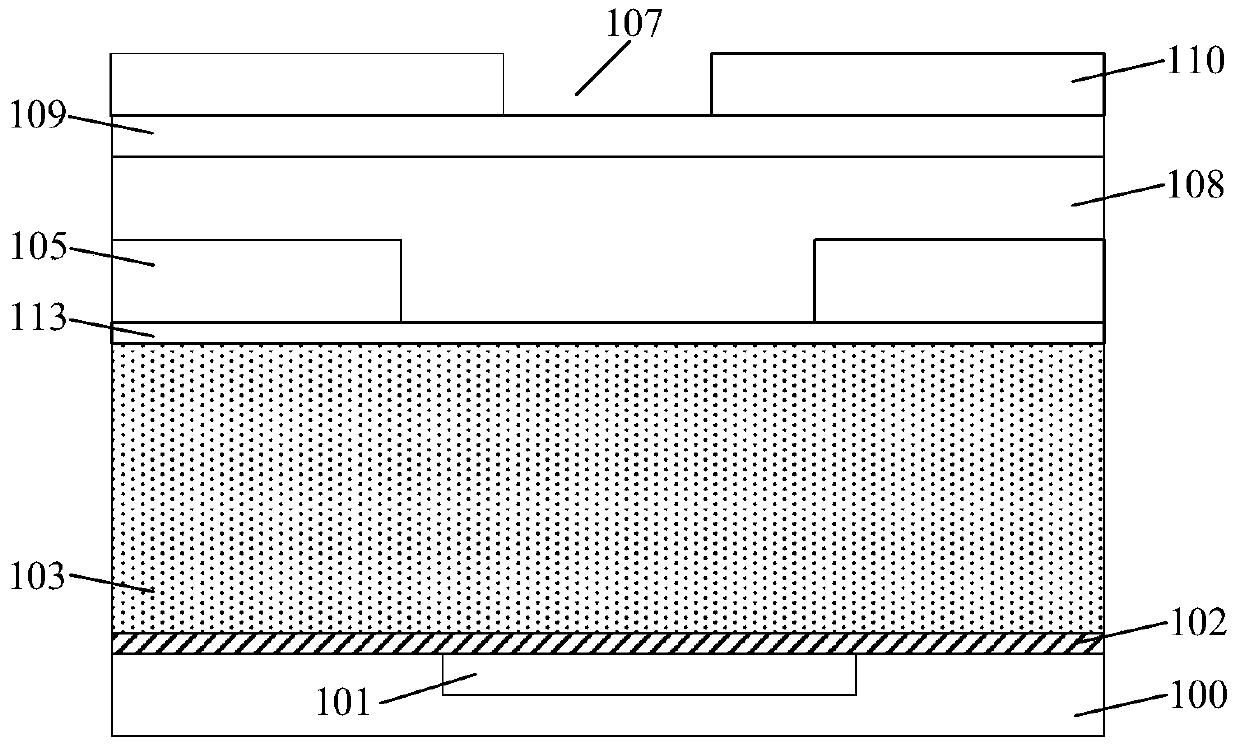

Single-photon detector, manufacturing method thereof and single-photon detector array

ActiveCN113921646AReduce complexitySuppress breakdownFinal product manufactureSolid-state devicesPhysicsOhmic contact

The invention provides a single-photon detector and a manufacturing method thereof, and a single-photon detector array. The method comprises the steps of sequentially growing a plurality of epitaxial layers on one side of a provided substrate, and enabling the epitaxial layers to comprise a buffer layer, an absorption layer, a transition layer, a charge layer, a multiplication layer, an inversion layer, a migration layer, a window layer, and an ohmic contact layer, and forming an arc-shaped diffusion region in the ohmic contact layer and the window layer through a diffusion process, etching the edge of a part of the epitaxial layer on the substrate to form a mesa structure, forming an optical window on the back surface of the substrate, forming a P-type electrode on the ohmic contact layer, and forming an N-type electrode on the back surface of the substrate. According to the scheme, the edge electric field of the diffusion area can be effectively reduced only through one-time diffusion treatment and combination of the inversion layer, then the edge breakdown problem is effectively restrained, and compared with an existing mode needing secondary diffusion treatment or secondary growth, the complexity of the manufacturing process is effectively reduced.

Owner:XIAMEN SANAN INTEGRATED CIRCUIT

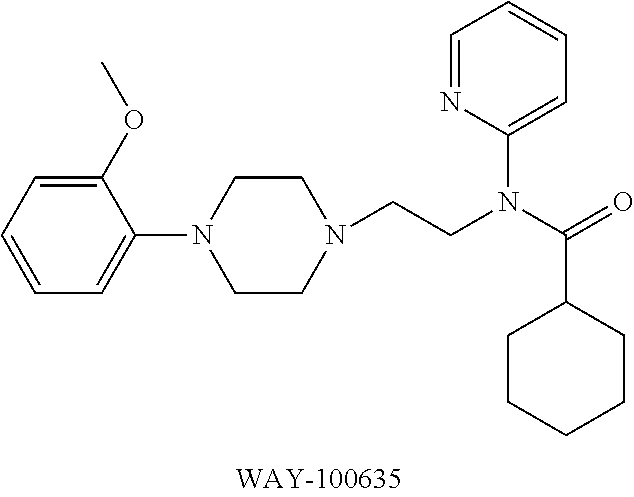

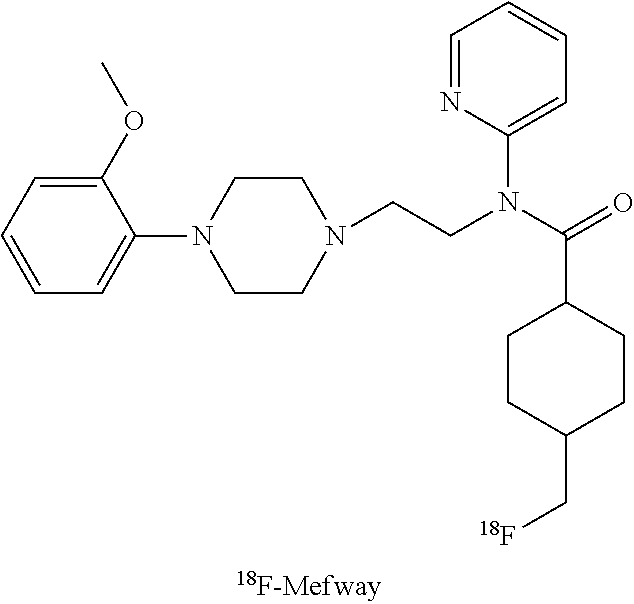

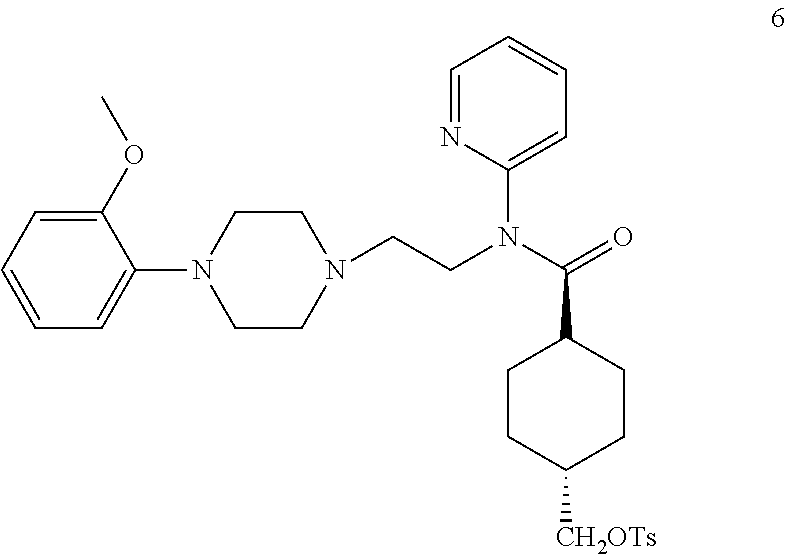

Efficient synthetic method of 18f-mefway precursor

The present invention relates a novel method for preparing an 18F-mefway precursor. The present invention provides an efficient synthetic method of an 18F-mefway precursor, which comprises an improved the acid chloride coupling reaction and proper reduction condition to suppress breakdown of amide bond and can obtain the precursor in high yield.

Owner:IND ACADEMIC COOP FOUNDATION YONSEI UNIV

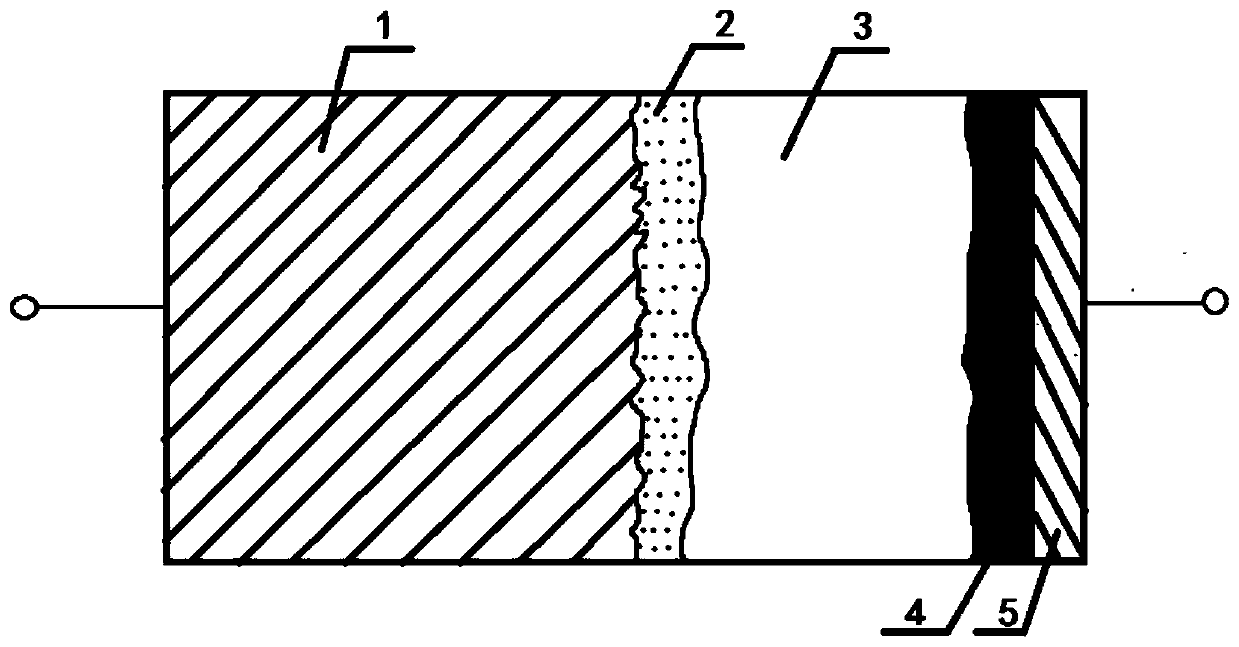

Junction barrier Schottky diode with gradient depth P type region and preparation method thereof

PendingCN112531007ASuppress breakdownImprove performanceSemiconductor/solid-state device manufacturingDiodeElectrical field strengthOhmic contact

The invention relates to a junction barrier Schottky diode with a gradient depth P type region and a preparation method thereof. The junction barrier Schottky diode comprises: a substrate; a negativeelectrode, which is manufactured on the back surface of the substrate; an n+ type gallium nitride layer, which epitaxially grows on the front surface of the substrate; an n type gallium nitride layer,which epitaxially grows on the n+ type gallium nitride layer, wherein an annular high-resistance region is arranged on the periphery of the n type gallium nitride layer, a plurality of grooves with gradient depths are etched in the n type gallium nitride layer, and p type gallium nitride grows in each groove; and a positive electrode, which is manufactured on the surfaces of the n type gallium nitride layer, the p type gallium nitride layer and the annular high-resistance region. The P type region with the gradient depth can adjust the electric field distribution of the high-electric-field-intensity region of the device; meanwhile, good ohmic contact and better PN junctions can be formed through the double-layer epitaxial gallium nitride structure, and the performance of the device is effectively improved; and in addition, the high-resistance region can effectively restrain breakdown of the device located on the edge of the electrode under high voltage, and the breakdown performance of the device is enhanced.

Owner:CHANGCHUN INST OF OPTICS FINE MECHANICS & PHYSICS CHINESE ACAD OF SCI

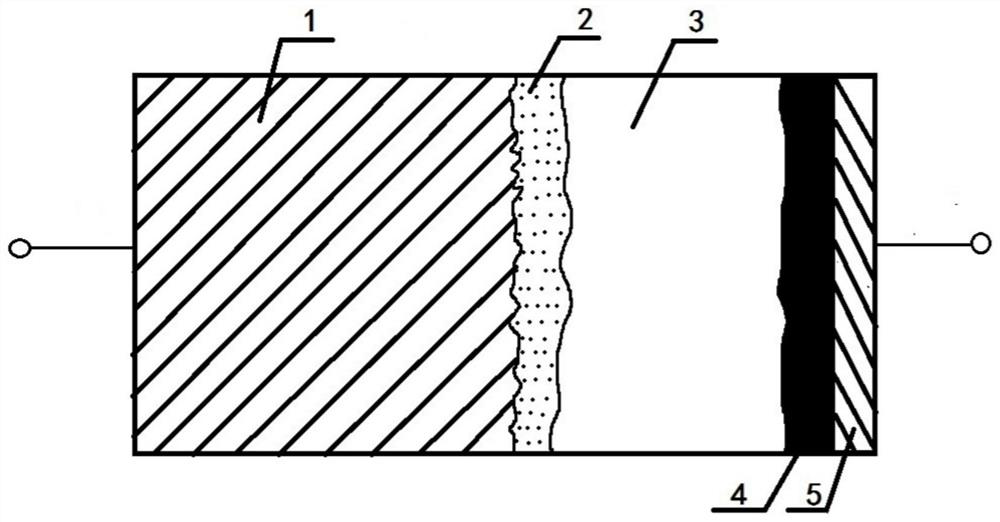

All-solid aluminum electrolytic capacitor and preparation method thereof

ActiveCN109887749AIncrease the flash voltageImprove stabilityCapacitor detailsComposite filmElectrolysis

The invention relates to an all-solid aluminum electrolytic capacitor and a preparation method thereof. The aluminum electrolytic capacitor replaces the electrolytic paper in the traditional capacitorwith a solid nano-composite film containing anode aluminum foil repair ions, and replaces the traditional anode aluminum foil with an anode aluminum foil with a silane oxygen group coupling surface.The preparation route includes the steps of preparing nano-composite film by in-situ polymerization, introducing anode foil repair ions, performing silane oxygen group coupling on the surface of the anode aluminum foil, and assembling an all-solid aluminum electrolytic capacitor with a graphite layer and conductive silver slurry. Compared with the prior art, the all-solid aluminum electrolytic capacitor provided by the invention solves the problems of large leakage current, liquid leakage, poor temperature characteristics and short service life at extreme temperatures of the aluminum electrolytic capacitor prepared by the traditional liquid organic electrolyte. At the same time, the problems of low flashover voltage and poor withstand voltage of the newly developed solid state aluminum electrolytic capacitor in recent years are solved, and the overall comprehensive performance of the aluminum electrolytic capacitor is greatly improved.

Owner:NANTONG RUITAI ELECTRONICS +1

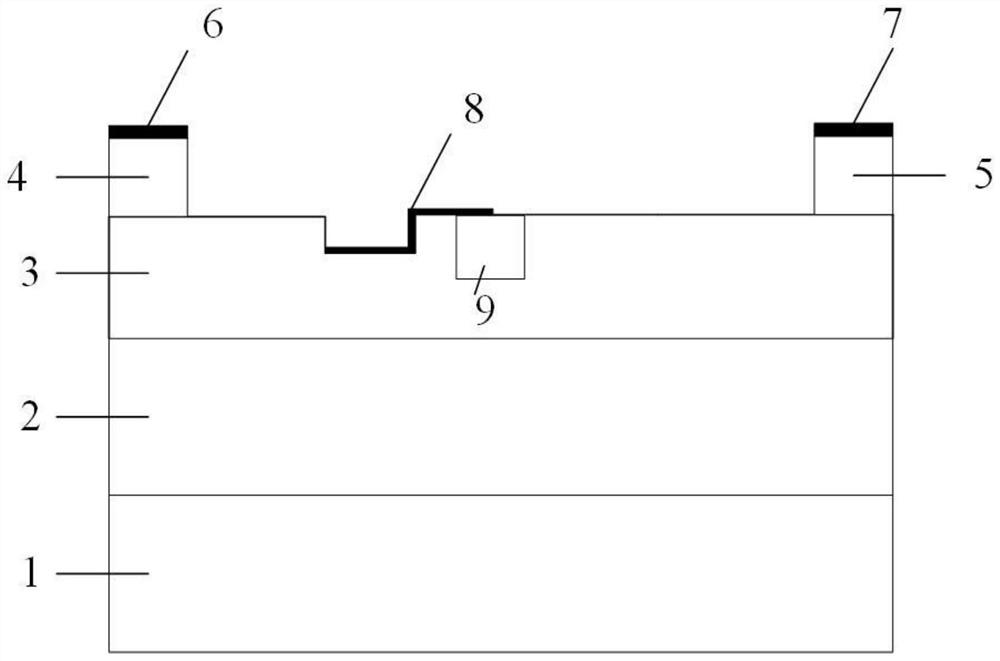

Semiconductor device

InactiveUS20100224933A1Suppress impact ionizationHigh withstand voltageSemiconductor/solid-state device detailsSolid-state devicesElectric fieldN channel

Provided is a semiconductor device including an N-channel high-voltage MOS transistor, in which wiring metal connected to a drain region is laid above a boundary portion between an oxide film formed by LOCOS process or the like on a low impurity concentration region and a high impurity concentration region forming the drain region, to thereby alleviate an electric field concentration at the boundary portion which is a contact portion between the low impurity concentration region and the high impurity concentration region by an electric field generated from the wiring metal toward a semiconductor substrate.

Owner:SEIKO INSTR INC

CMOS SPAD photoelectric device with deep N well in reverse doping distribution

InactiveCN113659030AImprove detection efficiencyReduce utilizationSemiconductor devicesCMOSQuantum efficiency

The invention relates to a CMOS SPAD photoelectric device with a deep N well in reverse doping distribution. The CMOS SPAD photoelectric device comprises a P substrate, the deep N well, a central N well and a P + layer are arranged on the P substrate, N wells are arranged at the two sides of the deep N well, the deep N well is of a reverse doping distribution structure, namely, the concentration of the deep N well close to the surface of the device is low, and the concentration of the deep N well is higher with the longitudinal depth away from the surface of the device is increased, transverse diffusion exists between the N wells at the two sides in the deep N well and the central N well, an n-virtual protection ring is formed at the edge of the PN junction, when incident photons are emitted into the device and are mainly absorbed by the deep N well, most photons can be utilized by the P + layer / central N well junction to form photon-generated carriers, and only a small number of photons penetrate through the deep N well to form a photon-generated carrier on the P substrate. The photon detection efficiency of the device is improved mainly from two aspects of increasing the thickness of the absorption region of the device and optimizing the quantum efficiency of the device.

Owner:重庆亚川电器有限公司

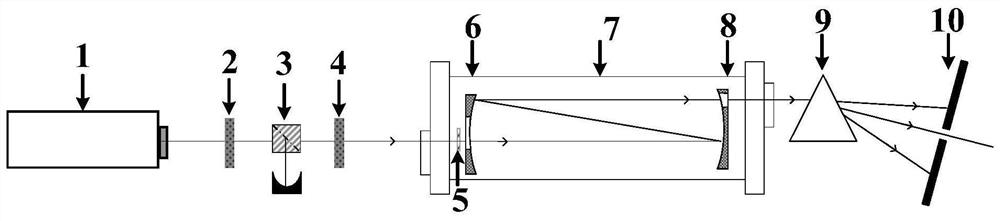

Discrete mirror multi-pass pool gas stimulated Raman scattering device

PendingCN114552351AOptical path number increasedEasy to adjustLaser using scattering effectsPhysicsErbium lasers

The invention provides a discrete mirror multi-pass pool gas stimulated Raman scattering device. The discrete mirror multi-pass pool gas stimulated Raman scattering device comprises a pump laser, and a lambda / 2 piece, a polarization splitting prism, a lambda / 4 piece, a Raman pool, a splitting prism and a separation baffle which are sequentially arranged along the laser output direction of the pump laser, a focusing lens and a laser reflector group are sequentially arranged in the Raman cell along the laser incident direction, the focusing lens converges incident laser to the central position of the Raman cell, and the laser reflector group is configured to be capable of adjusting the reflection times of the laser in the Raman cell; and the Raman cell is filled with Raman active gas. According to the invention, a multi-pass pool structure is designed, the design is simple, the debugging is convenient, the conversion rate of Raman light in gas is effectively improved, and the device can be widely applied to the field of laser frequency conversion.

Owner:DALIAN INST OF CHEM PHYSICS CHINESE ACAD OF SCI

4h-sic metal-semiconductor field-effect transistor with lightly doped gate edge and drain side parts

ActiveCN109524474BAlleviate the effect of electric field concentrationImprove stabilityTransistorField effectSemiconductor

The invention discloses a 4H-SiC metal-semiconductor field effect transistor with light doping on the drain side of the gate edge, including a 4H-SiC semi-insulating substrate, a P-type buffer layer, an N-type channel layer, and an N-type channel from bottom to top. Both sides of the upper surface of the channel layer are provided with a source cap layer and a drain cap layer, the upper surface of the source cap layer is provided with a source electrode, the upper surface of the drain cap layer is provided with a drain electrode, and the bottom of the N-type channel layer is close to the source One side of the pole cap layer is provided with a gate electrode, and a lightly doped region is formed at the bottom of the N-type channel layer under the gate of a part of the gate electrode and between part of the gate and drain. The vertical line is the axis of symmetry and the structure is axisymmetric. The invention can alleviate the electric field concentration effect on the drain side of the gate edge to optimize the electric field and current on the drain side of the gate edge, thereby suppressing breakdown; it can alleviate the hot electron charging effect, so as to reduce the generation of interface states and suppress the decline of device performance, thereby Improve device life.

Owner:XIDIAN UNIV

Formation method of semiconductor structure

ActiveCN106206408BImprove breakdown voltageImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor structurePhysical chemistry

Disclosed is a formation method for a semiconductor structure. The formation method comprises the steps of providing a substrate and a dielectric layer which is positioned on the surface of the substrate, wherein a bottom layer metal layer is formed in the substrate; etching the dielectric layer to form an opening which runs through the dielectric layer, wherein the surface of the bottom layer metal layer is exposed out of the bottom of the opening; performing etching post-processing on the opening by adopting an H<2>-containing gas; forming a silicon layer on the surface of the side wall of the opening after the etching post-processing is carried out; after the silicon layer is formed, performing wet cleaning processing on the opening; and forming a conductive layer, wherein the opening is filled with the conductive layer. By adoption of the formation method, when the impurities in the opening are removed, corrosion to the dielectric layer on the side wall of the opening is avoided in the process of the wet cleaning processing, so that the breakdown voltage is increased; the time dependent dielectric breakdown problem is restrained; and the reliability and the electrical performance of the semiconductor structure are improved.

Owner:SEMICON MFG SOUTH CHINA CORP +1

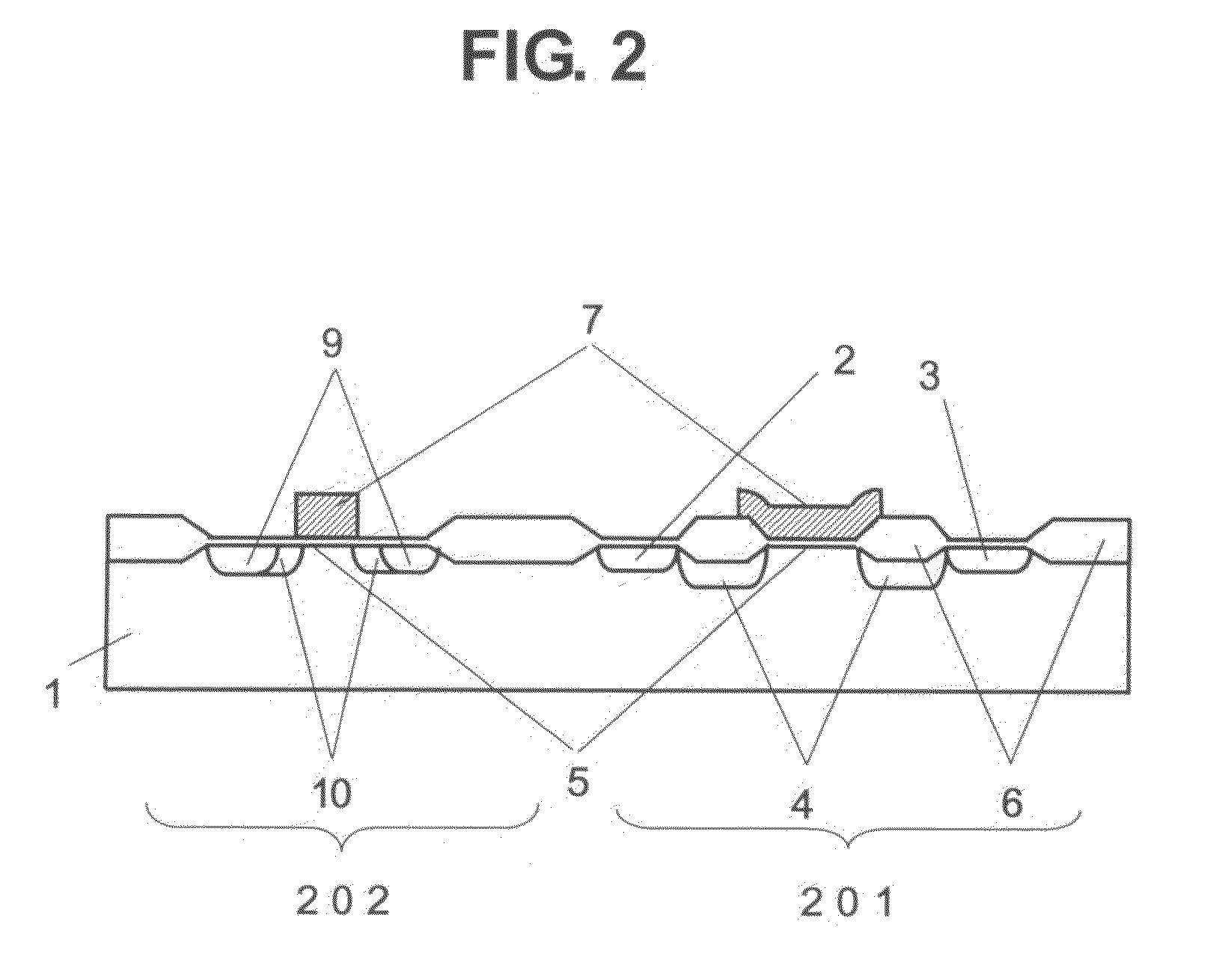

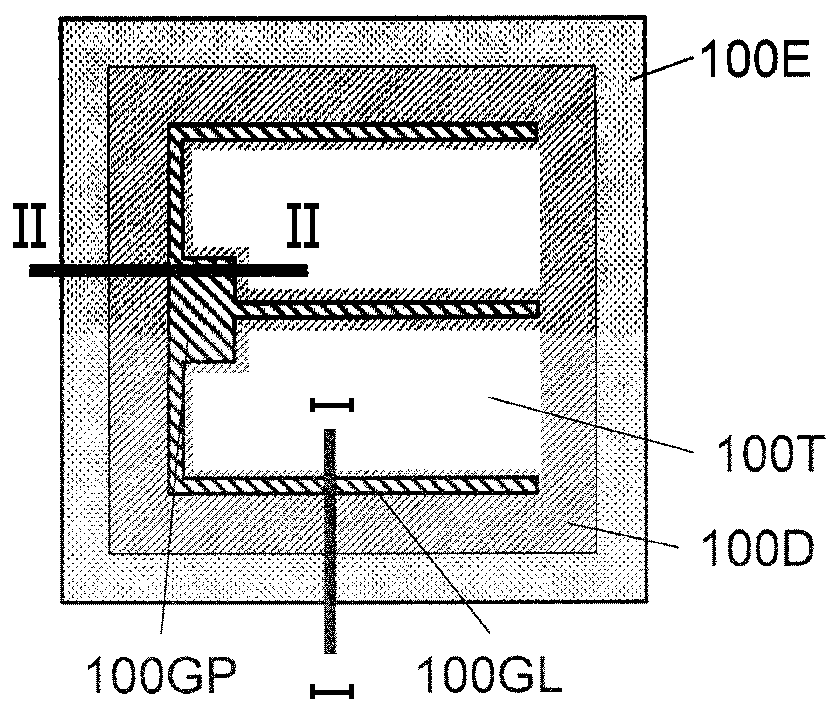

Semiconductor device

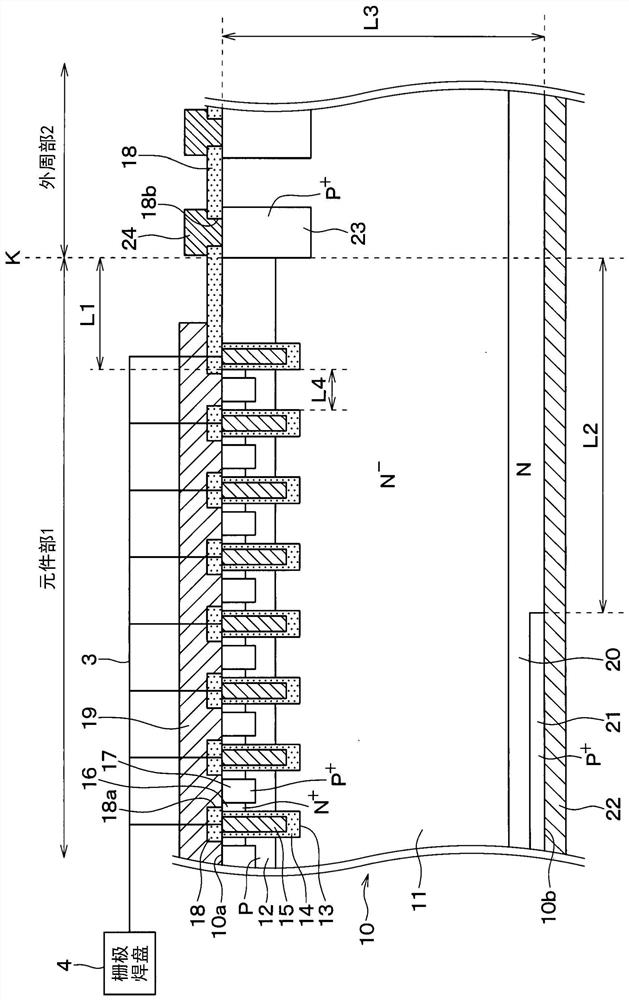

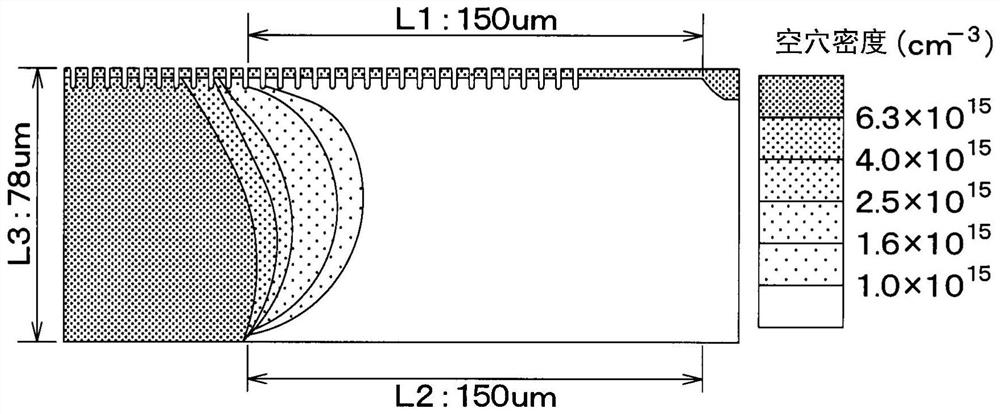

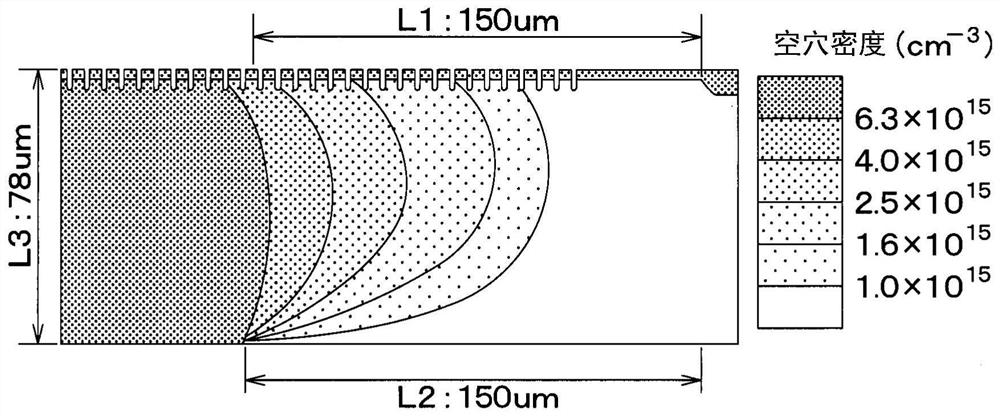

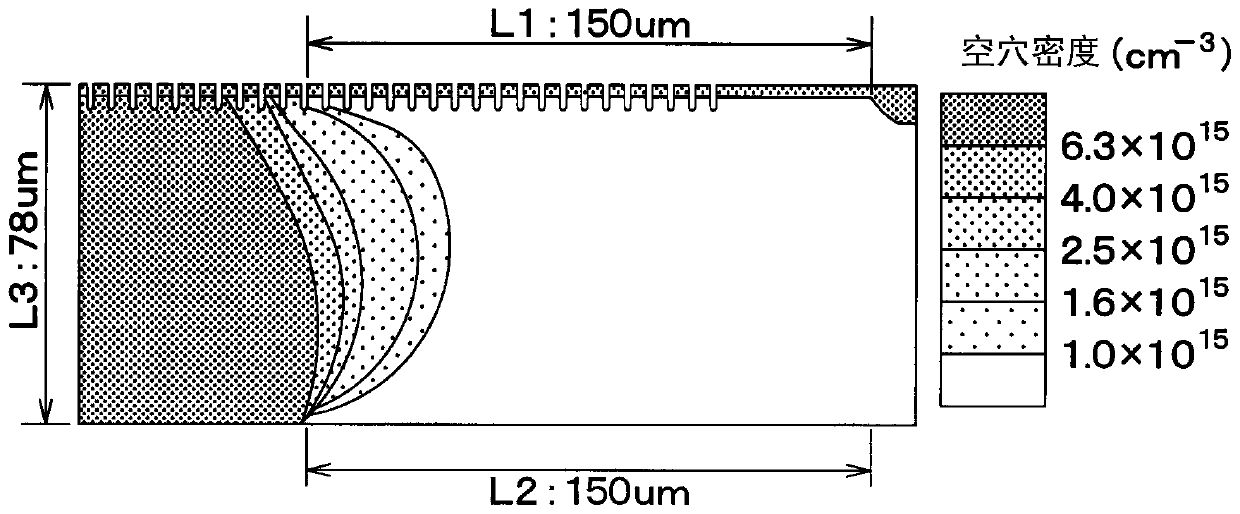

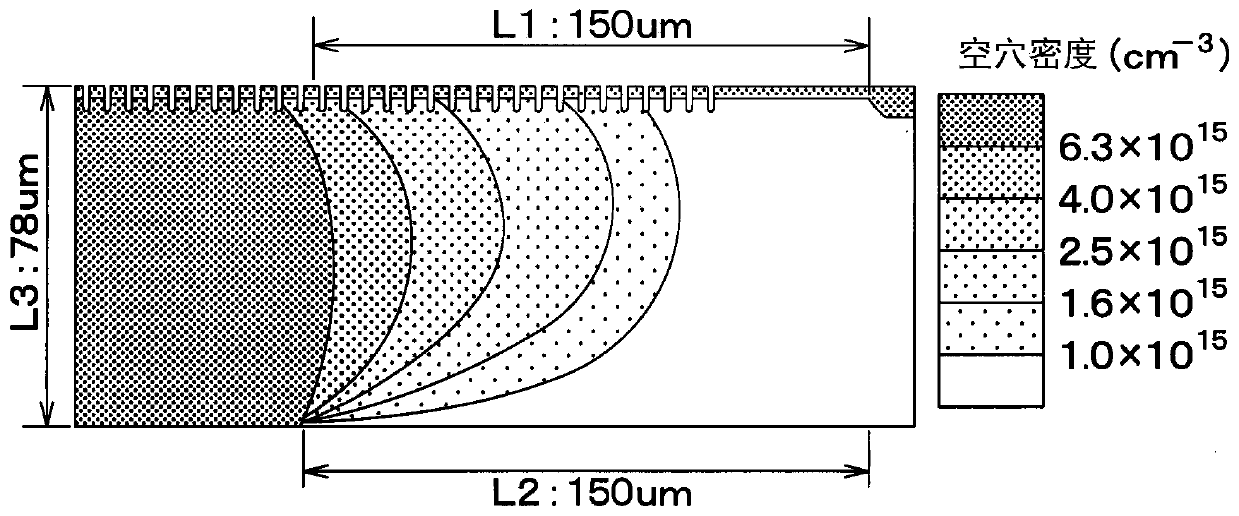

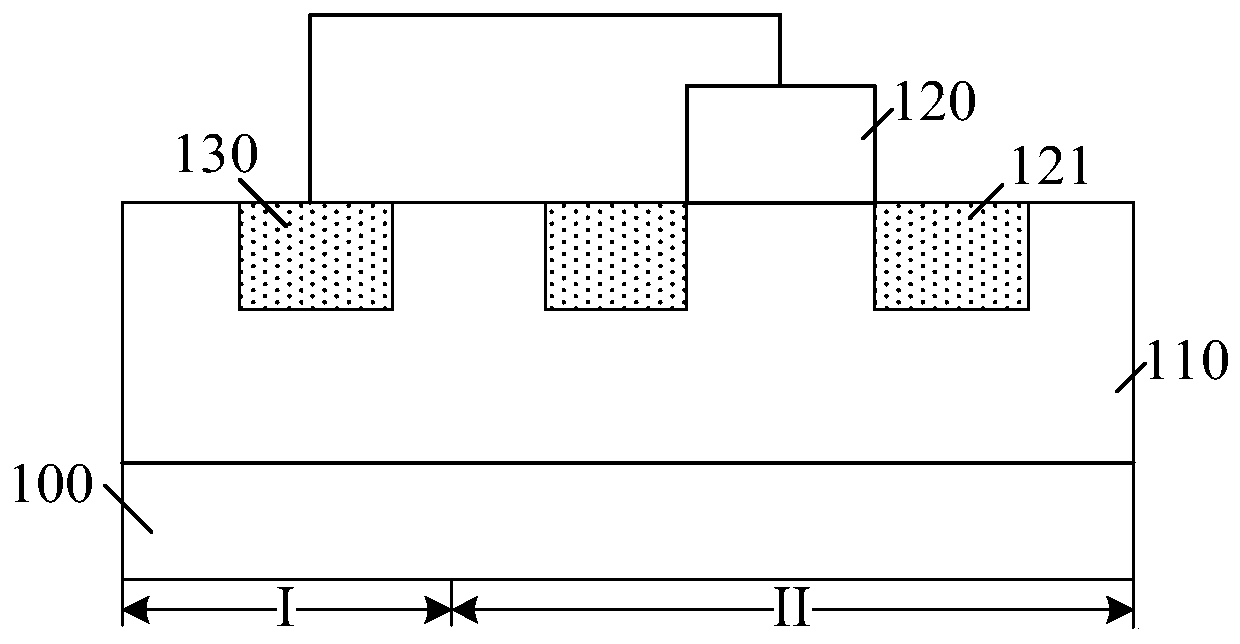

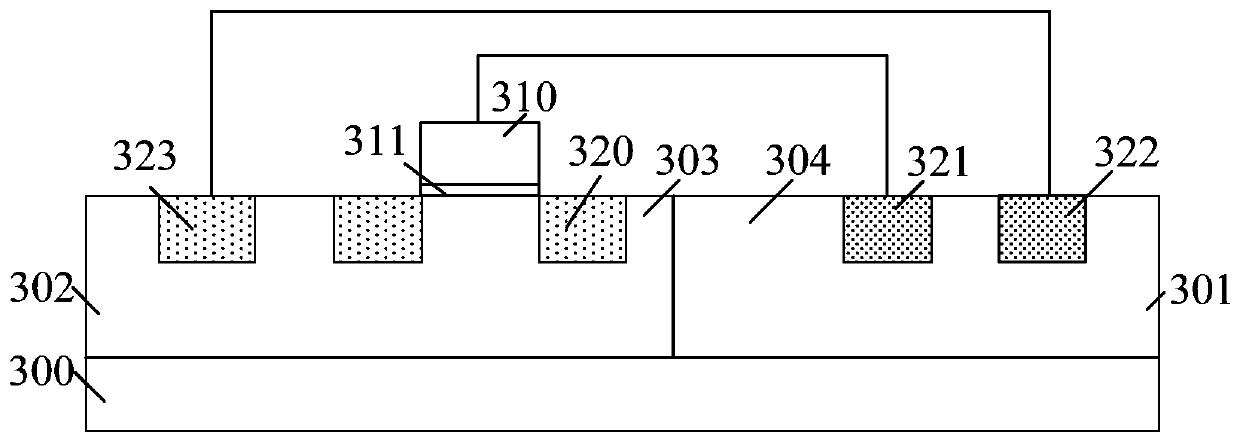

ActiveCN110249431BAvoid damageSuppress breakdownTransistorSolid-state devicesDevice materialCharge-carrier density

Owner:DENSO CORP

Arc-extinguishing device of control and protection switch

Owner:RADIN ELECTRIC TECH

Silicon carbide semiconductor device

ActiveCN106463541BRaise the potentialSuppress breakdownSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductorTransistor

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

A kind of all-solid aluminum electrolytic capacitor and its preparation method

ActiveCN109887749BIncrease the flash voltageImprove stabilityCapacitor detailsElectrolytic agentSilver paste

The invention relates to an all-solid aluminum electrolytic capacitor and a preparation method thereof. In the aluminum electrolytic capacitor, the electrolytic paper in a traditional capacitor is replaced by a solid nanocomposite film containing anode aluminum foil repair ions, and the anode aluminum foil with siloxy-coupling on the surface is used instead. Traditional anodized aluminum foil. Its preparation route includes preparing nanocomposite membranes by in-situ polymerization and introducing anode foil repair ions, performing siloxyl coupling on the surface of anode aluminum foils, and then combining graphite layers and conductive silver pastes to assemble into all-solid aluminum electrolytic capacitors. Compared with the prior art, the all-solid aluminum electrolytic capacitor provided by the present invention solves the problems of large leakage current, liquid leakage, poor temperature characteristics and short service life under extreme temperatures of the traditional aluminum electrolytic capacitor prepared with liquid organic electrolyte, and at the same time It also solves the problems of low flashover voltage and poor voltage resistance of solid aluminum electrolytic capacitors newly developed in recent years, and greatly improves the overall comprehensive performance of aluminum electrolytic capacitors.

Owner:NANTONG RUITAI ELECTRONICS +1

Semiconductor device

ActiveCN110249431AAvoid damageSuppress breakdownTransistorSolid-state devicesCharge-carrier densityDevice material

This semiconductor device has an element part (1) and an outer peripheral part (2) surrounding the element part (1), wherein a deep layer (23) is formed more deeply in the outer peripheral part (2) than in a base layer (12). When the position which, in the deep layers (23), is closest to the element part (1) is a boundary position (K), the distance between the boundary position (K) and the position which is closest to the outer peripheral part (2) in an emitter region (16) into which first carriers can be injected is a first distance (L1), and the distance between the boundary position (K) and the position of a stepped part in a surface direction of a semiconductor substrate (10) in a collector layer (21) is a second distance (L2), the first distance (L1) and the second distance (L2) are adjusted so that a carrier density at the outer peripheral part (2) is decreased on the basis of the withstand voltage of the outer peripheral part (2), the withstand voltage having been decreased by the deep layer (23).

Owner:DENSO CORP

Semiconductor structures and methods of forming them

ActiveCN109037195BReduce voltageSuppress breakdownTransistorSemiconductor/solid-state device detailsSemiconductor structureElectrical connection

The invention provides a semiconductor structure and a forming method thereof, wherein, the method comprises the following steps: a substrate; a first well region, a second well region, a third well region and a fourth well region located between the third well region and the first well region which are located in the substrate, the third well region and the second well region being the same in conductivity type of doped ions and the fourth well region and the third well region being opposite in conductivity type of doped ions; a device structure located on the third well region; a first dopedregion and a second doped region located in the first well region, the first doped region and the second doped region being separate, the conductivity type of the doped ions in the first doped regionand the second doped region being opposite to that of the first well region, the first doped region being electrically connected to the device structure; a third doped region located in the second well region, the third doped region being electrically connected to the second doped region. The first doped region, the first well region and the second doped region form a transistor, which can improve the performance of the semiconductor structure.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Graphene-assisted GaN rectifier and preparation method thereof

PendingCN109873031ASuppress breakdownImprove stabilitySemiconductor/solid-state device detailsSolid-state devicesHeterojunctionThermal breakdown

The invention discloses a graphene-assisted GaN rectifier and a preparation method thereof. The preparation method comprises the steps of transferring graphene on an epitaxial wafer for preparing a primary electrode; carrying out photoetching development on the epitaxial wafer subjected to graphene transfer; evaporating a metal layer on the epitaxial wafer subjected to photoetching development; removing glue on the epitaxial wafer subjected to metal layer evaporation; removing redundant graphene on the epitaxial wafer subjected to glue removal; partially evaporating Schottky metal at a Schottky electrode on the epitaxial wafer subjected to redundant graphene removal; depositing a patterned passivation layer on the epitaxial wafer subjected to Schottky metal evaporation; and depositing a top metal layer on the patterned passivation layer. The obtained graphene-assisted GaN rectifier can reduce the high-frequency working thermal breakdown frequency of a GaN rectifier and effectively enhance the electrode current expansion capability of the GaN rectifier; and a graphene introduction method can be widely applied to the preparation of various types of GaN rectifier structures or III nitride power devices taking AlGaN / GaN heterojunctions as structure foundations.

Owner:SOUTH CHINA UNIV OF TECH