3D-RESURF terminal structure of power semiconductor device and manufacturing method thereof

A technology of power semiconductors and terminal structures, applied in semiconductor devices, electrical components, circuits, etc., can solve problems such as low chip area efficiency, large space area, and cost reduction, and achieve improved chip area efficiency, electric field concentration relief, and reduced requirements. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

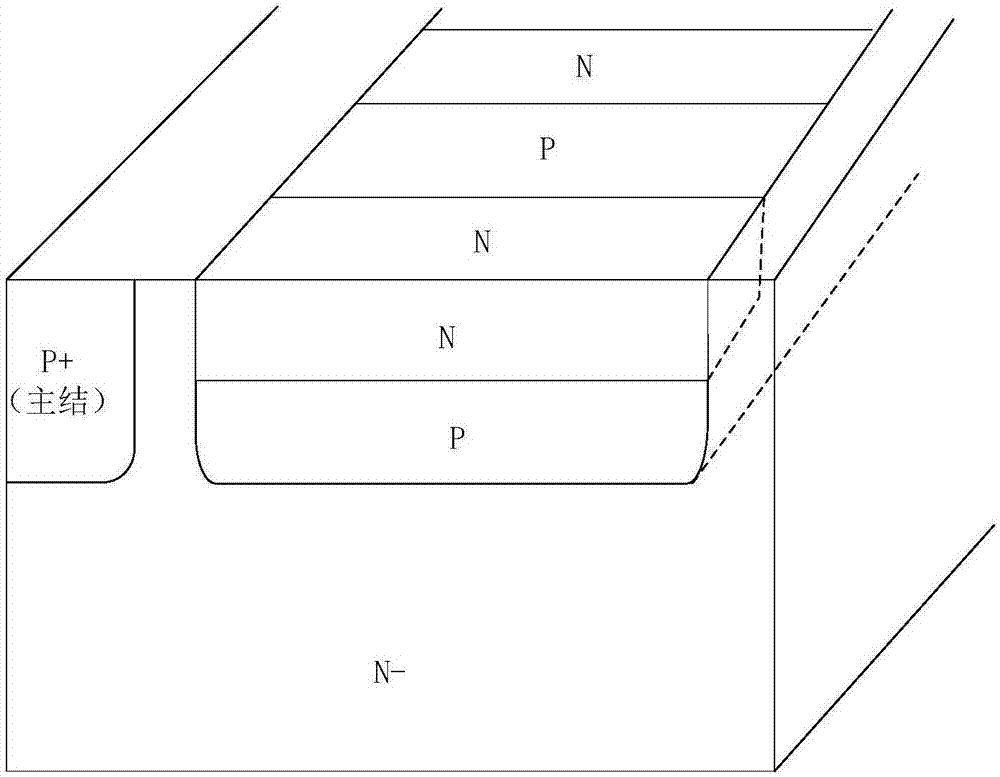

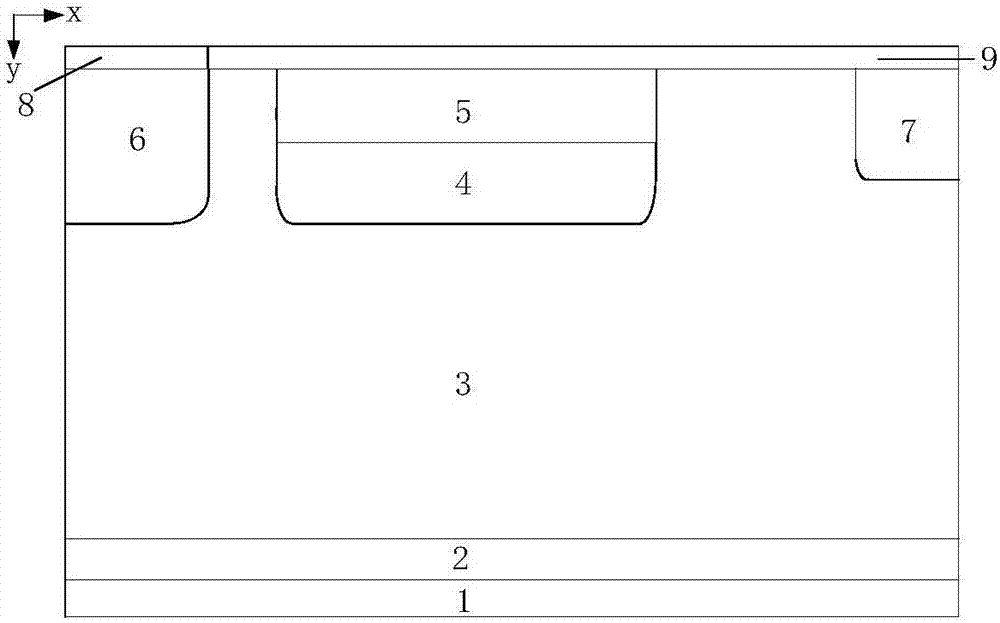

[0033] Such as figure 1 As shown, a 3D-RESURF terminal structure of a power semiconductor device includes a metalized cathode 1, a heavily doped semiconductor substrate of a first conductivity type above the metalized cathode 1, and a heavily doped first conductivity type from bottom to top. The first conductivity type lightly doped drift region 3 above the semiconductor substrate 2; the upper surface of the first conductivity type lightly doped drift region 3 is a field oxide layer 9; the interior of the first conductivity type lightly doped drift region 3 The upper left part is the second conductivity type semiconductor main junction 6; the upper surface of the second conductivity type semiconductor main junction 6 is connected to the metallization anode 8; the upper right part of the interior of the first conductivity type lightly doped drift region 3 is the first conductivity Type heavily doped stop ring 7; located between the second conductive type semiconductor main juncti...

Embodiment 2

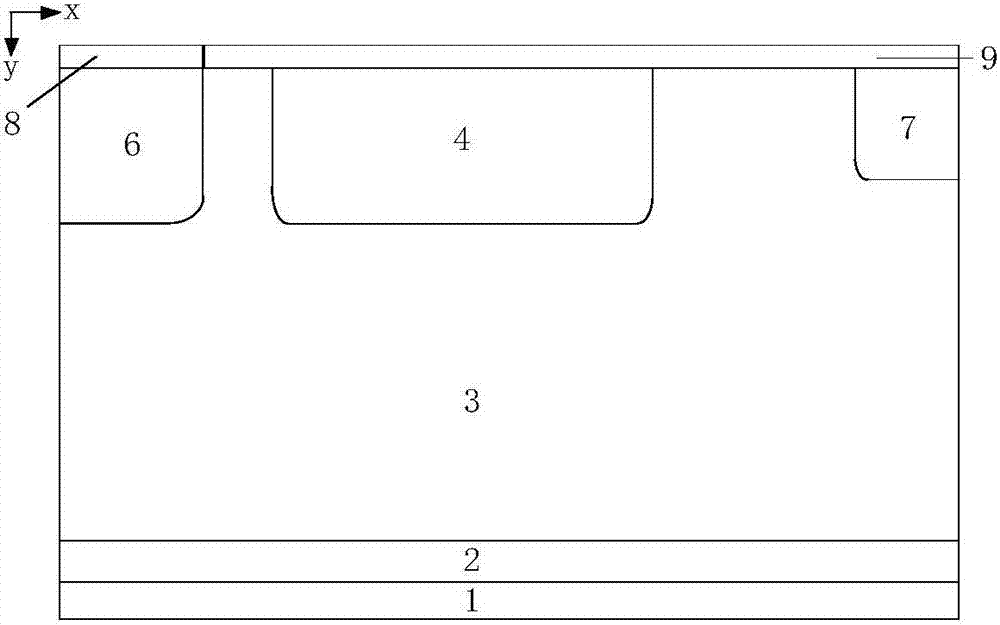

[0051] Such as Picture 12 As shown, this embodiment is basically the same as Embodiment 1, except that the first conductivity type semiconductor drift regions 5 are continuously arranged in the Z direction. When the first conductivity type semiconductor drift region 5 is continuous in the Z direction, the same photolithography is used when preparing the first conductivity type semiconductor drift region 5 and the second conductivity type semiconductor RESURF layer 4.

[0052] The semiconductor surface of this embodiment has no electric field component in the z direction, and its effect is slightly worse than that of Embodiment 1. However, this embodiment can be used when preparing the second conductivity type semiconductor RESURF region 4 and the first conductivity type semiconductor drift region 5 The same lithography plate, thereby reducing manufacturing costs. At the same time, this embodiment adopts the same preparation process as in embodiment 1. As the diffusion process is...

Embodiment 3

[0054] Such as Figure 13 As shown, this embodiment is basically the same as Embodiment 1, but the difference is that there are multiple first conductivity type semiconductor regions 5 above the second conductivity type semiconductor RESURF region 4, and the first conductivity type semiconductor drift region 5 is in the X direction and None are arranged continuously in the Z direction.

[0055] The structure proposed in this embodiment can better control the total amount of impurities, achieve charge balance, and completely deplete the surface; at the same time, the structure can change the surface to a certain extent by adjusting the distribution of the first conductivity type semiconductor region 5. The peak position of the electric field achieves higher withstand voltage.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More