Patents

Literature

58 results about "Edge cell" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

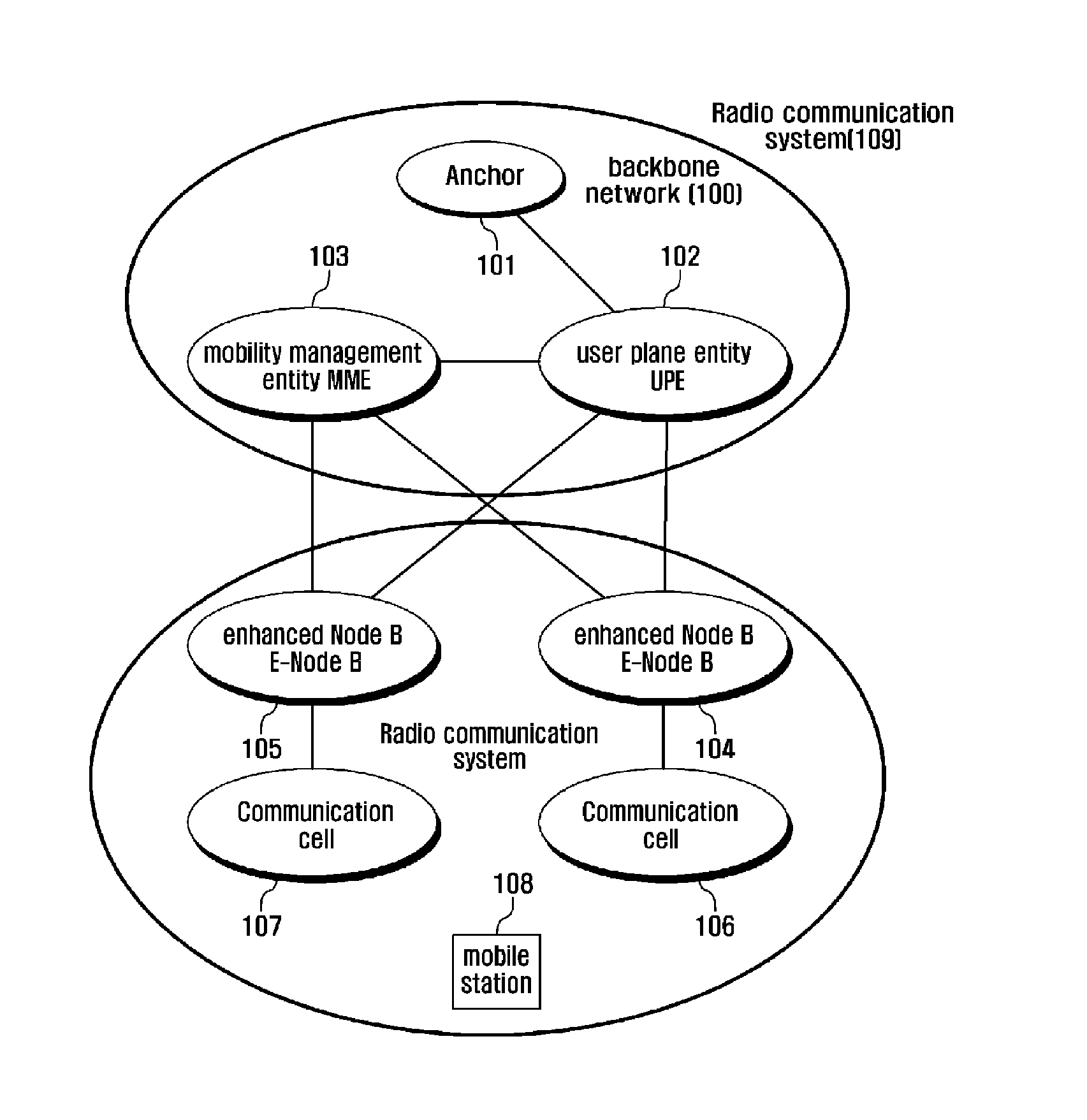

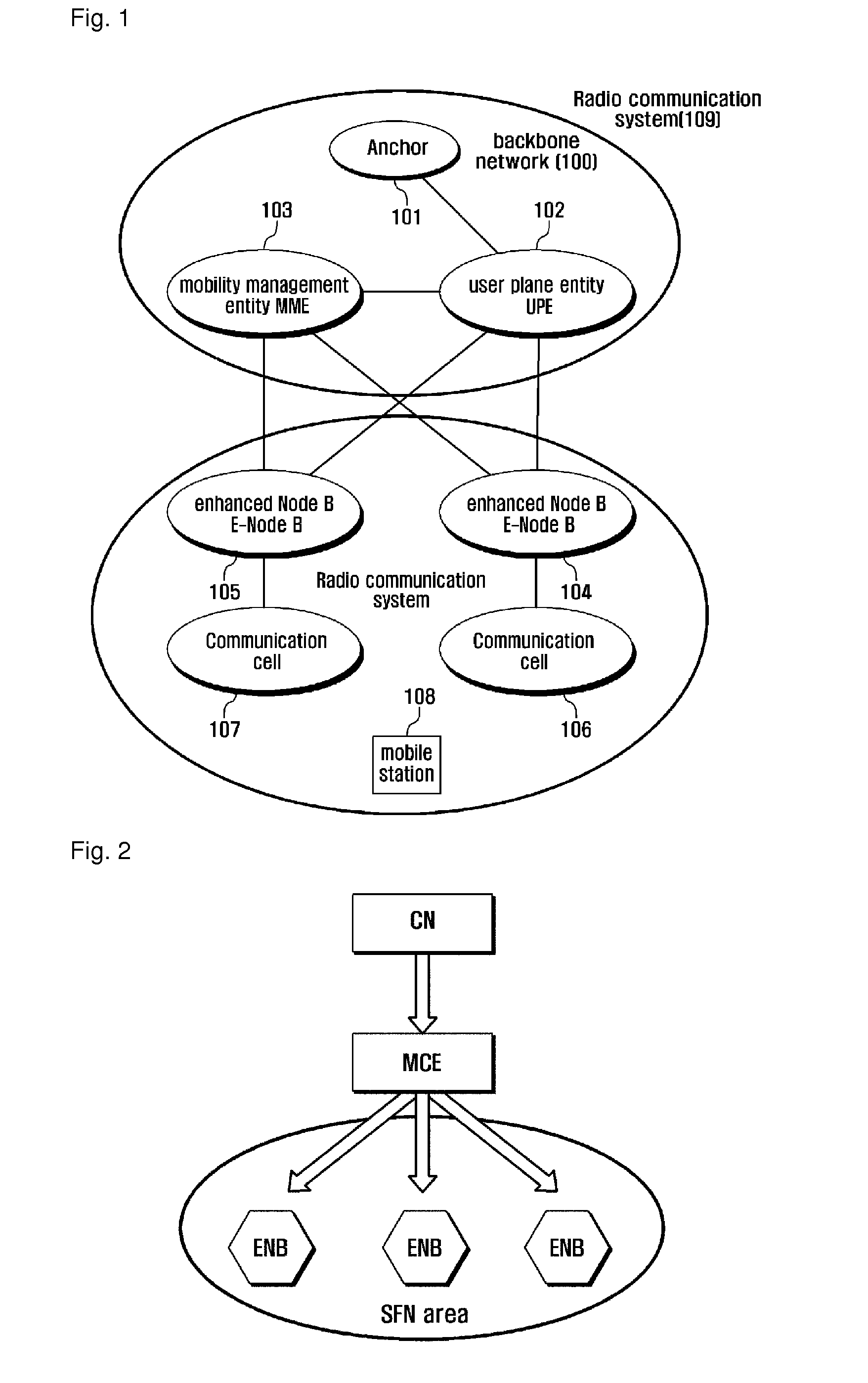

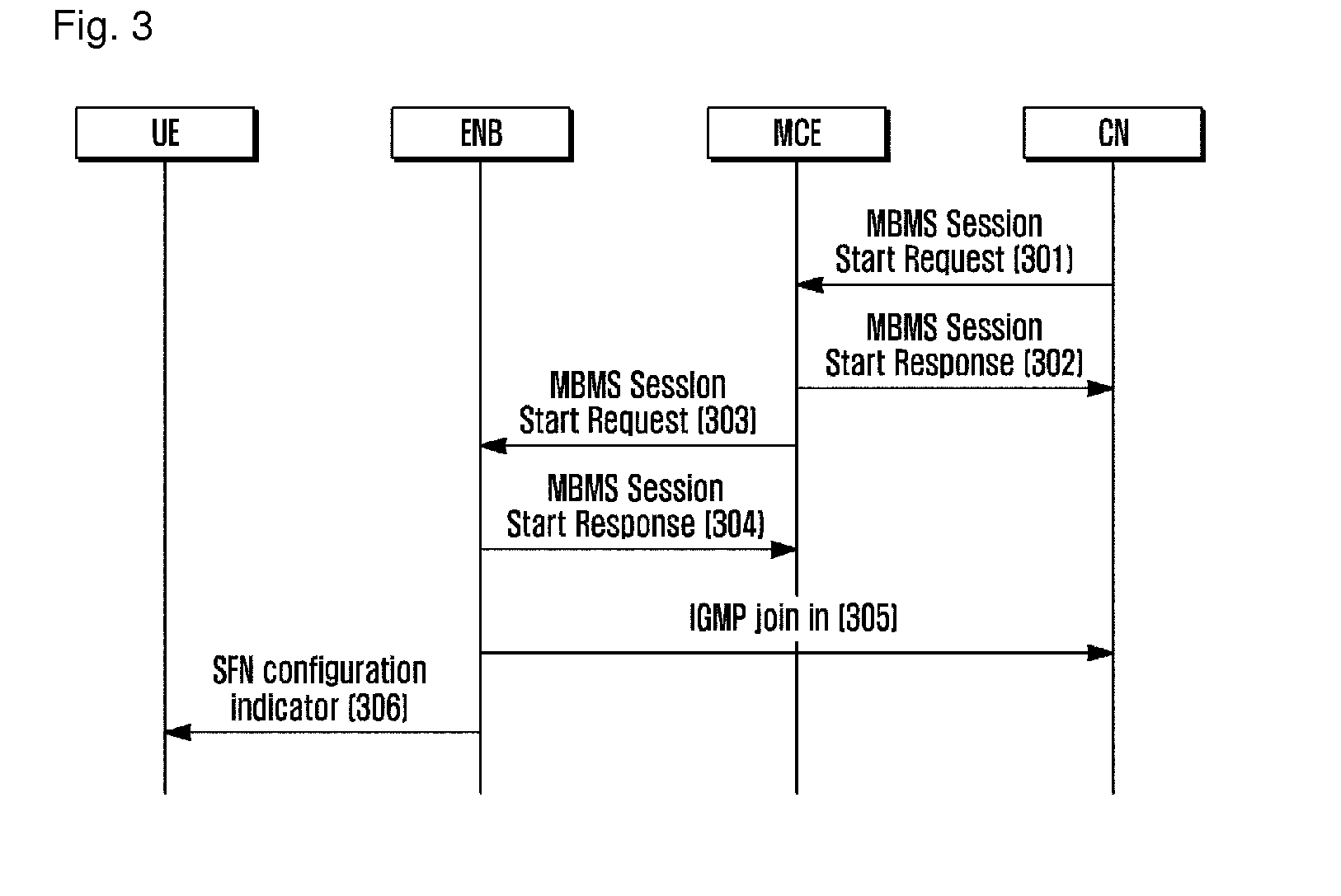

Method for supporting continuous reception of evolved broadcast and multicast service data

ActiveUS20100254352A1Reduce MBMS data lossReduce data lossConnection managementOrthogonal multiplexCurrent cellTransfer mode

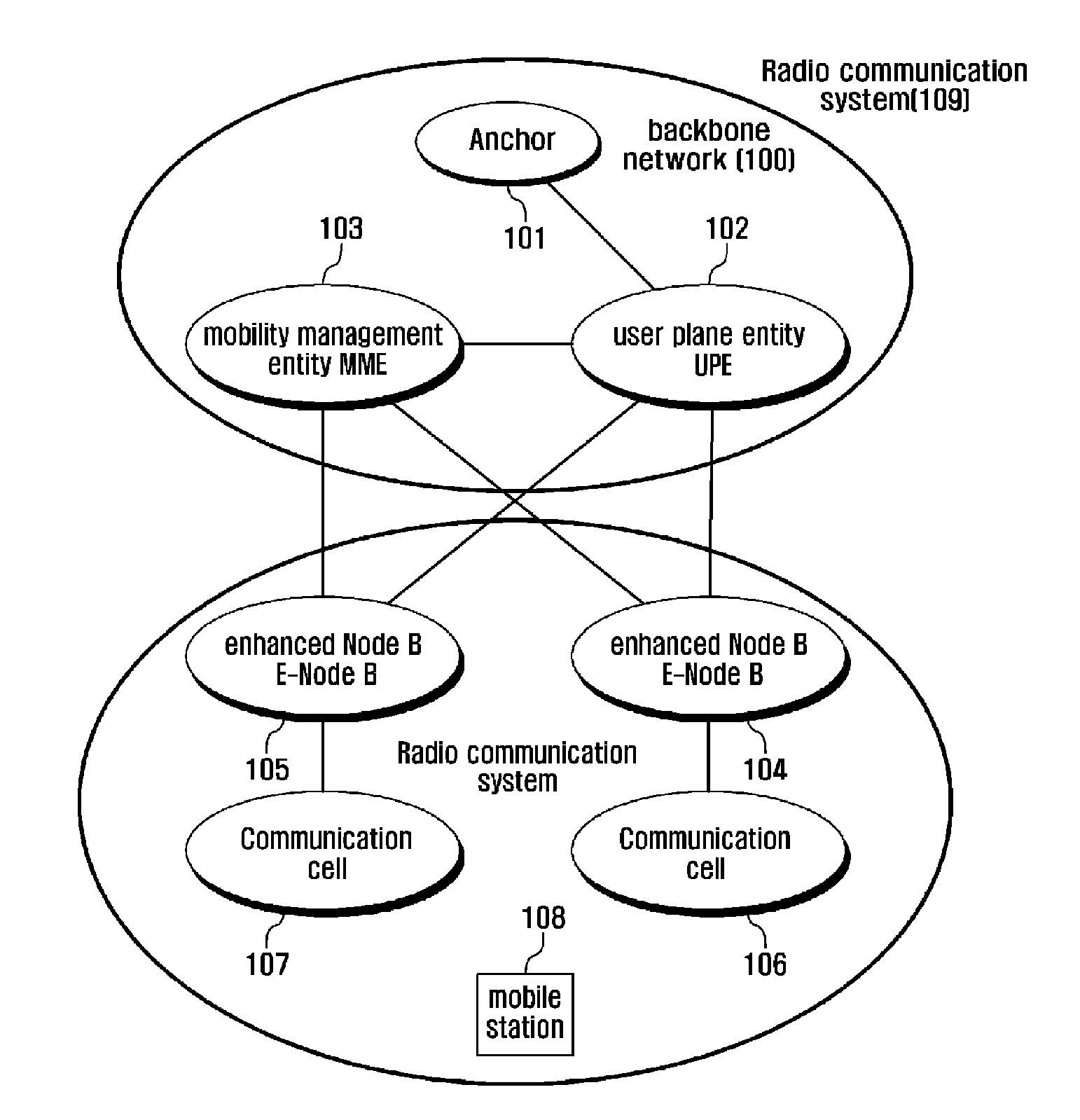

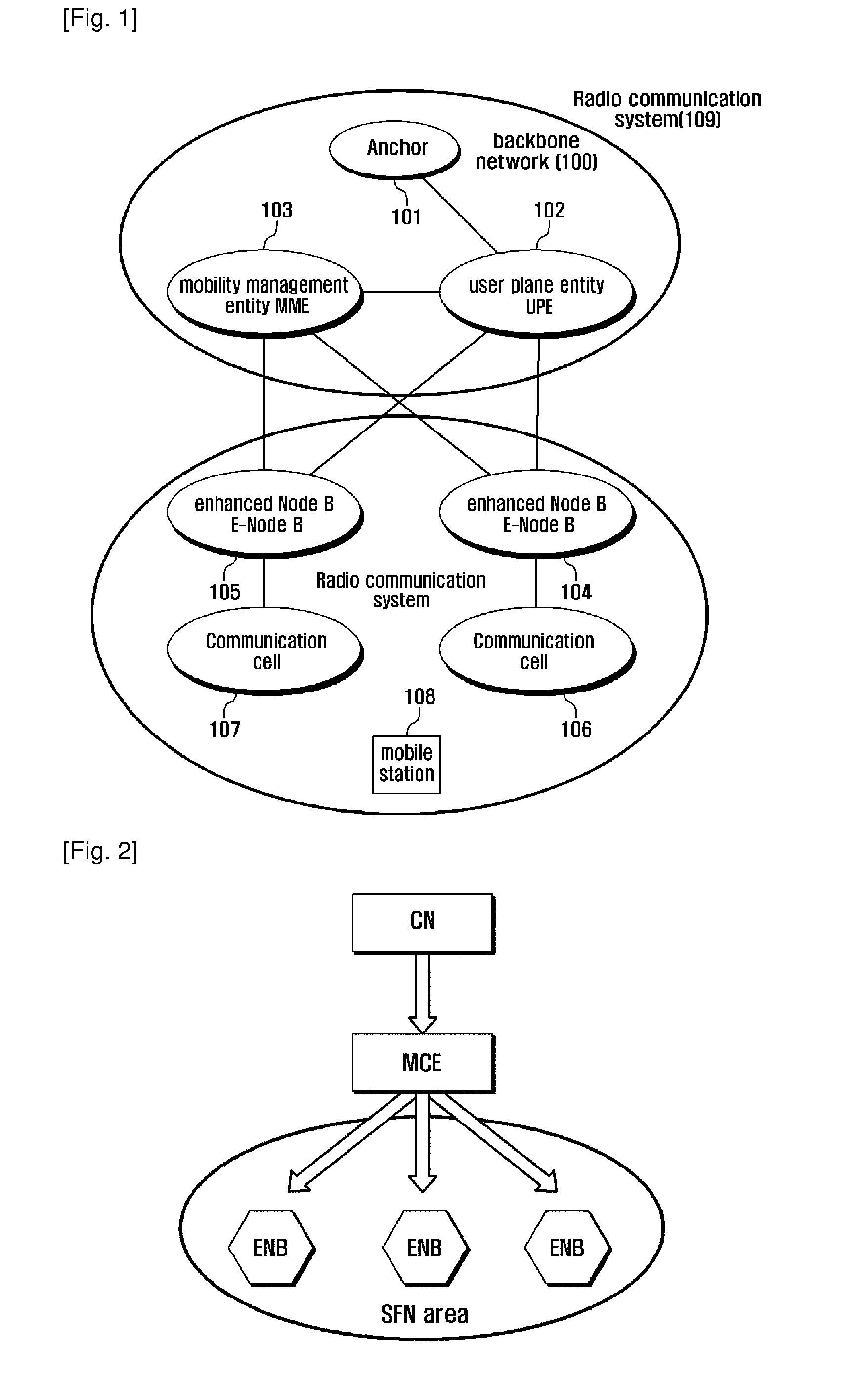

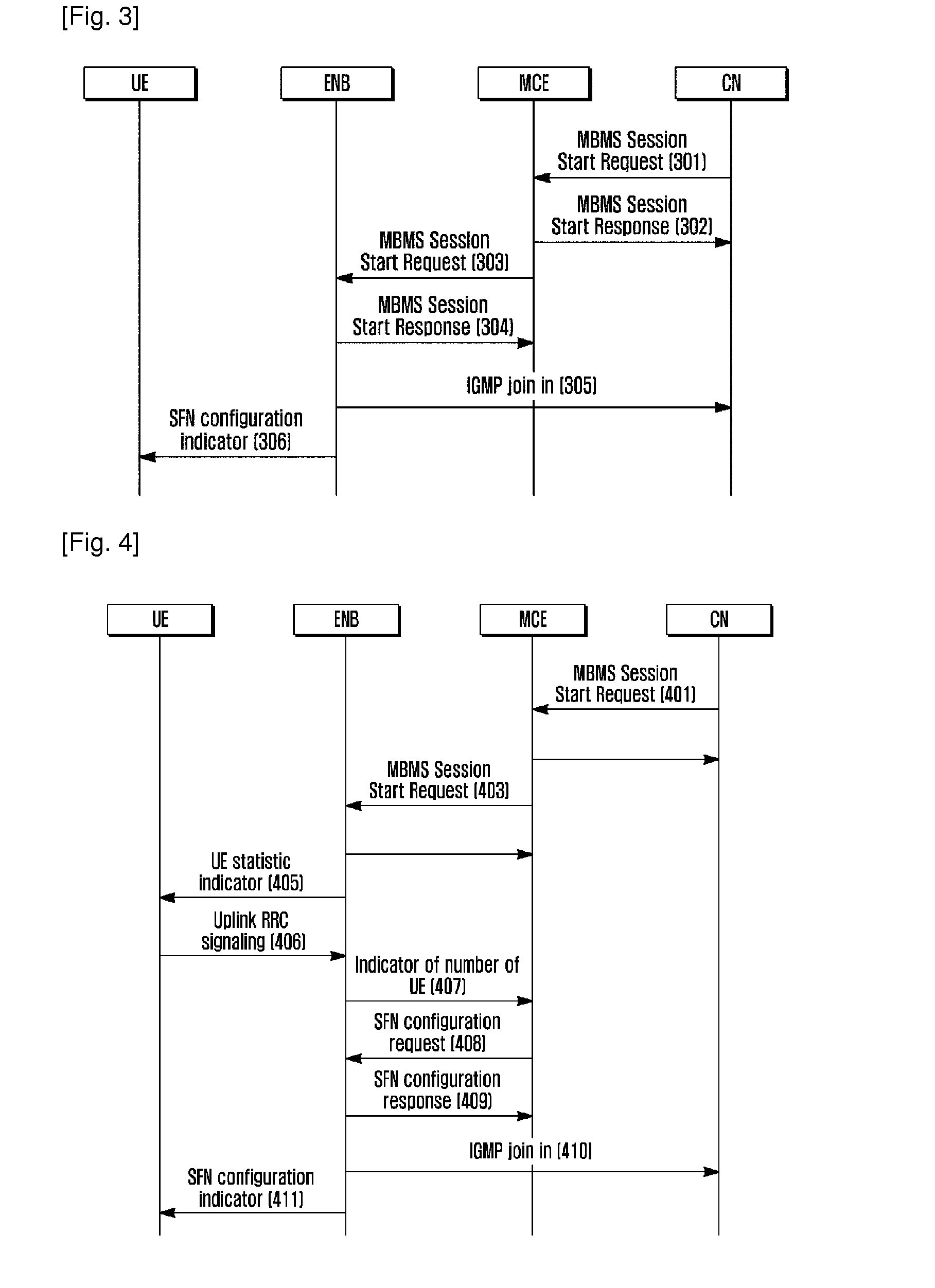

The method for supporting continuous reception of enhanced broadcast service data comprising steps of: an MCE receiving an “MBMS Session Start Request” message from a core network; after the MCE receives the message, transmitting a response message to the core network; MCE transmitting an “MBMS Session Start Request” message to an ENB, the message including information of adjacent cells; and the ENB broadcasting the information of adjacent cells on a current cells. With the scheme of present invention, if a user wants to move to a common cell when he / she receives MBMS service in an SFN edge cell, he / she can enter the active mode and switch into the common cell so as to reduce MBMS data loss. When a UE moves from a cell with SC-PTM transmission mode into a cell with SC-PTM transmission mode, data loss can also be reduced.

Owner:SAMSUNG ELECTRONICS CO LTD

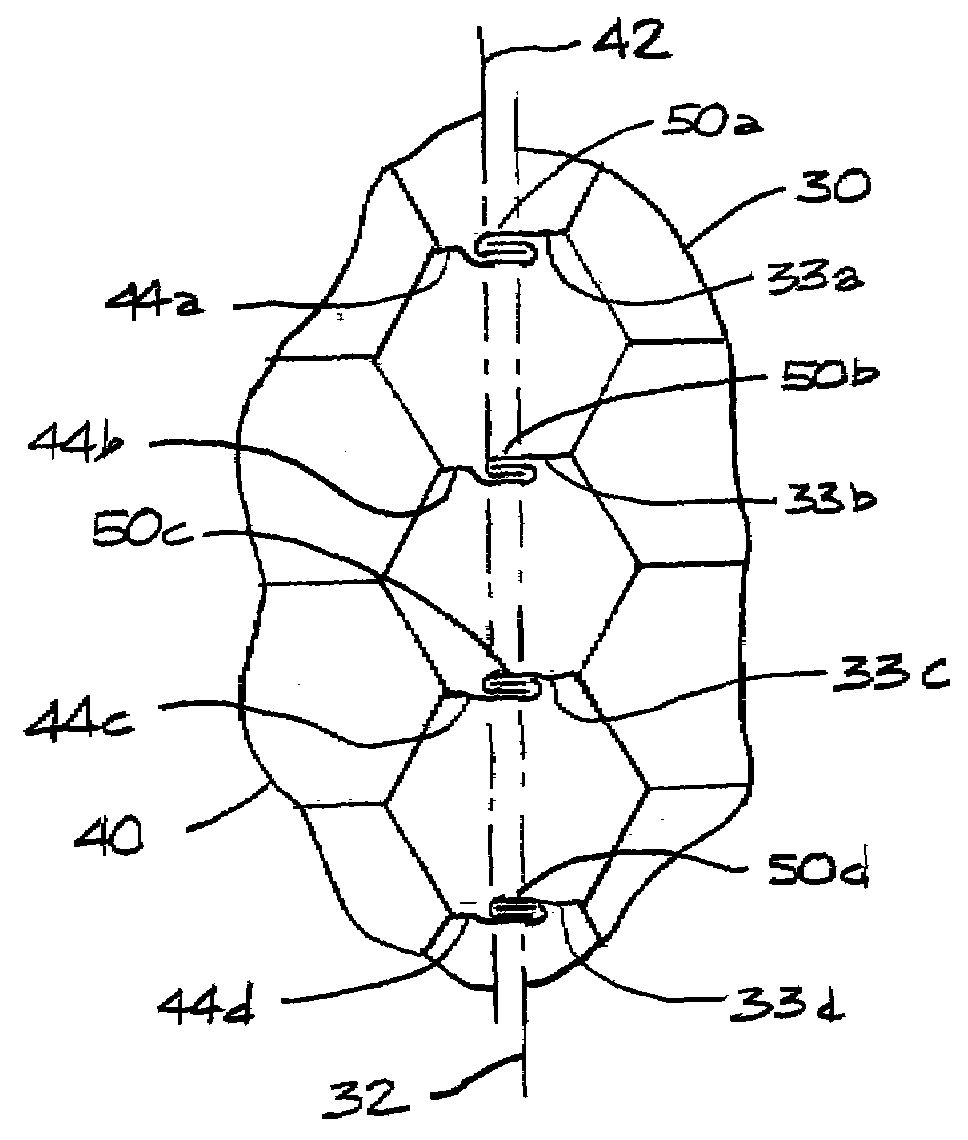

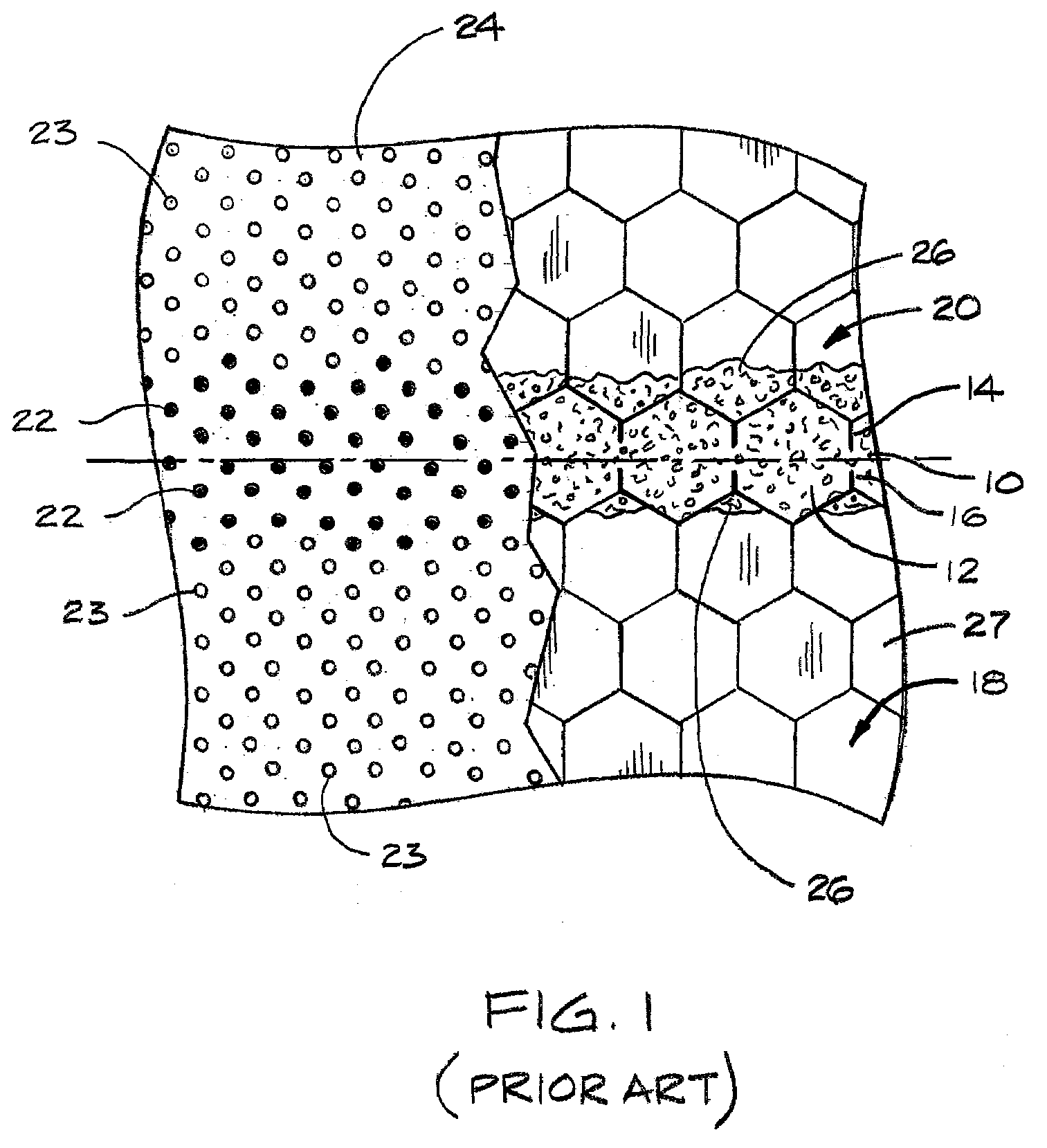

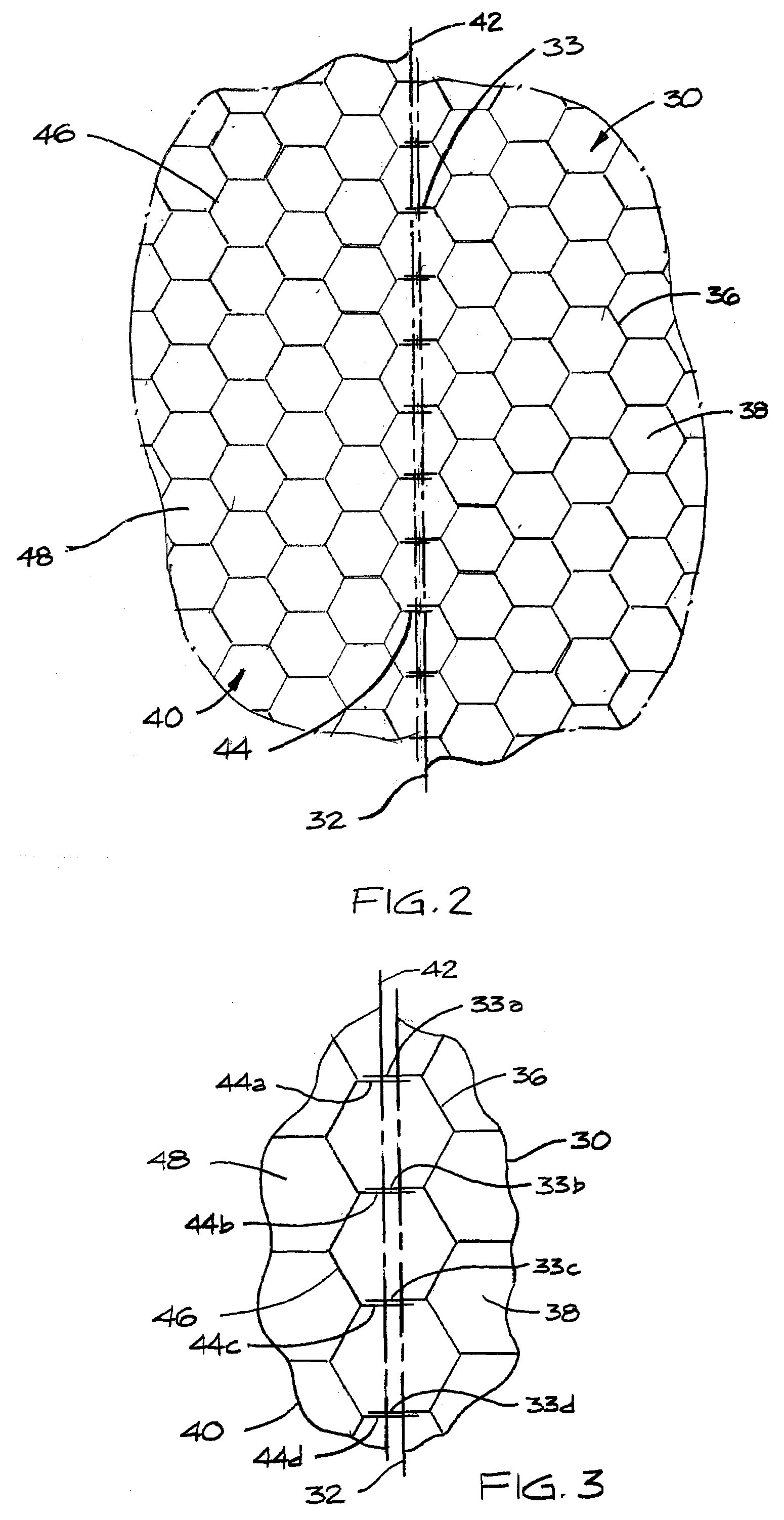

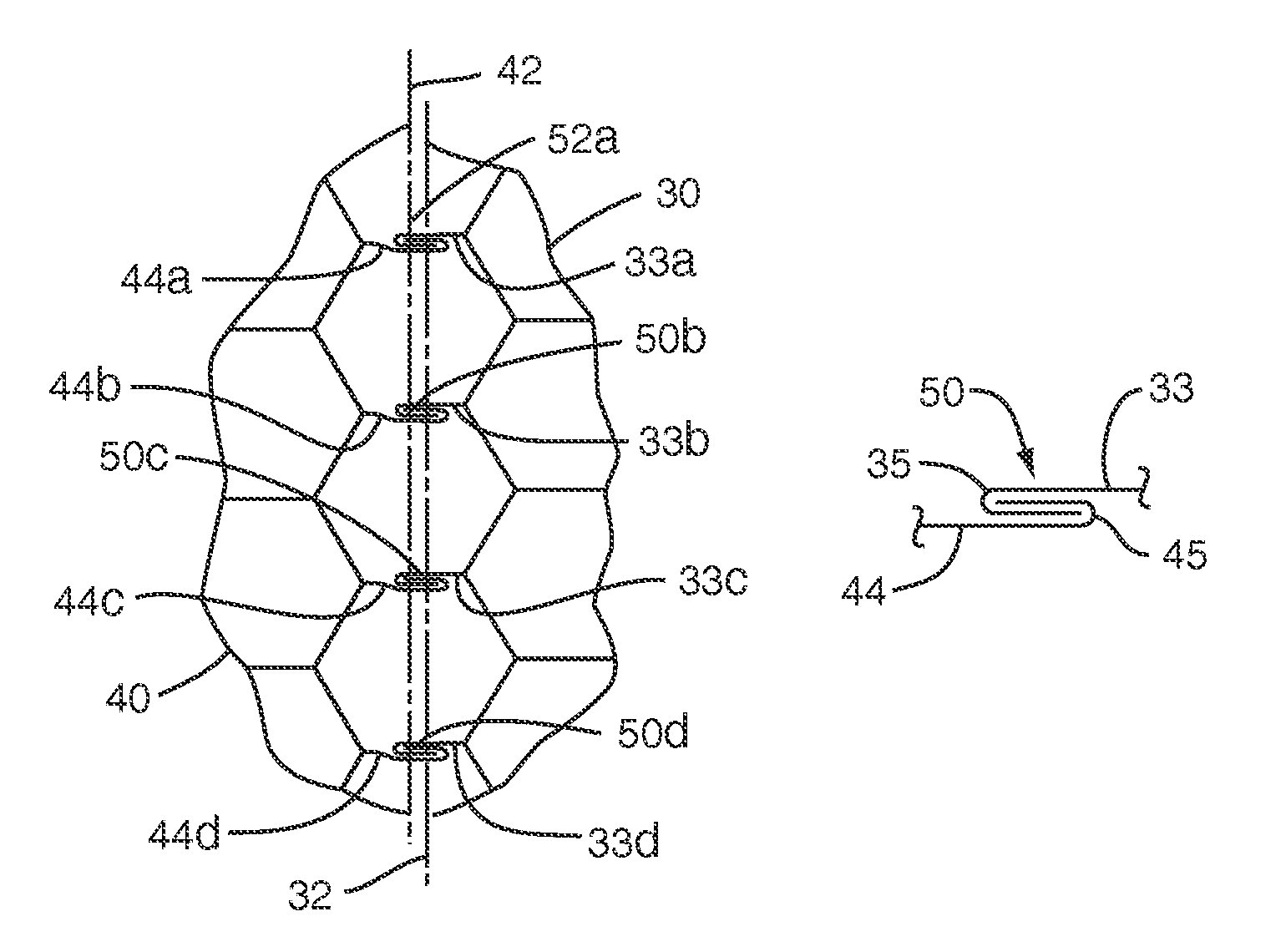

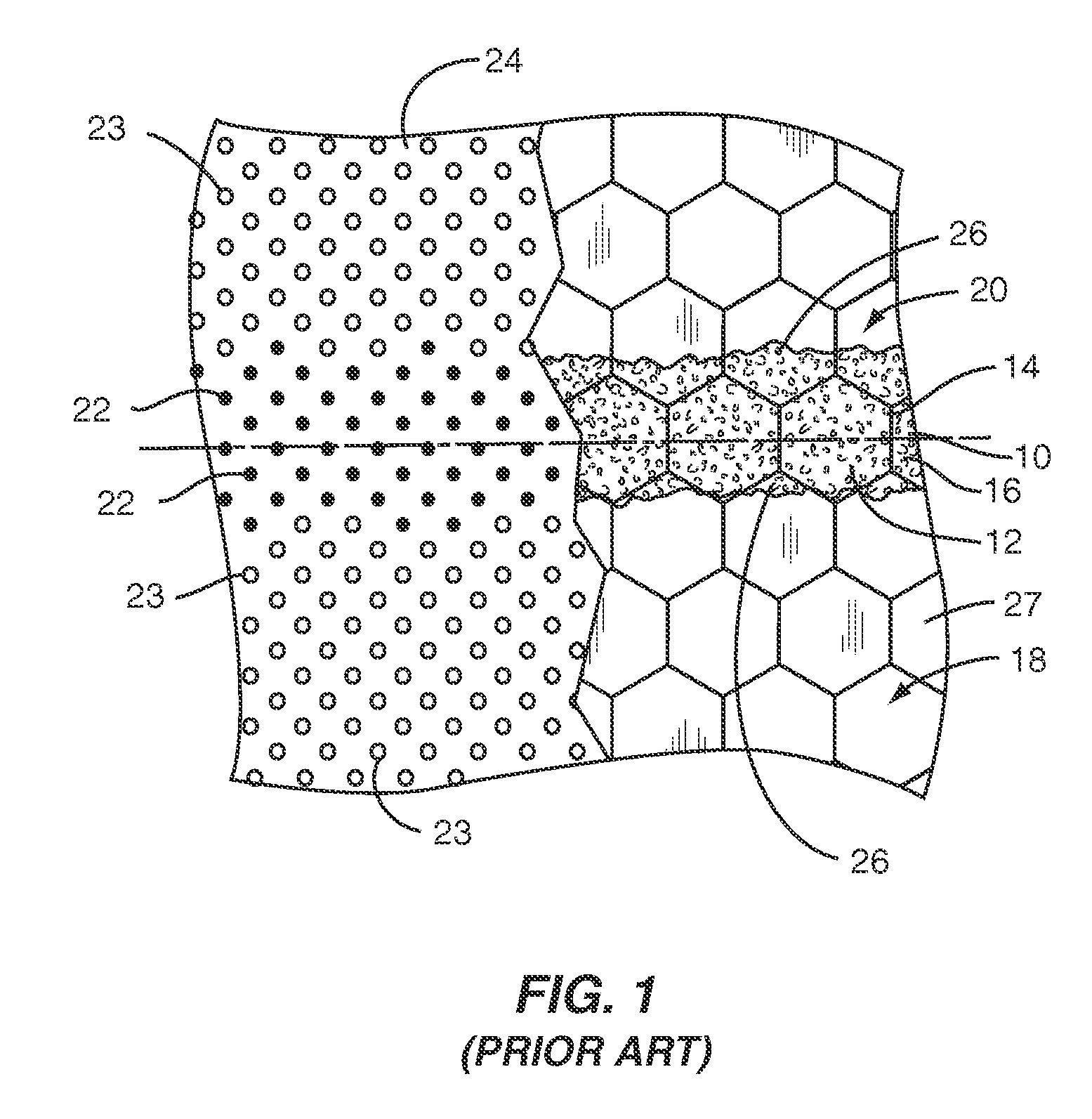

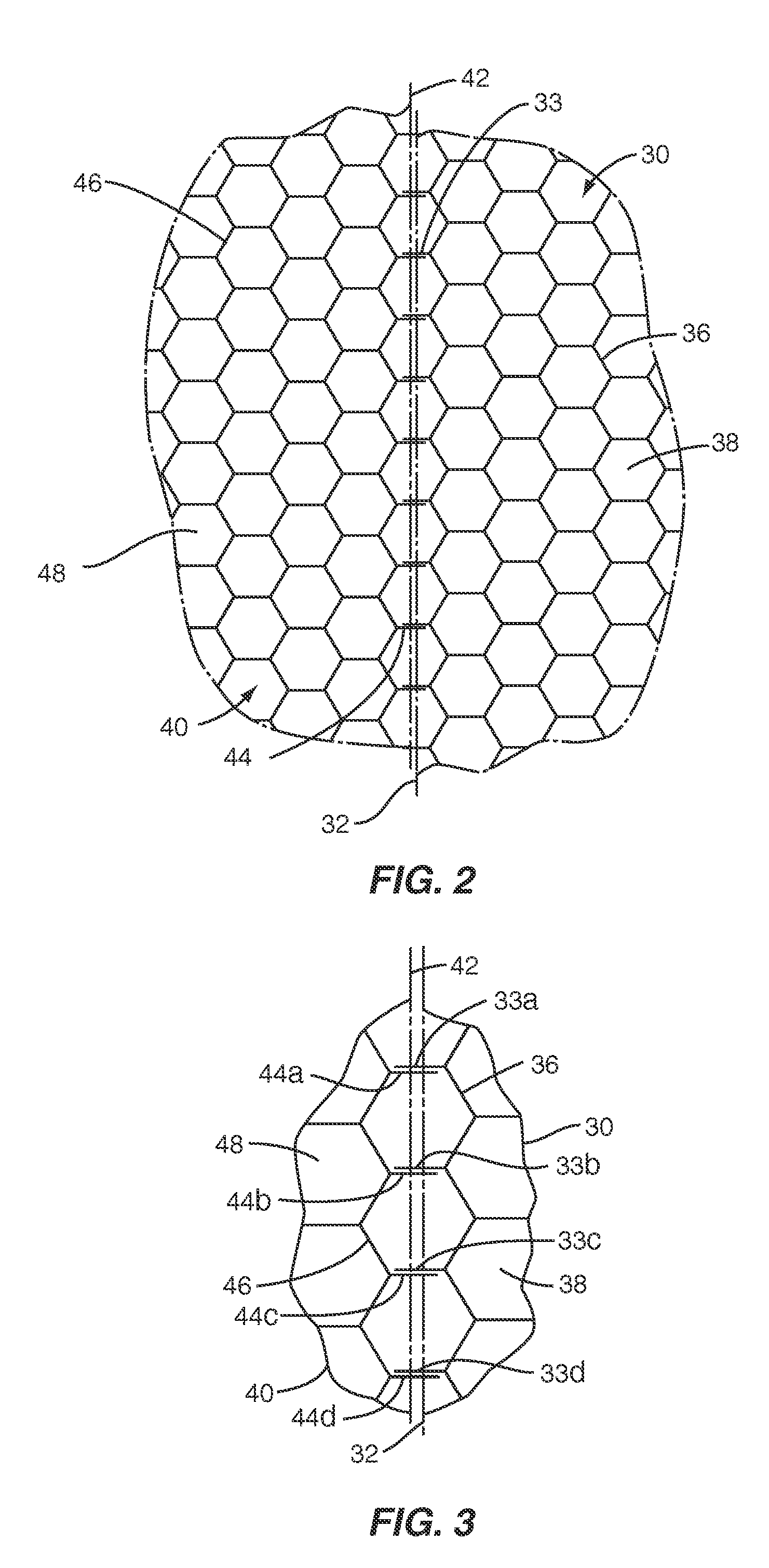

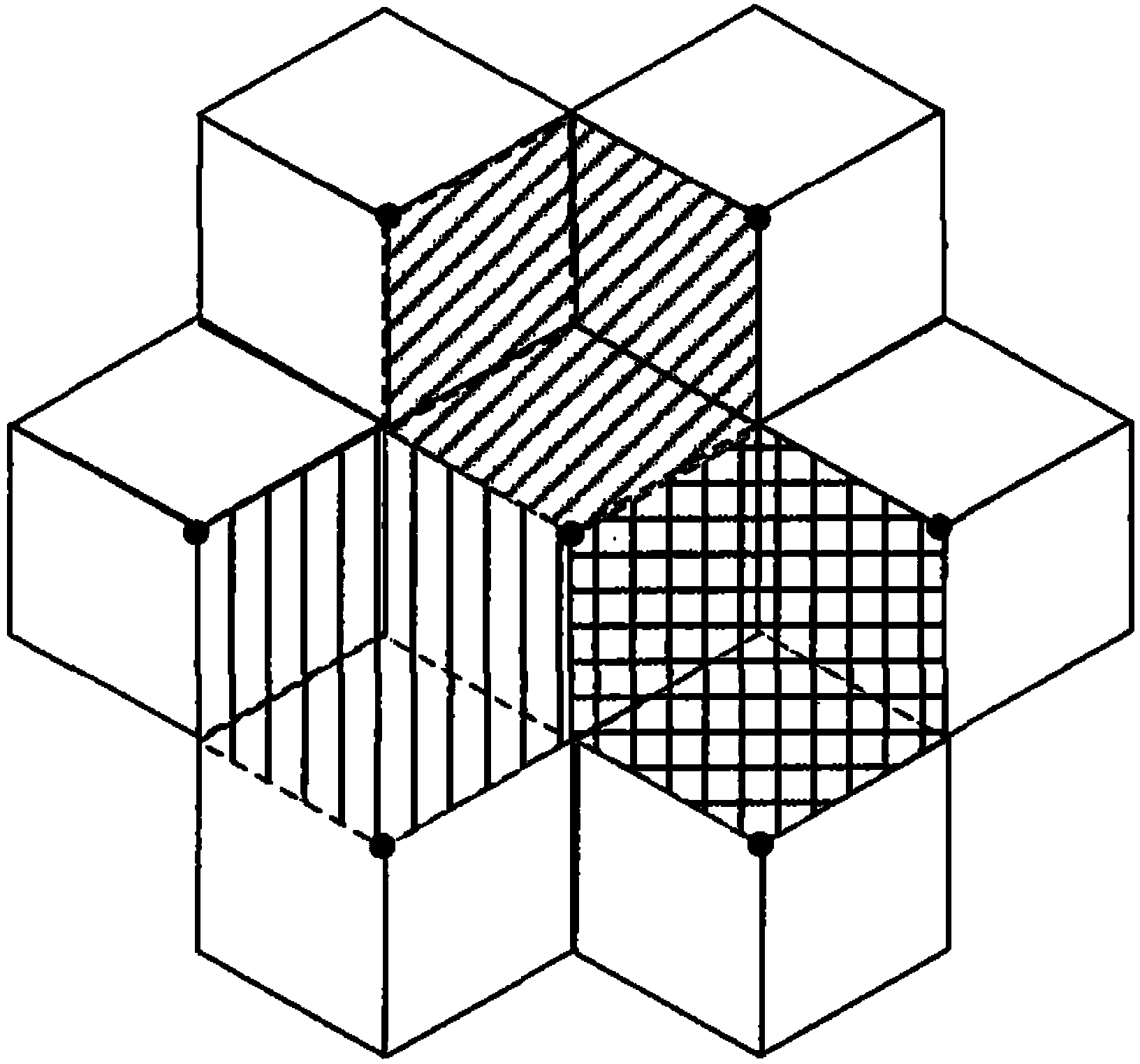

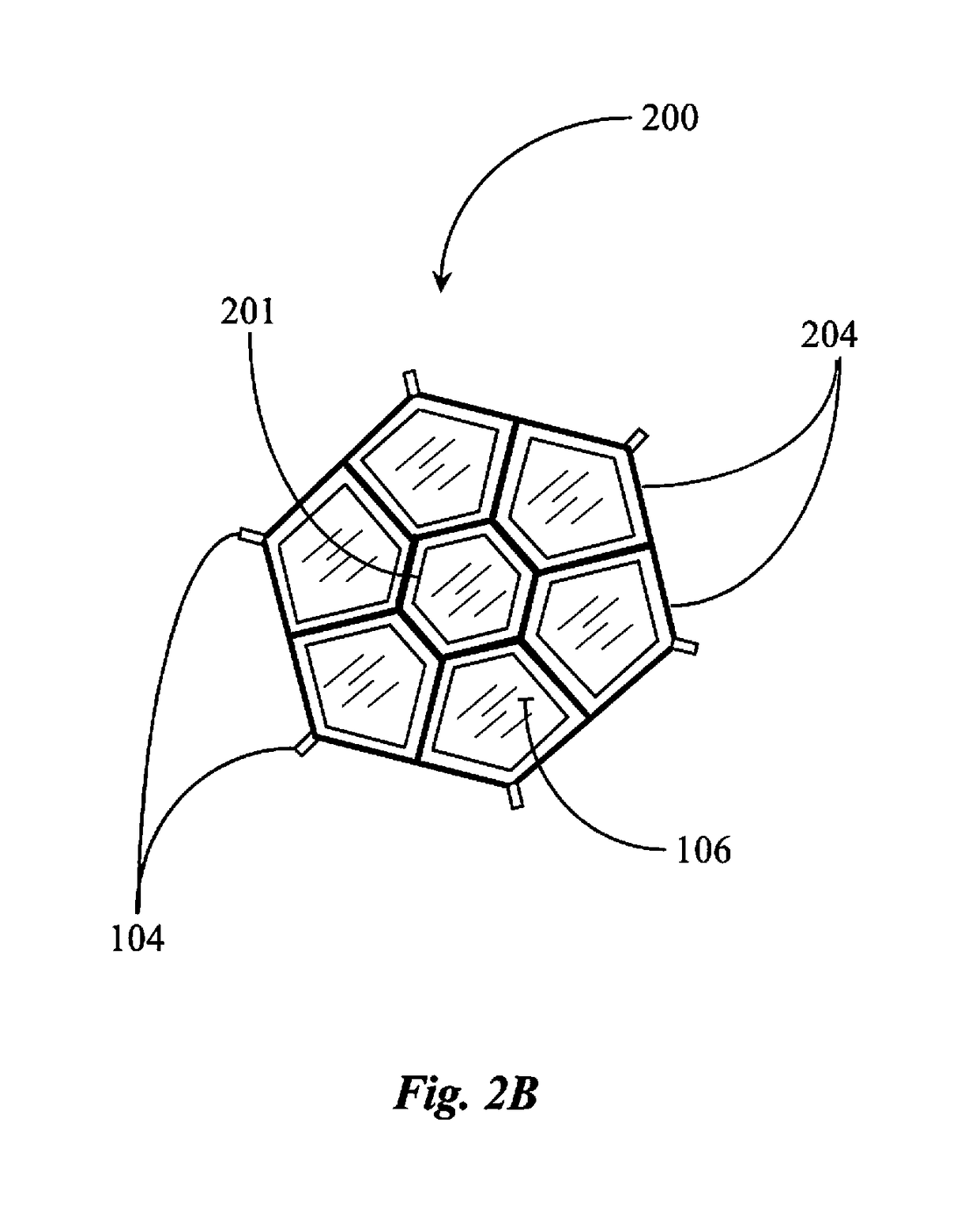

Method of joining composite honeycomb panel sections, and composite panels resulting therefrom

The invention includes a method of joining edges of adjacent honeycomb core panel sections. In one embodiment, the method includes forming a first edge along a first cellular core panel section. The first edge includes a first plurality of edge cell walls along the first edge. The method further includes forming a second edge along a second cellular core panel section, wherein the second edge includes a second plurality of edge cell walls along the second edge. The first edge is positioned proximate to the second edge. At least a portion of at least one of the first plurality of edge cell walls is mechanically interlocked with at least a portion of at least one of the second plurality of edge cell walls to form a joint therebetween. The invention also includes a composite structure at least partially produced by such a method.

Owner:ROHR INC

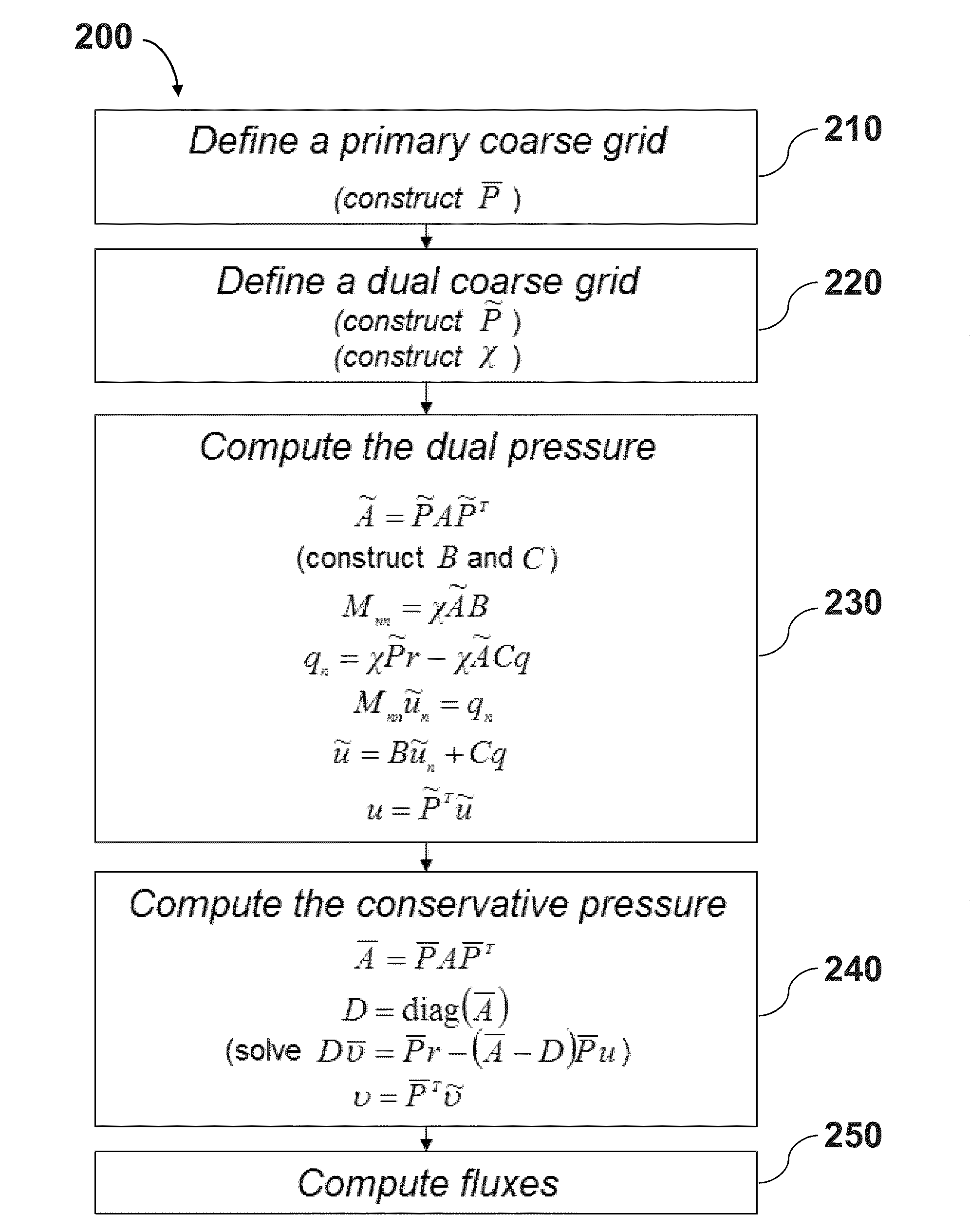

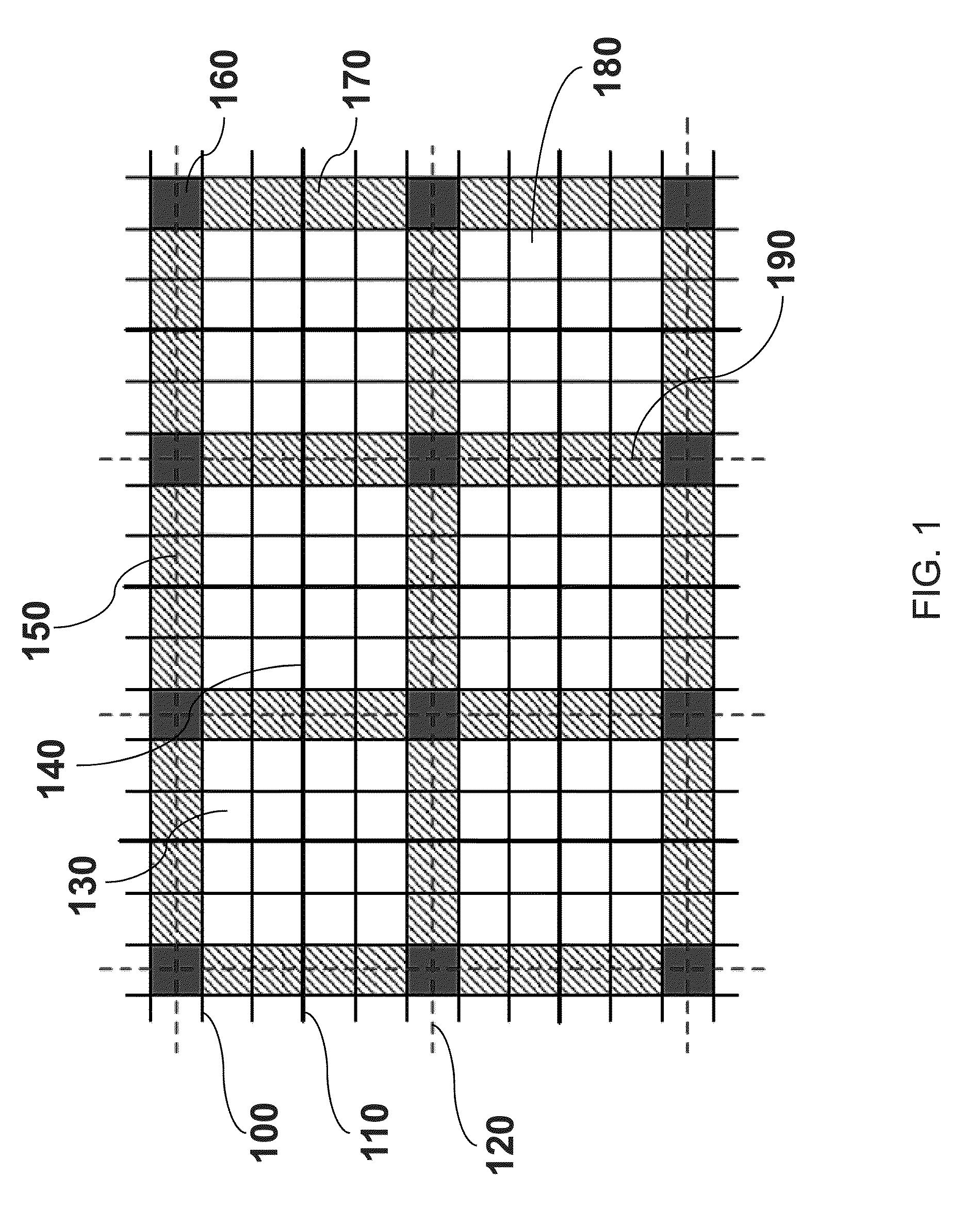

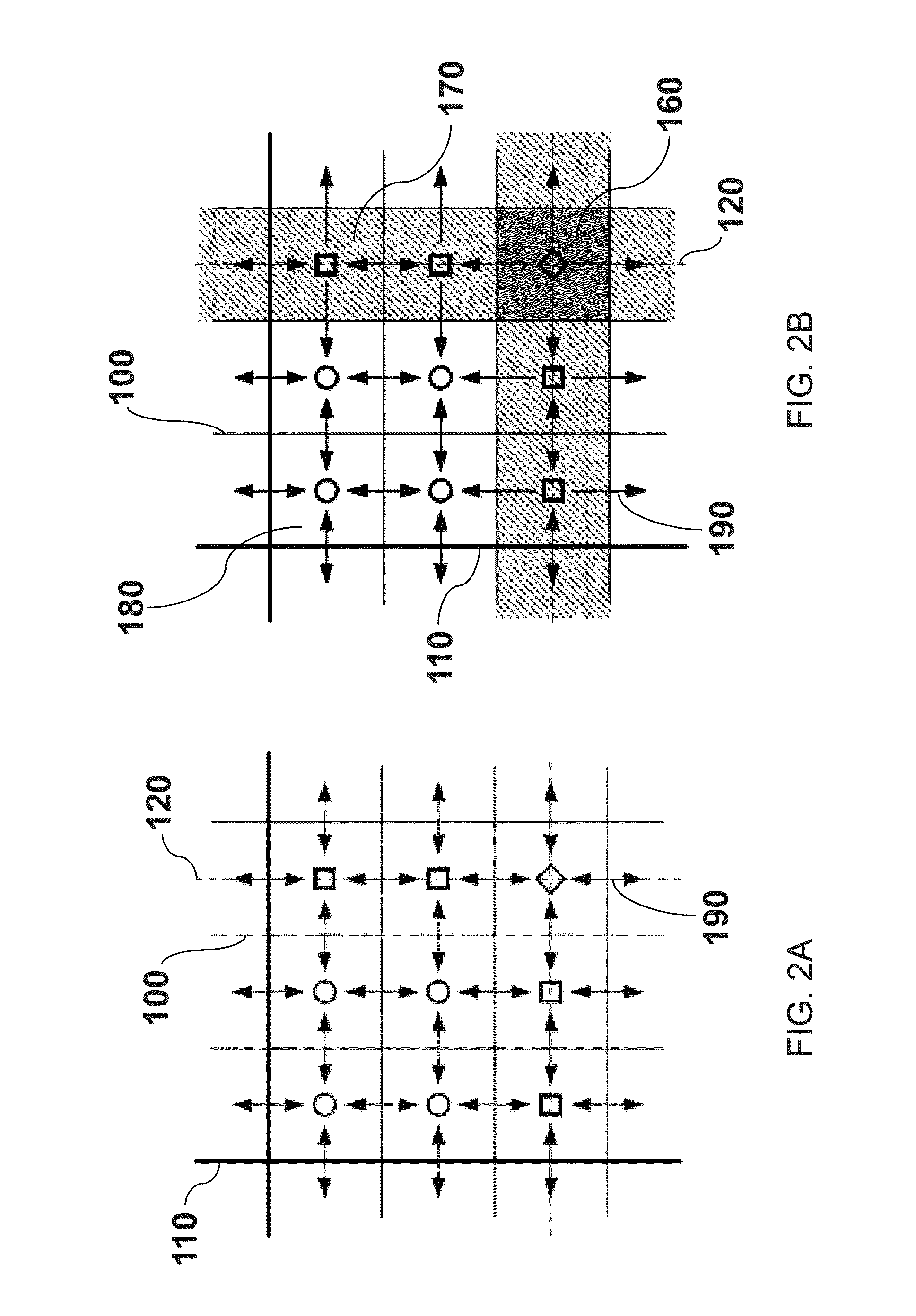

Multi-scale finite volume method for reservoir simulation

ActiveUS20100004908A1Maintain mass balanceComputation using non-denominational number representationDesign optimisation/simulationComputational scienceEdge cell

A multi-scale finite volume method for simulating a fine-scale geological model of subsurface reservoir is disclosed. The method includes providing a fine-scale geological model of a subsurface reservoir associated with a fine-scale grid, a coarse-scale grid, and a dual coarse-scale grid. A coarse-scale operator is constructed based on internal cells, edge cells, and node cells on the fine-scale grid that are defined by the dual coarse-scale grid. Pressure in the dual coarse-scale cells is computed using the coarse-scale operator. Pressure in the primary coarse-scale cells is computed using the computed pressure in the dual coarse-scale cells. A display is produced using the computed pressure in the primary coarse-scale cells. An iterative scheme can be applied such that the computed pressure in the primary coarse-scale cells converges to the fine-scale pressure solution and mass balance is maintained on the coarse-scale.

Owner:SCHLUMBERGER TECH CORP +1

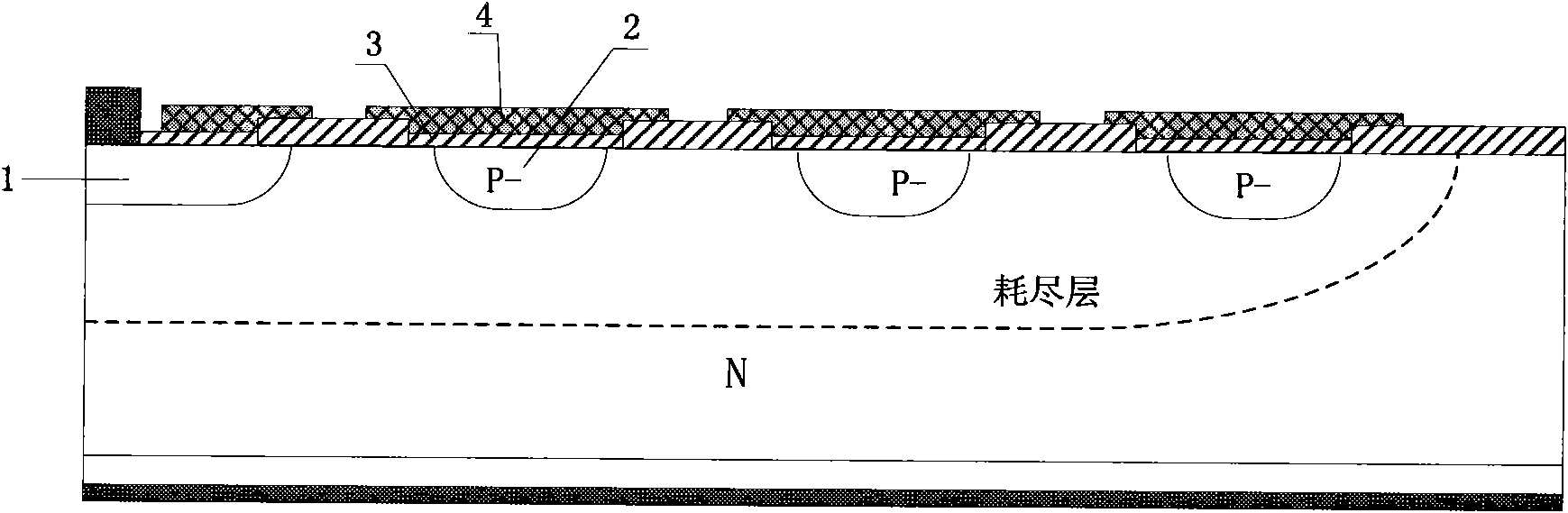

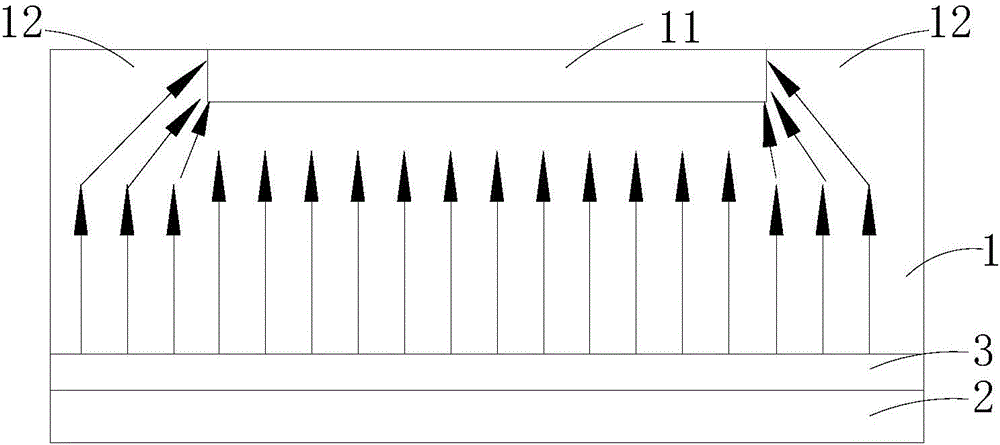

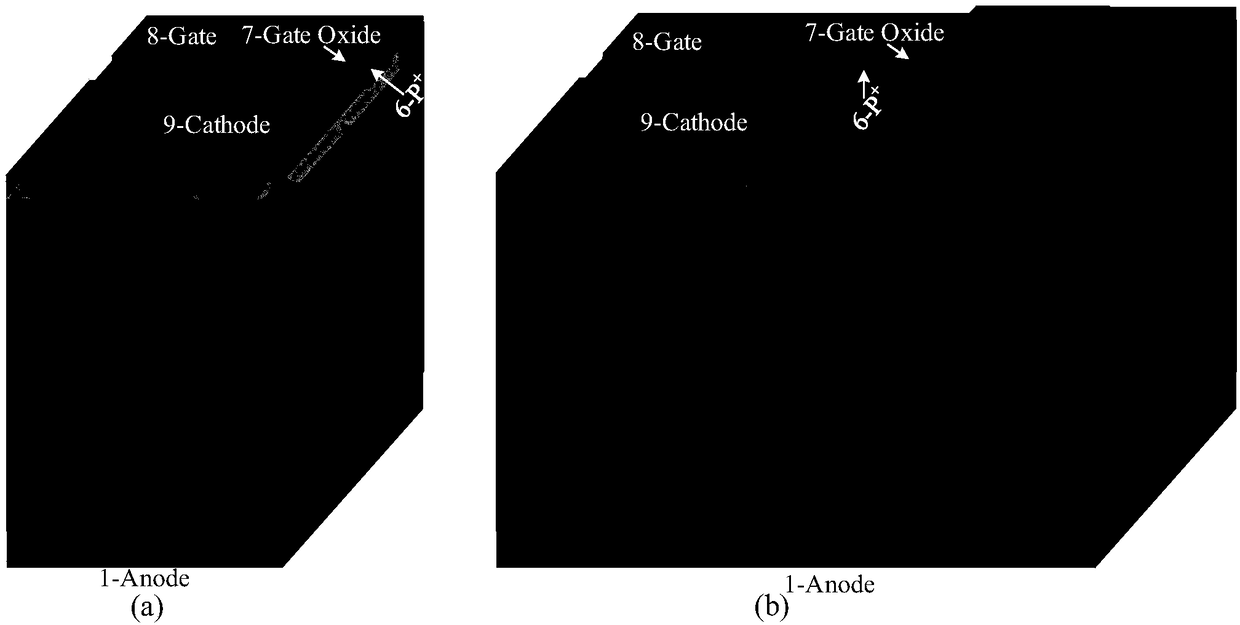

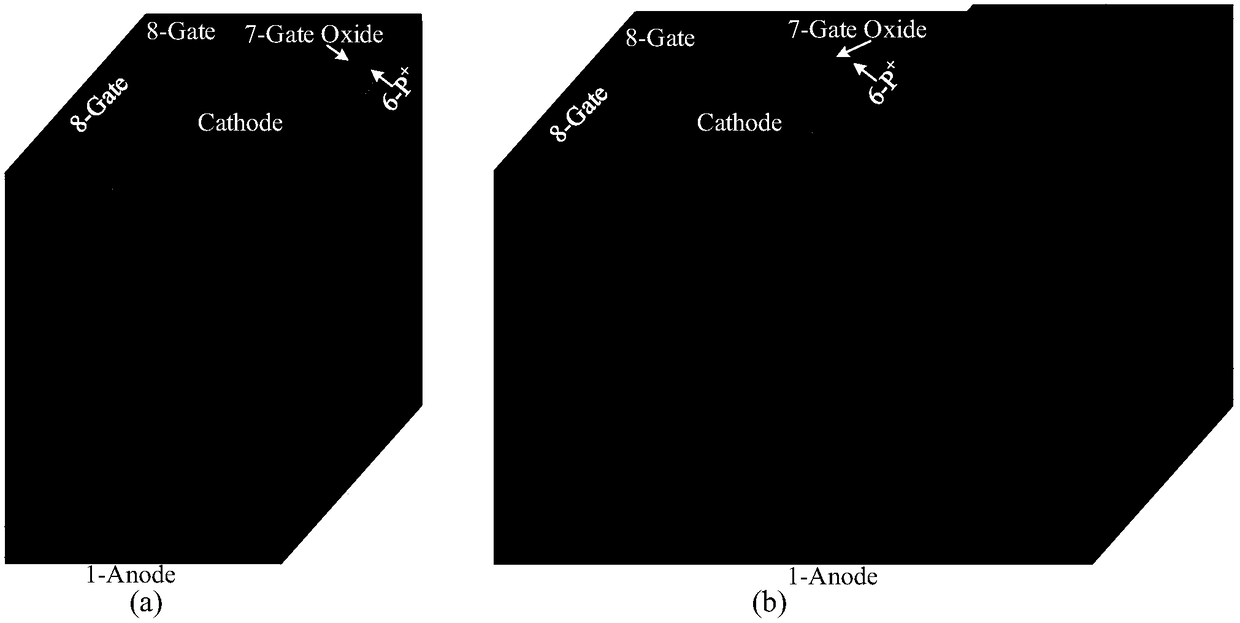

Edge terminal structure of high-voltage power semiconductor device

InactiveCN101969069AReduce areaLow costSolid-state devicesSemiconductor devicesPower semiconductor deviceOxygen

The invention discloses an edge terminal structure of a high-voltage power semiconductor device. The edge terminal structure comprises a plurality of field limiting rings which surround the power semiconductor device and have the conduction type opposite to that of a substrate, wherein doping regions which have the same conduction type as the field limiting rings and lower doping density than the field limiting rings are arranged around the field limiting rings; the field limiting rings are wrapped by the doping regions and coated by field plates; and the field limiting rings are separated from the field plates by using silicon dioxide layers. The field plates can be made of copper, aluminum, polycrystalline silicon, oxygen-doped polycrystalline silicon and the like. Because the doping regions with lower density are arranged around the conventional field limiting rings, the density of edge cell electric field lines can be effectively reduced, the electric field strength born by an edge cell is reduced, the breakdown voltage is increased, the area efficiency of the edge terminal structure is effectively improved, the chip area is saved and the chip cost is reduced.

Owner:ZHEJIANG UNIV +1

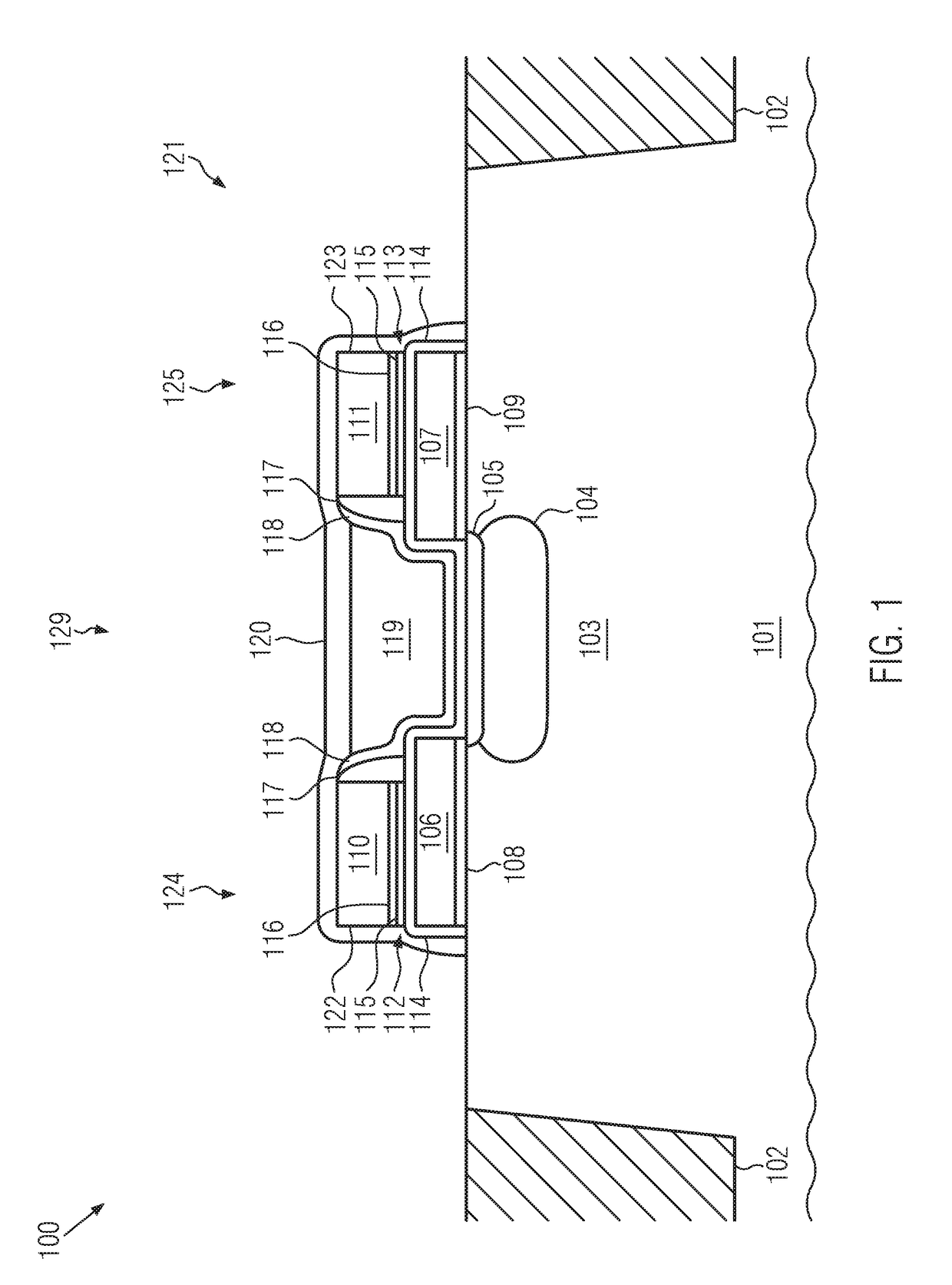

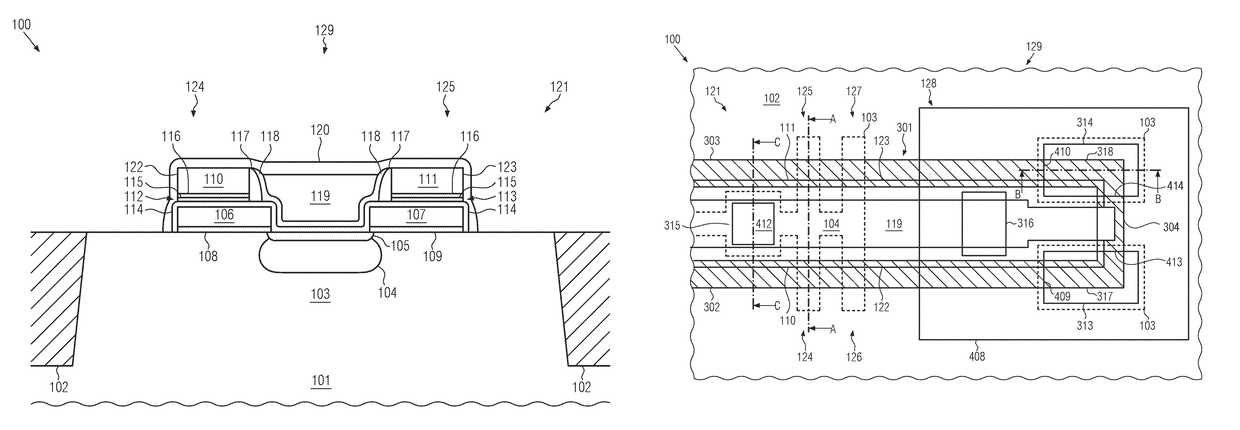

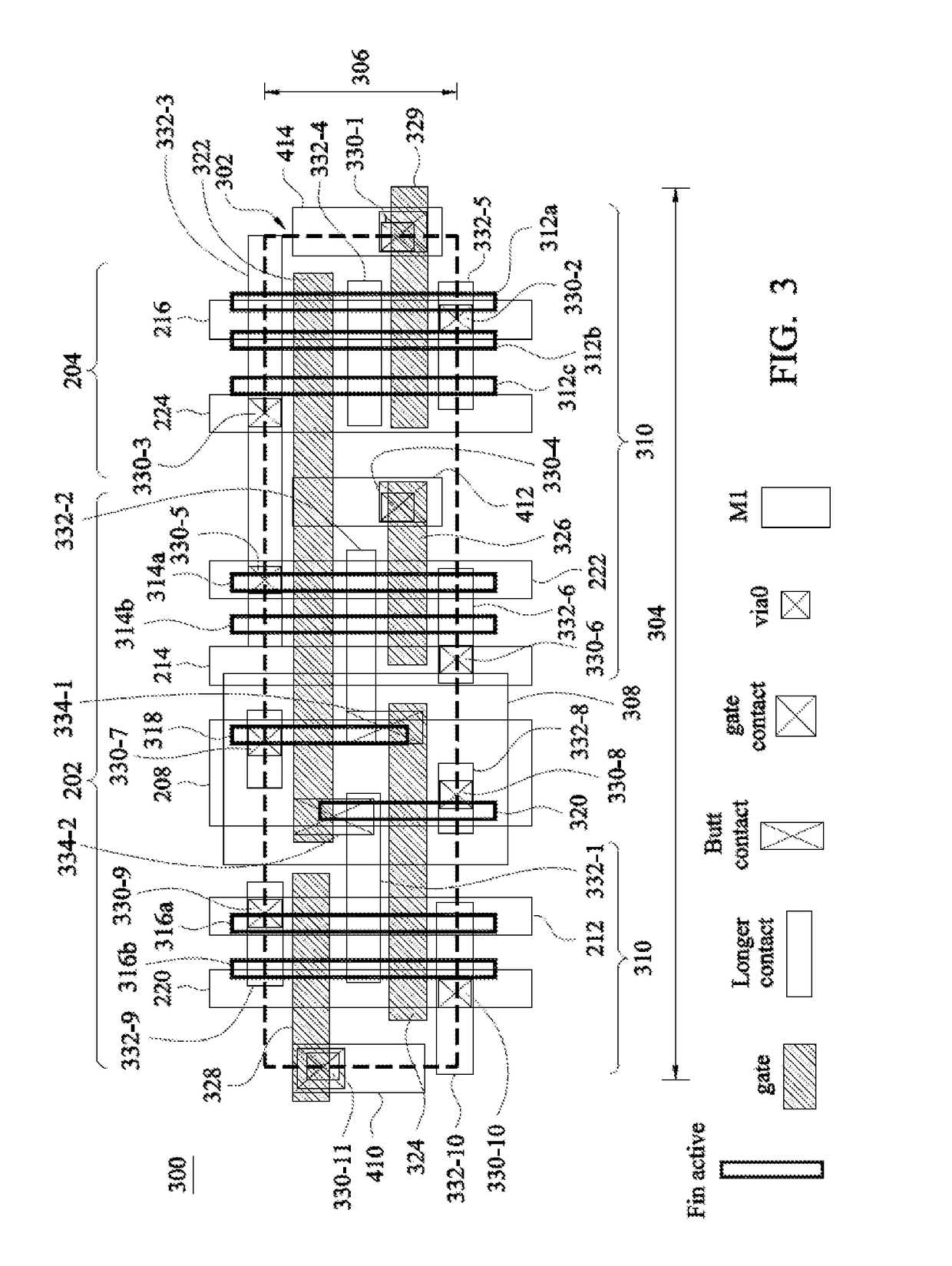

Novel Dummy Gate Technology to Avoid Shorting Circuit

ActiveUS20160372476A1Semiconductor/solid-state device detailsSolid-state devicesActive memoryEngineering

Semiconductor devices and method of manufacturing such semiconductor devices are provided for improved FinFET memory cells to avoid electric short often happened between metal contacts of a bit cell, where the meal contacts are positioned next to a dummy gate of a neighboring dummy edge cell. In one embodiment, during the patterning of a gate layer on a substrate surface, an improved gate slot pattern is used to extend the lengths of one or more gate slots adjacent bit lines so as to pattern and sectionalize a dummy gate line disposed next to metal contacts of an active memory cell. In another embodiment, during the patterning of gate lines, the distances between one or more dummy gates lines disposed adjacent an active memory cell are adjusted such that their locations within dummy edge cells are shifted in position to be away from metal contacts of the active memory cell.

Owner:UNITED MICROELECTRONICS CORP

Method of joining composite honeycomb sections

The invention includes a method of joining edges of adjacent honeycomb core panel sections. In one embodiment, the method includes forming a first edge along a first cellular core panel section. The first edge includes a first plurality of edge cell walls along the first edge. The method further includes forming a second edge along a second cellular core panel section, wherein the second edge includes a second plurality of edge cell walls along the second edge. The first edge is positioned proximate to the second edge. At least a portion of at least one of the first plurality of edge cell walls is mechanically interlocked with at least a portion of at least one of the second plurality of edge cell walls to form a joint therebetween. The invention also includes a composite structure at least partially produced by such a method.

Owner:ROHR INC

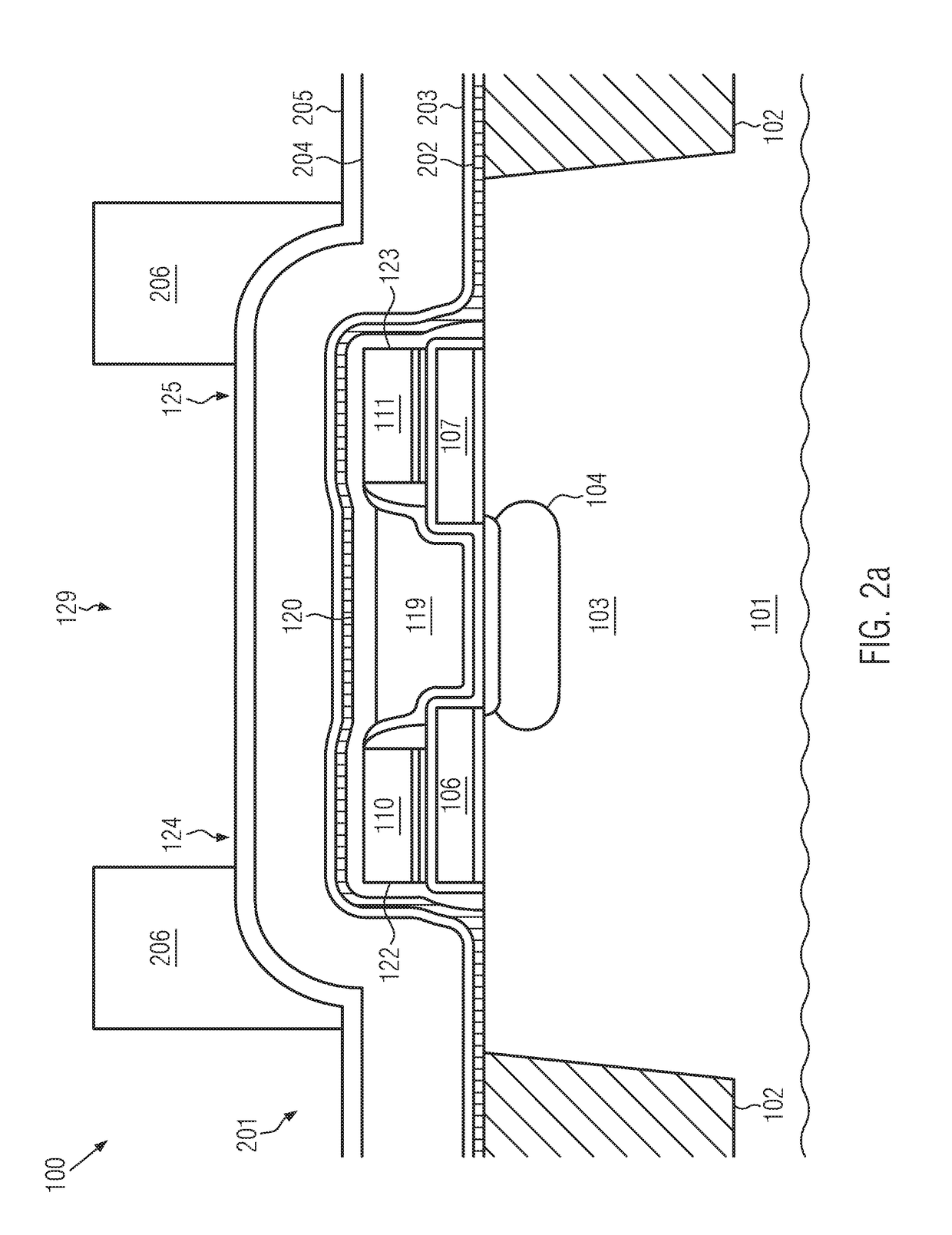

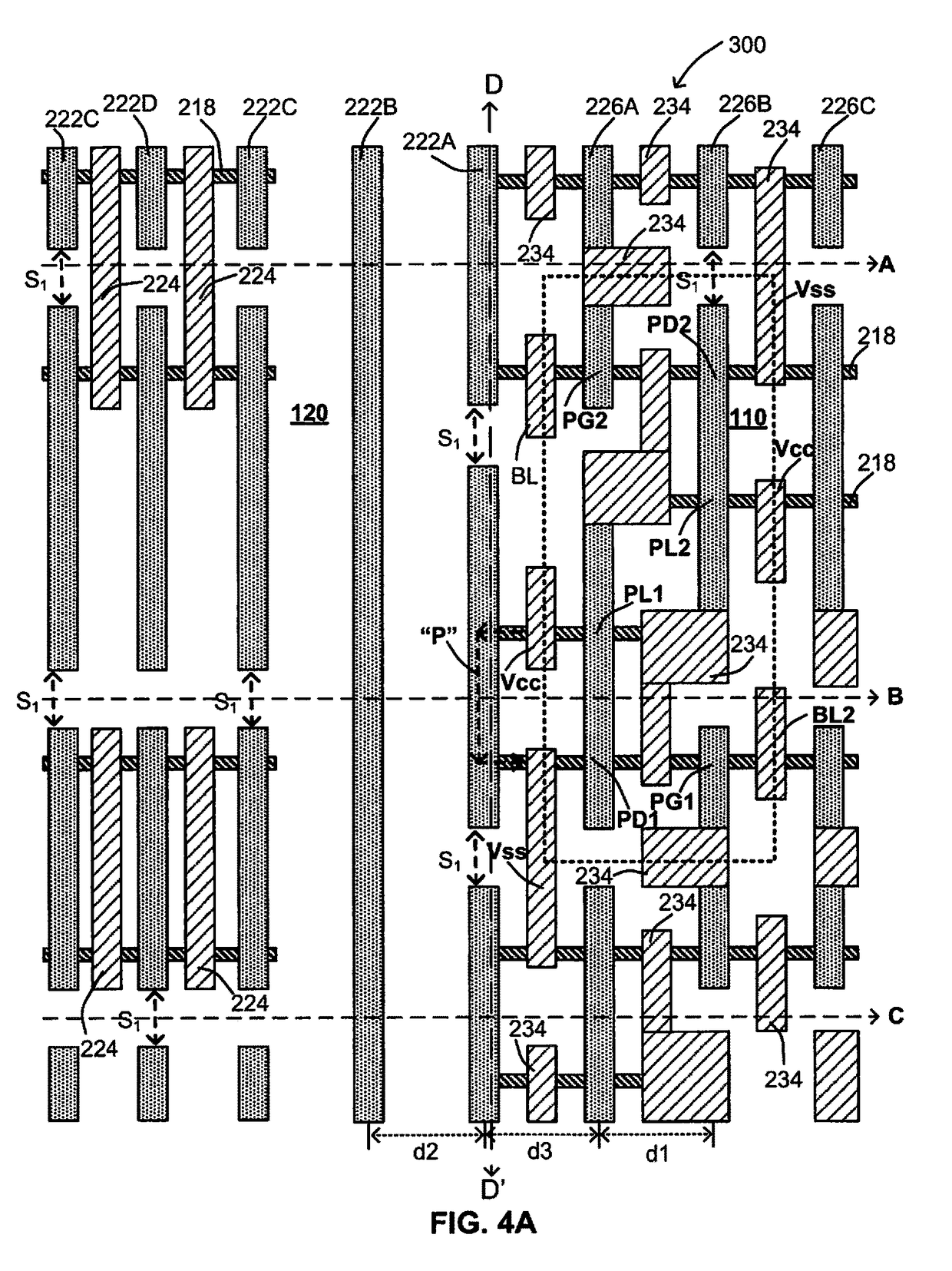

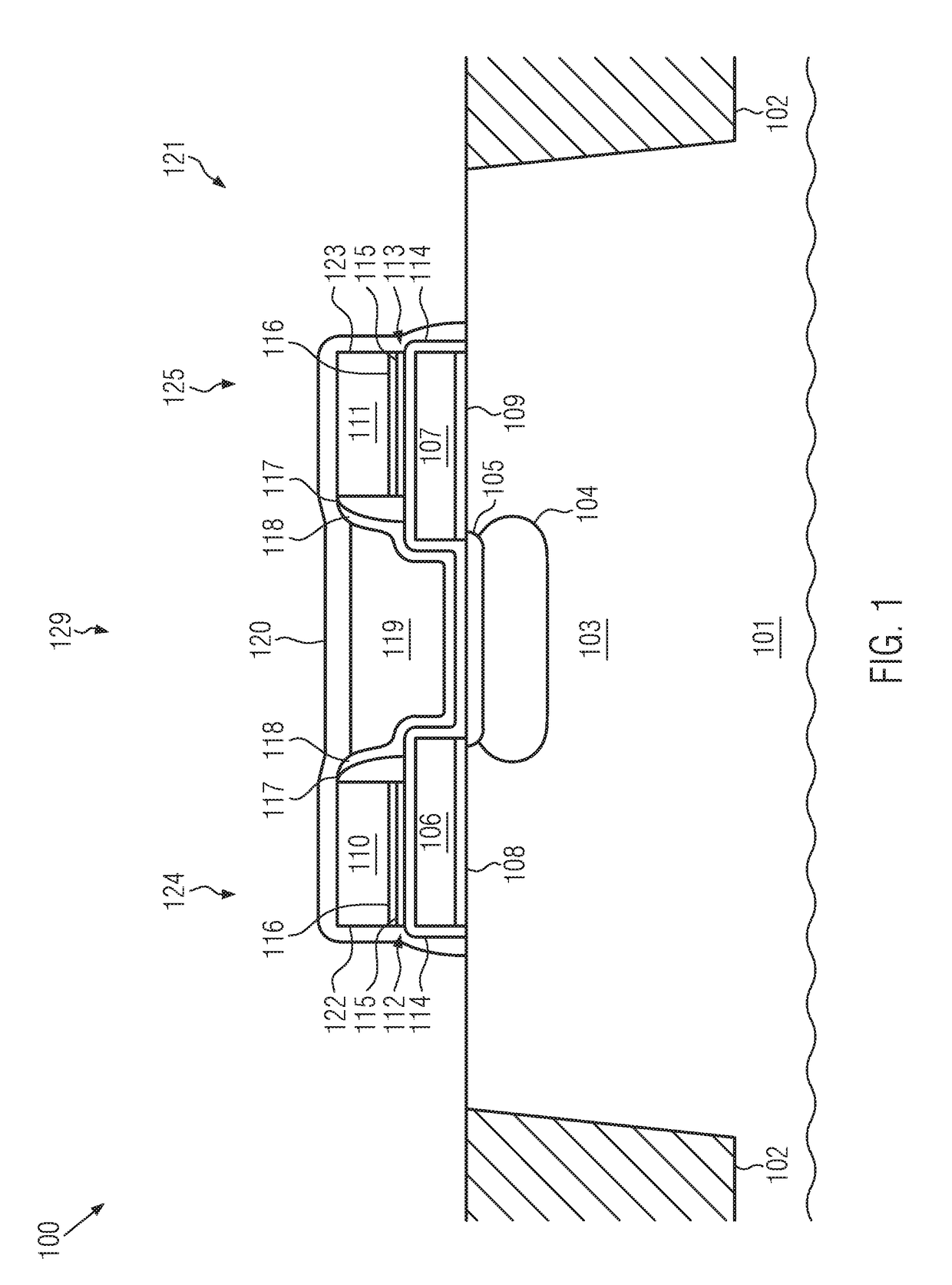

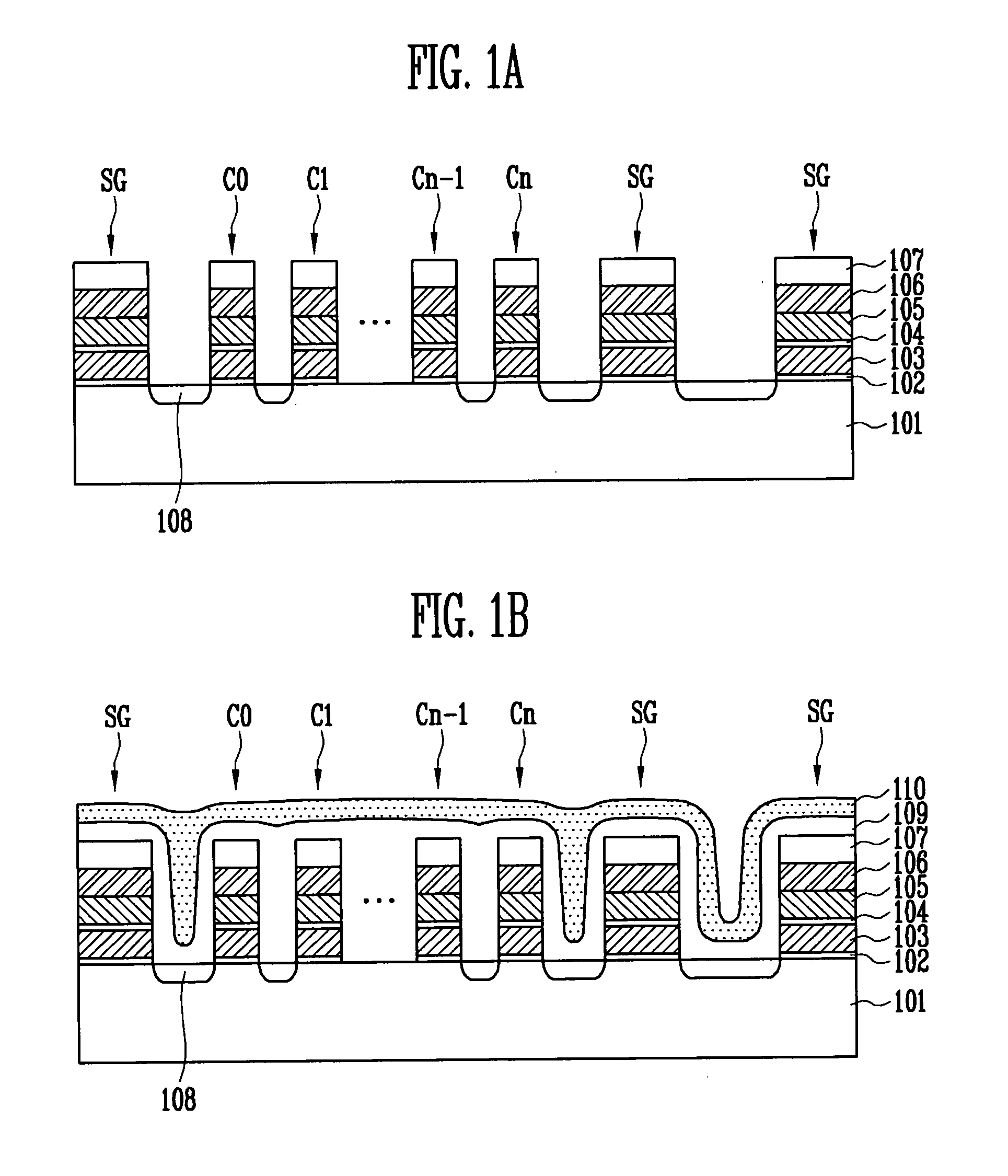

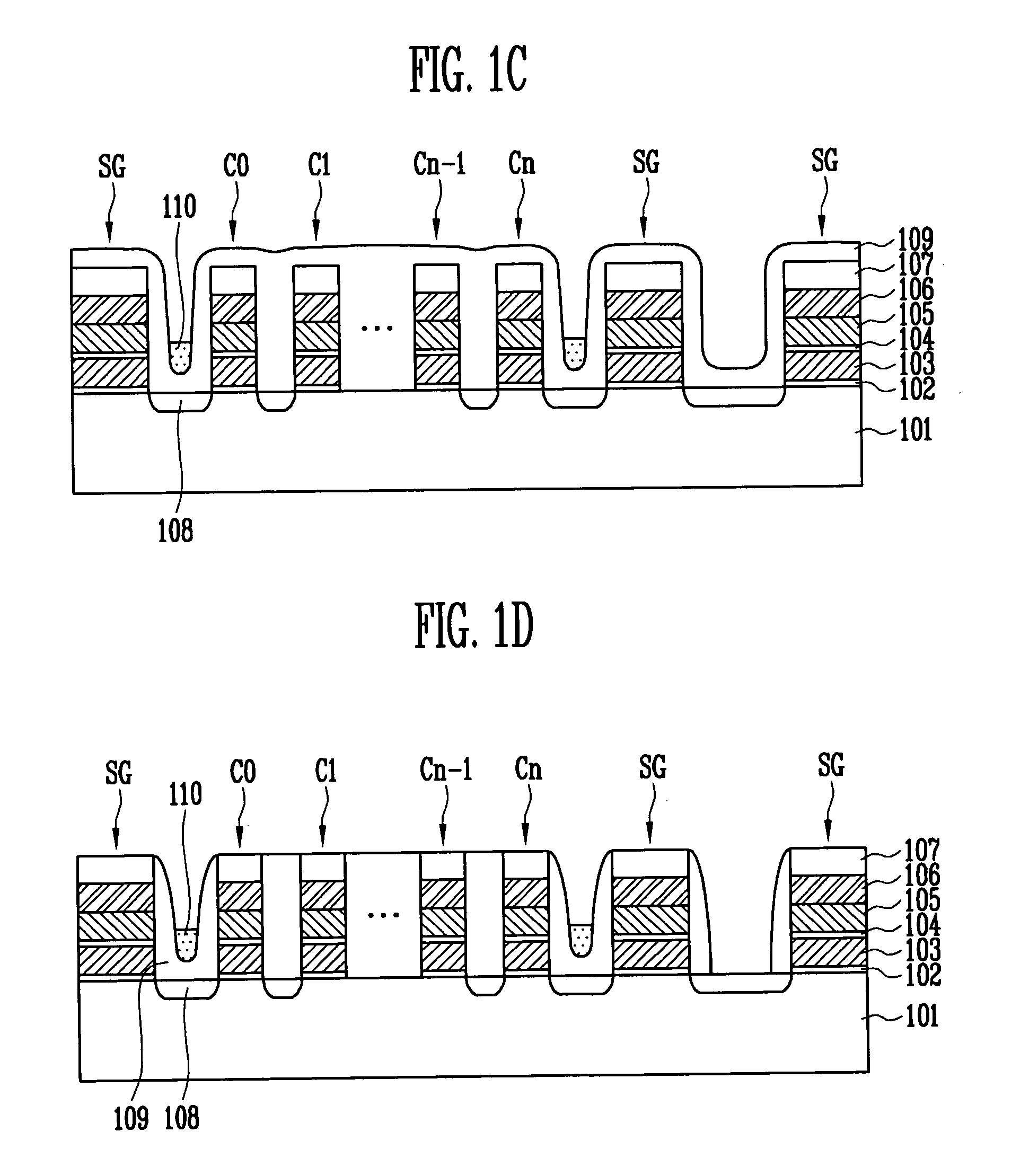

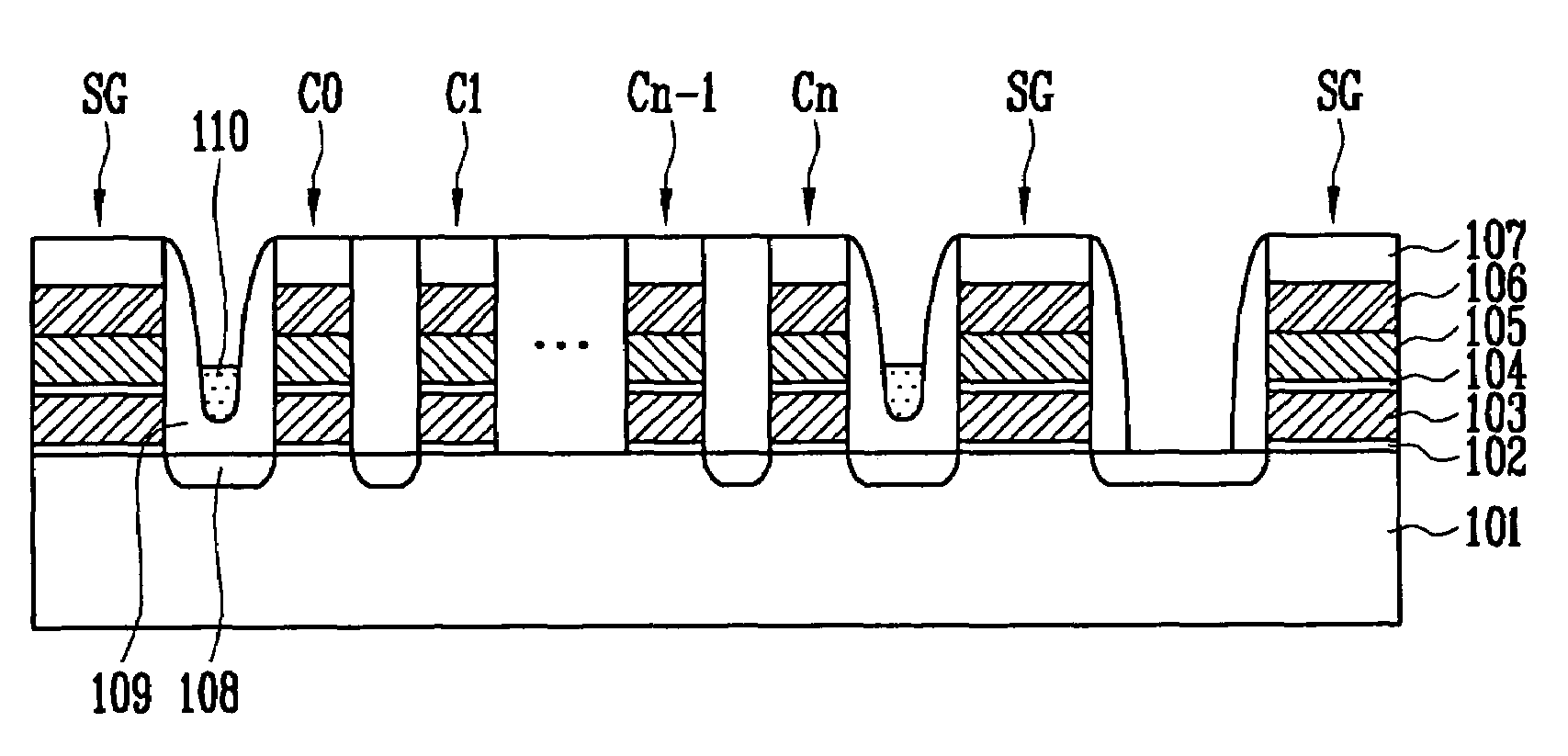

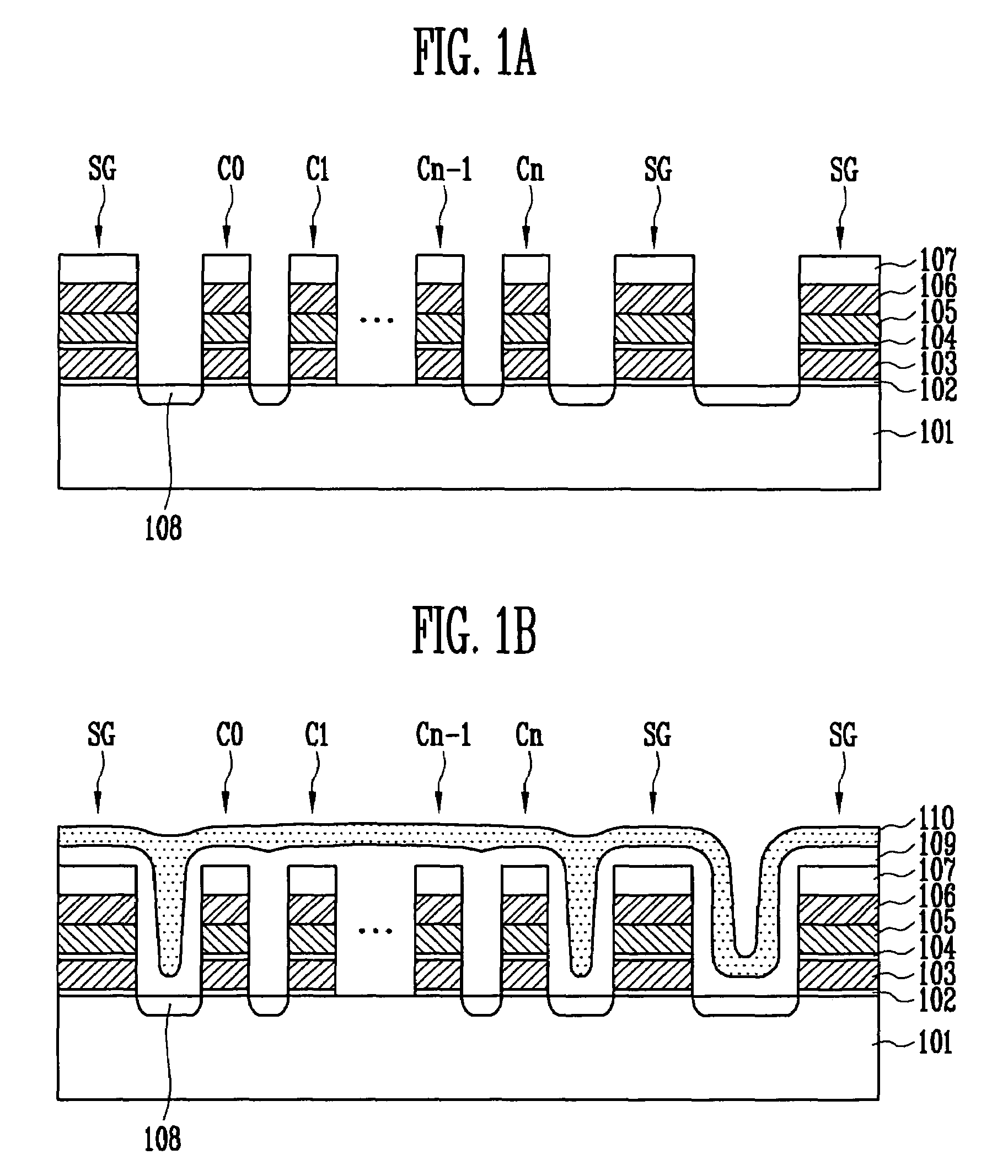

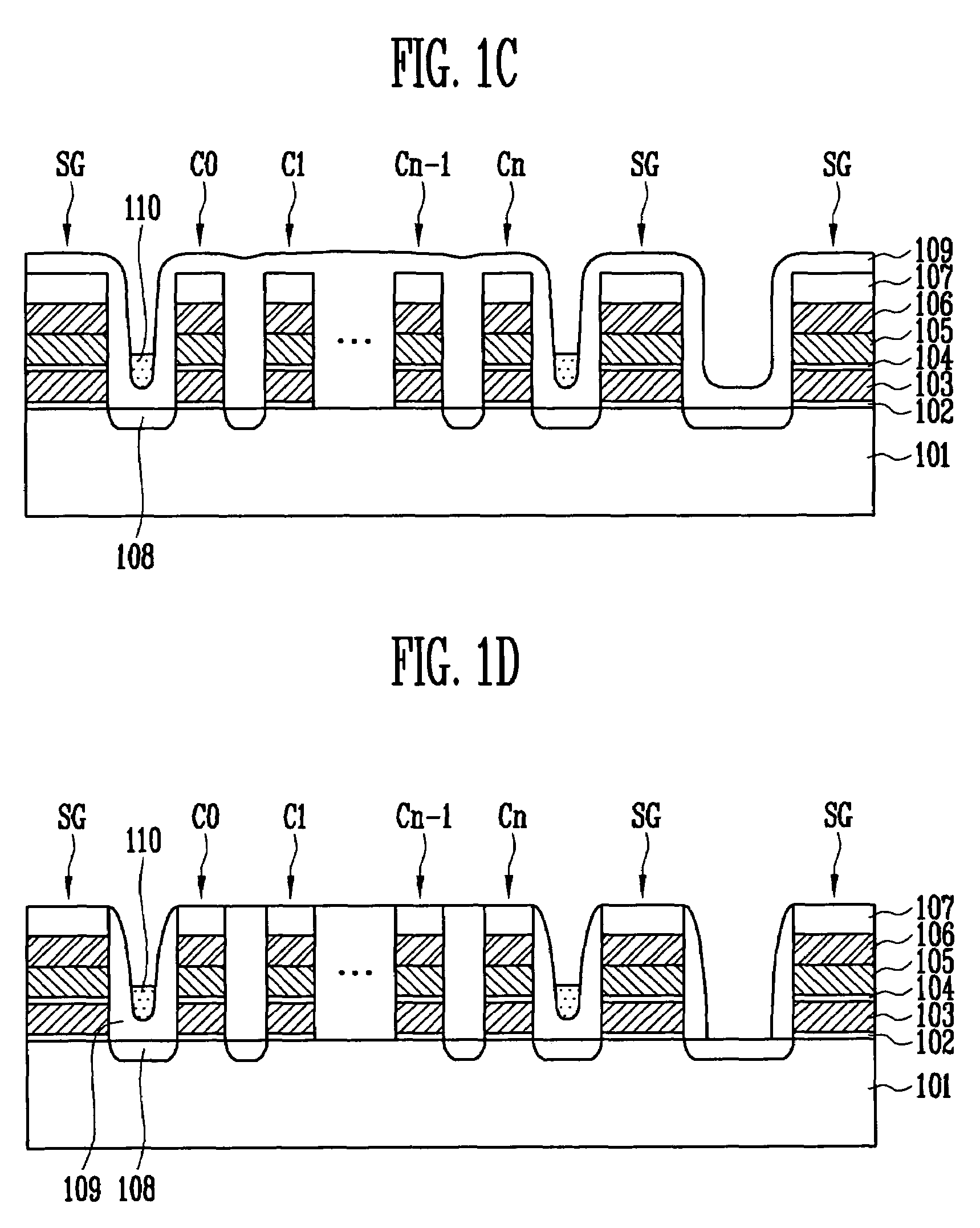

Semiconductor structure including a plurality of pairs of nonvolatile memory cells and an edge cell and method for the formation thereof

ActiveUS20170330889A1Well formedSolid-state devicesSemiconductor devicesSemiconductor structureEdge cell

A method includes providing a semiconductor structure having a gate structure arrangement provided over a substrate. The gate structure arrangement includes one or more first gate structures and has a first sidewall and a second sidewall on opposite sides of the gate structure arrangement. A second gate structure is formed including a first portion at the first sidewall, a second portion at the second sidewall and a third portion connecting the first and second portions. Each of the first, second and third portions of the second gate structure includes a first part over the gate structure arrangement and a second part over a portion of the substrate adjacent the gate structure arrangement. After the formation of the second gate structure, one or more sections of the second gate structure are removed, wherein the first and second portions of the second gate structure are separated from each other.

Owner:GLOBALFOUNDRIES US INC

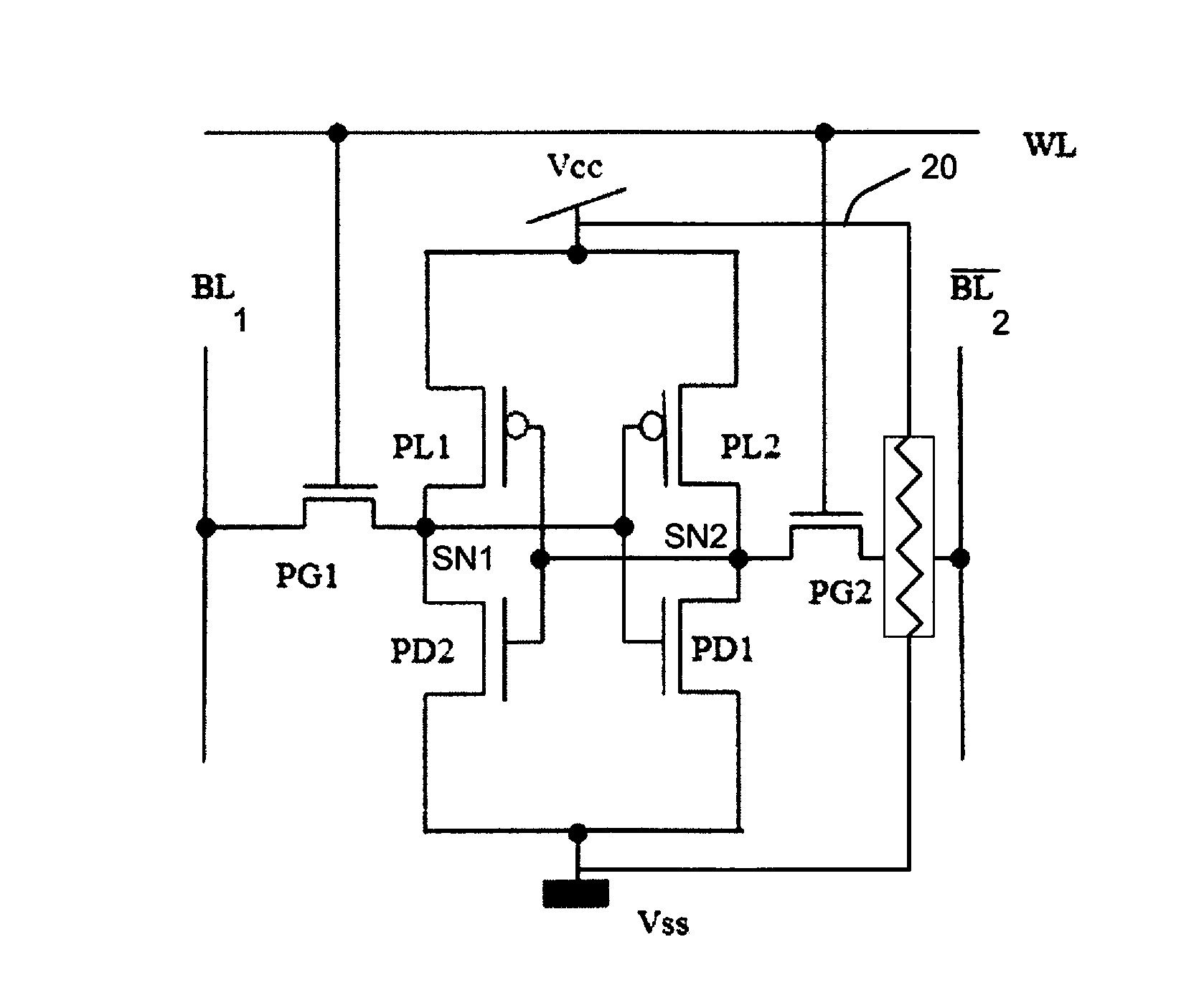

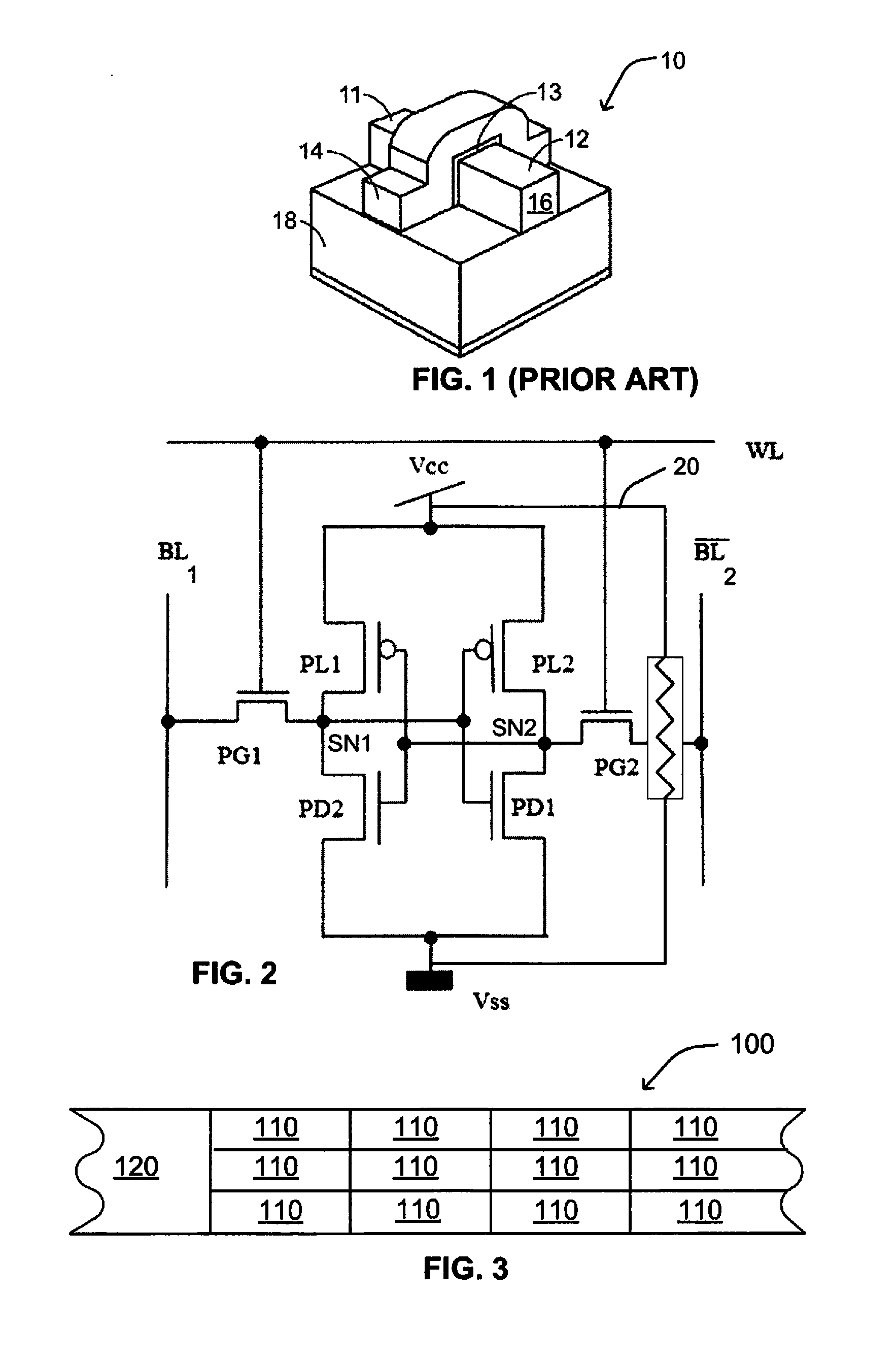

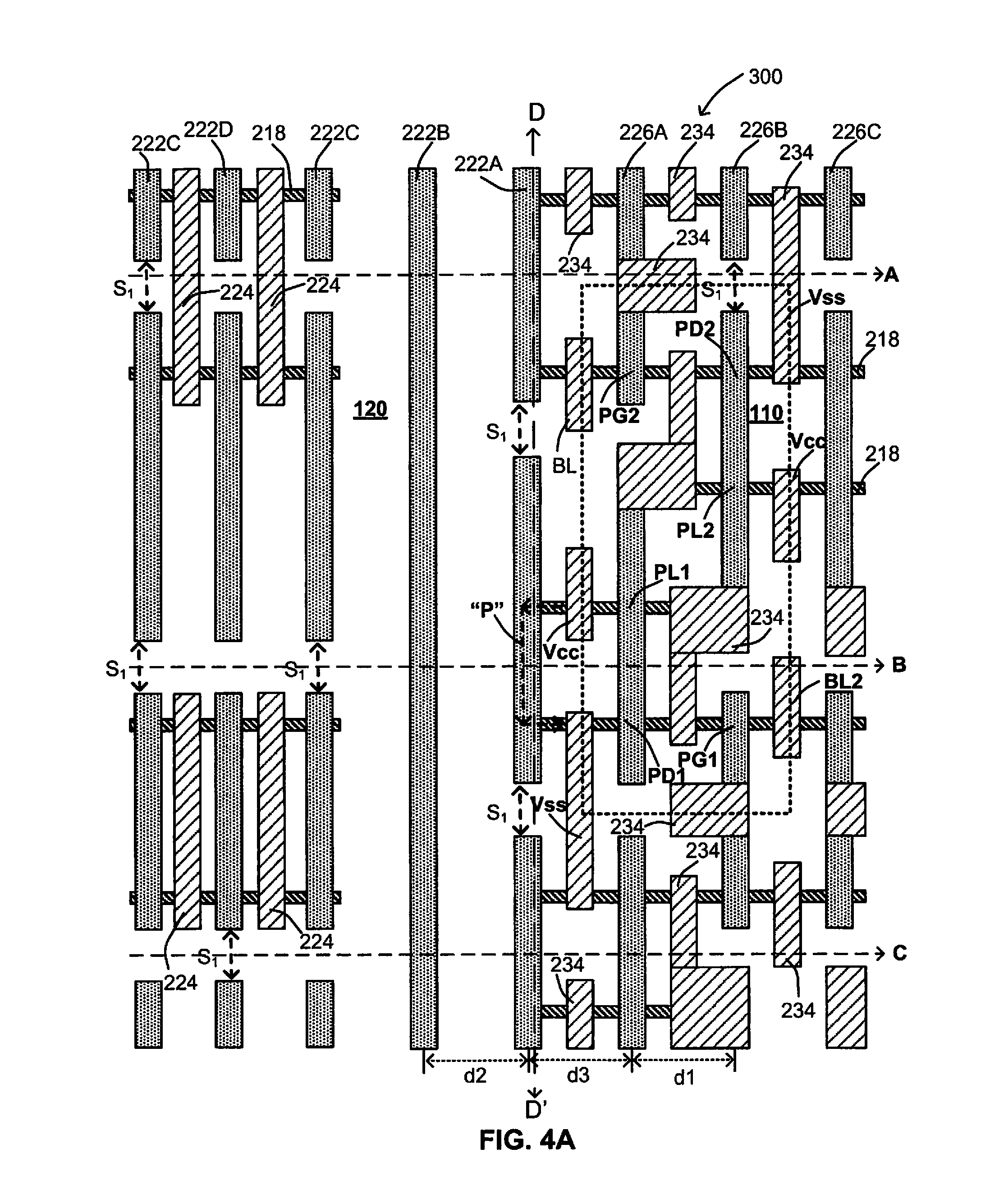

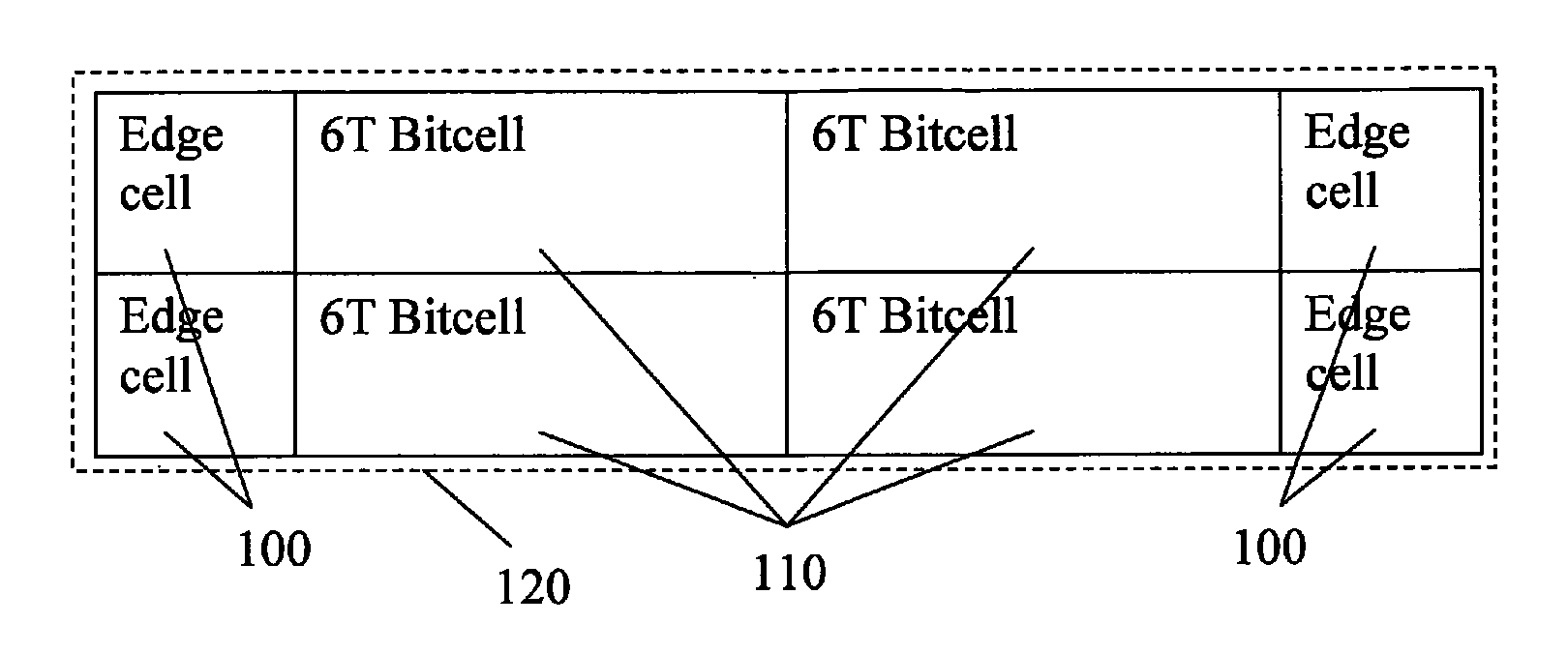

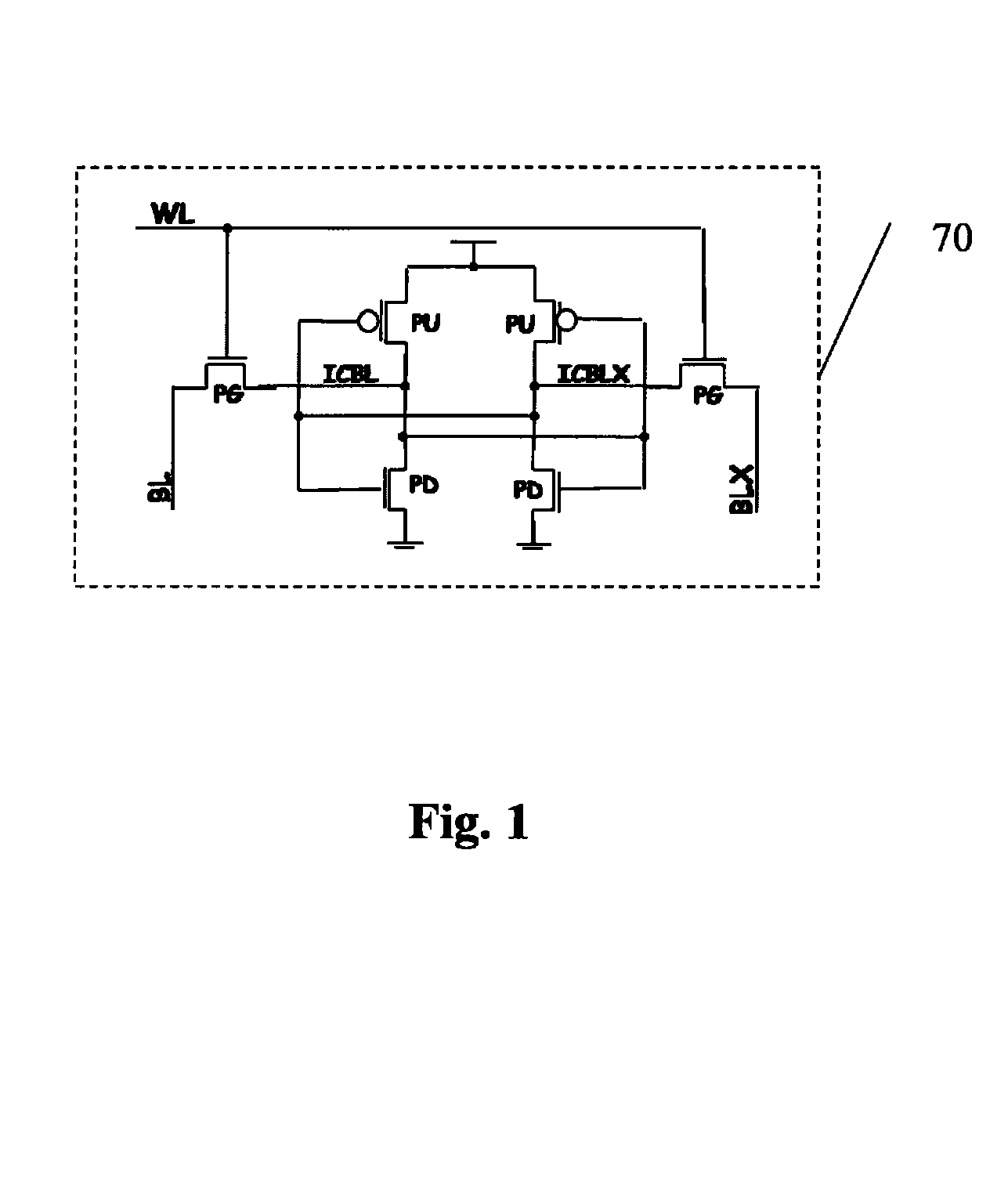

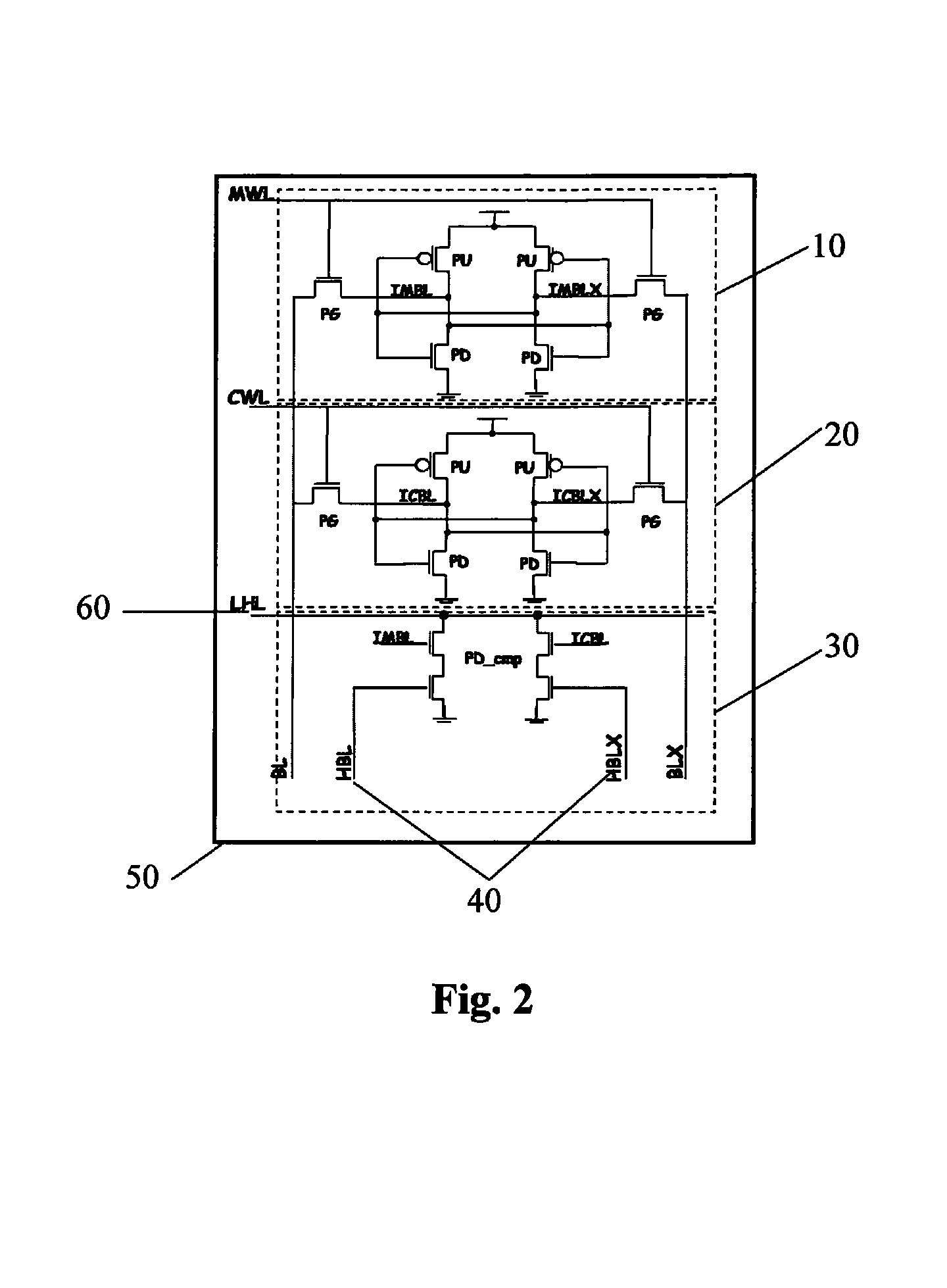

Pushed-rule bit cells with new functionality

ActiveUS8355269B1Reduce areaImprove performanceDigital storageInterconnectionTernary content addressable memory

A memory bit cell suitable for use in semiconductor integrated circuits that utilizes pushed design rules and layout geometries optimized by a semiconductor foundry for standard memory bit cells and edge-cell structures that provides a different functionality from that provided by the foundry standard bit cell. This different functionality is achieved by interconnecting the elements of one or a plurality of standard foundry bit cells and edge cells to implement a different circuit with different operation from the original bit cells and edge cells. The positioning and interconnection of the standard bit cells and edge cells are implemented in a manner so as to maintain the same periodic geometric proximity effects to the maximum degree possible. A preferred embodiment of this invention is to interconnect two standard foundry six-transistor SRAM bit cells and two edge cells to create a Ternary Content Addressable Memory bit cell with mask and compare functionality in addition to bit storage functionality.

Owner:SYNOPSYS INC

Multi-scale finite volume method for reservoir simulation

ActiveUS8594986B2Computation using non-denominational number representationDesign optimisation/simulationComputational scienceEdge cell

A multi-scale finite volume method for simulating a fine-scale geological model of subsurface reservoir is disclosed. The method includes providing a fine-scale geological model of a subsurface reservoir associated with a fine-scale grid, a coarse-scale grid, and a dual coarse-scale grid. A coarse-scale operator is constructed based on internal cells, edge cells, and node cells on the fine-scale grid that are defined by the dual coarse-scale grid. Pressure in the dual coarse-scale cells is computed using the coarse-scale operator. Pressure in the primary coarse-scale cells is computed using the computed pressure in the dual coarse-scale cells. A display is produced using the computed pressure in the primary coarse-scale cells. An iterative scheme can be applied such that the computed pressure in the primary coarse-scale cells converges to the fine-scale pressure solution and mass balance is maintained on the coarse-scale.

Owner:SCHLUMBERGER TECH CORP +1

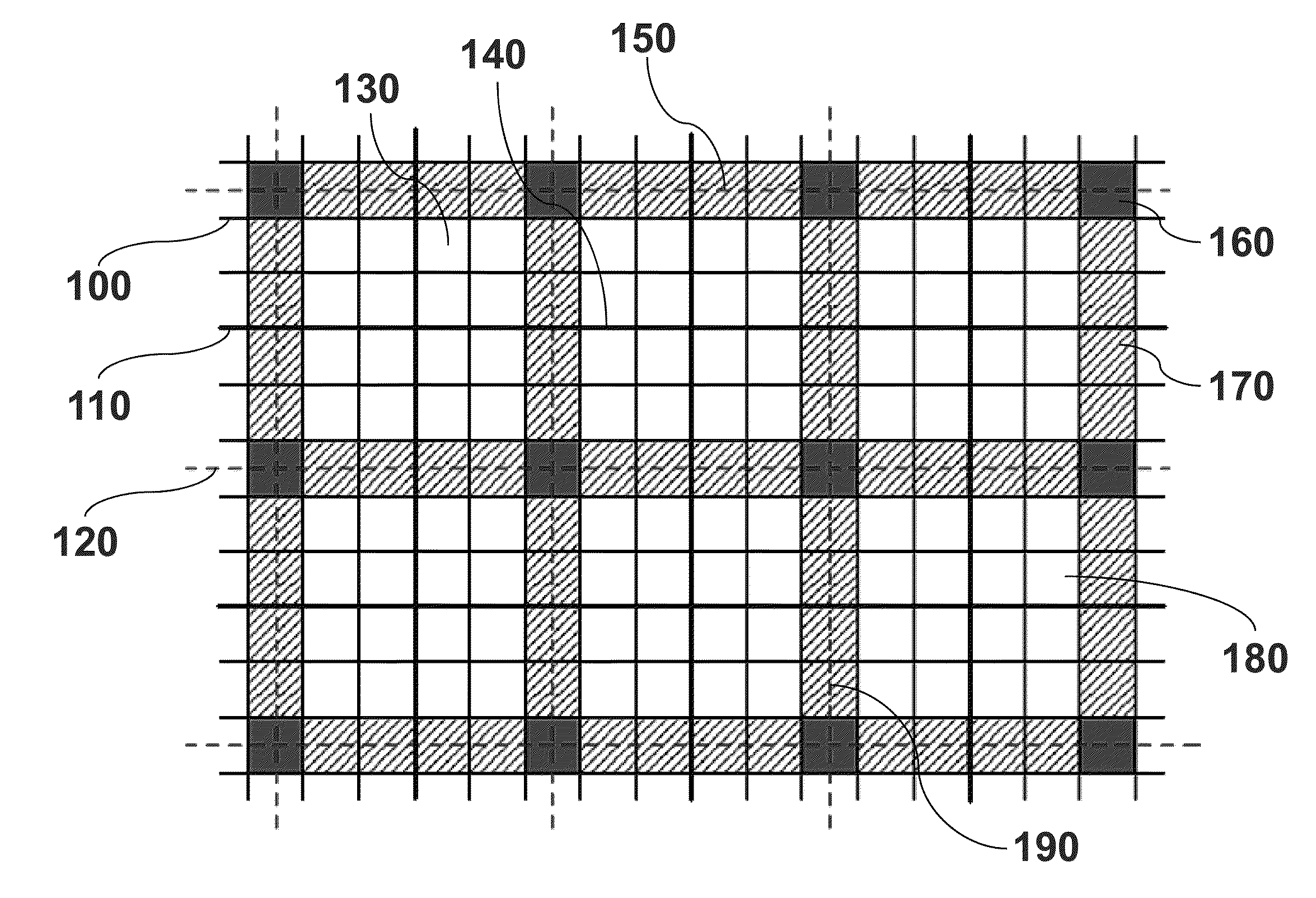

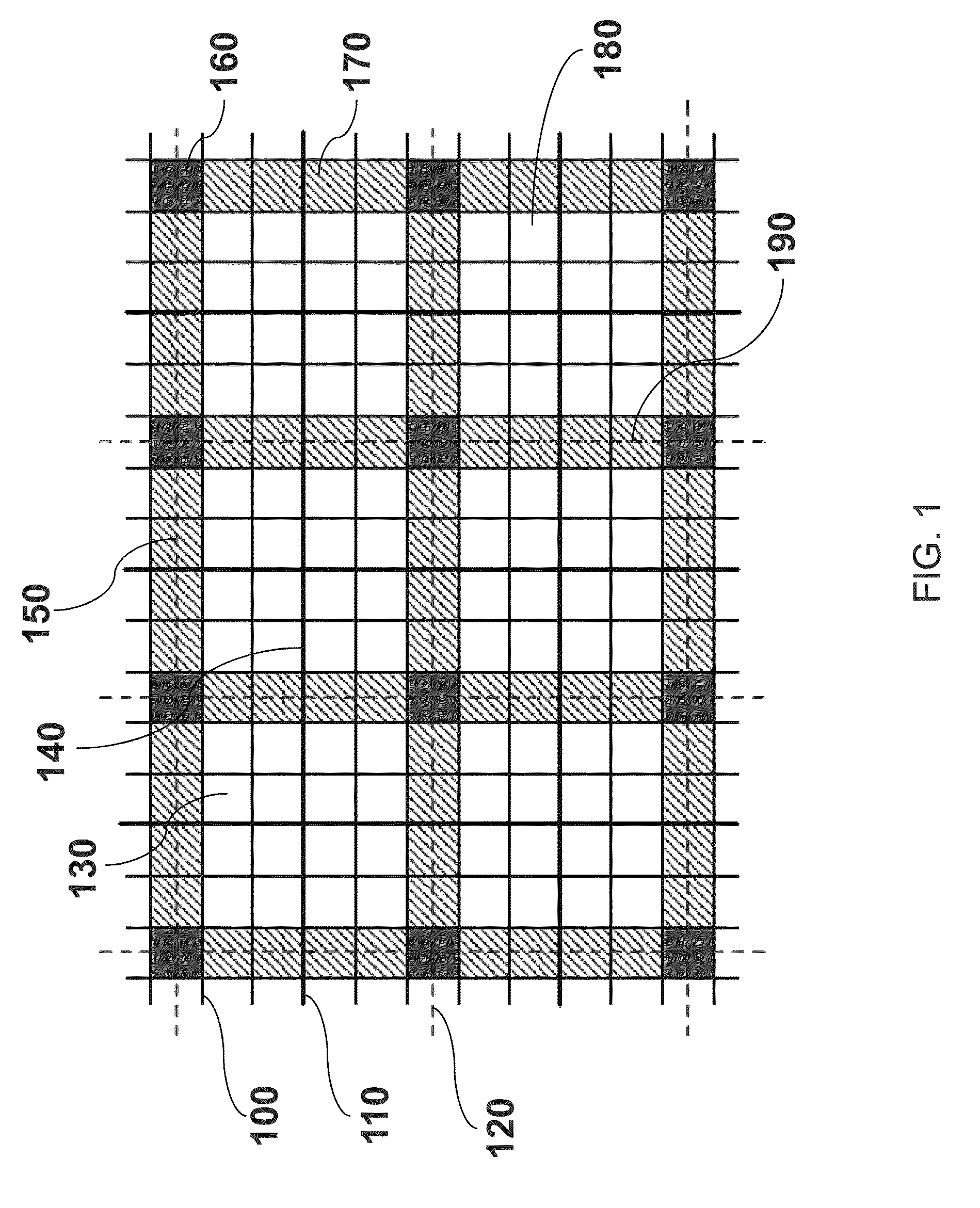

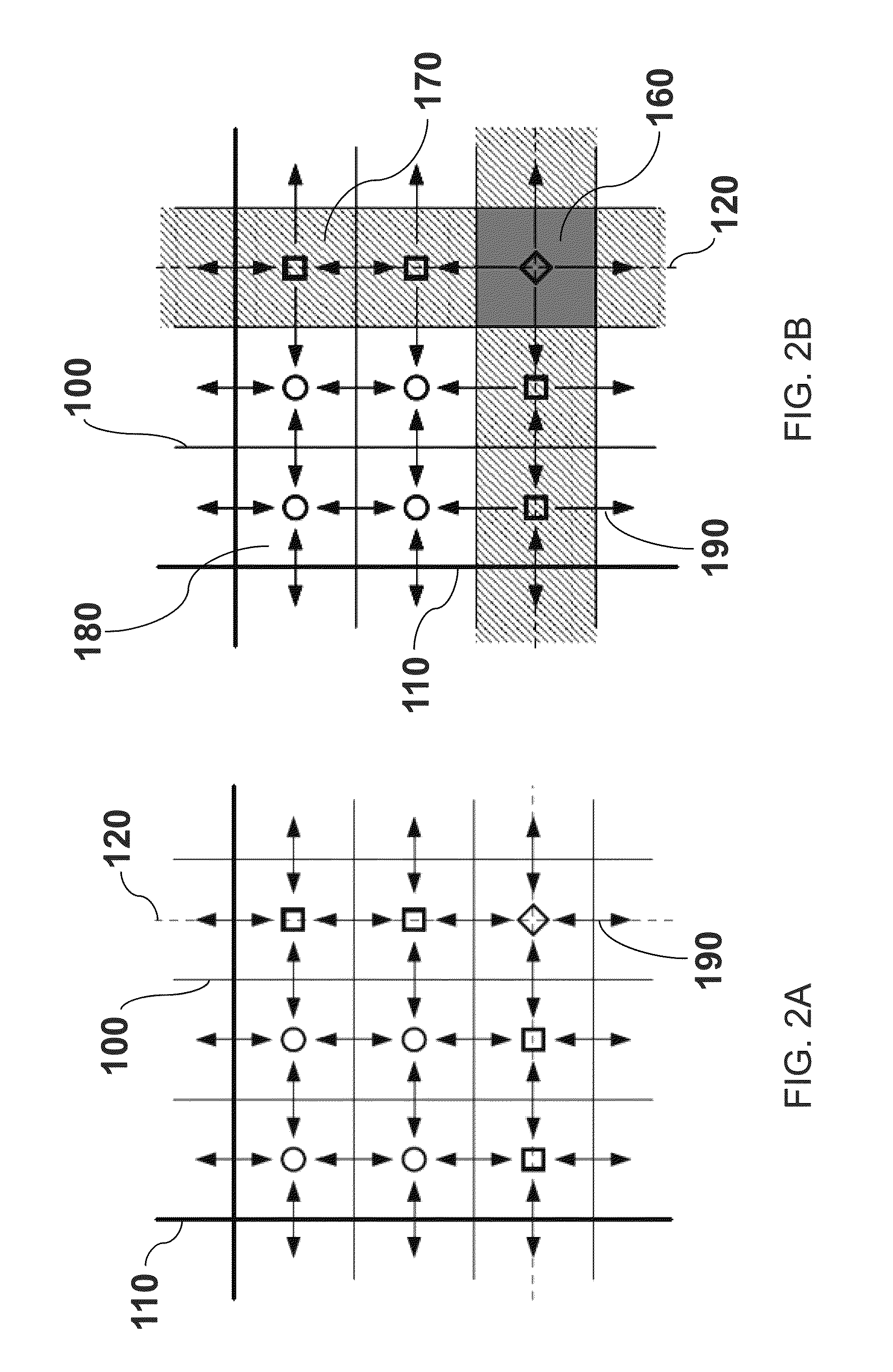

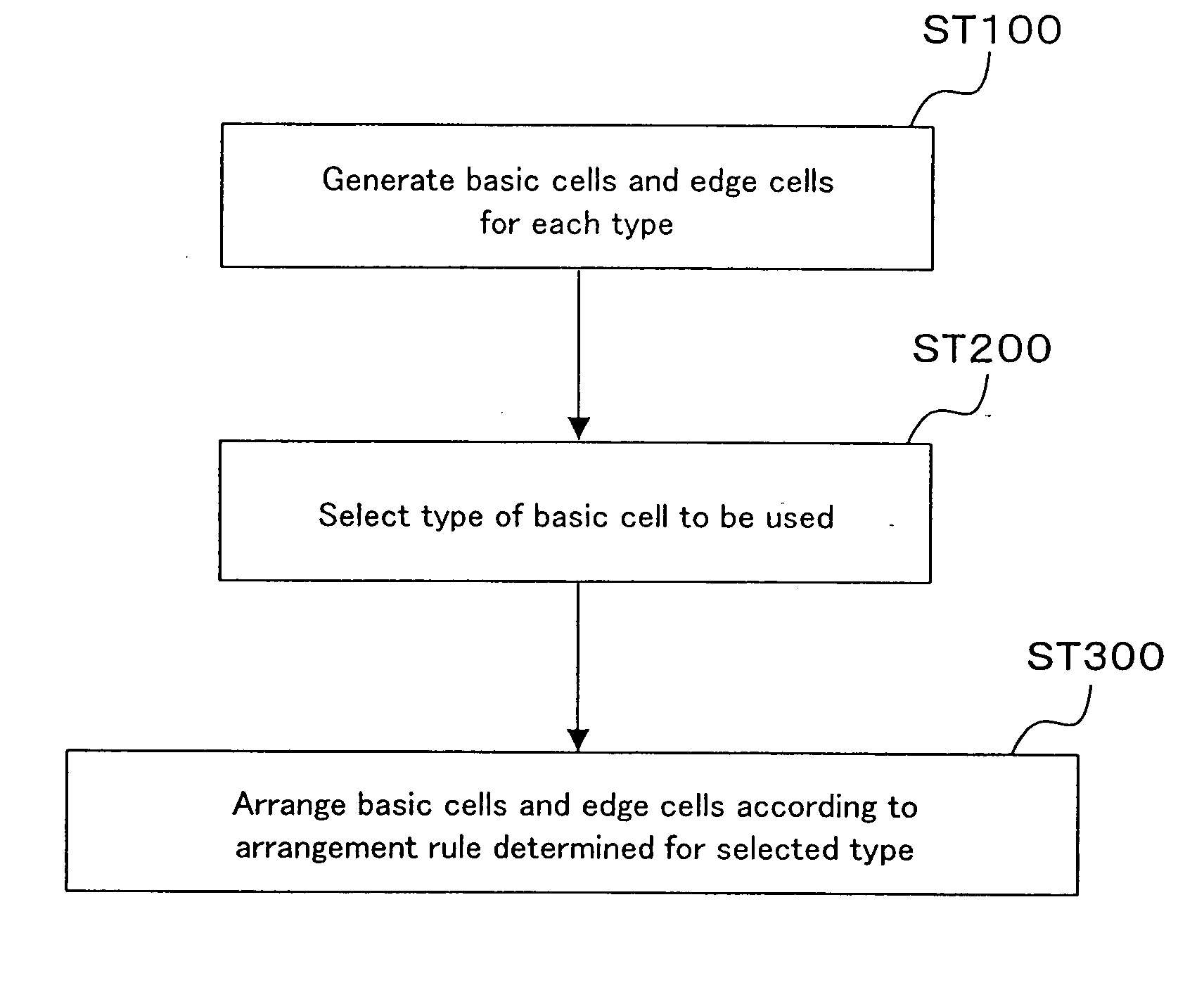

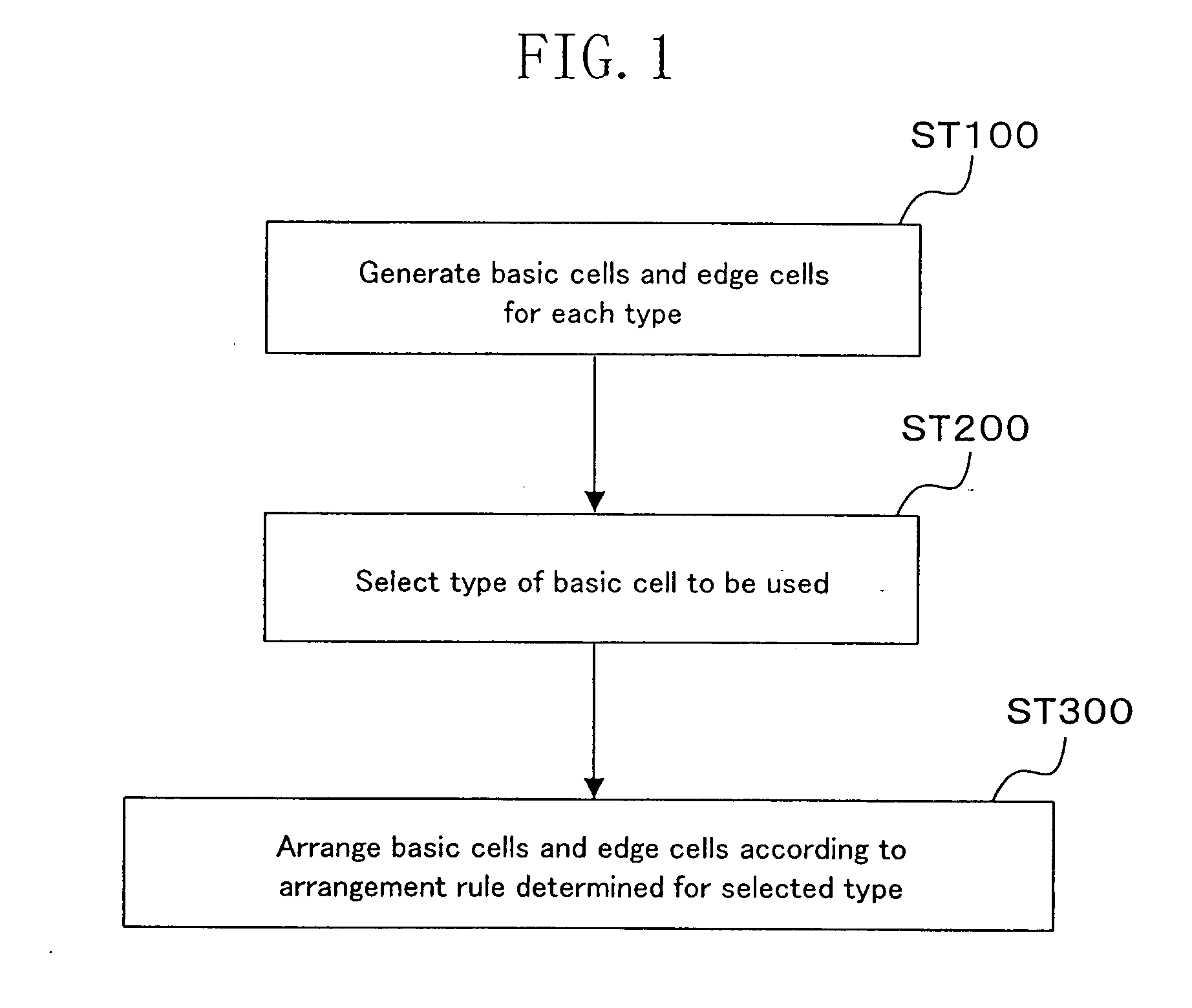

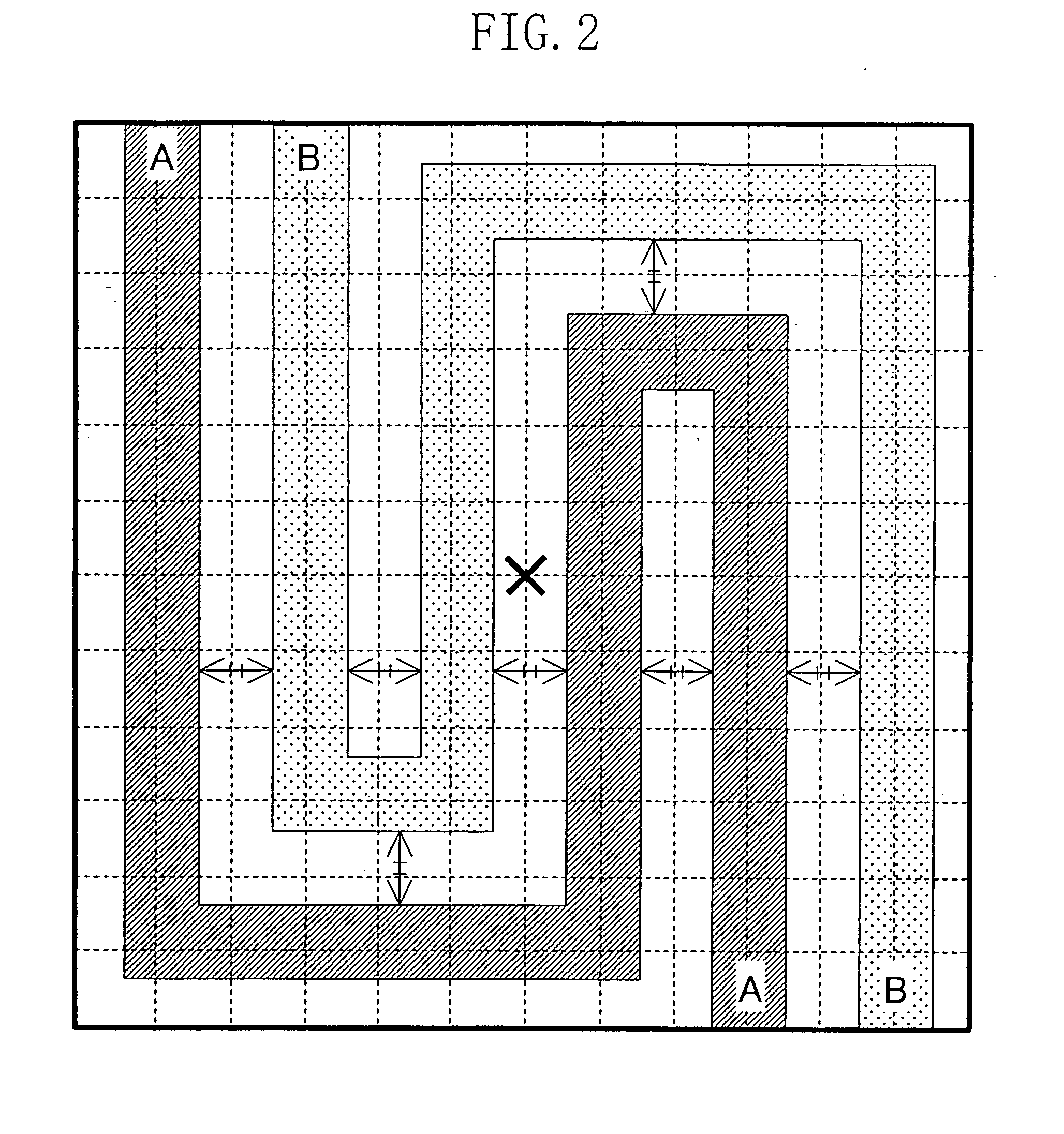

Basic cell, edge cell, wiring shape, wiring method, and shield wiring structure

ActiveUS20070162884A1Doubles processing time requiredIncrease the difficulty of the processSemiconductor/solid-state device detailsSolid-state devicesEdge cellElectrical and Electronics engineering

A basic cell of the present invention comprises a plurality of wires which constitute a wiring route of 90°, one ends of the plurality of wires being on one of opposite sides, and the other ends of the plurality of wires being on the other one of the opposite sides, wherein: each of the one ends of the plurality of wires is point-symmetric to any of the other ends of the plurality of wires with respect to the center of the area of the basic cell; and routes of the plurality of wires do not cross one another.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

Dummy gate technology to avoid shorting circuit

Semiconductor devices and method of manufacturing such semiconductor devices are provided for improved FinFET memory cells to avoid electric short often happened between metal contacts of a bit cell, where the meal contacts are positioned next to a dummy gate of a neighboring dummy edge cell. In one embodiment, during the patterning of a gate layer on a substrate surface, an improved gate slot pattern is used to extend the lengths of one or more gate slots adjacent bit lines so as to pattern and sectionalize a dummy gate line disposed next to metal contacts of an active memory cell. In another embodiment, during the patterning of gate lines, the distances between one or more dummy gates lines disposed adjacent an active memory cell are adjusted such that their locations within dummy edge cells are shifted in position to be away from metal contacts of the active memory cell.

Owner:UNITED MICROELECTRONICS CORP

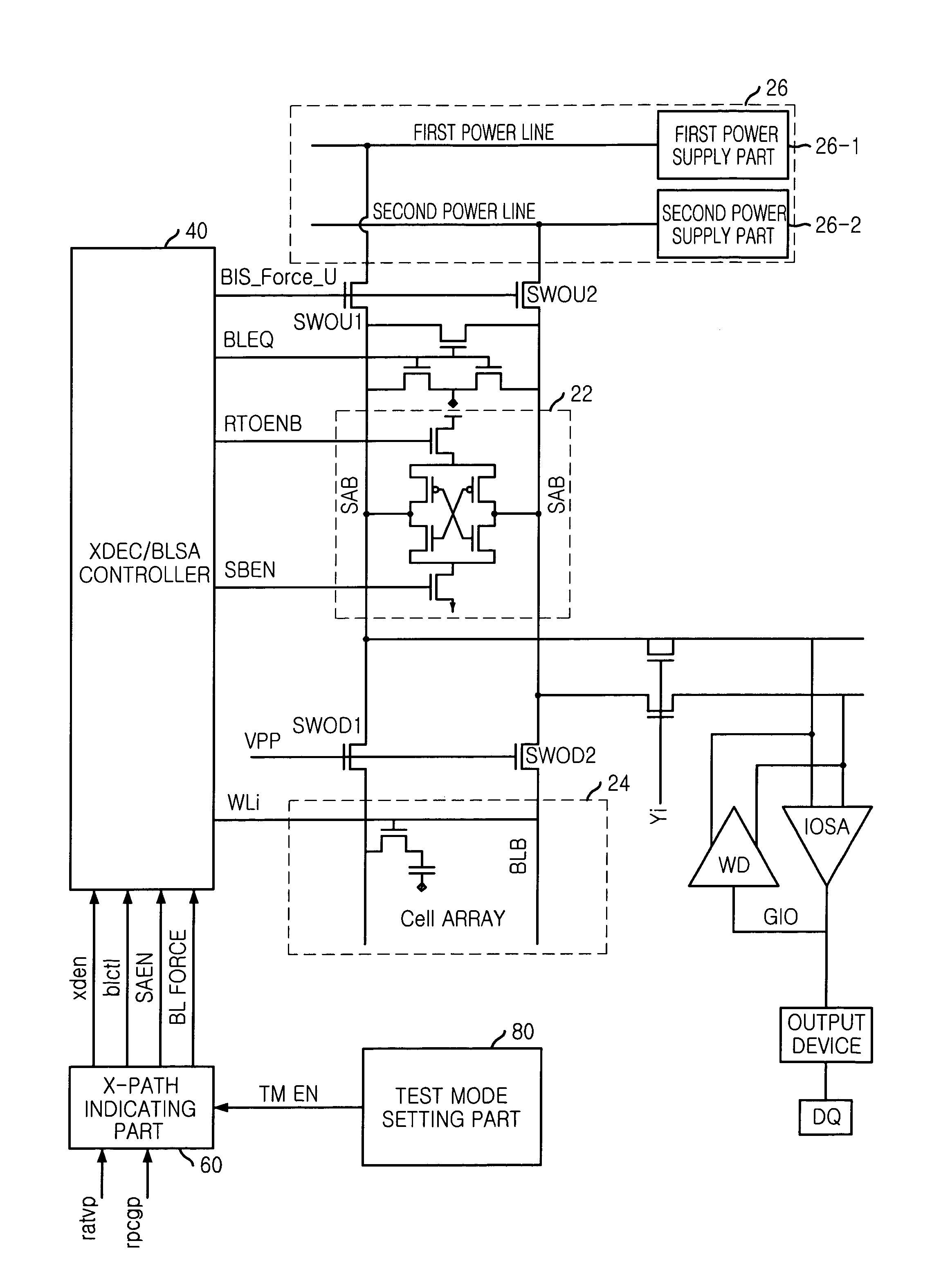

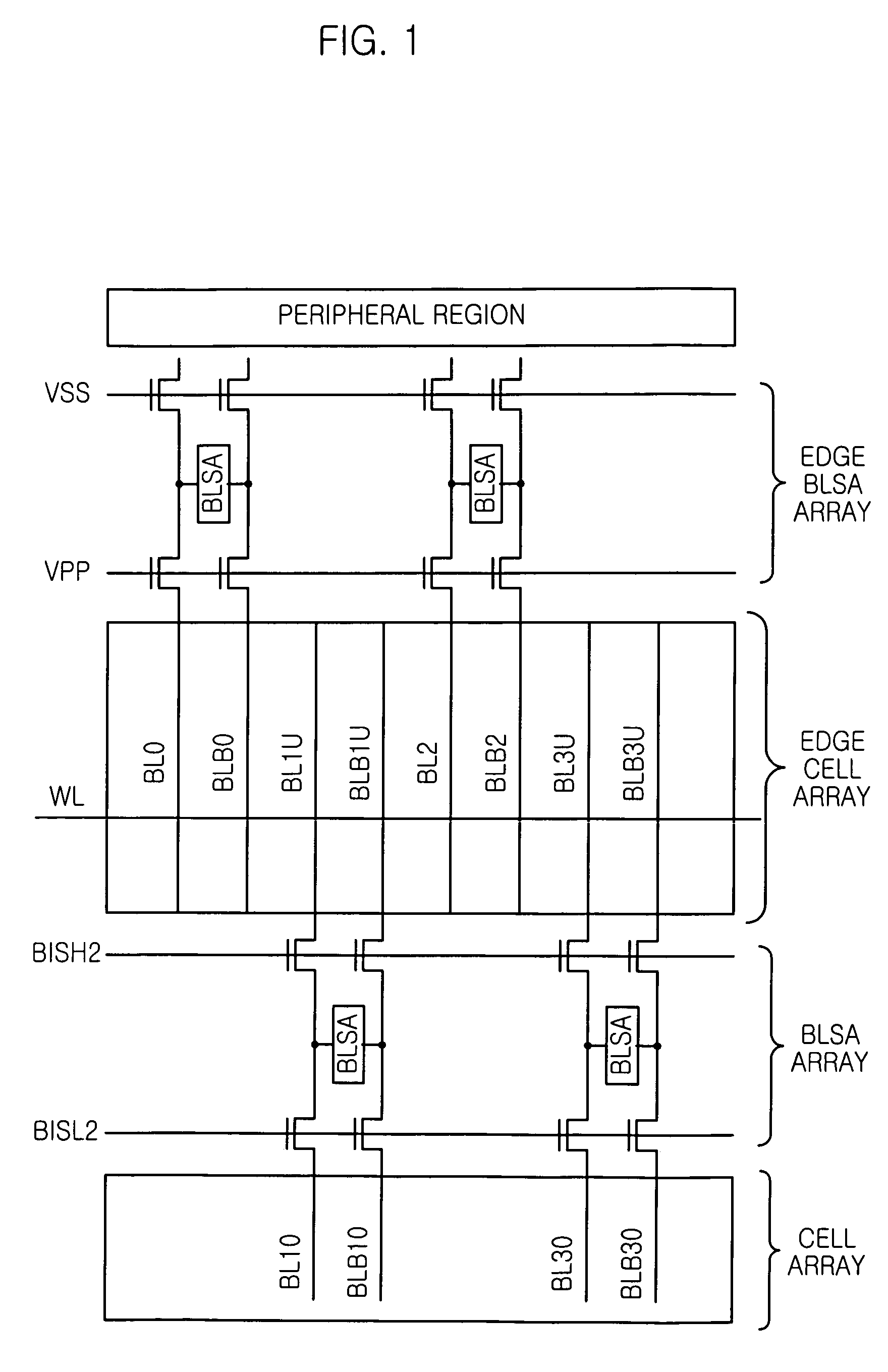

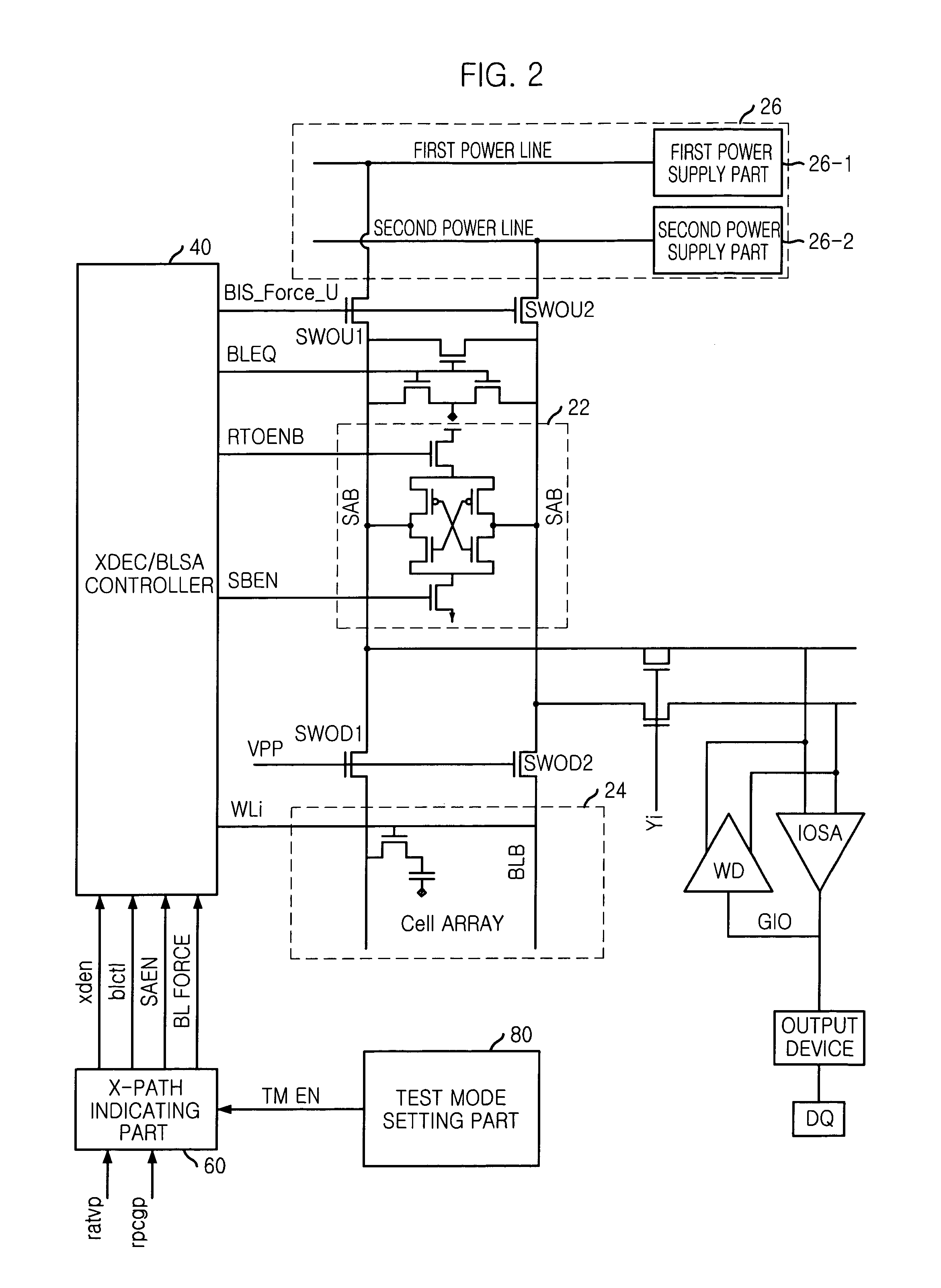

Bit line sense amplifier and semiconductor memory device having the same

There is provided a semiconductor memory device that can calculate an offset voltage of a bit line sense amplifier. The semiconductor memory device includes a cell array, an edge bit line sense amplifier for amplifying data of an edge cell array, and a power supply part for applying a predetermined voltage to the edge bit line sense amplifier. The power supply part includes a first power supply part for supplying a predetermined voltage to a bit line of the edge bit line sense amplifier and a second power supply part for supplying a predetermined voltage to a complementary bit line of the edge bit line sense amplifier.

Owner:SK HYNIX INC

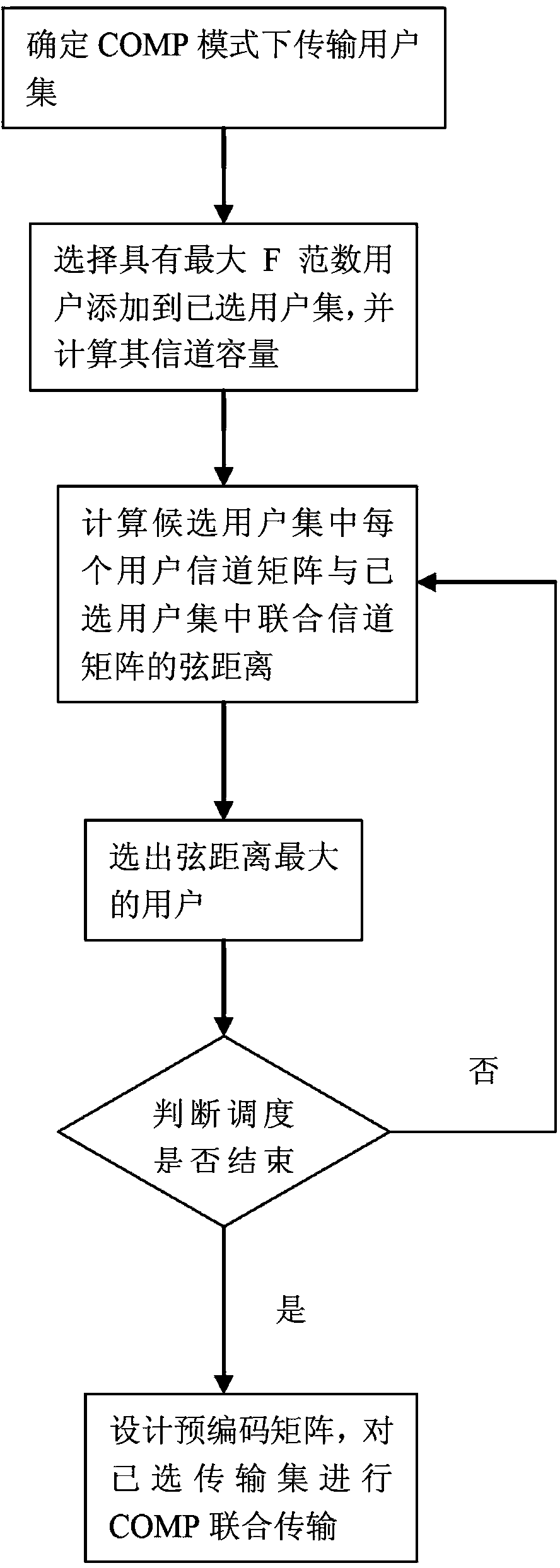

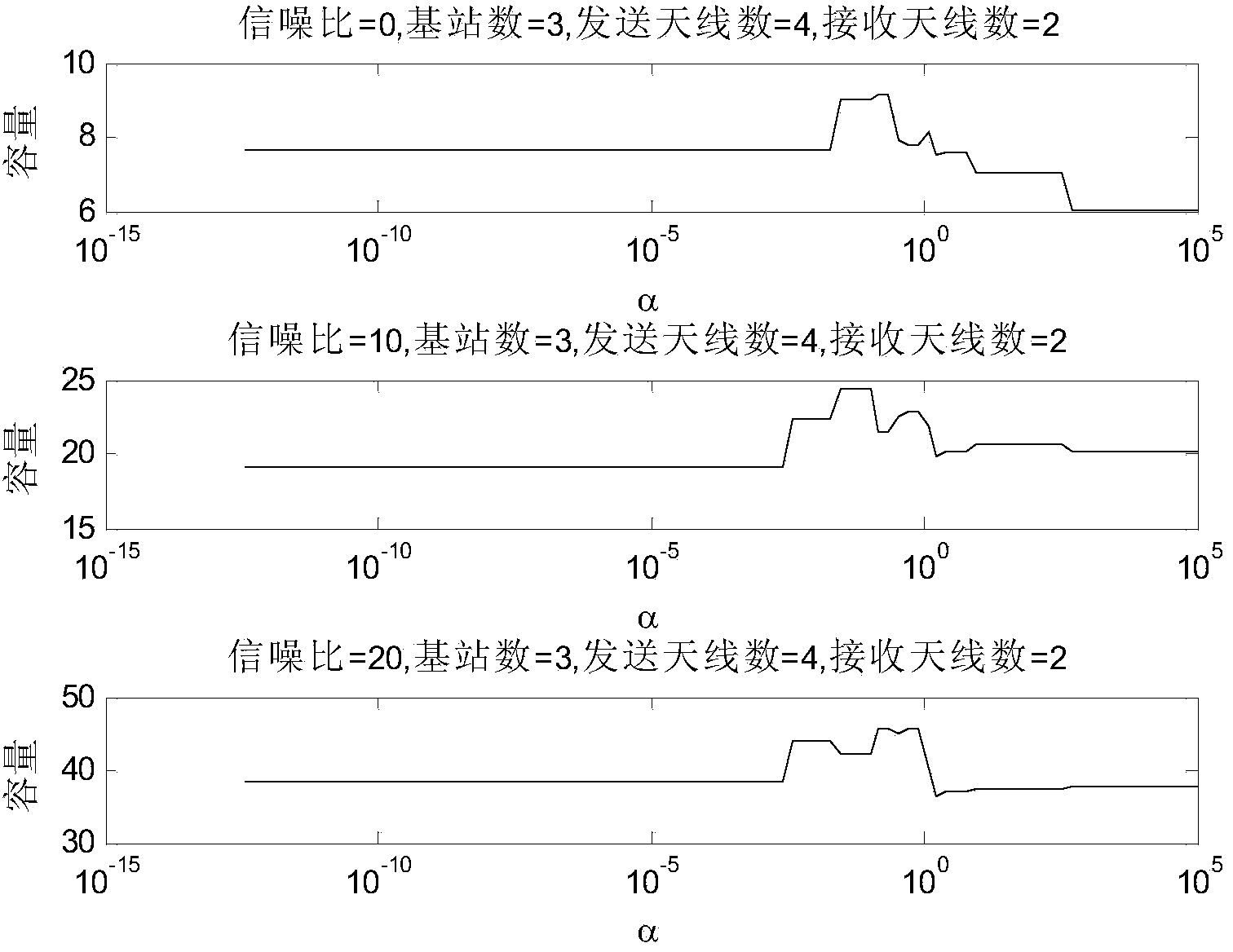

Downlink MU_COMP scheduling algorithm based on improved chordal distance

ActiveCN103402268AImprove service qualityReduce complexityWireless communicationChordal distanceAlgorithm

The invention discloses a downlink MU_COMP (Multi-User_Coordinated Multiple Point) scheduling algorithm based on an improved chordal distance, which comprises the following steps that S1, edge cell users detect the strength of a current interference signal and feed back current signal interference noise ratios, and an activated user set in a coordinated transmission mode is determined according to the signal interference noise ratios; S2, a candidate user set and a selected user set are established, wherein the candidate user set comprises users in the activated user set; one of the users with the maximum F norm in the candidate user set is added to the selected user set, and the channel capacity of the users in the selected user set is computed; S3, a chordal distance between each user channel matrix in the candidate user set and a combined channel matrix in the selected user set is computed; S4, the user with the maximum chordal distance between the user channel matrix and the combined channel matrix in the selected user set is selected; S5, whether the users in the selected user set reach an upper user limit is judged, if so, S2 is skipped to, and if not, S6 is skipped to; and S6, block diagonalization precoding matrixes are designed for the edge cell users in the selected user set respectively, and a coordination base station uses the block diagonalization precoding matrixes to perform combined precoding and sending on the edge cell users.

Owner:XIDIAN UNIV

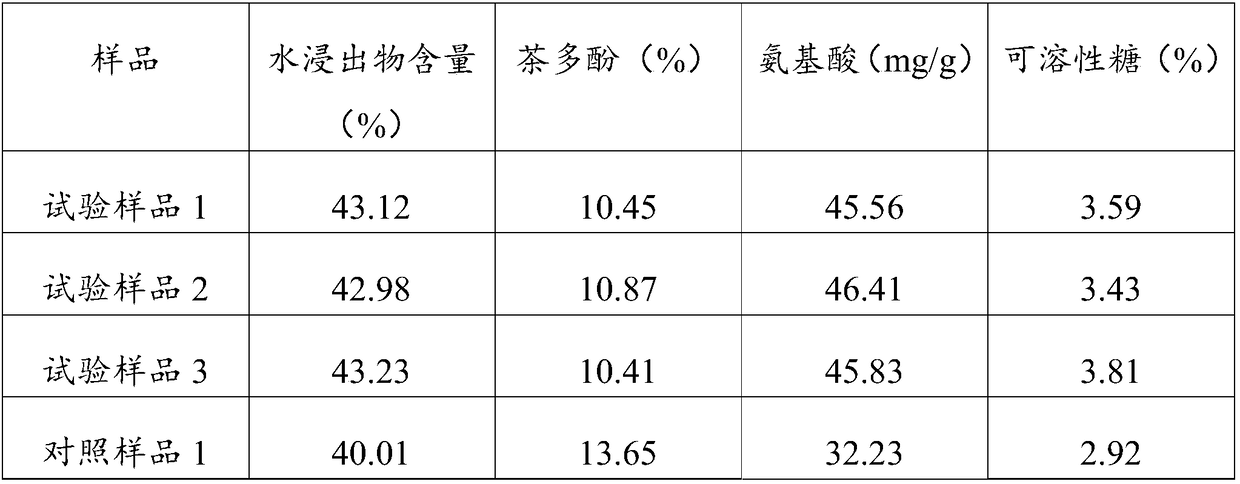

Preparation method of Xinyang white tea

The invention provides a preparation method of Xinyang white tea. The preparation method comprises the following steps of (1) picking fresh leaves; (2) performing withering for the first time; (3) performing rocking of green leaves for the first time; (4) performing withering for the second time; (5) performing rolling for the first time; (6) performing rocking of green leaves for the second time;(7) performing rolling for the second time; (8) performing baking for the first time; (9) performing choosing and rejecting; and (10) performing baking for the second time. According to the preparation method disclosed by the invention, the withering time is prolonged, so that substances contained in tea leaves generate sufficient physical and chemical changes; through rocking of green leaves twice, edge cells of the fresh leaves are appropriately destructed, the fragrance and the taste of the made tea leaves are improved, and enzymes in the tea leaves catalyze fragrance precursor substancesto be transformed and formed into unique fragrance; through rocking of green leaves for the first time, the activity of enzymes in the tea leaves can be improved, the hydrolysis and the transformationof soluble substances of amino acids, carbohydrate and the like are facilitated, the fresh and brisk degree of the tea leaves is increased, and the taste of the tea leaves is better; and through rocking of green leaves for the second time, transformation of fragrance substances is promoted, and fragrance is further promoted.

Owner:XINYANG AGRI & FORESTRY UNIV

Semiconductor structure including a plurality of pairs of nonvolatile memory cells and an edge cell and method for the formation thereof

Owner:GLOBALFOUNDRIES U S INC

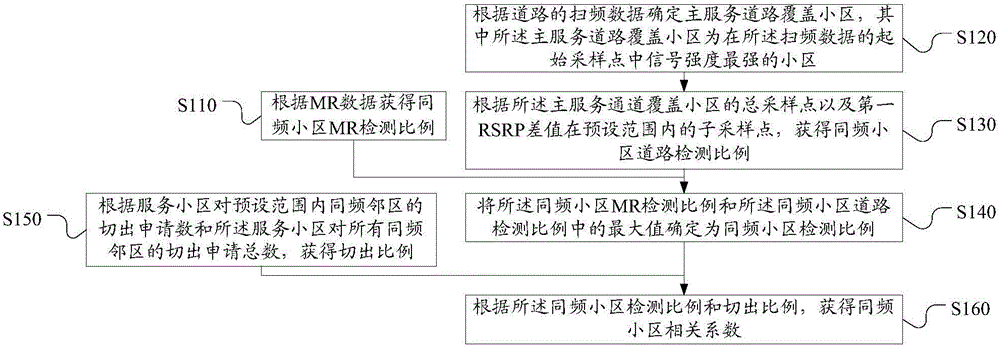

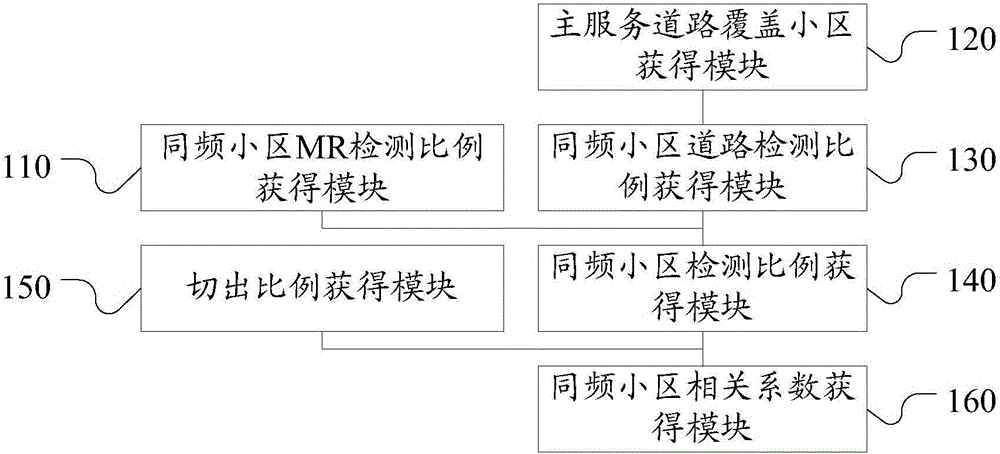

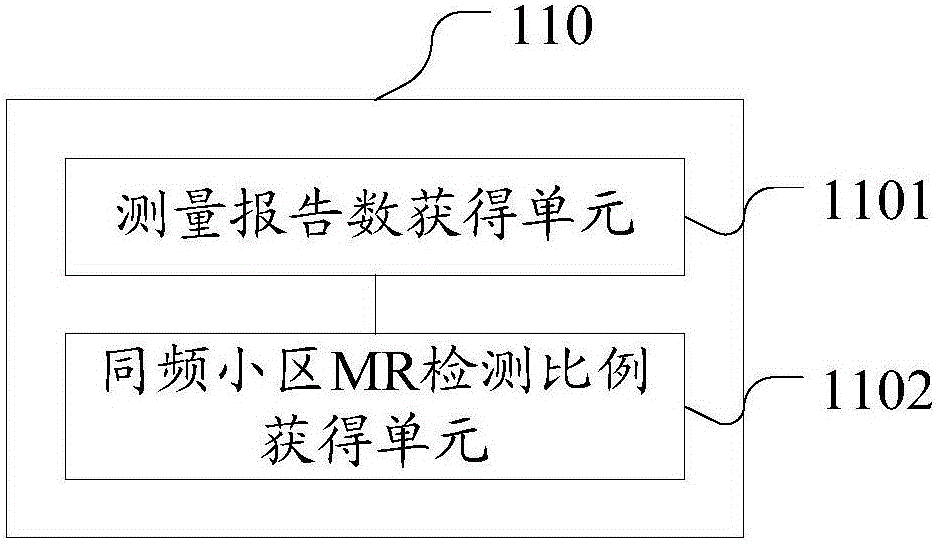

Same-frequency cell correlated coefficient acquisition method based on LTE (Long Term Evolution) network and same-frequency cell correlated coefficient acquisition device based on LTE network

The invention relates to a same-frequency cell correlated coefficient acquisition method based on an LTE (Long Term Evolution) network and a same-frequency cell correlated coefficient acquisition device based on an LTE network. The method comprises the following steps of: acquiring a same-frequency cell MR detection ratio according to MR data; according to frequency scanning data of a road, determining a main service road coverage cell; according to a general sampling point of the main service road coverage cell and a sub-sampling point of a first RSRP (Reference Signal Received Power) difference value in a pre-set range, acquiring a same-frequency cell road detection ratio; determining a maximum value in the same-frequency cell MR detection ratio and the same-frequency cell road detection ratio as a same-frequency cell detection ratio; according to the cutting-out application quantity of a same-frequency adjacent region in the pre-set range of a service cell and a cutting-out application total quantity of all same-frequency adjacent regions of the service cell, acquiring a cutting-out ratio; and according to the same-frequency cell detection ratio and the cutting-out ratio, acquiring a same-frequency cell correlated coefficient. An MR lacked quantity can be made up and the correlation of a road cell is accurately reflected; the relation of edge cells is accurately represented.

Owner:GUANGDONG HAIGE ICREATE TECHNOLOGY CO LTD

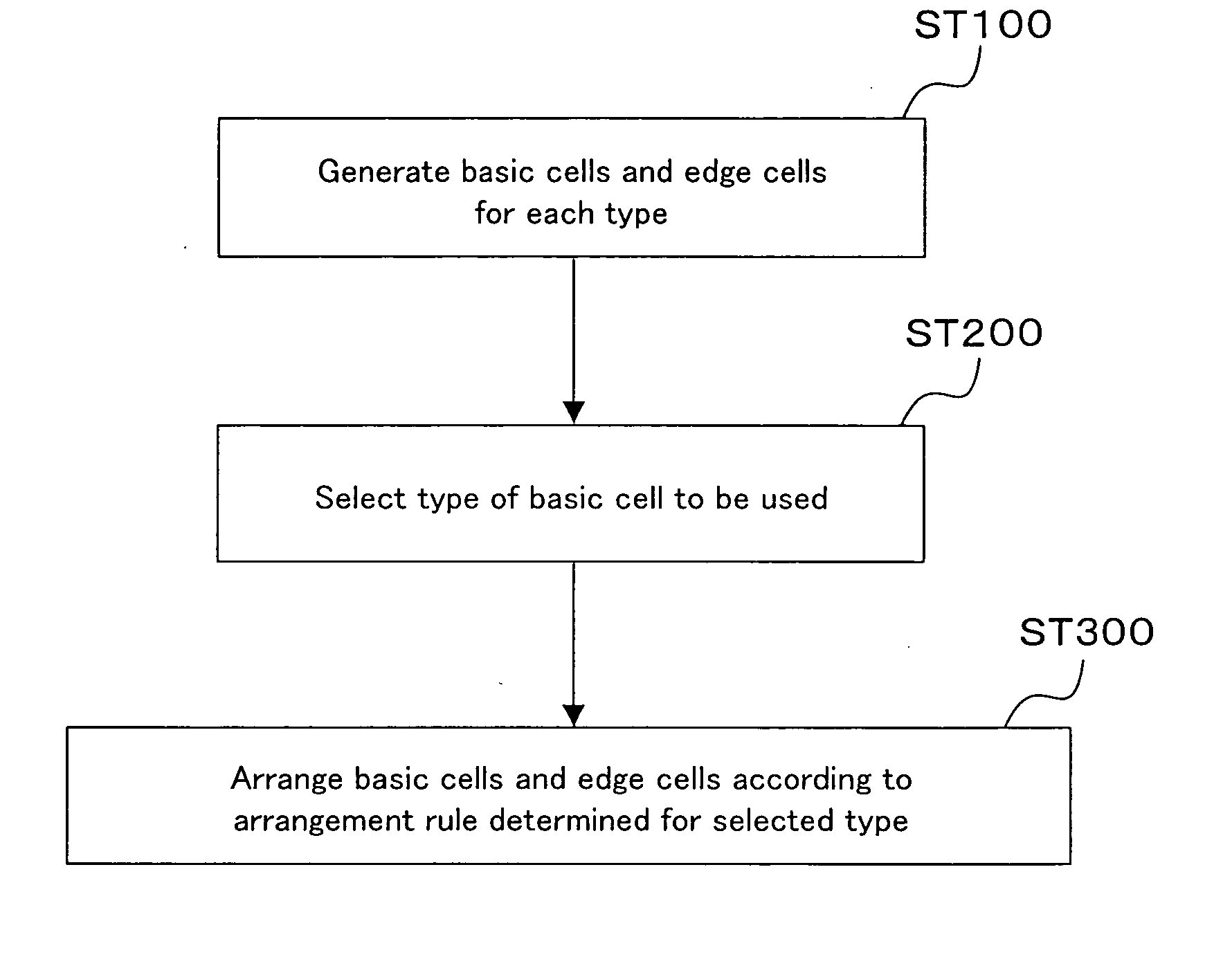

Basic cell, edge cell, wiring shape, wiring method, and shield wiring structure

ActiveUS20050050507A1Reduce regularityDoubles processing time requiredSemiconductor/solid-state device detailsSolid-state devicesEngineeringEdge cell

A basic cell of the present invention comprises a plurality of wires which constitute a wiring route of 90°, one ends of the wires being on one of opposite sides, and the other ends of the wires being on the other one of the opposite sides, wherein: each of the one ends of the wires is point-symmetric to any of the other ends of the wires with respect to the center of the area of the basic cell; and routes of the plurality of wires do not cross one another.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

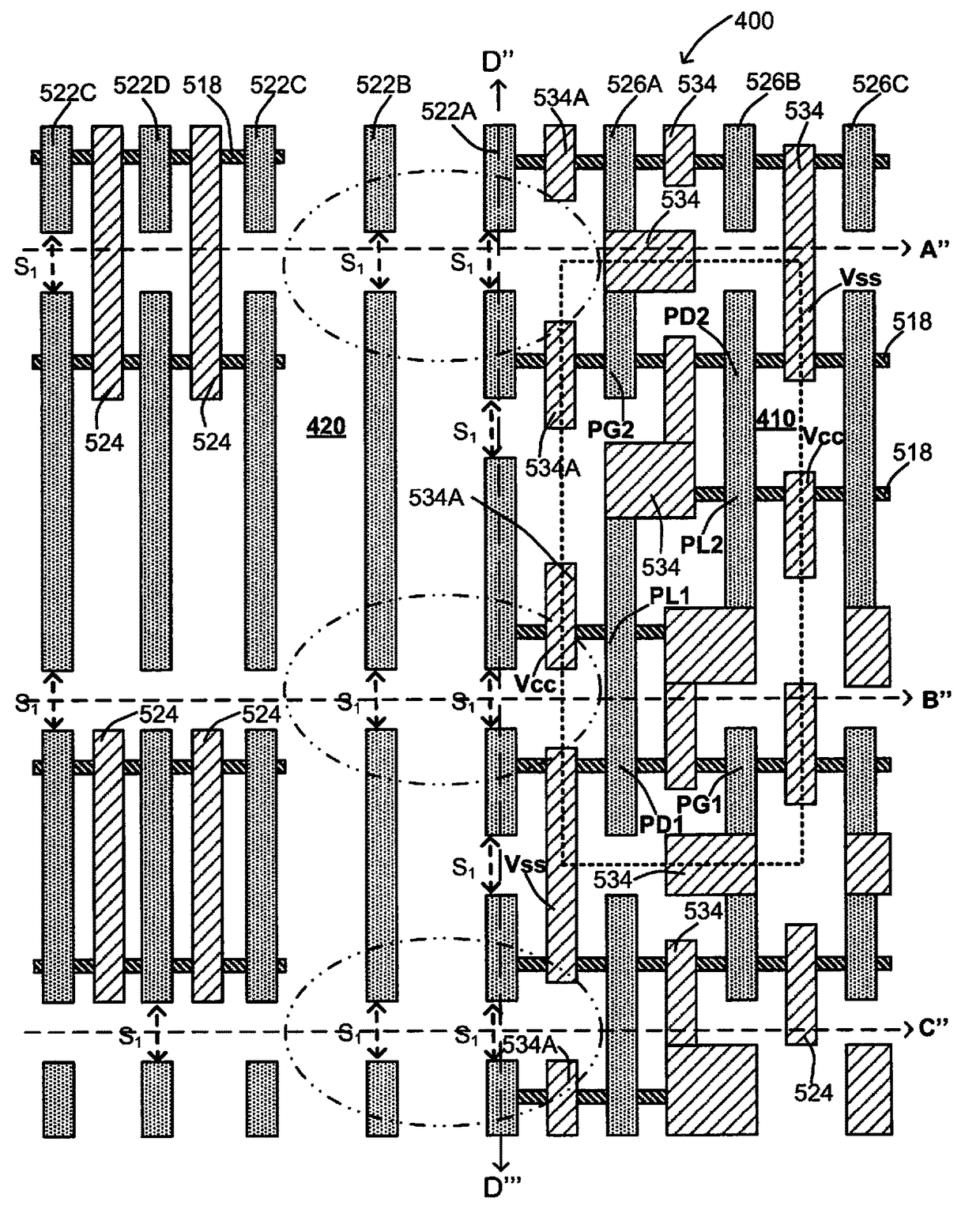

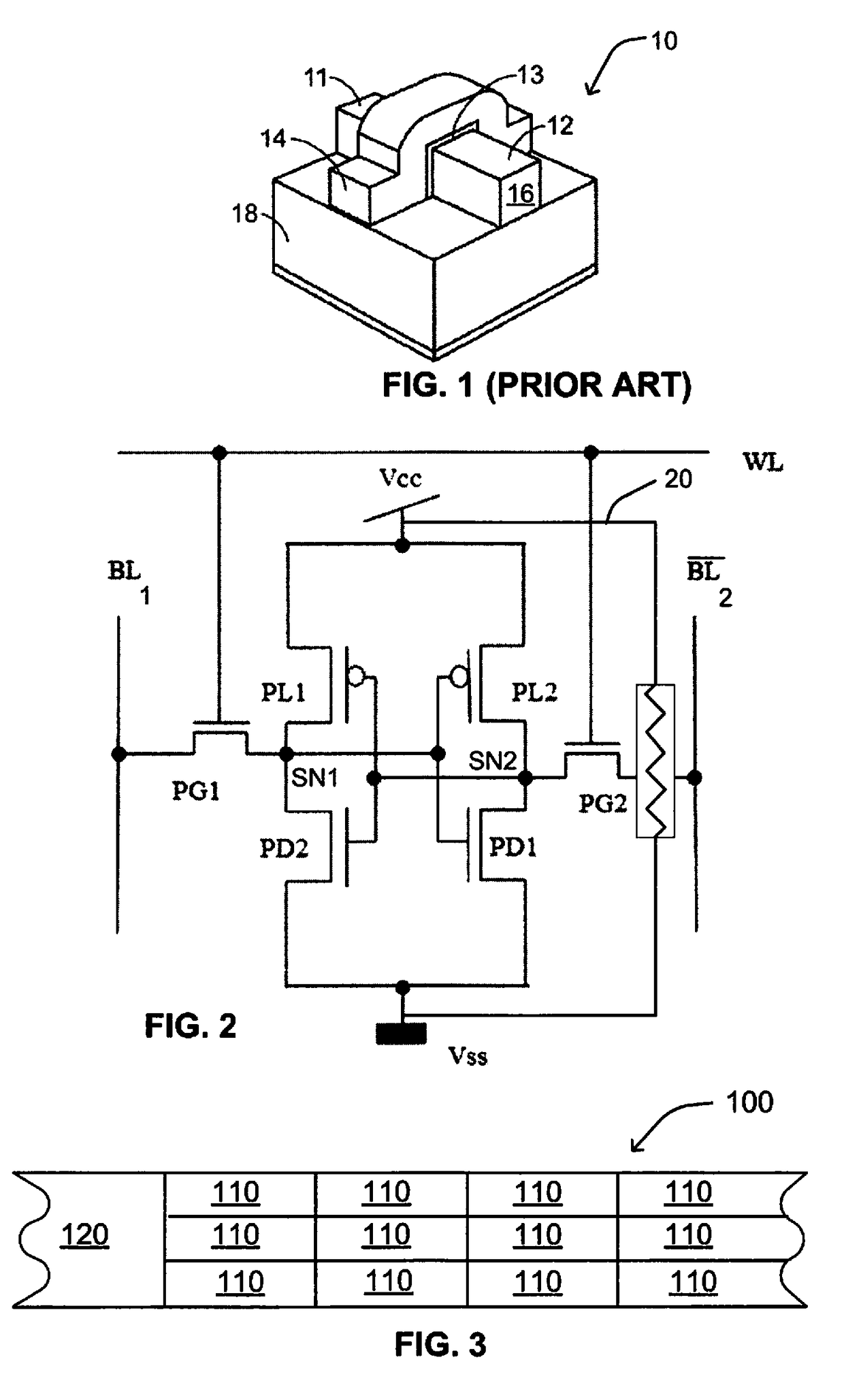

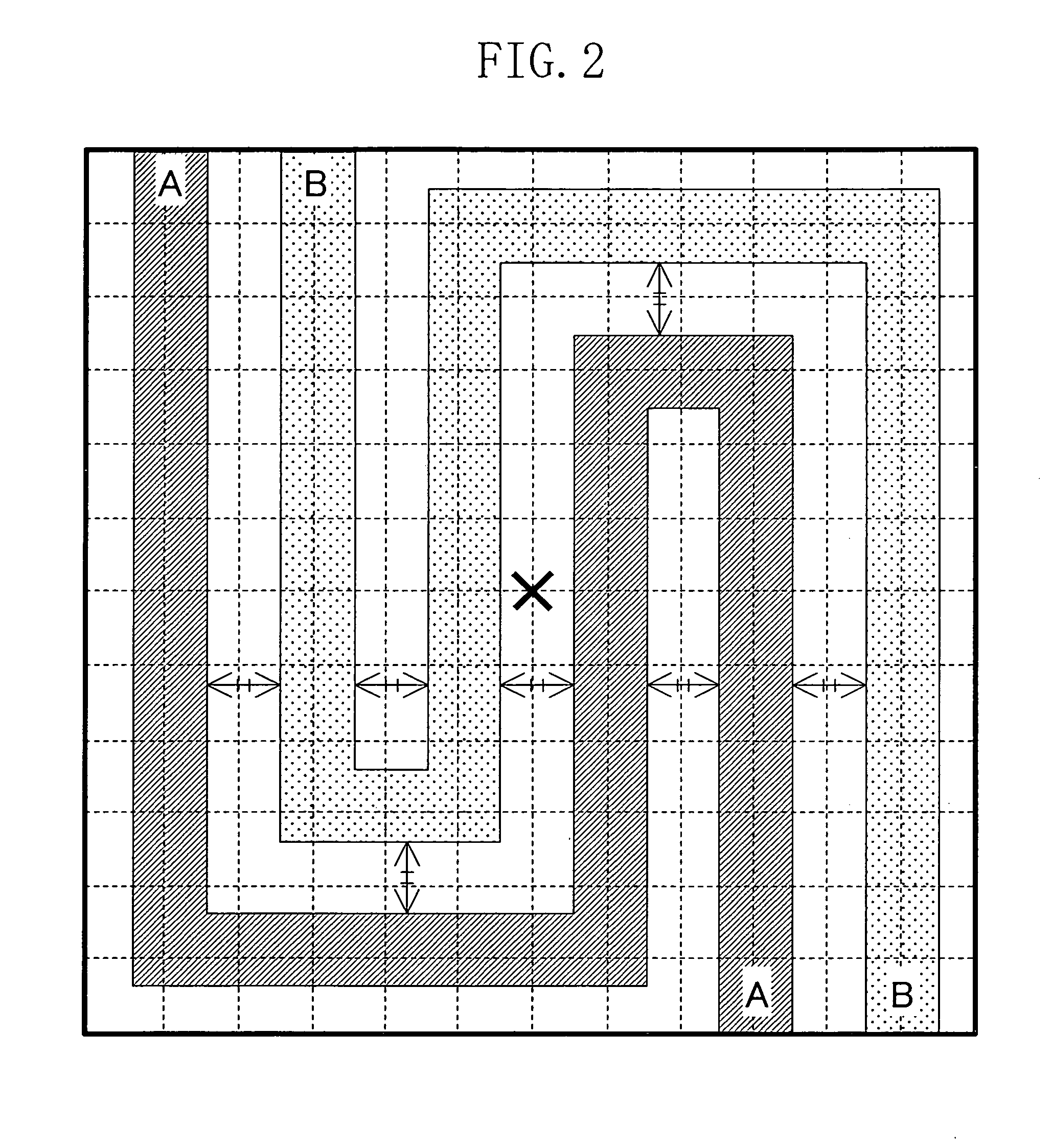

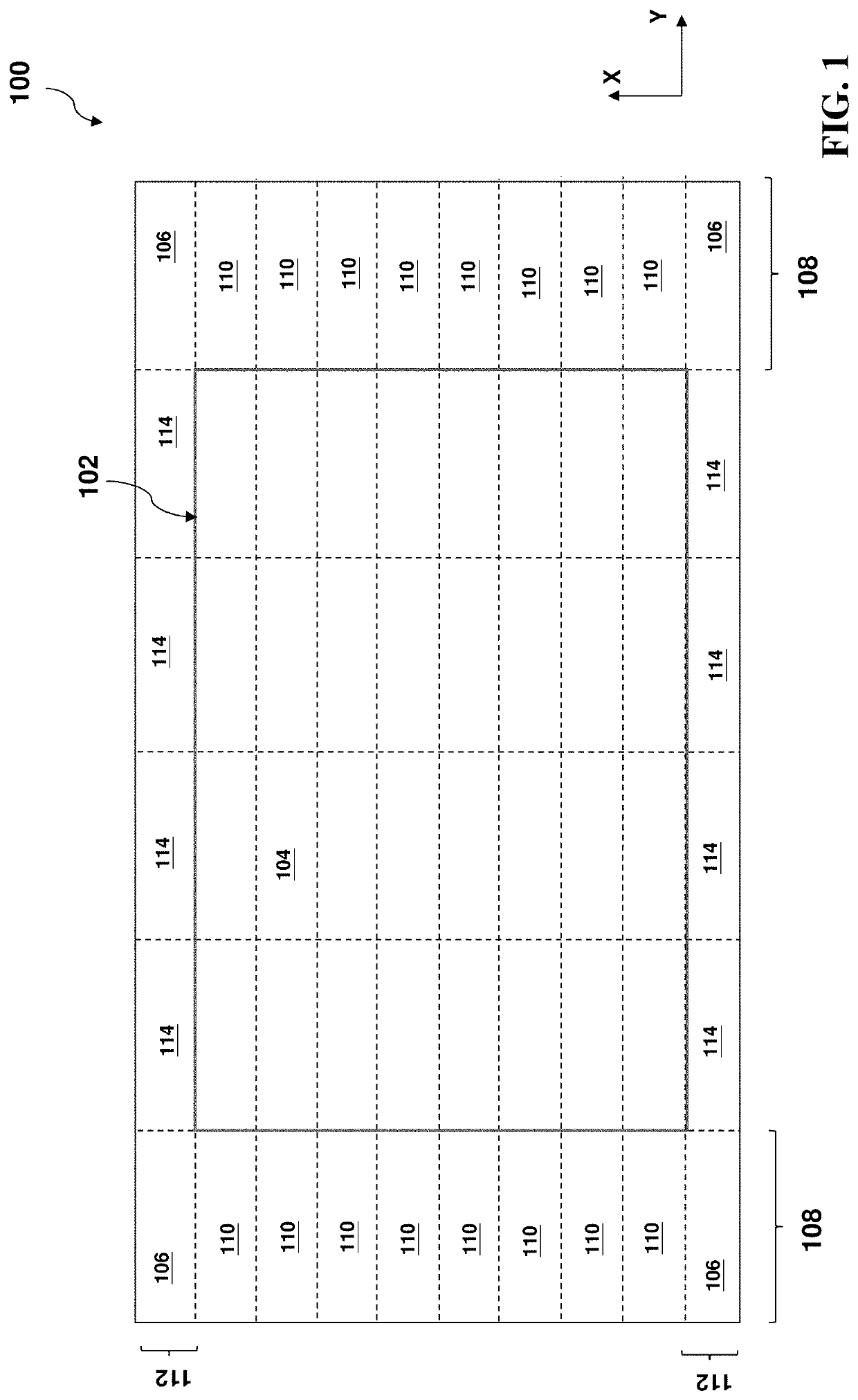

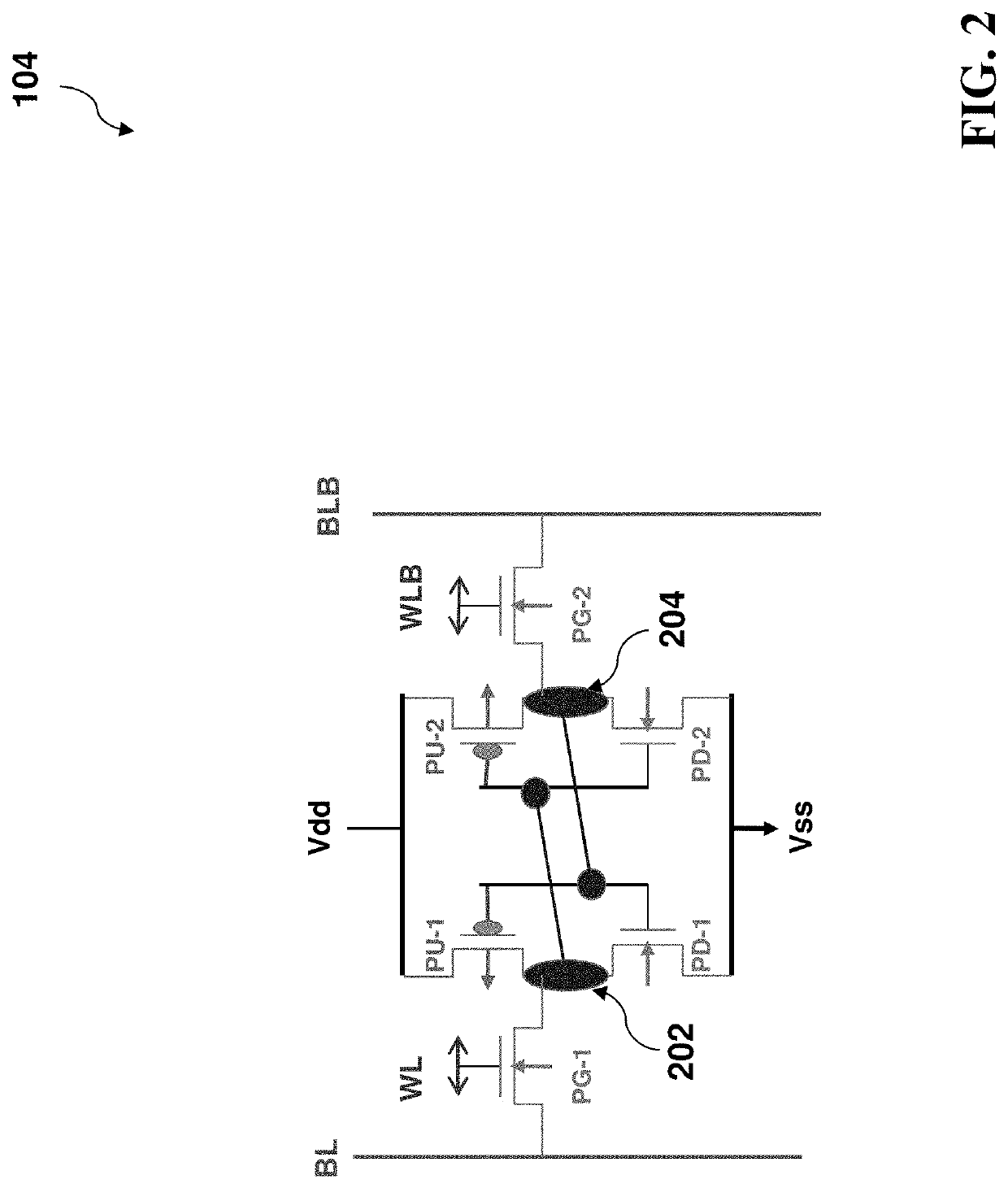

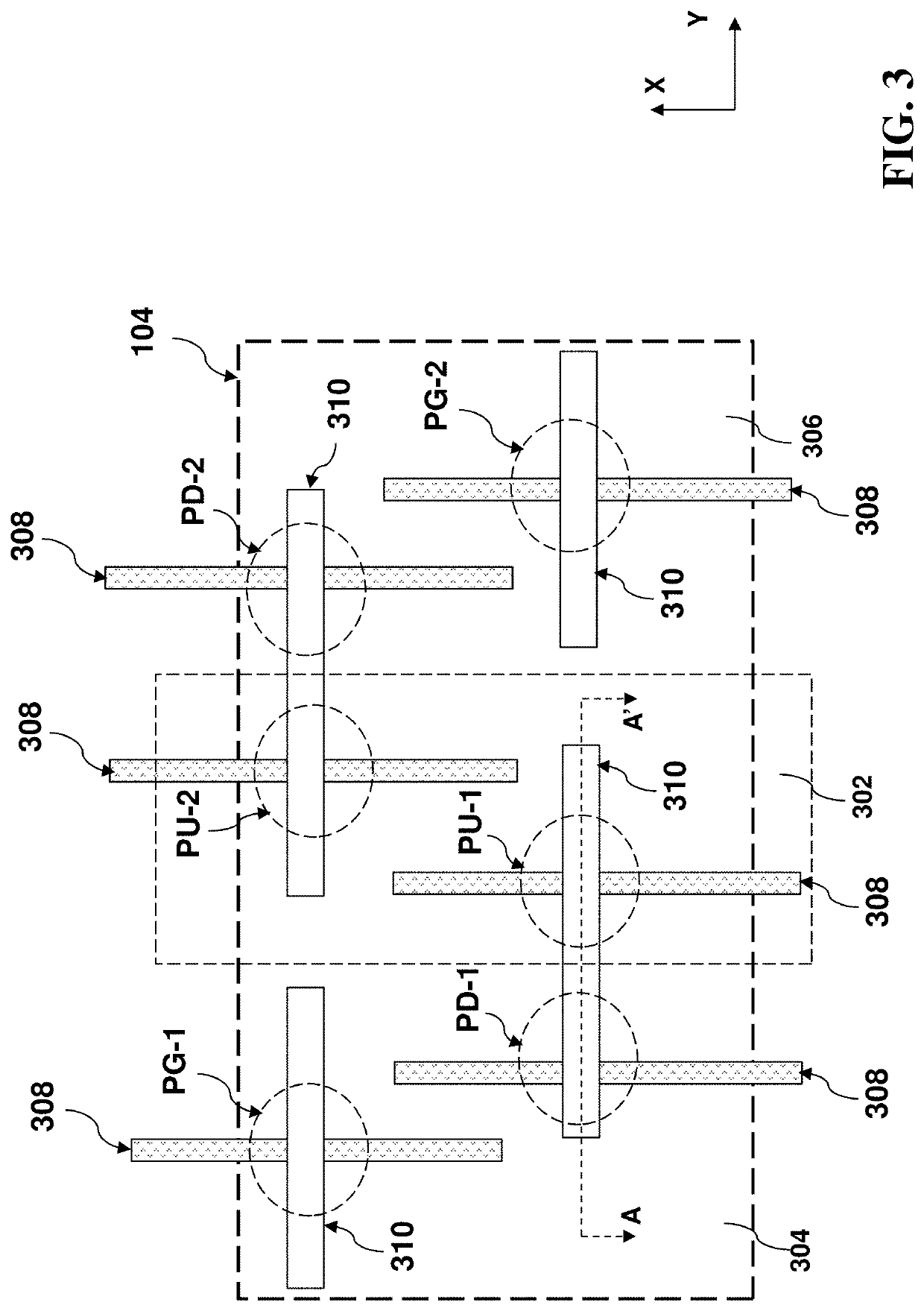

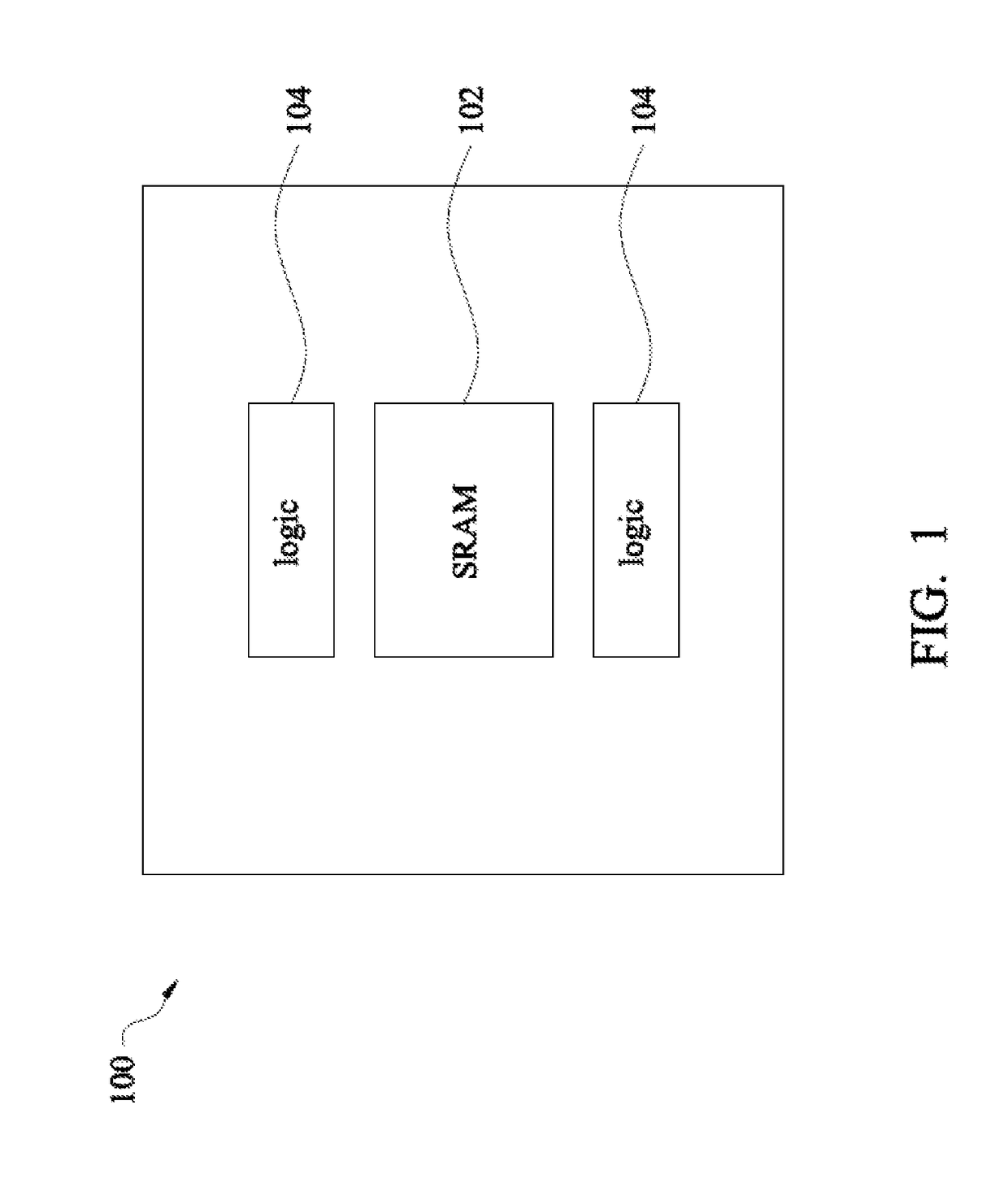

SRAM Structure and Connection

ActiveUS20200135741A1TransistorSemiconductor/solid-state device detailsSemiconductor structureElectrical connection

A semiconductor structure includes SRAM cells, bit-line edge cells, and word-line edge cells, wherein the SRAM cells are arranged in an array, bordered by the bit-line edge cells and the word-line edge cells, each of the SRAM cells including two inverters cross-coupled together and a pass gate coupled to the two inverters, and the pass gate includes a FET; a first bit-line of a first metal material, disposed in a first metal layer, and electrically connected to a drain feature of the FET; a first word-line of a second metal material, and electrically connected to a gate electrode of the FET, and disposed in a second metal layer; and a second bit-line of a third metal material, electrically connected to the first bit-line, and disposed in a third metal layer. The first metal material and the third metal material are different from each other in composition.

Owner:TAIWAN SEMICON MFG CO LTD

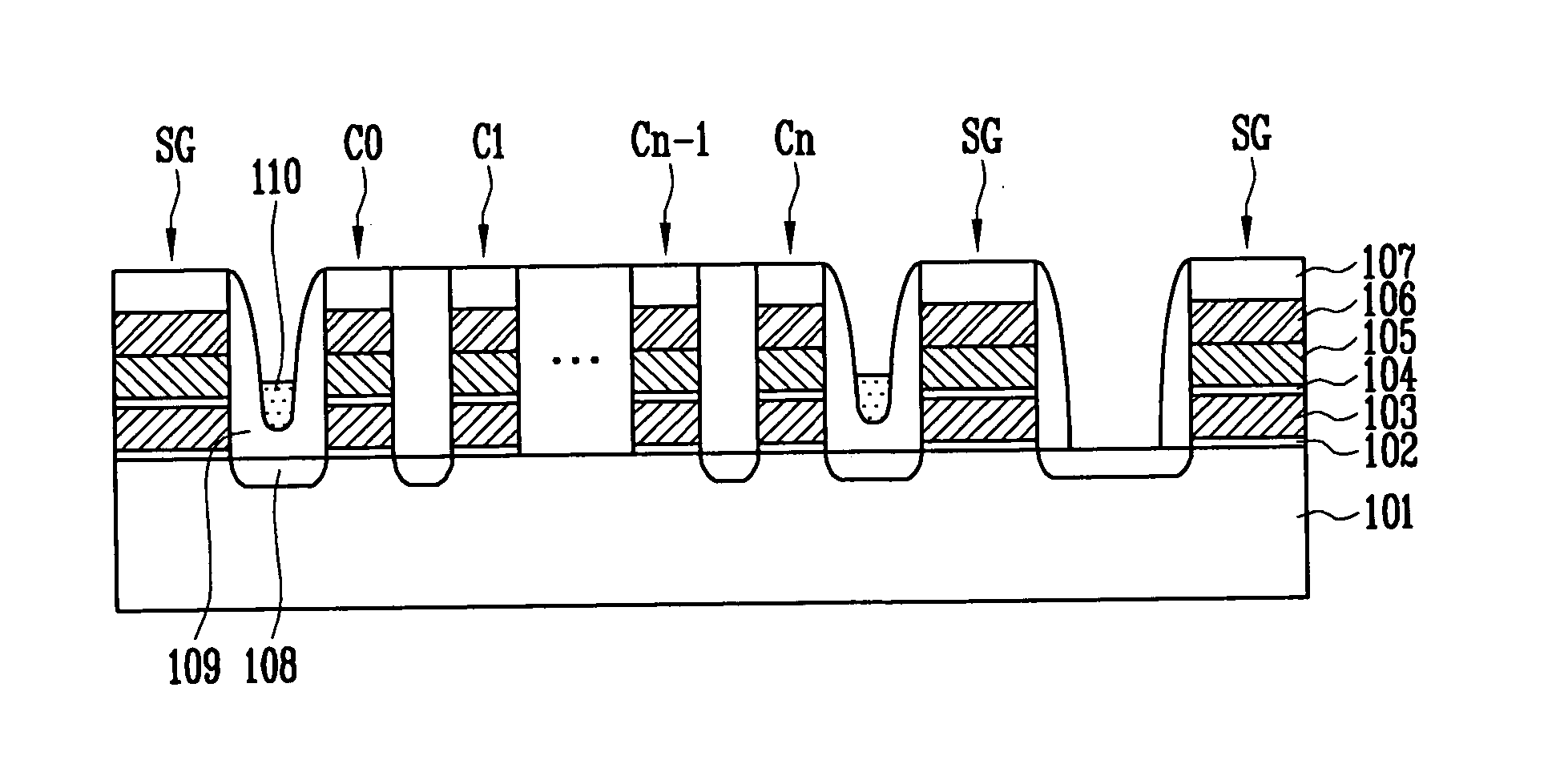

Method of manufacturing NAND flash memory device

InactiveUS20070122972A1Avoid damageSolid-state devicesSemiconductor/solid-state device manufacturingCell regionEngineering

Owner:SK HYNIX INC

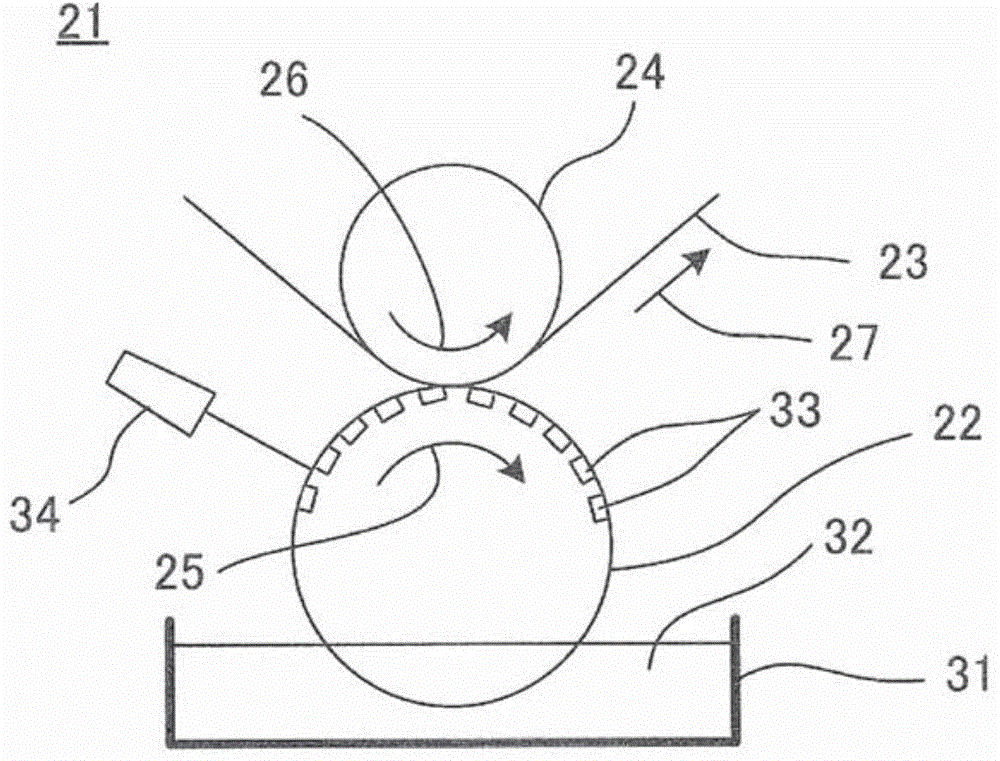

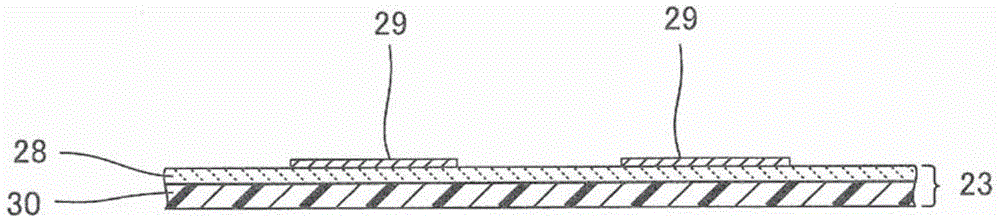

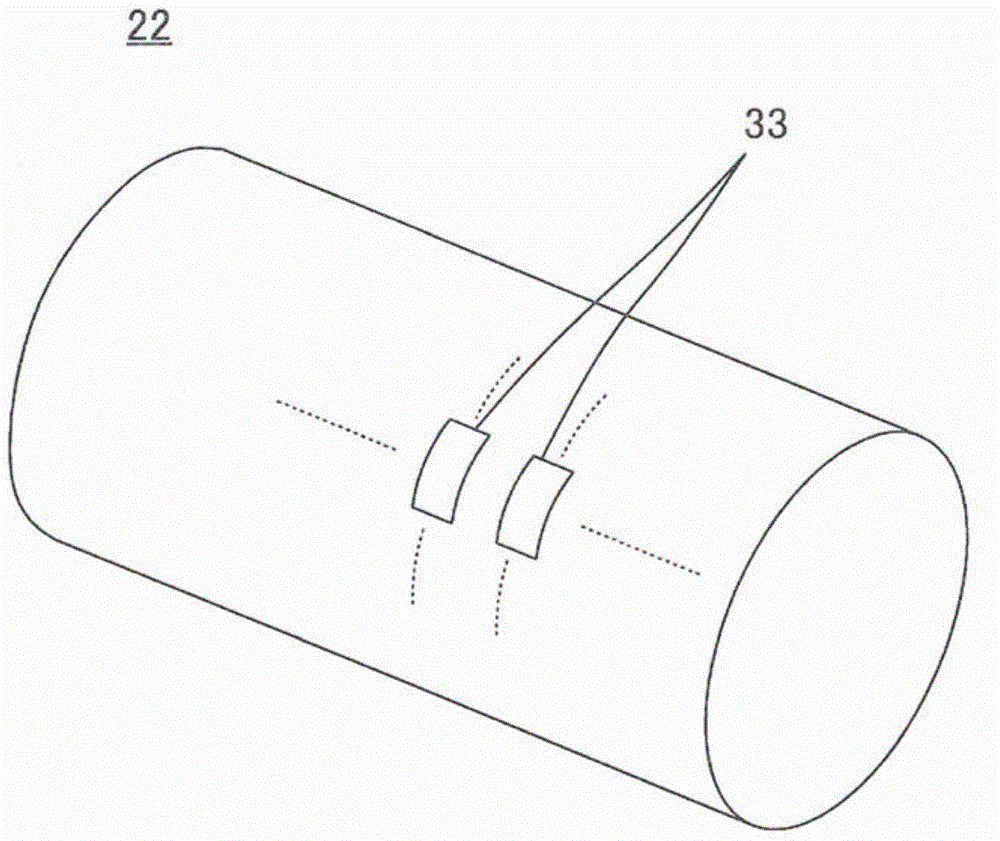

Gravure printing plate, manufacturing method thereof, gravure printing machine, and manufacturing method for laminated ceramic electronic component

ActiveCN104553436AReduce bumpinessImprove transfer efficiencyFixed capacitor electrodesFixed capacitor dielectricElectronic componentEdge cell

Banks, as well as a plurality of substantially recess-shaped cells defined by the banks, are provided in an image section formed in a gravure printing plate. Each of edge cells located along an outer edge of the image section is provided with a projecting portion that projects from a part of a base surface of that edge cell, and each projecting portion is distanced from the banks and located closer to the outer edge than the center of the corresponding edge cell. Preferably, the projecting portions and the banks that face the outer edge are positioned at a predetermined interval from the outer edge, and substantially frame-shaped recess portions that extend continuously along the outer edge are provided in the image section.

Owner:MURATA MFG CO LTD

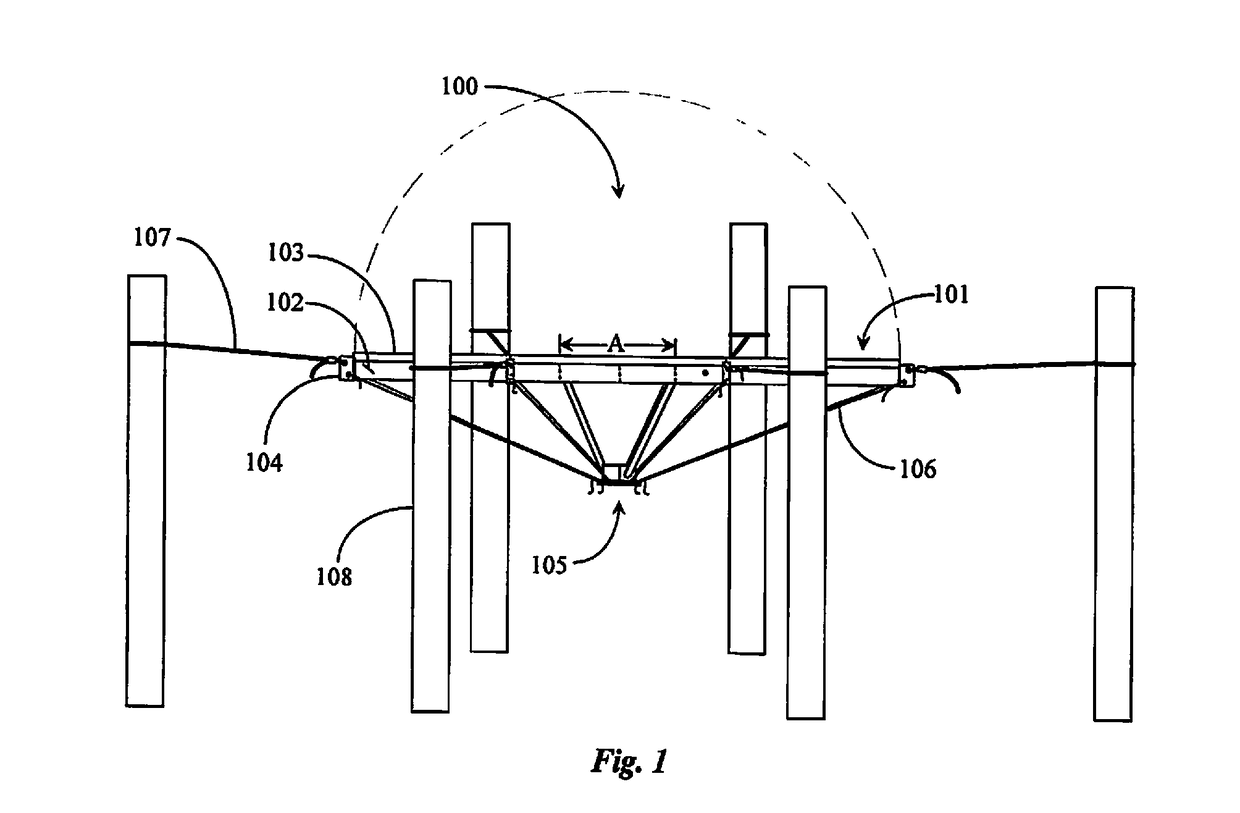

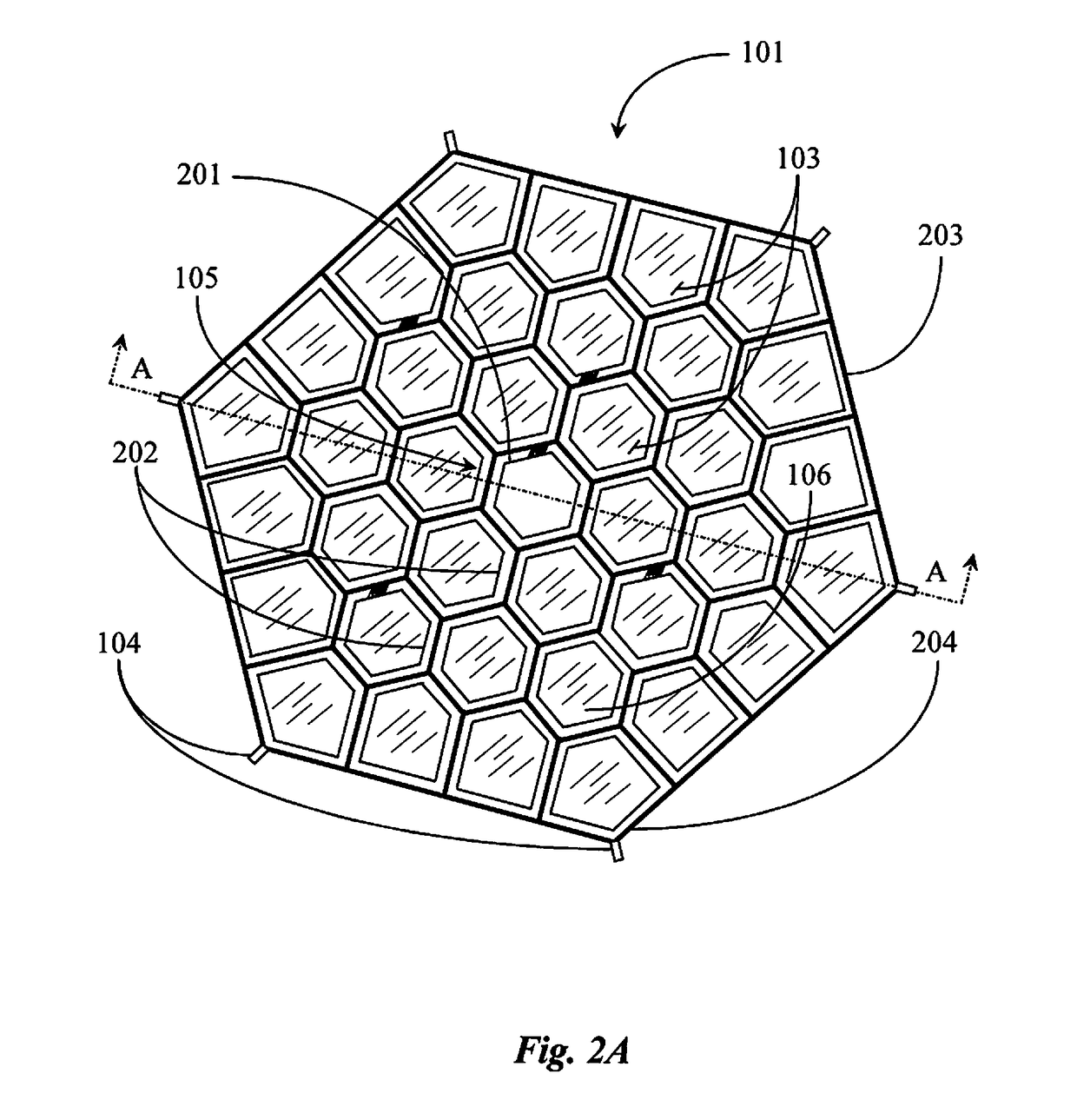

Modular trussed suspended platform

A trussed suspended modular platform having uniform weigh distribution for use as a platform to construct a temporary shelter such as a tent or other structure or to hold or hang equipment and other materials off the ground. The modular geometric design includes a polygon shaped center cell, a plurality of polygon shaped body cells, and a plurality of polygon shaped edge cells forming the platform edge and corners, each corner having an anchor bar with attachment holes and hardware for attaching the platform to support posts and for attaching a center extended truss hub structure positioned over the center cell with truss cables extending from the hub to anchored platform corners. The modular design allows for use as a sturdy suspend able mobile platform with trussing system that allows for assembly and disassembly in the field without need for an even ground surface or footings.

Owner:VAIOS BOZIKIS

Method for supporting continuous reception of evolved broadcast and multicast service data

The method for supporting continuous reception of enhanced broadcast service data comprising steps of: an MCE receiving an “MBMS Session Start Request” message from a core network; after the MCE receives the message, transmitting a response message to the core network; MCE transmitting an “MBMS Session Start Request” message to an ENB, the message including information of adjacent cells; and the ENB broadcasting the information of adjacent cells on a current cells. With the scheme of present invention, if a user wants to move to a common cell when he / she receives MBMS service in an SFN edge cell, he / she can enter the active mode and switch into the common cell so as to reduce MBMS data loss. When a UE moves from a cell with SC-PTM transmission mode into a cell with SC-PTM transmission mode, data loss can also be reduced.

Owner:SAMSUNG ELECTRONICS CO LTD

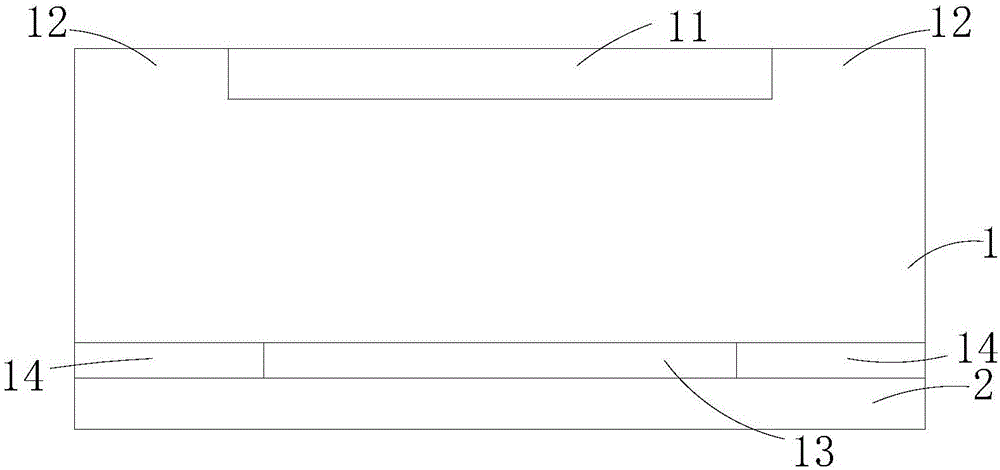

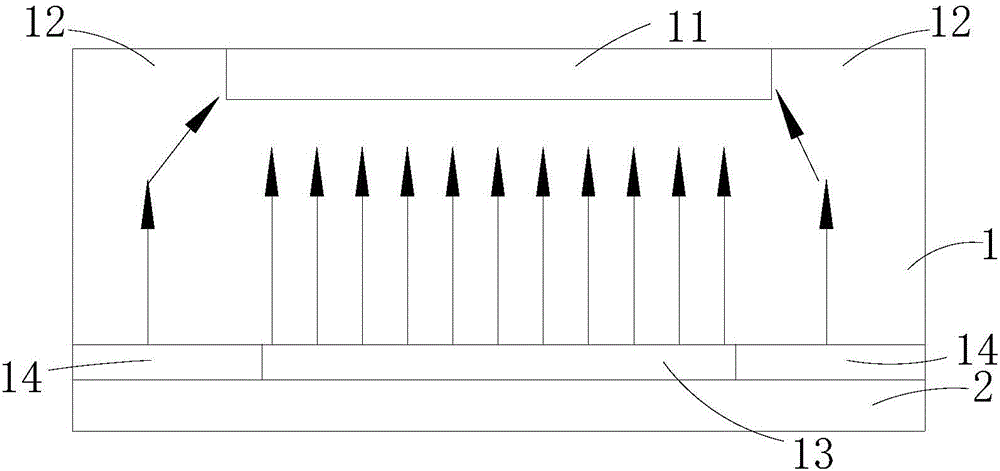

Switching power-semiconductor device and manufacturing method thereof

PendingCN106684118AReduce functionImprove safe work areaSemiconductor/solid-state device manufacturingSemiconductor devicesEdge cellSwitching power

The invention relates to the technical filed of a power semiconductor device, in particular to a switching power semiconductor and a manufacturing method thereof. The device comprises a silicon layer and a metal layer connected with the silicon layer, wherein the silicon lay comprises a relative first surface and a second surface on the opposite side, and the first surface comprises an active area and a junction termination area, and the active area is surrounded by the junction termination area. The second surface comprises a first ion doping region according to the junction termination area and a second ion doping region according to the junction termination area which ion doping concentration is lower than the first ion doping region, the second ion doping region is surrounded by the first ion doping region. The switching power semiconductor and a manufacturing method thereof has the advantages that the free carrier concentration and current density in the device junction termination area is reduced, the collision ionization and dynamic avalanche breakdown is cut down, the edge cell latch-up damage due to the concentration of the current is decreased and the integral safety area of the device is expanded.

Owner:CR TECH PINGTAN CO LTD

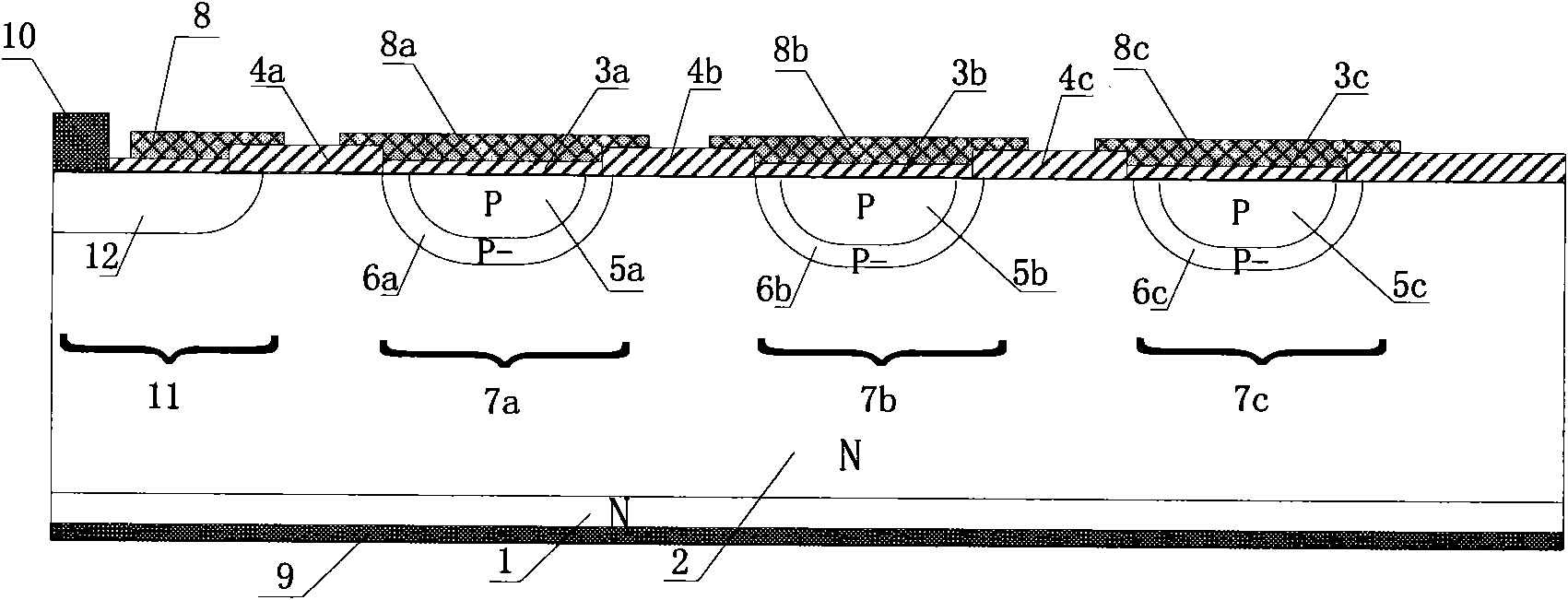

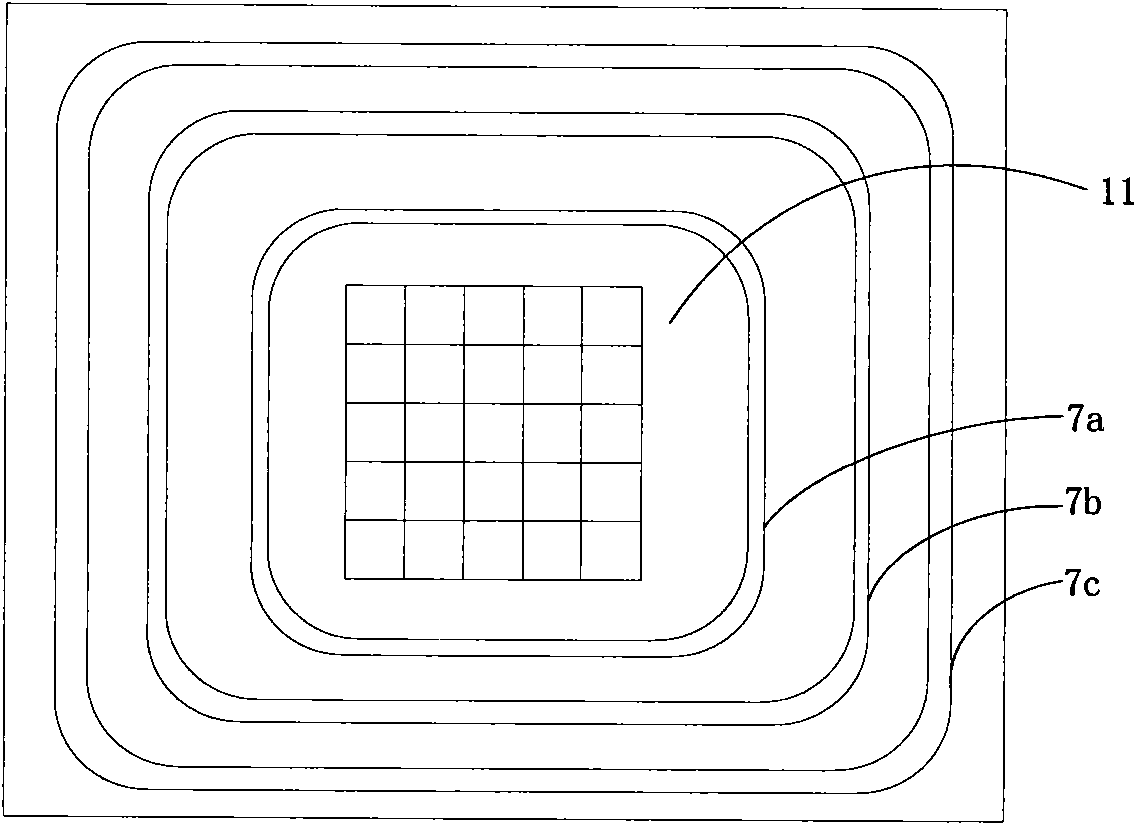

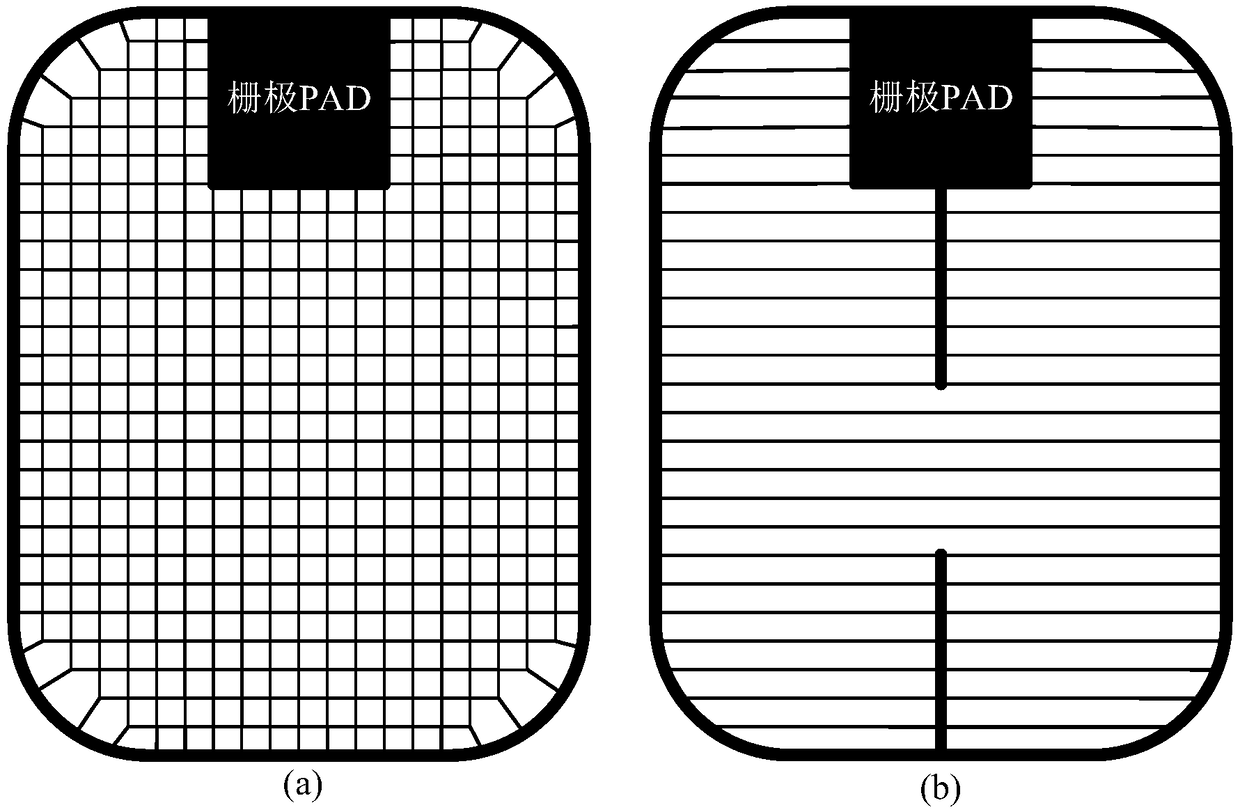

Design method for cathode short MOS-controlled thyristor layout

InactiveCN109309086AExtend the time to enter the latchThe time to enter the latch is advancedSolid-state devicesSemiconductor devicesCapacitanceEngineering

The invention belongs to the technical field of power semiconductor devices, and relates to a design method for a cathode short MOS-controlled thyristor (CS-MCT) layout. The method main includes forming a cellular grid structure into a bar-shaped grid structure in a horizontal direction; and defining a circle of cells connected to a junction terminal as edge cells, and defining other cells as internal cells, wherein the semiconductor doping regions of the edge cells are connected to a cathode through a bar-shaped contact hole, and the internal cells are connected to the cathode through a square-shaped contact hole. The latching current of the edge cells can be increased through improved measurements, and the time of the edge cells entering a latch can be prolonged; gate capacitance can bereduced, and the time of internal cells entering the latch can be advanced; in the middle part of the horizontal direction, bar-shaped grids also have metal interdigital in a vertical direction, so that the gate resistance parasitized on polysilicon can be reduced, and the time of the internal cells entering the latch can be advanced as well; and in a word, current can be uniformly distributed bymaking the edge cells and the internal cells simultaneously trigger the latch.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

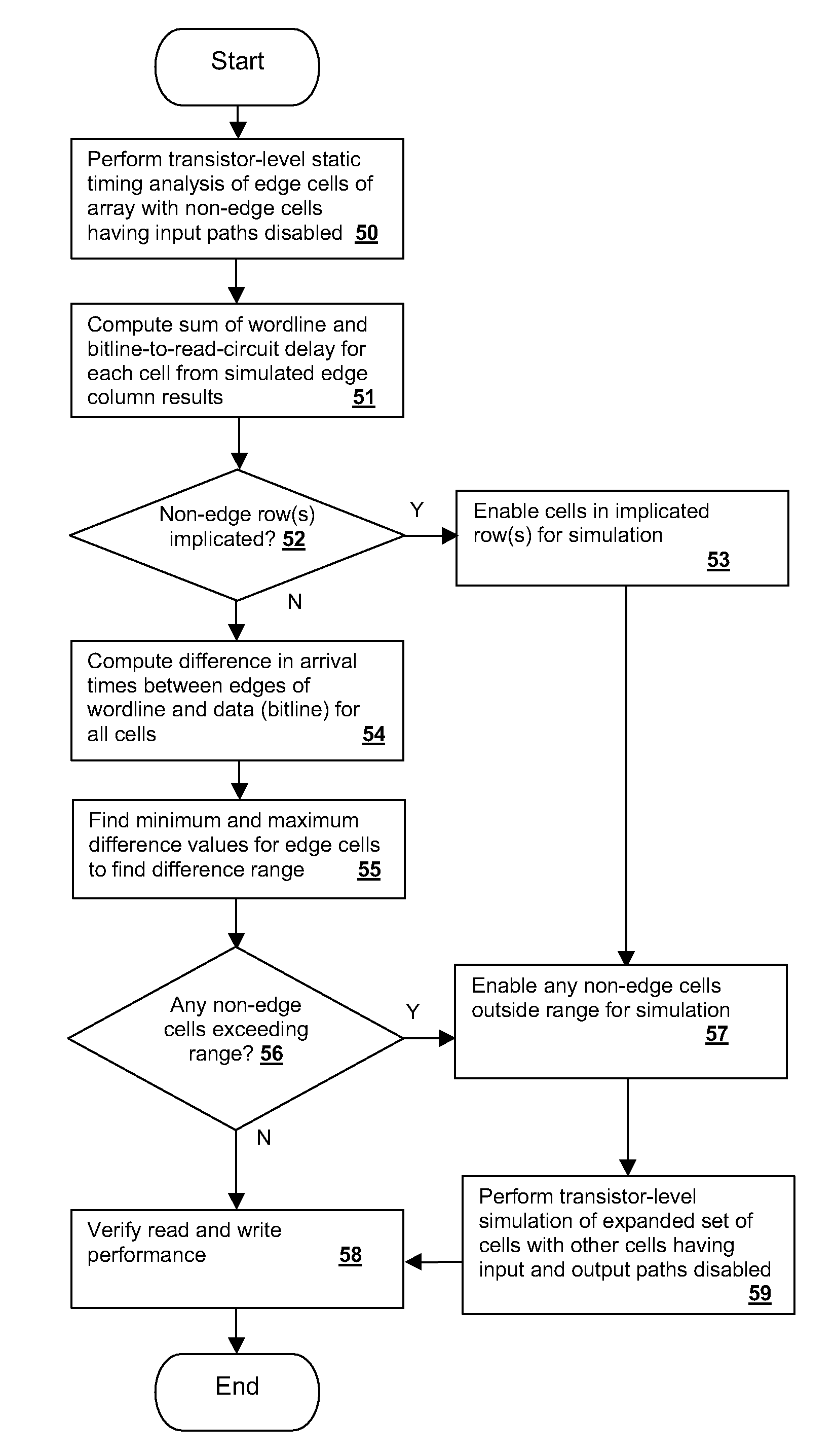

Method for verifying performance of an array by simulating operation of edge cells in a full array model

Owner:TAIWAN SEMICON MFG CO LTD

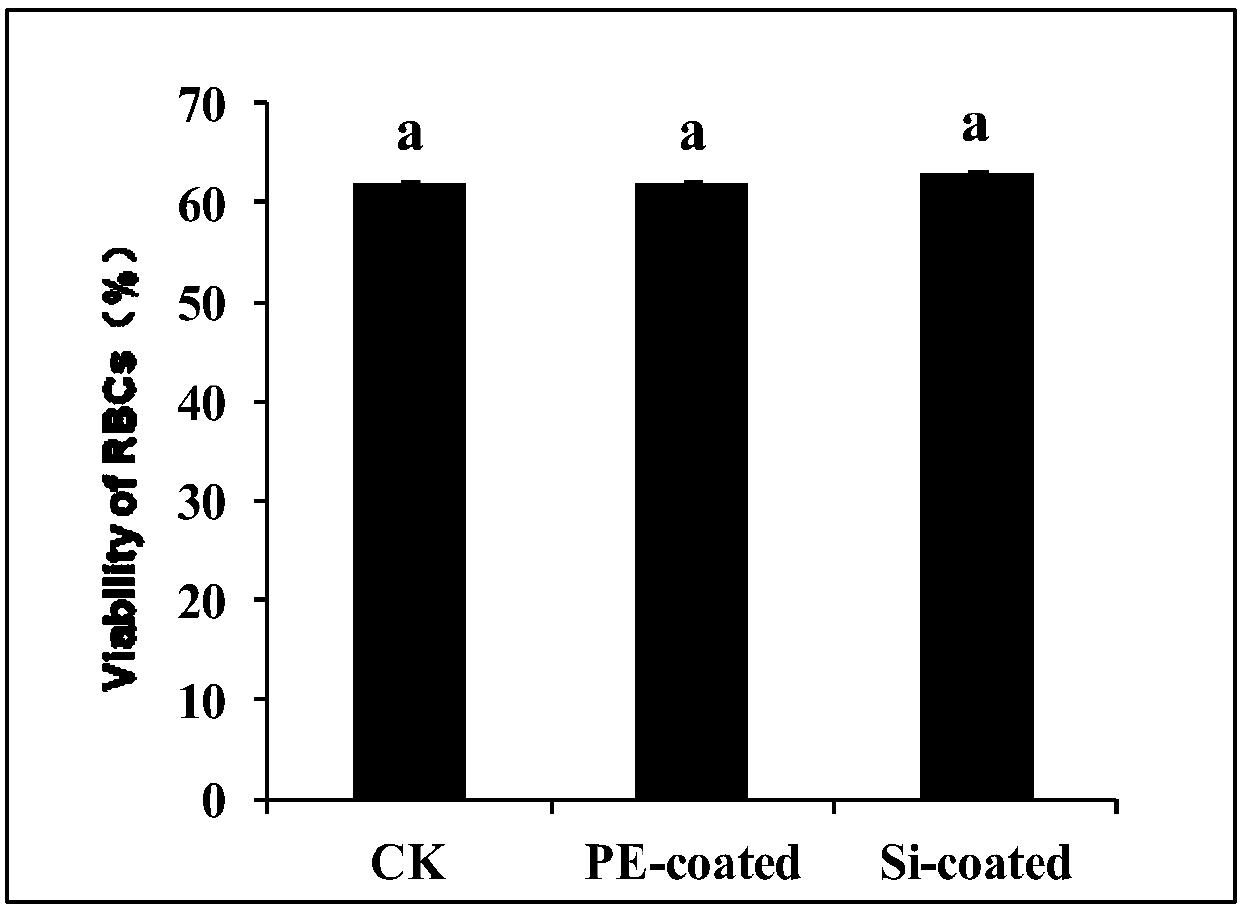

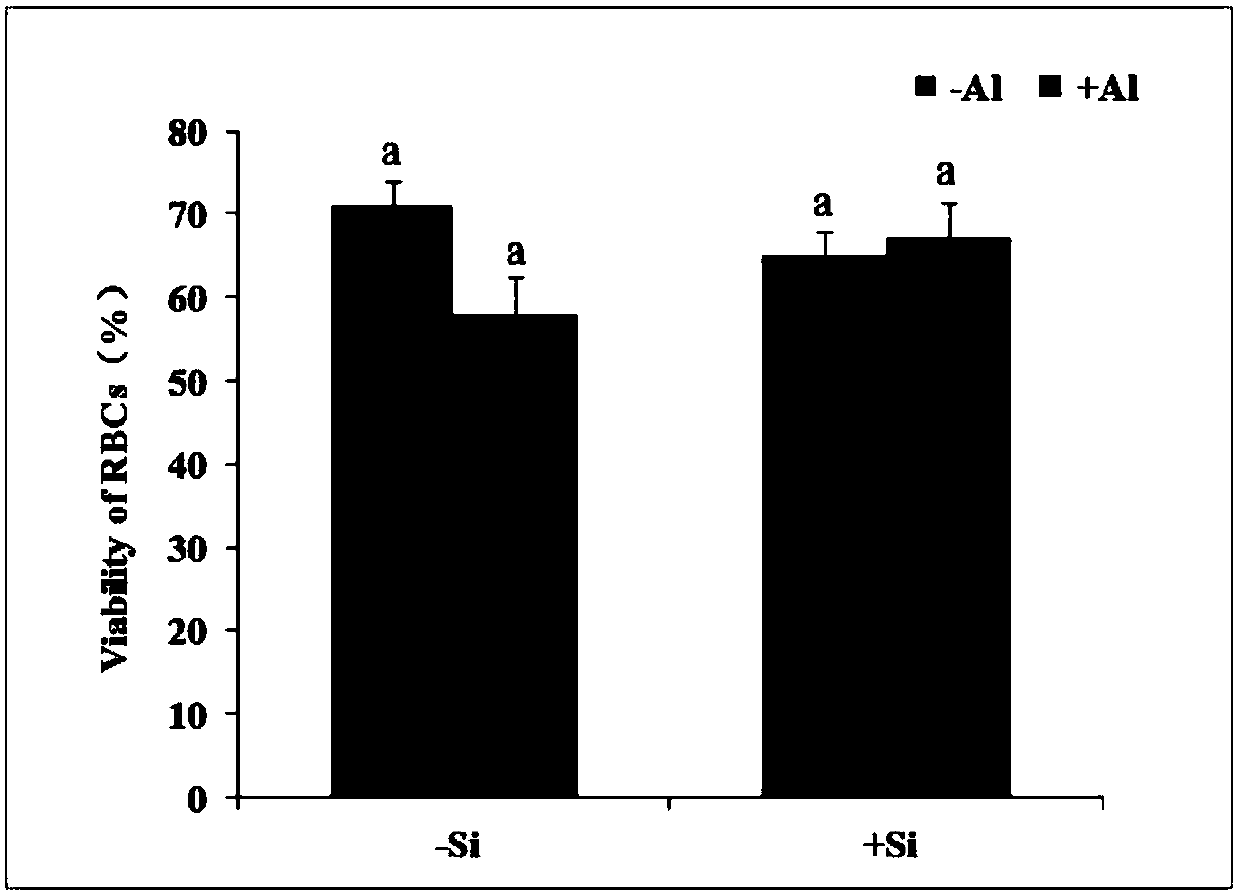

Plant root border cell silicon coating treatment method

InactiveCN107779426AEfficient formationImprove the ability to resist aluminum toxicityPlant cellsPlant rootsSilicic acid

The invention discloses a plant root border cell silicon coating treatment method which comprises the following process steps: 1. collecting plant seedling root border cell in a CaCl2 solution to obtain a cell collection solution; 2. transferring the cell collection solution into a CaCl2 solution containing 0.005g / ml of polyethylenimine, incubating for 10min, and washing the CaCl2 solution for 1-2times; and 3. transferring the obtained solution into a silicic acid solution, incubating for 20min, silicifying the surface of the cell and then washing with the CaCl2 solution. According to the invention, a nanosilicon coating layer is formed on the surface of a plant root border cell effectively, so that technical basis is provided for improving the aluminum toxicity resistant capacity of theplant root border cell.

Owner:FOSHAN UNIVERSITY

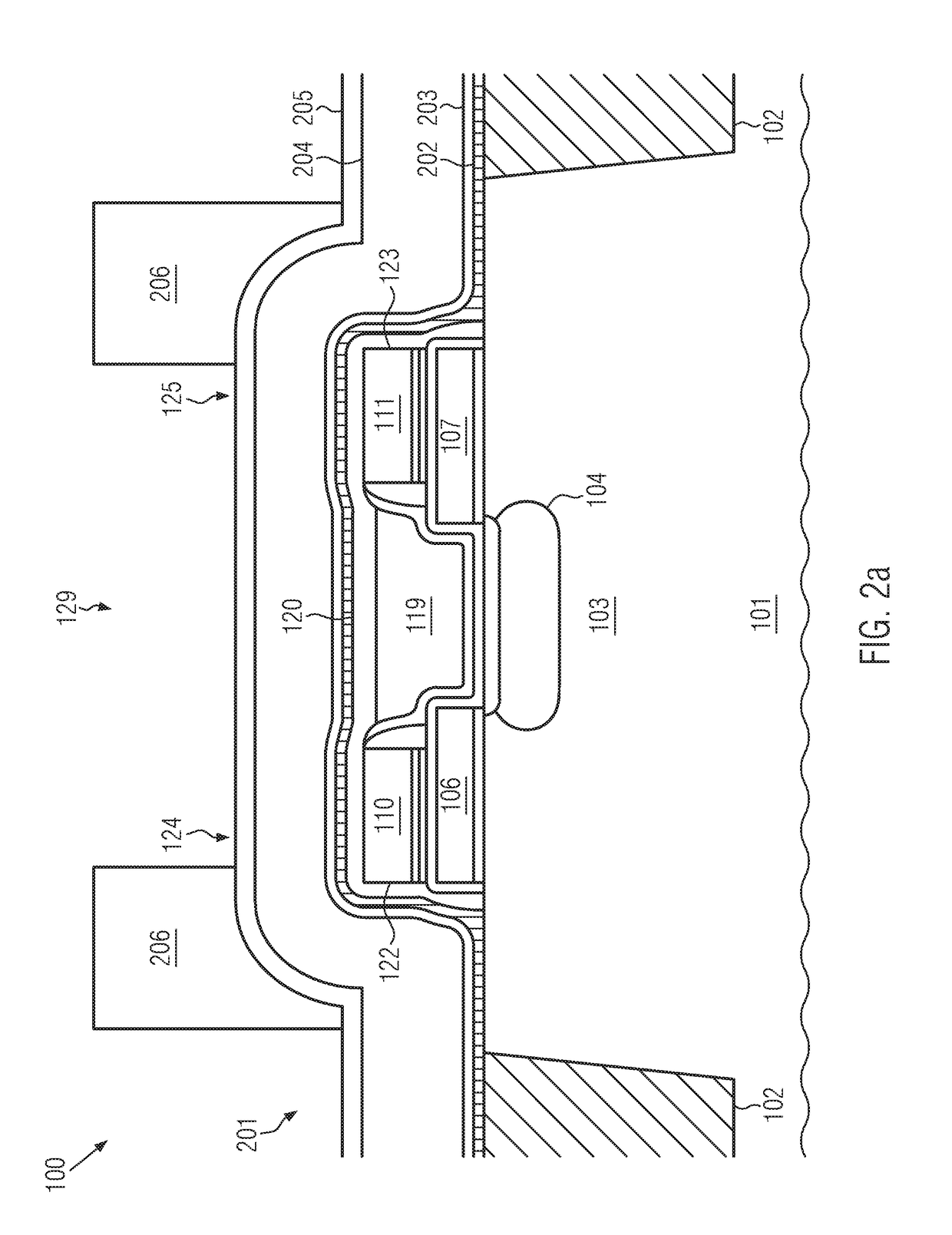

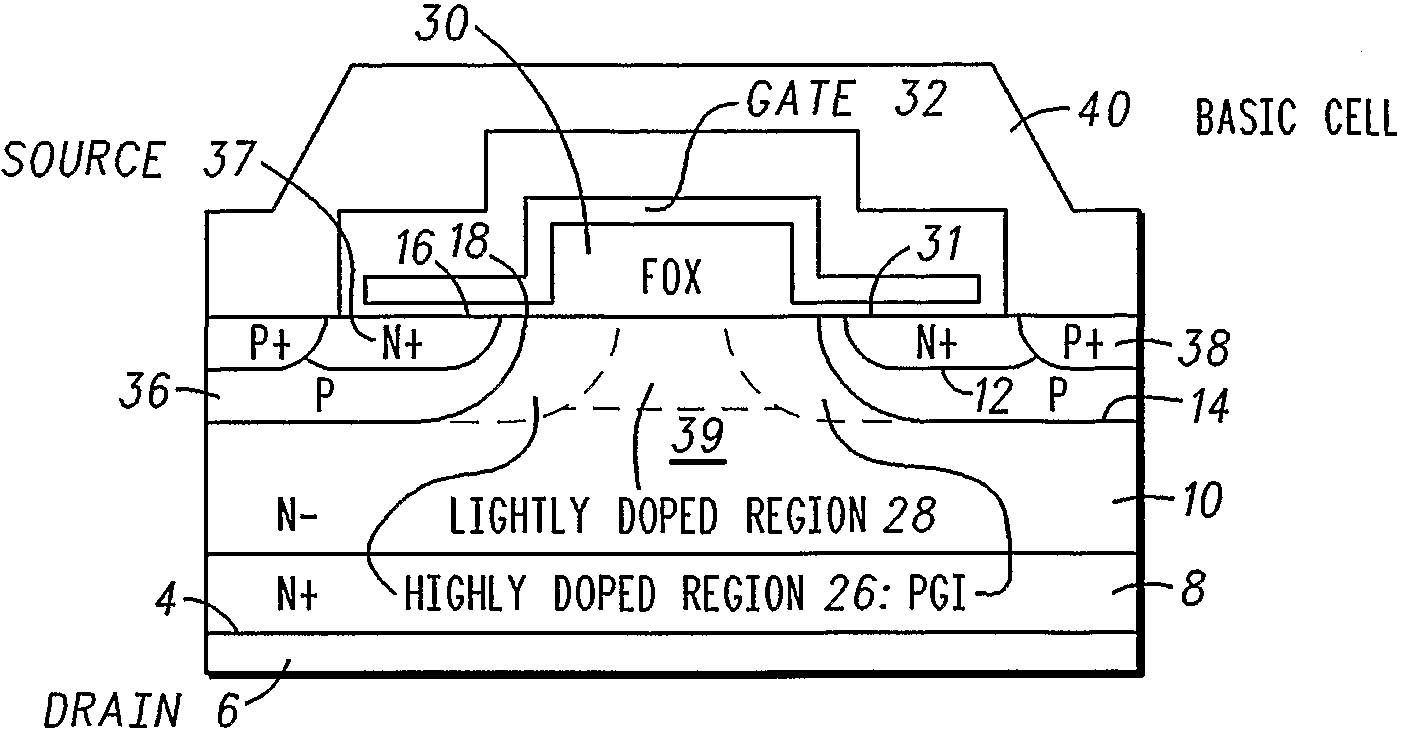

Power semiconductor device and method of manufacturing a power semiconductor device

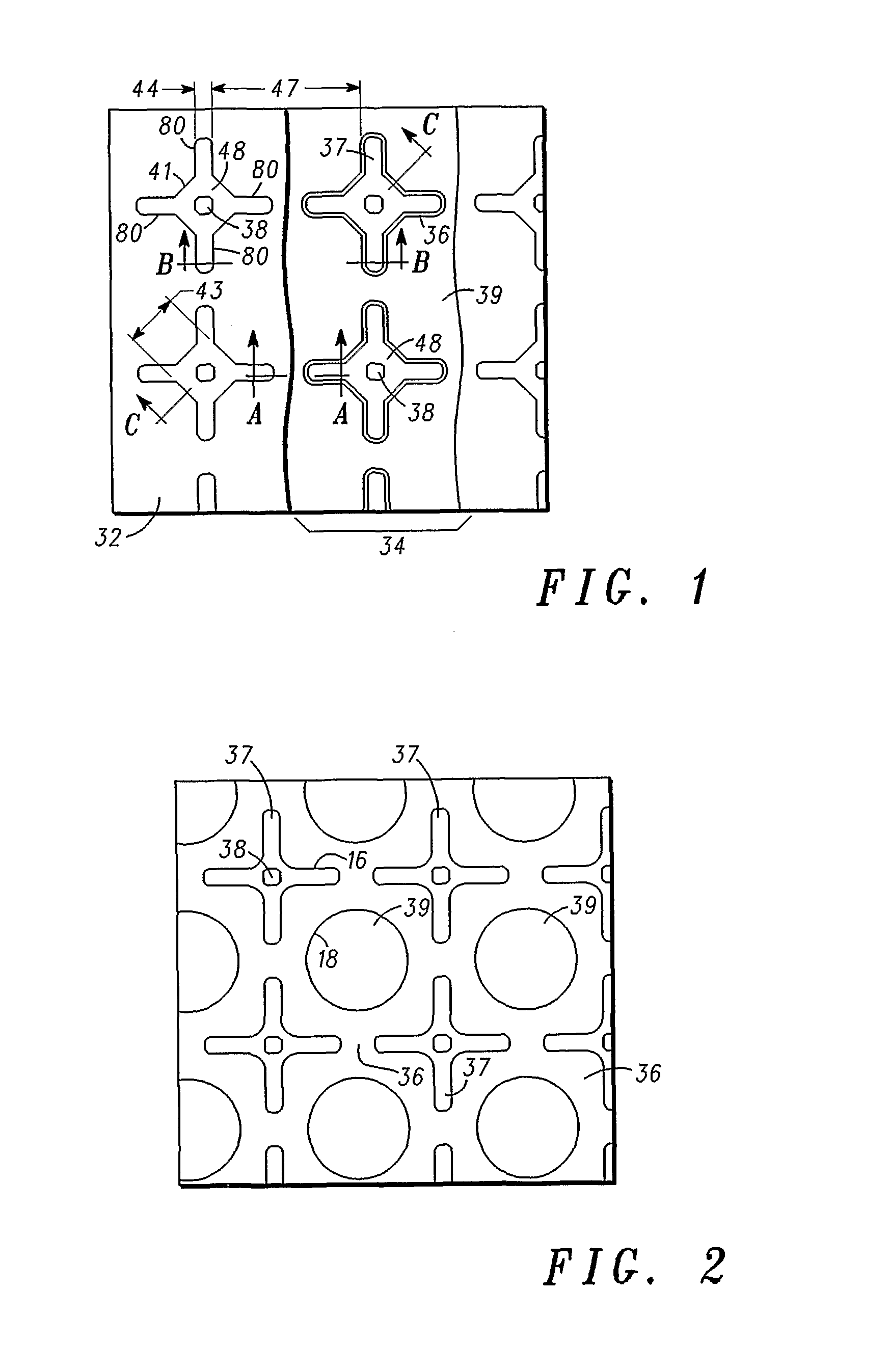

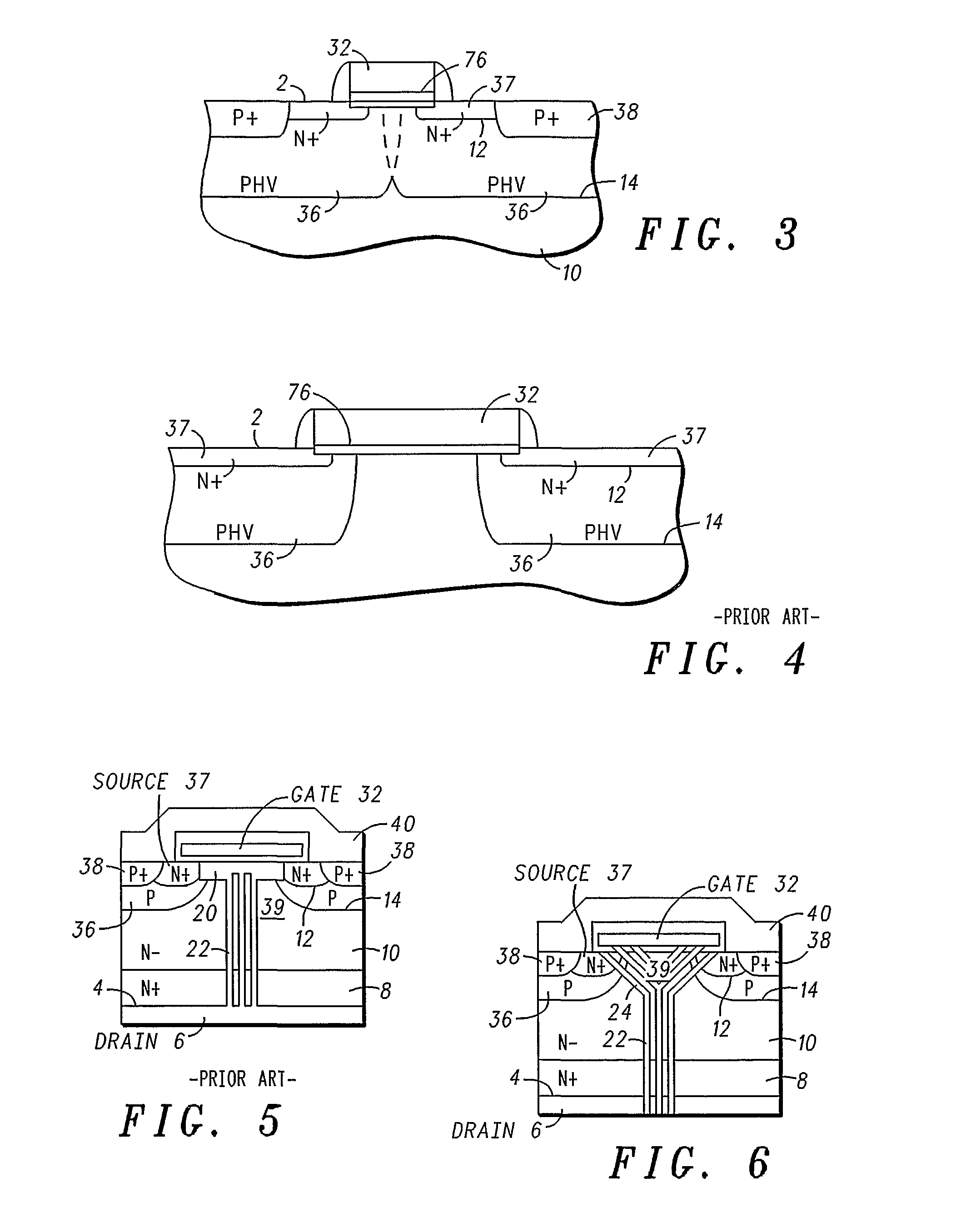

A semiconductor power switch having an array of basic cells in which peripheral regions in the active drain region extend beside the perimeter of the base-drain junction, the peripheral regions being of higher dopant density than the rest of the second drain layer. Intermediate regions in the centre of the active drain region are provided of lighter dopant density than the rest of the second drain layer. This provides an improved compromise between the on-state resistance and the breakdown voltage by enlarging the current conduction path at in its active drain region. On the outer side of each edge cell of the array, the gate electrode extends over and beyond at least part of the perimeters of the base-source junction and the base-drain junction towards the adjacent edge of the die. Moreover, on the outer side of each edge cell, the second drain layer includes a region of reduced dopant density that extends beyond the gate electrode right to the adjacent edge of the die.

Owner:NXP USA INC

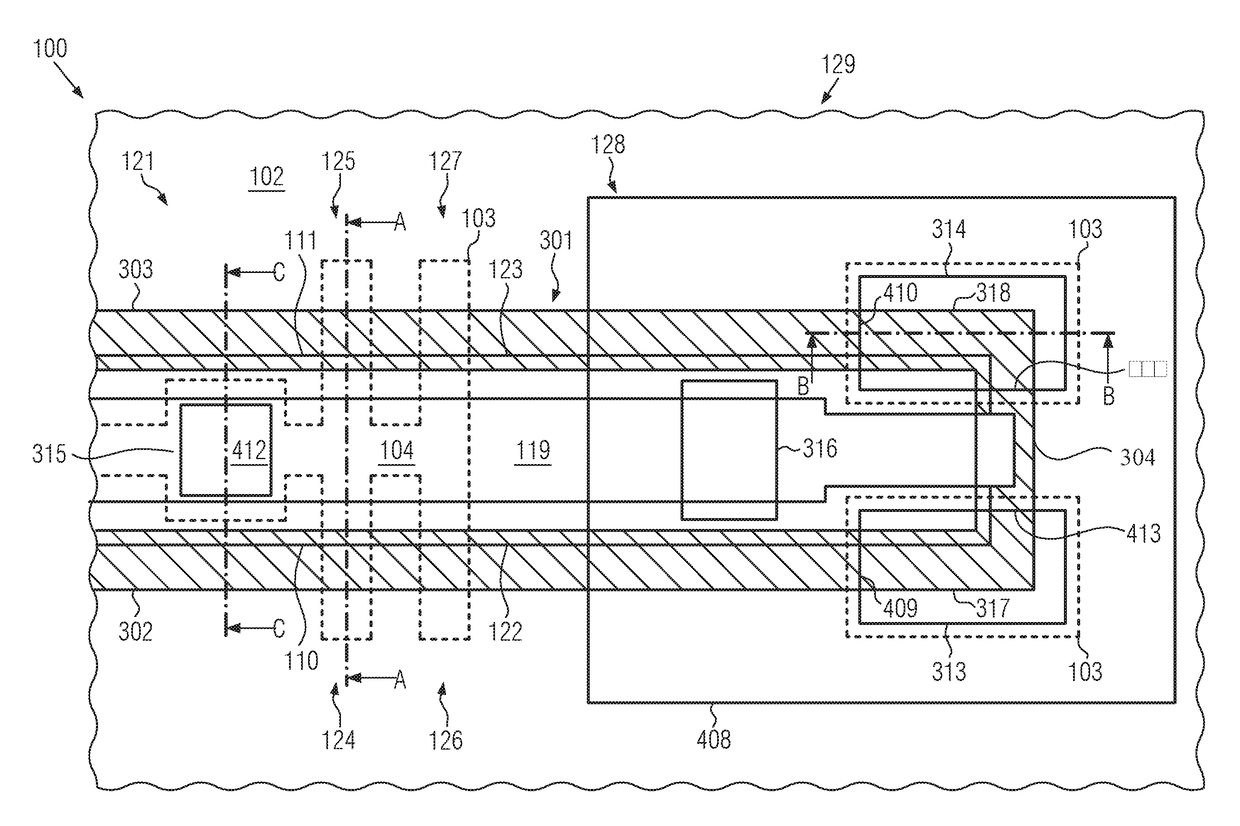

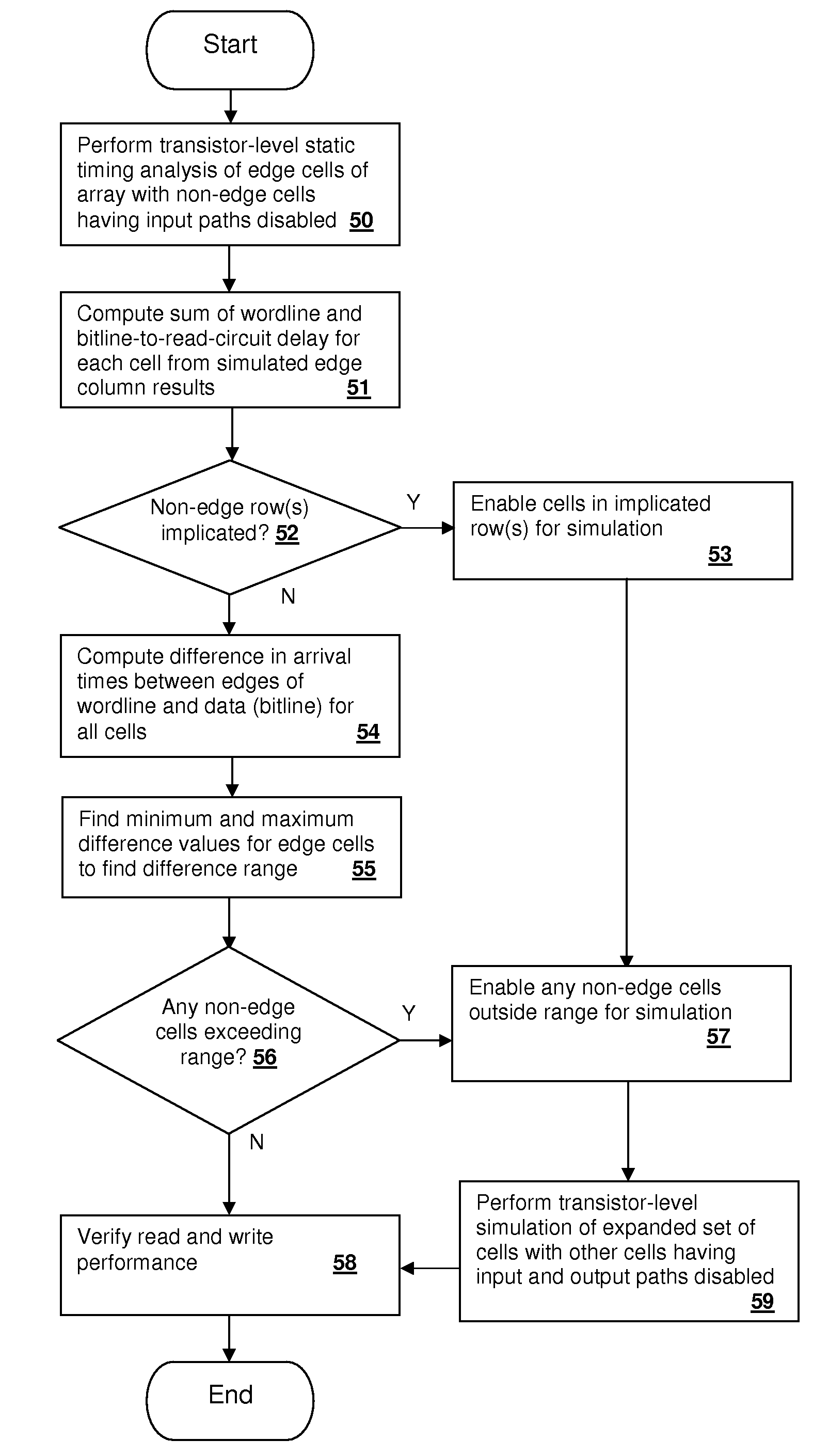

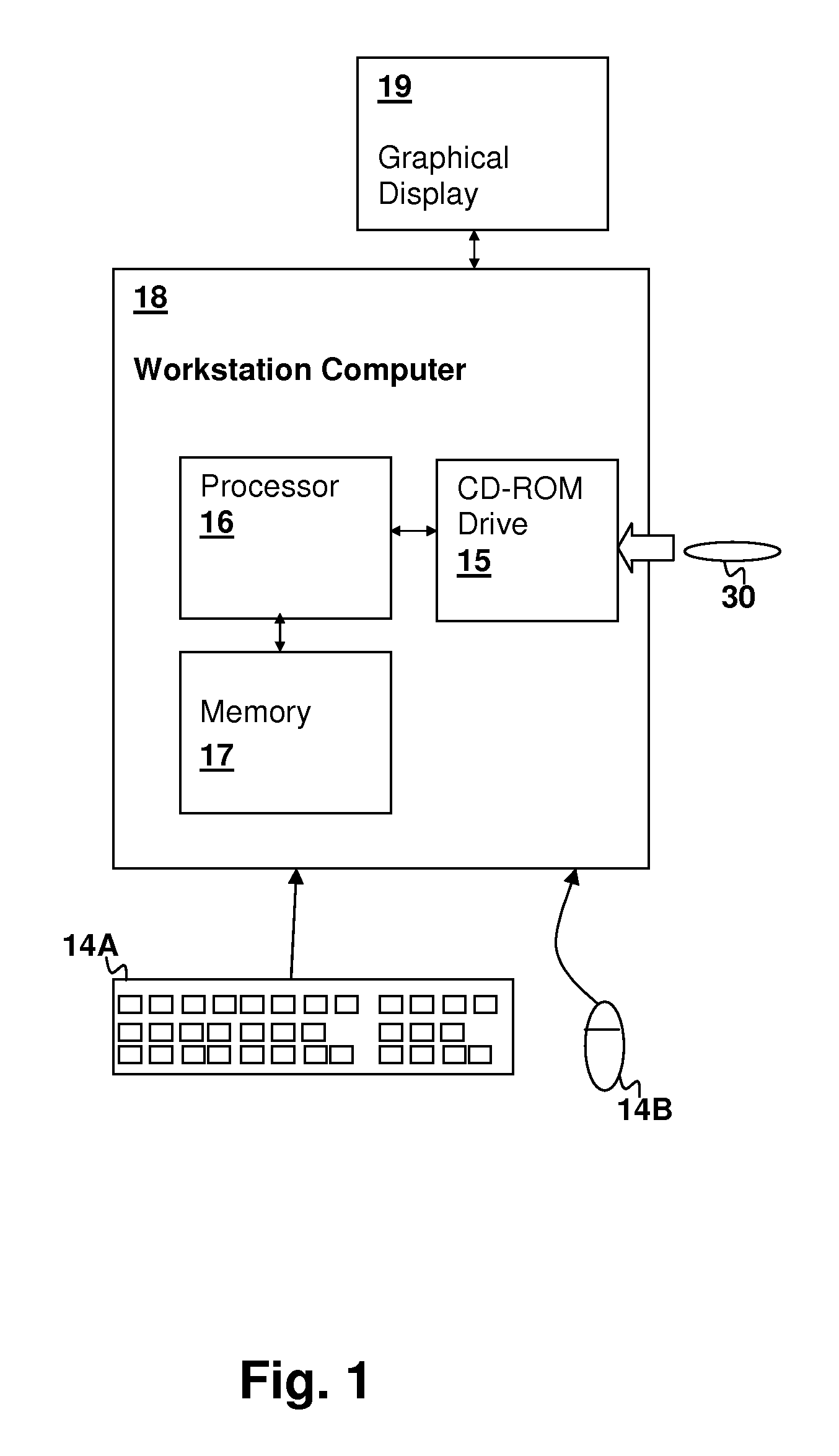

System and computer program for verifying performance of an array by simulating operation of edge cells in a full array model

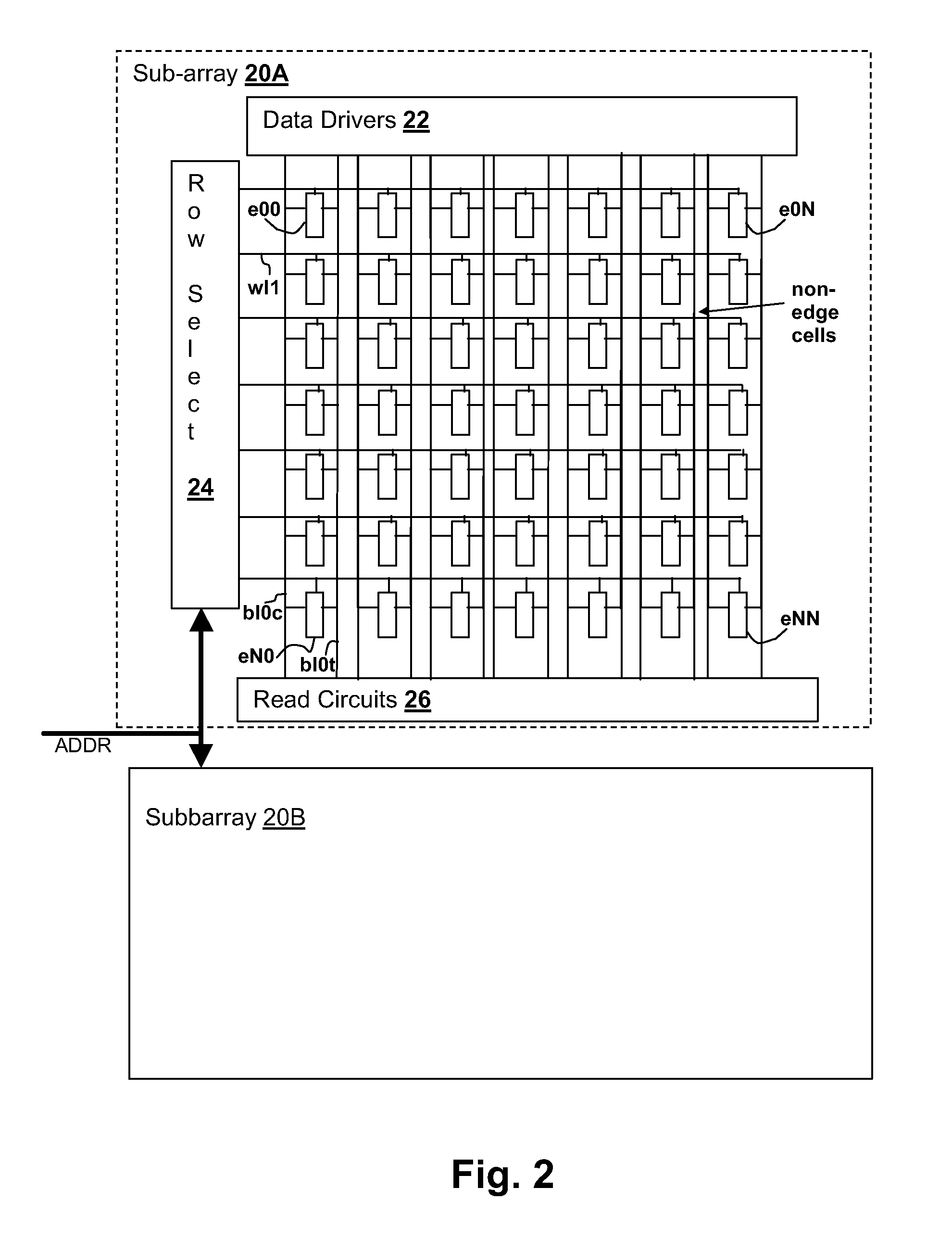

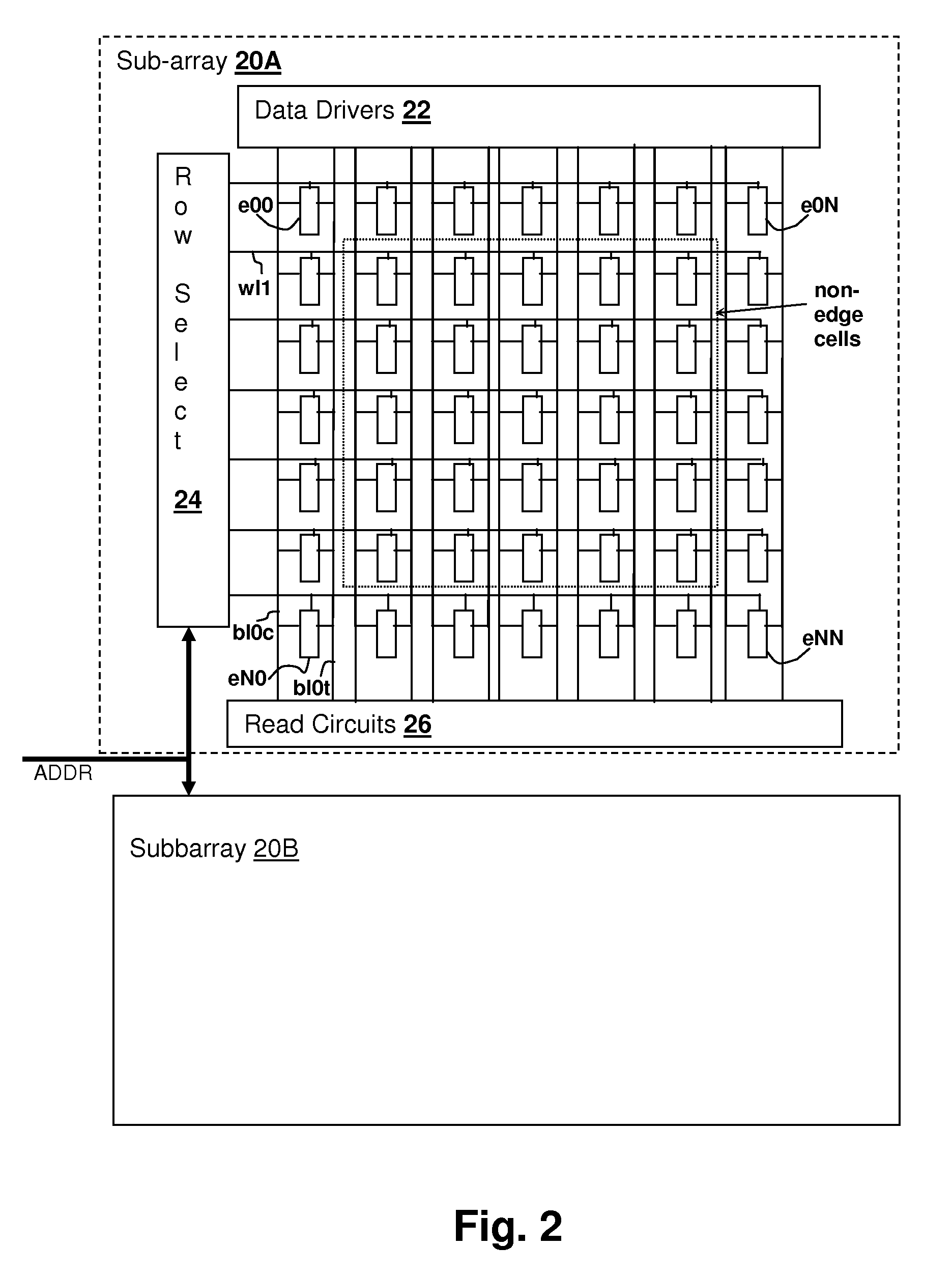

ActiveUS20080270963A1Reduce computing timeDigital storageCAD circuit designParallel computingOutlier

A system and computer program for verifying performance of an array by simulating operation of edge cells in a full array model reduces the computation time required for complete design verification. The edge cells of the array (or each subarray if the array is partitioned) are subjected to a timing simulation while the center cells of the array are logically disabled, but remain in the circuit model, providing proper loading. Additional cells are specified for simulation if calculations indicate a worst-case condition due to a non-edge cell. Wordline arrivals are observed to determine worst-case rows for selection. For write operations, the difference between the wordline edges and the data edges is used to locate any non-edge “outlier” cells. For read operations, the wordline delays are summed with the bitline delays determined from edge column data to locate any outliers.

Owner:TAIWAN SEMICON MFG CO LTD

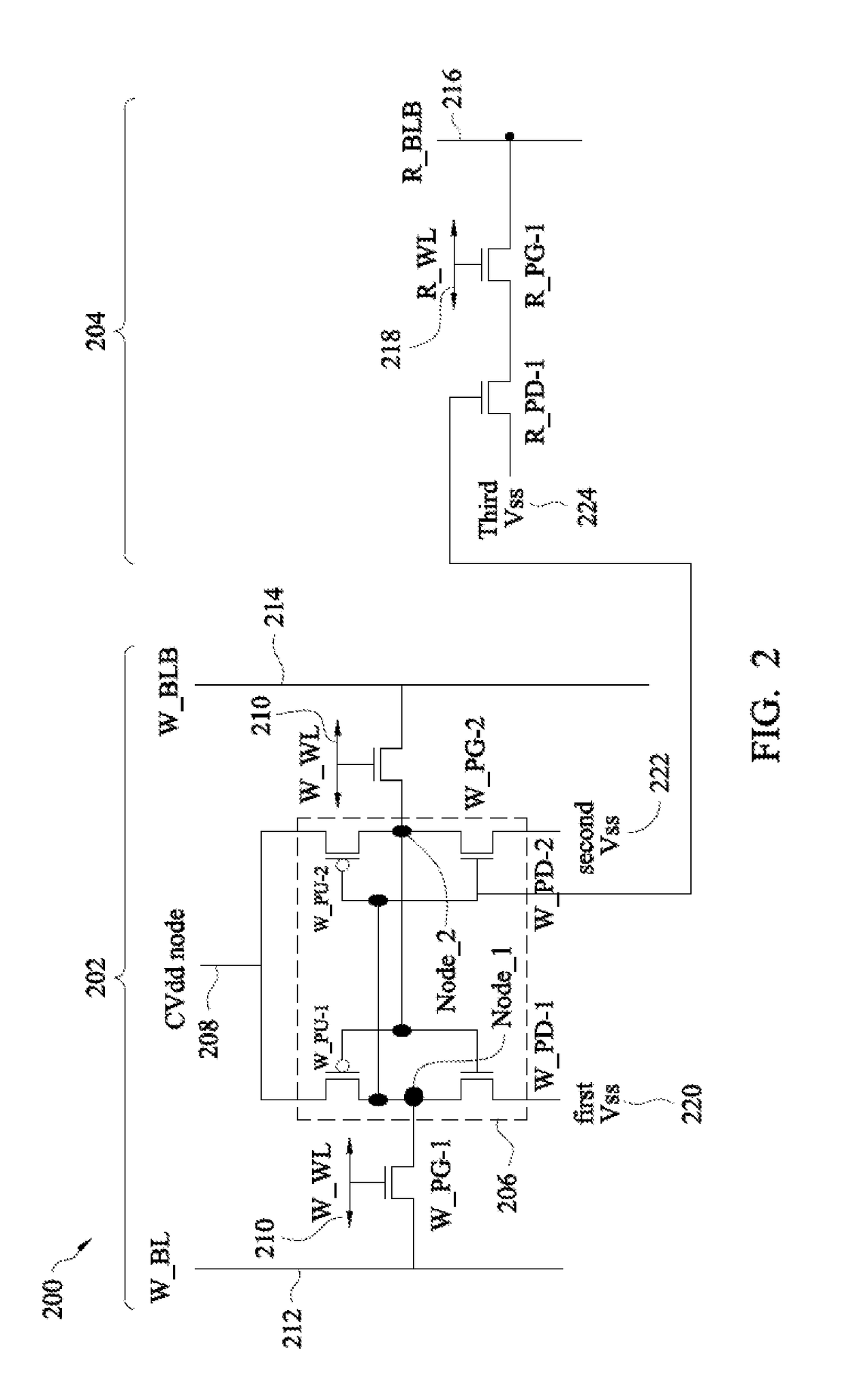

Two-port SRAM connection structure

A static random access memory (SRAM) device is provided in accordance with some embodiments. The SRAM device comprises a plurality of two-port SRAM arrays, which comprise a plurality of two-port SRAM cells. Each two-port SRAM cell comprises a write port portion, a read port portion, a first plurality of metal lines located in a first metal layer, a second plurality of metal lines located in a second metal layer, a third plurality of metal lines located in a third metal layer a plurality of edge cells, a plurality of well strap cells, and a plurality of jumper structures. Each jumper structure comprises first, second, and third metal landing pads located in the second metal layer and electrically connecting metal lines of the first and third metal layers.

Owner:TAIWAN SEMICON MFG CO LTD

Method of manufacturing NAND flash memory device

InactiveUS7335558B2Avoid damageSolid-state devicesSemiconductor/solid-state device manufacturingCell regionEngineering

A method of manufacturing a NAND flash memory device, including the steps of providing a semiconductor substrate in which a cell region and a select transistor region are defined; simultaneously forming a plurality of cell gates on the semiconductor substrate of the cell region and forming selection gates on the semiconductor substrate of the select transistor region; forming an oxide film on the entire structure and then forming a nitride film; etching the nitride film so that the nitride film remains only between the selection gates and adjacent edge cell gates; and, blanket etching the oxide film to form spacers on sidewalls of the selection gates. Accordingly, uniform threshold voltage distributions can be secured, and process margins for a spacer etch target can be secured when etching the spacers. Furthermore, the nitride film partially remains between the edge cell gates and the selection gates even after the gate spacers are etched. It is therefore possible to prohibit the infiltration of moisture or hydrogen ion, which may occur in a subsequent process.

Owner:SK HYNIX INC