Method for preparing double side dielectric groove part SOI material

A dielectric groove and double-sided technology, which is applied in the field of material preparation of SOI power devices, can solve the problems of low withstand voltage, easy breakdown in advance, and low withstand voltage of SOI devices, so as to ensure the quality of SiO2, reduce self-heating effect, and withstand high voltage The effect of heat dissipation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0059] Refer to the attached Figure 1a Referring to Fig. 11, the present invention discloses a method for preparing SOI material of a double-sided dielectric tank, the steps are as follows:

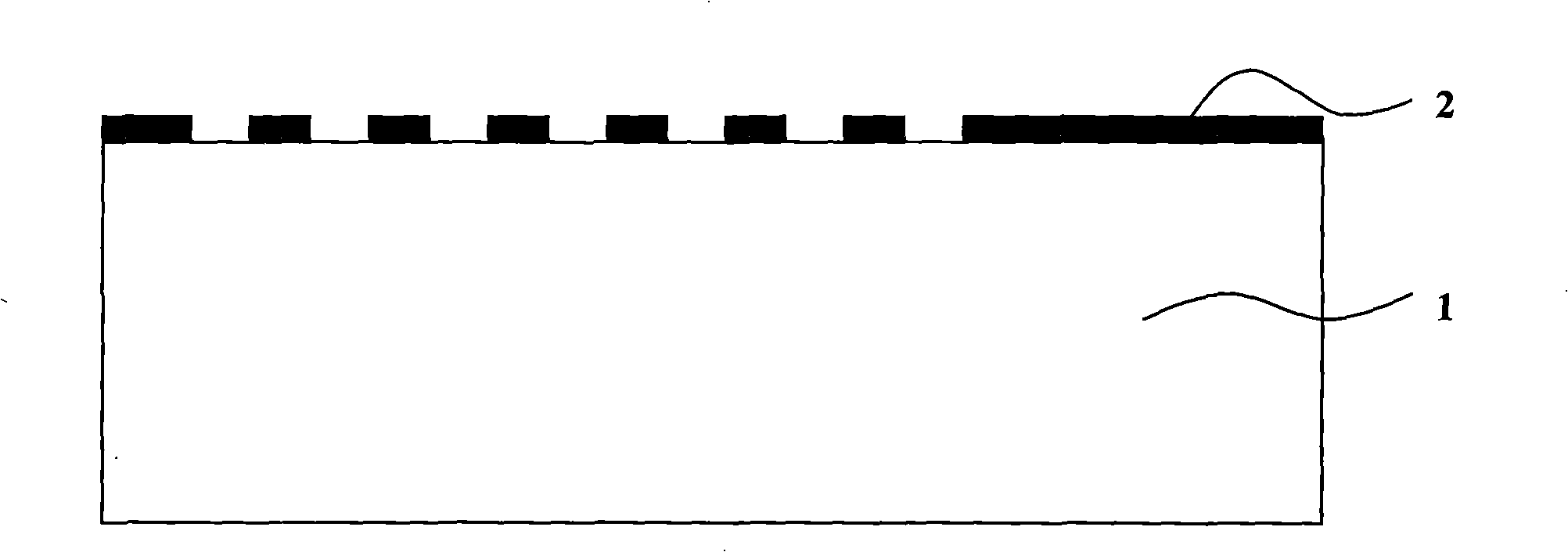

[0060] a. Apply photoresist on the back of the top layer of silicon 1, and photoresist to form a photoresist mask 2, the photoresist mask 2 located below the source region and the channel region will continuously cover the back of the top layer of silicon 1, and the rest of the photoresist The mask 2 intermittently covers the back side of the top layer silicon 1, the back side of the top layer silicon 1 refers to the surface where the top layer silicon 1 is in contact with the dielectric buried layer, and the thickness of the photoresist mask 2 is 0.5-1.5 μm;

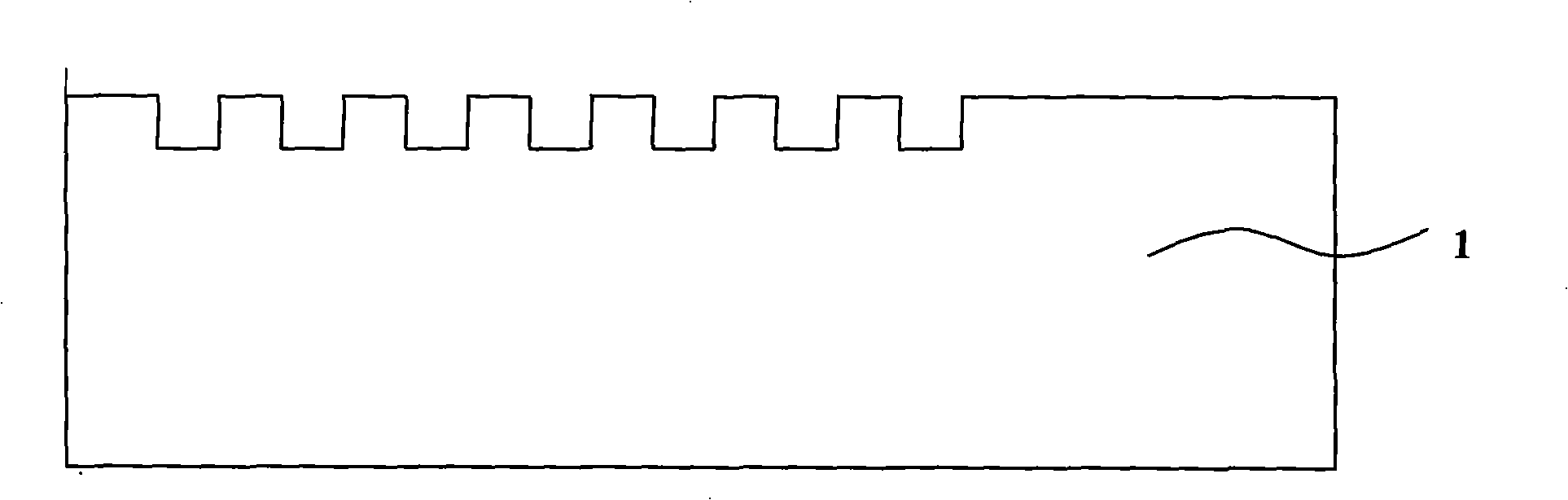

[0061] b. Remove the silicon not covered by the photoresist mask 2 on the back of the top layer of silicon 1 by dry etching to form a silicon groove with a depth of 200-2000nm, and then remove the mask;

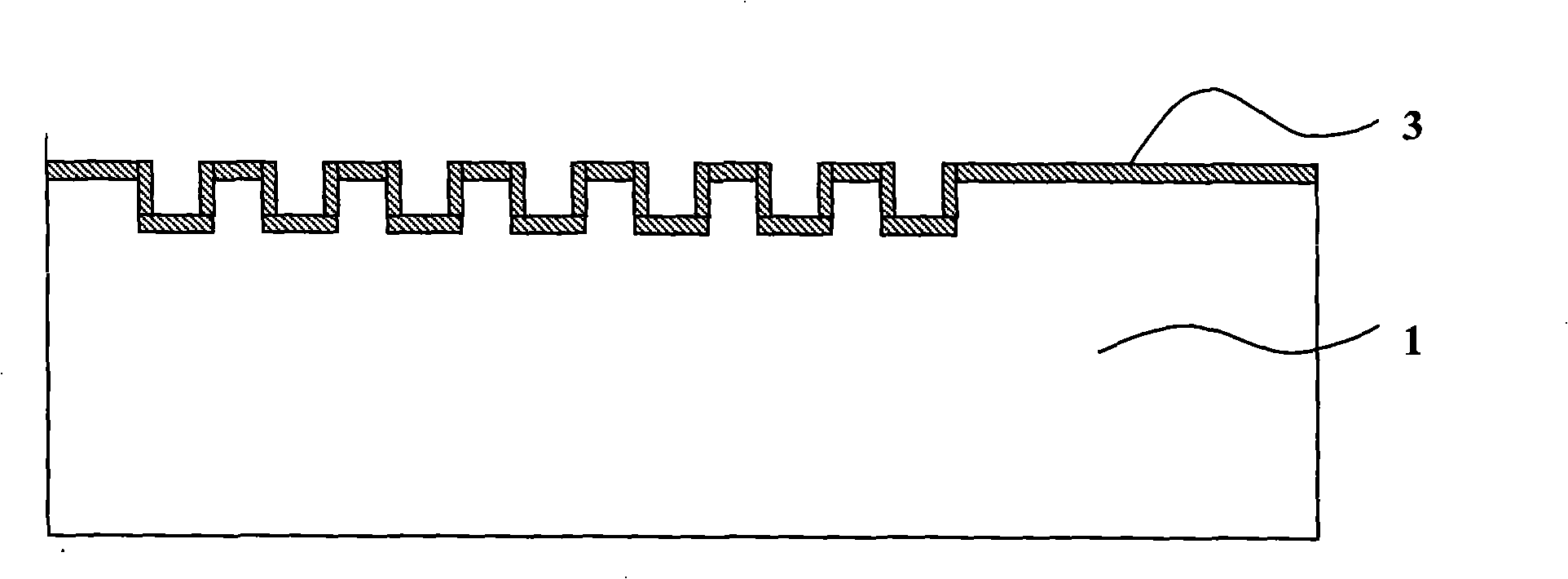

[0062] c. A thin layer of...

Embodiment 2

[0073] A more preferred embodiment of the present invention is: on the basis of Example 1, in step d, SiO is deposited first and then densified. 2layer, the densification temperature is 850-1000°C, and the densification time is 0.5-2 hours.

Embodiment 3

[0075] On the basis of Example 1, another more preferred embodiment of the present invention is if required SiO 2 If the layer is thicker (>600nm), SiO is formed by densification after multiple depositions. 2 layer, the deposition temperature is still 700-900°C, each deposition is 200nm-600nm, the densification temperature is 850-1000°C, and the densification time is 0.5-2 hours.

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More