Preparation method for semiconductor power device structure, and structure

A technology of power devices and semiconductors, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, transistors, etc., can solve the problems of long turn-off time of devices and affect the high-frequency performance of devices, so as to improve device performance, reduce on-resistance, The effect of increasing the effective concentration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

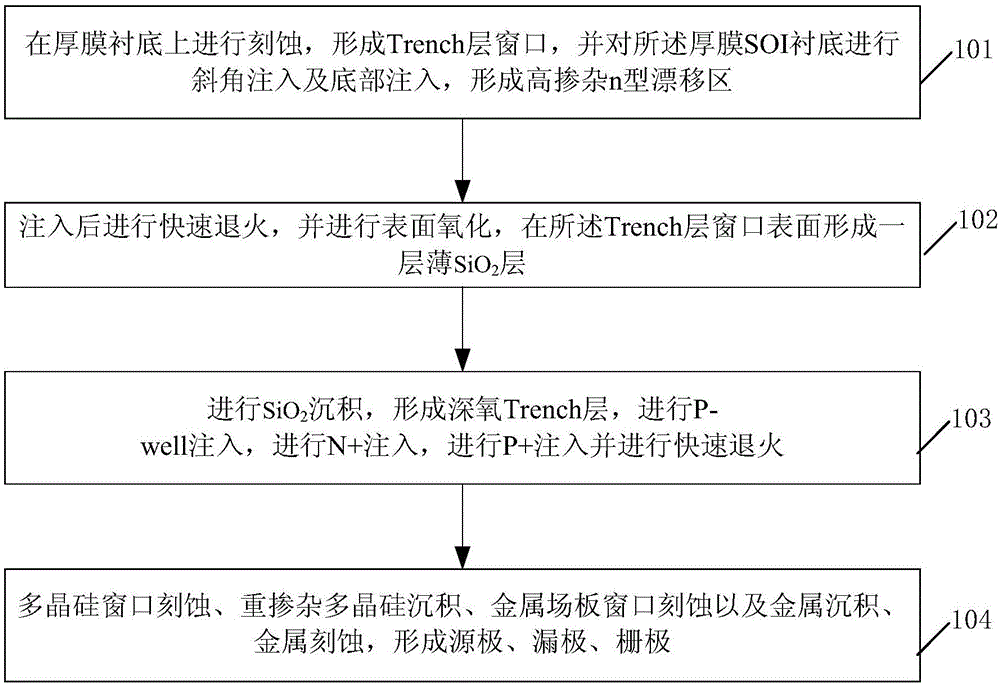

[0028] refer to figure 1 , figure 1 It is a schematic flow chart of a method for preparing a semiconductor power device structure according to an embodiment of the present invention.

[0029] In Embodiment 1, the preparation method of the semiconductor power device structure includes:

[0030] Step 101, performing etching on the thick-film SOI substrate to form a Trench layer window, and performing oblique angle implantation and bottom implantation on the thick-film SOI substrate to form a highly doped n-type drift region;

[0031] Step 102, perform rapid annealing after implantation, and perform surface oxidation to form a thin layer of SiO on the surface of the Trench layer window 2 layer;

[0032] Step 103, carry out SiO 2 Deposition, formation of deep oxygen trench layer, P-well implantation, N+ implantation, P+ implantation and rapid annealing;

[0033] Step 104, polysilicon window etching, heavily doped polysilicon deposition, metal field plate window etching, metal...

Embodiment 2

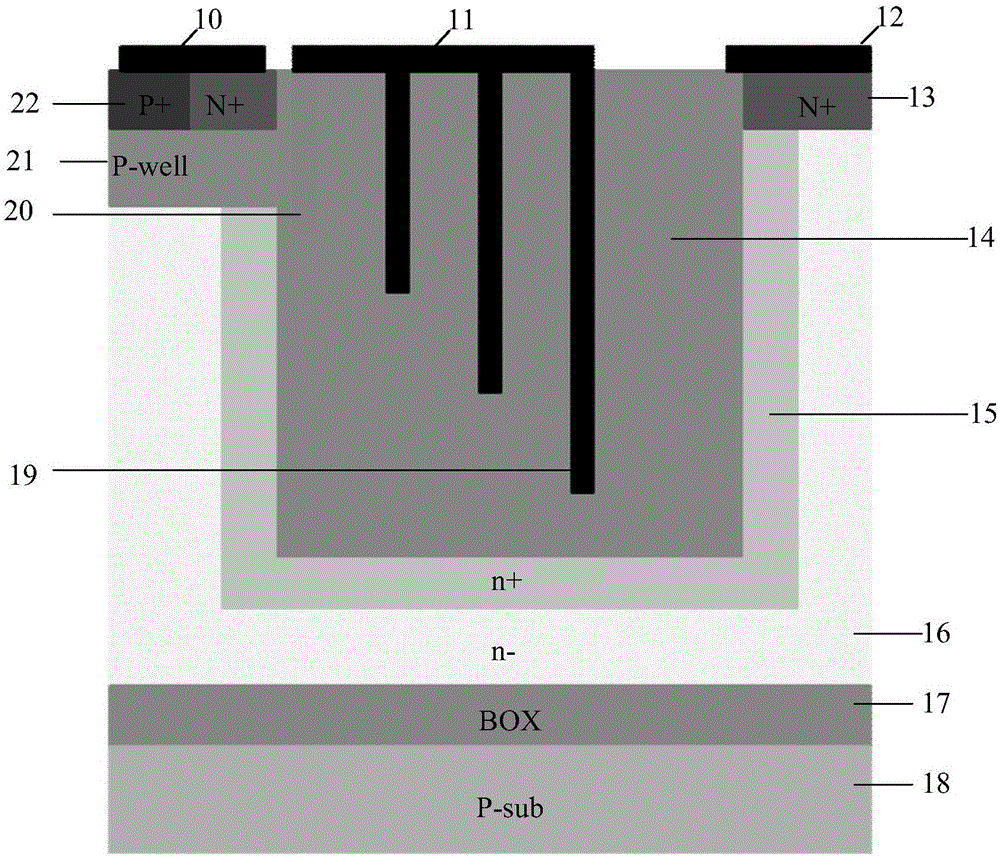

[0050] refer to figure 2 , figure 2 It is a schematic diagram of the structure of the semiconductor power device of the embodiment of the present invention.

[0051] In Embodiment 2, the semiconductor power device structure includes:

[0052] Source, source metal, gate metal, drain, drain metal, source body region, polysilicon, metal field plate, N-type heavily doped region, oxygen Trench layer, N-type drift region, buried oxide layer, P-type lining end;

[0053] The P-type substrate is on the bottom layer of the semiconductor power device structure, the buried oxide layer is on the P-type substrate, the N-type drift region is on the buried oxide layer, and the N-type The heavily doped region is above the N-type drift region, the oxygen Trench layer is above the N-type heavily doped region, and the metal field plate is a vertical field plate with multiple layers of different lengths. A heavily doped n-type layer is injected into the N-type drift region near the surface o...

Embodiment 3

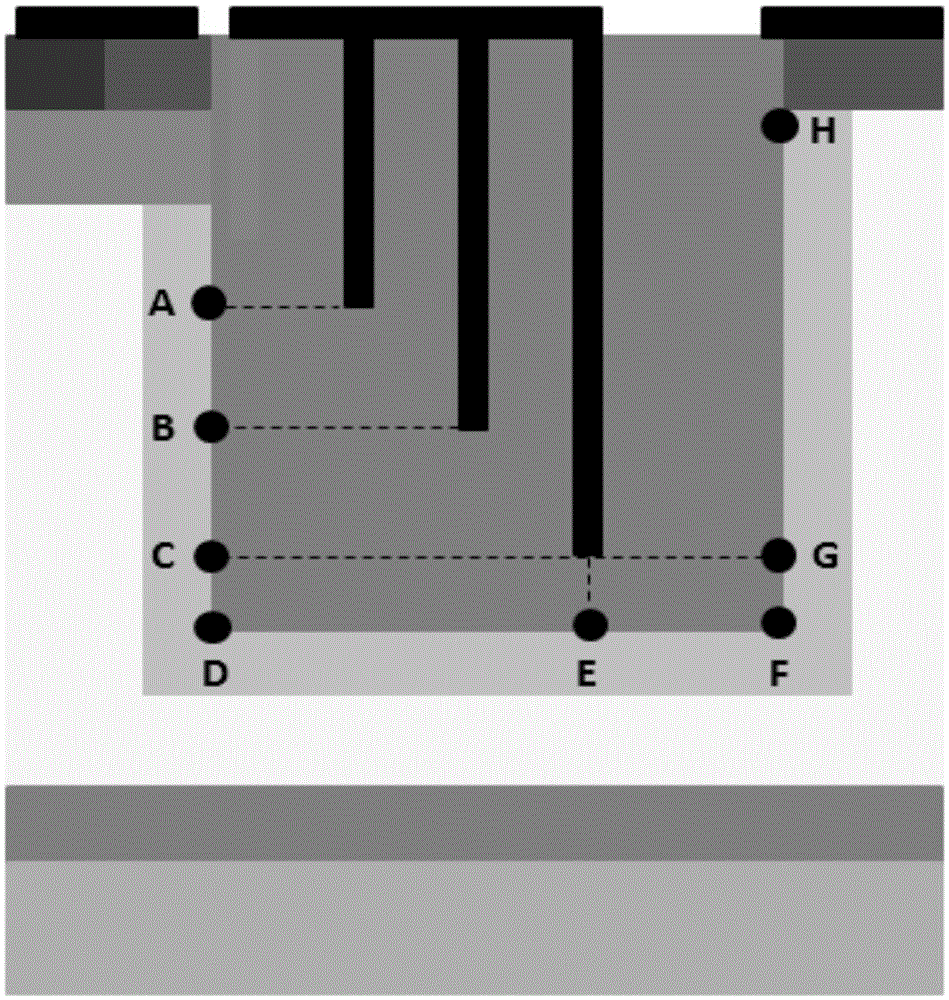

[0058] refer to image 3 , image 3 It is another schematic diagram of the structure of the semiconductor power device of the embodiment of the present invention.

[0059] Figure 4 It is a schematic diagram of the electric field of a semiconductor power device according to an embodiment of the present invention.

[0060] Specifically, the breakdown voltage of the LDMOS structure of a lateral power device is determined by both the lateral withstand voltage and the vertical withstand voltage, and within a certain range, the lateral withstand voltage of the device is proportional to the length of the drift region and inversely proportional to the doping concentration of the drift region , while the on-resistance of the device is just the opposite. Therefore, there is a contradictory relationship between the breakdown voltage and the on-resistance of the lateral power device.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More