Dual-Gated Group III-V Merged Transistor

a transistor and gate technology, applied in the field of group iiv, can solve the problems of depletion mode or enhancement mode group iii-v devices being susceptible to voltage breakdown

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015]The following description contains specific information pertaining to implementations in the present disclosure. One skilled in the art will recognize that the present disclosure may be implemented in a manner different from that specifically discussed herein. The drawings in the present application and their accompanying detailed description are directed to merely exemplary implementations. Unless noted otherwise, like or corresponding elements among the figures may be indicated by like or corresponding reference numerals. Moreover, the drawings and illustrations in the present application are generally not to scale, and are not intended to correspond to actual relative dimensions.

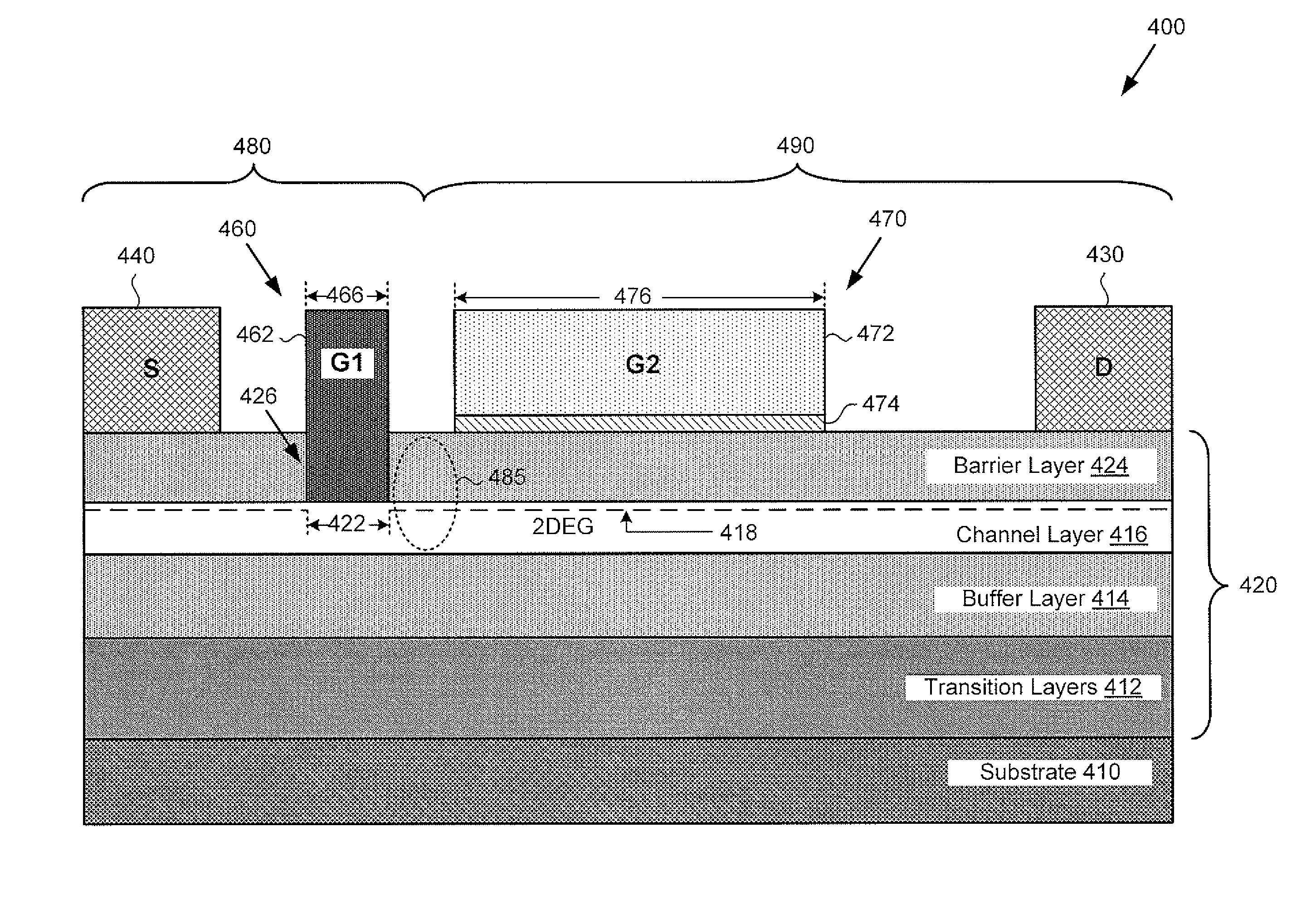

[0016]FIG. 1 shows a cross-sectional view of a dual gated merged III-Nitride transistor according to a conventional implementation. Dual gated merged transistor 100 includes support body 102, channel layer 104, barrier layer 108 overlying channel layer 104, drain electrode 130, source electrode 140,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More