Semiconductor device with dual-mosaic structure and forming method thereof

A dual damascene structure and semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problems that cannot meet the requirements of 45nm and below process nodes, and achieve the effect of reducing the k value

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

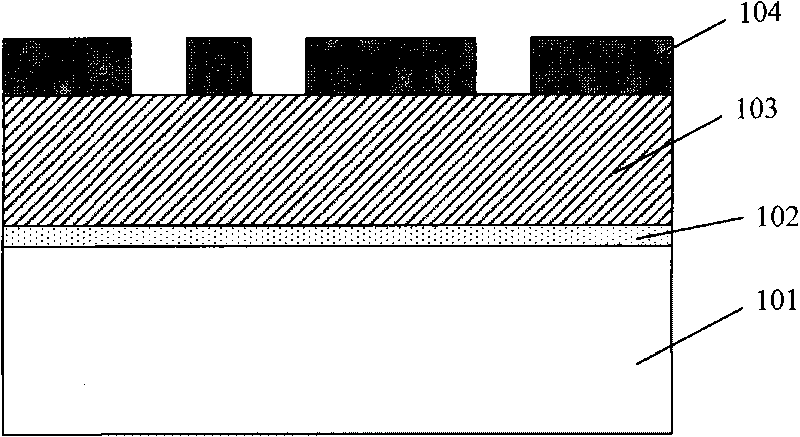

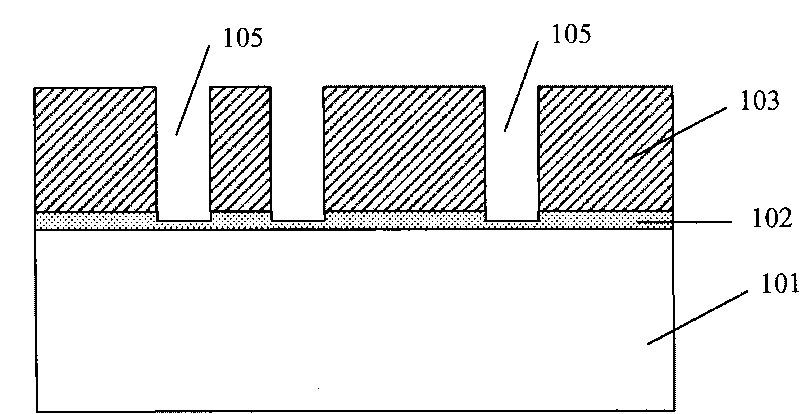

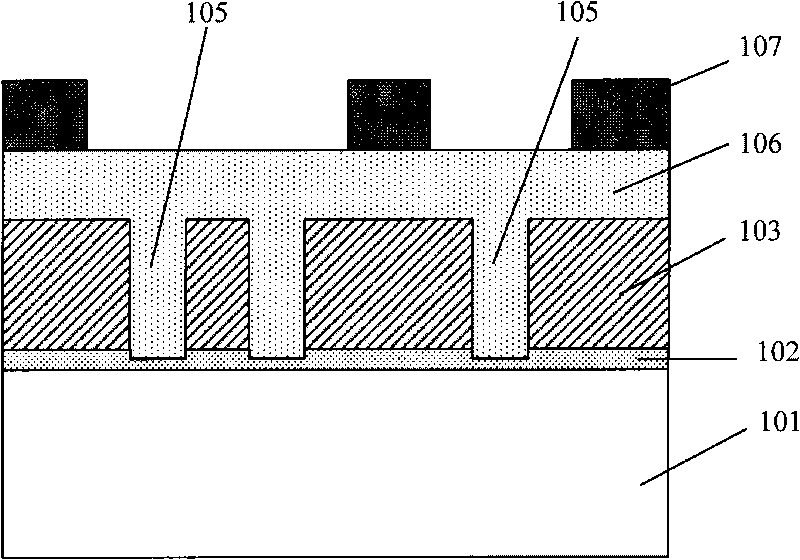

[0048] In order to make the above objects, features and advantages of the present invention more comprehensible, specific implementations of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0049] The processing method of the present invention can be widely used in various fields, and can utilize many suitable materials to make, and the following is to illustrate by specific embodiment, certainly the present invention is not limited to this specific embodiment, in this field Common replacements known to those of ordinary skill undoubtedly fall within the protection scope of the present invention.

[0050]Secondly, the present invention is described in detail using schematic diagrams. When describing the embodiments of the present invention in detail, for the convenience of explanation, the cross-sectional view showing the device structure will not be partially enlarged according to the general scale, which should not be us...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More