Method for reducing RC delay of integrated circuit

A technology for integrated circuits and low dielectric constant materials, which is applied in the field of reducing the RC delay of integrated circuits, and can solve the problems of increasing the k value and large k value of the latter dielectric material

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] In order to make the content of the present invention clearer and easier to understand, the content of the present invention will be described in detail below in conjunction with specific embodiments and accompanying drawings.

[0017] Figure 2 to Figure 6 Each step of the method for reducing the RC delay of an integrated circuit according to a preferred embodiment of the present invention is schematically shown.

[0018] Specifically, as Figure 2 to Figure 6 As shown, the method for reducing the RC delay of an integrated circuit according to a preferred embodiment of the present invention includes:

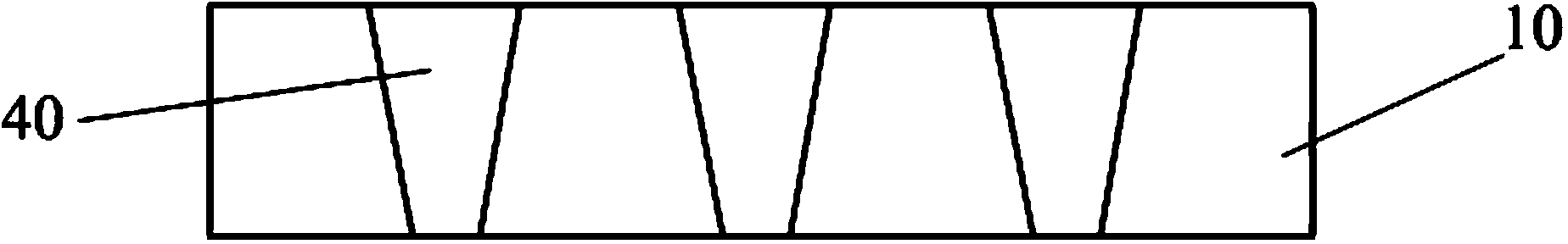

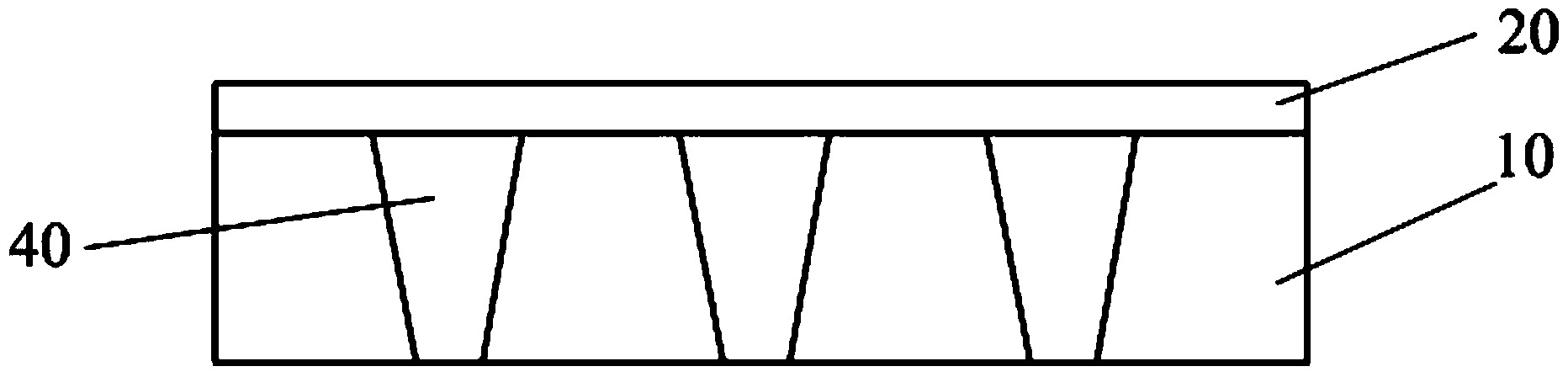

[0019] A copper interconnection structure 40 is formed in the porous low dielectric constant material 10, and the copper interconnection structure 40 is subjected to chemical mechanical polishing planarization treatment, such as figure 2 shown; for example, low-k materials have a k between 2.0-3.0.

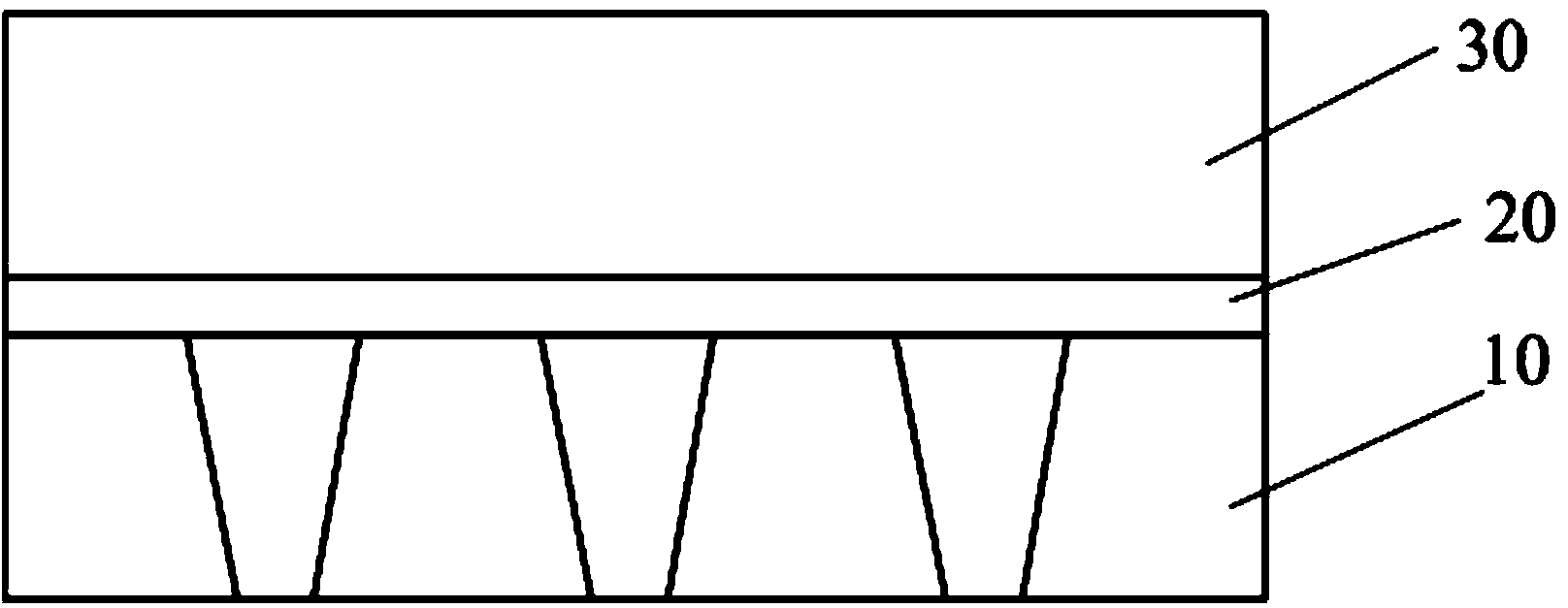

[0020] A copper diffusion dielectric barrier layer (for example, a ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More