Integration technology of copper and low K dielectric material

A dielectric material and process technology, which is applied in the field of integration technology of copper and low-K dielectric materials, can solve problems such as difficult to achieve effective integration of copper and low-K dielectric materials, increase of K value of dielectric materials, damage of dielectric materials, etc., to achieve improved Hole rate, reduce K value, avoid damage effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] In order to describe the technical content, achieved goals and effects of the present invention in detail, the following will be described in detail in conjunction with the embodiments and accompanying drawings.

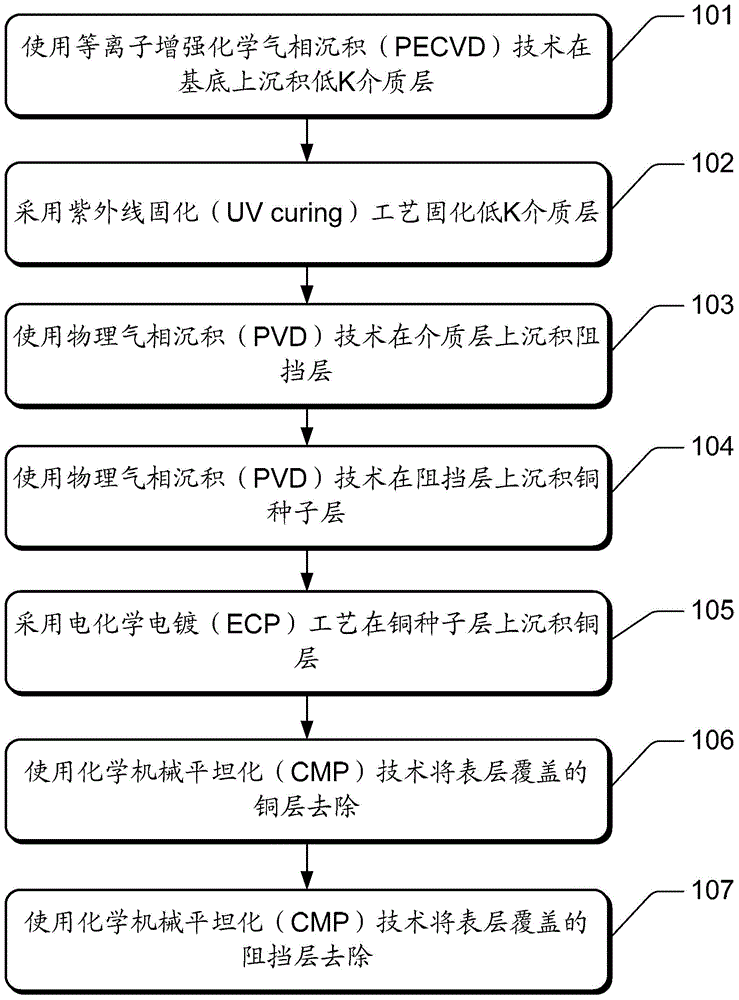

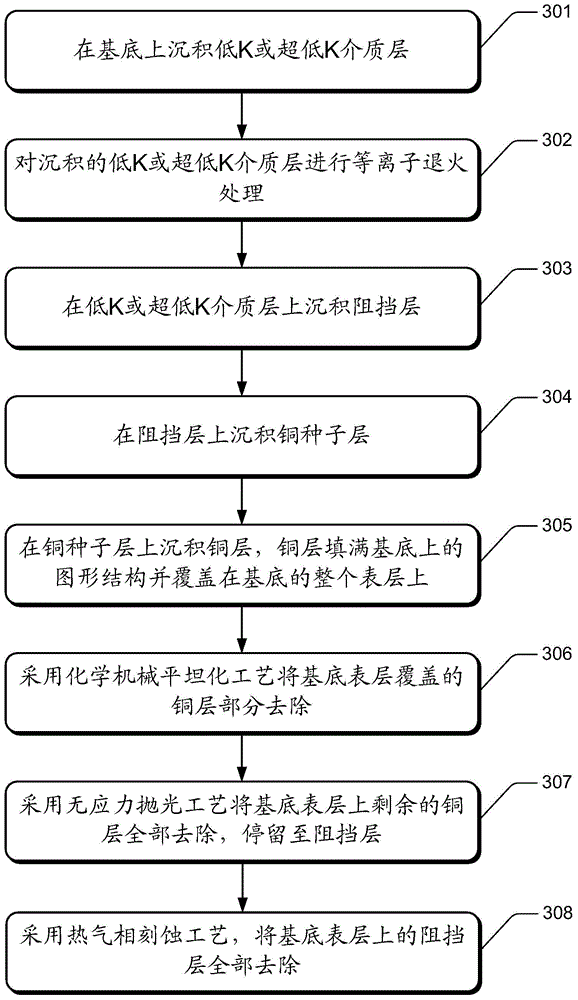

[0026] refer to image 3 and combine figure 2 As shown, an integration process of copper and low-K dielectric material disclosed by the present invention includes the following steps:

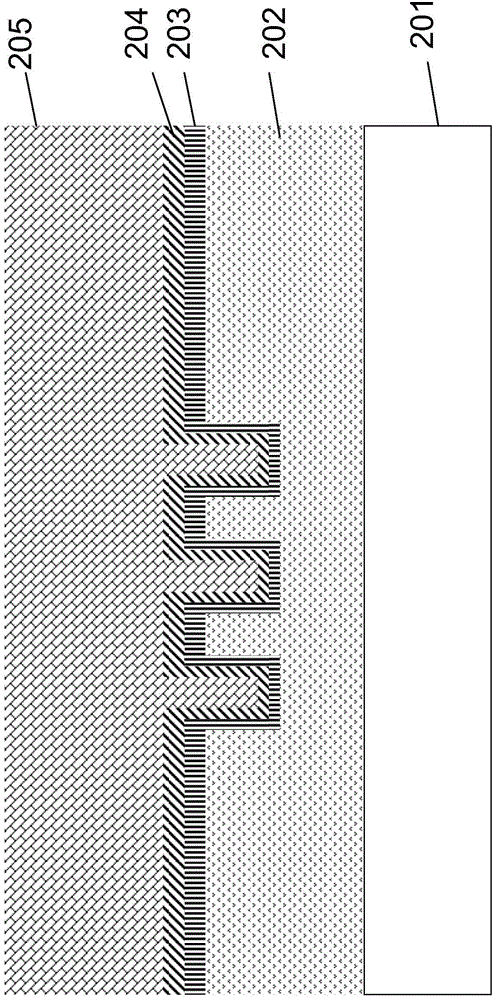

[0027] Step 301: Deposit a low-K or ultra-low-K dielectric layer 202 on the substrate 201, the K value of the low-K dielectric layer is less than 2.5, and the K value of the ultra-low-K dielectric layer is less than 2. Specifically, a low-K or ultra-low-K dielectric layer 202 is deposited on the substrate 201 by plasma enhanced chemical vapor deposition (PECVD), and the low-K or ultra-low-K dielectric layer 202 contains a sacrificial porogen.

[0028] Step 302: Perform plasma annealing (Plasma Anneal) on the deposited low-K or ultra-low-K dielectric layer 202, specifically, ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Wavelength | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More