Patents

Literature

64results about How to "Increase K value" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

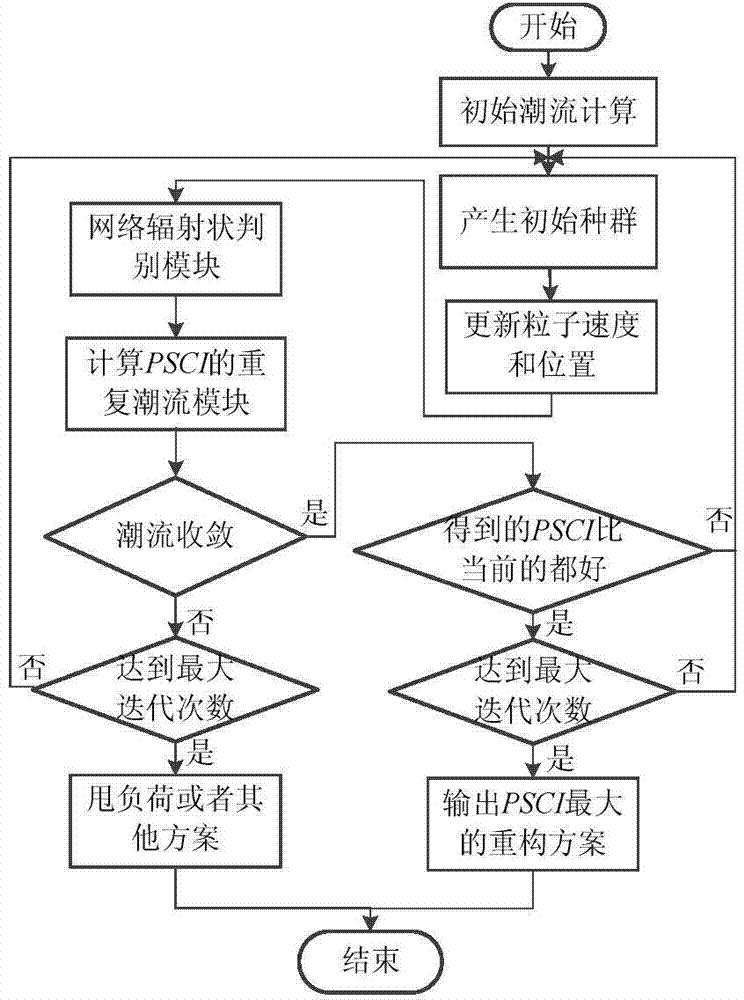

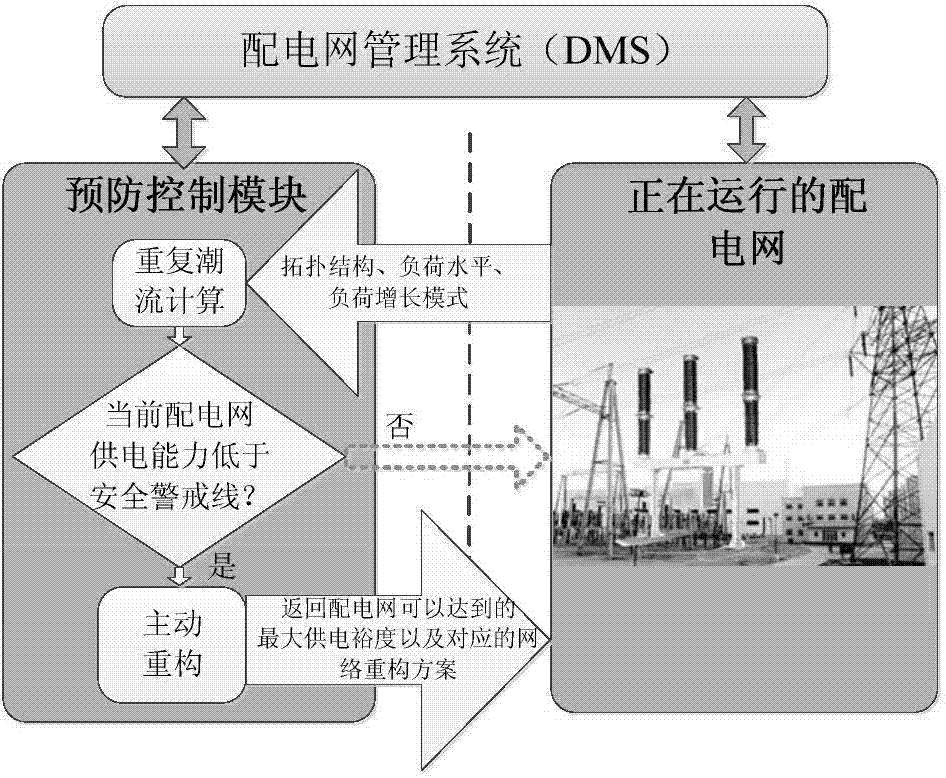

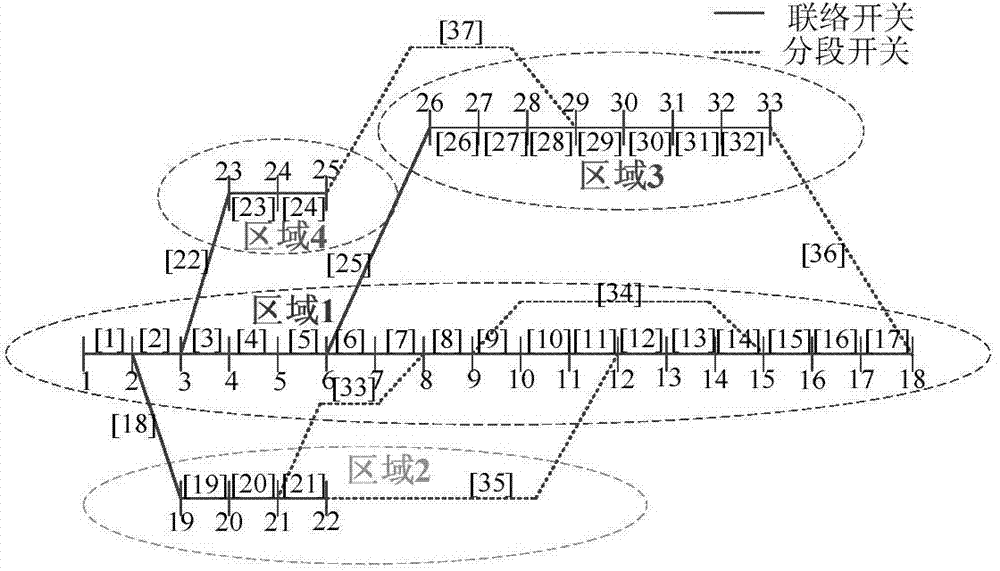

Active reconfiguration strategy of distribution network and preventing control method thereof

InactiveCN103779861AGuaranteed economyEnsure safetyData processing applicationsSystems intergating technologiesShort termsPrevention control

The present invention relates to a safe operation and prevention control technique of an active distribution network, wherein preventive control is performed through optimizing a network structure for satisfying a safe margin requirement in operation of the distribution network, thereby effectively improving operation reliability of the distribution network; and simultaneously operation and short-term planning of the distribution network are guided for realizing higher economic benefit and social benefit. For this purpose, the technical solution adopted in the active reconfiguration strategy of the invention is characterized in that the active reconfiguration strategy of the distribution network and the preventing control method comprise the steps of: firstly, establishing a maximal power supply capability evaluating index which is adapted for the active distribution network; when the maximal power supply capability index of the distribution network is lower than a system safe guard line, performing active reconfiguration of the distribution network for achieving multiple targets of improving the maximal power supply capability index and minimizing number of times of operating a network reconfiguration switch; and if the maximal power supply capability index of the distribution network in the current operation manner is lower than a preset safe guard line, starting an active reconfiguration module for performing network optimizing reconfiguration. The active reconfiguration strategy of the distribution network and the preventing control method according to the invention are mainly applied for safe operation and preventing control of the distribution network.

Owner:TIANJIN UNIV

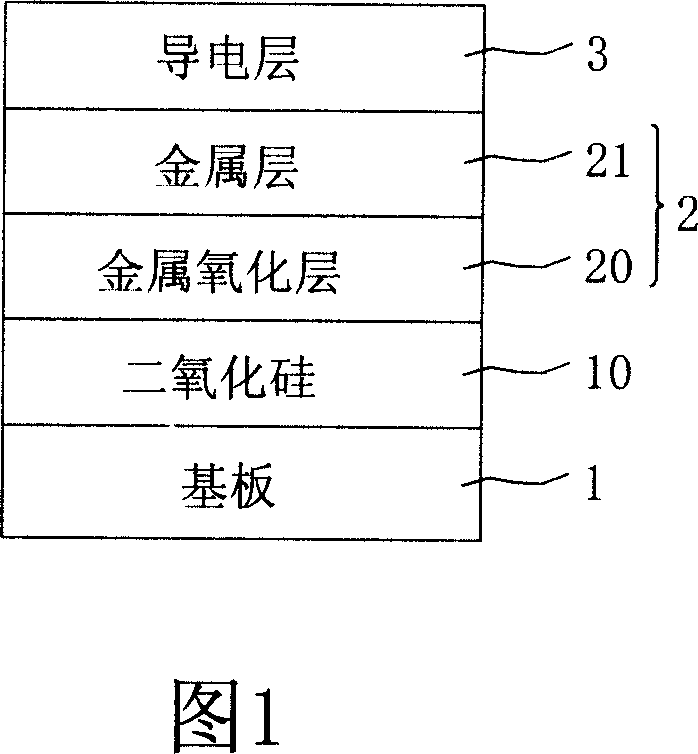

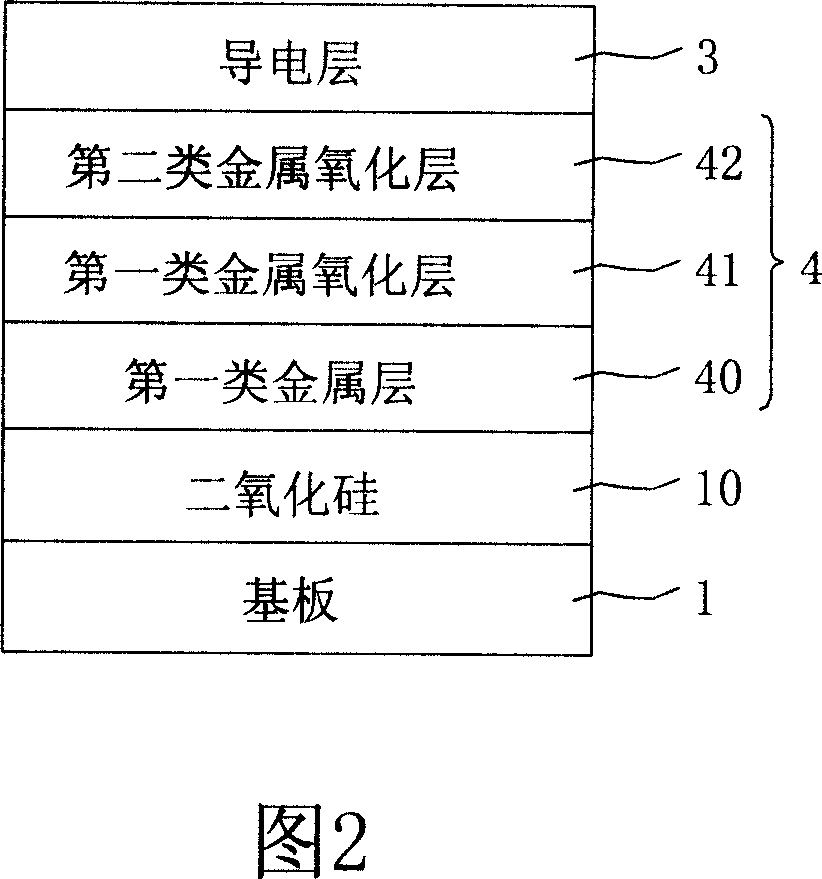

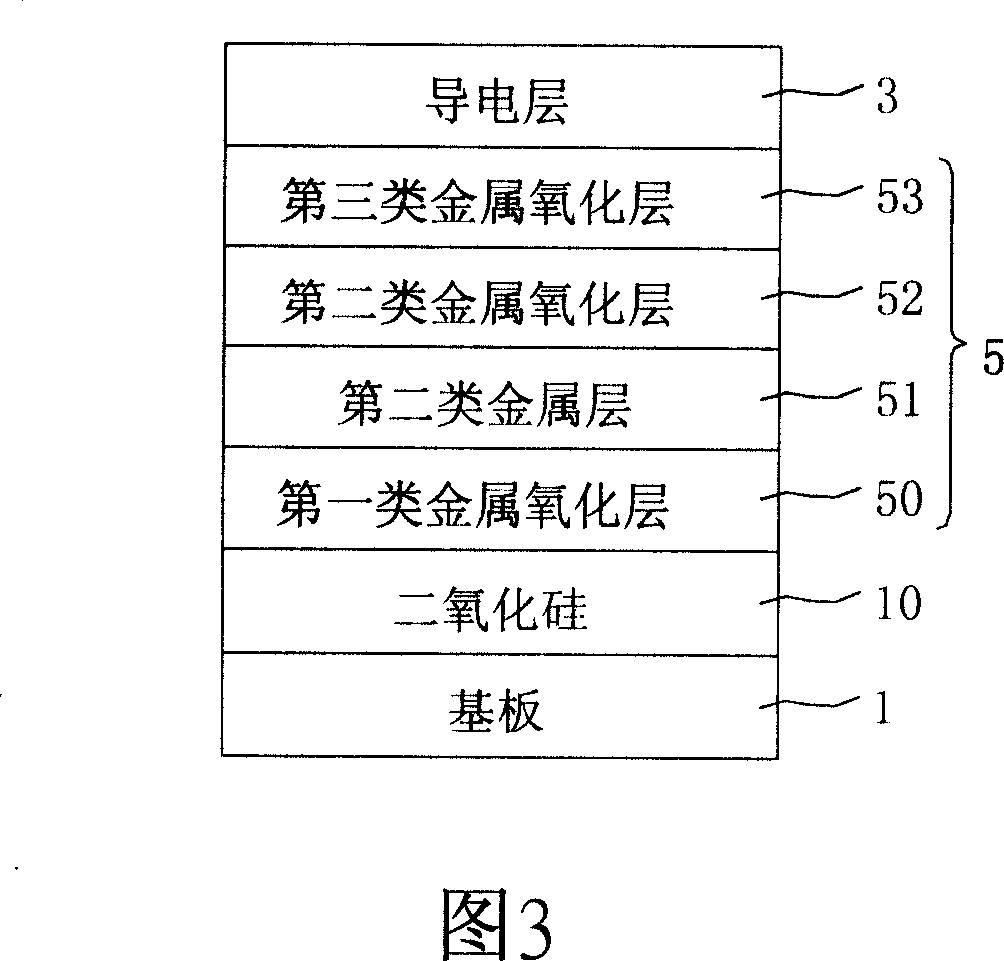

Semiconductor structure and mfg. method thereof

InactiveCN1949532AReduce thicknessCompliant with manufacturing processSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureInterface layer

The invention relates to a semiconductor structure and the making method, especially relating to an interface layer applied to transistor grid, namely high-dielectric constant semiconductor stacked structure and the making method thereof, using on-HfO2 Ti to absorb oxygen atoms on the interface layer so as to reduce the thickness of the interface layer until no interface layer. And the growth of TiO2 on Ti can help follow-up HfO2 growth. Besides, TiO2 dielectric constant is about 50, able to largely increase equivalent dielectric constant of grid dielectric layer. It can absorb oxygen by Ti to reduce Ti thickness, increase k value and reduce EOT. In addition, after heat treatment, the formed TiO2 can increase k value, too. And in TiO2, leakage current can not leap. And the invention can speed up application of high-dielectric constant grid dielectric and provide a space for future EOT sustained reduction.

Owner:IND TECH RES INST

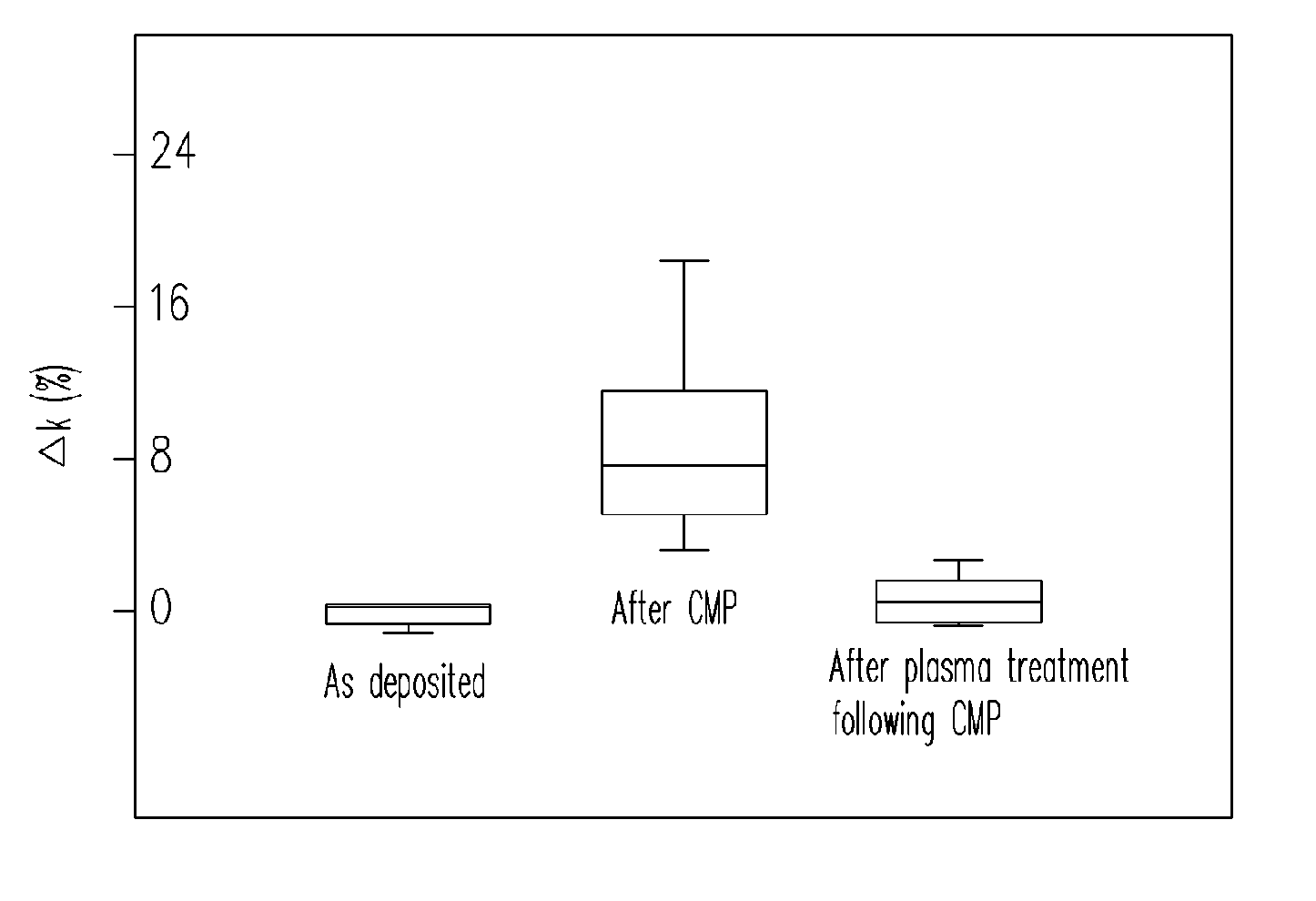

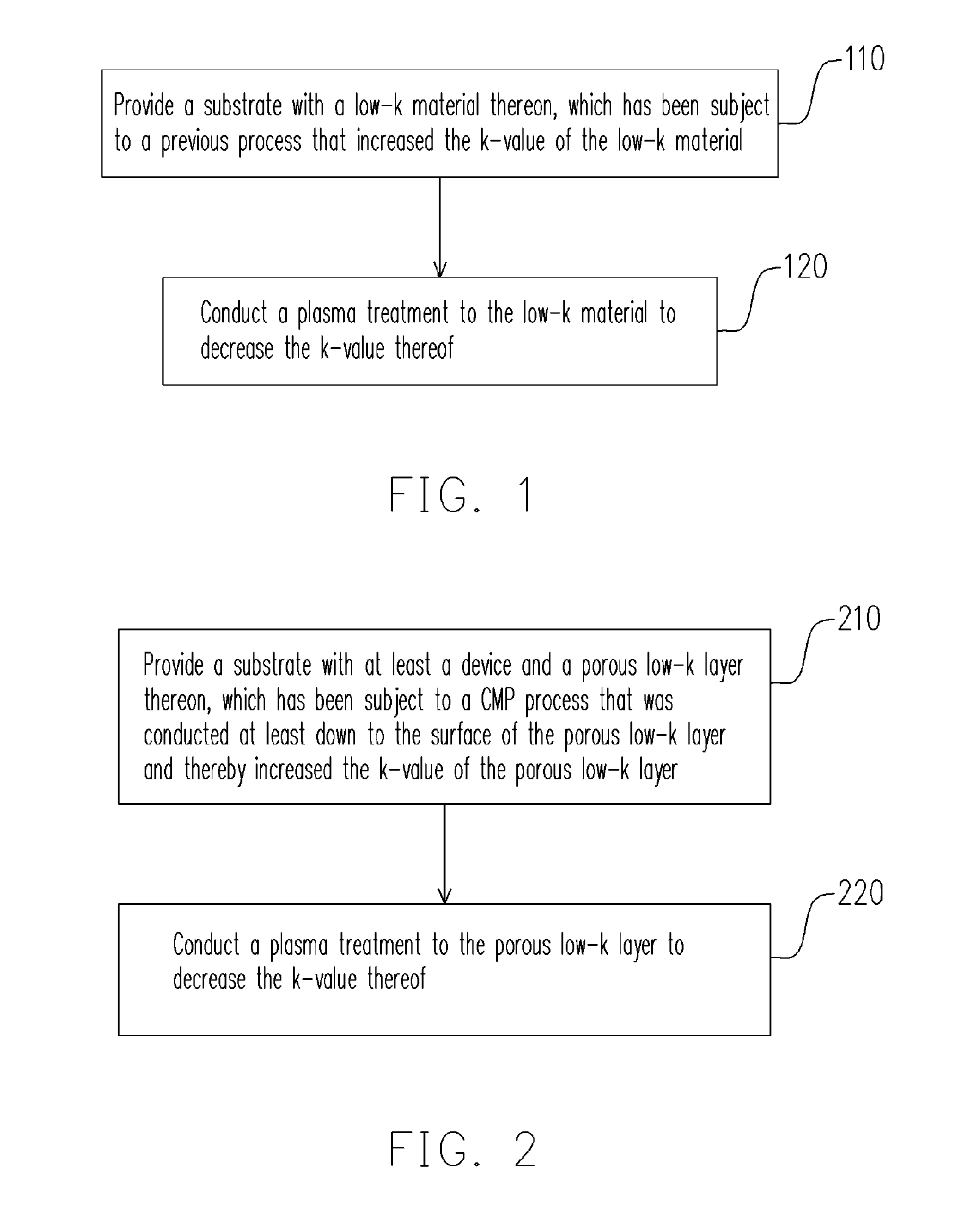

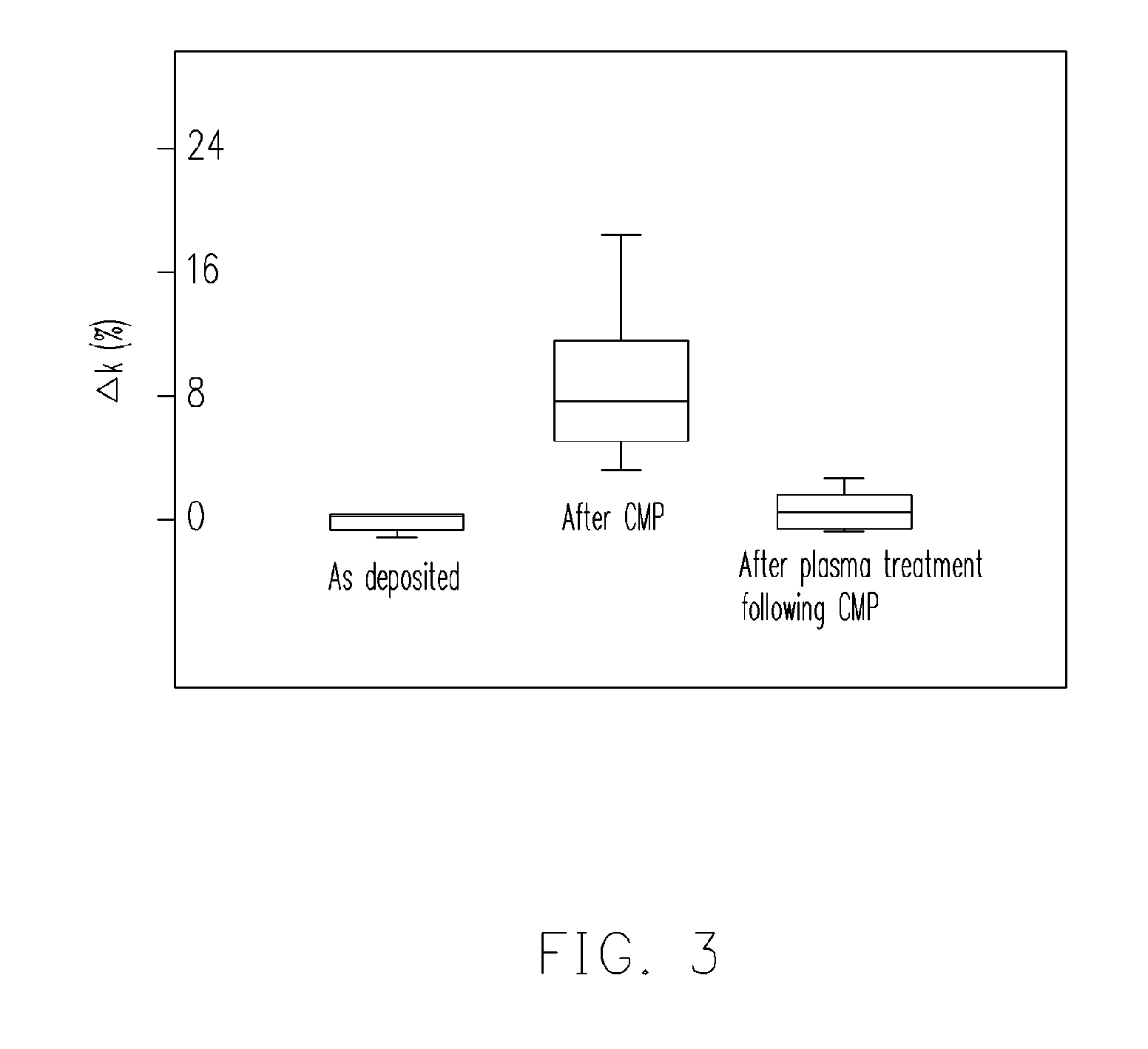

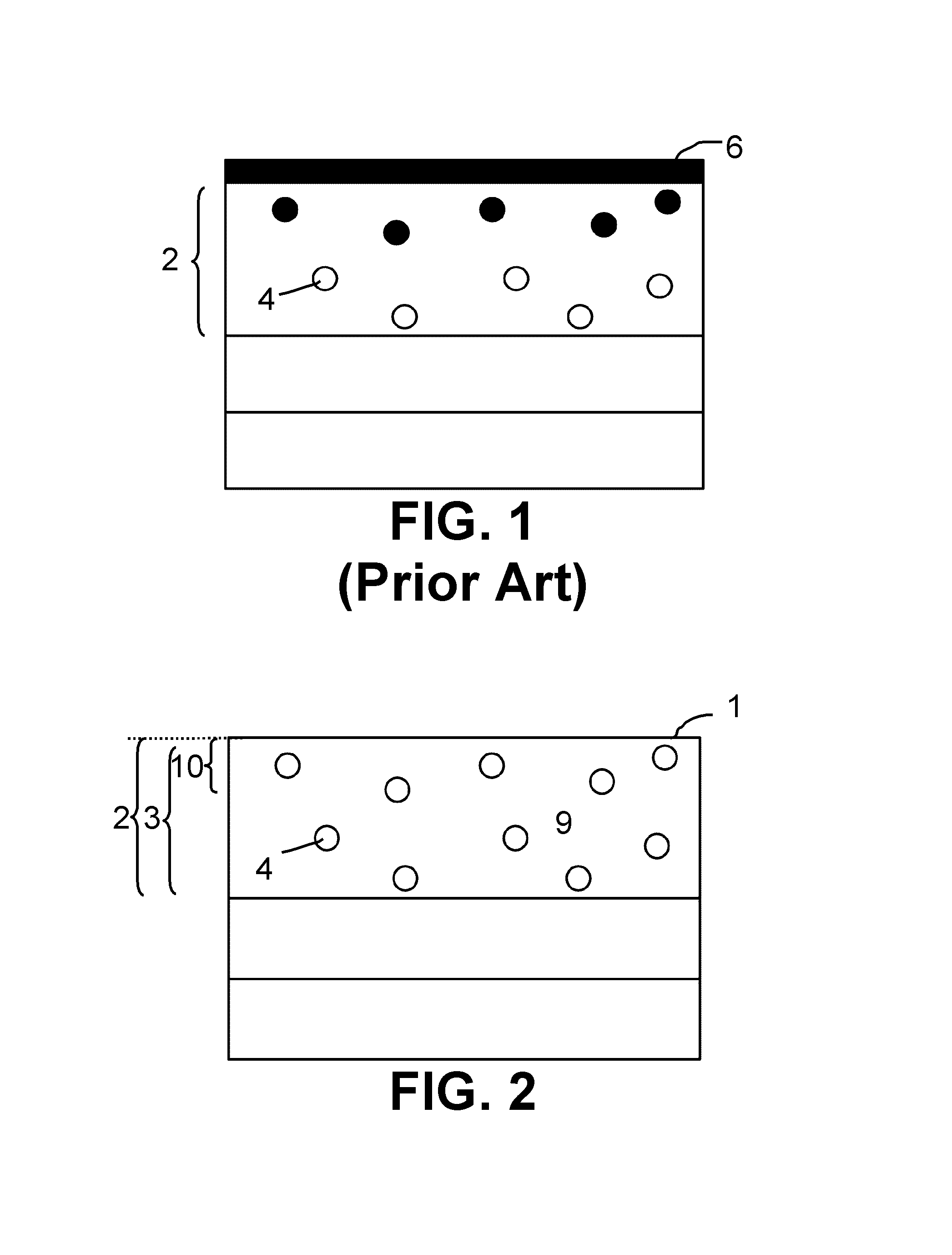

Method of restoring low-k material or porous low-k layer

InactiveUS20070077751A1Lower the k-value of the low-k materialLower the k-value of the porous low-k layerSemiconductor/solid-state device manufacturingPlasma treatmentComposite material

A method of restoring a low-k material is described, applied to a substrate with a low-k material thereon, wherein the substrate has been subject to a previous process that raised the k-value of the low-k material. The method includes performing a plasma treatment to the low-k material to decrease the k-value thereof.

Owner:UNITED MICROELECTRONICS CORP

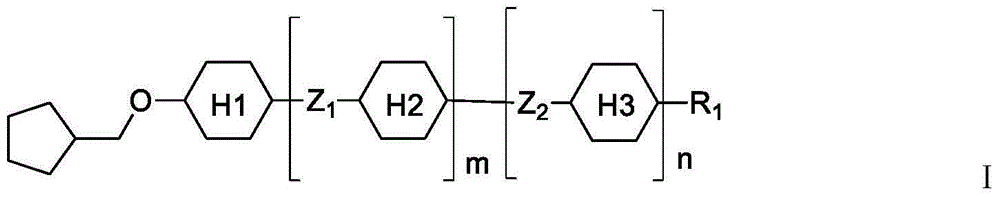

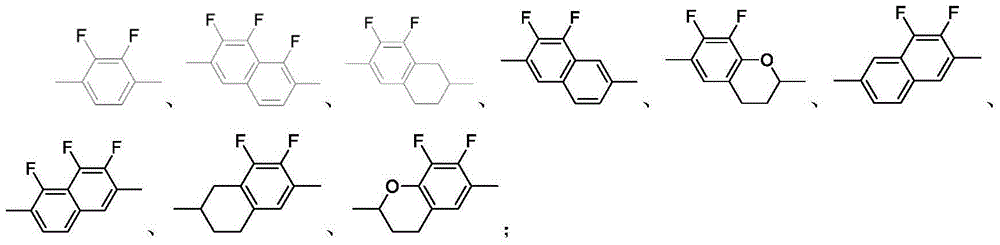

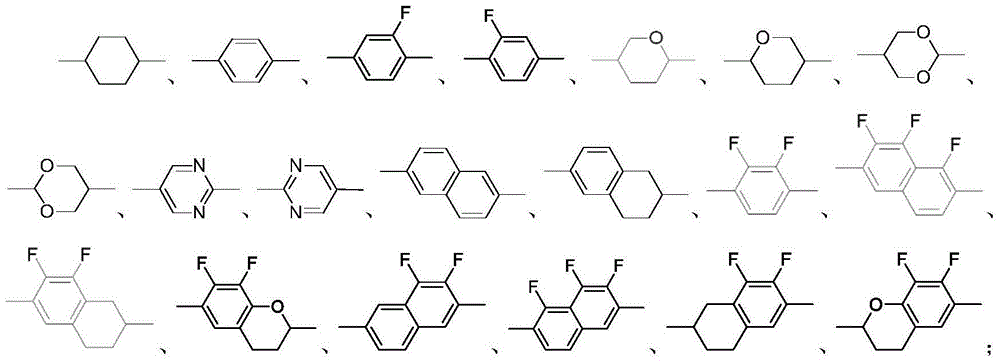

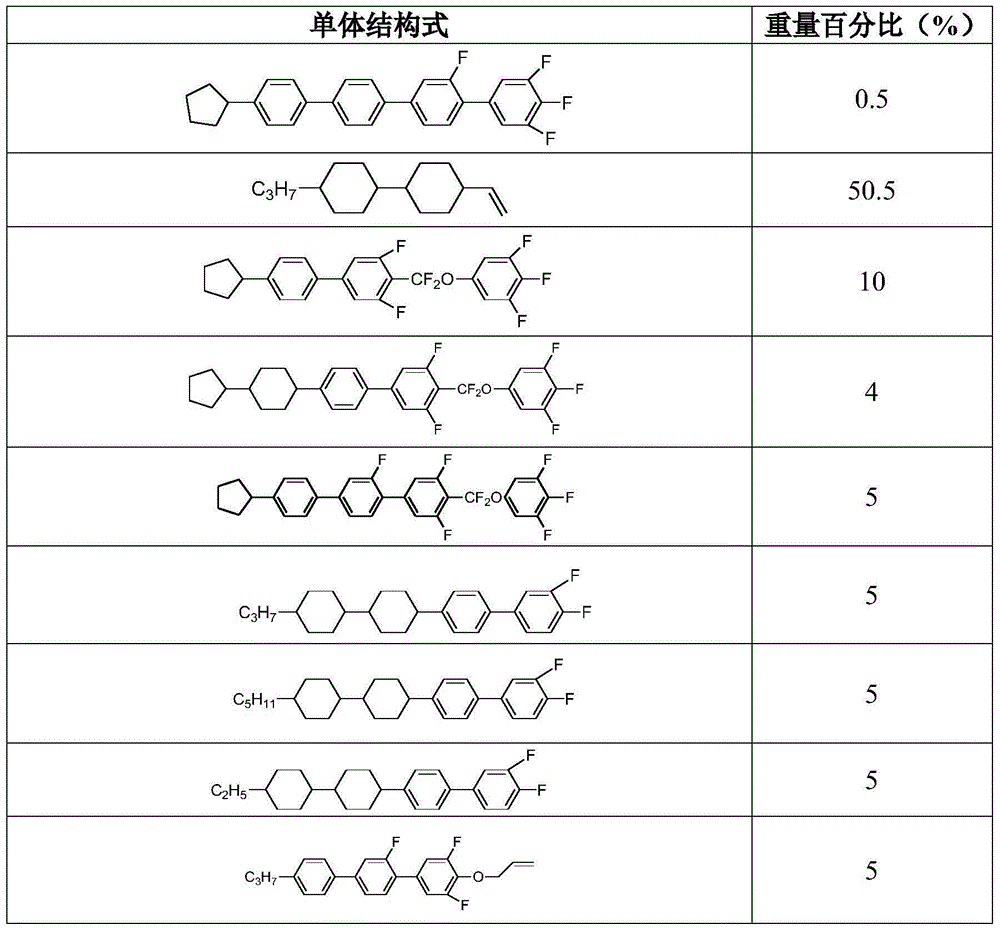

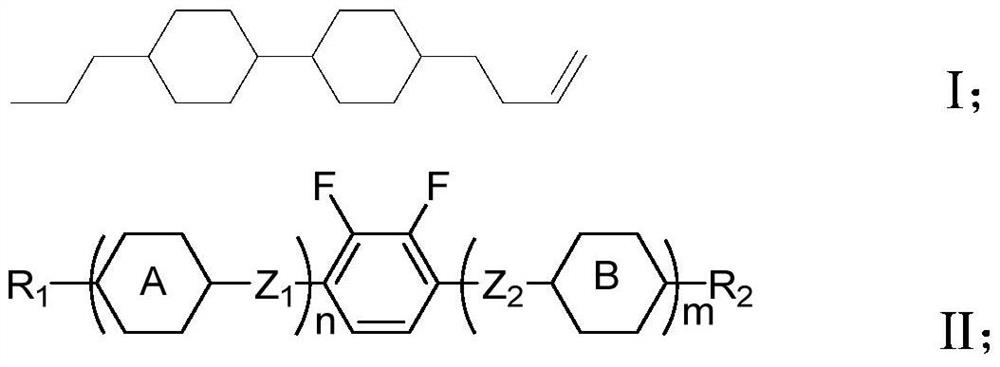

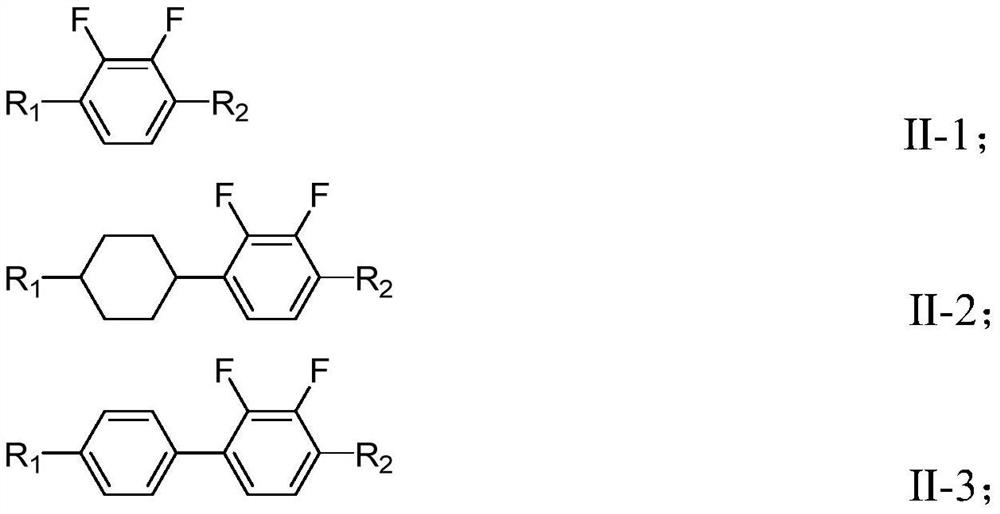

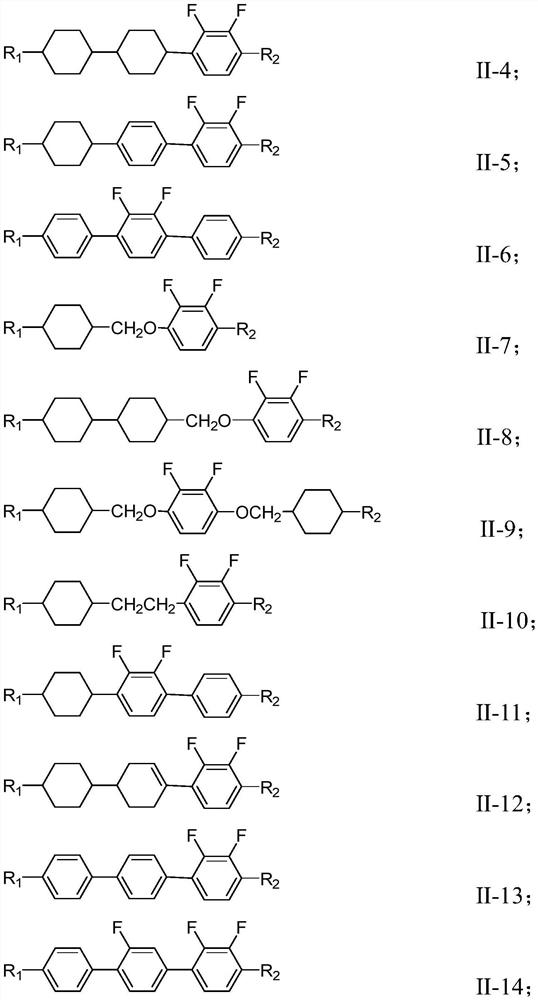

Liquid crystal compound and liquid crystal medium containing same

InactiveCN104628541AIncrease K valueAppropriate negative dielectric anisotropyLiquid crystal compositionsOrganic chemistryLiquid-crystal displayLiquid crystal

The invention relates to a negative dielectric liquid crystal compound containing a structural formula I and a liquid crystal medium of at least one compound containing the structural formula I and an electro-optical display containing the type of liquid crystal medium. The compound has high negative dielectric constant, relatively great K value and relatively low rotary viscosity and is suitable for quick-response VA liquid crystal and particularly suitable for VA-TFT and VA-IPS liquid crystal display.

Owner:SHIJIAZHUANG CHENGZHI YONGHUA DISPLAY MATERIALS CO LTD

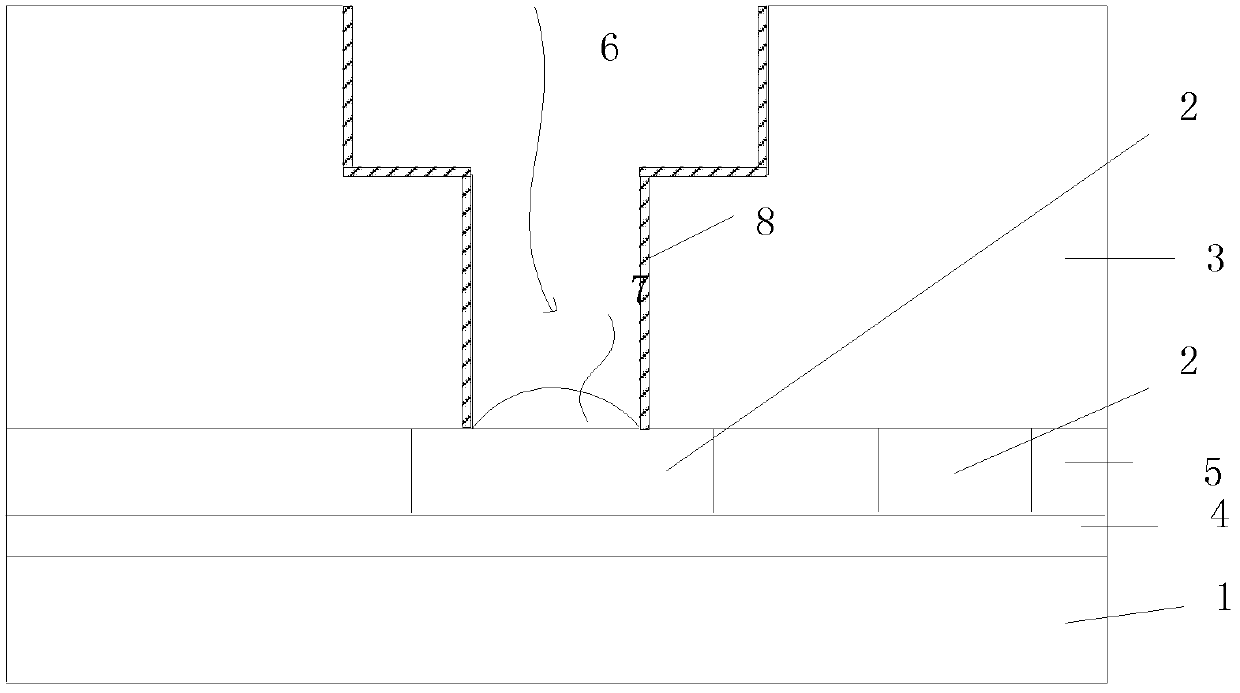

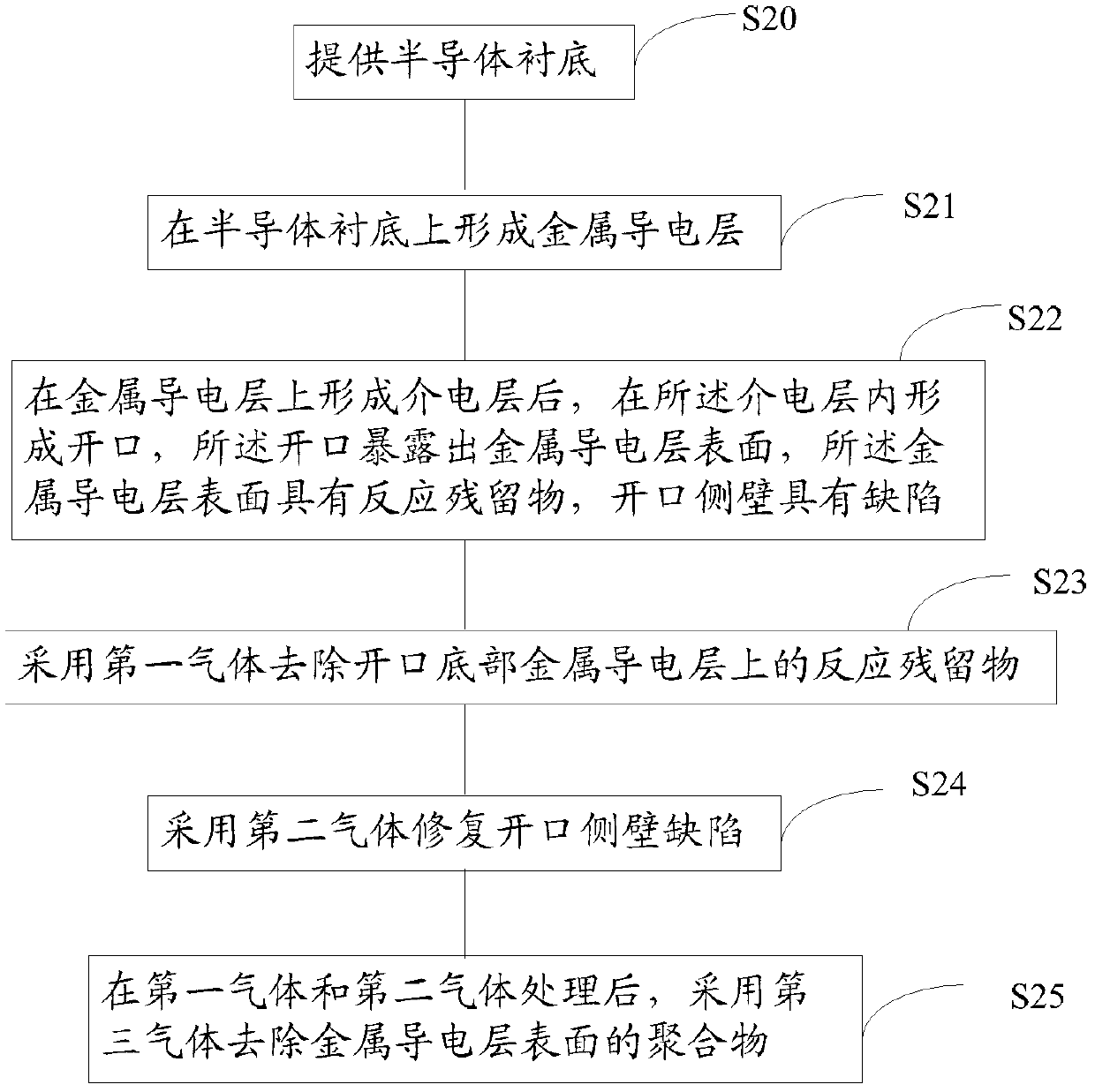

Method of forming opening

ActiveCN103377913AImprove yieldImprove reliabilitySemiconductor/solid-state device manufacturingAfter treatmentDielectric layer

Disclosed is a method of forming an opening. The method comprises the steps of providing a semiconductor substrate; forming a metal conductive layer on the semiconductor substrate; forming a dielectric layer on the metal conductive layer and forming an opening in the dielectric layer with the opening exposing a surface of the metal conductive layer, the surface of the metal conductive layer having a reaction residue and a side wall of the opening having a defect; removing the reaction residue on the metal conductive layer at the bottom of the opening by use of a first gas; repairing the defect on the side wall of the opening by use of a second gas; and removing, after treatment of the first gas and the second gas, a polymer on the surface of the metal conductive layer by use of a third gas. The method of forming the opening is used for improving electrical properties, stability and yield of an integrated circuit.

Owner:SEMICON MFG INT (SHANGHAI) CORP

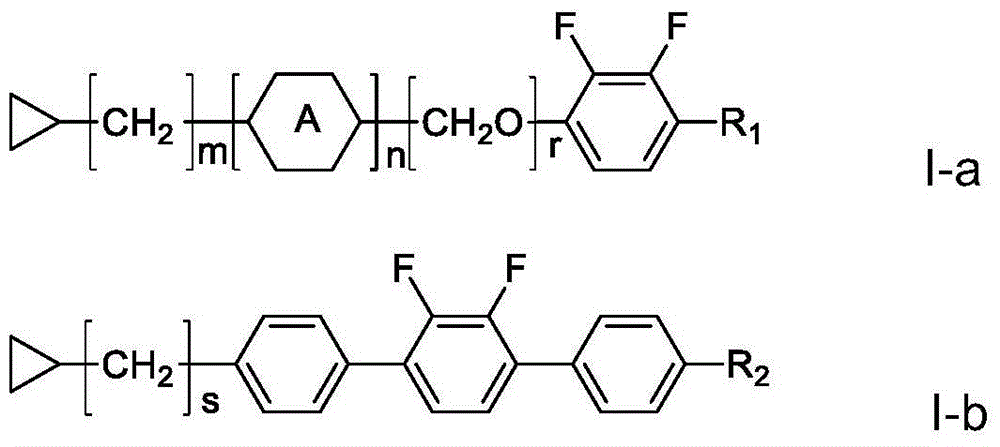

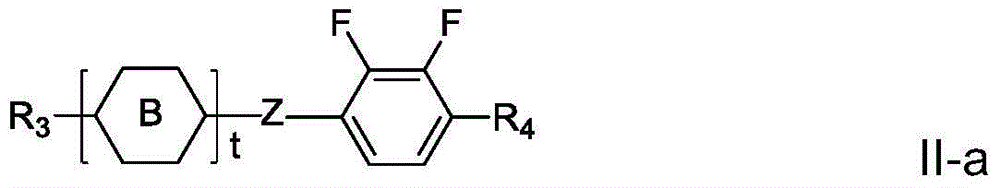

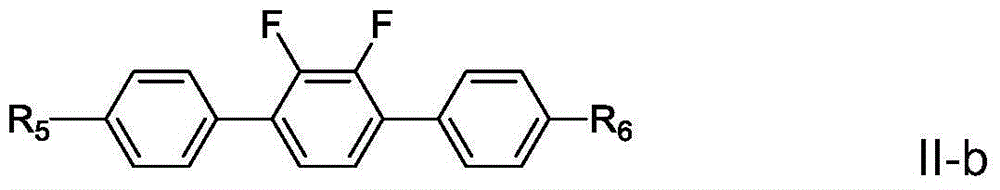

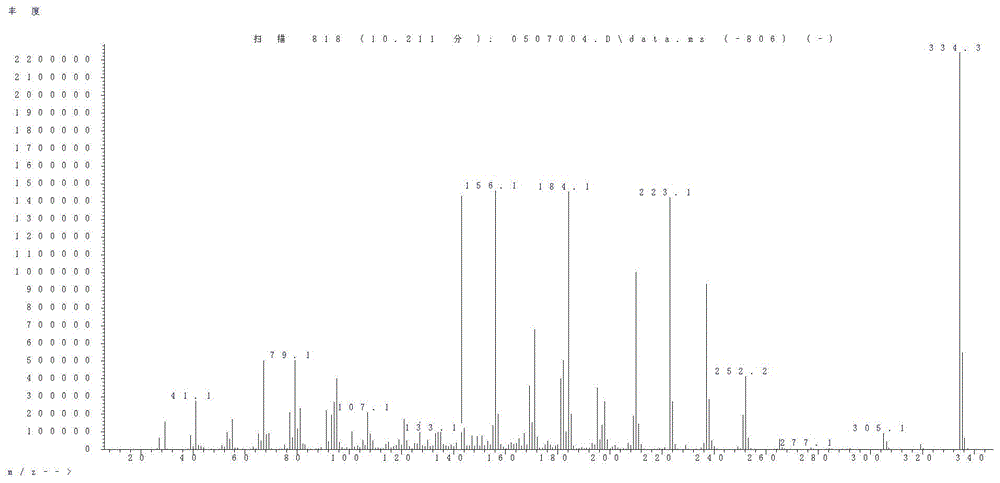

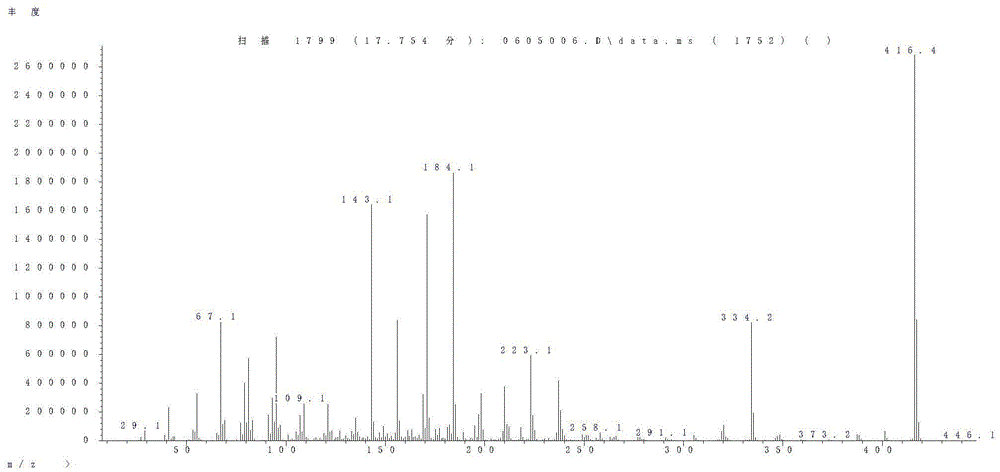

Cyclopropyl-containing negative dielectric anisotropic liquid crystal medium and application thereof

ActiveCN104650924AThe absolute value of the negative dielectric anisotropy is largeReduce viscosityLiquid crystal compositionsNon-linear opticsDielectric anisotropyActive matrix

The invention relates to a cyclopropyl-containing negative dielectric anisotropic liquid crystal composition which contains at least one or more of compounds shown in the formulas I-a and I-b and at least one ore more of compounds shown in the formulas II-a and II-b. The cyclopropyl-containing negative dielectric anisotropic liquid crystal composition disclosed by the invention has the advantages of proper negative dielectric anisotropy, proper optical anisotropy, low viscosity and wide nematic temperature range, thereby having preferable application in an electro-optical display and an active matrix display with VA, FFS or IPS effect especially. (The formulas I-a and I-b and the formulas II-a and II-b are shown in the specification).

Owner:SHIJIAZHUANG CHENGZHI YONGHUA DISPLAY MATERIALS CO LTD

Liquid crystal compound and liquid crystal medium comprising compound

InactiveCN104591982AQuick responseFast VA-TFT modeLiquid crystal compositionsOrganic chemistryCrystallographyLiquid-crystal display

The invention relates to a novel negative dielectricity liquid crystal compound having a structural formula I as shown in the description, relates to a liquid crystal medium comprising at least one compound having the structural formula I and also relates to an electro-optic display containing the liquid crystal medium. The compound has the advantages of high negative dielectricity, larger K value and lower rotational viscosity and is suitable for fast-response VA liquid crystals, especially VA-TFT smf VA-IPS LCD liquid crystal display.

Owner:SHIJIAZHUANG CHENGZHI YONGHUA DISPLAY MATERIALS CO LTD

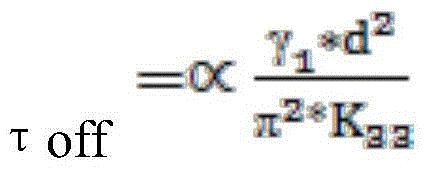

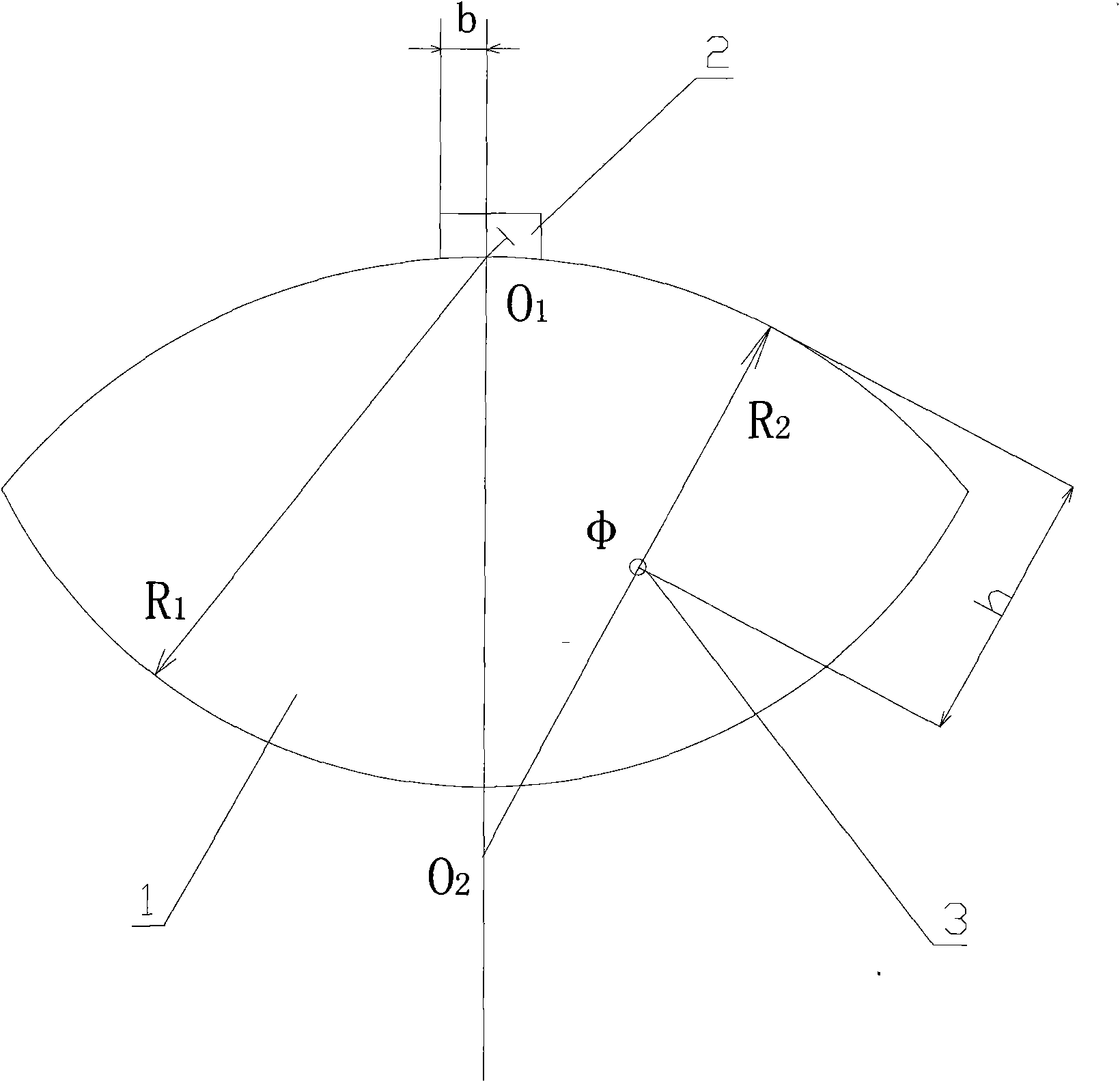

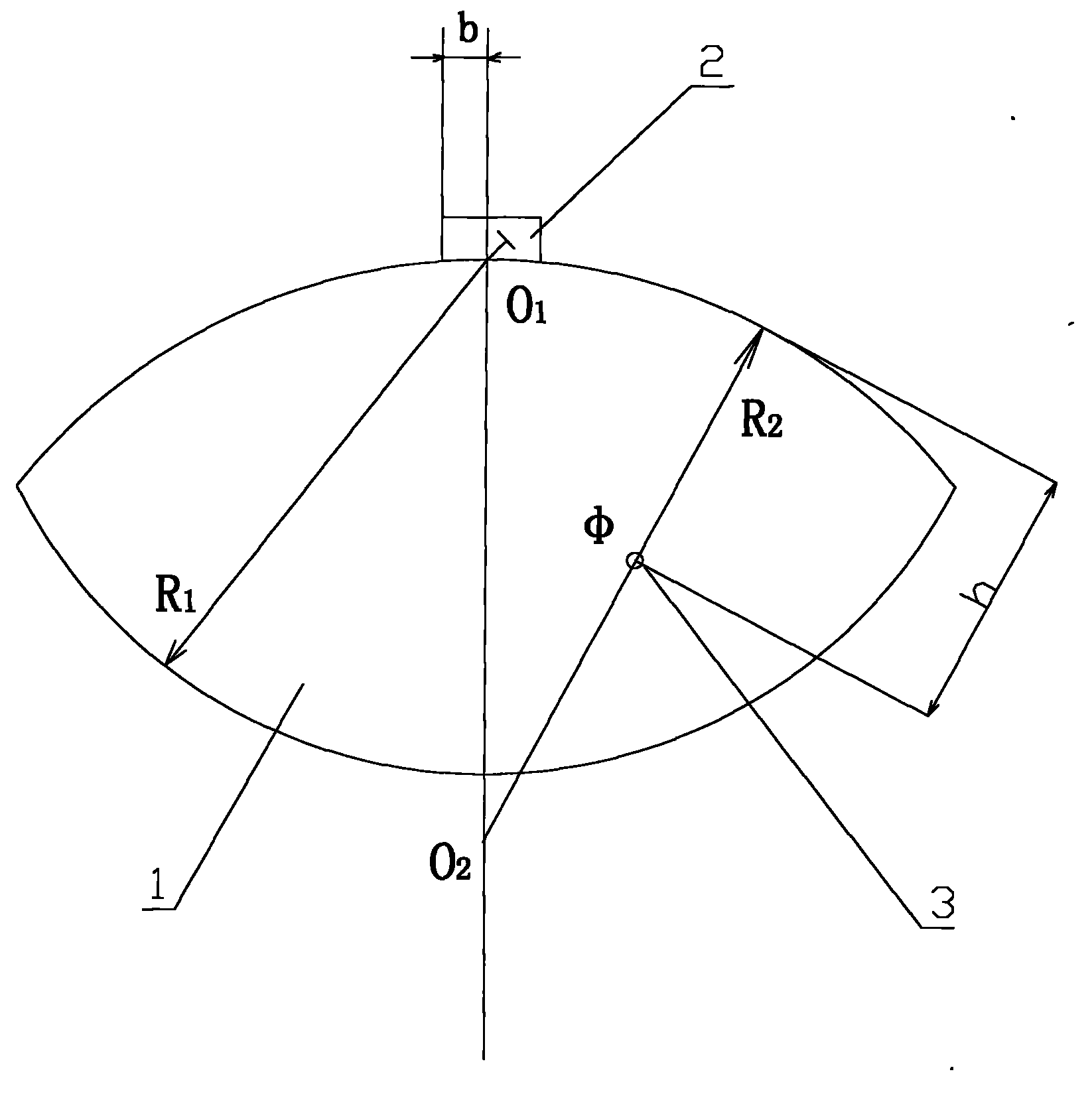

Method for calibrating small-diameter probe for ultrasonic flaw detector

InactiveCN101806779AReduce volumeReduce weightMaterial analysis using sonic/ultrasonic/infrasonic wavesFront edgeProbe calibration

The invention discloses a method for calibrating a small-diameter probe for an ultrasonic flaw detector, belonging to the method for calibrating an instrument. The method for calibrating the small-diameter probe for the ultrasonic flaw detector comprises the following steps in sequence: manufacturing a test block for calibrating the small-diameter probe for the ultrasonic flaw detector; moving the external circular arc probe near the point O1 on the surface of the arc of the test block back and force, wherein the arc of the test block is drawn by adopting the radius R2; obtaining the range S1 of the echo of a radius R1; measuring the distance between the point O1 and the foremost edge of the small-diameter probe, wherein the distance is the front edge b of the small-diameter probe; adjusting the direction of the small-diameter probe to make the small-diameter probe aligned to the direction of the hole, and obtaining the range S of the echo of the hole; and obtaining the range a of the echo in the small-diameter probe and the value K of the small-diameter probe. The invention makes up the blank of the calibration of the value K of the small-diameter probe, the front edge b of small-diameter probe and the range a of the echo in the small-diameter probe and reduces the loss cost of the small-diameter probe.

Owner:符丰

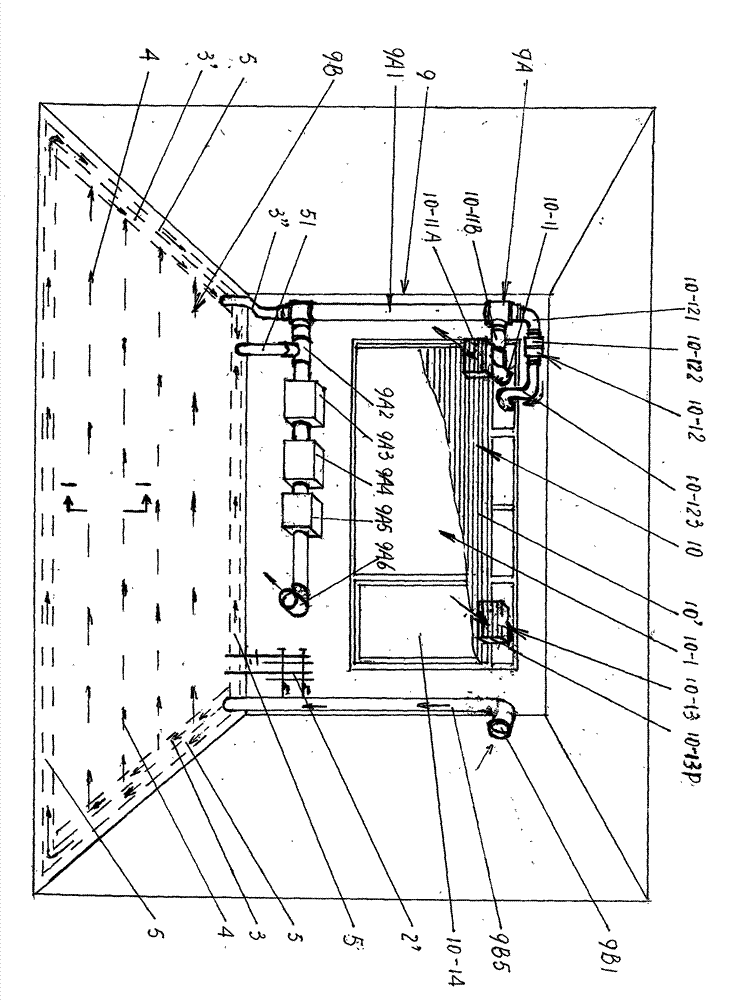

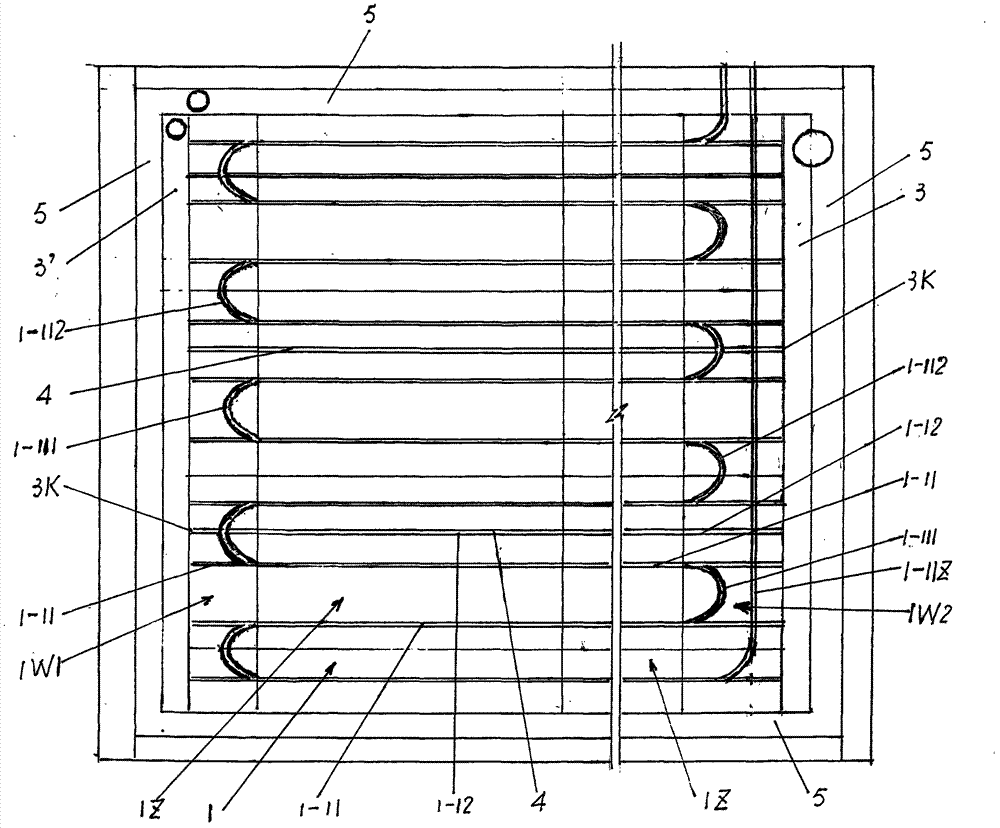

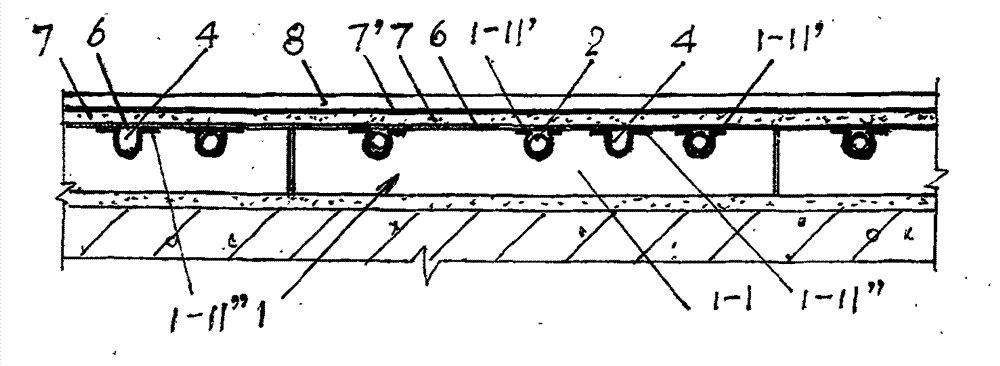

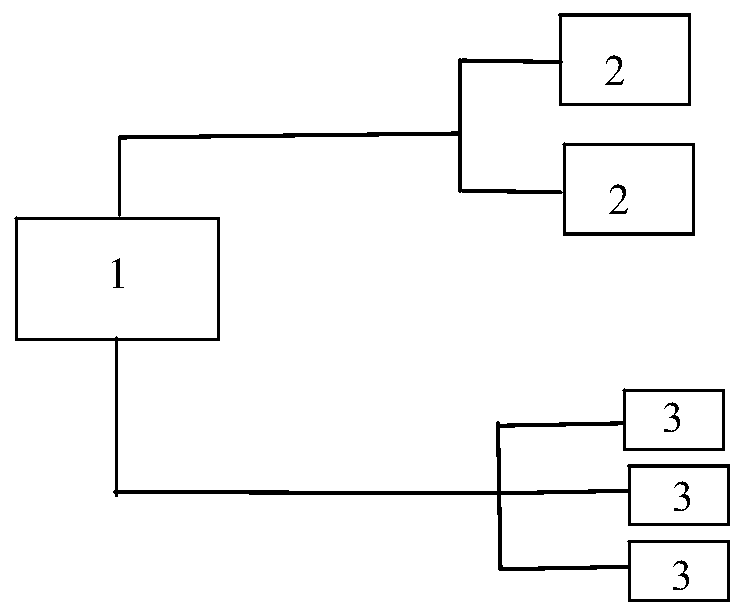

Ventilation and heat preservation module heating and cooling floor and energy-saving ventilation and air conditioning system

InactiveCN104763087AReduce energy consumptionImprove the effect of ventilation and air conditioningDucting arrangementsHot-air central heatingFresh airEngineering

The invention relates to a ventilation and heat preservation module heating and cooling floor and energy-saving ventilation and air conditioning system which comprises a ventilation and heat preservation module heating and cooling floor body, a ventilation and air conditioning system body and a heat preservation and ventilation window. The ventilation and heat preservation module heating and cooling floor body is composed of an expandable polyethylene cushion layer, a ventilation and heat preservation module body, a floor heating pipeline, a water division and collection device, a dehumidification and heat radiation air supply pipe, a dehumidification and heat radiation air channel, a dehumidification and heat radiation air collection pipe, an air conditioner floor air supply pipe, a dampproof heat conduction layer and a wood floor from bottom to top in sequence. The heat preservation and ventilation window and the ventilation and air conditioning system body are communicated to form the complete energy-saving ventilation and air conditioning system. The K value of the window is improved, the heat preservation and ventilation window is adopted as an air inlet and exhaust channel, and the energy consumption of a ventilation air conditioner is lowered. The effect of the ventilation air conditioner is improved, a floor heating tail end has the two purposes for heating and cooling, waste heat is recycled, and mounting and running cost is lowered. The aims that air is purified, and a user can breathe clean and fresh air without opening the window are achieved.

Owner:冯刚克

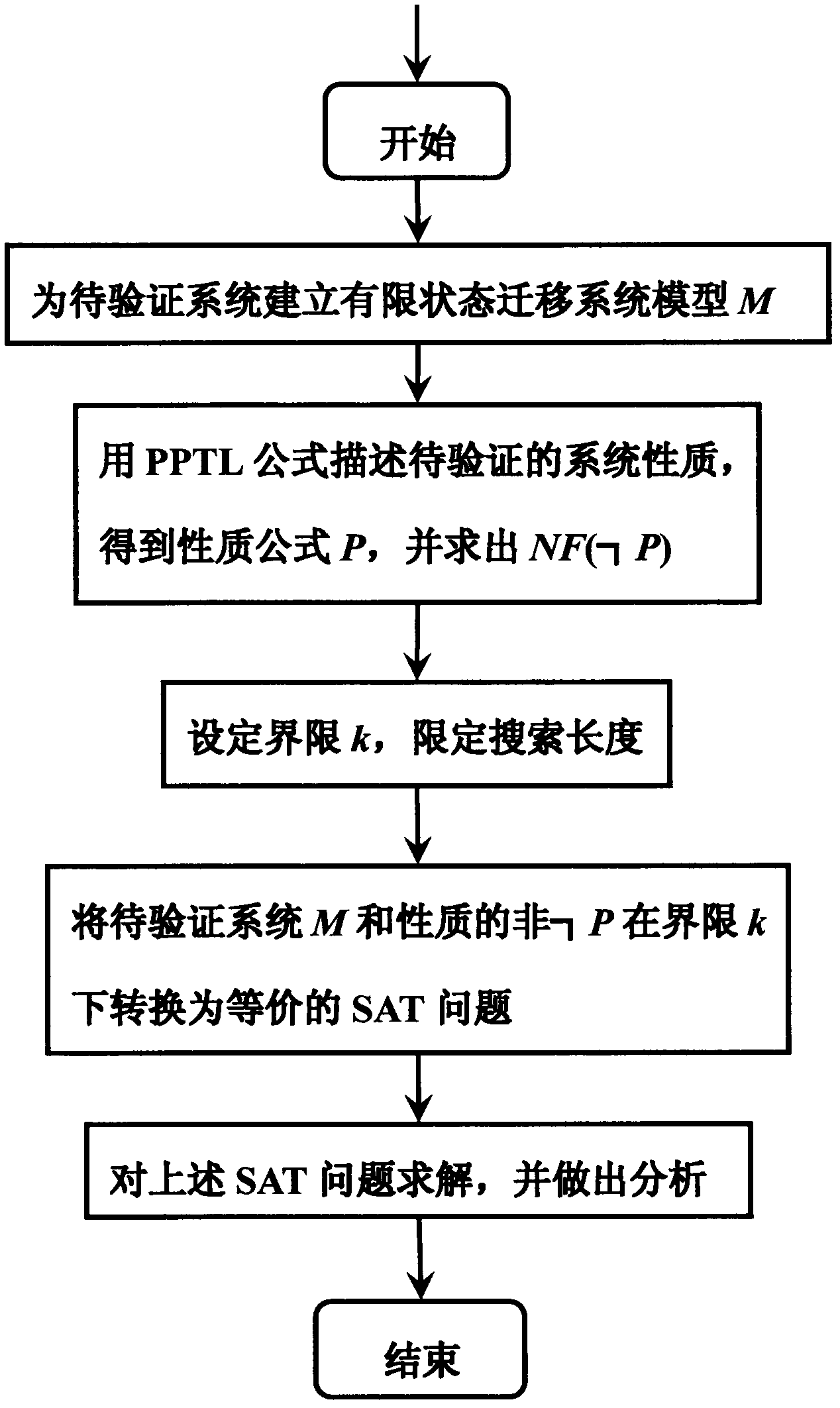

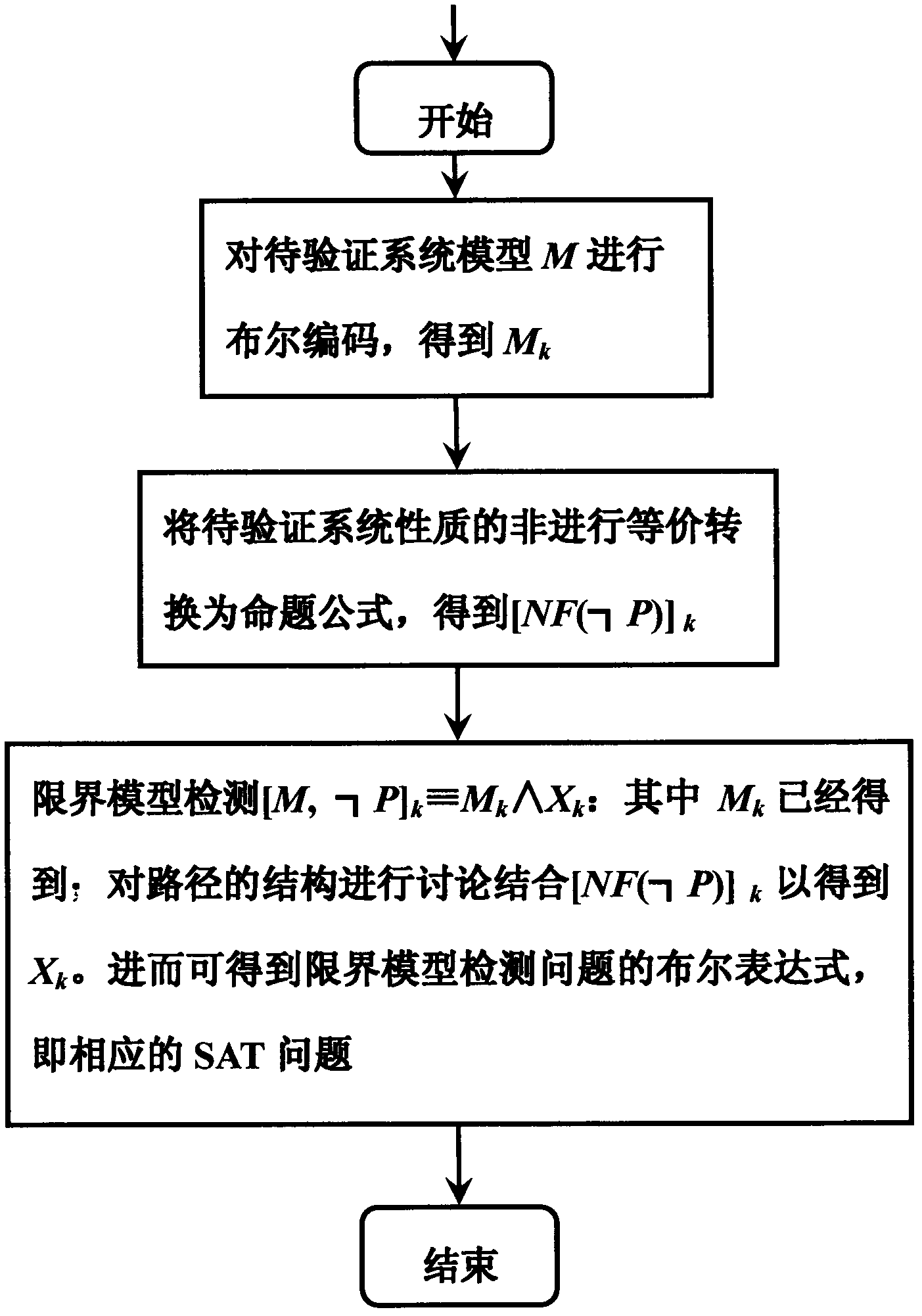

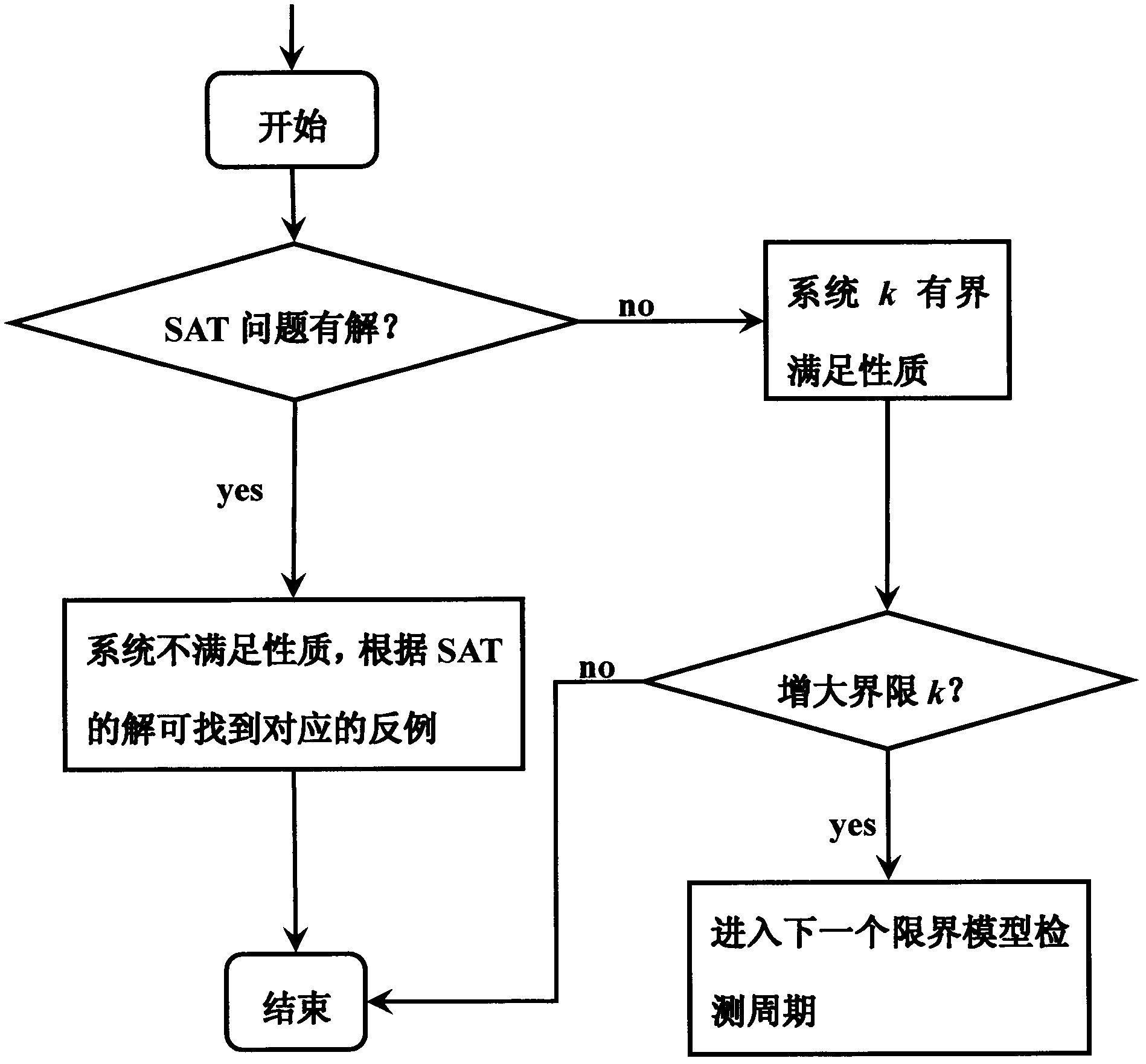

SAT (satisfiability) based method for bounded model checking (BMC) for propositional projection temporal logic (PPTL)

ActiveCN102663191AImprove detection efficiencyConvenient verificationSpecial data processing applicationsComputation tree logicSat problem

The invention relates to an SAT (satisfiability) based method for bounded model checking (BMC) for propositional projection temporal logic (PPTL). The method includes the following steps of utilizing a Kripke structure to describe a system model M to be verified; utilizing a PPTL formula to describe a property P; setting up a bound k; converting the bounded model checking for the PPTL into an SAT problem; and solving the SAT problem. In the step of solving the SAT problem, a solution of the SAT problem indicates that the system model M is not satisfiable to the property P, otherwise, non-solution of the SAT problem indicates that the bound of the system model M is satisfiable to the property P; the value of the K is increased to move on to the next checking period until the value of the k is large enough and the bound of the system model M is satisfiable to the property P in every bounded model checking period. The problem that a CTL (computation tree logic) and an LTL (linear temporal logic) are limited in abilities of expression is solved by utilizing the PPTL to describe the system property, the status space explosion problem is released by limiting searching length to reduce searching status number, and convenience and effectiveness for checking complex system property are improved by combining respective advantages of the PPTL and the BMC. The SAT based method for the bounded model checking for the PPTL is applicable to formal verifications for soft and hardware systems and communication protocols.

Owner:XIDIAN UNIV

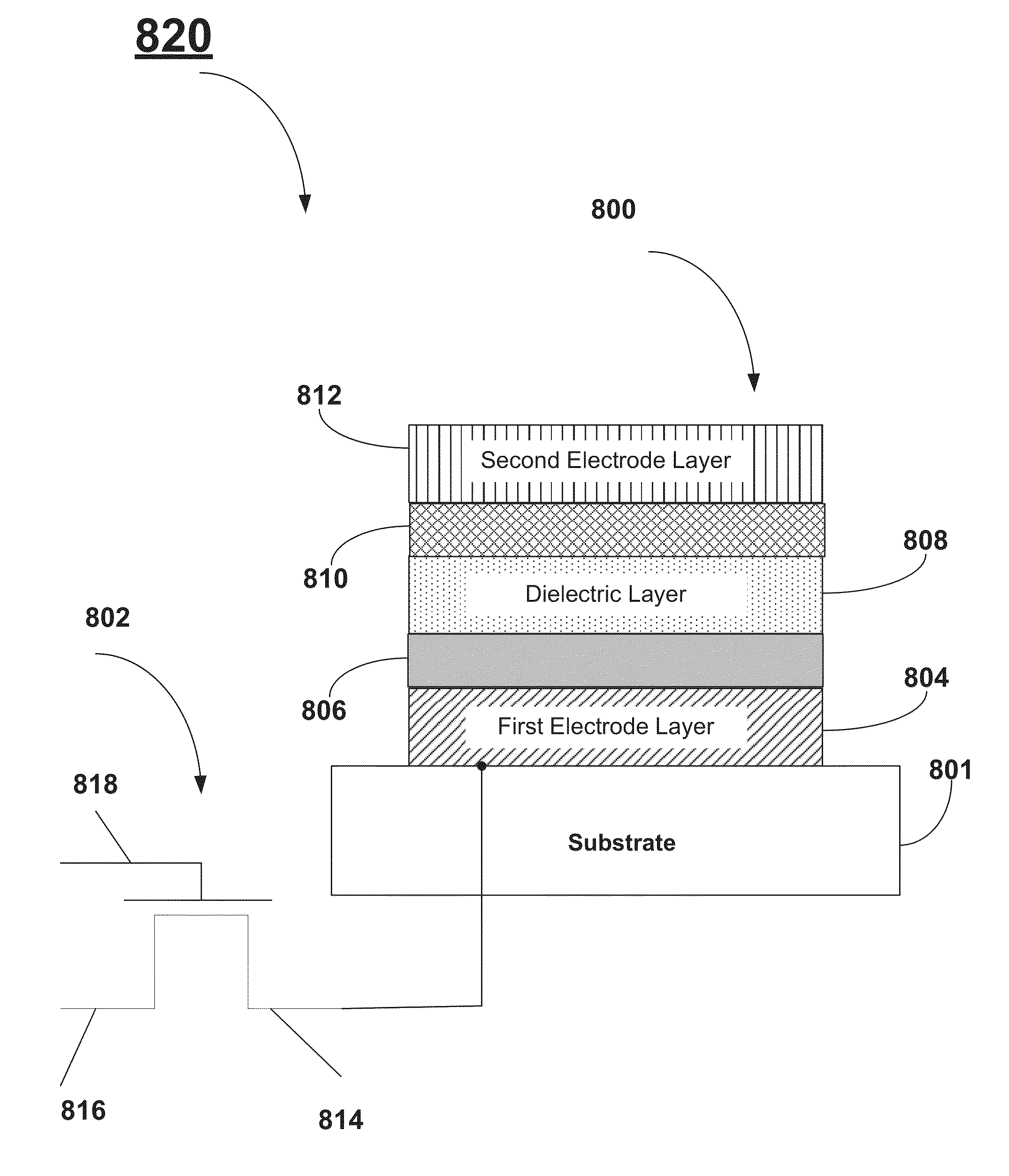

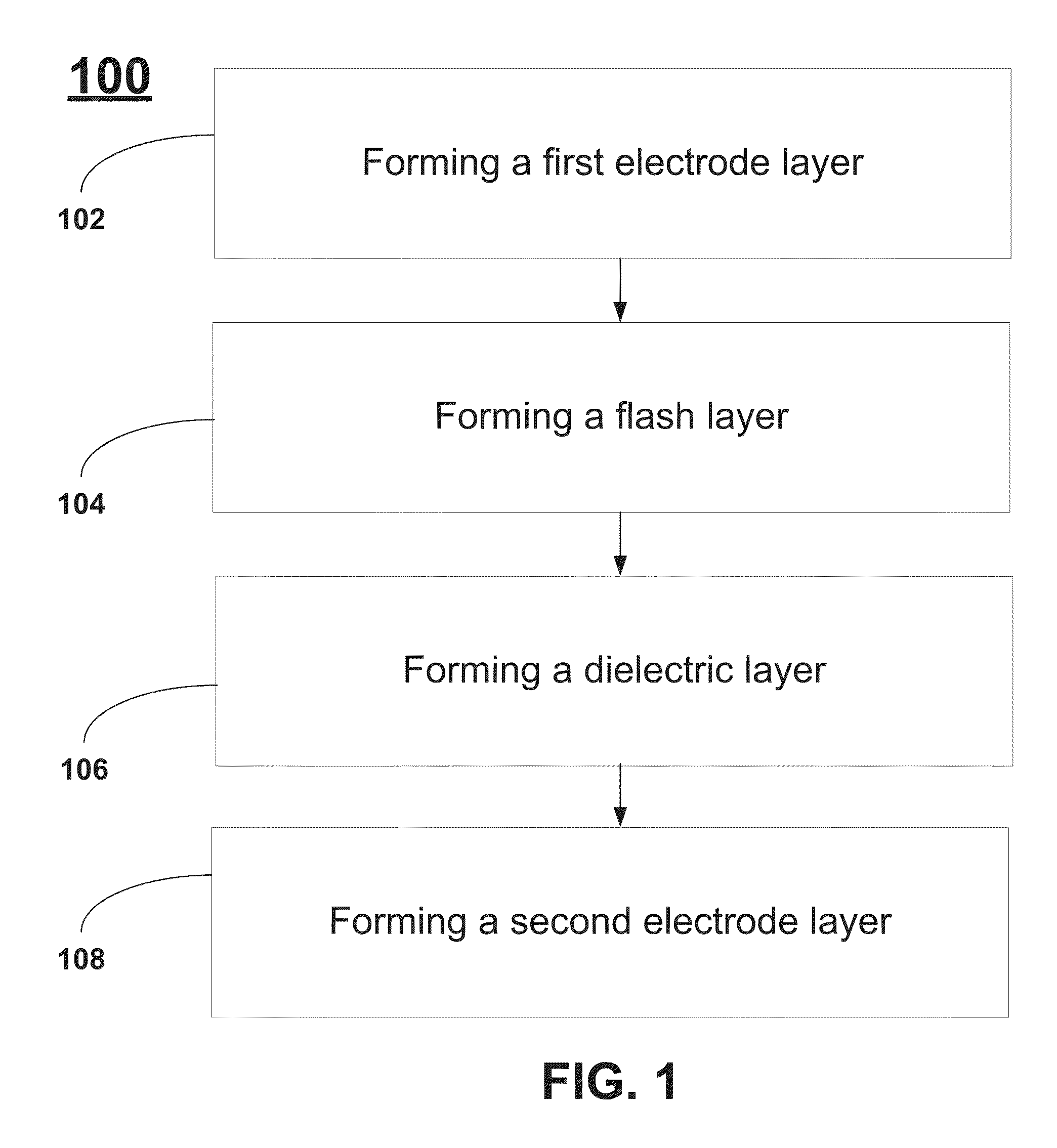

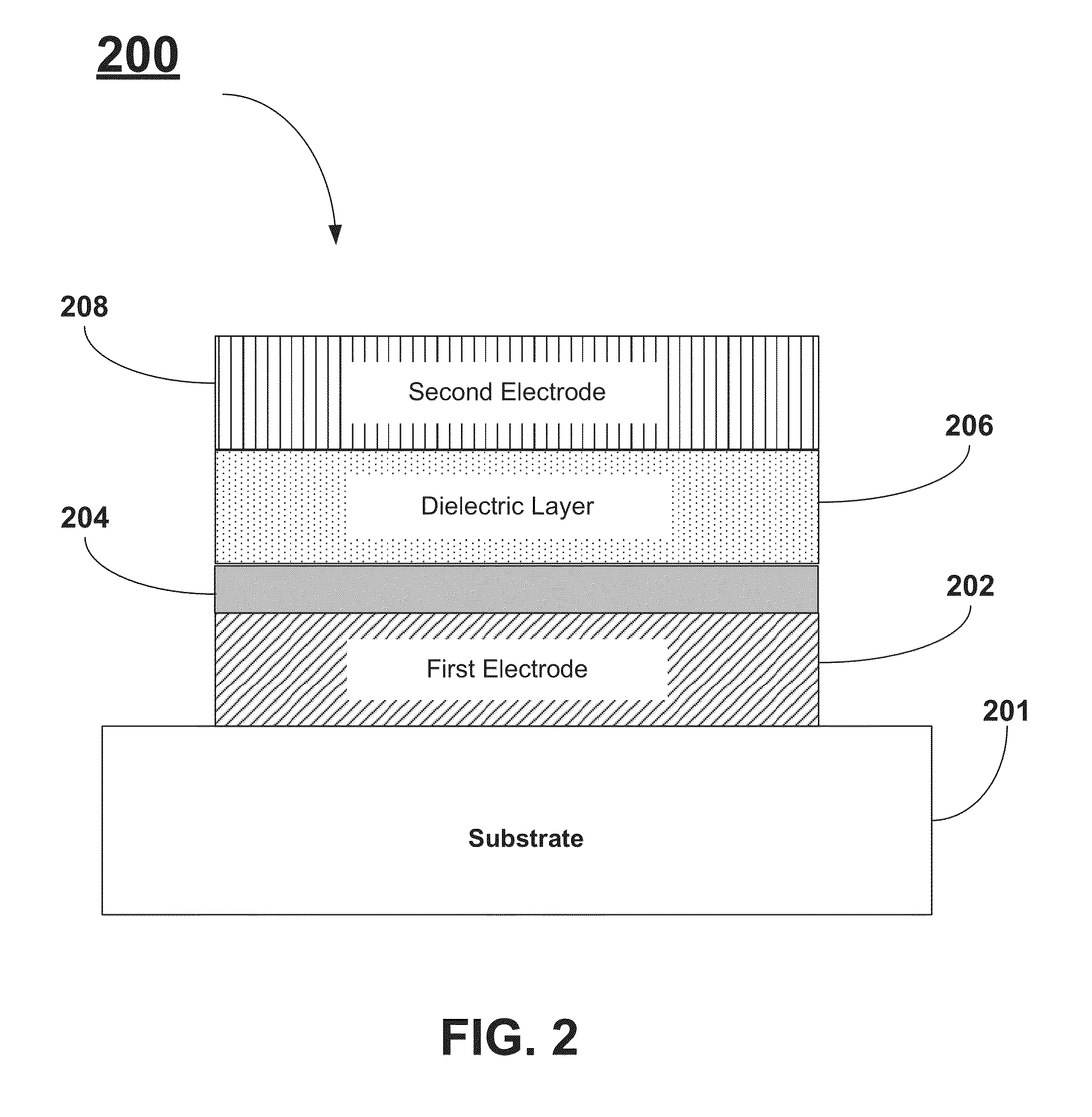

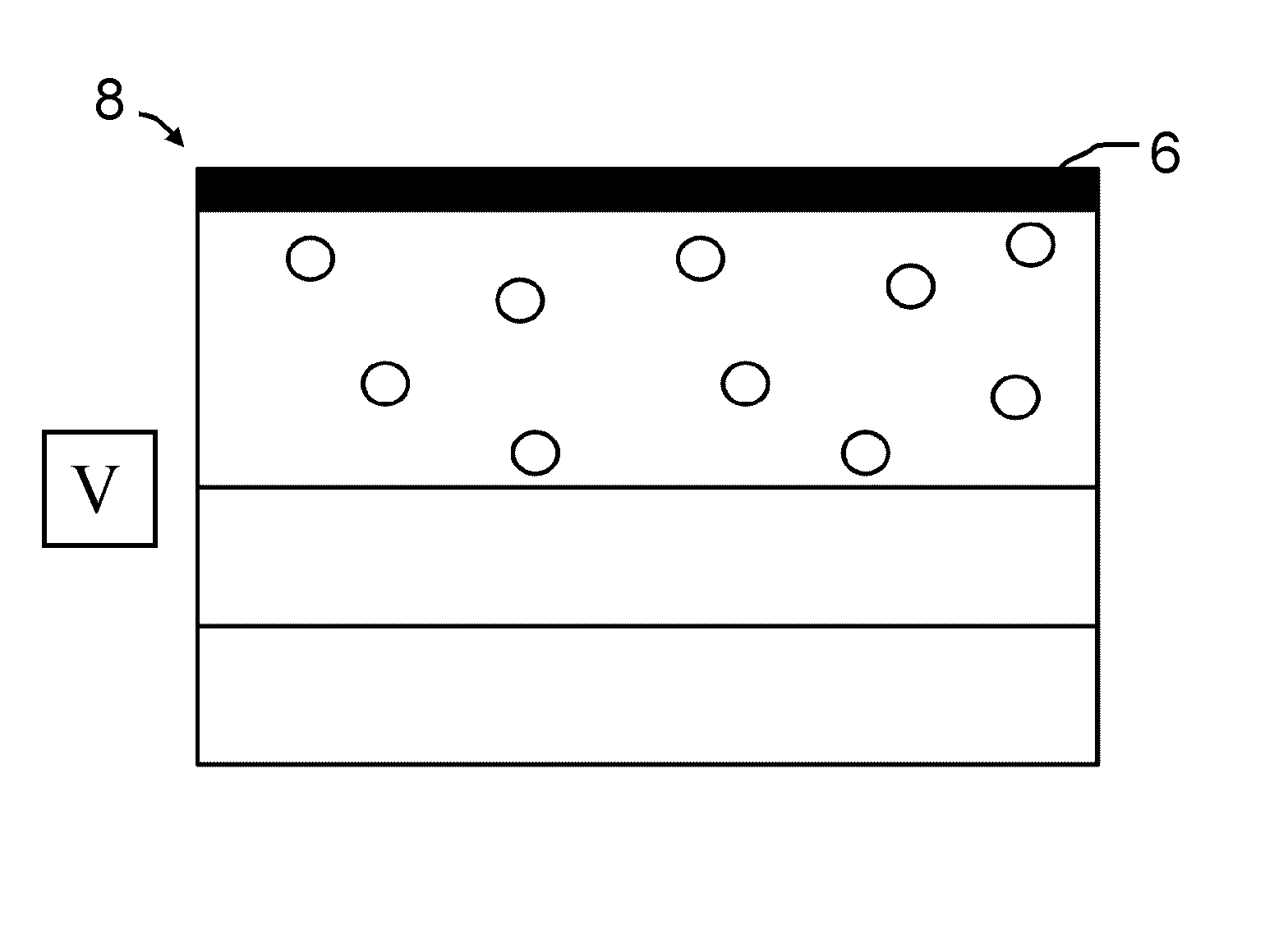

Methods for Reproducible Flash Layer Deposition

InactiveUS20140183695A1Reduce leakage currentIncrease K valueSolid-state devicesSemiconductor/solid-state device manufacturingMetal-insulator-metalOxygen

A method for reducing the leakage current in DRAM Metal-Insulator-Metal capacitors includes forming a flash layer between the dielectric layer and the first electrode layer. A method for reducing the leakage current in DRAM Metal-Insulator-Metal capacitors includes forming a capping layer between the dielectric layer and the second electrode layer. The flash layer and the capping layer can be formed using an atomic layer deposition (ALD) technique. The precursor materials used for forming the flash layer and the capping layer are selected such they include at least one metal-oxygen bond. Additionally, the precursor materials are selected to also include “bulky” ligands.

Owner:INTERMOLECULAR

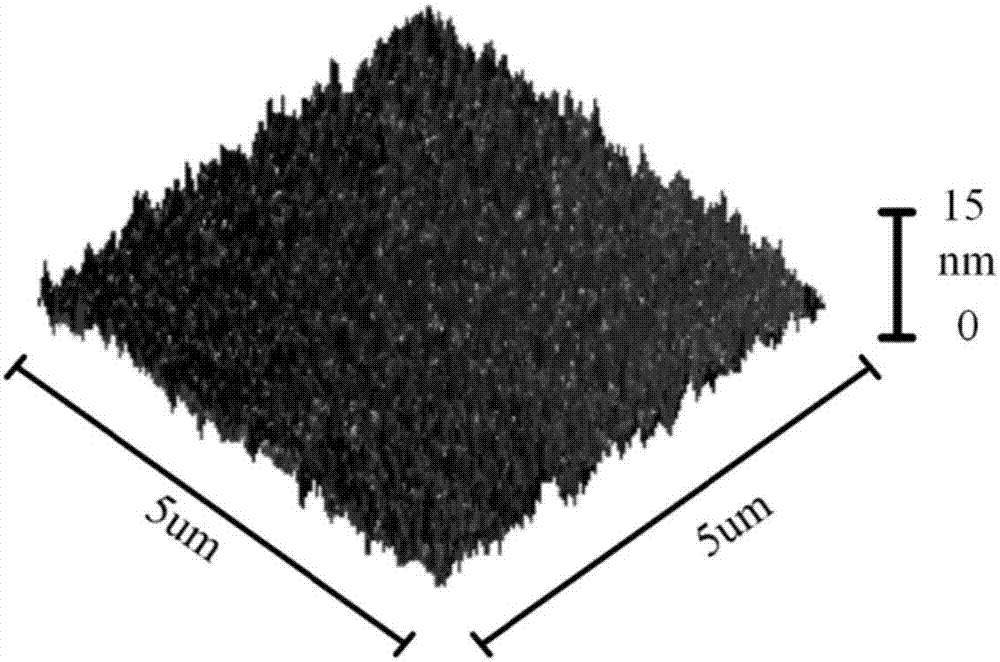

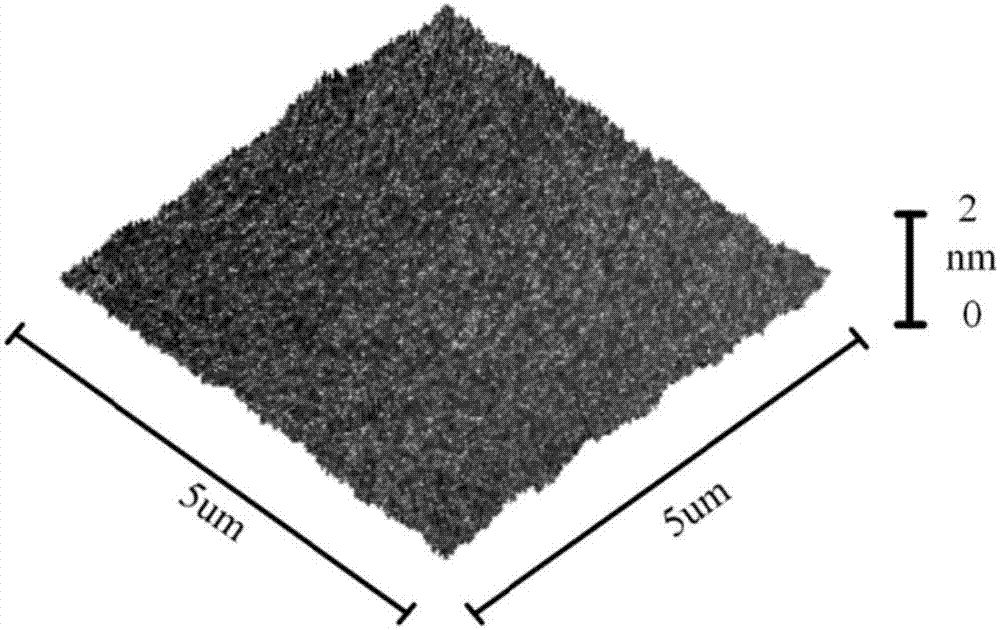

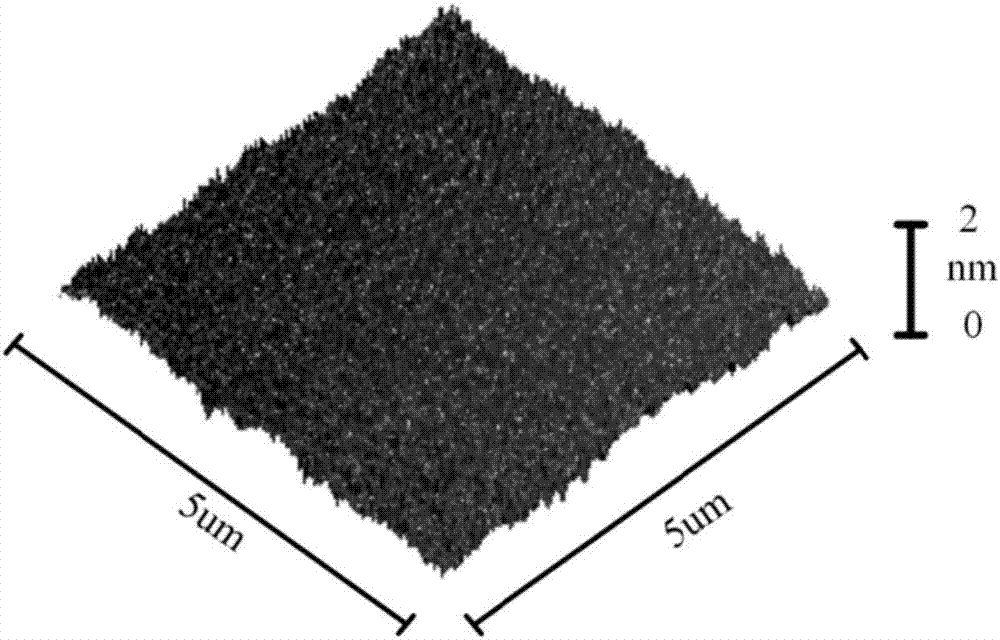

Oxide thin film transistor device based on composite insulation layer and preparation method of oxide thin film transistor device

ActiveCN107403842AReduce surface roughnessReduce off-state currentTransistorSemiconductor/solid-state device manufacturingInsulation layerOxide thin-film transistor

The invention discloses an oxide thin film transistor device based on composite insulation layer and a preparation method of the oxide thin film transistor device, and belongs to the technical field of electronics. The objective of the invention is to solve the problem of damage to performance of an IGZO thin film transistor caused by phenomenon of high roughness and appearance of a pin hole of the reactive sputtering aluminum oxide surface. According to the invention, the device comprises a substrate, a gate electrode, the composite insulation layer, an oxide semiconductor layer, a source electrode and a drain electrode, which are successively arranged up and down, wherein the source electrode and the drain electrode are arranged on the oxide semiconductor layer, the composite insulation layer comprises upper and lower layers, the lower layer is the aluminum oxide on the gate electrode and the upper layer is the organic material on the aluminum oxide. Thus, performance of the thin film transistor is improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

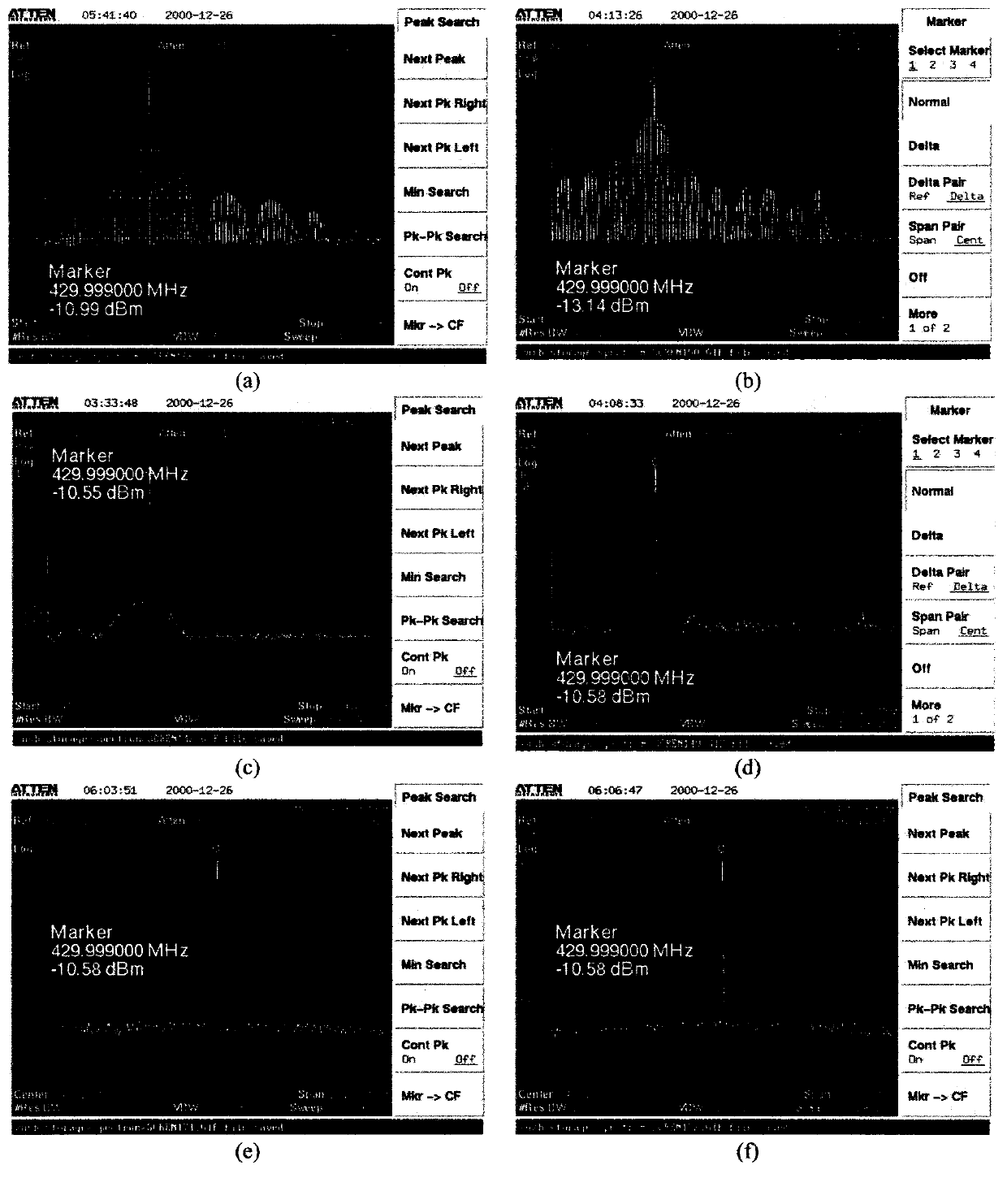

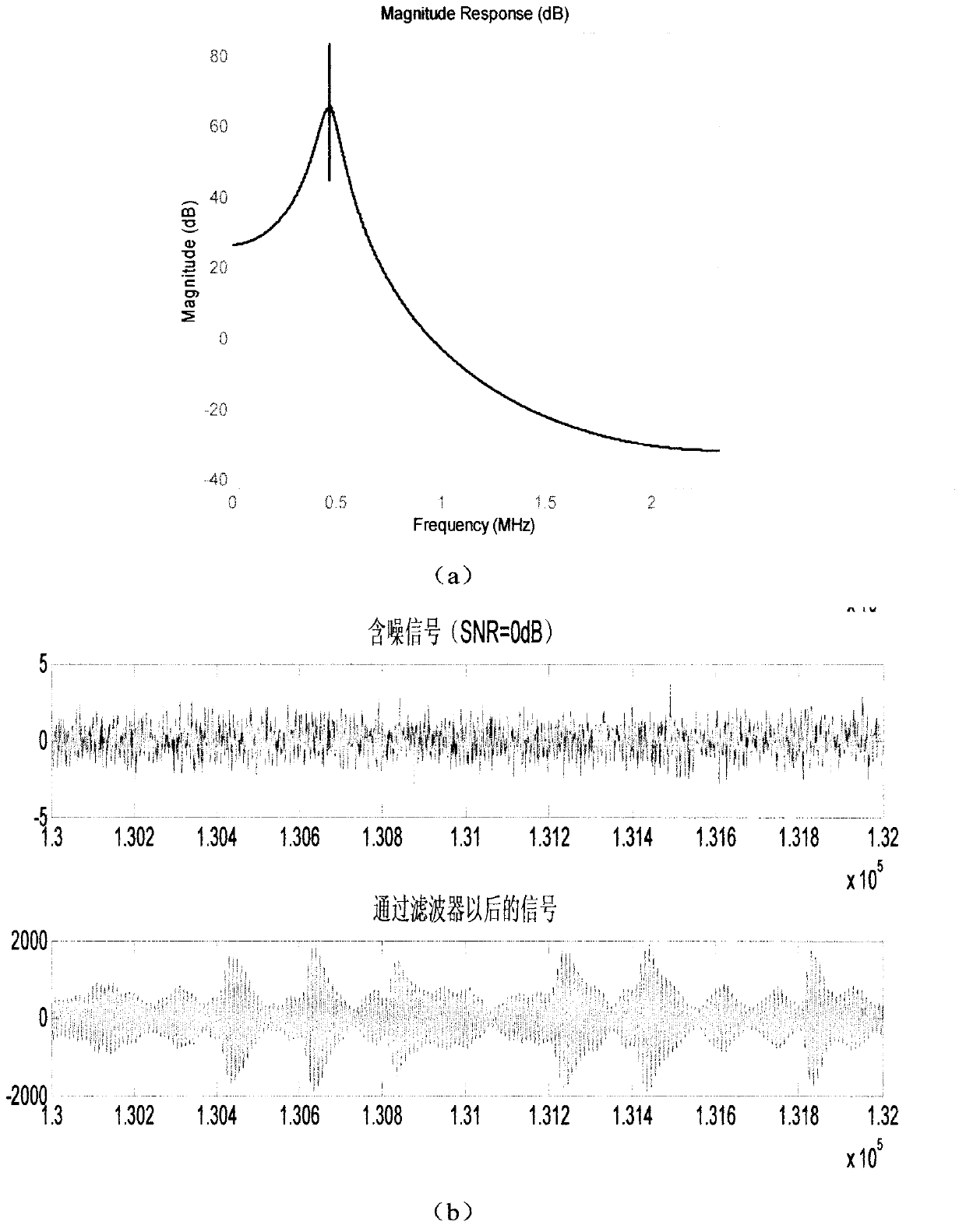

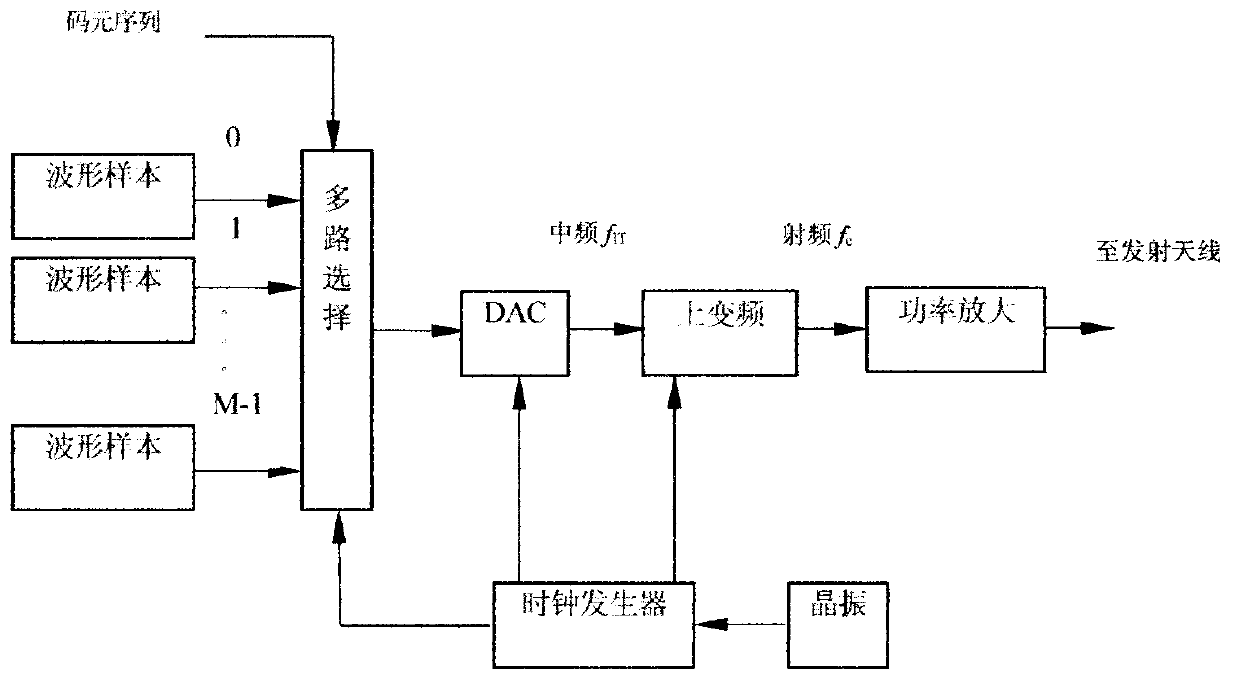

Transmitting and receiving system for improving comprehensive efficiency of M-ary position phase shift keying (MPPSK) modem

InactiveCN102868655AImprove spectrum utilizationHigh code ratePhase-modulated carrier systemsModem deviceIntermediate frequency

The invention discloses a transmitting and receiving system for improving comprehensive efficiency of an M-ary position phase shift keying (MPPSK) modem. An MPPSK modulation simple expression is used as basis, FORMULA, wherein omegac is angular frequency of a modulation carrier; Tc is equal to 2Pi / omegac and serves as a carrier period; rg is more than or equal to 0 and less than 1 and is used as a sign protection interval control factor; rg and integers M, N and K form a modulation parameter for changing the bandwidth, the transmission efficiency and the demodulation performance of a signal; an emitter is modulated by radio frequency or an emission medium frequency which is as high as possible; a receiver performs impact filter demodulation by up conversion frequency or a receiving medium frequency which is as high as possible; and therefore, a K value which is reduced by the emission end is increased, and the code error rate performance is improved.

Owner:苏州东奇信息科技股份有限公司

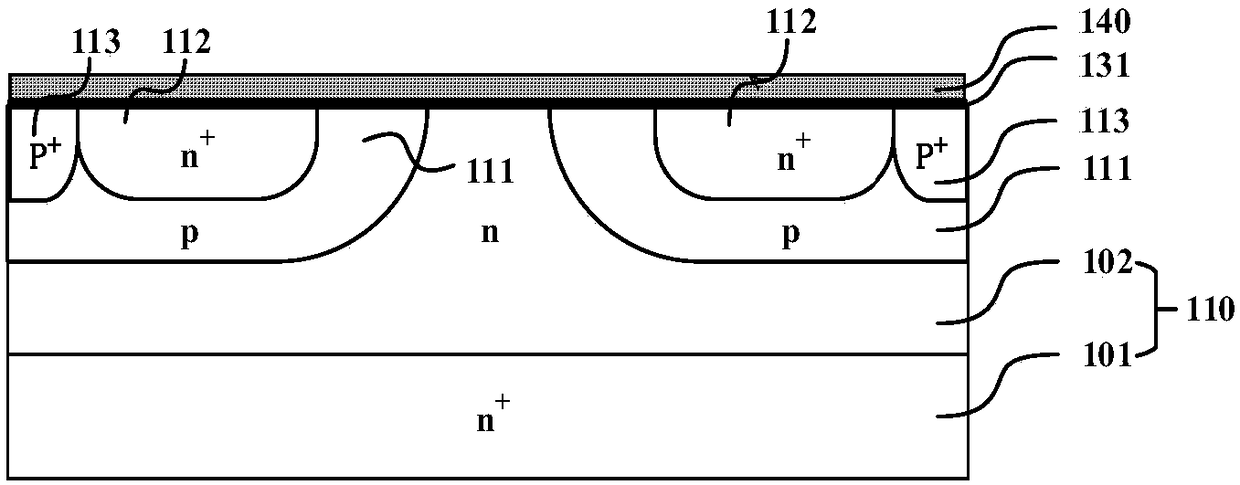

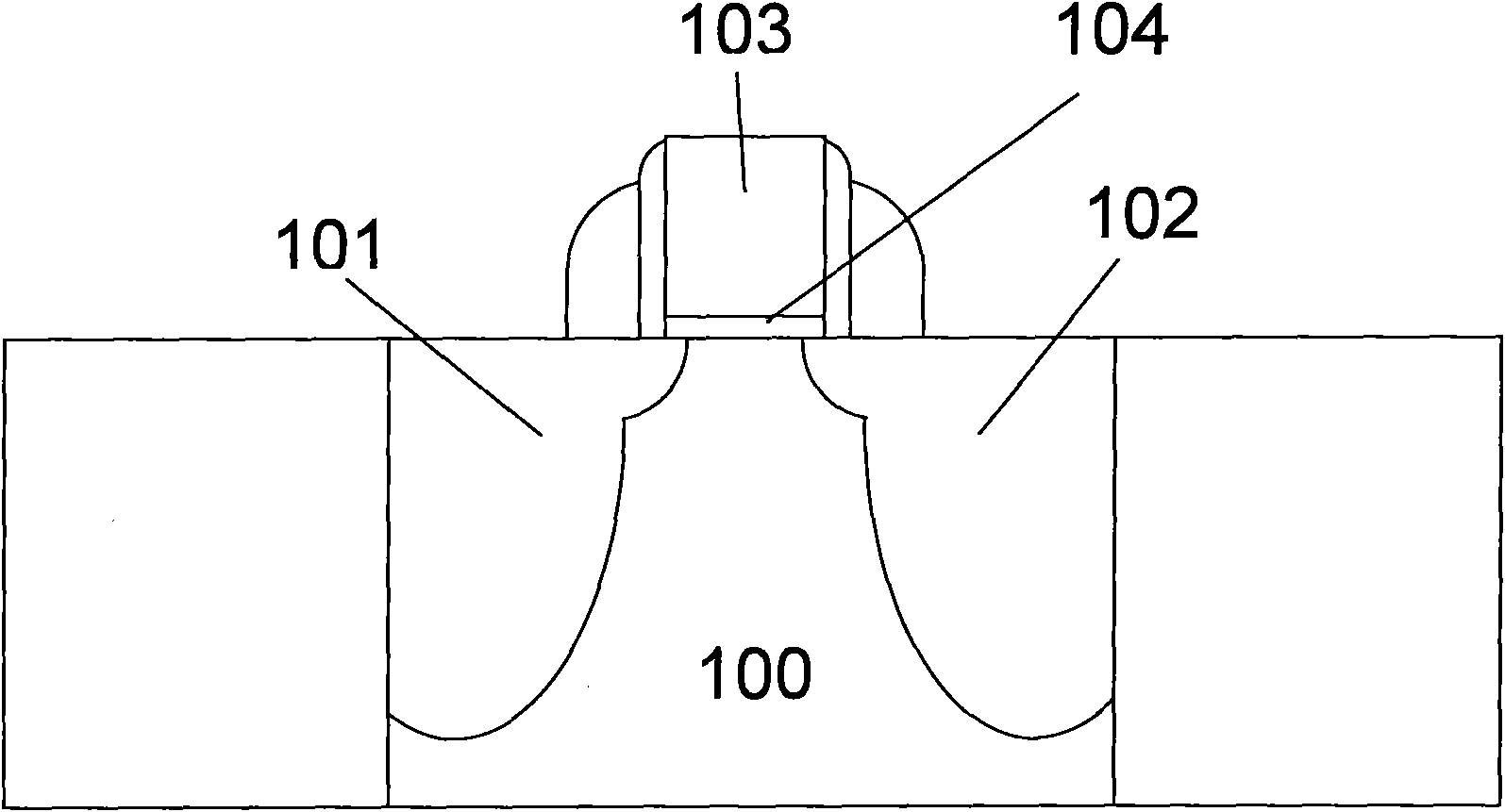

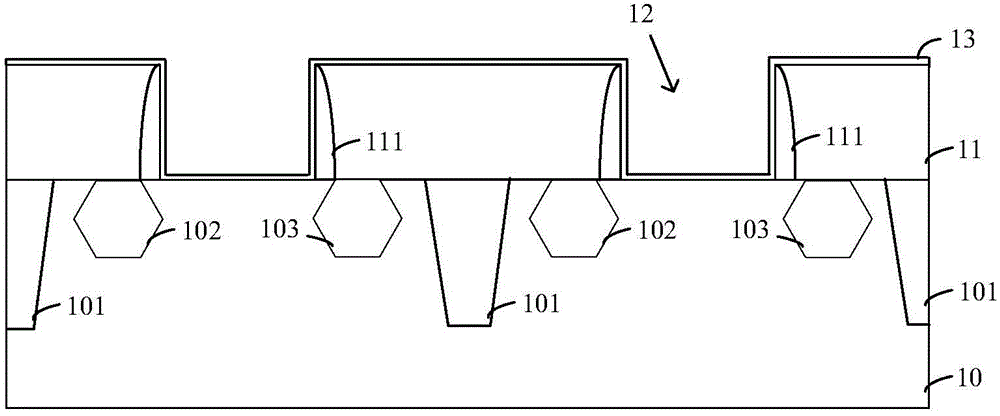

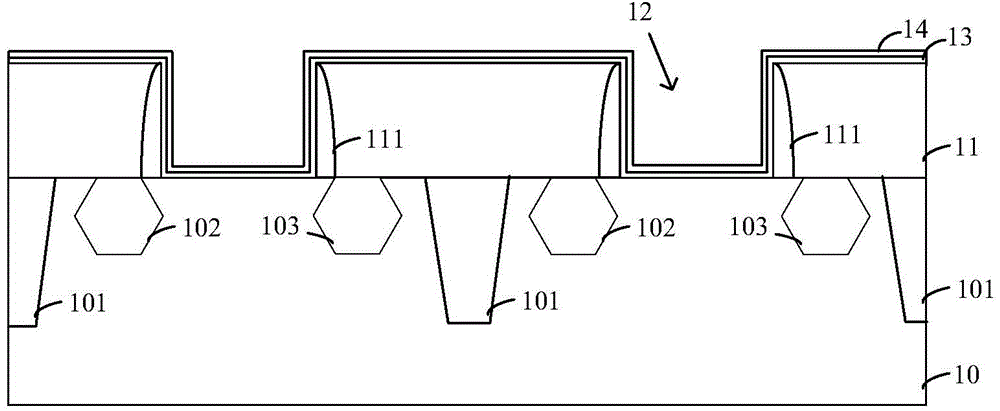

Preparation method of high k-gate dielectric layer and silicon carbide MOS power device

ActiveCN108257855AImprove pressure resistanceEliminate lattice damageSemiconductor/solid-state device manufacturingSemiconductor devicesLattice defectsGate dielectric

The present invention provides a preparation method of a high k-gate dielectric layer and a silicon carbide MOS power device. The preparation method comprises the steps of: performing high-temperaturesacrificial oxidation of a silicon carbide epitaxial wafer with a first conductive type, and forming a sacrificial oxidation layer at the upper surface of the epitaxial layer of the silicon carbide epitaxial wafer; performing corrosion of the sacrificial oxidation layer until the sacrificial oxidation layer on the epitaxial layer is completely removed; performing high-temperature surfacing processing of the upper surface of the epitaxial layer after removal of the sacrificial oxidation layer, and forming a smooth passivated surface; and depositing an Al2O3 dielectric coating layer, a LaAlO3 dielectric layer and an Al2O3 dielectric coating layer at the smooth passivated surface in order, performing annealing of a laminated structure formed by the Al2O3 dielectric coating layer, the LaAlO3dielectric layer and the Al2O3 dielectric coating layer, and forming a high k-gate dielectric layer. Compared to the prior art, the preparation method of the high k-gate dielectric layer and the silicon carbide MOS power device can reduce the interface defects caused by impurities and / or surface lattice defects at a SiC / SiO2 interface so as to improve the voltage endurance capability of the gate dielectric layer.

Owner:GLOBAL ENERGY INTERCONNECTION RES INST CO LTD +2

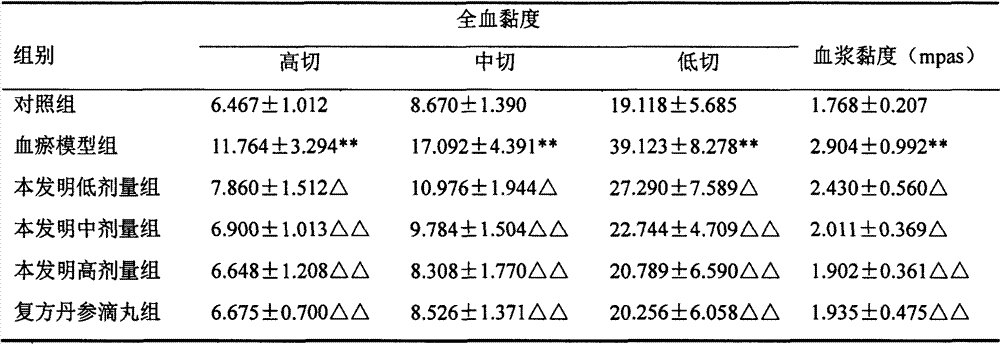

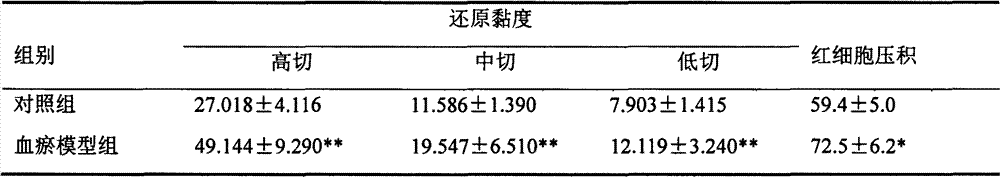

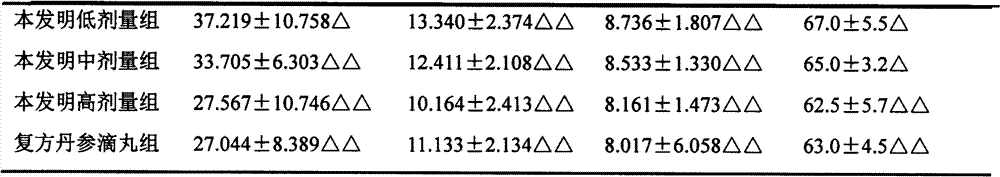

Composition for stagnant blood constitution, and preparation method and application of composition

ActiveCN102846793AReduce the electrophoretic indexImprove rigidityDigestive systemAntinoxious agentsMedicineRemove blood

The invention relates to a composition for stagnant blood constitution, and a preparation method and application of the composition. Used medicinal materials are extracted and purified by using a semi-bionic extraction method and an ultrasonic method, active ingredients are effectively kept, and the composition is obtained by preparation. The composition has effects of invigorating the circulation of blood, moistening dryness and removing blood stasis for promoting tissue regeneration, and has unique curative effects for blood stasis symptoms.

Owner:SHAN DONG DONG E E JIAO

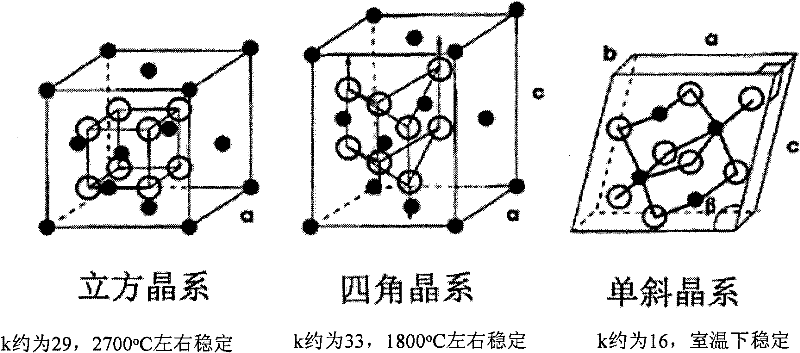

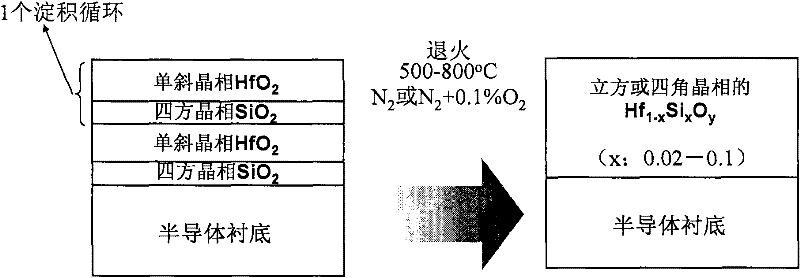

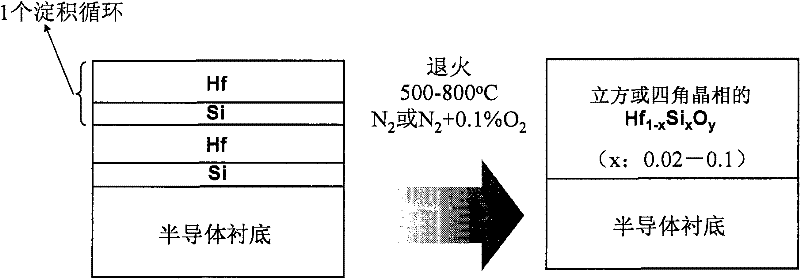

High-dielectric-constant gate dielectric material and preparation method thereof

InactiveCN102453866AIncrease K valueImprove thermal stabilityVacuum evaporation coatingSputtering coatingGate dielectricThin membrane

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Method for activating a porous layer surface

ActiveUS9117666B2Increase K valueImprove responseSemiconductor/solid-state device manufacturingPorous layerDielectric layer

A method is provided for activating an exposed surface of a porous dielectric layer, the method comprising the steps of: filling with a first liquid at least the pores present in a part of the porous dielectric layer, the part comprising the exposed surface, removing the first liquid selectively from the surface, activating the exposed surface, and removing the first liquid from the bulk part of the porous dielectric layer.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW) +1

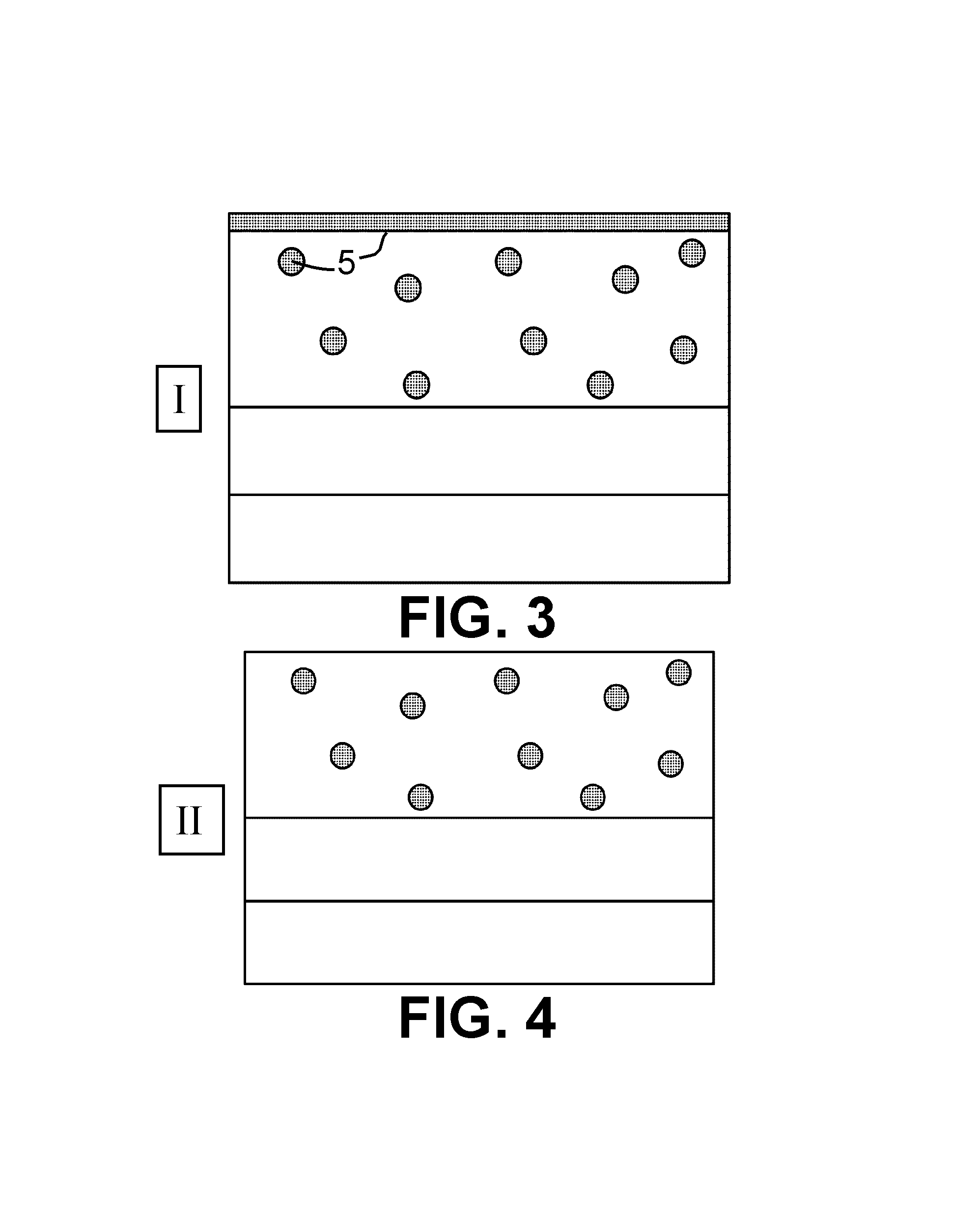

MOS (Metal Oxide Semiconductor) field effect transistor

ActiveCN102142458AEasy to controlGood communication characteristicsSemiconductor devicesCMOSCapacitance

The invention provides an MOS (Metal Oxide Semiconductor) field effect transistor comprising a substrate, a source electrode, a drain electrode and a grid stack, wherein the source electrode and the drain electrode are formed in the substrate; the grid stack is formed above the substrate and positioned between the source electrode and the drain electrode; and a grid dielectric layer is made of a dielectric material with an adjustable K value. In the embodiment of the invention, the dielectric material with the adjustable K value is applied to the grid dielectric layer of a CMOS (Complementary Metal-Oxide-Semiconductor Transistor) device; the grid capacitance is increased by dynamically obtaining the high K value; and the capability of the CMOS device on controlling the short channel effect and the switching rate are improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

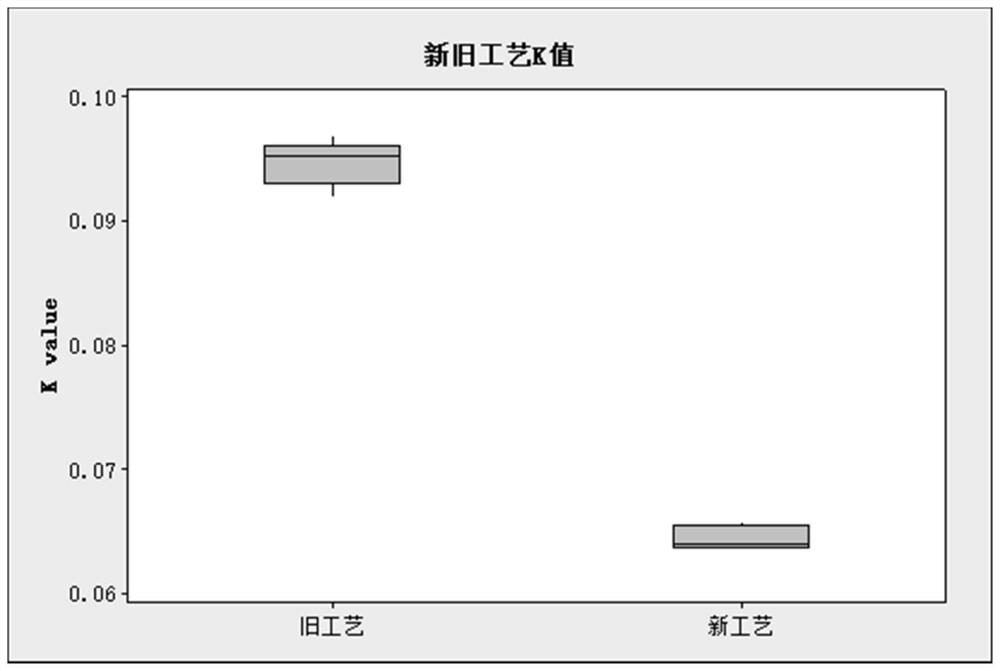

Method for improving infiltration effect of battery cell and lithium ion battery cell

ActiveCN112366356AImprove wettabilityImprove securityFinal product manufactureElectrolyte accumulators manufactureEngineeringLithium-ion battery

The invention belongs to the technical field of lithium ion batteries, and discloses a method for improving the infiltration effect of a battery cell. The method comprises the steps of primary infiltration, micro-charging, rolling, pre-charging, high-temperature infiltration and the like. The invention further discloses the lithium ion battery cell obtained after treatment by the method. By adopting the infiltration method provided by the invention, the infiltration effect of the battery cell pole piece is greatly improved, the surface of the battery cell pole piece is fully infiltrated by theelectrolyte, the surface of the pole piece is free of lithium precipitation, wrinkles and peeling, and the safety performance of the battery cell is improved. Performance comparison data show that compared with the prior art, the K value, DCR and capacity of the process provided by the invention are improved.

Owner:WANXIANG 123 CO LTD

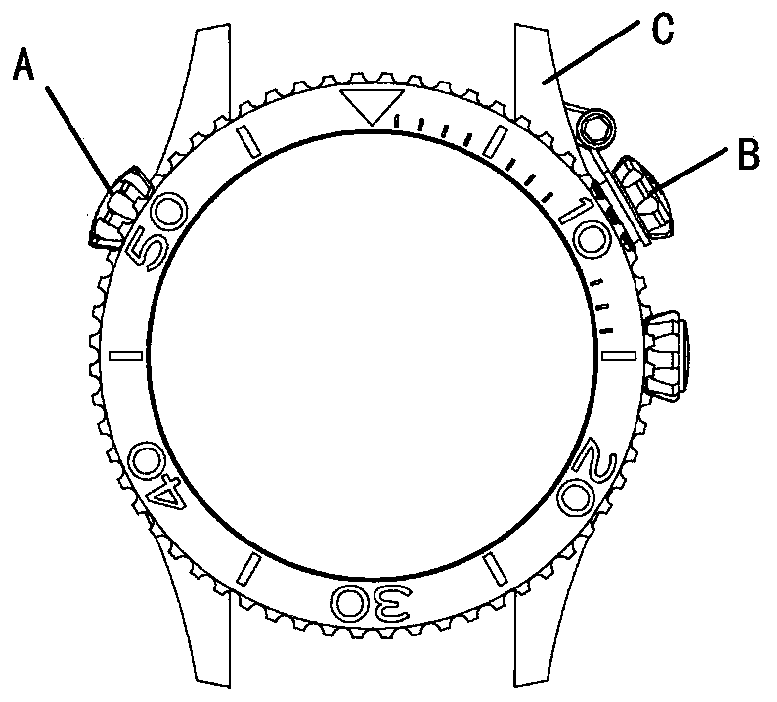

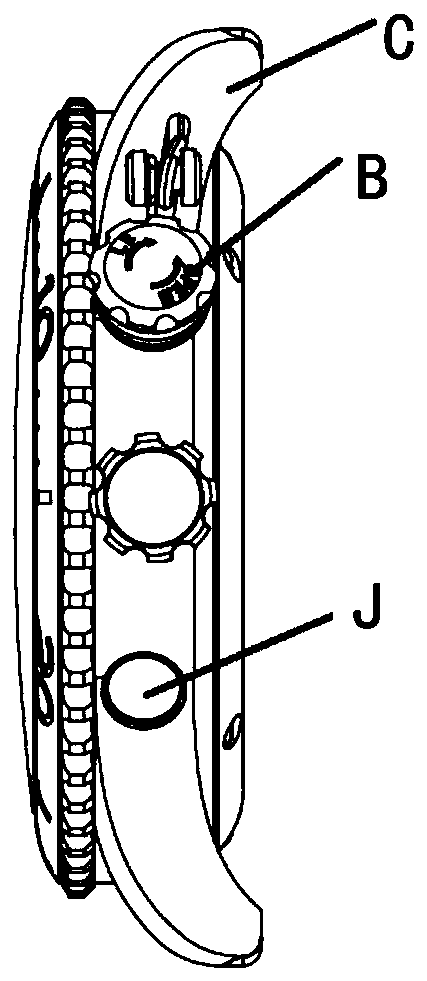

Watch capable of dehumidifying and demisting

The invention provides a watch capable of dehumidifying and demisting, which comprises a bottom cover, a watchcase and a glass surface, and is characterized in that the side surface of the watchcase is provided with a gas inlet valve and a gas exhaust valve, and the hollow interior of the watch is filled with an argon gas by means of the gas inlet valve; the hollow interior of the watch is furtherprovided with a drying agent; and the gas exhaust valve is used for exhausting a gas in the hollow interior of the watch when the argon gas is injected by means of the gas inlet valve. The interior of the watch is kept dry by means of the internally arranged drying agent; meanwhile, the inert gas argon is filled in to replace the common air in the hollow interior of the watch, the K value of thehollow interior is effectively improved, condensation of the glass is reduced, the interior of the glass watch surface is effectively kept dry, the outer surface of the watch surface is not prone to frost, and the adaptive capacity of the watch in an extreme environment is improved; and whether the drying agent needs to be replaced or not is conveniently identified by means of a transparent observation window.

Owner:SHENZHEN BOWDOR WATCH IND

Production method of metal-silicon nitride-metal capacitor

ActiveCN102446709AIncrease capacitanceIncrease K valueSemiconductor/solid-state device manufacturingDielectricCapacitance

The invention provides a production method of a metal-silicon nitride-metal capacitor, which comprises the steps of: 1) depositing a low-k-value dielectric layer; 2) forming a metal-oxide-metal (MOM) area through photoetching and etching; 3) depositing high-k-value silicon nitride through a plasma enhanced chemical vapor deposition (PECVD) method; 4) removing excessive silicon nitride through chemical and mechanical grinding to form a low-k-value dielectric and silicon nitride mixed layer; 5) completing photoetching and etching to form a metal groove on the low-k-value dielectric and silicon nitride; 6) completing the deposition and the chemical and mechanical grinding of the metal layer and then forming the metal fillers of a conducting wire and an MOM capacitor; and 7) completing copper interconnection and the production of the MOM capacitor. By improving the k value of the dielectric of the inter-layer capacitor, the capacitance of the inter-layer capacitor is effectively improved. By improving the performance of the high-k-value silicon nitride, the electric properties such as the puncture voltage, the leakage current and the like of the MOM capacitor and the electric uniformity of devices are effectively improved. The production method is very practical.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

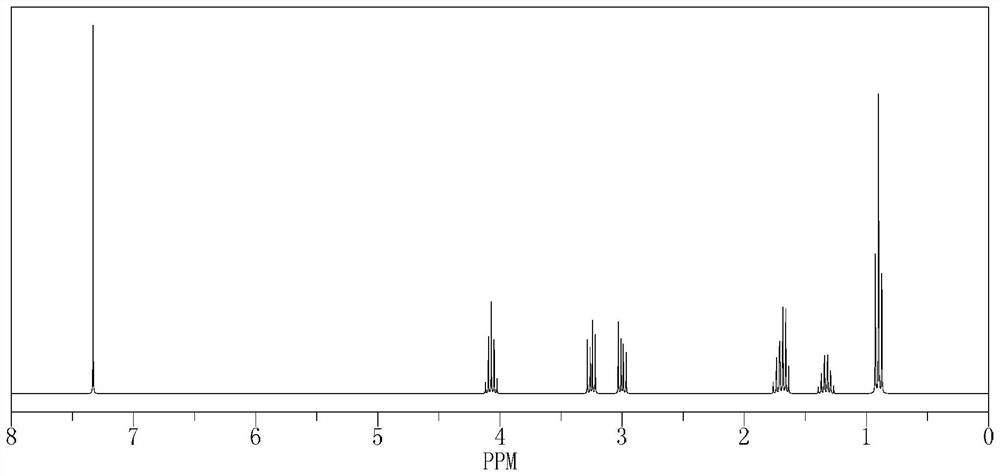

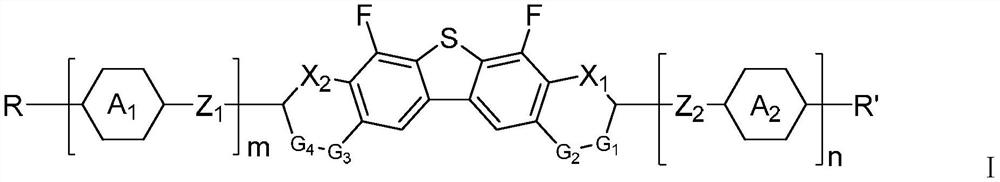

Liquid crystal compound containing dibenzothiophene and oxygen-containing heterocycles and application of liquid crystal compound

PendingCN113355105AGood rotational viscosityGood miscibility at low temperatureLiquid crystal compositionsCrystallographyPhysical chemistry

The invention belongs to the field of liquid crystal compound materials, and relates to a liquid crystal compound containing dibenzothiophene and oxygen-containing heterocycles and application of the liquid crystal compound. The chemical structural formula is shown in the formula I. The liquid crystal compound and a liquid crystal composition containing the liquid crystal compound have the advantages of large dielectric, high clearing point, high refractive index, high K value and the like, and are suitable for displays in VA, ECB, PALC, FFS or IPS modes.

Owner:SHIJIAZHUANG CHENGZHI YONGHUA DISPLAY MATERIALS CO LTD

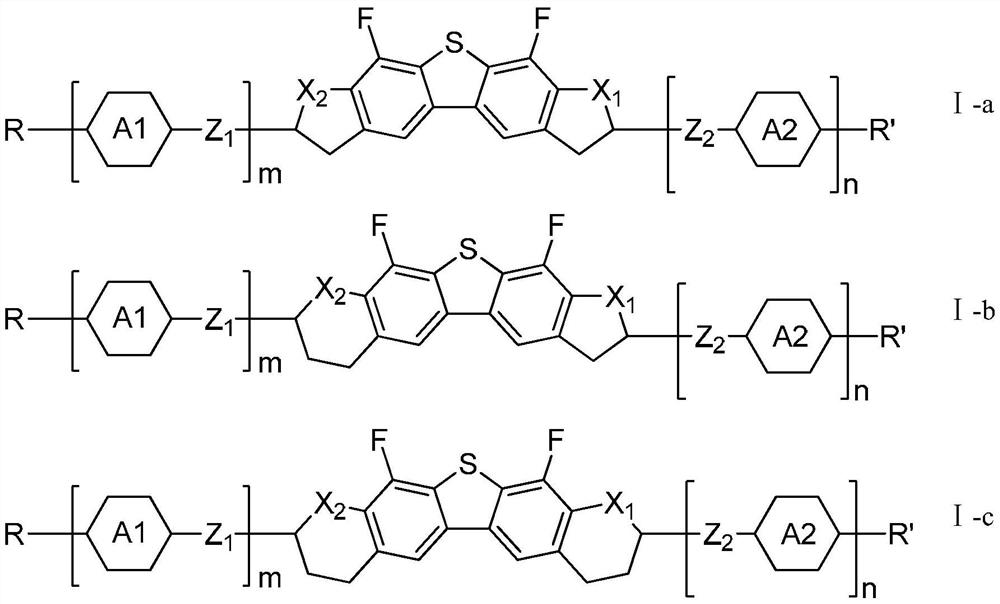

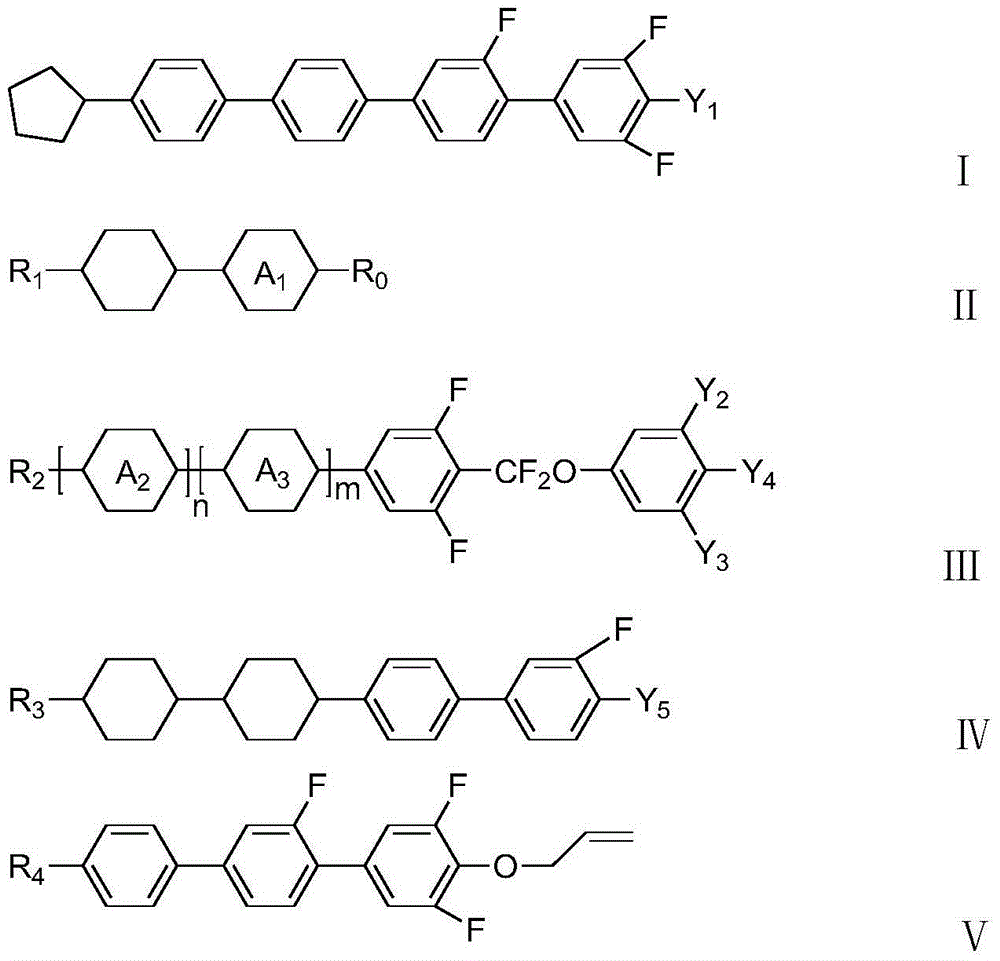

Liquid crystal composition

ActiveCN104560057AImprove performanceHigh resistivityLiquid crystal compositionsNon-linear opticsCrystallographyDielectric anisotropy

The invention discloses a liquid crystal composition and the application of the liquid crystal composition to a liquid crystal display. The liquid crystal composition has positive dielectric anisotropy and is excellent in performance; the refractive index of the liquid crystal composition is larger than 0.100 and smaller than 0.120; the liquid crystal composition is suitable for a liquid crystal panel which is small in thickness and high in respond speed, has a wide application prospect and a good application value, and is particularly suitable for displays which comprise TN-TFT, IPS-TFT and FFS-TFT active matrixes and are high in respond speed, small in thickness, and high in image display quality. The liquid crystal composition comprises the following liquid crystal compounds of I, II, III, IV and V which are shown in the description.

Owner:SHIJIAZHUANG CHENGZHI YONGHUA DISPLAY MATERIALS CO LTD

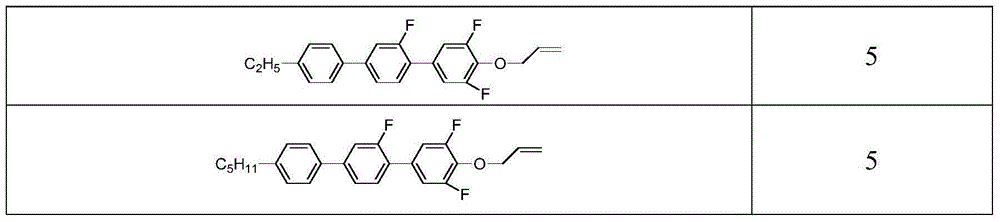

Campus bullying behavior early warning system and method based on artificial intelligence technology

InactiveCN110348754ALower the K valueIncrease K valueResourcesArtificial Intelligence SystemIntelligence analysis

The invention discloses a campus bulwark behavior early warning system and method based on an artificial intelligence technology. The system comprises a processor, a student terminal and a teacher terminal. The processor is used for executing calculation and artificial intelligence analysis; the student terminal is used for students to carry out bulking alarm, the teacher terminal is used for teachers to receive information sent by the processor and carry out subsequent processing according to the sent information, the processor comprises a memory, a basic database is stored in the memory, andthe basic database comprises information of all students. The system can be used for carrying out accurate bulking early warning.

Owner:郭俊雄

Method for producing multilayer metal-silicon nitride-metal capacitor

ActiveCN102592968AIncrease capacitanceImprove electrical uniformitySemiconductor/solid-state device manufacturingCapacitanceElectricity

The invention provides a method for producing a multilayer metal-silicon nitride-metal capacitor, which includes the following steps: 1) using a plasma enhanced chemical vapor deposition (PECVD) method to deposit a silicon nitride thin film with a high k value on a silicon chip substrate; 2) removing silicon nitride in a non-metal-oxide-metal area through photoetching and etching; 3) depositing a dielectric layer with a low k value; 4) removing redundant silicon nitride through chemical mechanical polishing, and forming a mixing layer of low-k-value dielectric and silicon nitride; 5) completing photoetching and etching to form a metallic channel in the low-k-value dielectric and the silicon nitride; 6) forming metal fillers of a lead and a metal-oxide-metal (MOM) capacitor after deposition and chemical mechanical polishing of a metal layer are completed; and 7) repeating Step 1) to Step 6) to form multilayer MOM capacitor. The method for producing the multilayer metal-silicon nitride-metal capacitor can effectively improve the capacitance of the interlayer capacitor, can also effectively improve various electric characteristics of the MOM capacitor such as breakdown voltage, leakage current and the like, can effectively improve electric uniformity among various apparatuses, and is very practical.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

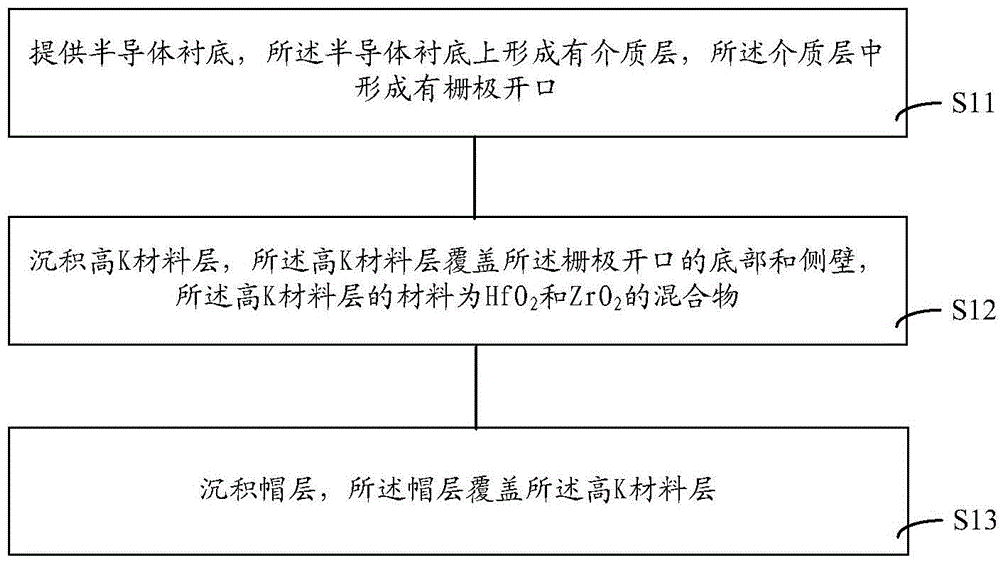

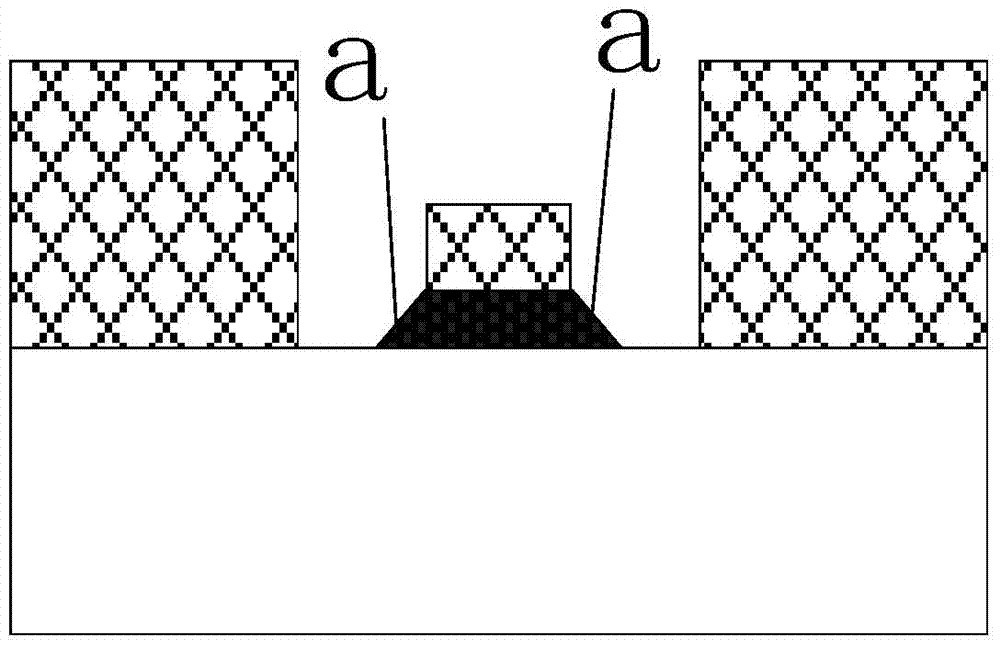

High-K gate dielectric layer formation method and semiconductor device

InactiveCN105304476ASmall grain sizeSmall sizeSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceGate dielectric

The invention provides a high-K gate dielectric layer formation method and a semiconductor device. The method comprises the following steps: providing a semiconductor substrate, a dielectric layer being formed on the semiconductor substrate, and a gate opening being formed in the dielectric layer; and depositing a high-K material layer, wherein the high-K material layer covers the bottom portion and side wall of the gate opening, and the high-K material layer is made of the mixture of HfO2 and ZrO2. The method helps to improve the film quality of a high-K gate dielectric layer, and helps to form the high-K gate dielectric layer having higher K value and thinner equivalent oxide layer thickness.

Owner:SEMICON MFG INT (SHANGHAI) CORP

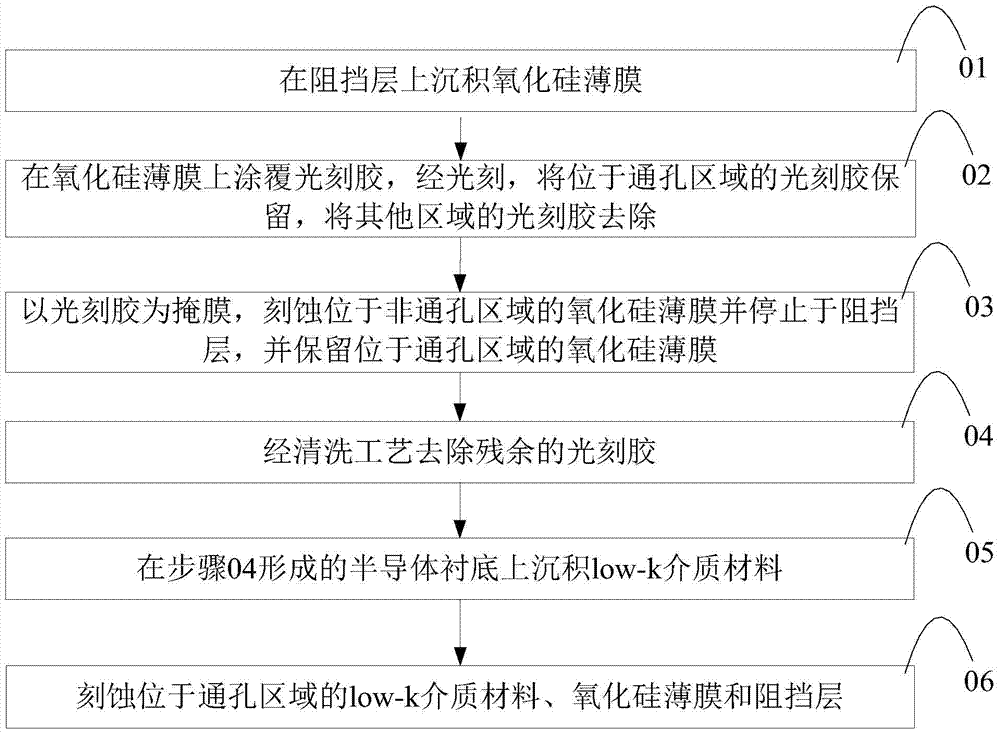

A method for reducing the k value of the dielectric material between vias in the back-end copper interconnection process

ActiveCN104505367BIncrease K valueAvoid breakdown leakageSolid-state devicesSemiconductor/solid-state device manufacturingCopper interconnectSilicon oxide

The invention provides a method for lowering k value of a dielectric material among through holes in a back end copper interconnect process. After deposition of a barrier layer, a silicon oxide film is deposited; before deposition of a low-k dielectric material, a silicon oxide film in a non through hole area is etched, and a silicon oxide film in a through hole area is reserved, so that in following process of etching of through holes, a slope is formed on a side wall of the silicon oxide film as the silicon oxide film is hard and has a low etching rate, another slope is also formed on a side wall of the barrier layer, and the two slopes jointly form a through hole slope. Compared with the through hole slopes prepared by conventional technologies, the through hole slope prepared by the method is increased in height and angle, so that electric leakage caused by breakdown of a metal piece due to too small corner cut of the through holes is prevented; furthermore, the k value of the dielectric material among the through holes is increased as the bottom of the low-k dielectric material has silicon oxide and nitrogen doped silicon carbide in the prior art, however, the k value can be reduced by adopting the method.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Liquid crystal composition, liquid crystal display element and liquid crystal display

ActiveCN112080287AIncrease K valueHD highlightsLiquid crystal compositionsNon-linear opticsCrystallographyLiquid-crystal display

The invention relates to a liquid crystal composition, a liquid crystal display element containing the liquid crystal composition and a liquid crystal display, and belongs to the field of liquid crystal display. The liquid crystal composition disclosed by the invention comprises a compound shown as a formula I, one or more compounds shown as a formula II and one or more polymerizable compounds, and the liquid crystal composition has a large K value, a relatively high clearing point (CP) and a large dielectric property (delta epsilon).

Owner:SHIJIAZHUANG CHENGZHI YONGHUA DISPLAY MATERIALS CO LTD

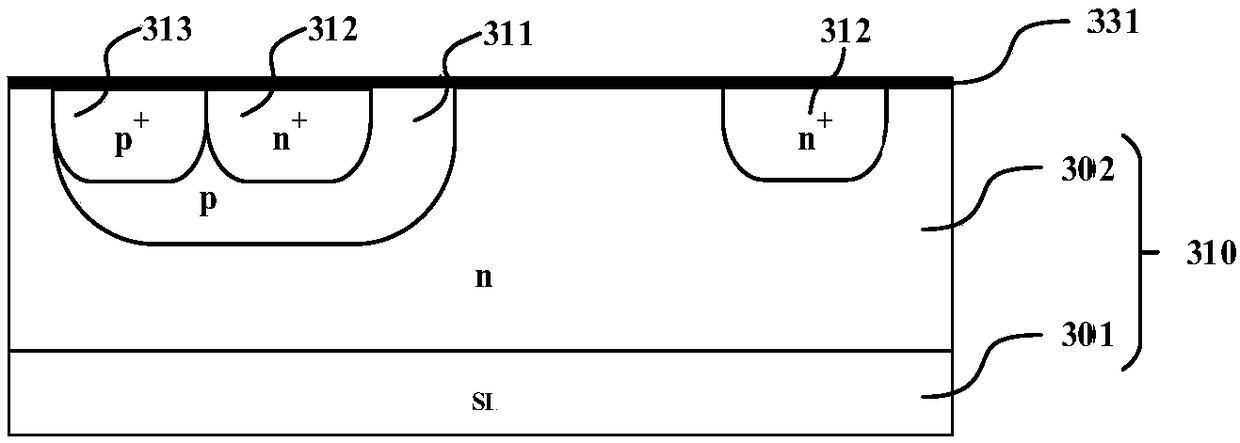

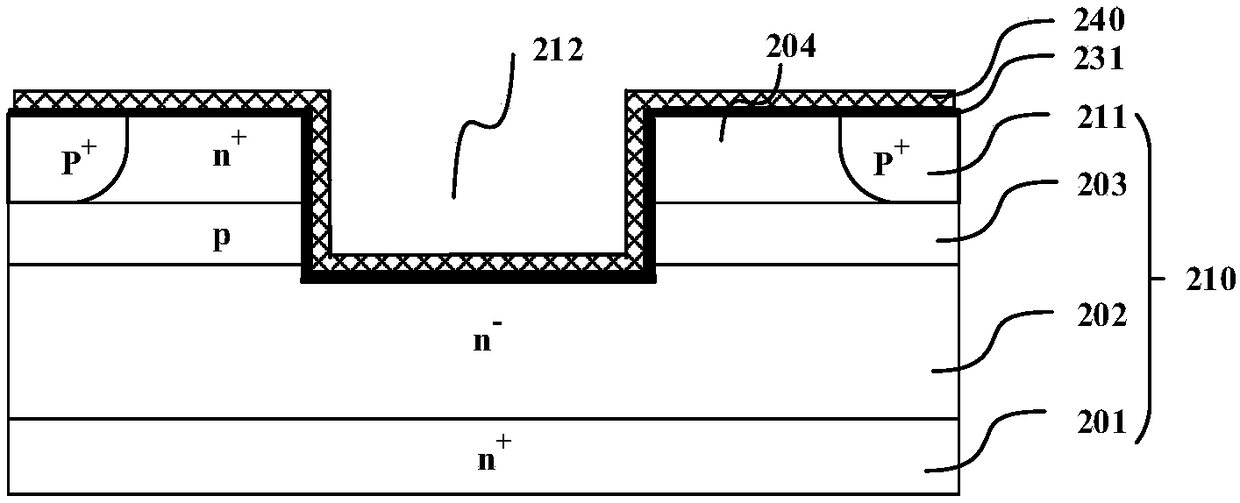

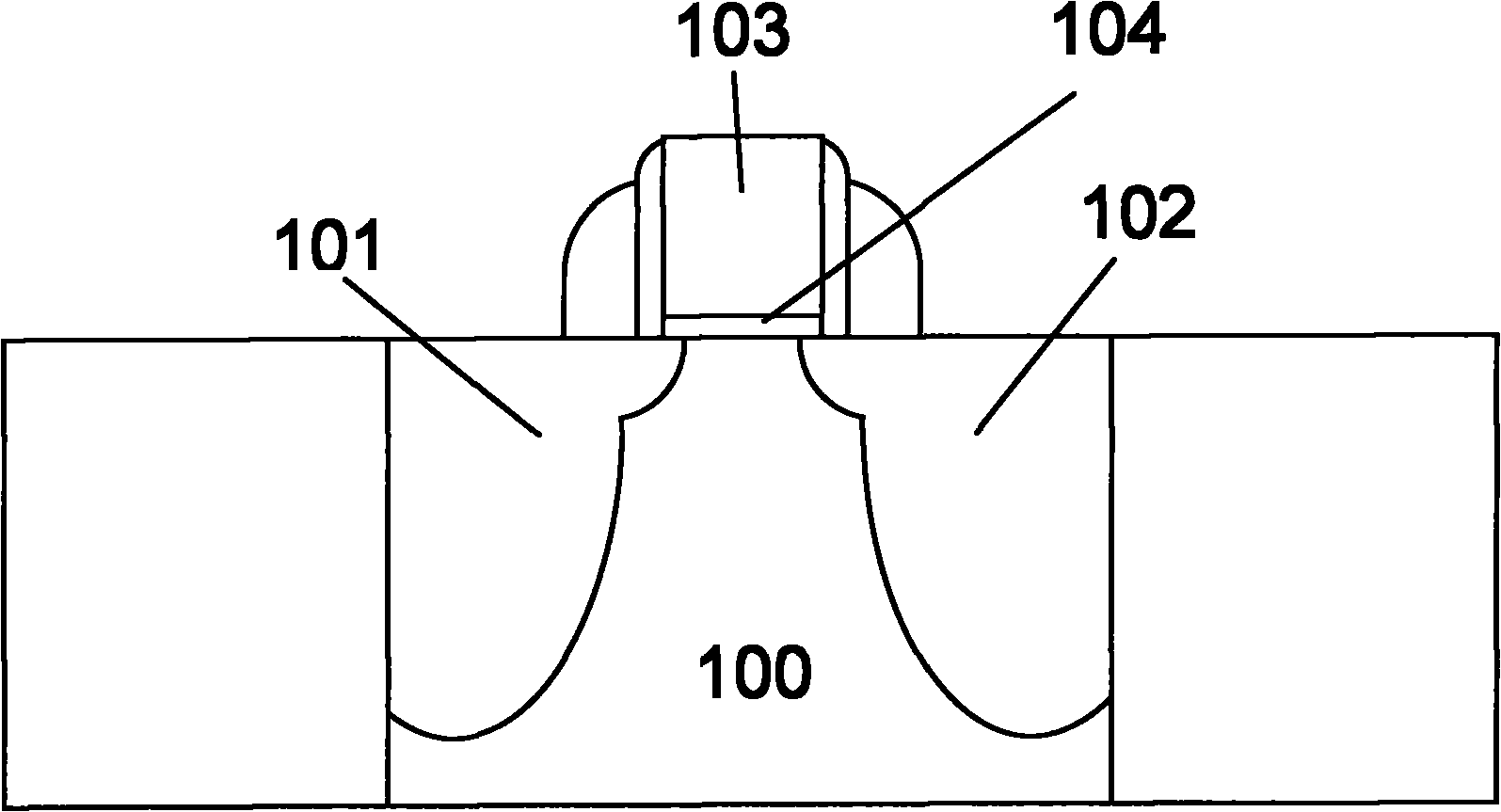

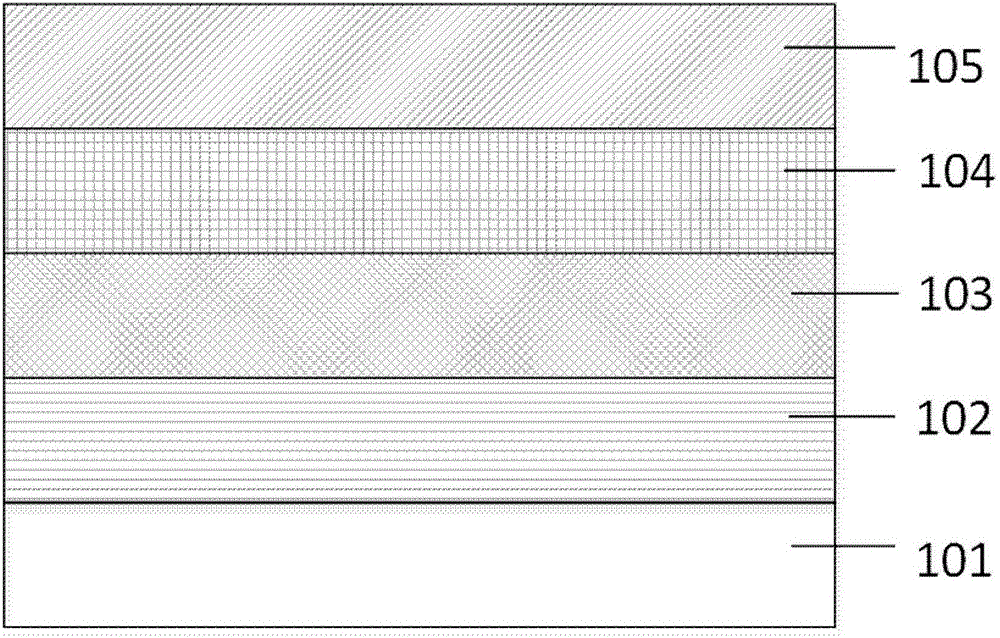

InP substrate MOSCAP structure and manufacturing method thereof

InactiveCN106298780AReduce leakageImprove reliabilityTransistorSolid-state devicesGate dielectricSemiconductor

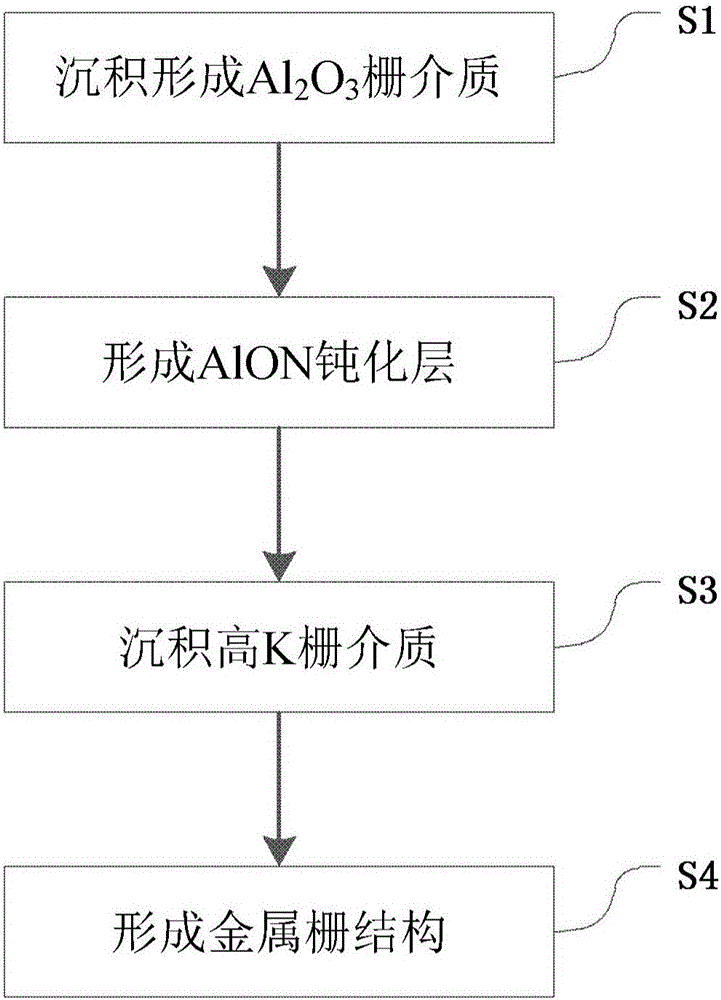

The invention discloses an InP substrate MOSCAP structure and a manufacturing method thereof. The method includes the steps that S1, an Al2O3 gate dielectric (102) is deposited on an InP substrate; S2, N2 plasma treatment is conducted on the surface of the Al2O3 gate dielectric to form an AlON passivation layer (103); S3, a high-K gate dielectric (104) is deposited on the AlON passivation layer; S4, a metal gate structure (105) is formed on the high-K gate dielectric. The AlON passivation layer is formed by conducting N2 plasma treatment on the surface of the Al2O3 gate dielectric, and the high-K gate dielectric grows on the AlON passivation layer, so that defects in the Al2O3 gate dielectric are effectively repaired, the quality of the gate dielectric is greatly improved, EOT is reduced while grid electrode electric leakage is reduced, device reliability is improved, and electrical properties of III-V semiconductors (MOS) are greatly improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

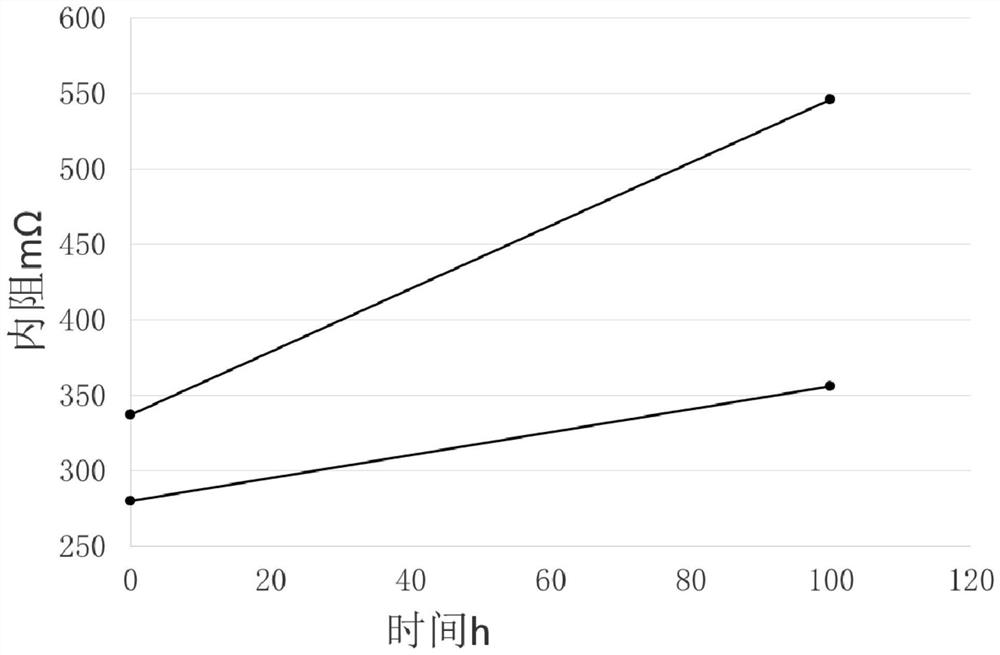

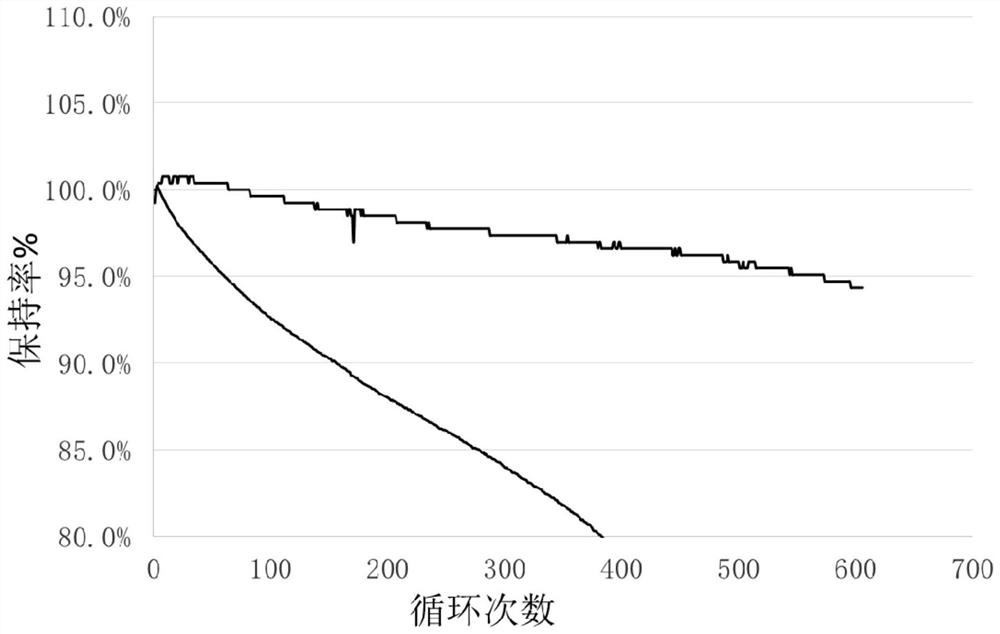

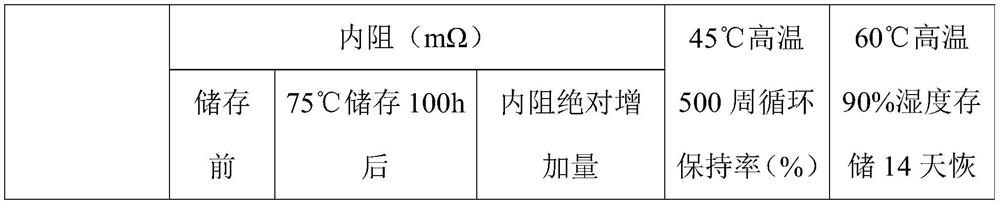

Anti-corrosion electrode shell of steel shell button cell, preparation method of anti-corrosion electrode shell, steel shell button cell and application of steel shell button cell

InactiveCN112713338AIncrease K valueImprove yieldEarpiece/earphone attachmentsCell component detailsSS - Stainless steelBattery cell

The invention provides an anti-corrosion electrode shell of a steel shell button cell, which comprises a stainless steel substrate and a coating which is coated on the inner surface of the stainless steel substrate and has the thickness of at least 10 mu m, the coating can prevent corrosion of the positive electrode shell due to high potential and corrosion of the negative electrode under low potential in high-temperature circulation and high-temperature and high-humidity storage processes, effectively alleviates the problems of blackening and yellowing of the positive electrode shell of the steel shell button cell, can also improve the K value, yield and appearance of the cell, does not need to change the existing process, and is suitable for large-scale production; only the coating design needs to be added, the cost increase is relatively low, and the application prospect is wide.

Owner:EVE HYPERPOWER BATTERIES INC +1