InP substrate MOSCAP structure and manufacturing method thereof

A technology of substrate and film, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of large leakage and high interface state density, reduce gate leakage, improve reliability, and reduce EOT Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

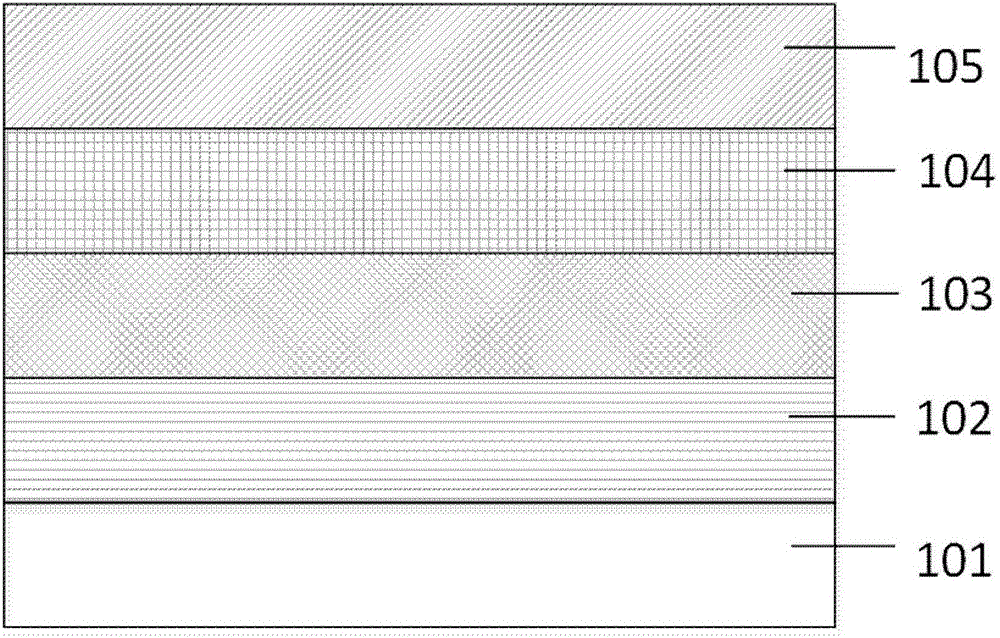

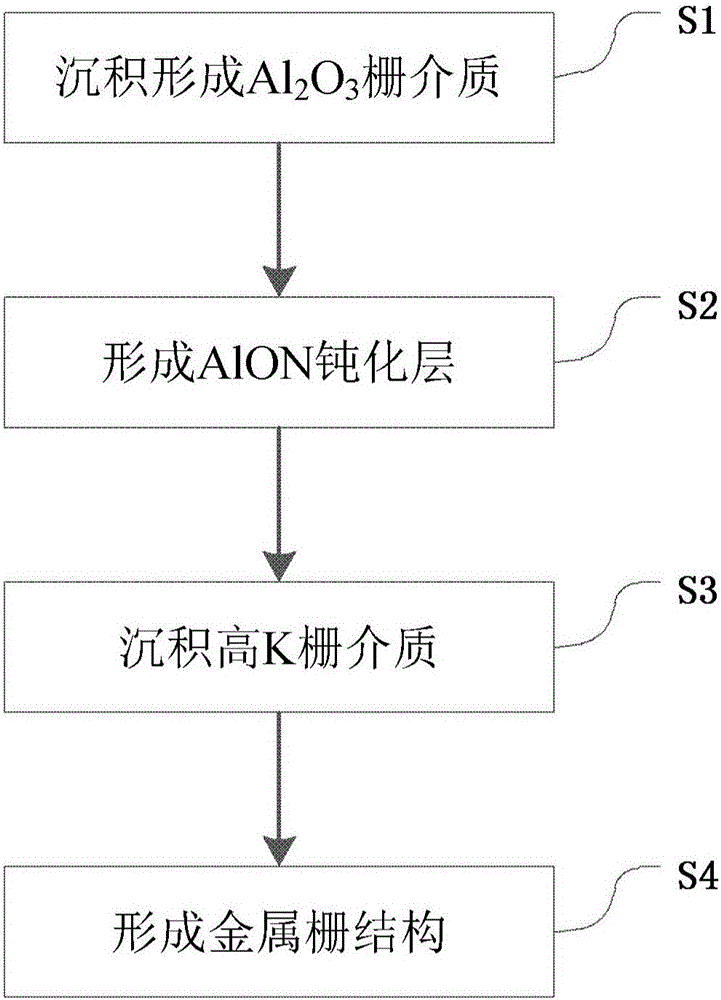

[0026] The present invention proposes a structure of InP substrate MOSCAP and its preparation method. An AlON passivation layer is formed by N2 plasma treatment on the surface of the Al2O3 gate dielectric, and a high-K gate dielectric is grown on the AlON passivation layer, which can effectively repair the Al 2 o 3 Defects in the gate dielectric improve the quality of the gate dielectric, reduce gate leakage, and improve device reliability. The AlON passivation layer improves the Al 2 o 3 The K value and depositing a high-K gate dielectric on the AlON passivation layer reduces the EOT, thereby greatly improving the electrical performance of the InP MOSCAP capacitor. But the passivation layer is not limited to N2 plasma treatment, it can also be grown after Al 2 o 3 Afterwards, N2 annealing is carried out.

[0027] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More