Method of forming opening

A patterned, gas technology, applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of the influence of the electrical performance of the semiconductor device, the damage of the inner wall of the opening, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

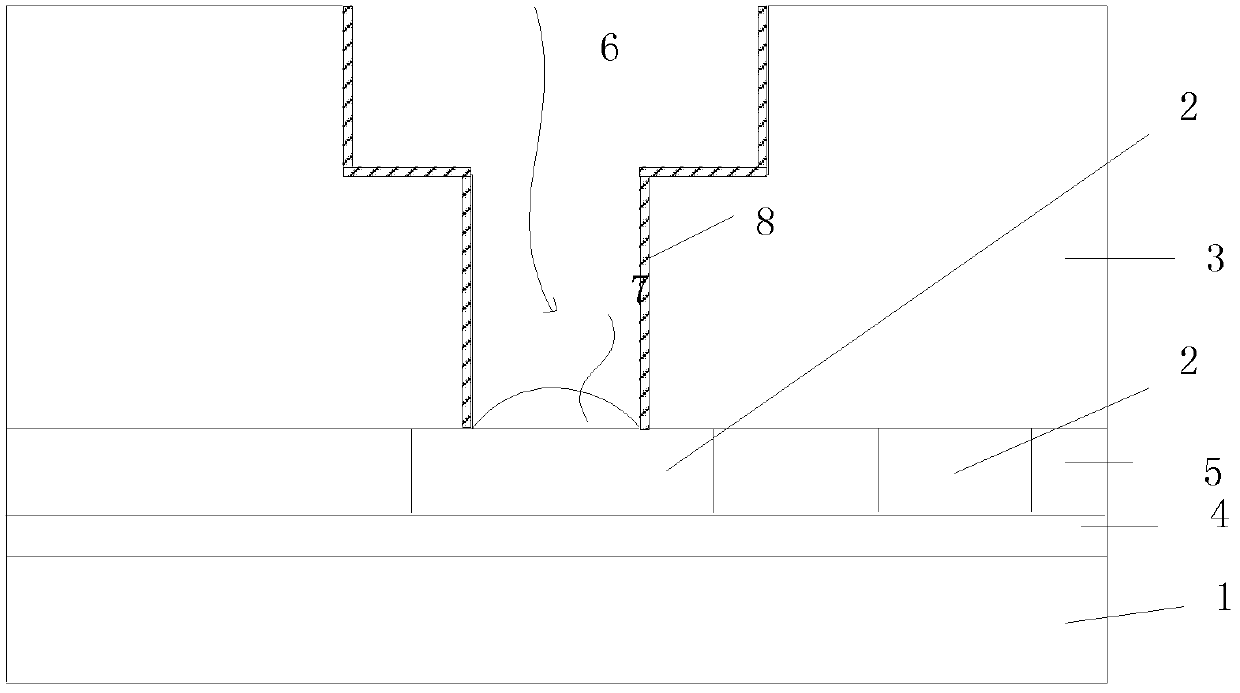

[0048] Figure 3 to Figure 14 It is a schematic diagram of an embodiment of forming a dual damascene structure with openings in the first embodiment of the present invention.

[0049] like image 3 As shown, a semiconductor substrate 10 is provided, and the semiconductor substrate 10 may be a monocrystalline silicon (monocrystalline) substrate or a silicon on insulator (silicon on insulator) substrate. Of course, it can also be other substrate materials known to those skilled in the art. Wherein, semiconductor elements, such as transistors, capacitors, rectifiers, etc., may have been formed on the semiconductor substrate 10 .

[0050] like Figure 4 As shown, a first interlayer dielectric layer 11 is formed on a semiconductor substrate 10 formed with semiconductor devices.

[0051] In this embodiment, the process for forming the first interlayer dielectric layer 11 may be chemical vapor deposition (CVD), physical vapor deposition (PVD), etc.; the material of the first inte...

Embodiment 2

[0083] The difference between the second embodiment and the above embodiment is that before forming the first patterned photoresist layer, a patterned hard mask layer can also be formed on the dielectric layer, and the patterned hard mask layer is used Where the trenches are defined, the photoresist layer is patterned to define the via hole locations, and then the remaining photoresist layer and hard mask layer are removed. details as follows:

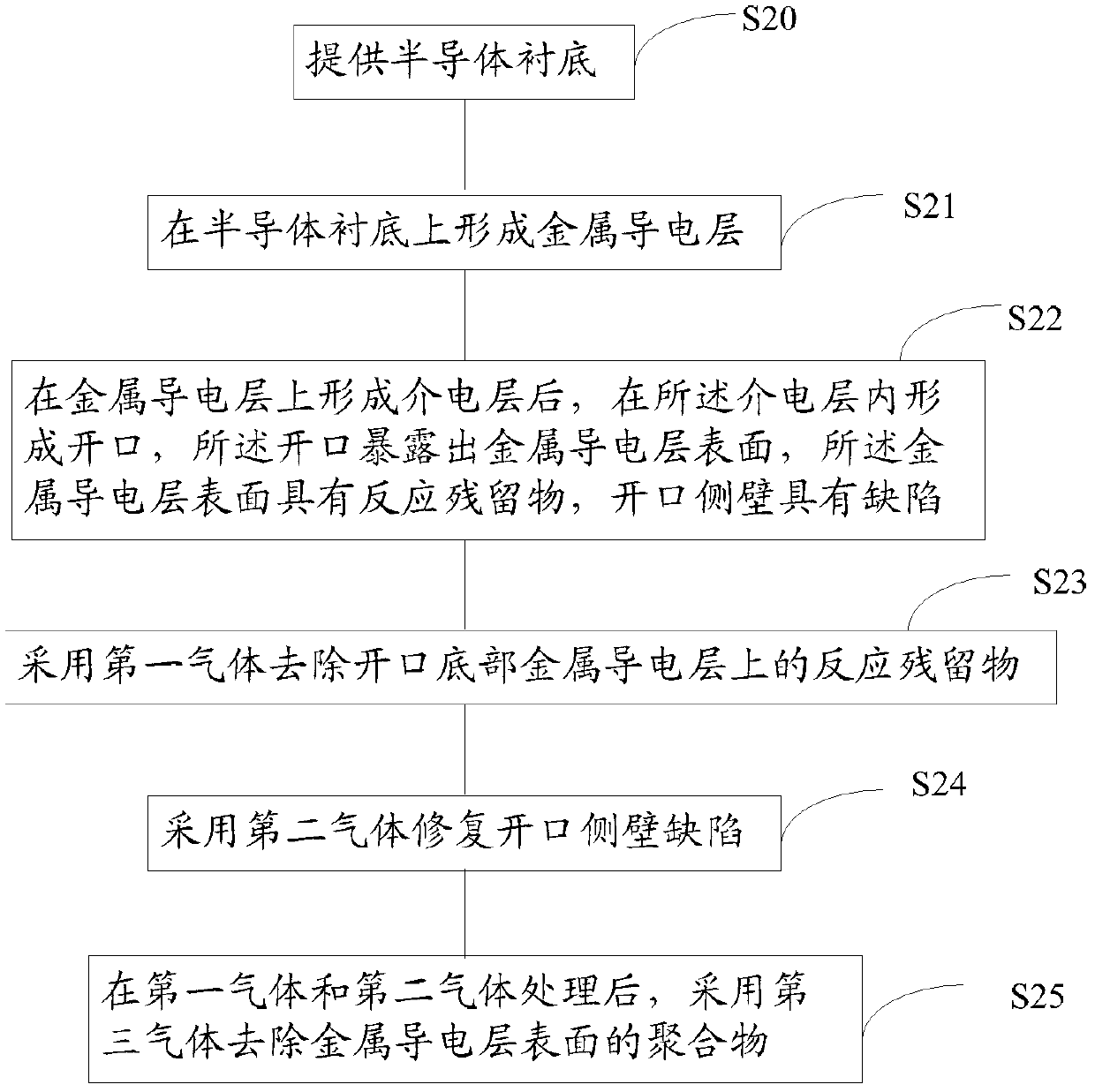

[0084] Firstly, a semiconductor substrate is provided; a metal conductive layer is formed on the semiconductor substrate; a dielectric layer is formed on the metal conductive layer, please refer to the first embodiment for details.

[0085] Next, a hard mask layer is formed on the dielectric layer.

[0086] The hard mask layer may be formed of common hard mask materials, such as silicon oxide, silicon nitride, silicon oxynitride, and silicon carbide. However, as the size of semiconductor devices continues to shrink, it becomes more a...

Embodiment 3

[0092] In the above embodiment, the first gas to the third gas are used to perform post-etching treatment on the dual damascene openings. In the third embodiment, the first gas to the third gas are used to directly perform post-etching treatment to the via holes in the dielectric layer.

[0093] like Figure 15 As shown, a semiconductor substrate 40 is provided, please refer to the first embodiment for details.

[0094] like Figure 16 As shown, a first interlayer dielectric layer 41 is formed on a semiconductor substrate 40 formed with semiconductor devices; a discrete metal conductive layer 42 is formed on the first interlayer dielectric layer 41, and the metal conductive layer 42 passes through the first interlayer dielectric layer 41. The conductive structure in the interlayer dielectric layer 41 is connected to the semiconductor element on the semiconductor substrate 40; the second interlayer dielectric layer 43 is formed on the first interlayer dielectric layer 41 betwe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More