High-K gate dielectric layer formation method and semiconductor device

A gate dielectric layer and semiconductor technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of thick equivalent oxide layer, poor film quality, instability, etc., and achieve thin equivalent Thickness of oxide layer, high K value, effect of increasing K value

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The present invention will be further described below with reference to specific embodiments and drawings, but the protection scope of the present invention should not be limited by this.

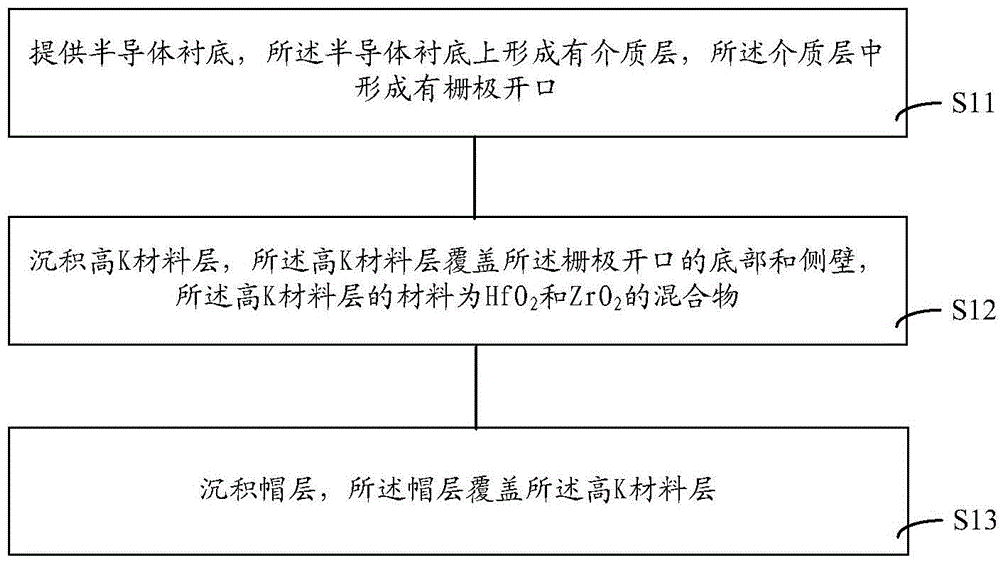

[0042] reference image 3 The method for forming the high-K gate dielectric layer of this embodiment includes the following steps:

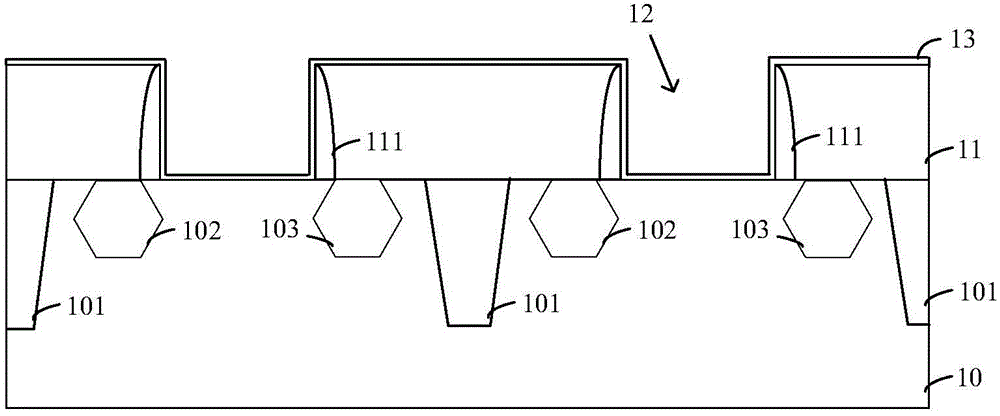

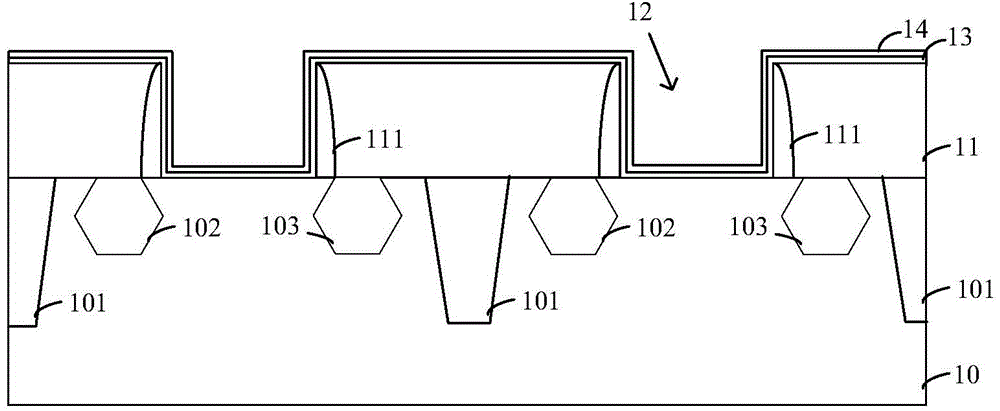

[0043] Step S11, providing a semiconductor substrate, a dielectric layer is formed on the semiconductor substrate, and a gate opening is formed in the dielectric layer;

[0044] Step S12, deposit a high-K material layer, the high-K material layer covers the bottom and sidewalls of the gate opening, and the material of the high-K material layer is HfO 2 And ZrO 2 mixture;

[0045] Step S13, depositing a cap layer, the cap layer covering the high-K material layer.

[0046] Combine below Figure 4 to Figure 13 Give details.

[0047] reference Figure 4 A semiconductor substrate 20 is provided, and a dummy gate 204 is formed on the semiconductor substrate 20, and a sp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More