Patents

Literature

54results about How to "Improve electrical uniformity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

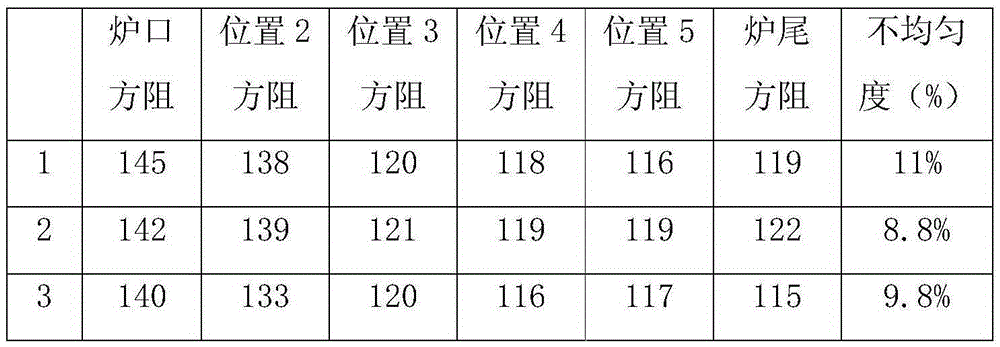

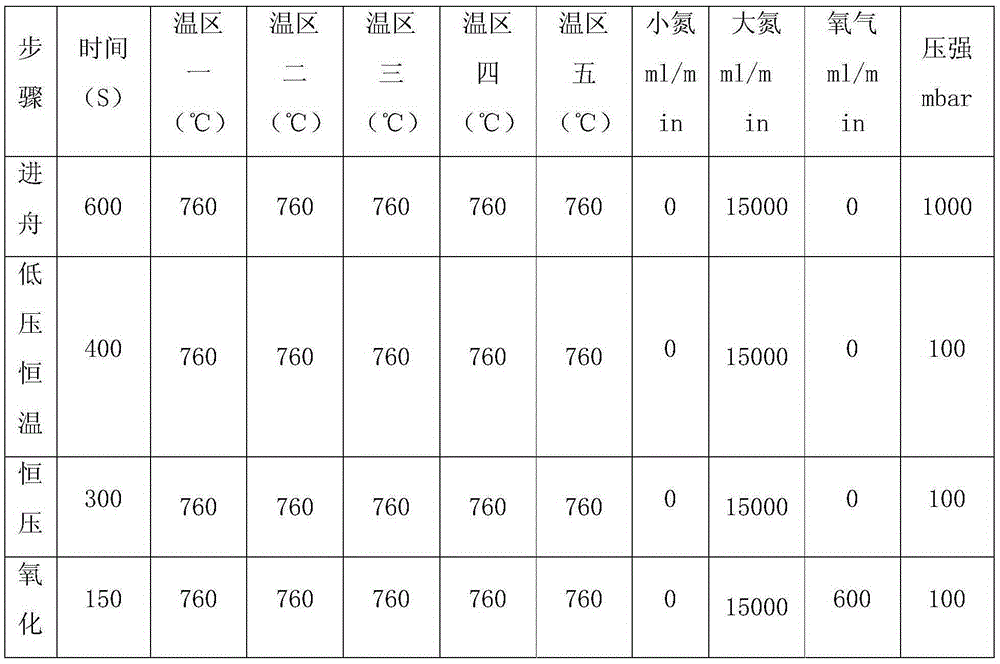

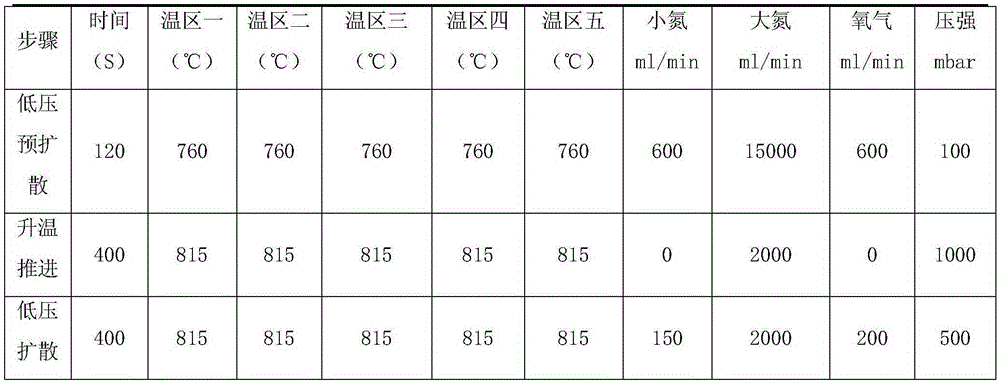

Low-pressure diffusion technology for crystalline silicon cell

ActiveCN105261670AIncrease chance of contactImprove uniformityFinal product manufactureSemiconductor/solid-state device manufacturingDiffusion methodsInternal pressure

The invention discloses a low-pressure diffusion technology for a crystalline silicon cell. The technology comprises the following steps: (1) a high-temperature oxidation before diffusion; (2) a low-pressure diffusion, namely preparing a PN knot by a sub-step diffusion method; and (3) annealing, namely changing internal pressure to remove impurities. According to the low-pressure diffusion technology, the uniformity between diffusion sheets can be improved; the temperature of a temperature zone in a fire hole is lowered, namely the temperature uniformity of various temperature zones of a diffusion tube is improved; the problem of a great fluctuation of sheet resistance of the fire hole of a diffusion furnace is solved; the service lifetime of a vacuum pump is prolonged; and the production cost of a diffusion procedure is reduced.

Owner:HUNAN RED SUN PHOTOELECTRICITY SCI & TECH

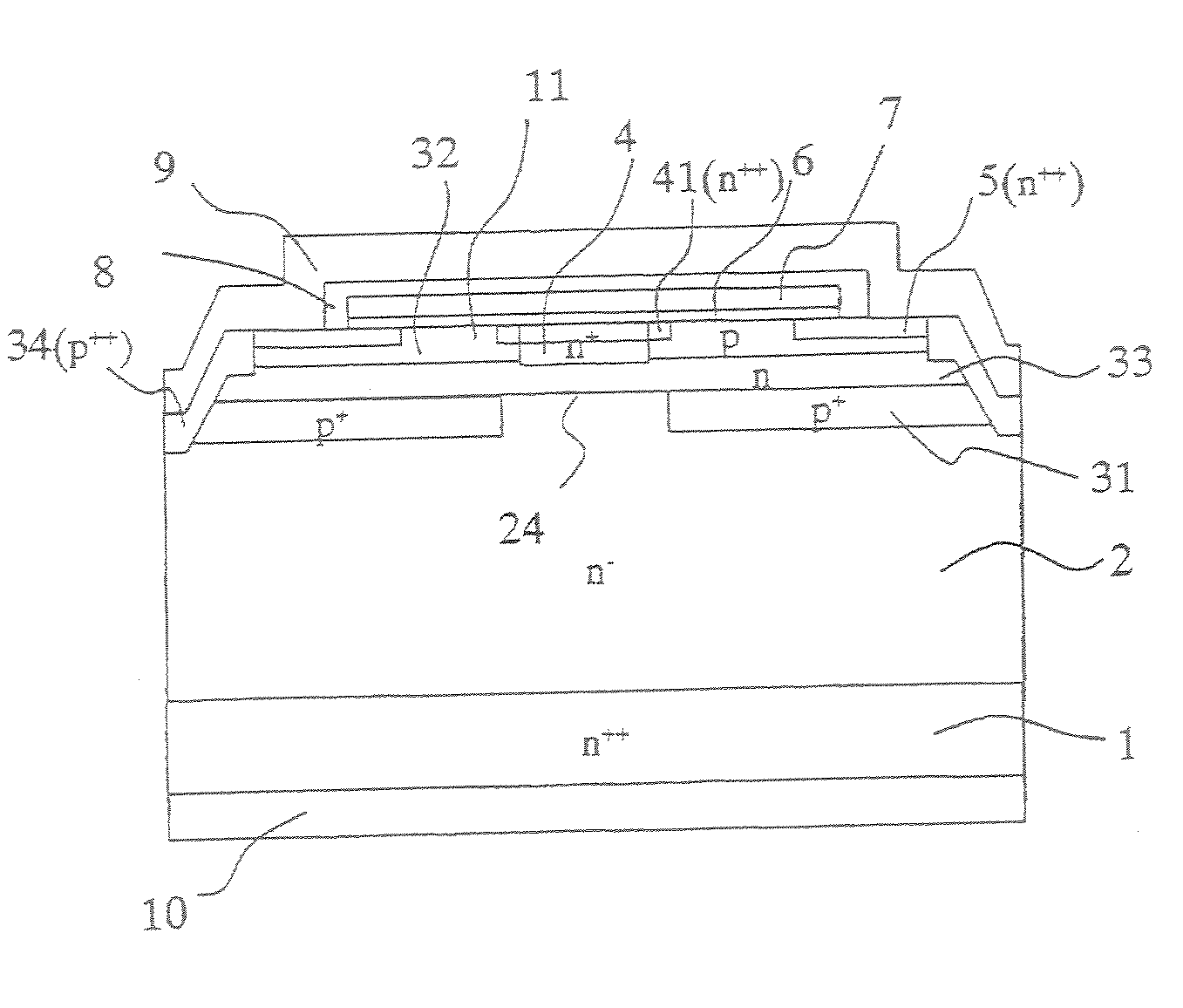

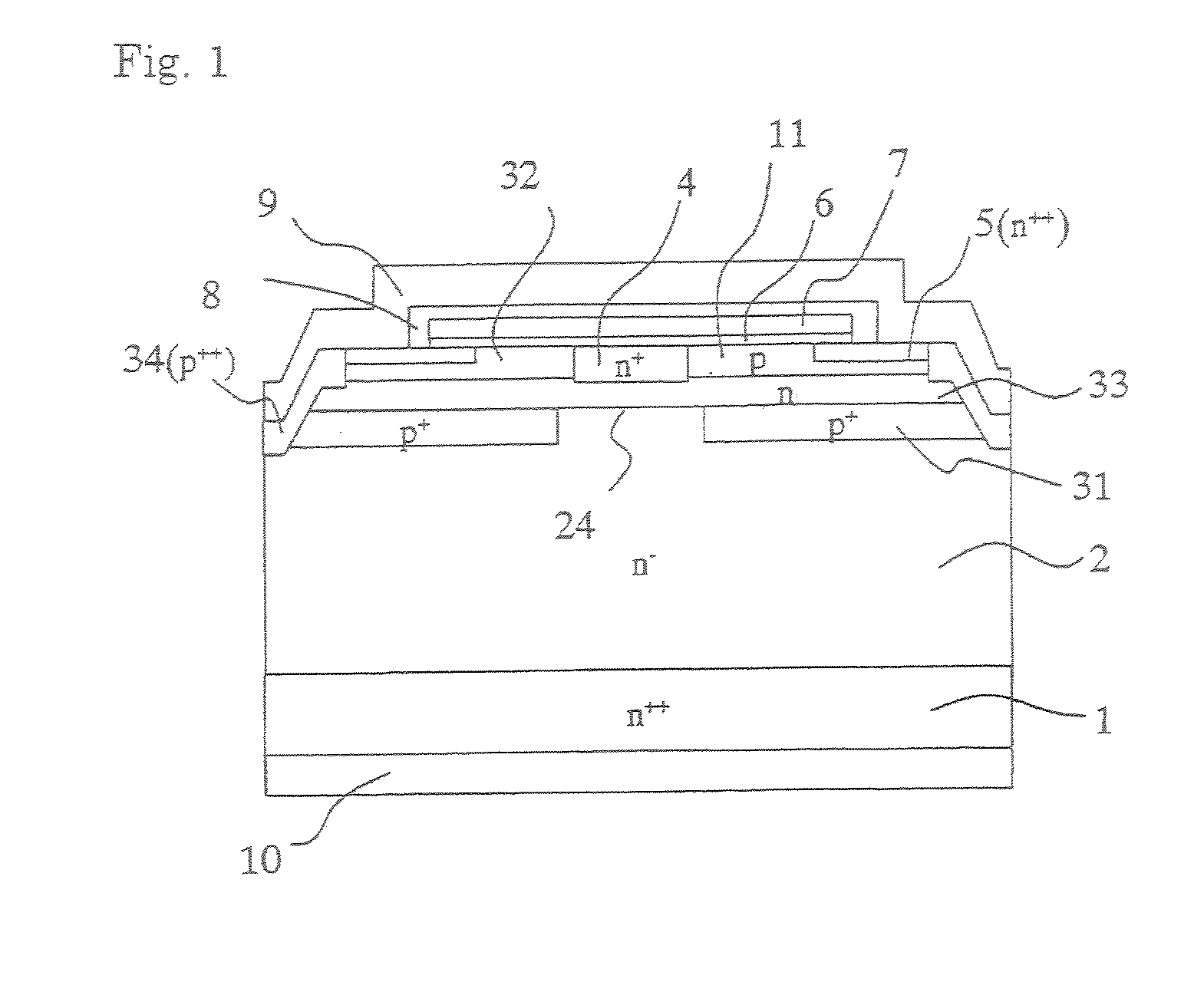

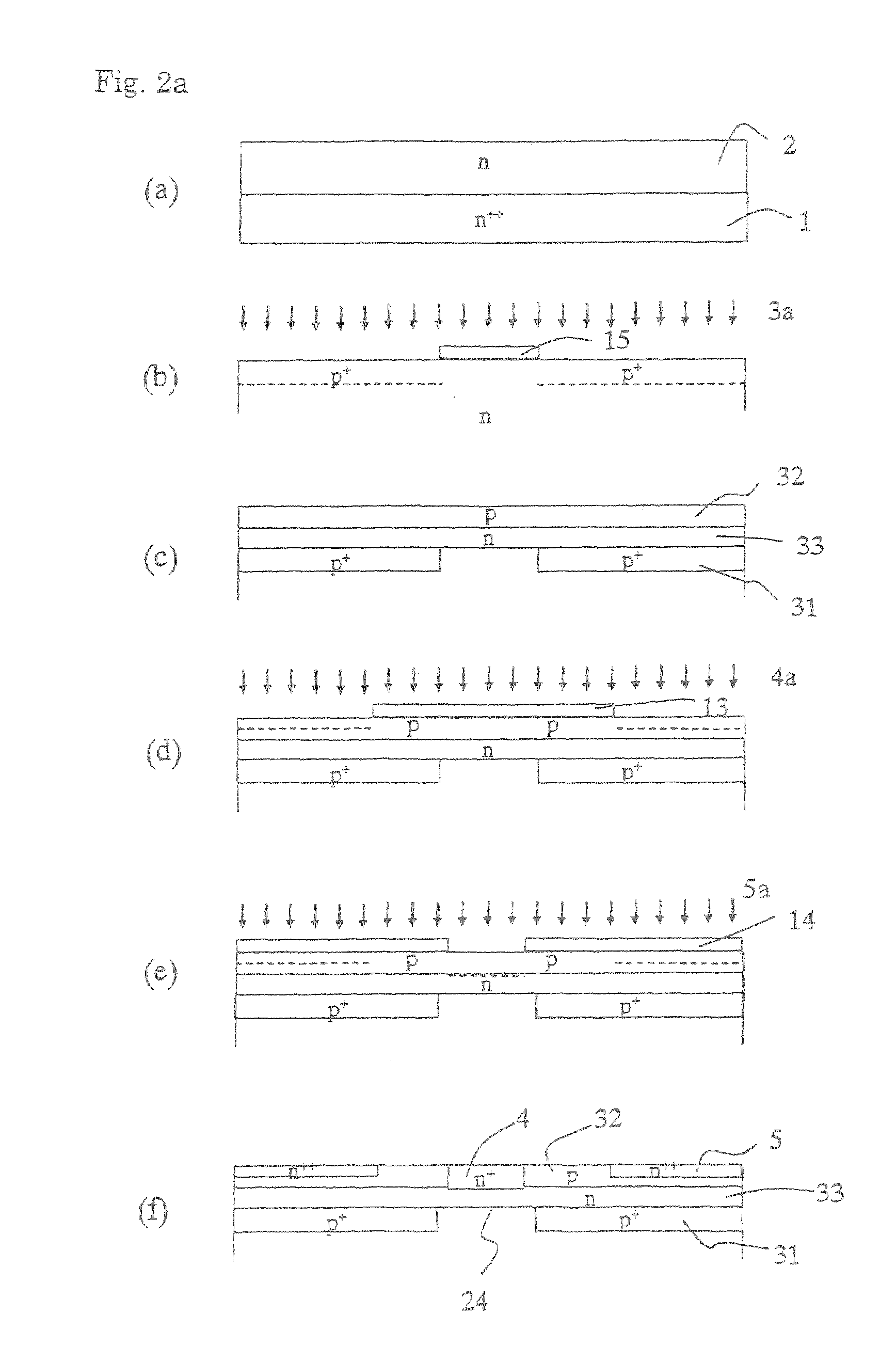

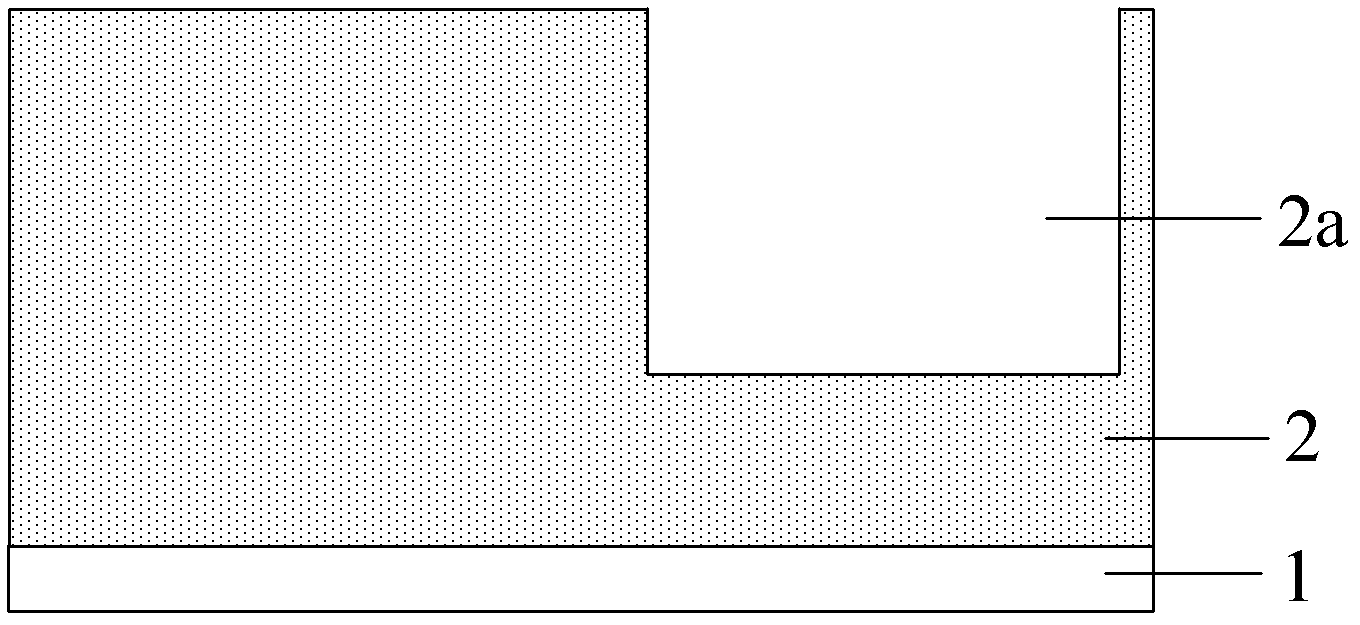

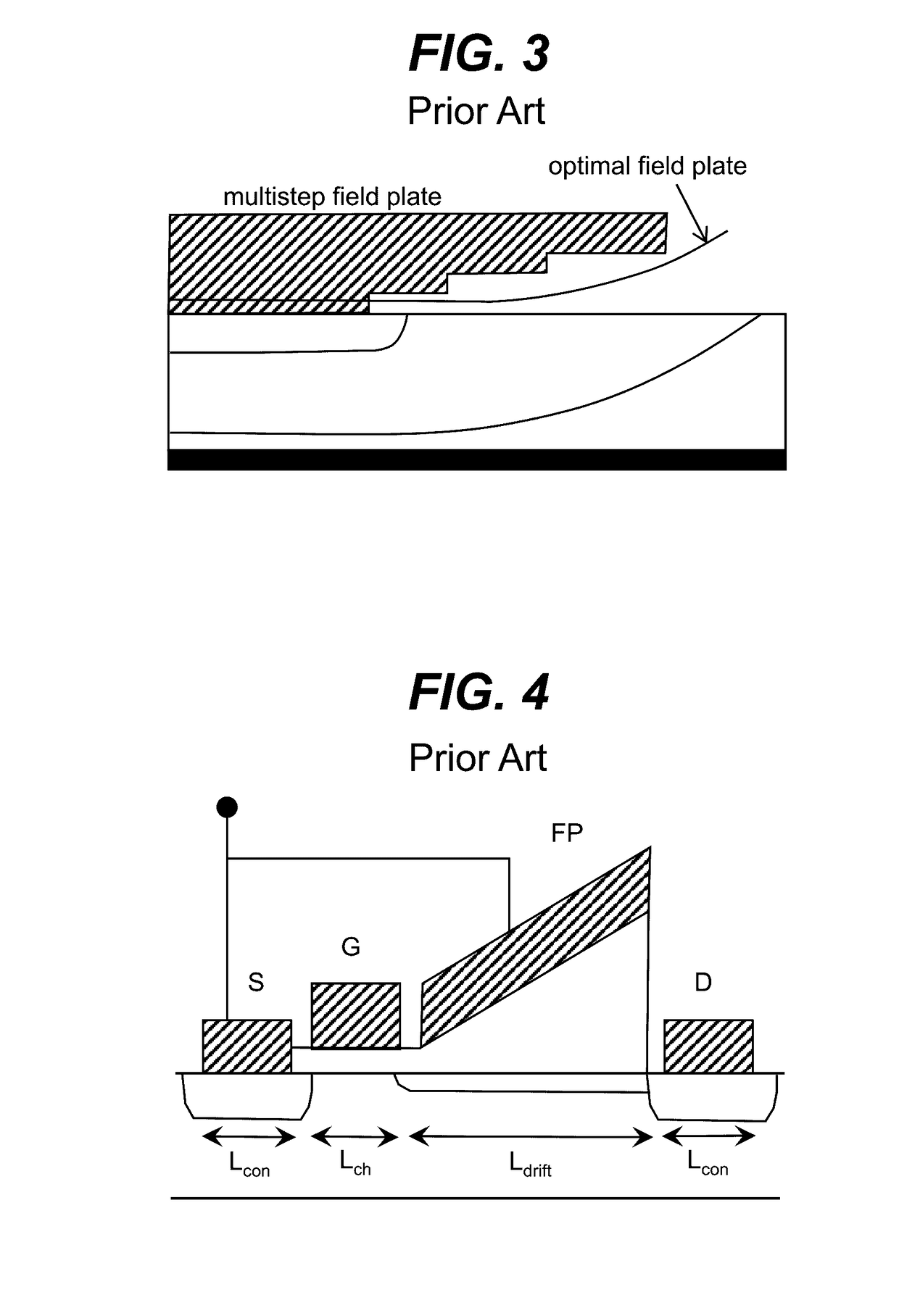

Silicon carbide mos field-effect transistor and process for producing the same

InactiveUS20090134402A1Lower on-resistanceHigh blocking voltageSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETHigh concentration

In the SiC vertical MOSFET having a low-concentration p-type deposition film provided therein with a channel region and a base region resulting from reverse-implantation to n-type through ion implantation, dielectric breakdown of gate oxide film used to occur at the time of off, thereby preventing a further blocking voltage enhancement. This problem has been resolved by interposing of a low-concentration n-type deposition film between a low-concentration p-type deposition film and a high-concentration gate layer and selectively forming of a base region resulting from reverse-implantation to n-type through ion implantation in the low-concentration p-type deposition film so that the thickness of deposition film between the high-concentration gate layer and each of channel region and gate oxide layer is increased.

Owner:NAT INST OF ADVANCED IND SCI & TECH

Preparation method and application of monocrystalline silicon sheet

ActiveCN109747055AIncrease profitEfficient use ofPolycrystalline material growthAfter-treatment detailsNanotechnologySingle crystal silicon

The invention discloses a preparation method and application of a monocrystalline silicon sheet. A monocrystalline silicon rod can be cut to be a strip-shaped right-angle silicon monocrystalline sheetand a monocrystalline silicon quasi square sheet or the strip-shaped right-angle silicon monocrystalline sheet and monocrystalline silicon square sheet, and the using ratio of the monocrystalline silicon rod can be increased.

Owner:CHANGZHOU SHICHUANG ENERGY CO LTD

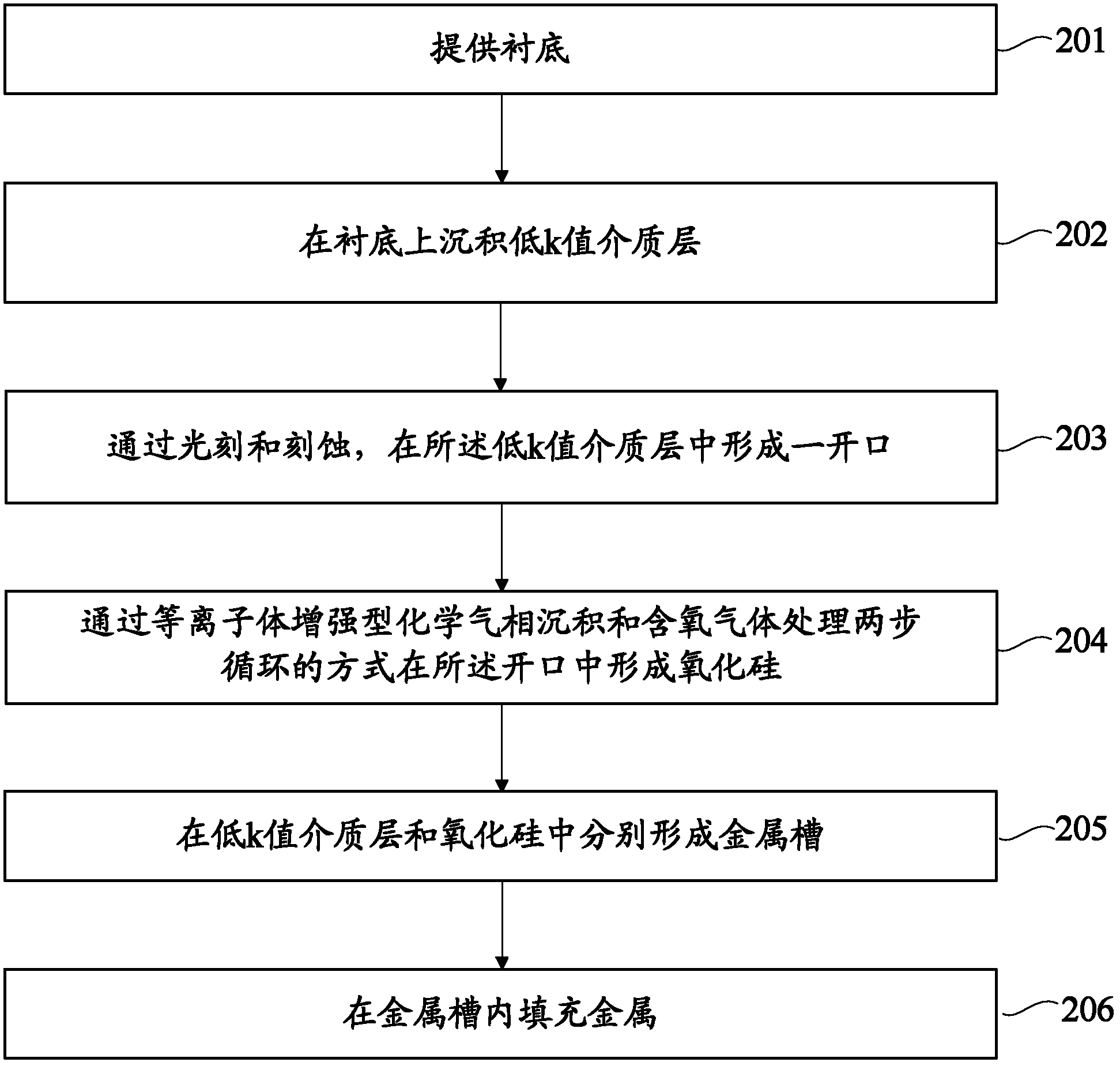

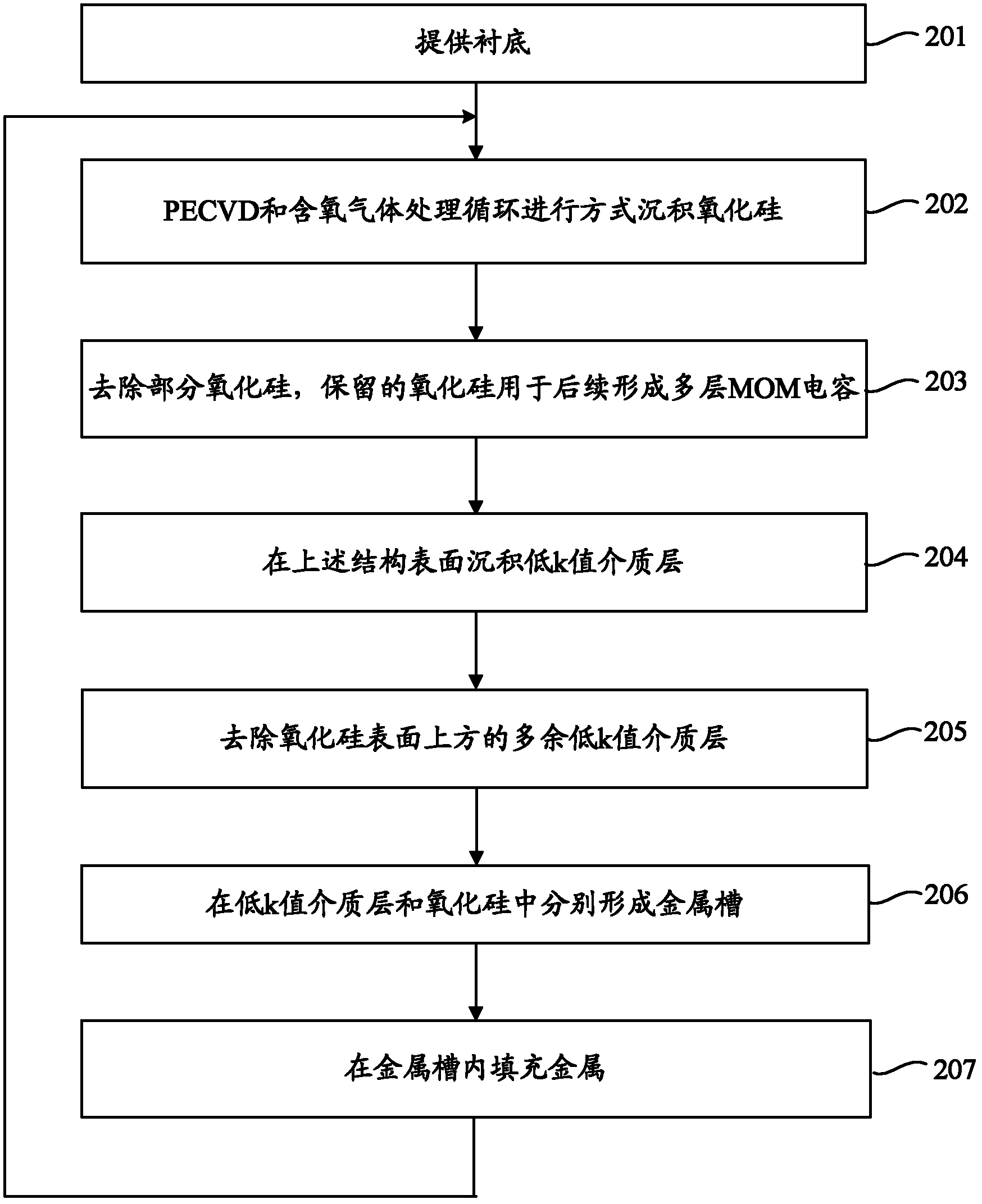

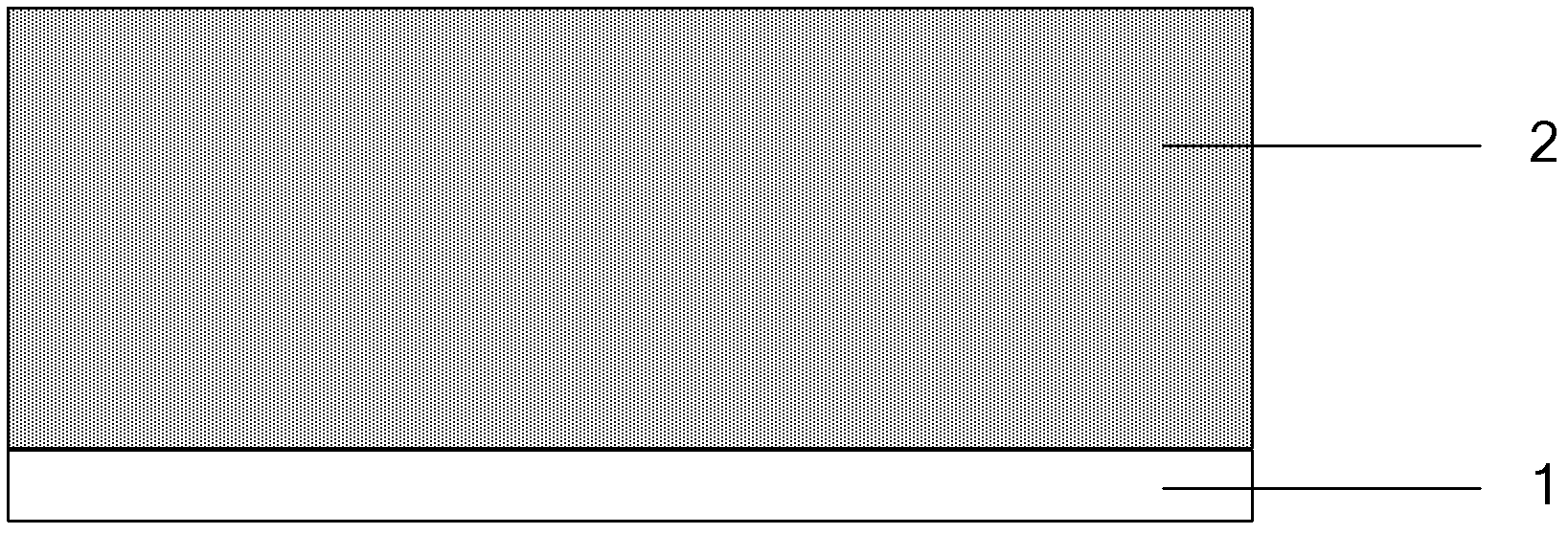

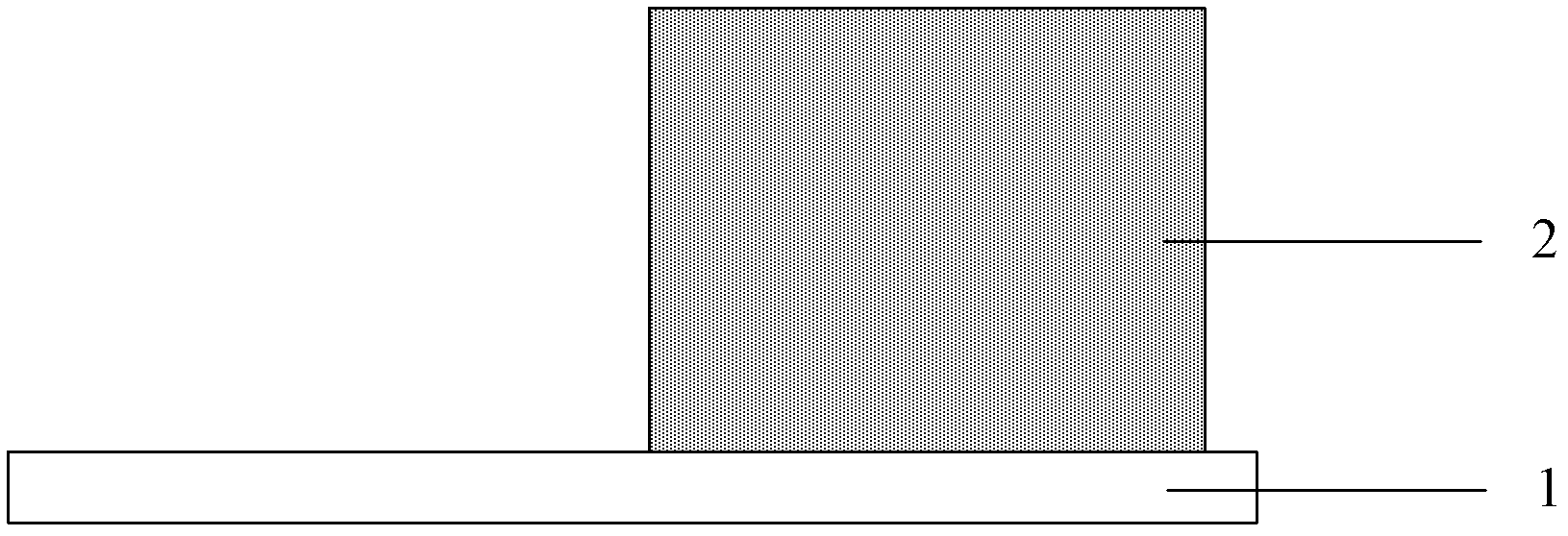

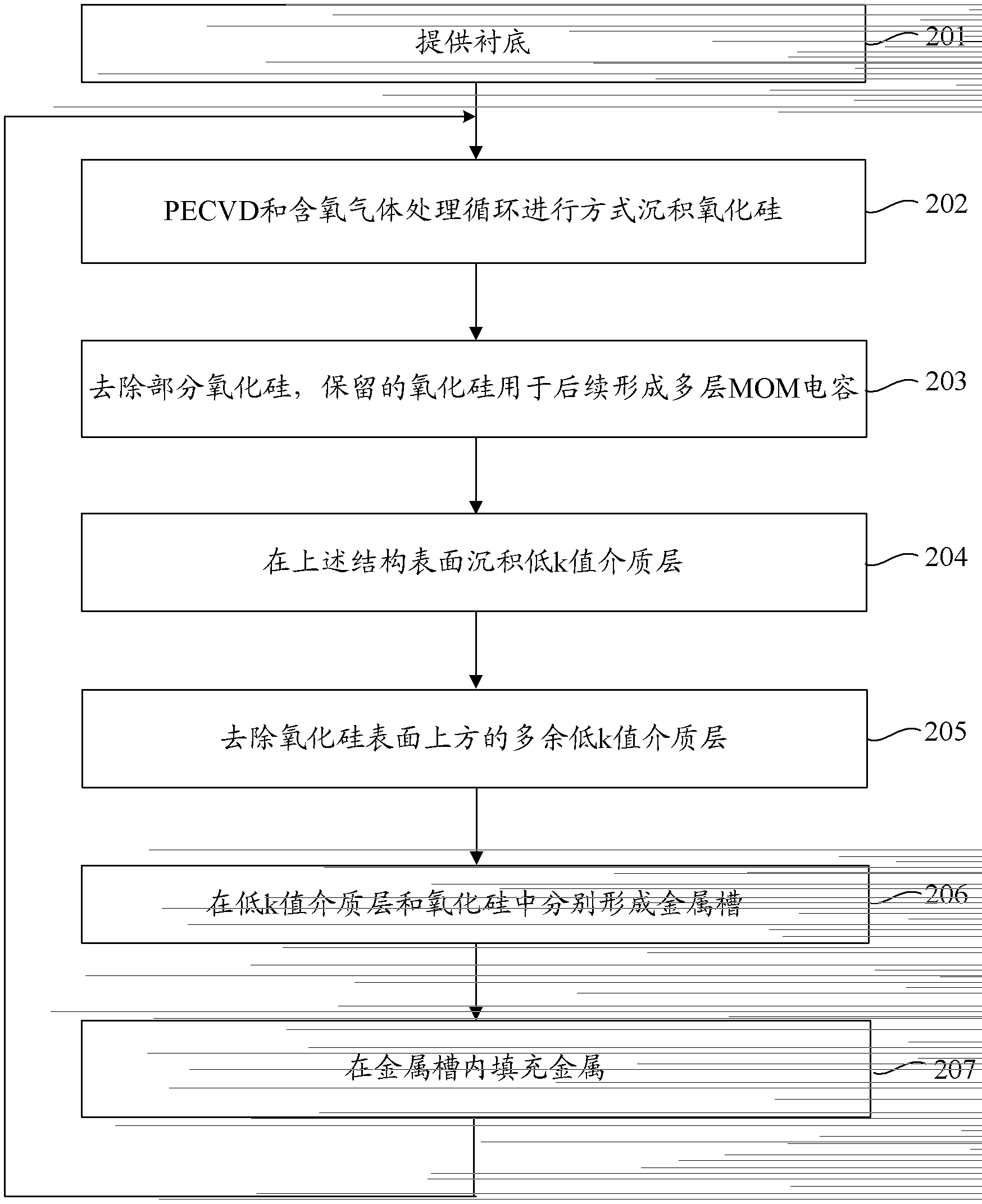

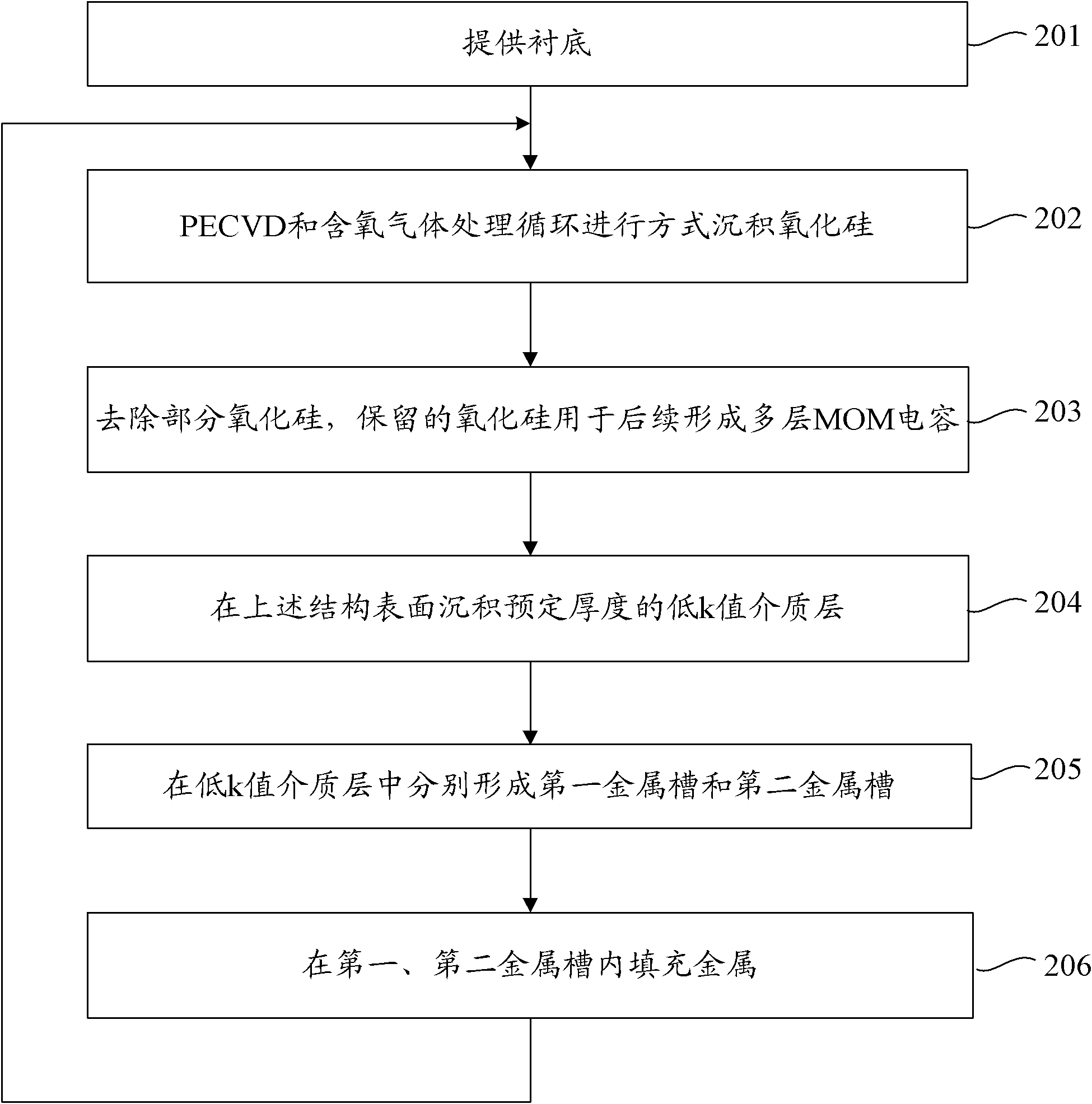

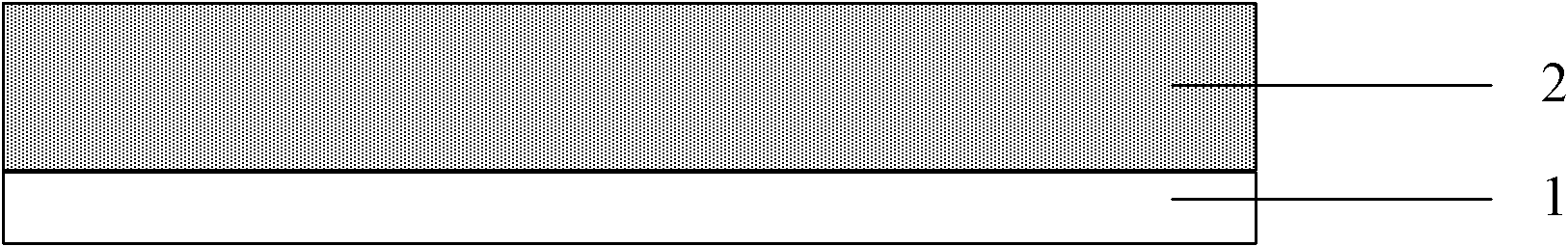

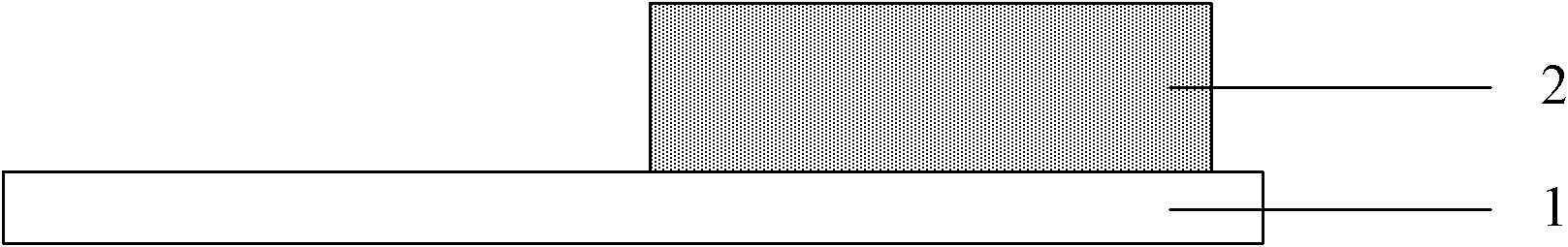

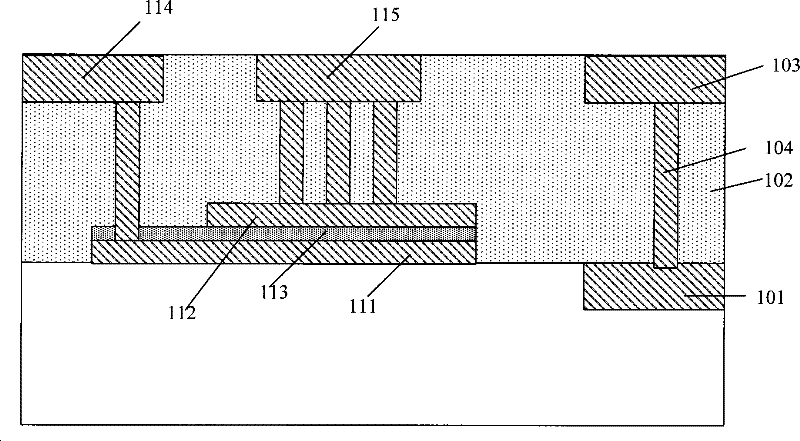

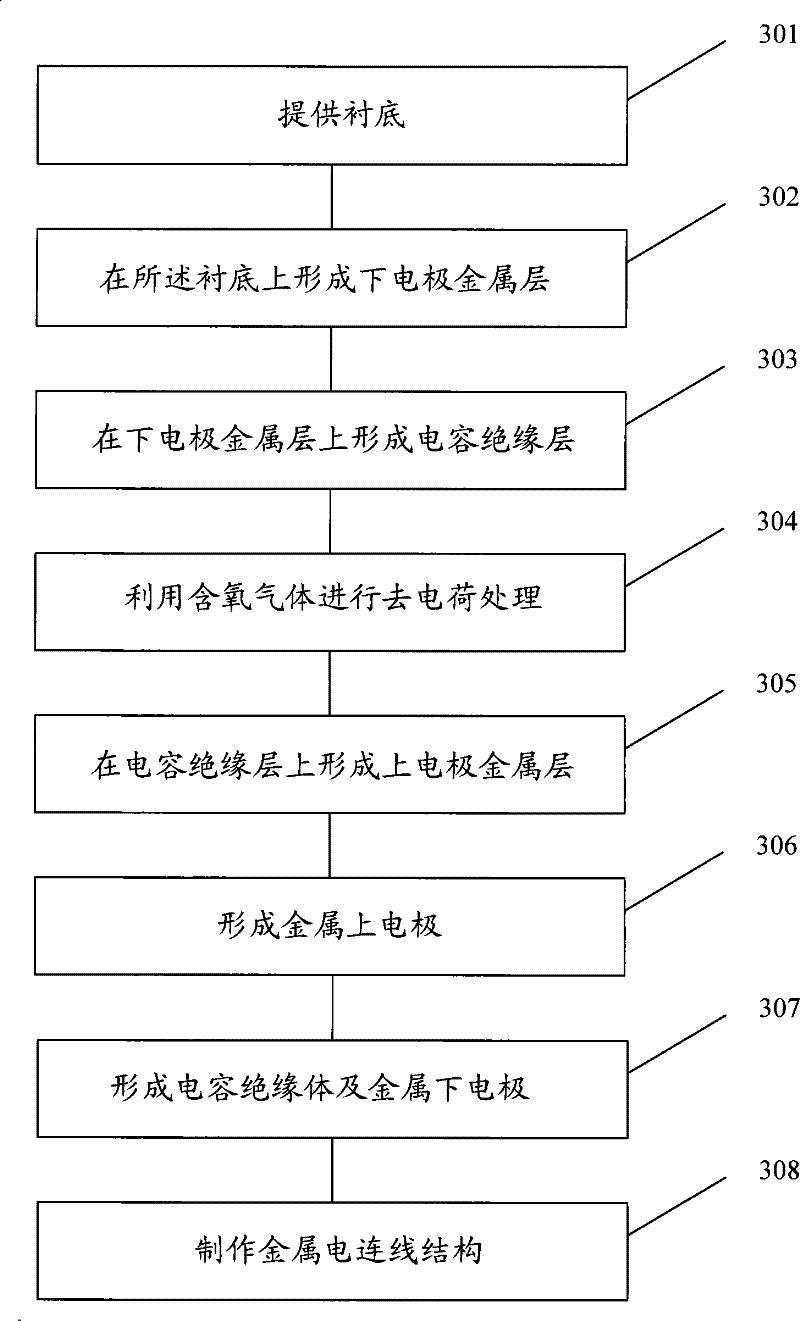

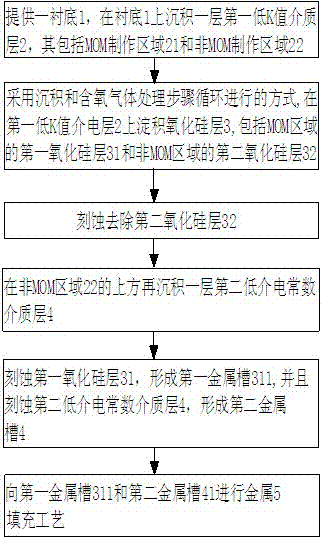

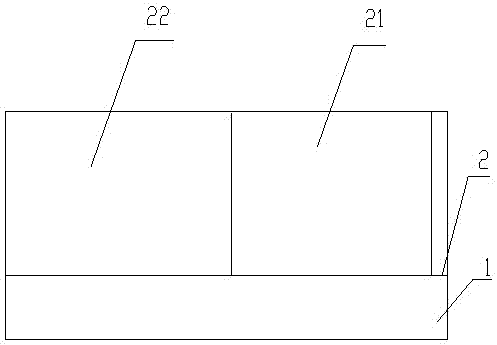

Manufacturing method of metal-oxide-metal capacitor

ActiveCN102386064AIncrease capacitanceImprove breakdown voltageSemiconductor/solid-state device manufacturingCapacitanceDrain current

The invention provides a manufacturing method of a metal-oxide-metal (MOM) capacitor. A mixed layer composed of low k-value dielectrics and high k-value silicon oxide is formed, metal grooves are formed in the low k-value dielectrics and the high k-value silicon oxide by the conventional photoetching process and filled with metals, so that a high-performance MOM capacitor structure is formed in the high k-value silicon oxide region, and the low k-value dielectrics are interconnected in other regions. The invention is characterized in that the high k-value silicon oxide is formed by means of PECVD (plasma enhanced chemical vapor deposition) and oxygen-containing gas processing cycles, which can effectively eliminate Si-H bonds in silicon oxide. Compared with the conventional single k-valuedielectric structure, the capacitance of the interlayer capacitor is effectively increased, the electrical properties (such as breakdown voltage and drain current) of the MOM capacitor are improved, and the uniformity of electrical properties between devices is improved.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

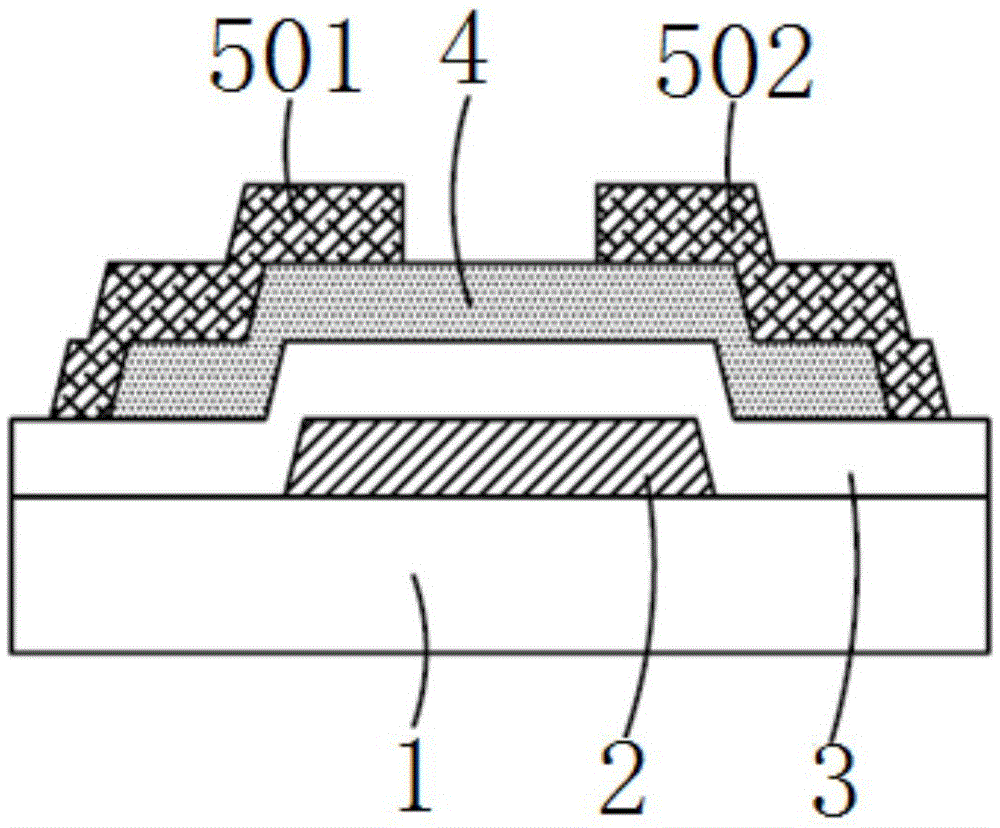

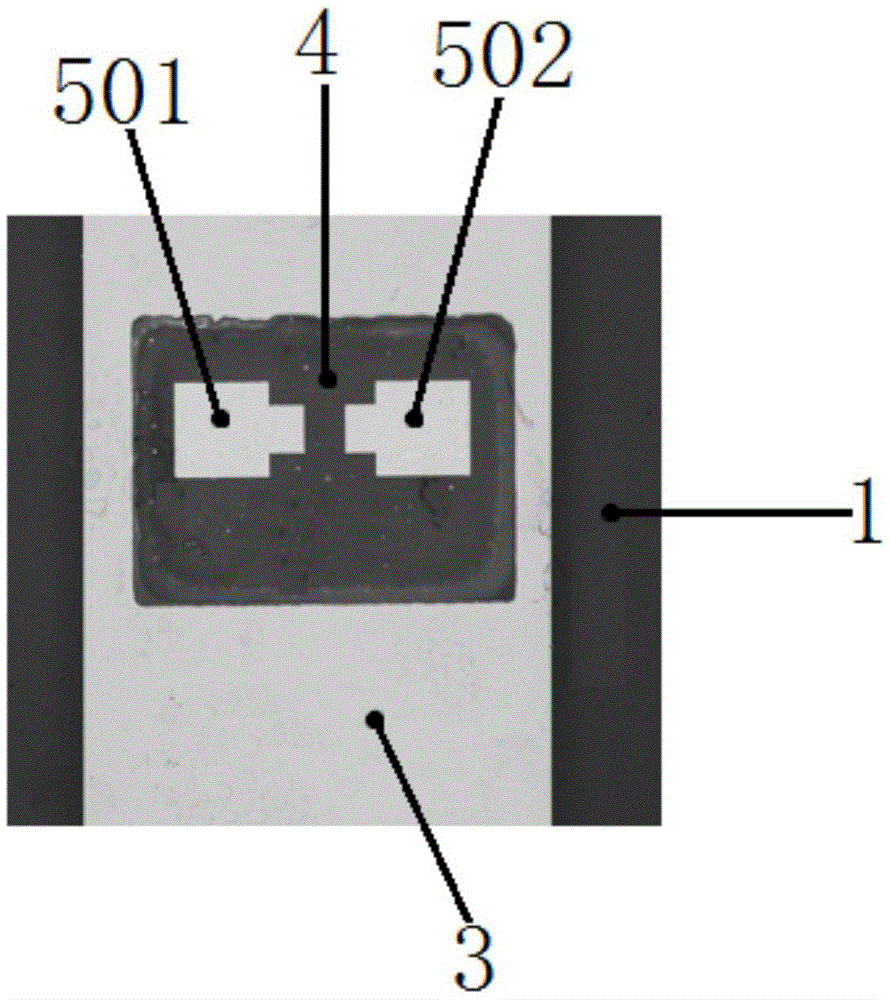

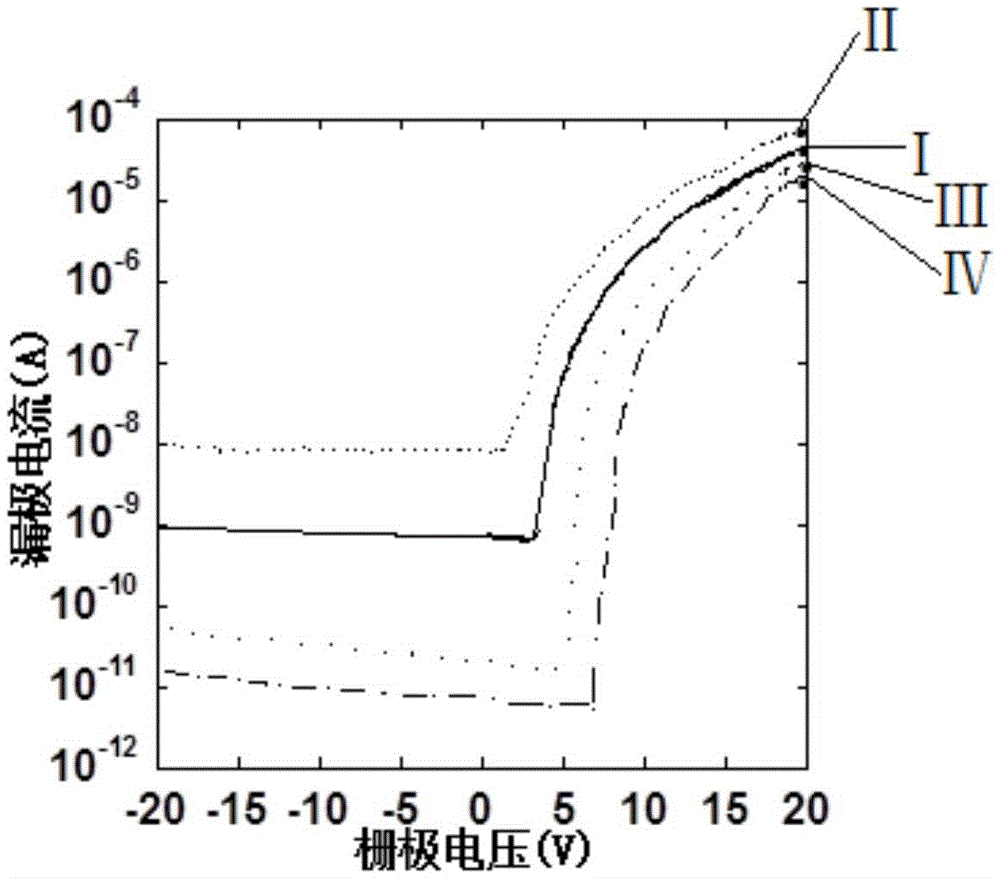

Active layer, film transistor, array substrate, display device and preparation methods

ActiveCN105655389AImprove mobilityOptical BandgapTransistorSolid-state devicesInsulation layerIndium

The invention discloses an active layer, a film transistor, an array substrate, a display device and preparation methods, and belongs to the field of the panel display. The material of the active layer is zirconium oxide indium, and the chemical formula of the zirconium oxide indium is ZrxIn100-xOy, wherein 0.1<=x<=20, and y>0. By adopting the active layer provided by the invention, various structure types such as the film transistor of a bottom gate intersection structure can be prepared by full direct current sputtering, high carrier mobility and high electricity homogeneity of the obtained film transistor are ensured, and thickness controllability of a gate insulation layer can be ensured.

Owner:BOE TECH GRP CO LTD +1

Touch panel

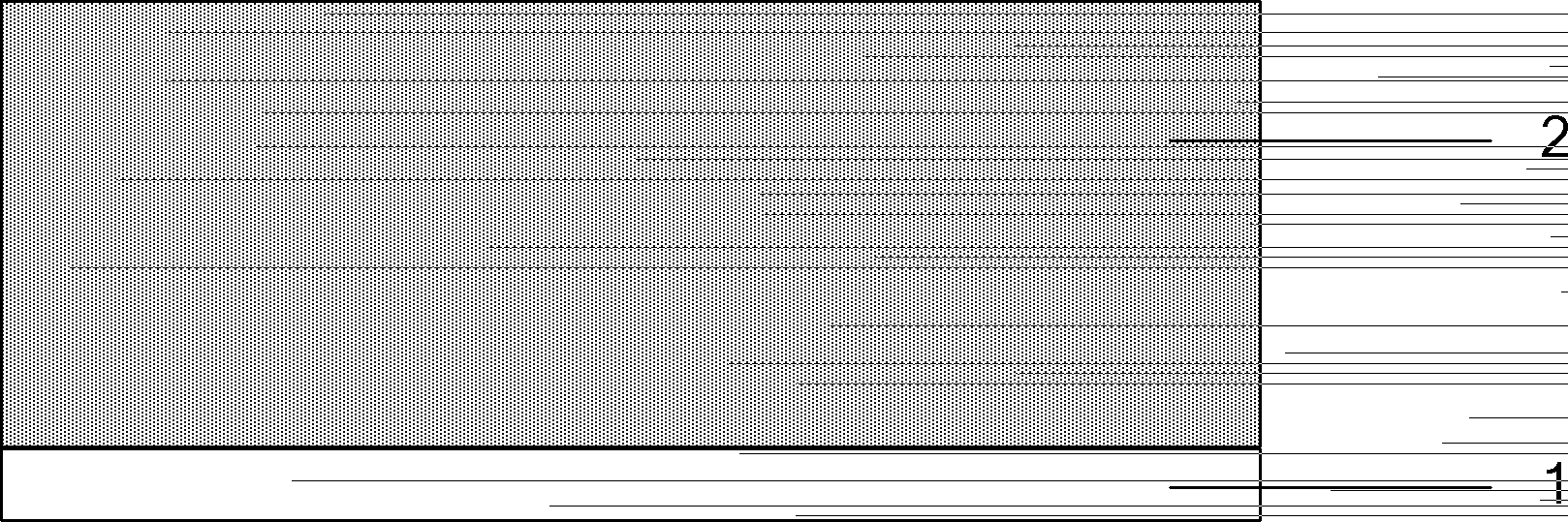

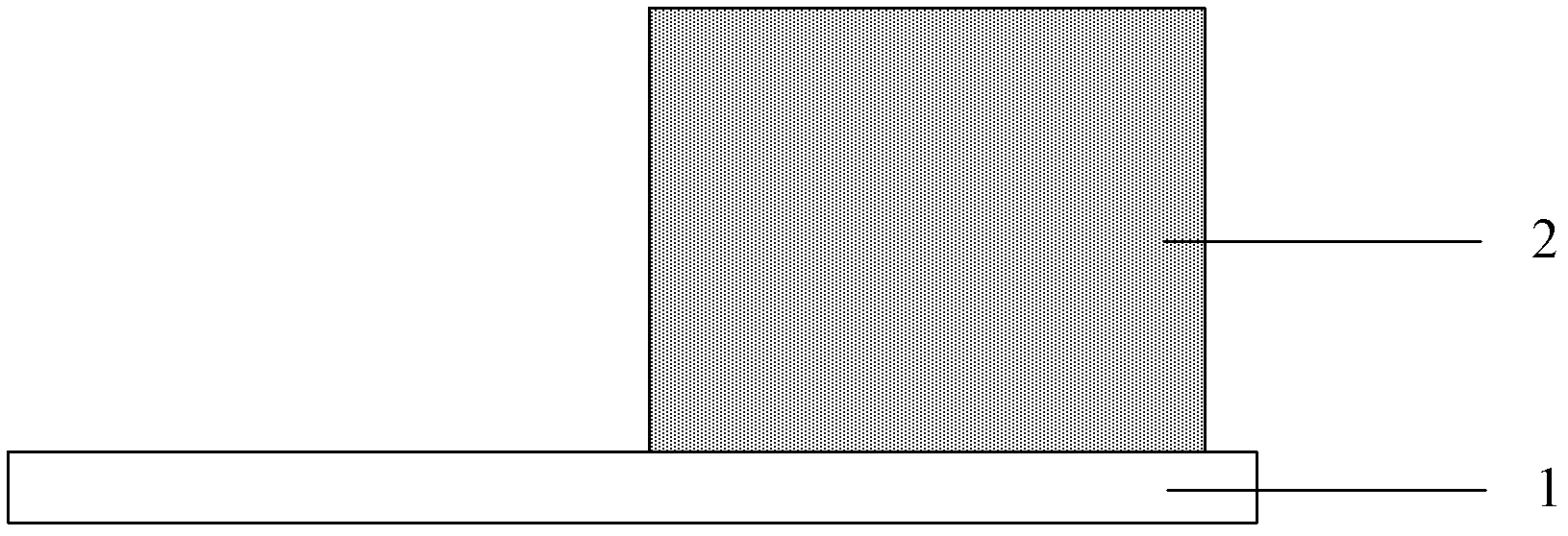

ActiveCN103793116AImprove electrical uniformityImprove touch sensitivityInput/output processes for data processingAuxiliary electrodeTouch panel

The invention relates to the technical field of touch and provides a touch panel. The touch panel is provided with at least one non-rectangular corner area at corners of the touch panel. The touch panel comprises a first electrode and a second electrode which are intersected and electrically insulated. The first electrode comprises a plurality of first strip electrodes extending along a first direction. The second electrode extends along a second direction and comprises a plurality of strip electrodes and at least one auxiliary electrode. The auxiliary electrodes are arranged in the one non-rectangular corner areas, form included angles smaller than 90 degrees with the second direction and are electrically connected with at least one adjacent second strip electrode. The touch panel has the advantage that touch sensitivity of the non-rectangular corner area of the touch panel is improved.

Owner:TPK TOUCH SYST XIAMEN

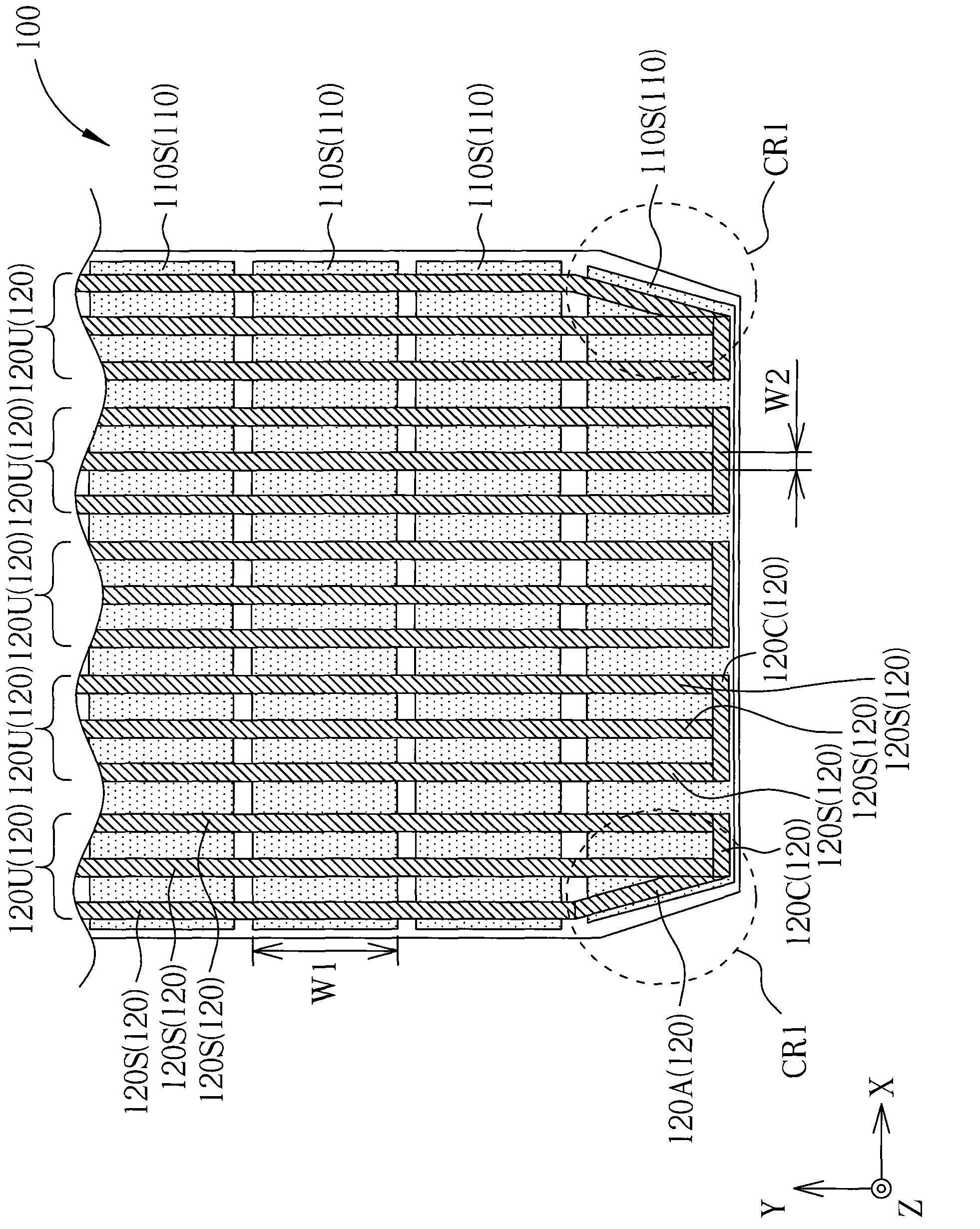

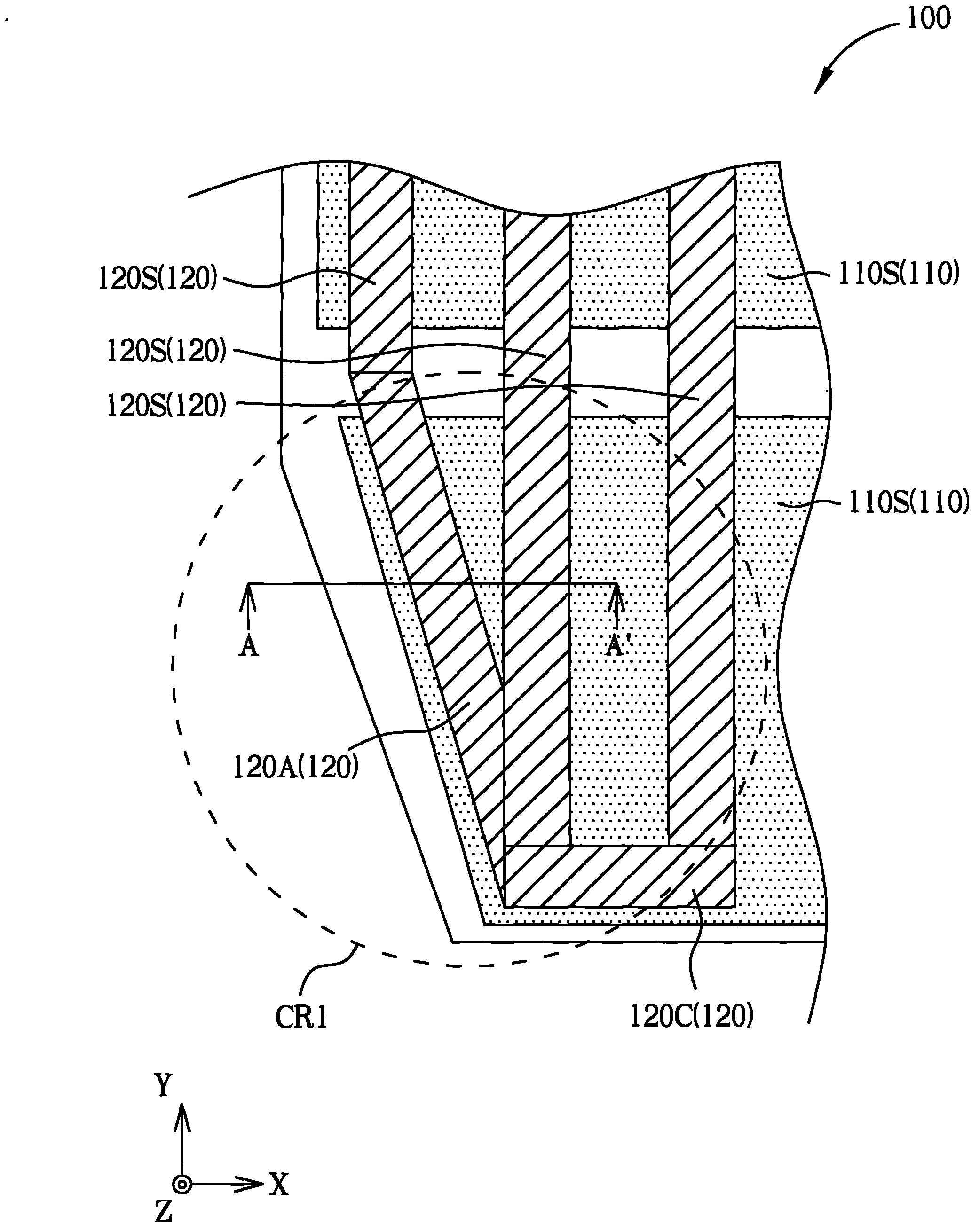

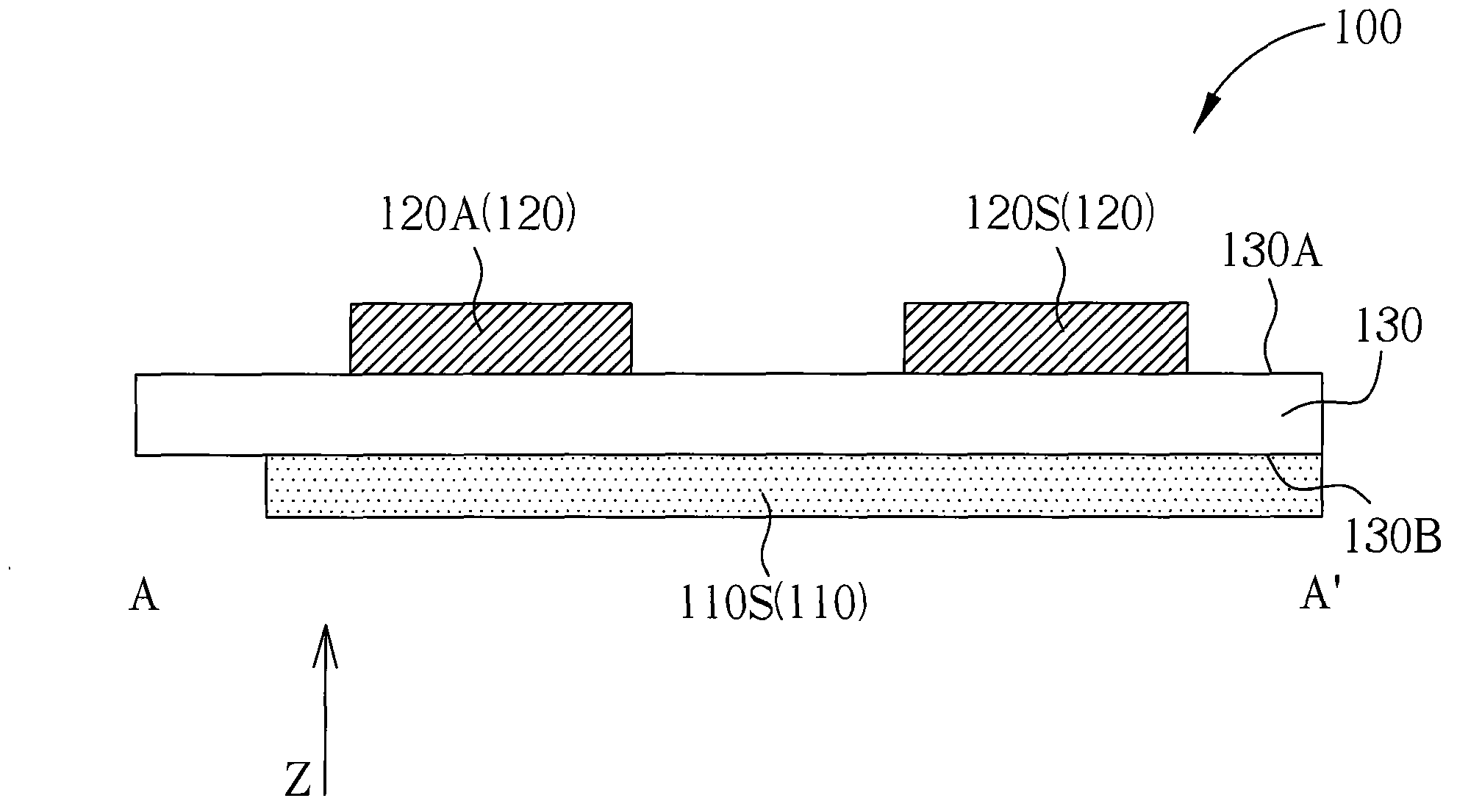

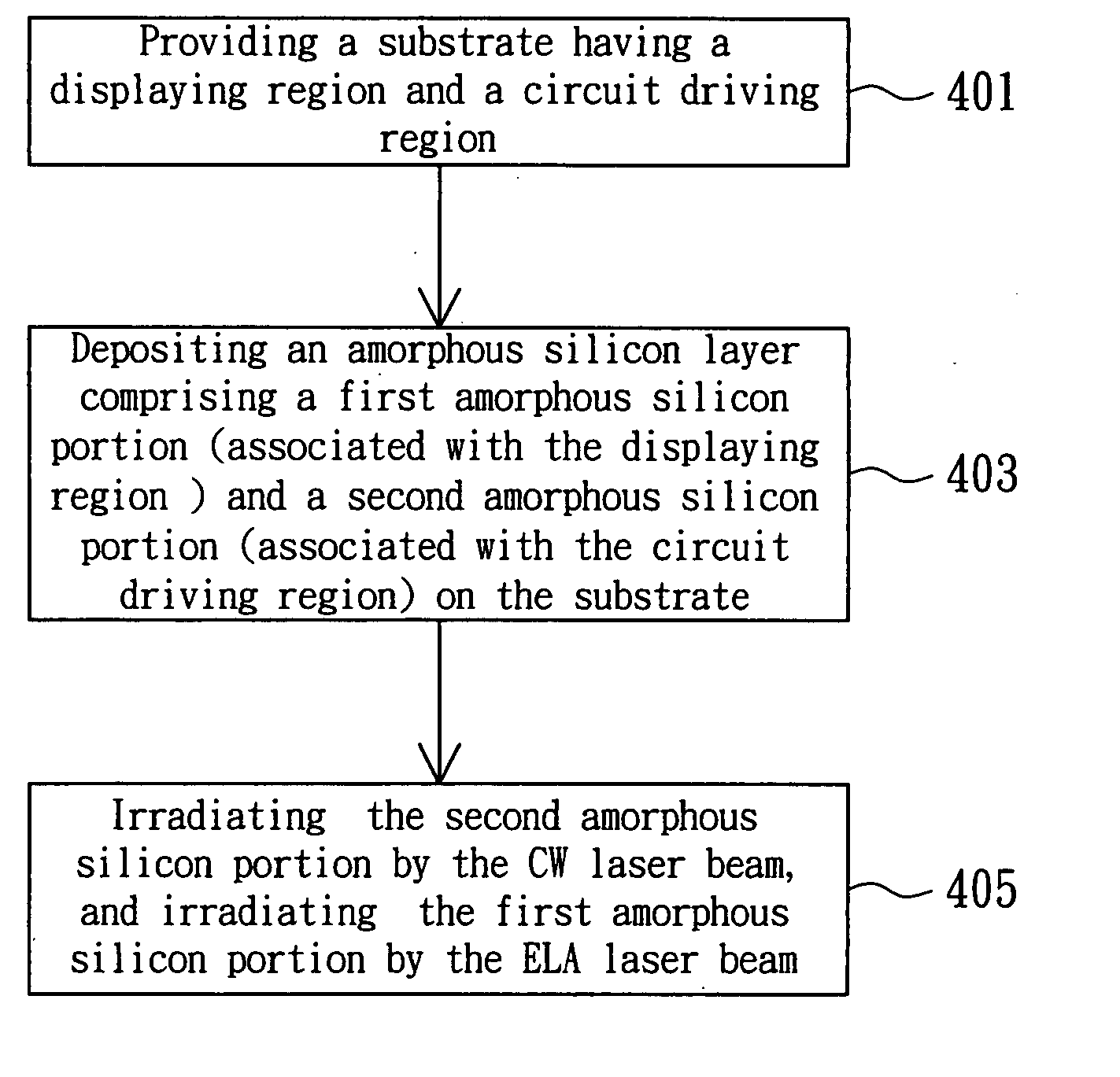

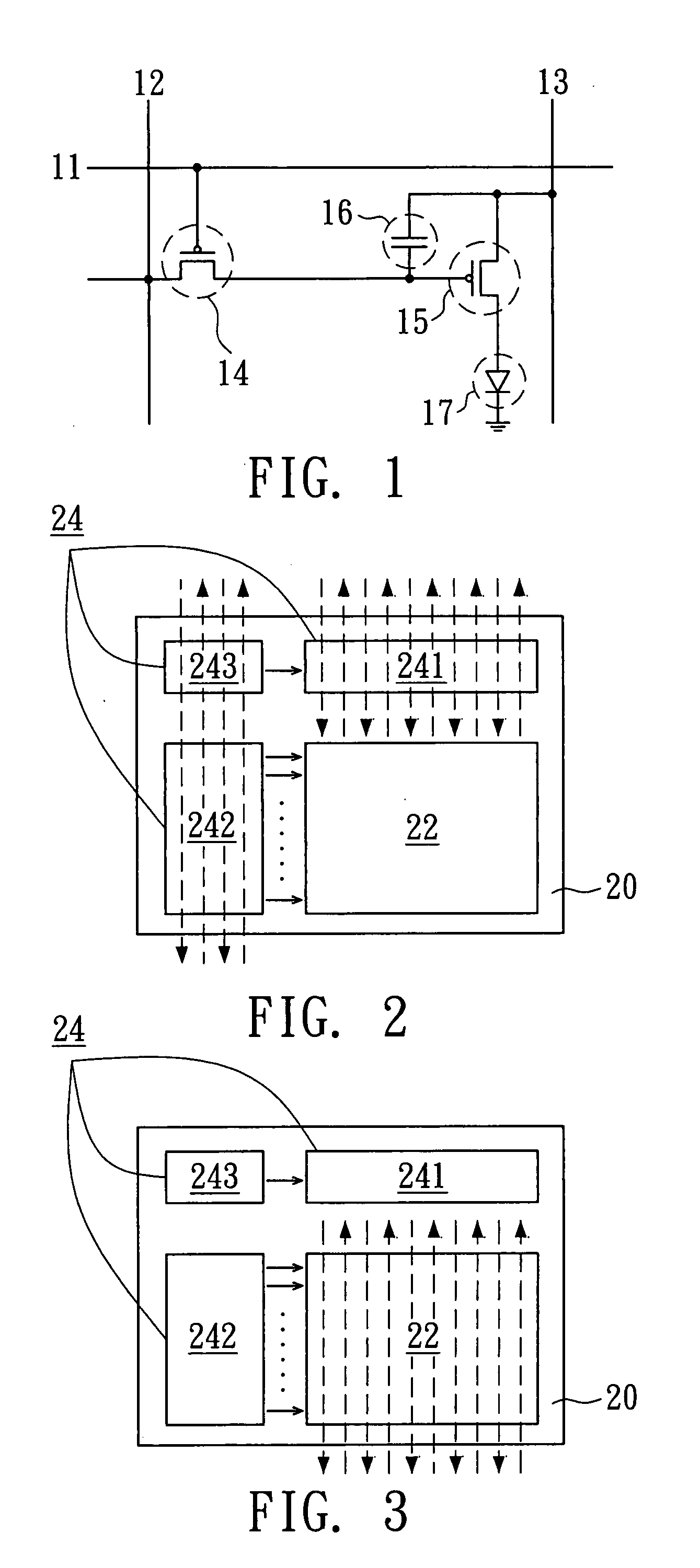

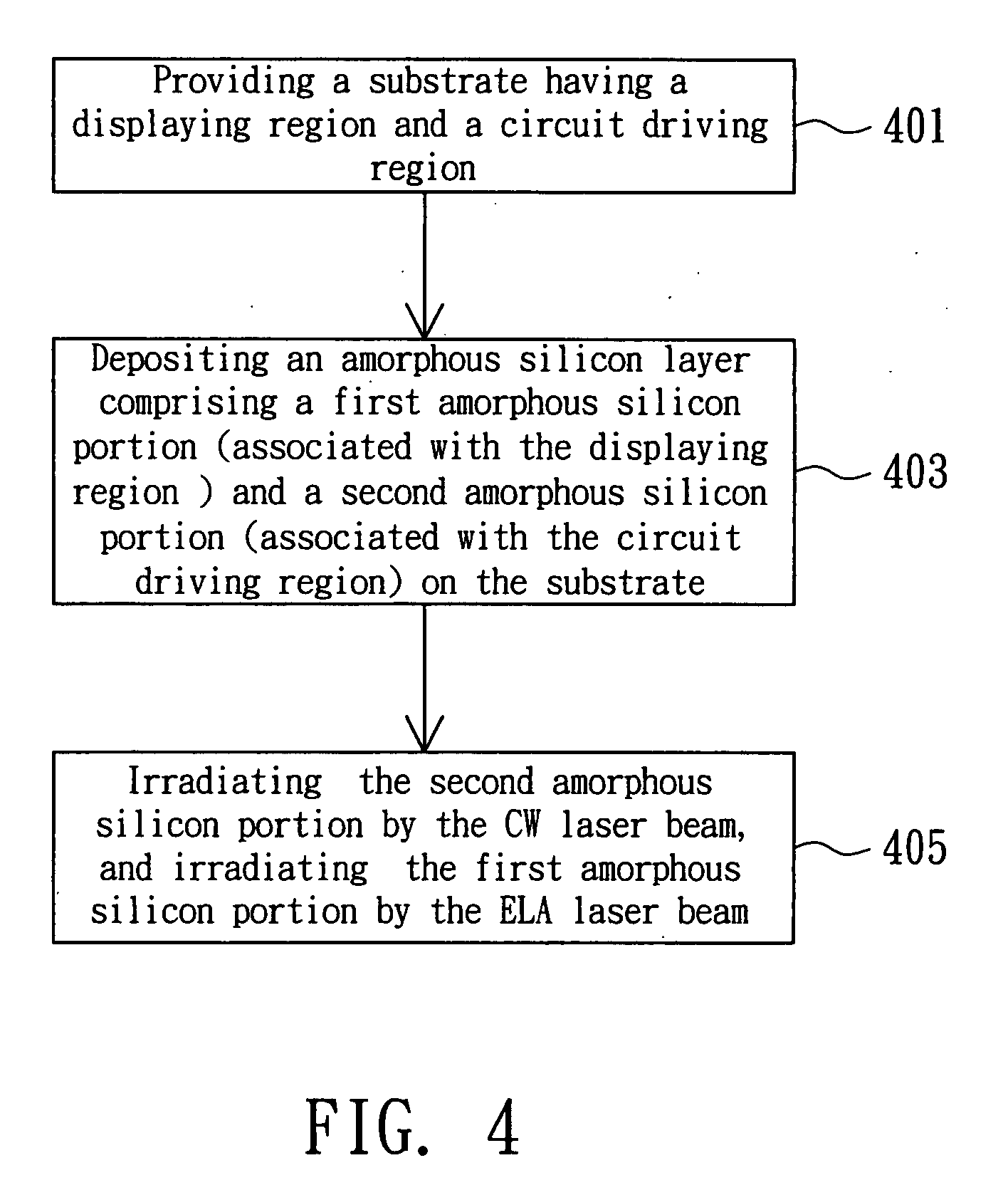

Method for selective laser crystallization and display panel fabricated by using the same

ActiveUS20080090340A1Improve electrical uniformityImprove throughputSolid-state devicesSemiconductor/solid-state device manufacturingLaser crystallizationOptoelectronics

Owner:XIAMEN TIANMA DISPLAY TECH CO LTD

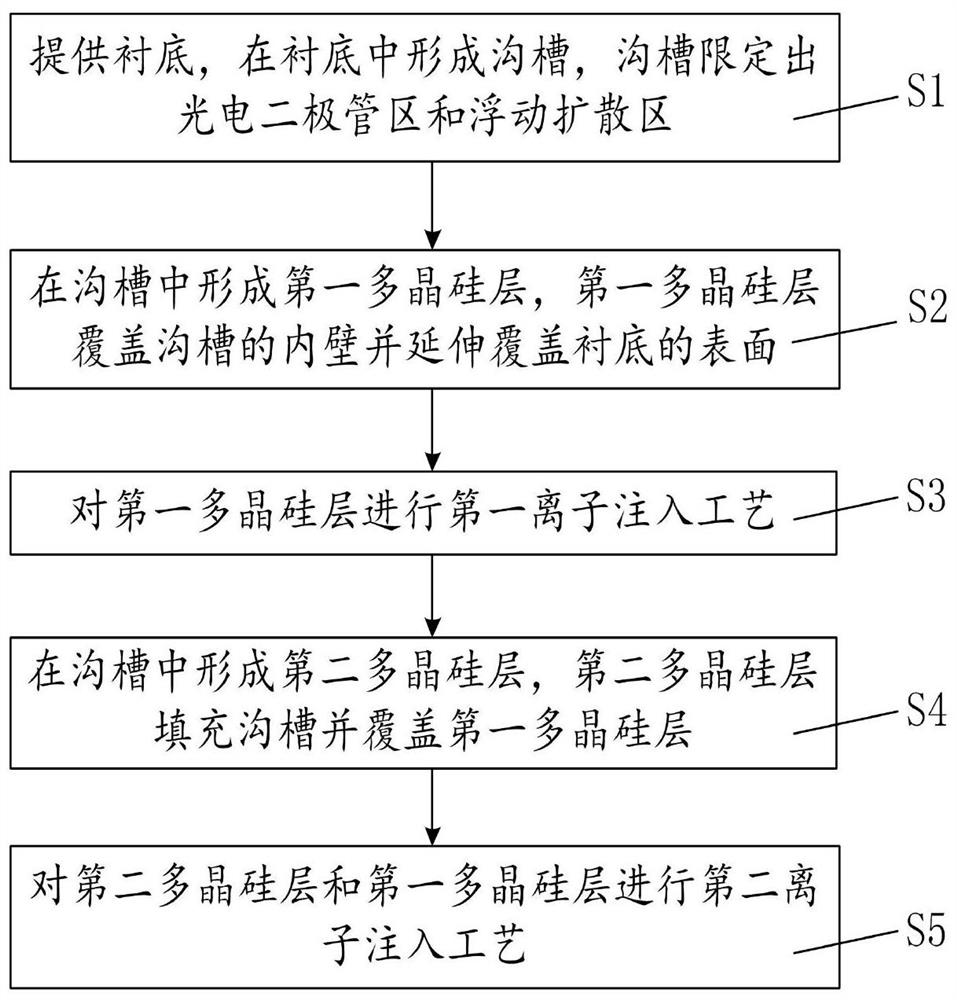

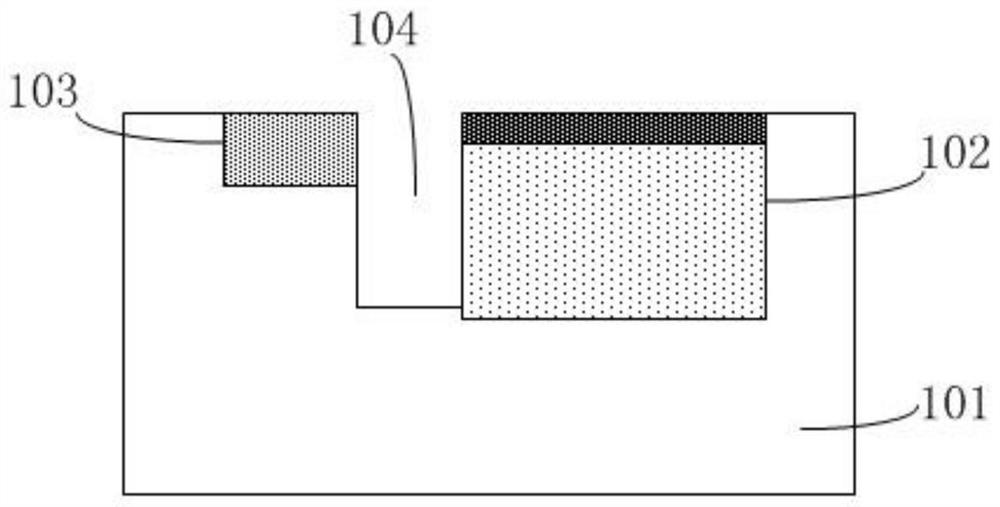

Preparation method of vertical-gate semiconductor device

PendingCN112614860AImprove doping uniformityAvoid Difficult DopingSolid-state devicesRadiation controlled devicesDevice materialEngineering

The invention provides a preparation method of a vertical-gate semiconductor device. The preparation method comprises the following steps: providing a substrate; forming a trench in the substrate, wherein the trench defines a photodiode region and a floating diffusion region; forming a first polycrystalline silicon layer in the trench, wherein the first polycrystalline silicon layer covers the inner wall of the trench and extends to cover the surface of the substrate; performing a first ion implantation process on the first polycrystalline silicon layer; forming a second polycrystalline silicon layer in the trench, wherein the trench is filled with the second polycrystalline silicon layer, and the second polycrystalline silicon layer covers the first polycrystalline silicon layer; and performing a second ion implantation process on the second polycrystalline silicon layer and the first polycrystalline silicon layer. According to the invention, the phenomenon of non-uniform electrical performance of an image sensor is improved.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Method of selective laser crystallization and display panel manufactured by same method

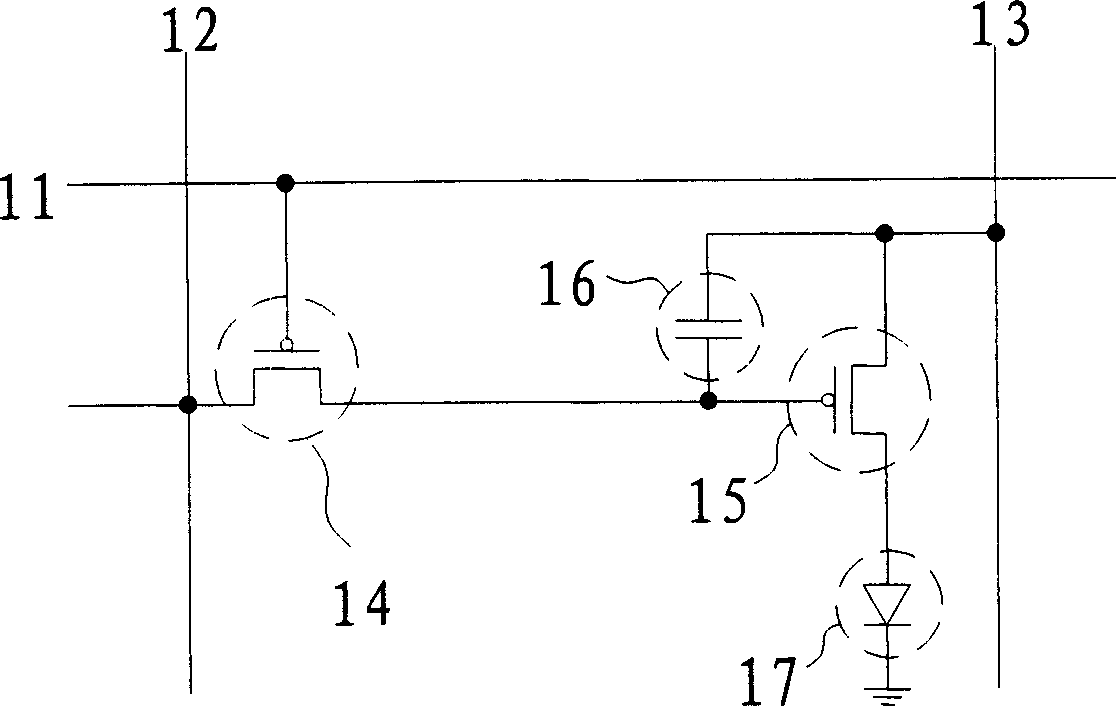

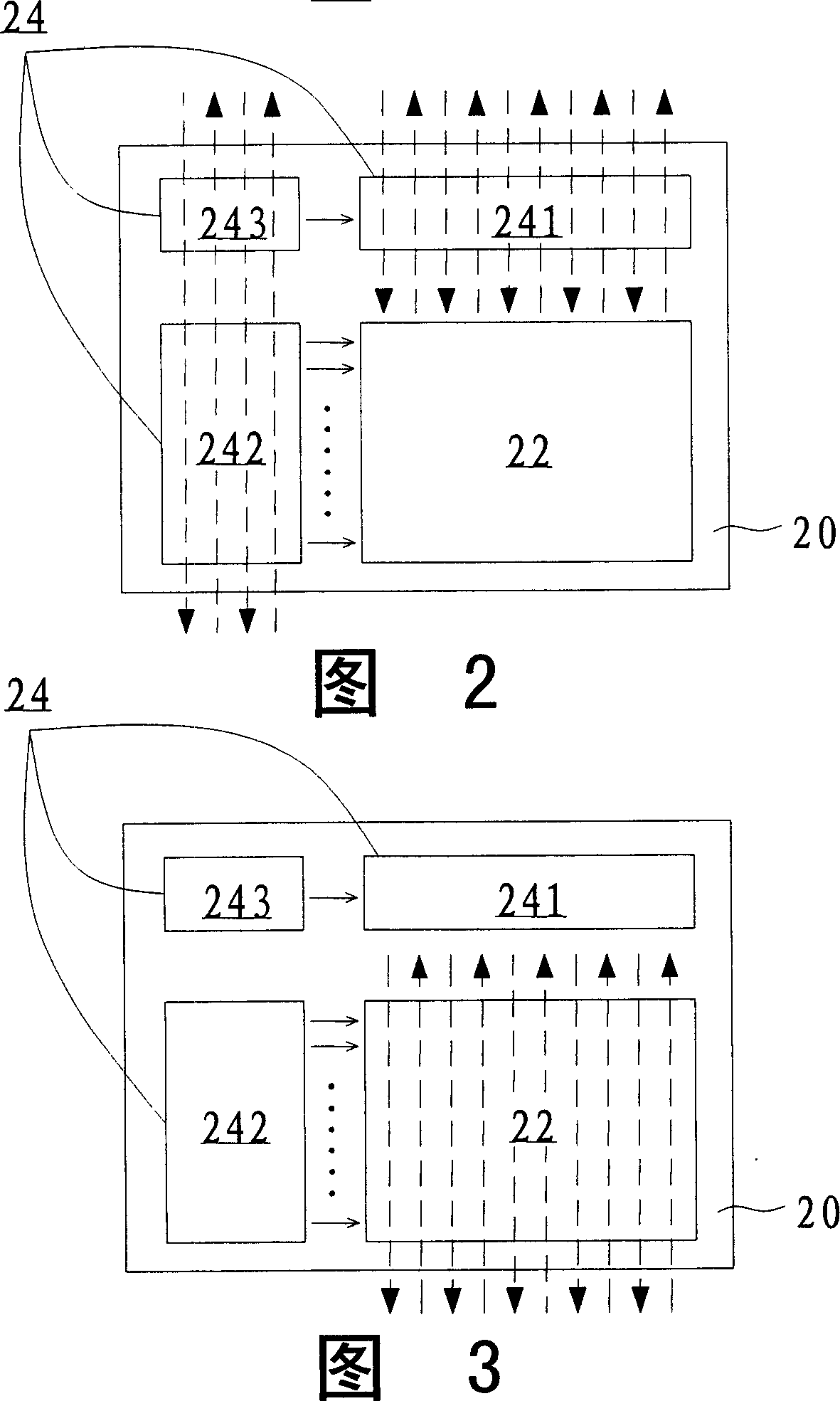

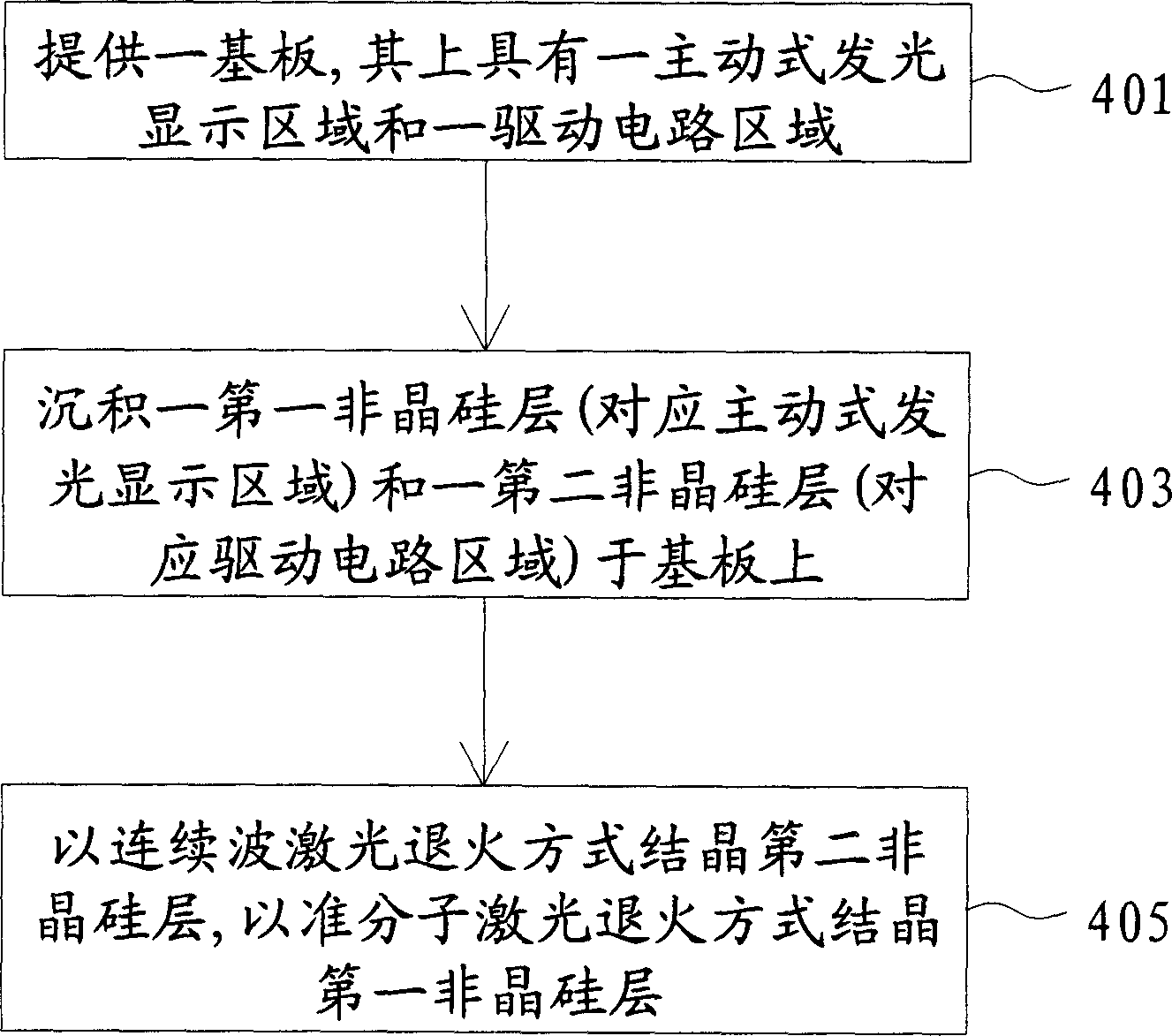

ActiveCN1622718AImprove electrical uniformityIncrease production capacityElectrical apparatusStatic indicating devicesLaser crystallizationEngineering

The display panel includes one substrate with one active light emitting display region and one circuit driving region; and one polysilicon layer formed on the substrate and with the first polysilicon layer arean and the second polysillicon layer area separately corresponding to the active light emitting display region and the circuit driving region, with the second polysillicon layer area having greater crystal grain size. The second polysillicon layer arean is formed in continuous wave laser annealing mode, while the first polysilicon layer arean is formed in excimer laser annealing mode.

Owner:테스콤가부시키가이샤

Production method of metal-silicon nitride-metal capacitor

ActiveCN102446709AIncrease capacitanceIncrease K valueSemiconductor/solid-state device manufacturingDielectricCapacitance

The invention provides a production method of a metal-silicon nitride-metal capacitor, which comprises the steps of: 1) depositing a low-k-value dielectric layer; 2) forming a metal-oxide-metal (MOM) area through photoetching and etching; 3) depositing high-k-value silicon nitride through a plasma enhanced chemical vapor deposition (PECVD) method; 4) removing excessive silicon nitride through chemical and mechanical grinding to form a low-k-value dielectric and silicon nitride mixed layer; 5) completing photoetching and etching to form a metal groove on the low-k-value dielectric and silicon nitride; 6) completing the deposition and the chemical and mechanical grinding of the metal layer and then forming the metal fillers of a conducting wire and an MOM capacitor; and 7) completing copper interconnection and the production of the MOM capacitor. By improving the k value of the dielectric of the inter-layer capacitor, the capacitance of the inter-layer capacitor is effectively improved. By improving the performance of the high-k-value silicon nitride, the electric properties such as the puncture voltage, the leakage current and the like of the MOM capacitor and the electric uniformity of devices are effectively improved. The production method is very practical.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

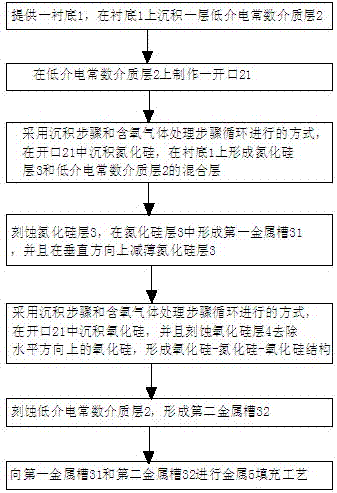

Manufacture method of metal-multilayer insulator-metal capacitor

InactiveCN102709154AIncrease capacitanceImprove stabilitySemiconductor/solid-state device manufacturingCapacitanceSilicon oxide

The invention discloses a manufacture method of a metal-multilayer insulator-metal capacitor. The manufacture method comprises the following steps of: providing a substrate; depositing a low-dielectric-constant dielectric layer on the substrate; forming a hole in the low-dielectric-constant dielectric layer; depositing silicon nitride in the hole via the way of circularly depositing and processing oxygen-containing gas to form a mixing layer of the silicon nitride and the low-dielectric-constant dielectric layer; etching a silicon nitride layer to form a first metallic channel in the silicon nitride layer, and thinning the silicon nitride layer; depositing silicon oxide in the hole via the way of circularly depositing and processing the oxygen-containing gas, and etching the silicon oxide layer to remove the silicon oxide along horizontal direction; etching the low-dielectric-constant dielectric layer to form a second metallic channel; and performing metal filling to the first metallic channel and the second metallic channel. The invention effectively improves the capacitance of the capacitor in the layer, improves the electrical characteristics of the capacitor, such as breakdown voltage, leakage current and the like, and improves the electrical uniformity among all elements.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

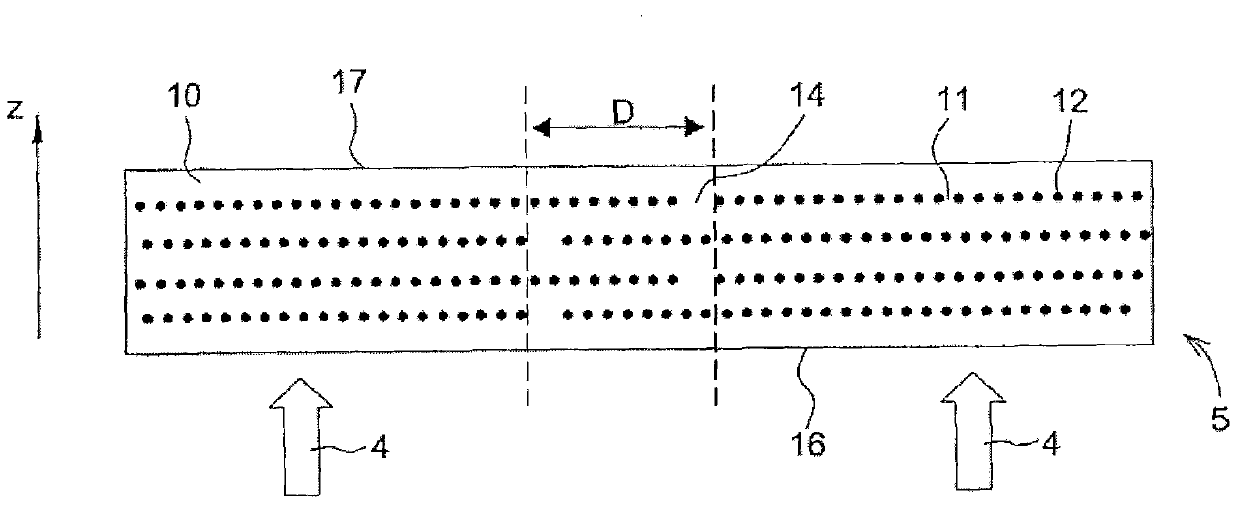

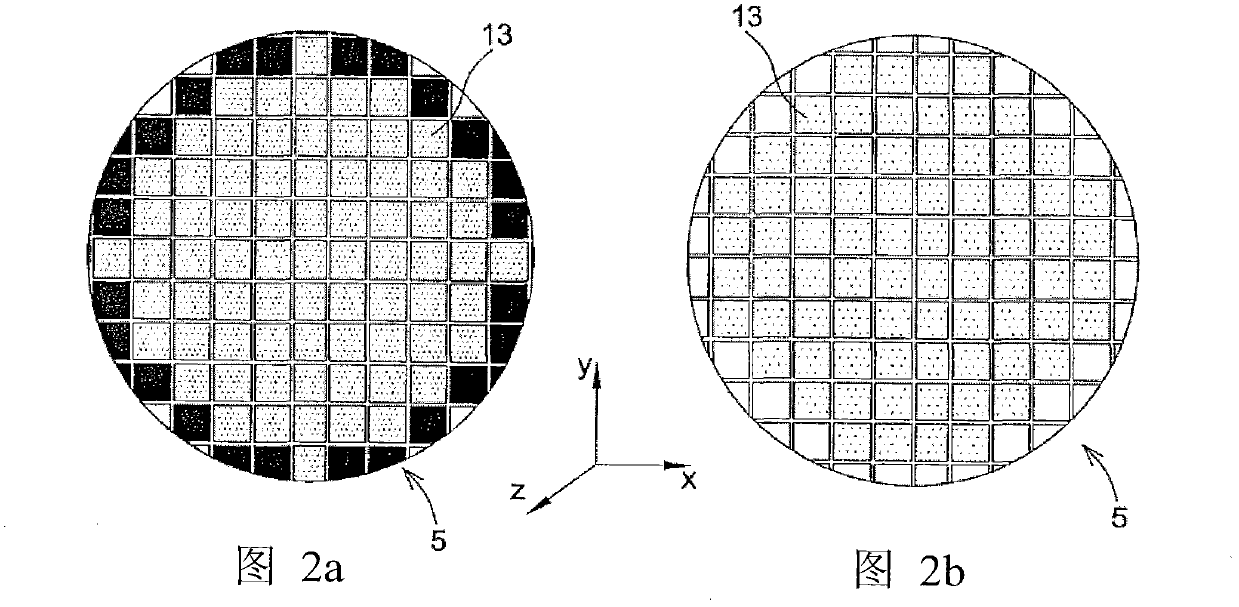

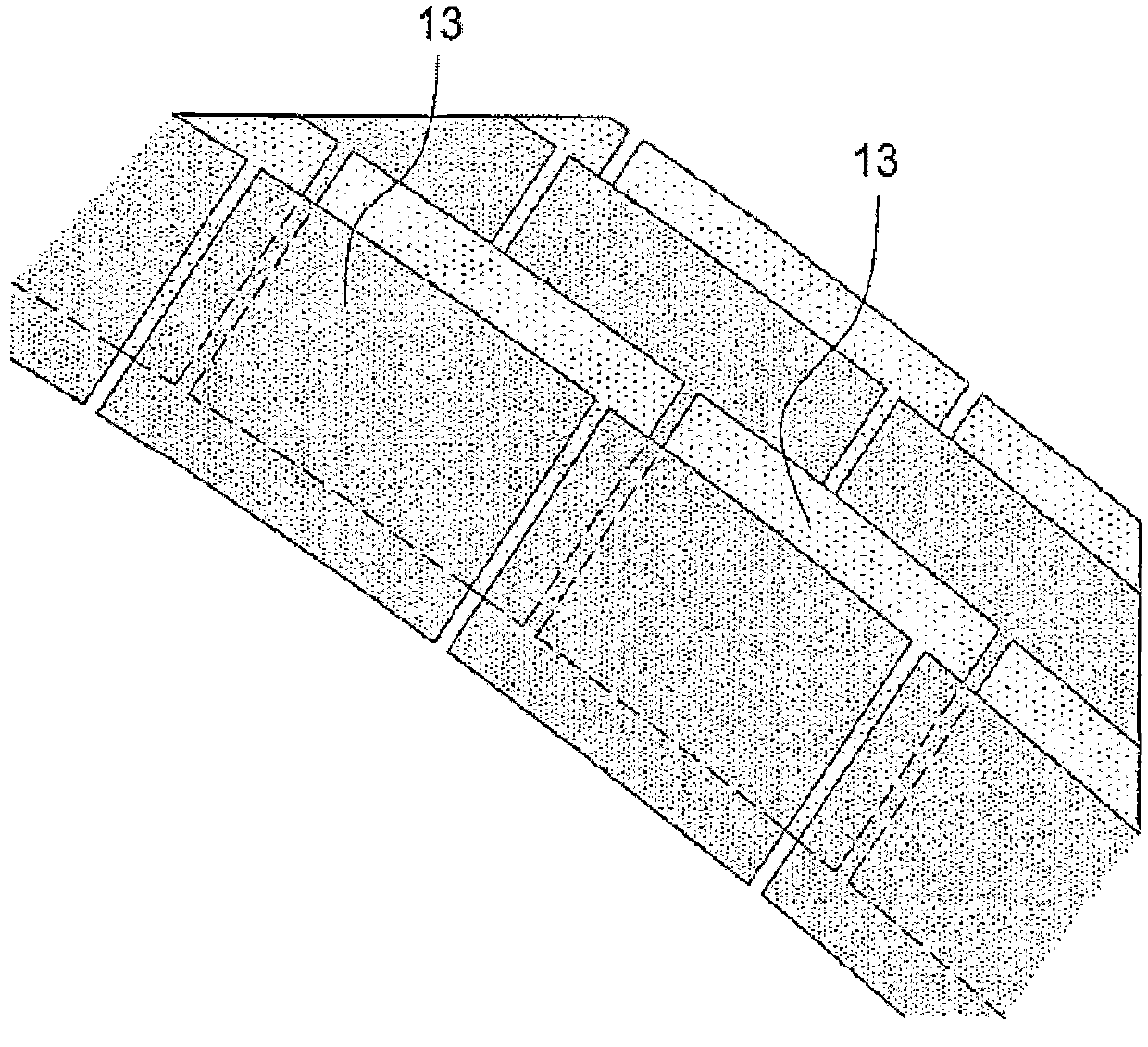

Deformable reflecting membrane for reconfigurable reflector and antenna having the same

The invention provides a deformable reflecting membrane for a reconfigurable reflector and an antenna having the same. The deformable reflecting membrane (5) comprises a conductive elastomer layer (10) and at least two reinforcing layer (11) which are intermeshed in a thickness direction. Each reinforcing layer is divided in a manner of being separated from each other in terms of space. Independent fragments are disposed on the plane of the membrane in a periodical manner. The invention is especially suitable for space area.

Owner:THALES SA

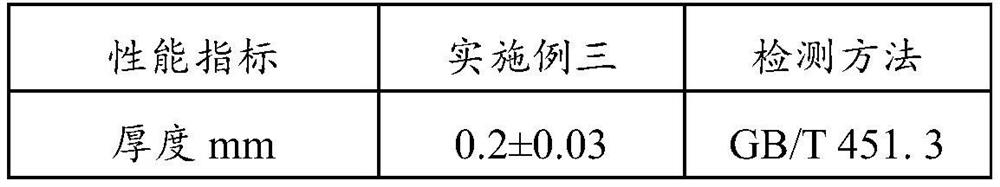

Water-blocking expansion type semi-conductive nylon tape for ultrahigh-voltage cable and preparation method thereof

PendingCN113338048AImprove electrical uniformityReduce surface resistanceClimate change adaptationInsulated cablesFiberElectrical resistance and conductance

The invention discloses a water-blocking expansion type semi-conductive nylon tape for an ultrahigh-voltage cable and a preparation method thereof. The preparation method comprises the following steps that S1, mixed weaving is carried out on metal wires and cellosilk to obtain base cloth; S2, an alcohol diluent, a dispersant, water-absorbent resin, conductive carbon black and an emulsion are uniformly mixed to prepare a water-blocking conductive liquid; and S3, the base cloth obtained in the step S1 is uniformly coated with the water-blocking conductive liquid obtained in the step S2, and then drying is carried out to obtain the water-blocking expansion type semi-conductive nylon tape. The base cloth is formed by blending the metal wires and the cellosilk, the metal wires effectively reduce the surface resistance and the volume resistance of the base cloth, and the semi-conductive performance is improved; and the water-blocking and conductive liquid is prepared by synchronously and uniformly mixing a water-absorbing material and a conductive material with the alcohol diluent, the alcohol diluent and the water-absorbing resin do not absorb, expand and react, so that the serious defects caused when water is used as the diluent in the traditional process are overcome, the prepared water-blocking and conductive liquid can endow the base cloth with semi-conductive performance and water-blocking performance at one time, working procedures are effectively reduced, production power consumption is reduced, and energy conservation and environmental protection are achieved.

Owner:YANG ZHOU TENGFEI ELECTRIC CABLE & APPLIANCE MATERIALS CO LTD

Method for producing multilayer metal-silicon nitride-metal capacitor

ActiveCN102592968AIncrease capacitanceImprove electrical uniformitySemiconductor/solid-state device manufacturingCapacitanceElectricity

The invention provides a method for producing a multilayer metal-silicon nitride-metal capacitor, which includes the following steps: 1) using a plasma enhanced chemical vapor deposition (PECVD) method to deposit a silicon nitride thin film with a high k value on a silicon chip substrate; 2) removing silicon nitride in a non-metal-oxide-metal area through photoetching and etching; 3) depositing a dielectric layer with a low k value; 4) removing redundant silicon nitride through chemical mechanical polishing, and forming a mixing layer of low-k-value dielectric and silicon nitride; 5) completing photoetching and etching to form a metallic channel in the low-k-value dielectric and the silicon nitride; 6) forming metal fillers of a lead and a metal-oxide-metal (MOM) capacitor after deposition and chemical mechanical polishing of a metal layer are completed; and 7) repeating Step 1) to Step 6) to form multilayer MOM capacitor. The method for producing the multilayer metal-silicon nitride-metal capacitor can effectively improve the capacitance of the interlayer capacitor, can also effectively improve various electric characteristics of the MOM capacitor such as breakdown voltage, leakage current and the like, can effectively improve electric uniformity among various apparatuses, and is very practical.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Method for manufacturing multilayer metal-silicon oxide-metal (MOM) capacitor

ActiveCN102437024AEfficient removalIncrease capacitanceSemiconductor/solid-state device manufacturingCapacitanceSilicon oxide

The invention provides a method for manufacturing a multilayer metal-silicon oxide-metal (MOM) capacitor. The method has the following beneficial effects: the multilayer MOM capacitor is formed by forming a mixed layer of a low-k dielectric and high-k silicon oxide, then utilizing the traditional photoetching and etching processes to form metal grooves in the low-k dielectric and silicon oxide respectively and filling metals into the metal grooves and repeating the previous steps; the MOM capacitor structure is realized in the high-k silicon oxide region and interconnection of the low-k dielectric is realized in other regions; and high-k silicon oxide is formed by circularly carrying out plasma enhanced chemical vapor deposition (PECVD) and oxygen-containing gas treatment so that the silicon-hydrogen bonds in silicon oxide can be effectively removed. Compared with the traditional single k dielectric structure, the method has the following advantages: not only can the capacitance of the capacitor in the layer be effectively improved, but also the electrical characteristics of the MOM capacitor such as breakdown voltage, leakage current and the like and the electrical uniformity among the components are improved.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Manufacturing method of multi-layer metal-silicon oxide-metal capacitor

InactiveCN102779734AEfficient removalIncrease capacitanceSemiconductor/solid-state device manufacturingCapacitanceHydrogen

The invention discloses a manufacturing method of a multi-layer metal-silicon oxide-metal capacitor. The manufacturing method comprises the steps of: firstly forming a mixing layer of a low-k-value medium and a high-k-value silicon oxide; conducting photoetching of a convention process to form a metallic channel and a capacitance metallic channel connected with each other in the low-k-value medium and high-k-value silicon oxide respectively, and filling metal in the channels; repeating the steps so as to realize a multi-layer MOM (Mass Optical Memory) capacitor structure in the region of the high-k-value silicon oxide and realize the interconnection of low k values in other regions, wherein the high-k-value silicon oxide is formed by adopting the mode of PECVD (Plasma Enhanced Chemical Vapor Deposition) and nitrogen-contained gas cyclic processing, and silicon-hydrogen bonds in silicon oxide can be removed effectively. Compared with a conventional single-k value medium structure, the manufacturing method provided by the invention has the advantages that the capacitance of a capacitor in a high layer can be improved effectively, the electrical characteristics of breakdown voltage, leakage current and the like of an MOM capacitor are improved, and the electricity uniformity of all the devices is improved.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

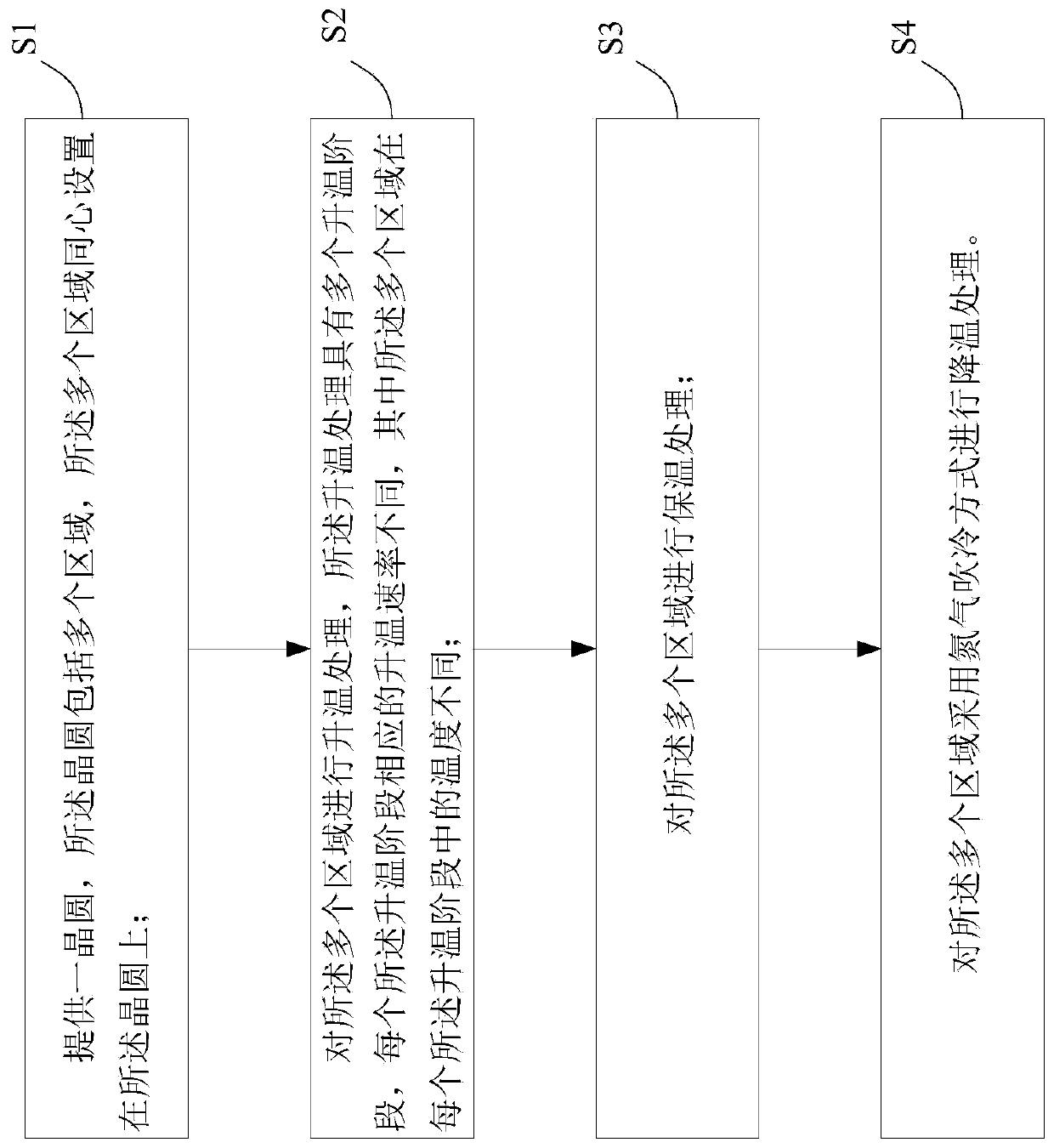

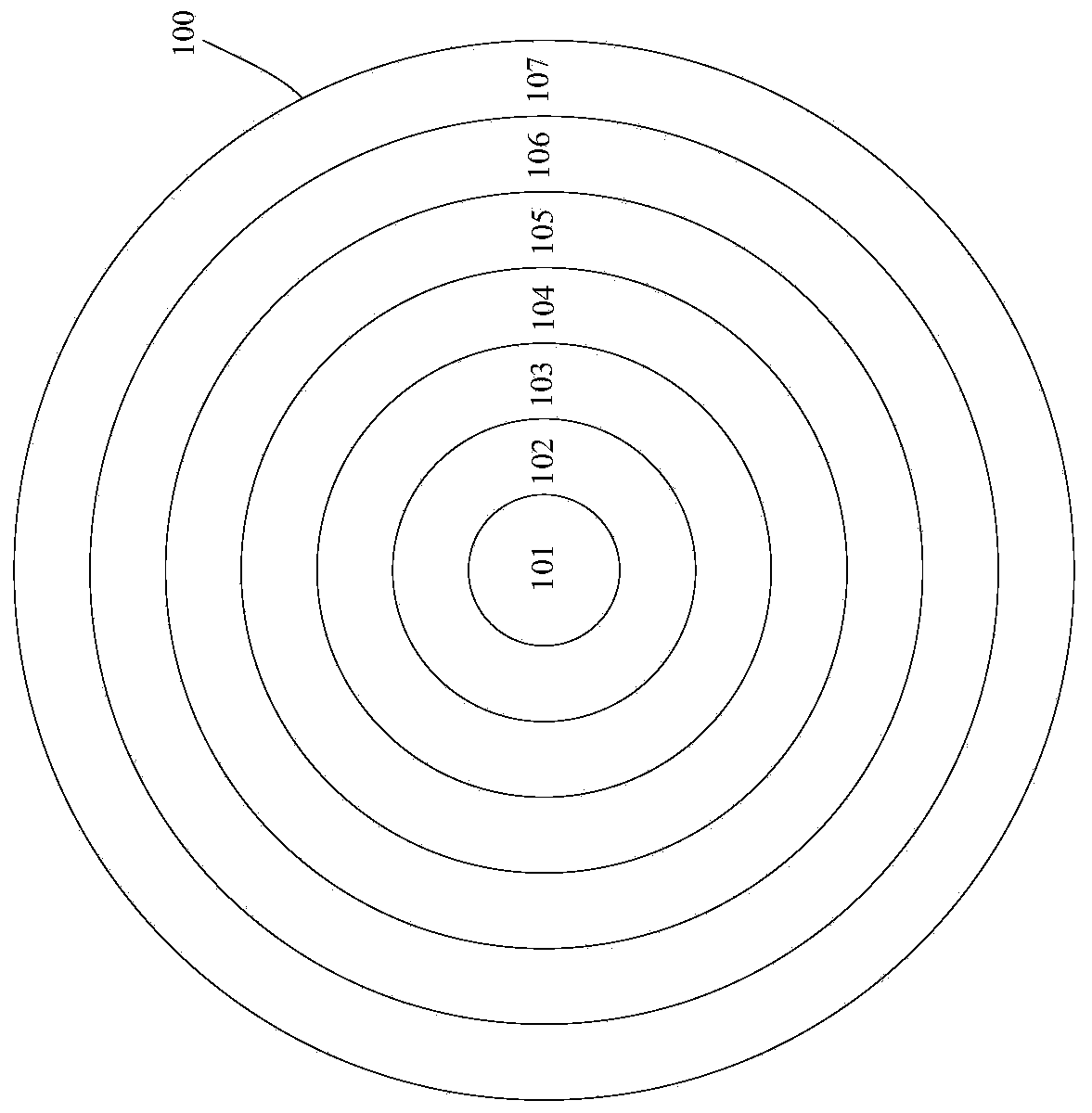

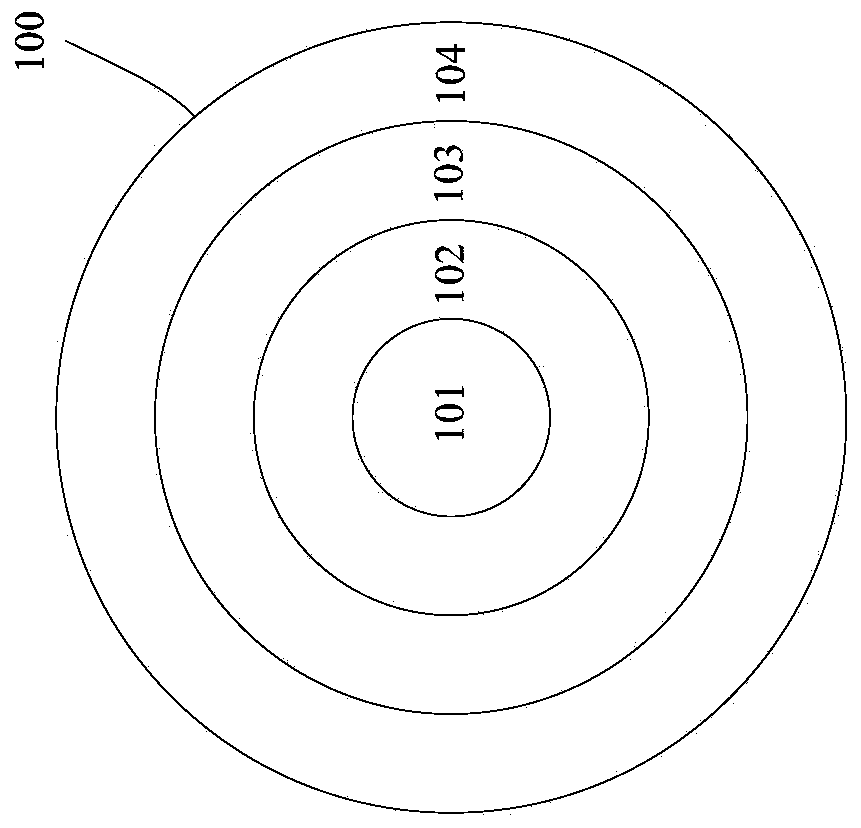

Wafer annealing method

ActiveCN111430236AImprove electrical uniformityReduce leakageTemperatue controlSemiconductor/solid-state device manufacturingWaferHeat conservation

The invention provides a wafer annealing method which comprises the following steps: providing a wafer which comprises a plurality of regions, and the plurality of regions are concentrically arrangedon the wafer; carrying out heating treatment on the plurality of regions, the heating treatment having a plurality of heating stages, the heating rates corresponding to the heating stages being different, and the temperatures of the plurality of regions in the heating stages being different; carrying out heat preservation treatment on the plurality of areas; and carrying out cooling treatment on the plurality of regions by adopting a nitrogen blowing cooling mode. According to the wafer annealing method provided by the invention, the electrical uniformity of the wafer can be improved.

Owner:NEXCHIP SEMICON CO LTD

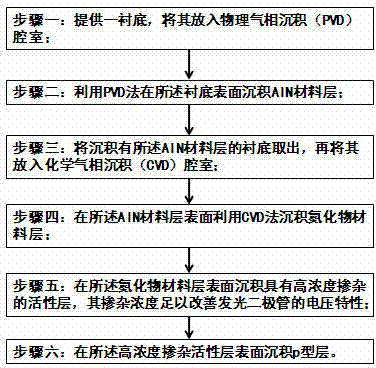

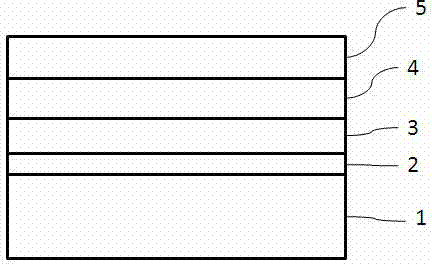

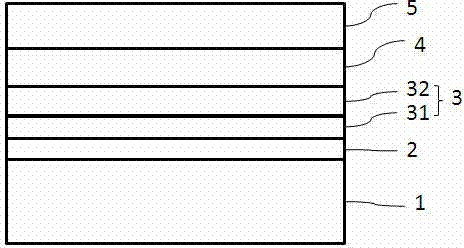

Manufacturing method for nitride light emitting diode

ActiveCN104505441AImproved Warp PlatingImprove electrical uniformitySemiconductor devicesHigh densityPhysical chemistry

The invention provides a manufacturing method for a nitride light emitting diode. The method comprises: using a PVD method to deposit an AIN film layer on a patterned substrate with larger depth, using a CVD method to deposit a nitride epitaxial layer on the AIN film layer, the thickness of the nitride epitaxial layer being relatively thin, through reducing the little stress of the epitaxial layer, improving warping of an epitaxial wafer, so as to improve electrical property uniformity of a single epitaxial wafer; using the patterned substrate with larger depth to improve light extraction efficiency; and mixing high density impurity in an active layer, under the condition of not influencing leakage, the impurity effectively reducing voltage feature, so as to improve integrated yield of the light emitting diode.

Owner:ANHUI SANAN OPTOELECTRONICS CO LTD

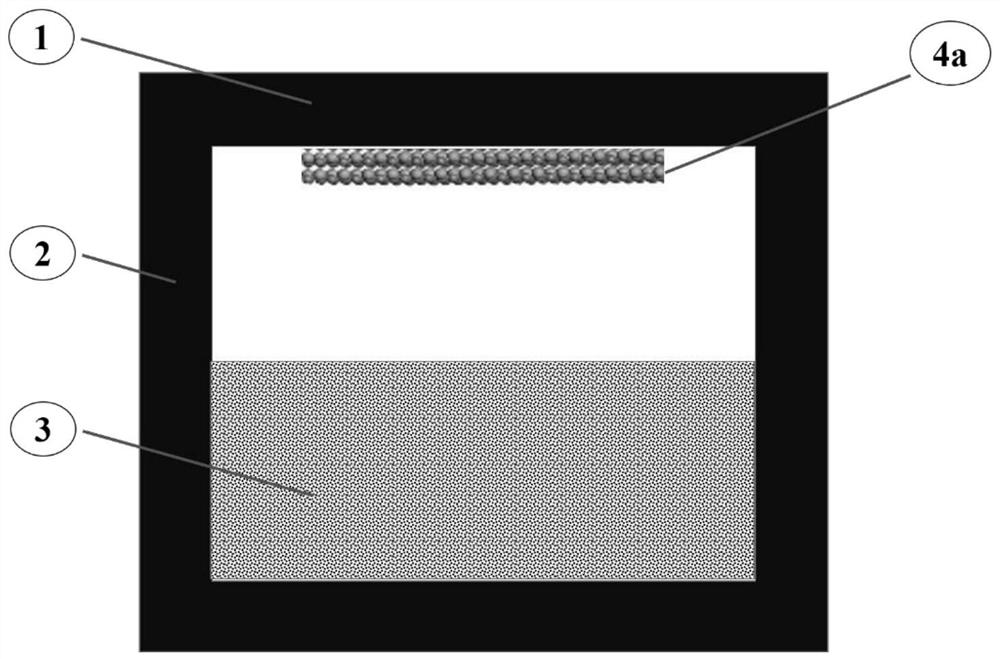

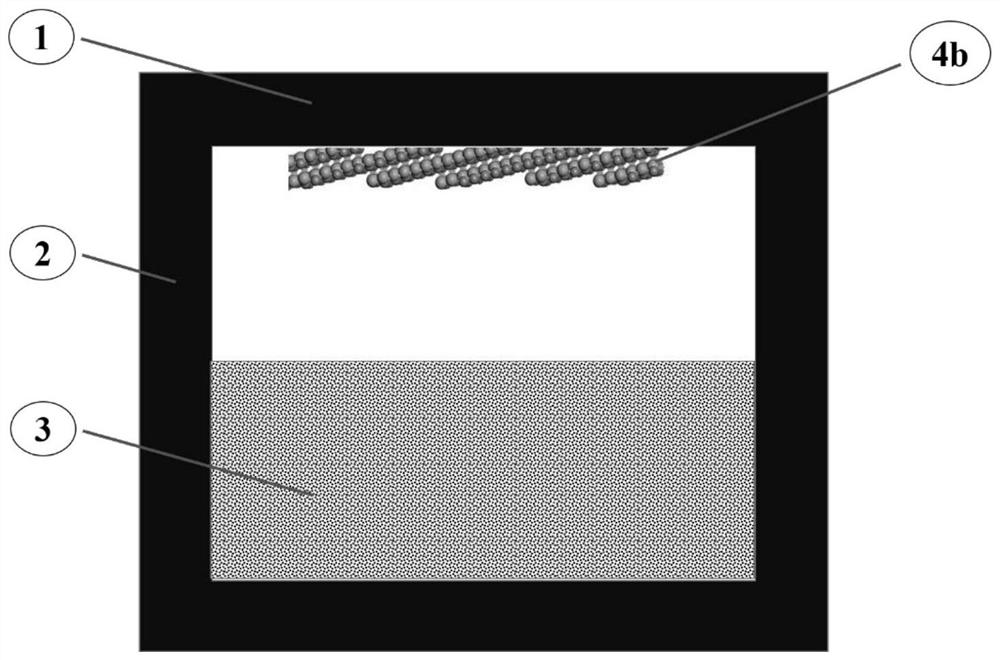

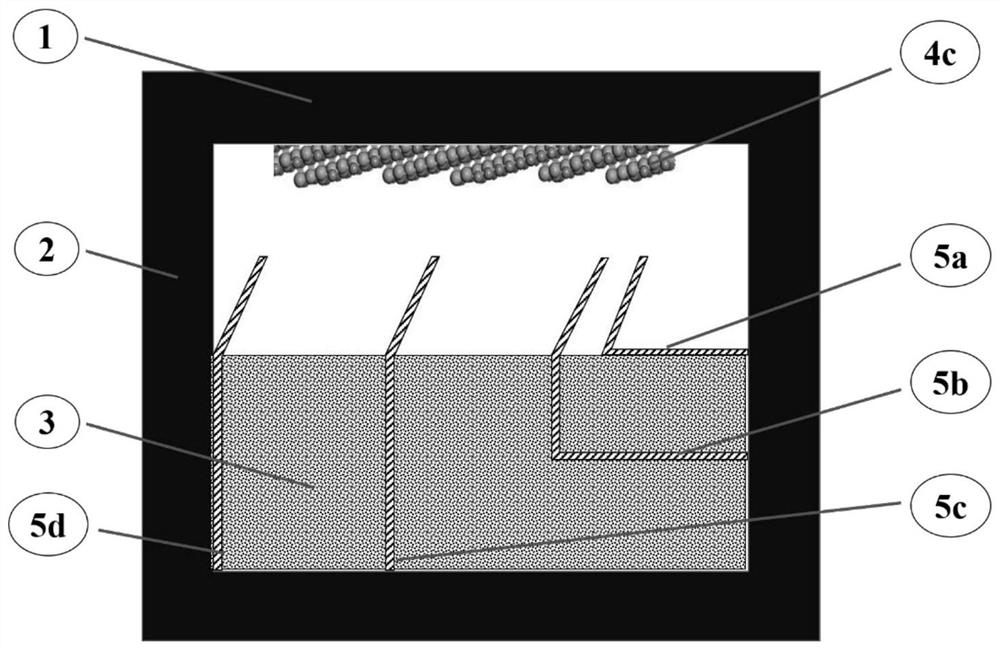

A method for preparing silicon carbide single crystal based on controllable growth center

ActiveCN110656376BImprove crystal qualityNo crackPolycrystalline material growthFrom condensed vaporsCarbide siliconNew energy

The invention discloses a method for preparing a silicon carbide single crystal based on a controllable growth center, belonging to the field of crystal growth. The present invention adjusts the transmission direction of the growth component flow and the flow density of the transport component by placing a deflected growth component flow guiding device in the powder and the growth chamber, preferentially forming a long and narrow growth center facet and keeping it at the edge of the growth surface Position, so that a balanced step flow growth mode can be maintained within the required single crystal diameter, and the crystal form of the seed crystal can be completely maintained, and finally a high-quality silicon carbide crystal with a single crystal form can be obtained. The high-quality silicon carbide single crystal prepared by the method of the present invention can be widely used in power electronics fields such as new energy electric vehicles, locomotive traction, industrial automation, uninterruptible power supplies, high-power charging piles, and energy Internet.

Owner:HEBEI SYNLIGHT CRYSTAL CO LTD +1

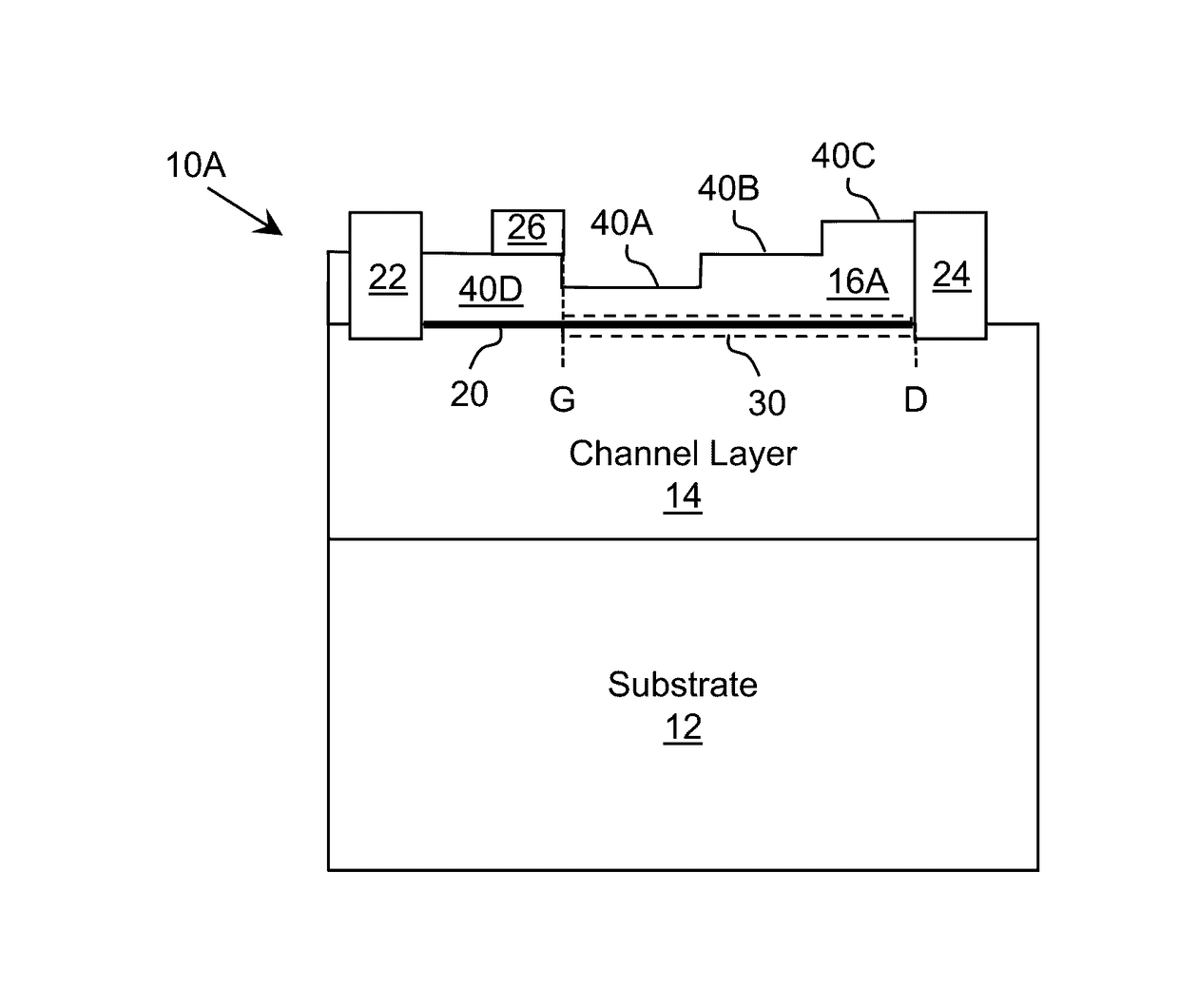

Device with Channel Having Varying Carrier Concentration

ActiveUS20170077278A1Improve electrical uniformityImprove uniformitySemiconductor devicesCharge carrierEngineering

A semiconductor device including a device channel with a gate-drain region having a carrier concentration that varies laterally along a direction from the gate contact to the drain contact is provided. Lateral variation of the carrier concentration can be implemented by laterally varying one or more attributes of one or more layers located in the gate-drain region of the device.

Owner:SENSOR ELECTRONICS TECH

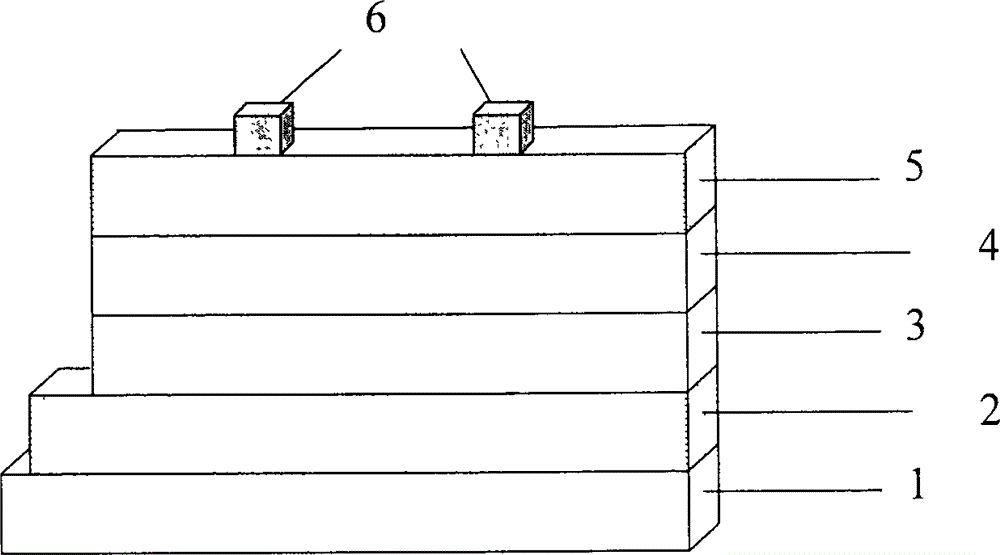

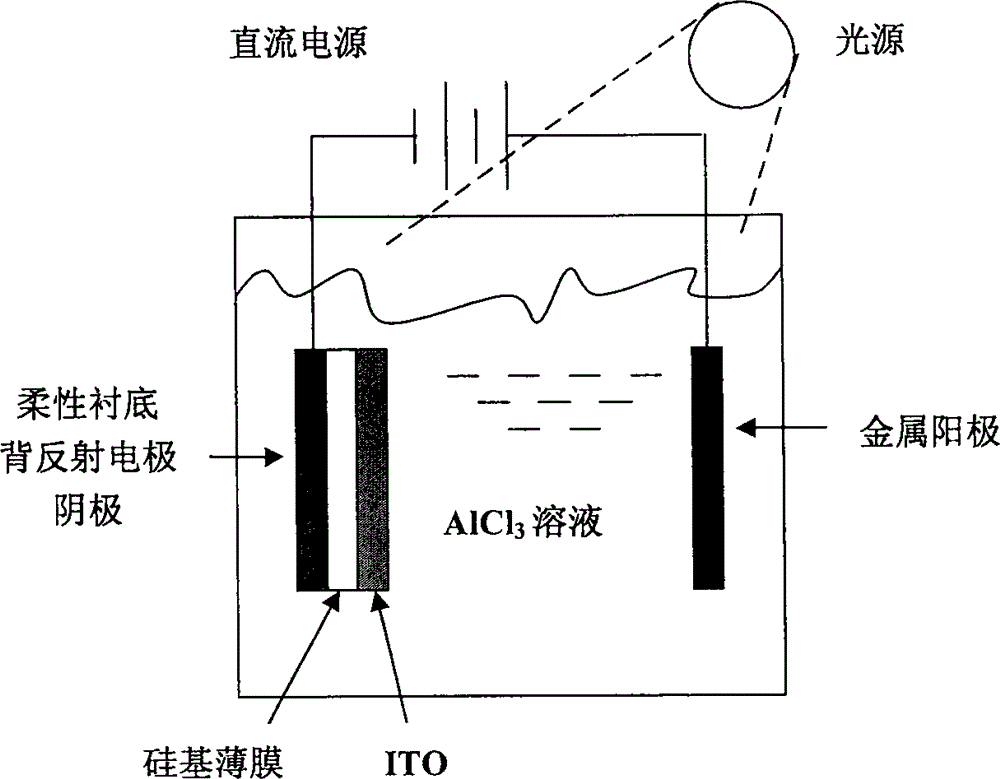

Flexible substrate silicon-based multi-junction stacked thin film solar cell and manufacturing method thereof

InactiveCN103077981BImprove electrical uniformityImprove conversion efficiencyPhotovoltaic energy generationRenewable energy productsPolyesterMetal foil

The invention relates to a photovoltaic solar cell and discloses a flexible substrate silicon-based multi-junction laminated thin-film solar battery. The flexible substrate silicon-based multi-junction laminated thin-film solar battery comprises a back reflection electrode, microcrystalline silicon (muc-Si:H) or amorphous silicon germanium (a-SiGe:H) bottom battery, an amorphous silicon (a-Si:H) top battery, a transparent conducting film and a metal grid line which are sequentially deposited on a metal foil or polyester film substrate, wherein the bottom battery is electrically connected with the top battery by adopting a composite tunneling junction. The invention also discloses a manufacturing method for the battery. The manufacturing method comprises the following steps of: carrying out sputtering deposition on the back reflection electrode; depositing microcrystalline silicon or amorphous silicon germanium bottom battery; depositing the amorphous silicon top battery; carrying out sputtering deposition on transparent conducting films such as ITO (Indium Tin Oxide), SnO2.F, ZnO:Al, ZnO:Ga and the like; carrying out electro chemical passivation; preparing the metal grid line and the like. The flexible substrate silicon-based multi-junction laminated thin-film solar battery disclosed by the invention has the beneficial effects that the conversion efficiency of the battery and the large-area uniformity are increased, high efficiency and high power specific weight ratio are obtained and the like; and meanwhile, a preparation process is simple and the scale production can be realized.

Owner:SHANGHAI INST OF SPACE POWER SOURCES

Preparation method and application of monocrystalline silicon wafer

ActiveCN109747055BIncrease profitEfficient use ofPolycrystalline material growthAfter-treatment detailsCondensed matter physicsMaterials science

The invention discloses a method for preparing a single crystal silicon wafer, which can cut a single crystal silicon rod into a strip-shaped right-angle single crystal silicon wafer and a single-crystal silicon quasi-square sheet, or cut a single crystal silicon rod into a strip-shaped right-angle single Crystal silicon wafers and monocrystalline silicon square wafers can improve the utilization rate of monocrystalline silicon rods.

Owner:CHANGZHOU SHICHUANG ENERGY CO LTD

Method for manufacturing multilayer metal-silicon oxide-metal (MOM) capacitor

ActiveCN102437024BEfficient removalIncrease capacitanceSemiconductor/solid-state device manufacturingCapacitanceSilicon oxide

The invention provides a method for manufacturing a multilayer metal-silicon oxide-metal (MOM) capacitor. The method has the following beneficial effects: the multilayer MOM capacitor is formed by forming a mixed layer of a low-k dielectric and high-k silicon oxide, then utilizing the traditional photoetching and etching processes to form metal grooves in the low-k dielectric and silicon oxide respectively and filling metals into the metal grooves and repeating the previous steps; the MOM capacitor structure is realized in the high-k silicon oxide region and interconnection of the low-k dielectric is realized in other regions; and high-k silicon oxide is formed by circularly carrying out plasma enhanced chemical vapor deposition (PECVD) and oxygen-containing gas treatment so that the silicon-hydrogen bonds in silicon oxide can be effectively removed. Compared with the traditional single k dielectric structure, the method has the following advantages: not only can the capacitance of the capacitor in the layer be effectively improved, but also the electrical characteristics of the MOM capacitor such as breakdown voltage, leakage current and the like and the electrical uniformity among the components are improved.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Metal-multilayer insulator-metal capacitor as well as preparation method and integrated circuit thereof

ActiveCN102623305BIncrease capacitanceImprove breakdown voltageSemiconductor/solid-state device detailsSolid-state devicesCapacitanceEngineering

The invention discloses a metal-multilayer insulator-metal capacitor as well as a preparation method and an integrated circuit thereof. The preparation method of the metal-multilayer insulator-metal capacitor disclosed by the invention comprises a dielectric layer providing step used for providing a dielectric layer, a capacitor slot forming step used for forming a capacitor slot of a capacitor in the dielectric layer, a capacitor slot filling step used for filling the capacitor slot with silicon nitride, a capacitor pattern forming step used for patterning the filled silicon nitride so as to form a plurality of silicon nitride pillars, a silicon nitride depositing step used for depositing the silicon nitride on the side walls of the silicon nitride pillars, and a metal filling step used for filling the concave parts in the patterned silicon nitride with metal. According to the invention, the capacitance between the layers and capacitance of the capacitor in the layers can be effectively enhanced, and the electrical characteristics, such as breakdown voltage, leakage current and the like of the metal-multilayer insulator-metal capacitor and the electrical uniformity among devices can be improved.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Method for manufacturing multilayer metal-oxide-metal capacitor

ActiveCN102437023BEfficient removalIncrease capacitanceSemiconductor/solid-state device manufacturingCapacitanceEtching

The invention provides a method for manufacturing a multilayer metal-oxide-metal (MOM) capacitor. The method comprises the following steps of: forming a mixed layer of a low-k-value medium and high-k-value silicon oxide; forming a metallic groove in the low-k-value medium by using photolithographic etching of the conventional process, and filling a metal into the metal groove; repeating the above steps; and thus, obtaining the multilayer metal-oxide-metal capacitor. An MOM capacitor structure is realized in a high-k-value silicon oxide area, and the interconnection of the low-k-value media is realized in another area; the high-k-value silicon oxide is formed in a mode of plasma enhanced chemical vapor deposition (PECVD) and oxygen-containing gas processing circulation; and silicon-hydrogen bonds in the silicon oxide can be effectively removed. Compared with the conventional single-k-value medium structure, the method can improve the capacitance of an in-layer capacitor effectively, and improve the electrical characteristics such as breakdown voltage, leakage current and the like of the MOM capacitor, and the electrical uniformity between devices.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

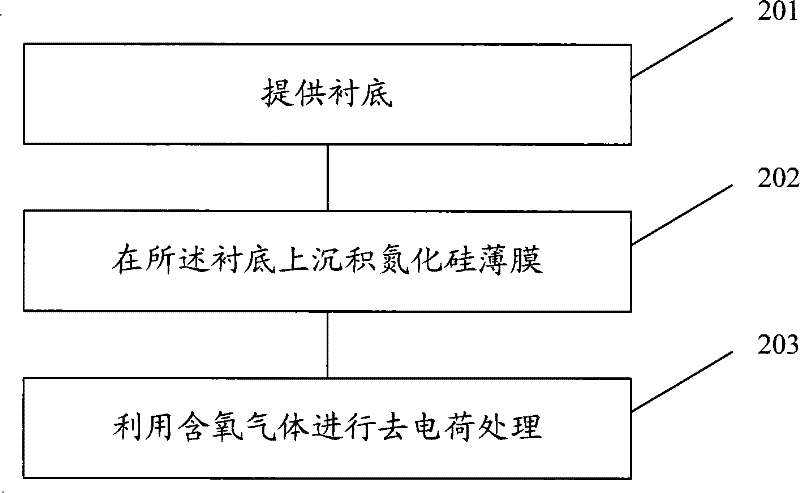

Forming methods of silicon nitride film and MIM capacitor

ActiveCN101577227BImprove electrical thickness uniformityReduce chargeSemiconductor/solid-state device manufacturingCapacitanceOxygen

The invention discloses a forming method of a silicon nitride film, comprising the steps: providing a substrate; depositing the silicon nitride film on the substrate, and processing the silicon nitride film by oxygen-containing gas. The invention also correspondingly discloses a forming method of an MIM capacitor by utilizing the forming method of the silicon nitride film. The silicon nitride filmformed by the method has less quantity of electric charge, so the evenness of the electrogenicity thickness and the physical thickness of the silicon nitride film are enhanced. The MIM capacitor formed by the method has the advantages that not only the electrical characteristics of puncturing voltages and leakage current, and the like are improved but also electricity evenness among components isenhanced.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

Method for producing multilayer metal-silicon nitride-metal capacitor

ActiveCN102592968BIncrease capacitanceImprove electrical uniformitySemiconductor/solid-state device manufacturingCapacitanceGas phase

The invention provides a method for producing a multilayer metal-silicon nitride-metal capacitor, which includes the following steps: 1) using a plasma enhanced chemical vapor deposition (PECVD) method to deposit a silicon nitride thin film with a high k value on a silicon chip substrate; 2) removing silicon nitride in a non-metal-oxide-metal area through photoetching and etching; 3) depositing a dielectric layer with a low k value; 4) removing redundant silicon nitride through chemical mechanical polishing, and forming a mixing layer of low-k-value dielectric and silicon nitride; 5) completing photoetching and etching to form a metallic channel in the low-k-value dielectric and the silicon nitride; 6) forming metal fillers of a lead and a metal-oxide-metal (MOM) capacitor after deposition and chemical mechanical polishing of a metal layer are completed; and 7) repeating Step 1) to Step 6) to form multilayer MOM capacitor. The method for producing the multilayer metal-silicon nitride-metal capacitor can effectively improve the capacitance of the interlayer capacitor, can also effectively improve various electric characteristics of the MOM capacitor such as breakdown voltage, leakage current and the like, can effectively improve electric uniformity among various apparatuses, and is very practical.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Manufacture method of metal-silicon oxide-metal capacitor

InactiveCN102709153AImprove electrical uniformityReduce silicon-hydrogen bondsSemiconductor/solid-state device manufacturingSilicon oxideOptoelectronics

The invention discloses a manufacture method of a metal-silicon oxide-metal capacitor. The manufacture method comprises the following steps of: providing a substrate; depositing a first low-dielectric-constant dielectric layer on the substrate, wherein the first low-dielectric-constant dielectric layer comprises a metal-oxide-metal manufacture area and a nonmetal-oxide-metal manufacture area; depositing a silicon oxide layer on the first low-dielectric-constant dielectric layer via the way of circularly depositing and processing oxygen-containing gas, wherein the silicon oxide layer comprises the first silicon oxide layer of the metal-oxide-metal manufacture area and the second silicon oxide layer of the nonmetal-oxide-metal manufacture area; etching the second silicon oxide layer; depositing a second low-dielectric-constant dielectric layer on the nonmetal-oxide-metal manufacture area; etching the first silicon oxide layer to form a first metallic channel, and etching the second low-dielectric-constant dielectric layer to form a second metallic channel; and performing a metal filling process to the first metallic channel and the second metallic channel. The invention improves the electrical characteristics and the electrical uniformity of the capacitor.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

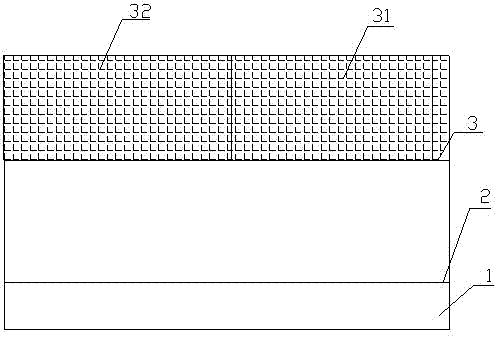

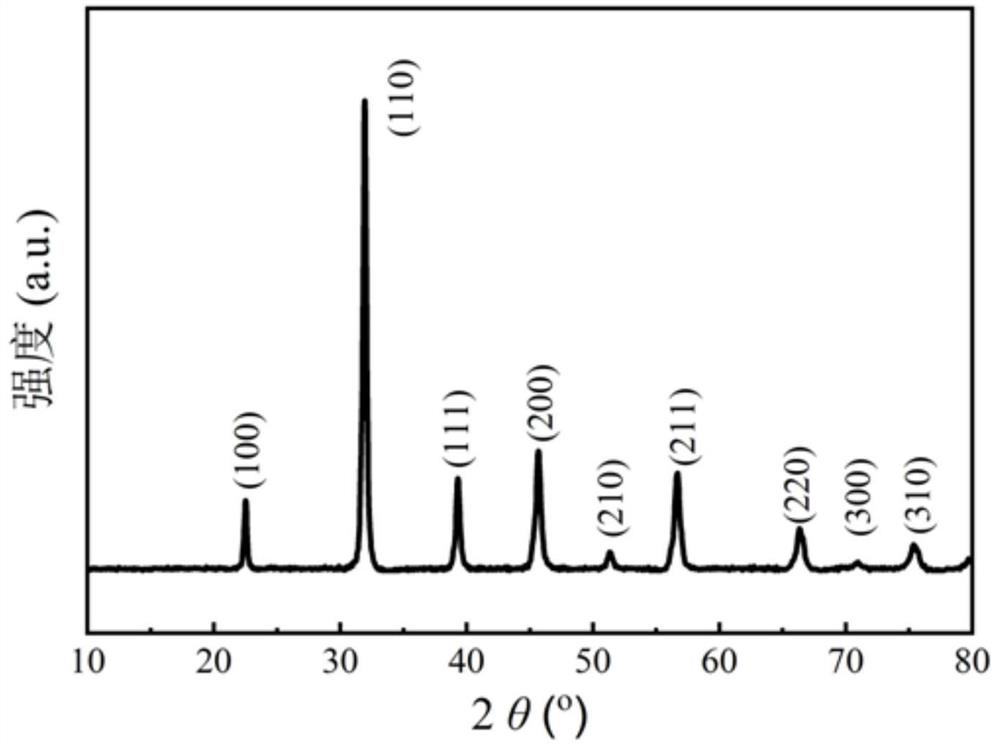

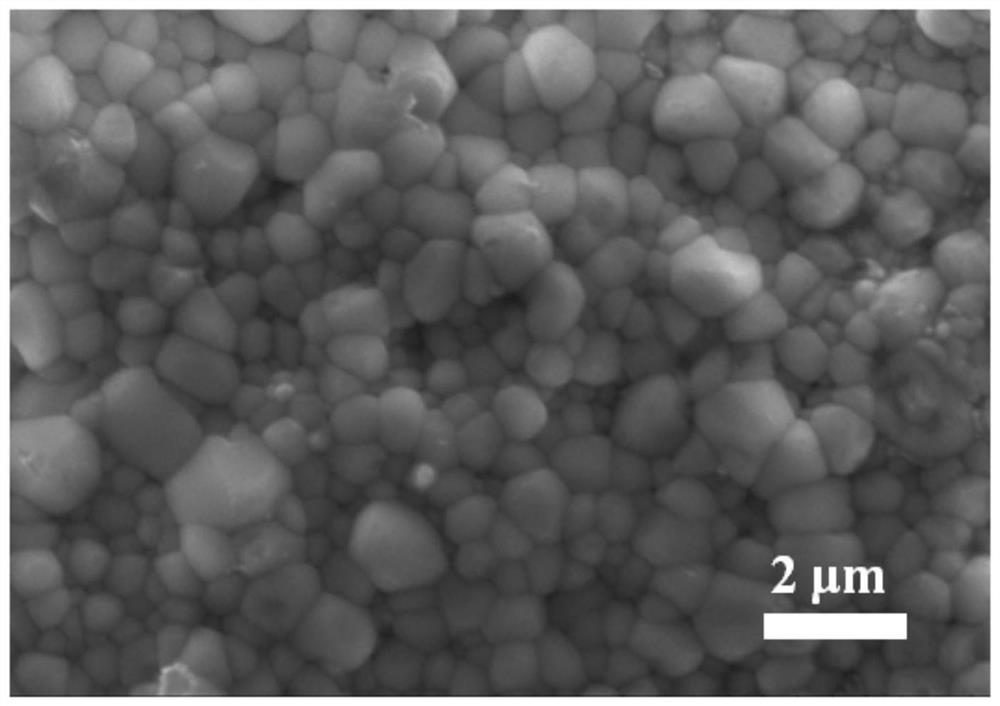

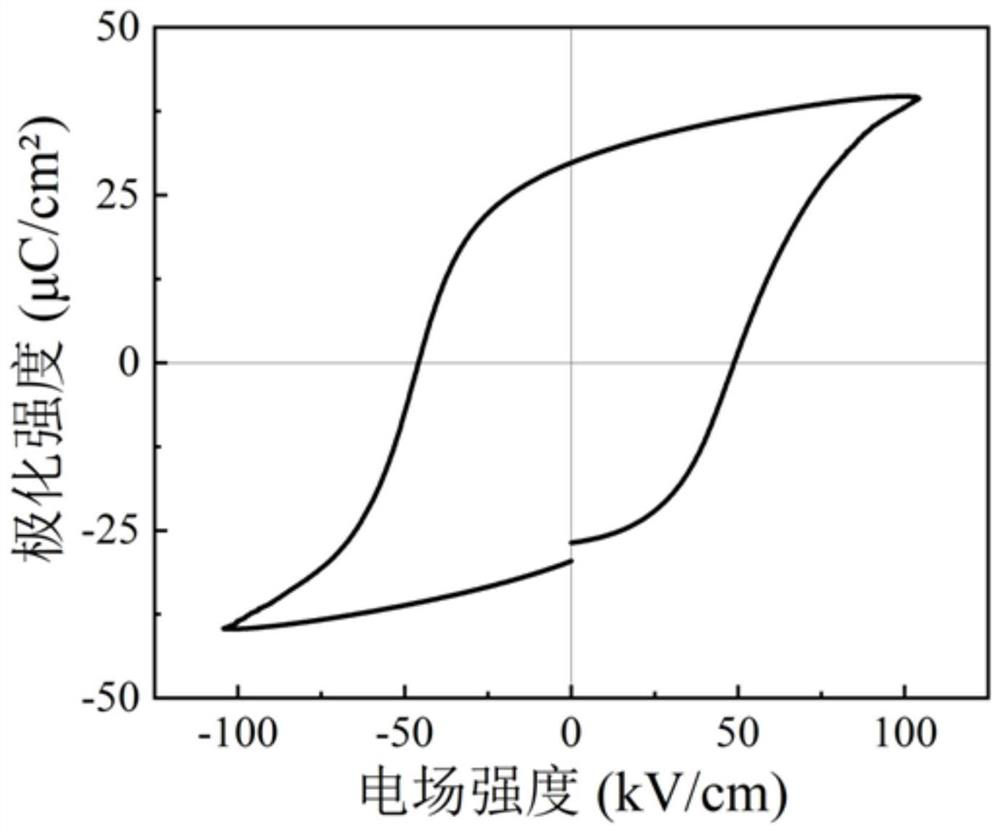

A kind of ceramic material with high electrical energy storage efficiency and preparation method thereof

ActiveCN111170735BImproved energy storage efficiencyGood chemical uniformityElectrical field strengthChemical composition

The invention discloses a ceramic material with high electric energy storage efficiency and a preparation method thereof, belongs to the technical field of electronic ceramic materials, overcomes the problems of low electric energy storage efficiency and serious energy waste of energy storage ceramics in the prior art, and the prepared product electric energy High storage efficiency, chemical uniformity and good electrical stability. The electronic ceramic material chemical composition of the present invention is (1-x) ((1-y) BaTiO 3 -y(Bi 0.5 Na 0.5 )TiO 3 )‑xSr(Sc 0.5 Nb 0.5 )O 3 , where x is 0.05‑0.15 and y is 0.35. The product of the invention has high repeatability, uniform internal grain size, high chemical uniformity and electrical uniformity, and exhibits high energy storage efficiency. The energy storage ceramic material prepared by the present invention has a maximum energy storage efficiency of 91% and an energy storage density of 1.63 J / cm³ when the applied electric field strength is 175 kV / cm3. The energy storage ceramic material prepared by the invention can be applied to high-power and high-stability electronic pulse components, and has great practical value and economic value.

Owner:XIAN TECH UNIV

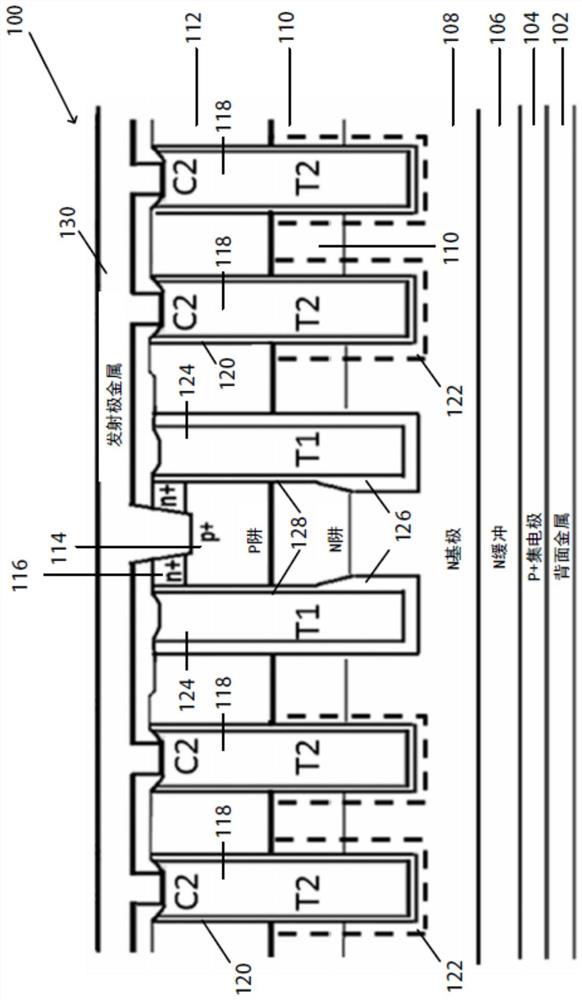

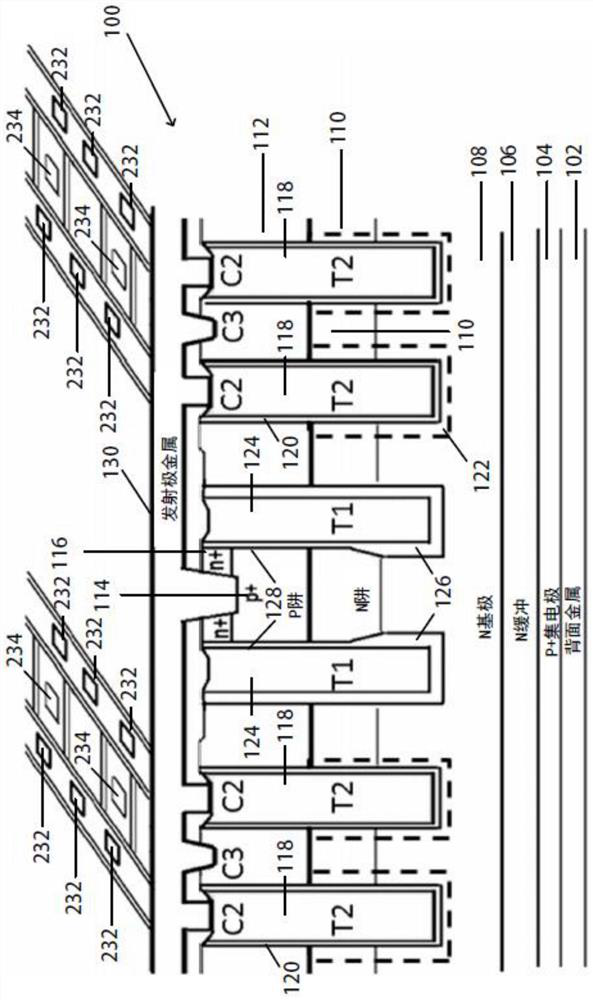

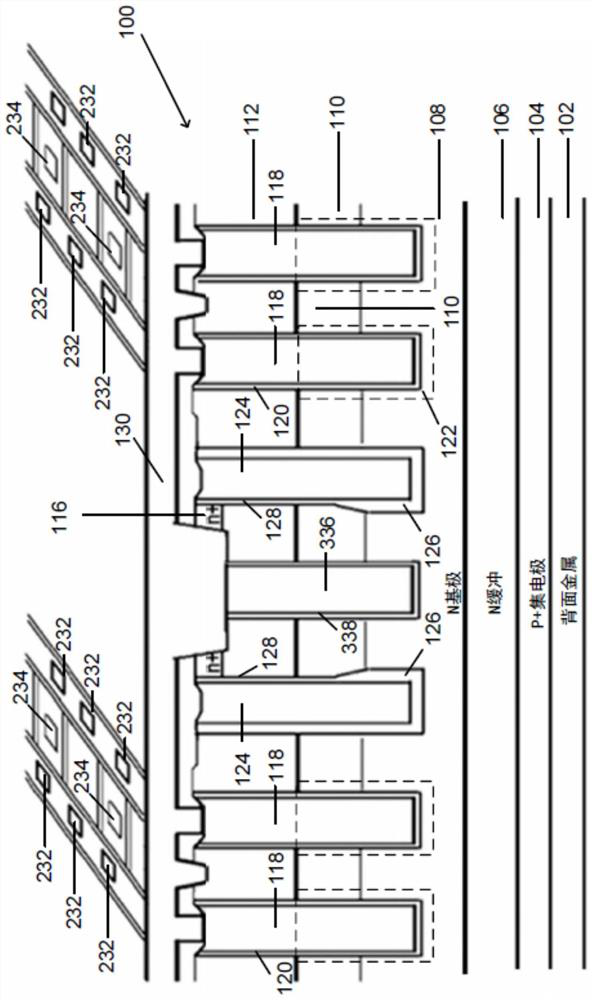

IGBT with varied trench oxide thickness region

PendingCN114788012AImprove uniformityImprove electrical uniformitySemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialPhysical chemistry

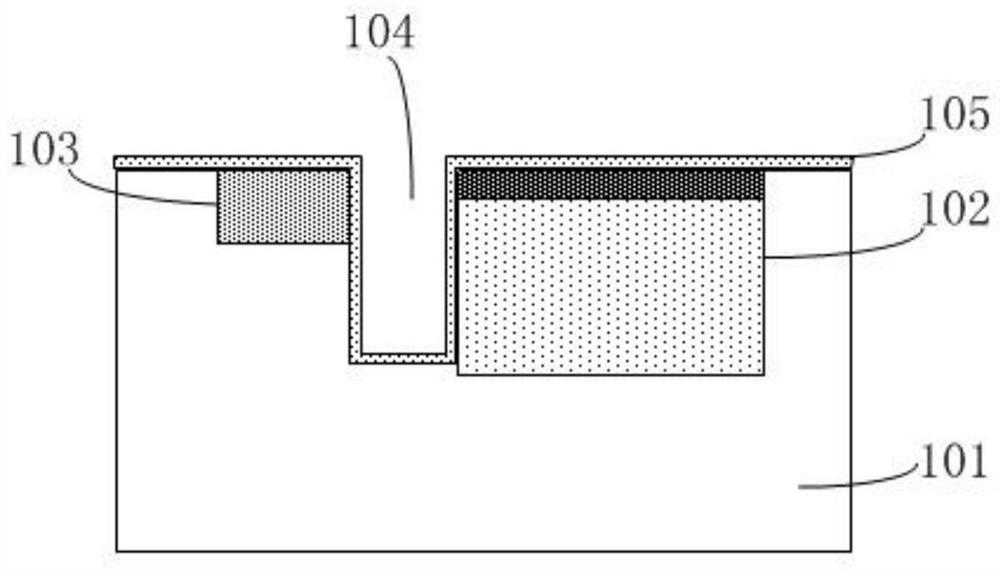

Described herein is a gated bipolar semiconductor device comprising a collector region (104) of a first conductivity type, a drift region (106, 108) of a second conductivity type over the collector region, a body region (110) of the first conductivity type over the drift region, a body region (112) of the second conductivity type over the drift region, at least one first contact region of a second conductivity type over the body region and having a higher doping concentration than the body region, at least one second contact region (116) of the first conductivity type laterally adjacent to the at least one first contact region, the at least one second contact region has a higher doping concentration than the body region, at least one active trench (124) extending from the surface into the drift region wherein the at least one first contact region adjoins the at least one active trench such that, in use, a channel region is formed along the at least one active trench and within the body region, and at least two auxiliary trenches (118) extending from the surface into the drift region. The at least two auxiliary trenches each include an insulating layer (122) along the vertical sidewalls and the bottom surface. A thickness of the insulating layer along two vertical sidewalls of the at least two auxiliary trenches is less than 1500 A. The body region of the first conductivity type and the body region of the second conductivity type are both at least located between two adjacent auxiliary trenches. Possibly, the device further includes a transmitter trench (336) located between the two active trenches (124) and recessed from the top surface.

Owner:DYNEX SEMICONDUCTOR +1