IGBT with varied trench oxide thickness region

A region and trench technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of inability to adjust the conduction dI/dt, collection of holes, poor thermal performance, etc., to improve process control and yield, The effect of reducing the number of defects and improving the uniformity of electrical properties

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

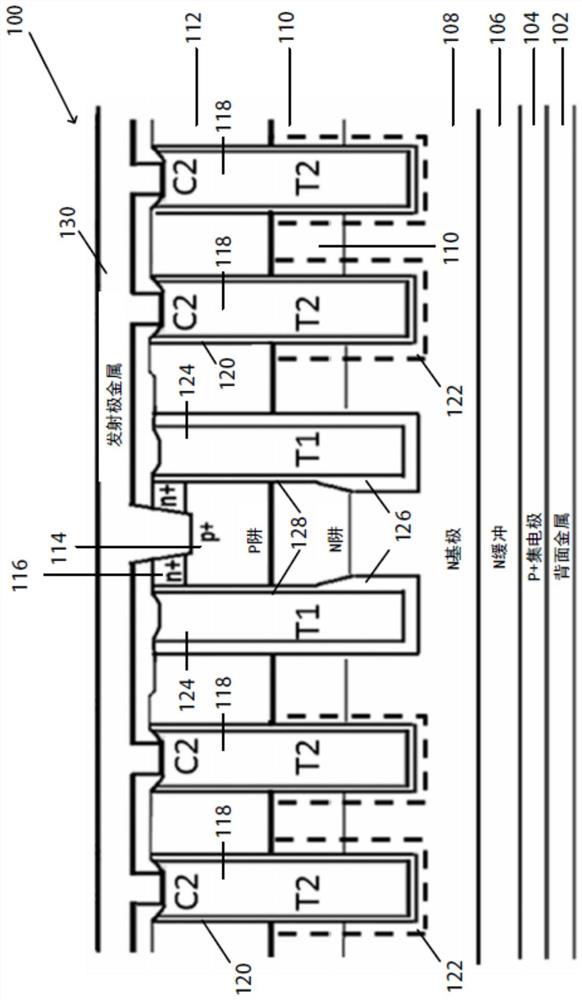

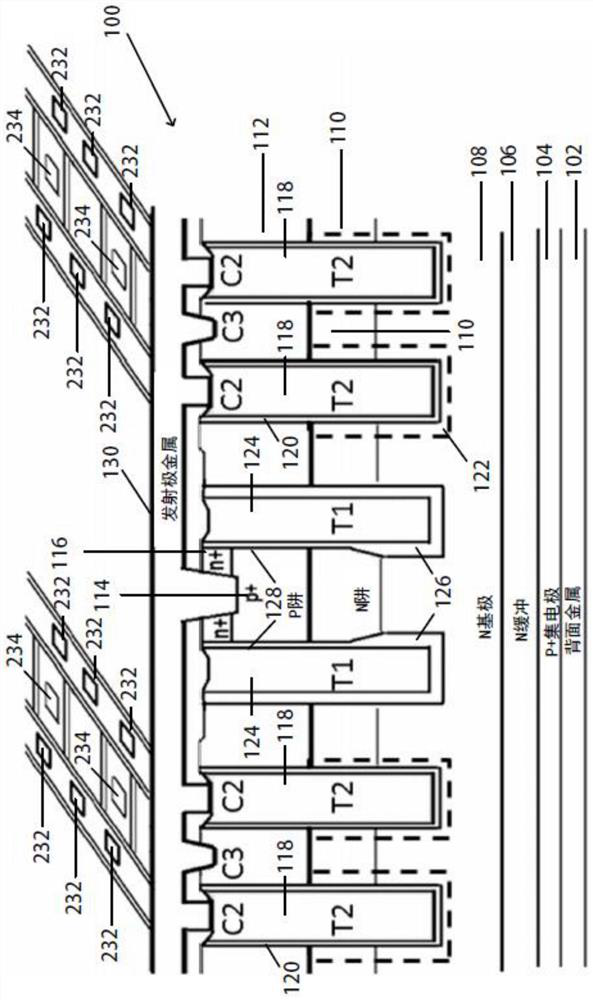

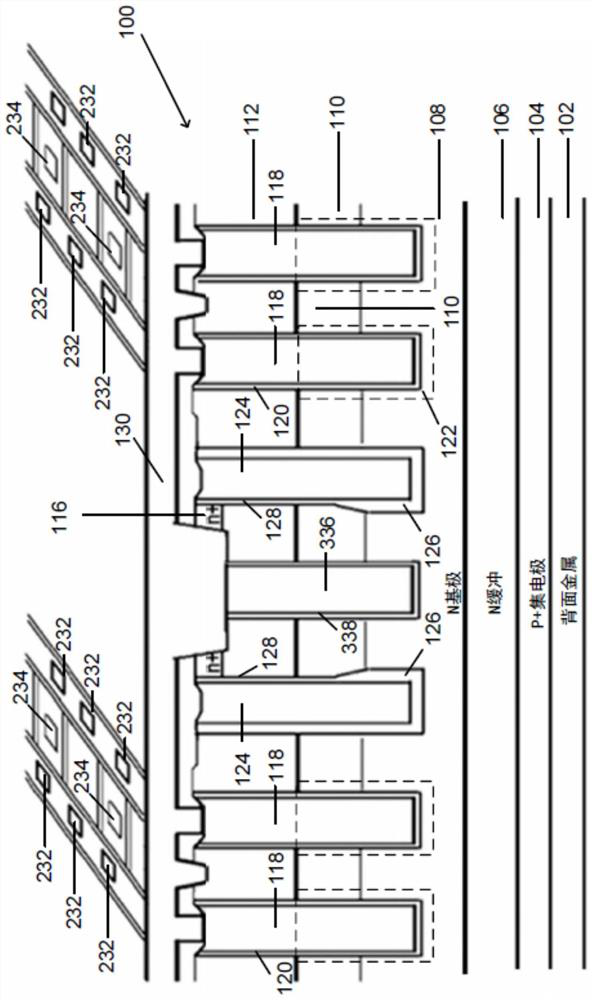

[0140] figure 1 A cross-sectional view of a semiconductor device 100 according to an embodiment of the present disclosure is shown. In this embodiment, device 100 includes an n-type voltage sustaining region or n-base (or drift region) 108 over a collector p+ layer (substrate) 104 . The collector p+ layer 104 is, for example, a p-type diffusion on the backside, which provides holes for bipolar conduction in the on state. The n buffer layer 106 is located between the p+ collector layer 104 and the n base region 108 . The back metal contact 102 is located below the collector p+ layer 104 .

[0141] Device 100 includes two active trenches 124 extending from the surface of n+ contact region (or first contact region) 116 down into n-base 108 . The active trench 124 acts as a trench gate along which a MOS channel is formed by applying a positive voltage in the on state. Above n-base region 108 and adjacent to active trench 124, a p-well or p-body (or body region) 112 is provided...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More