Preparation method of vertical-gate semiconductor device

A semiconductor and vertical gate technology, applied in the field of vertical gate semiconductor device preparation, can solve the problem of uneven electrical performance of image sensors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

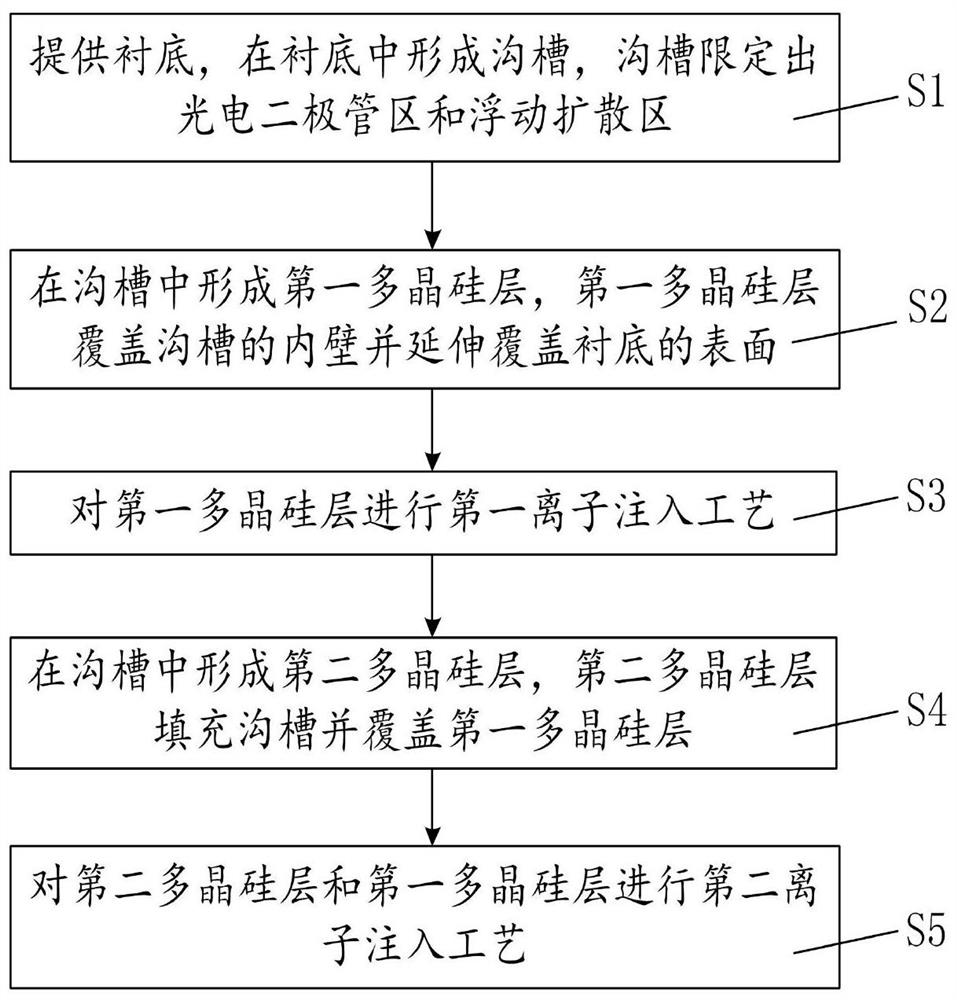

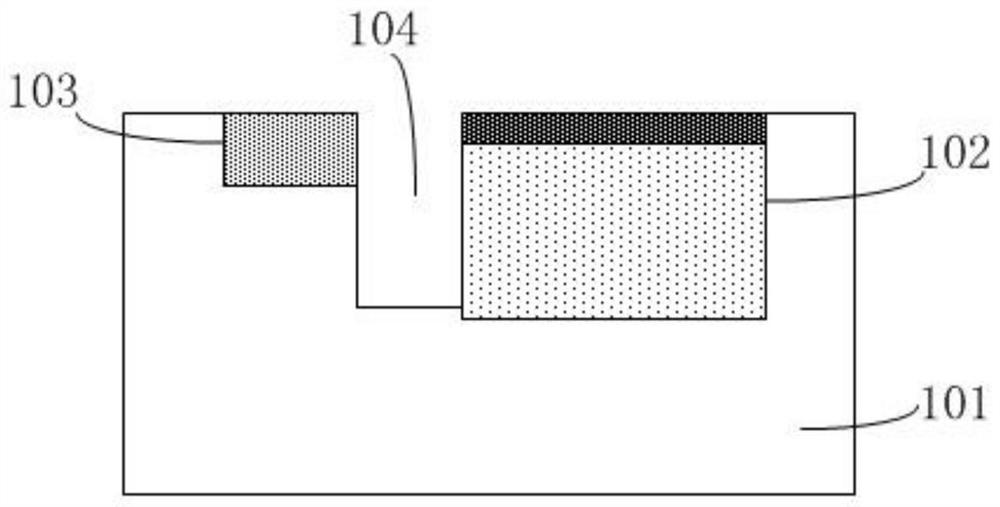

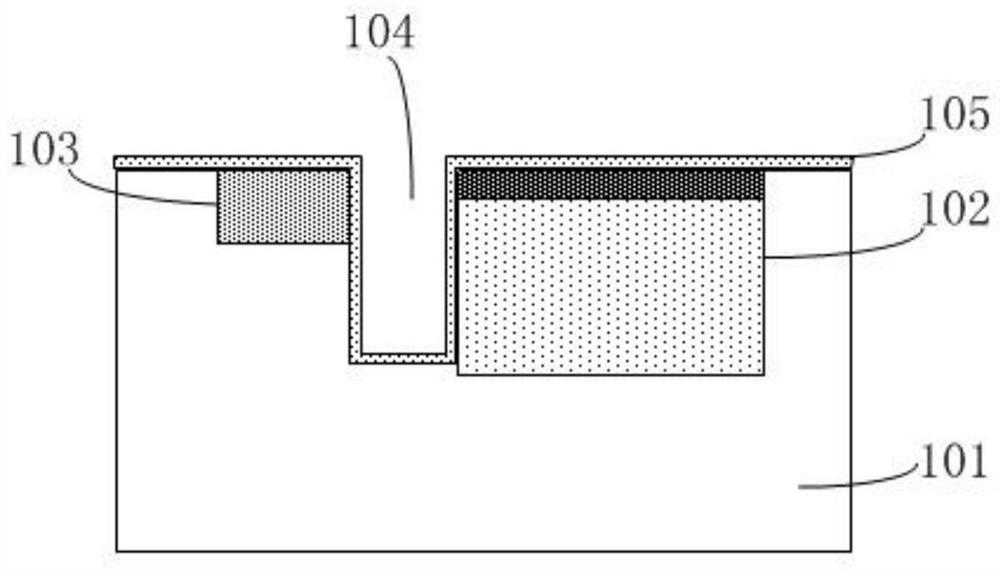

[0026] figure 1 A flowchart of a method for manufacturing a vertical gate semiconductor device provided in this embodiment, Figure 2A-2D A schematic structural diagram of a method for fabricating a vertical gate semiconductor device provided in this embodiment. This embodiment provides a method for fabricating a vertical gate semiconductor device, which is used to improve the phenomenon of uneven electrical properties of image sensors. Please refer to figure 1 ,include:

[0027] Step S1: providing a substrate, forming a trench in the substrate, the trench defines a photodiode region and a floating diffusion region;

[0028] Step S2: forming a first polysilicon layer in the trench, the first polysilicon layer covers the inner wall of the trench and extends to cover the surface of the substrate;

[0029] Step S3: performing a first ion implantation process on the first polysilicon layer;

[0030] Step S4: forming a second polysilicon layer in the trench, the second polysili...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More