Wiring structure forming method

A wiring structure and wet etching technology, which is applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the unfavorable manufacturing cost, the stability of the process quality, the high processing cost of the SOG planarization process, and the control of unfavorable costs etc. to achieve excellent photoelectric properties, improved step morphology, and low film stress

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

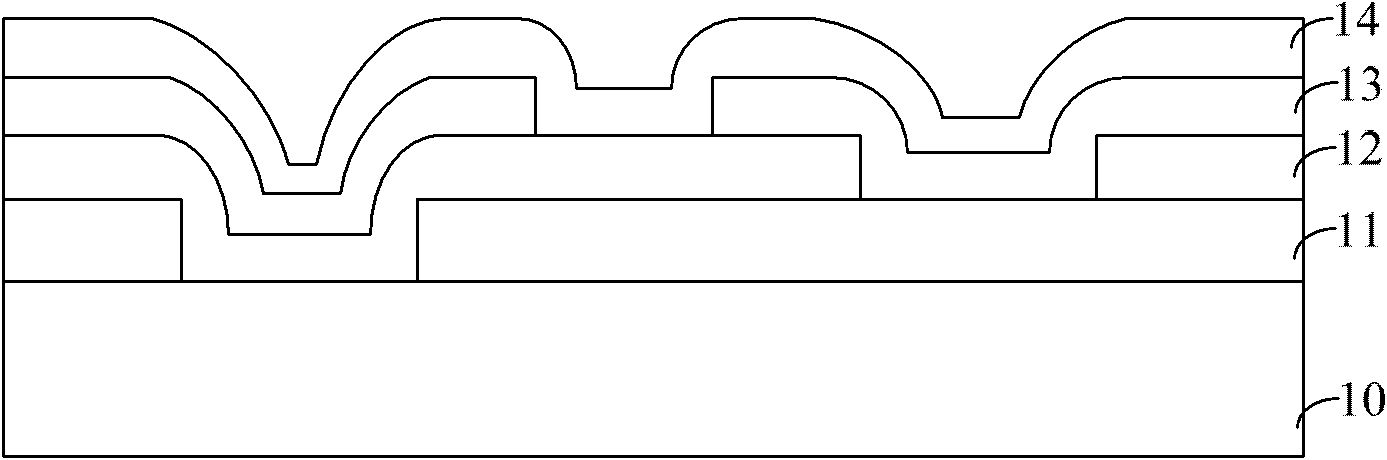

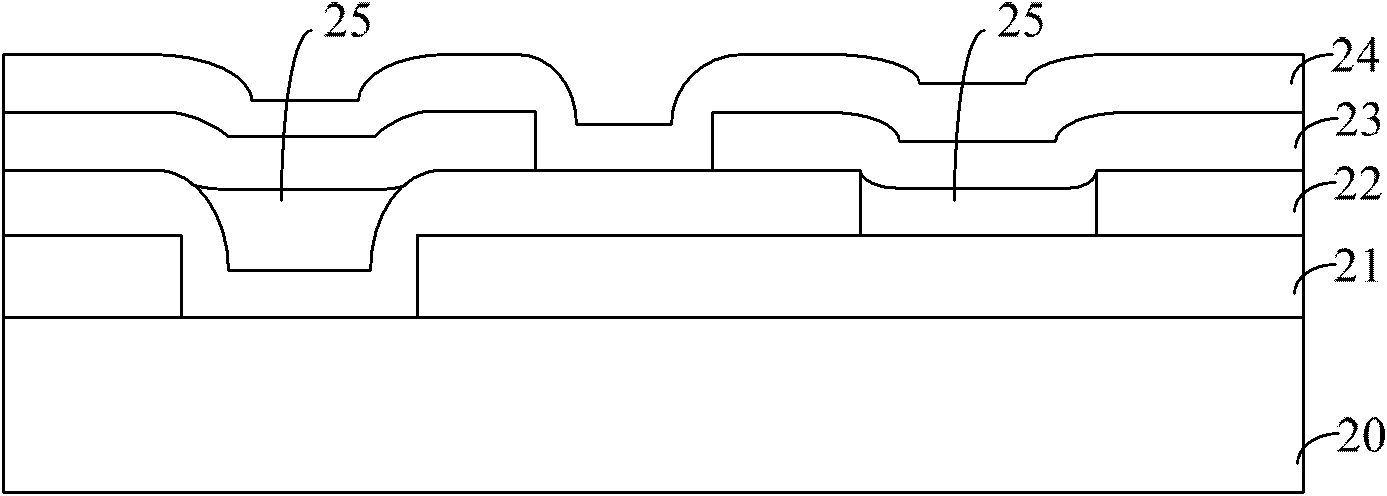

[0032] In the prior art wiring structure formation process, methods such as SOG planarization process are often used to fill the depressions in the front dielectric layer and metal layer, but such methods are relatively complicated and are not conducive to cost control.

[0033] In this embodiment, on the premise of not using the SOG planarization process, the climbing morphology of each film layer is improved by adopting oblique hole contact holes, inverted trapezoidal through-hole structures, and bowl-shaped metal layer openings to meet the step Coverage, step shape and other parameters are also conducive to reducing costs.

[0034]The present invention will be further described below in conjunction with specific embodiments and accompanying drawings, but the protection scope of the present invention should not be limited thereby.

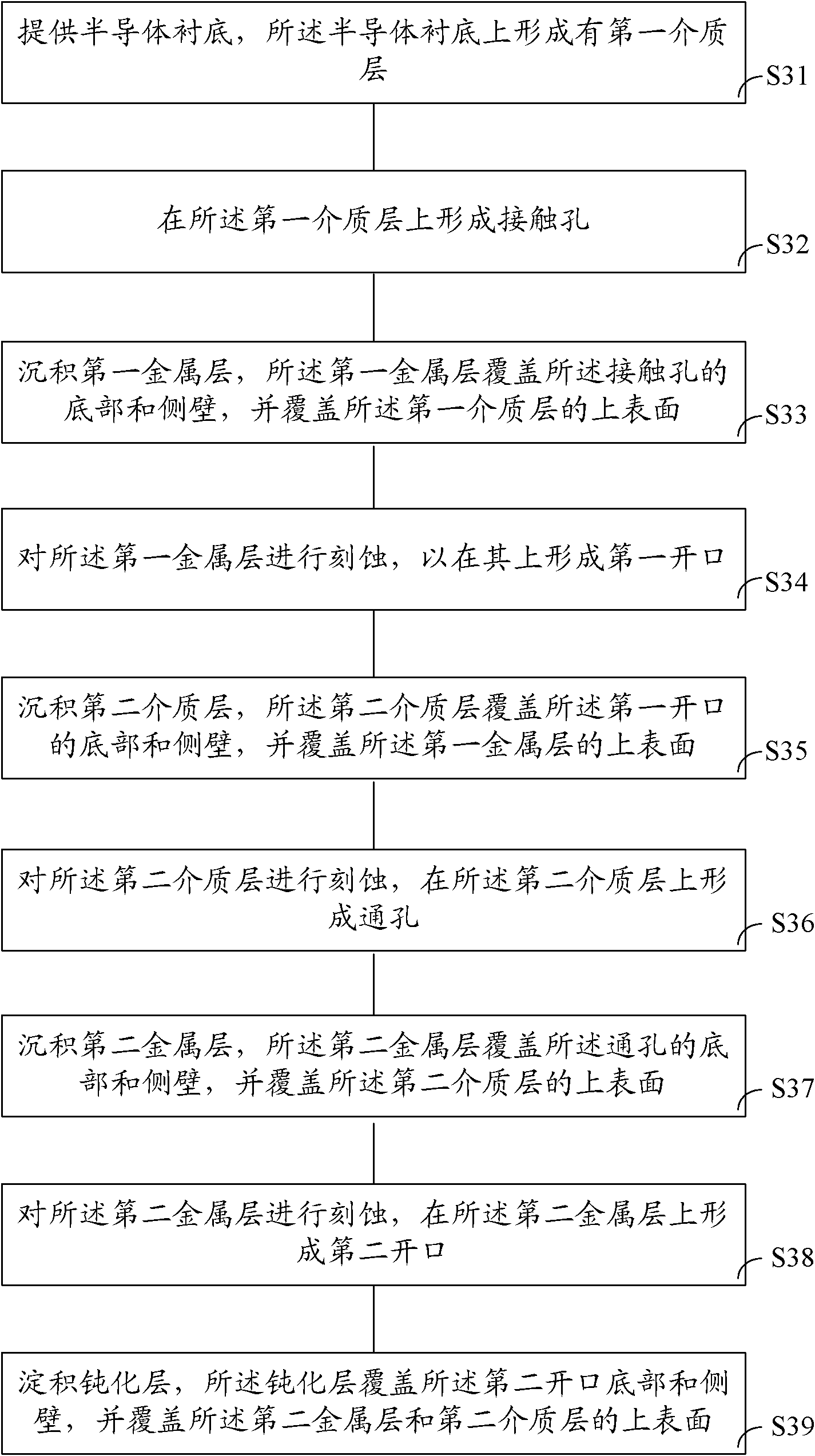

[0035] image 3 A schematic flowchart showing the method for forming the wiring structure of this embodiment, including:

[0036] Step S31, pr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More