Patents

Literature

84results about How to "Complete filling" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

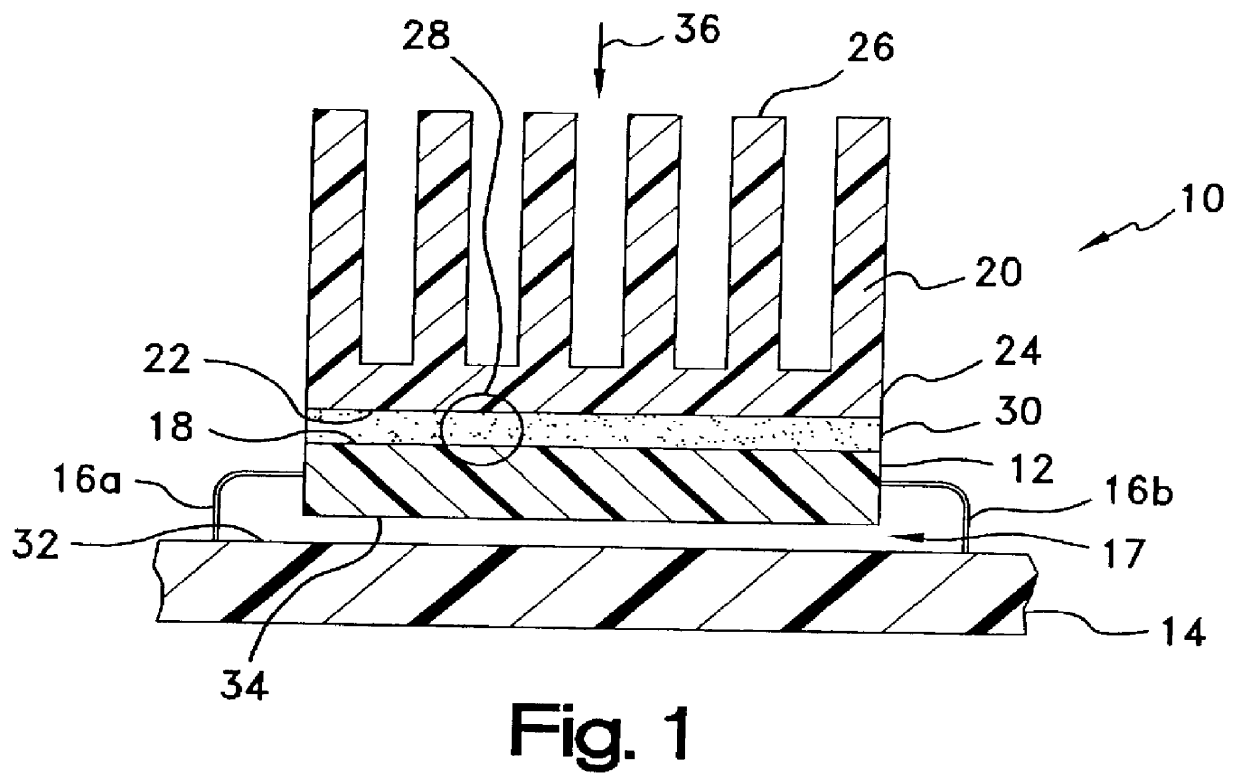

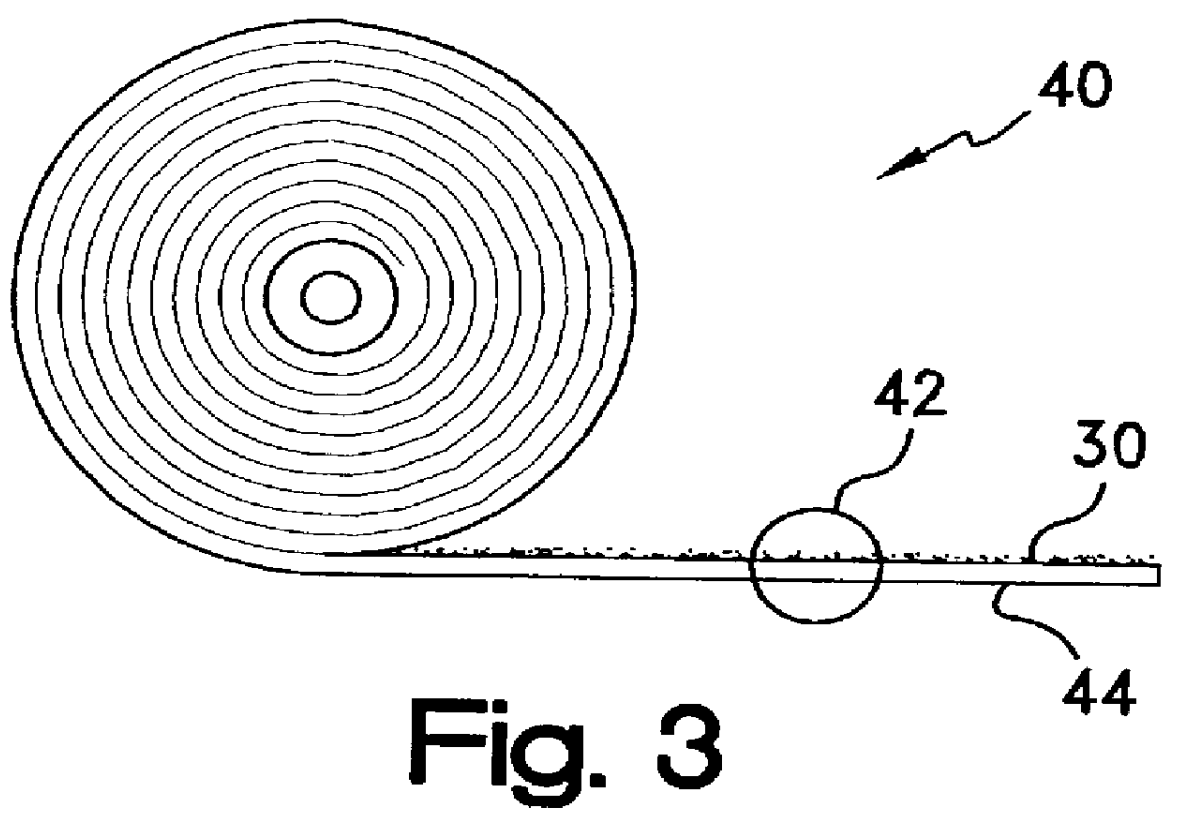

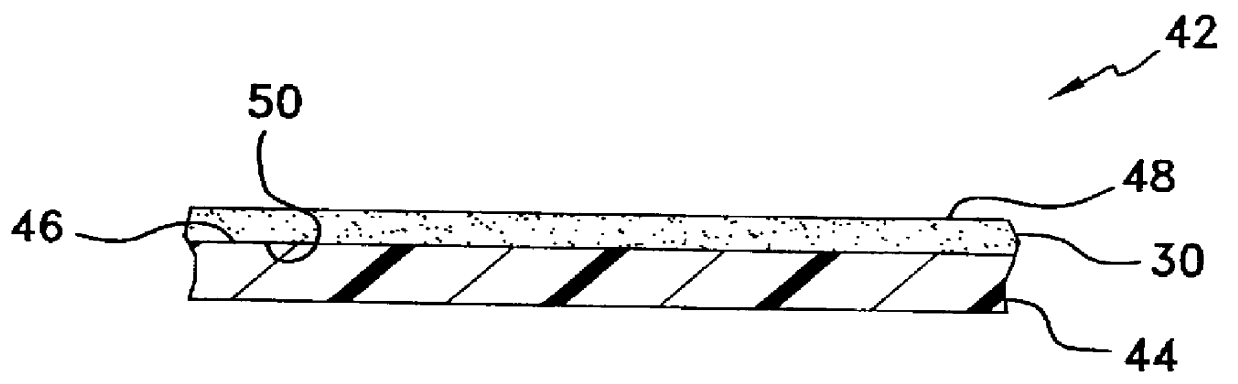

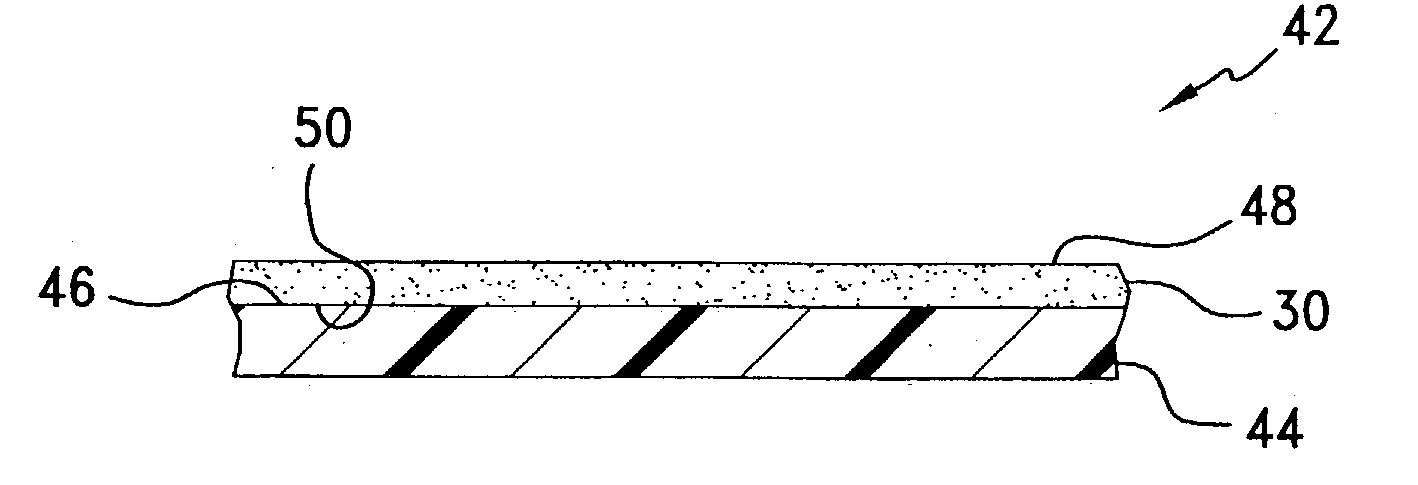

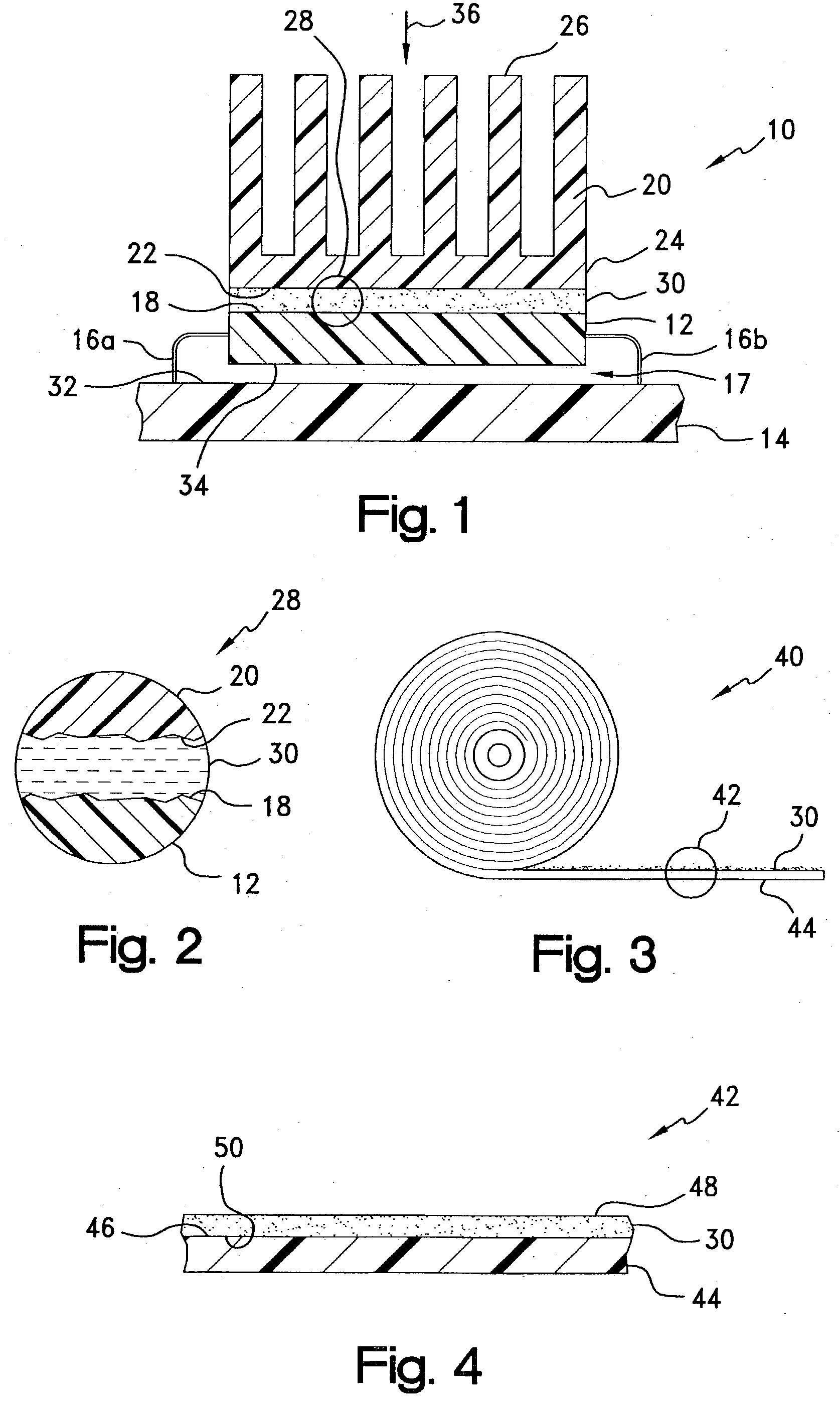

Conformal thermal interface material for electronic components

InactiveUS6054198AOptimize allocationReadily apparentSemiconductor/solid-state device detailsSolid-state devicesRoom temperatureConductive materials

A thermally-conductive interface for conductively cooling a heat-generating electronic component having an associated thermal dissipation member such as a heat sink. The interface is formed as a self-supporting layer of a thermally-conductive material which is form-stable at normal room temperature in a first phase and substantially conformable in a second phase to the interface surfaces of the electronic component and thermal dissipation member. The material has a transition temperature from the first phase to the second phase which is within the operating temperature range of the electronic component.

Owner:PARKER INTANGIBLES LLC

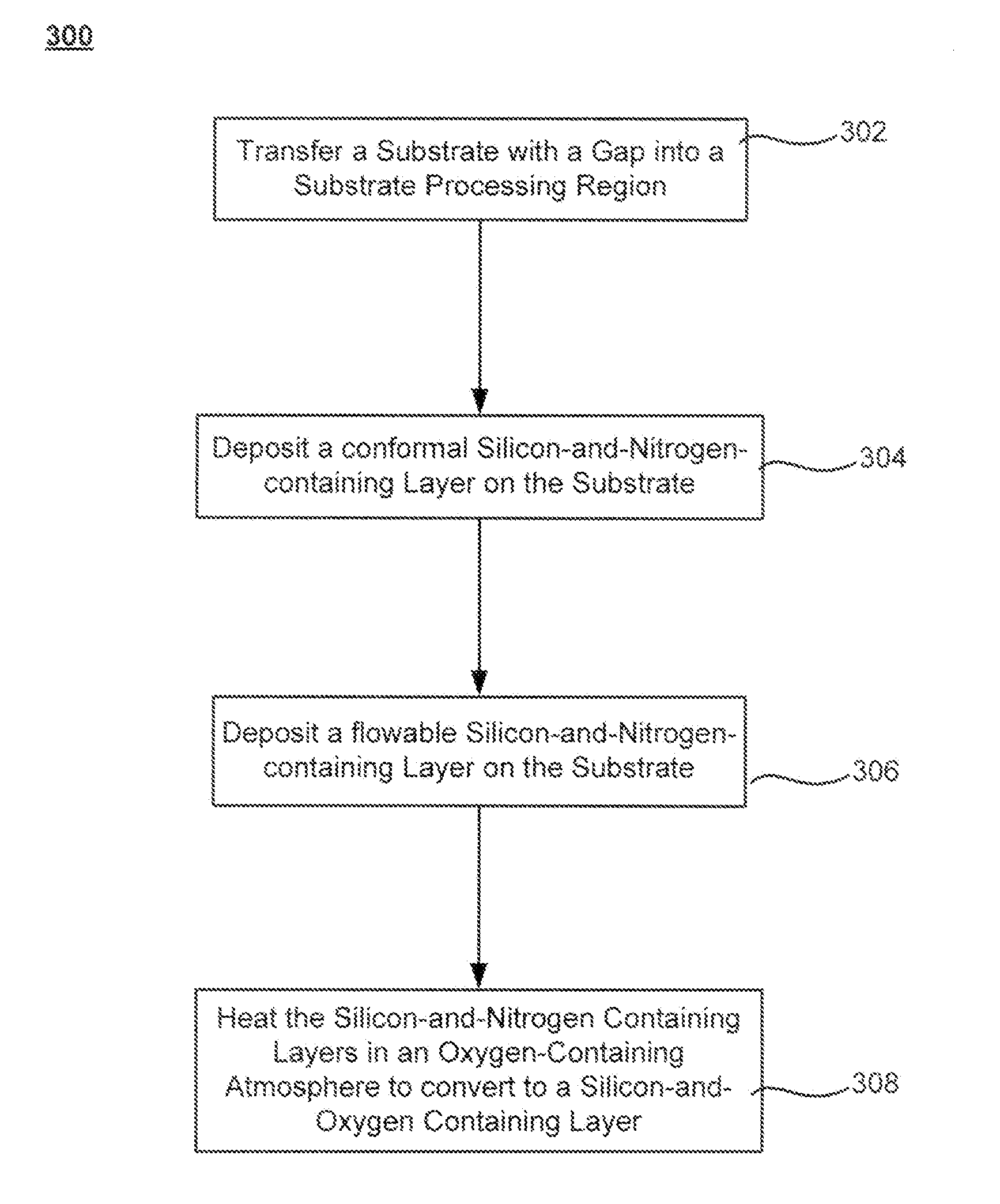

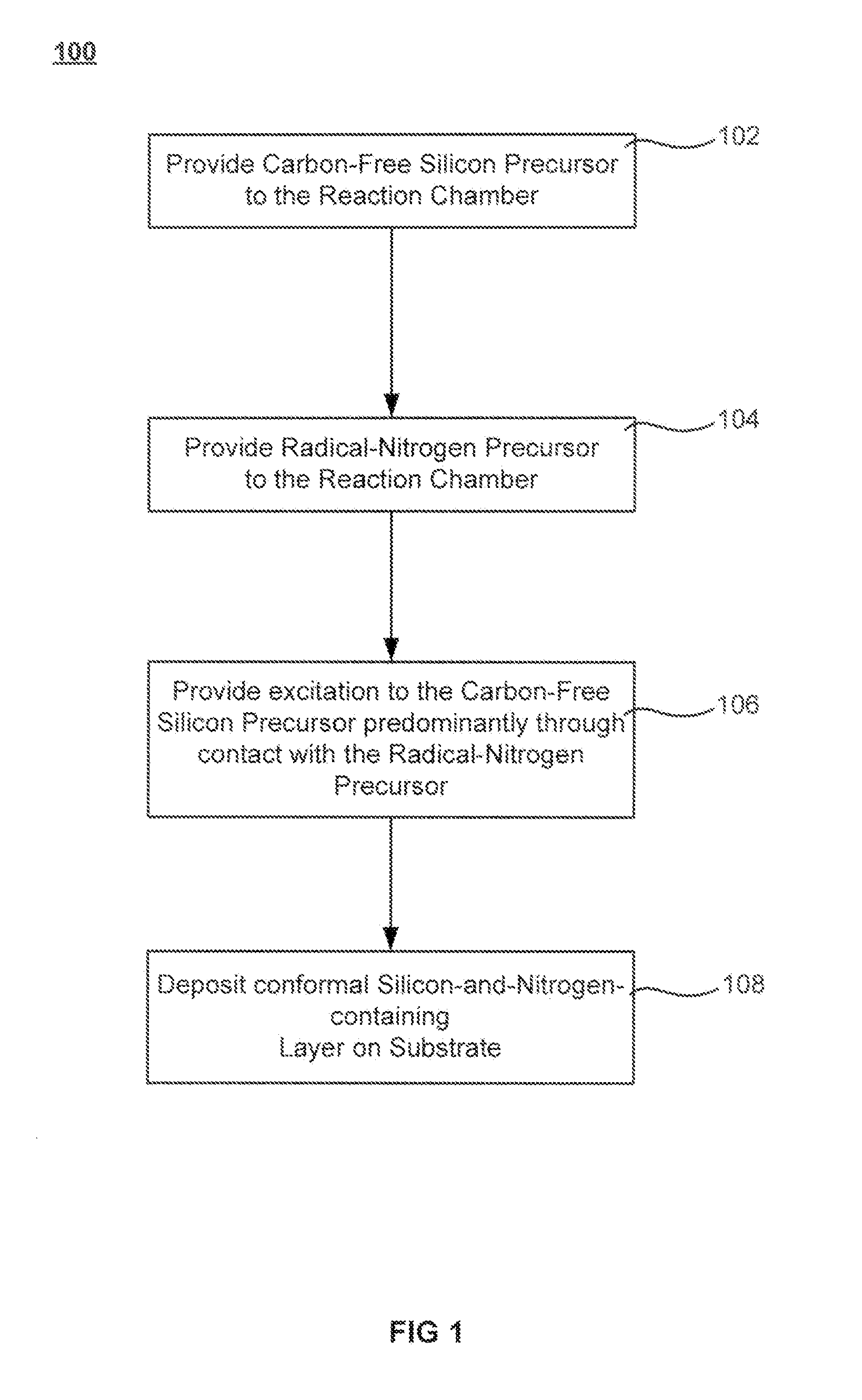

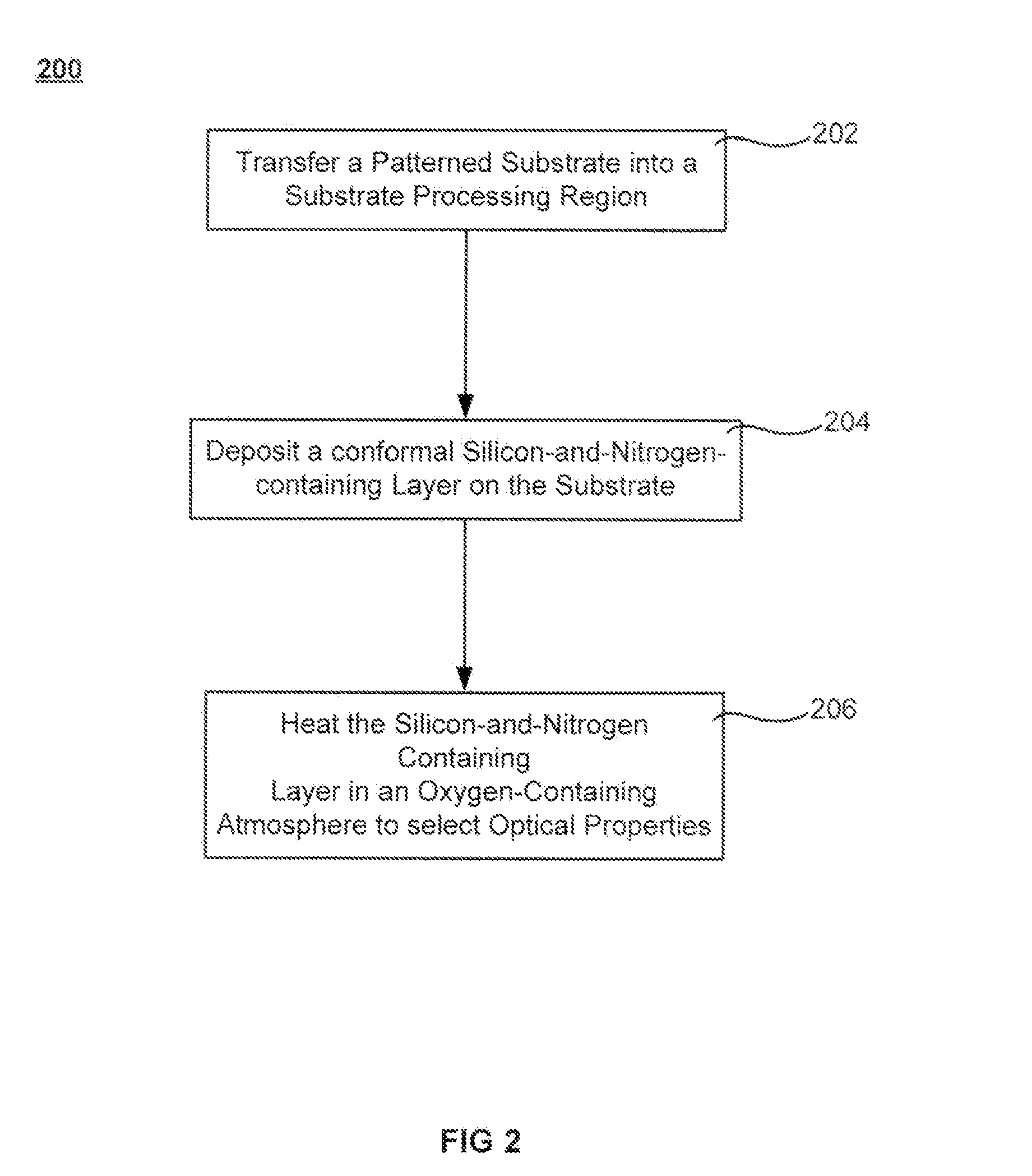

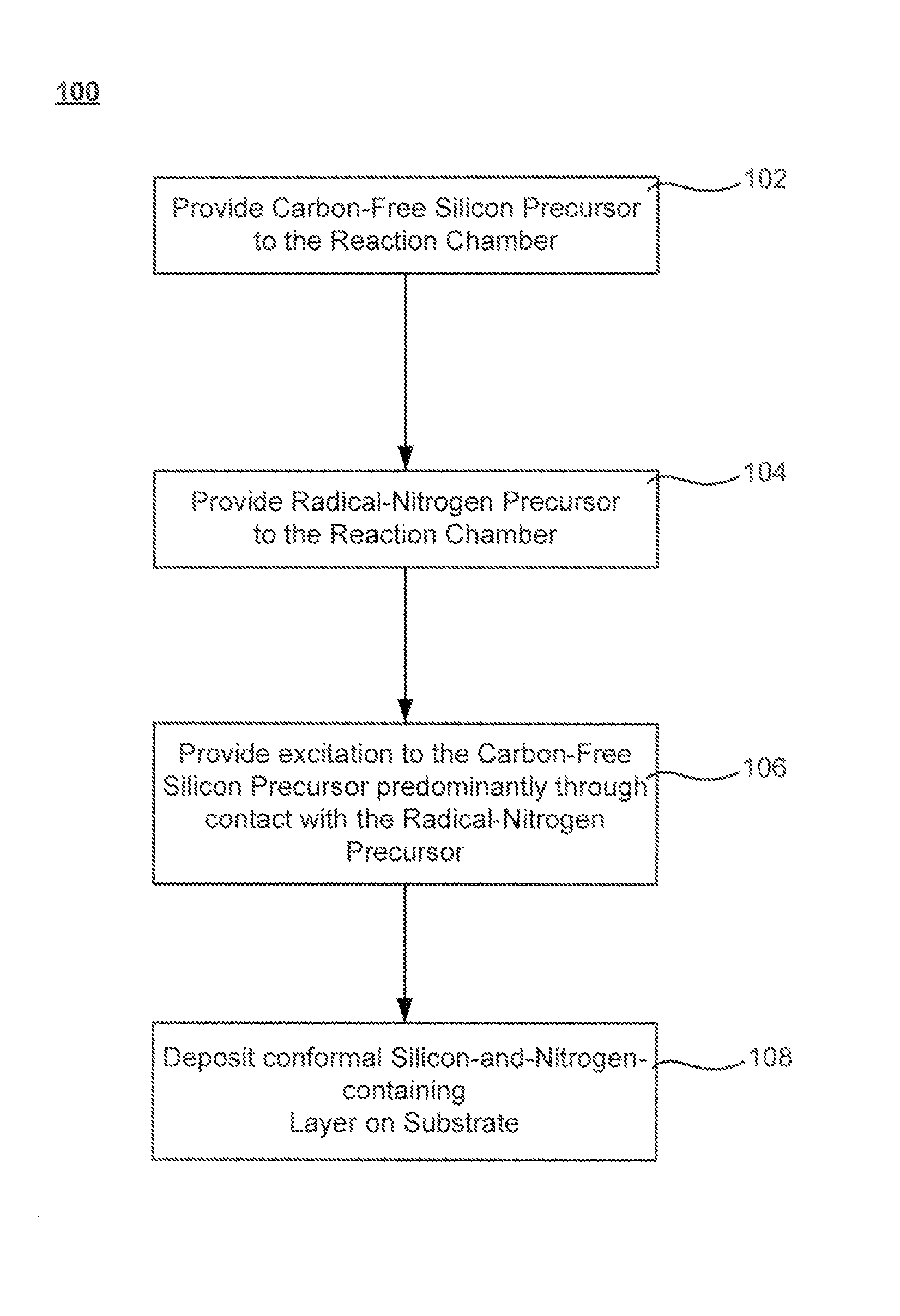

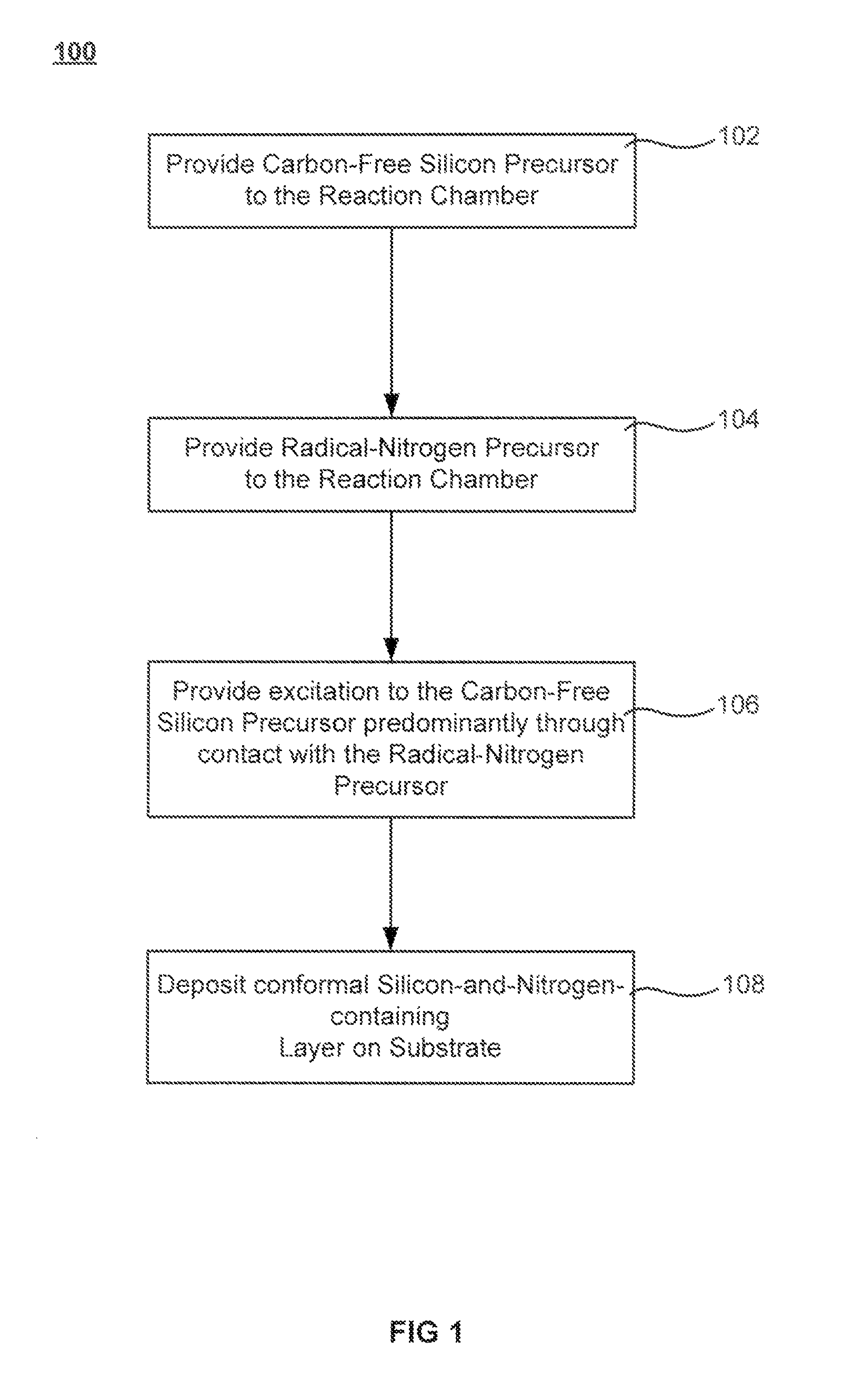

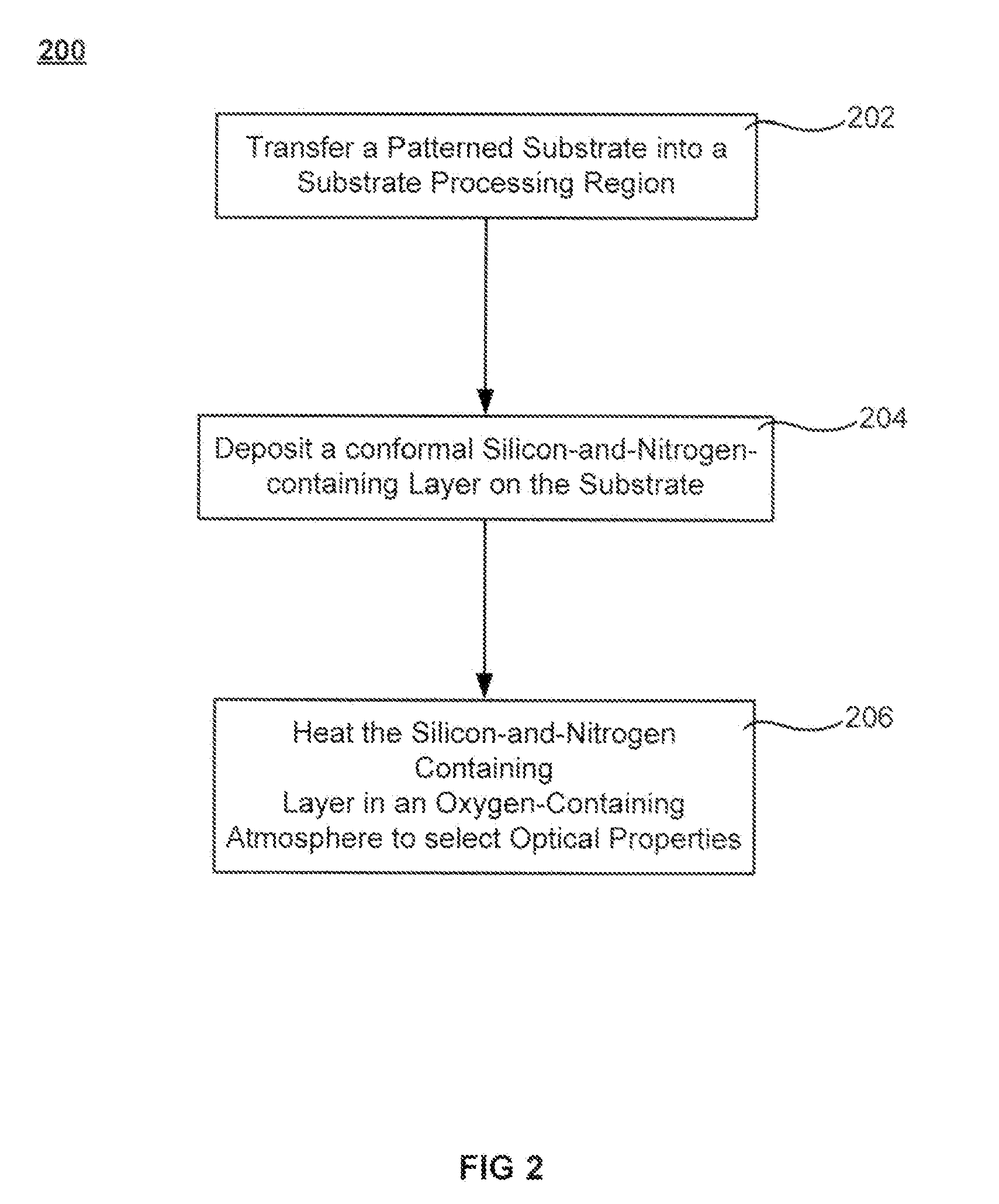

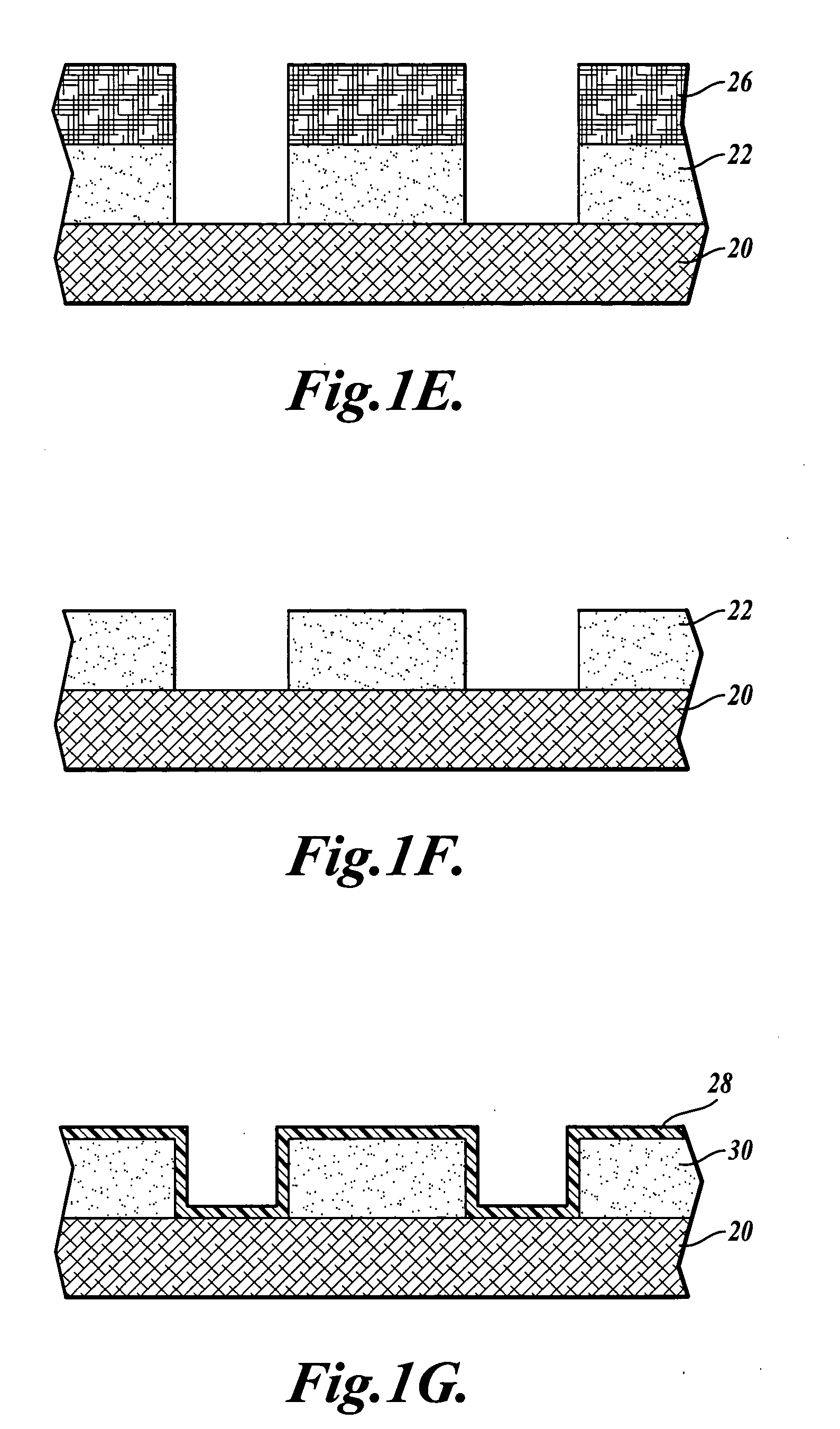

Conformal layers by radical-component CVD

ActiveUS20110217851A1Less volume shrinkageImprove wettabilitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingOptical propertyHydrogen

Methods, materials, and systems are described for forming conformal dielectric layers containing silicon and nitrogen (e.g., a silicon-nitrogen-hydrogen (Si—N—H) film) from a carbon-free silicon-and-nitrogen precursor and radical-nitrogen precursor. The carbon-free silicon-and-nitrogen precursor is predominantly excited by contact with the radical-nitrogen precursor. Because the silicon-and-nitrogen film is formed without carbon, the conversion of the film into hardened silicon oxide is done with less pore formation and less volume shrinkage. The deposited silicon-and-nitrogen-containing film may be wholly or partially converted to silicon oxide which allows the optical properties of the conformal dielectric layer to be selectable. The deposition of a thin silicon-and-nitrogen-containing film may be performed at low temperature to form a liner layer in a substrate trench. The low temperature liner layer has been found to improve the wetting properties and allows flowable films to more completely fill the trench.

Owner:APPLIED MATERIALS INC

Methods and devices for the preparation, storage and administration of calcium phosphate cements

InactiveUS6149655AStable reductionPromote resultsLiquid surface applicatorsShaking/oscillating/vibrating mixersCalcium biphosphatePhosphoric acid

A system is provided for the storage, preparation and administration of calcium phosphate cements. The subject invention provides a storage means for storing a two component calcium phosphate cement having a liquid component and a dry component. Also provided is a preparation means for combining the two components of the cement while present in the storage means. The subject invention further provides a means for administering the prepared cement to a physiological site. The subject devices and methods find use in a variety of applications where the introduction of a flowable material capable of setting to a solid calcium phosphate mineral to a physiological site is desired, including dental and orthopedic applications.

Owner:NORIAN CORP

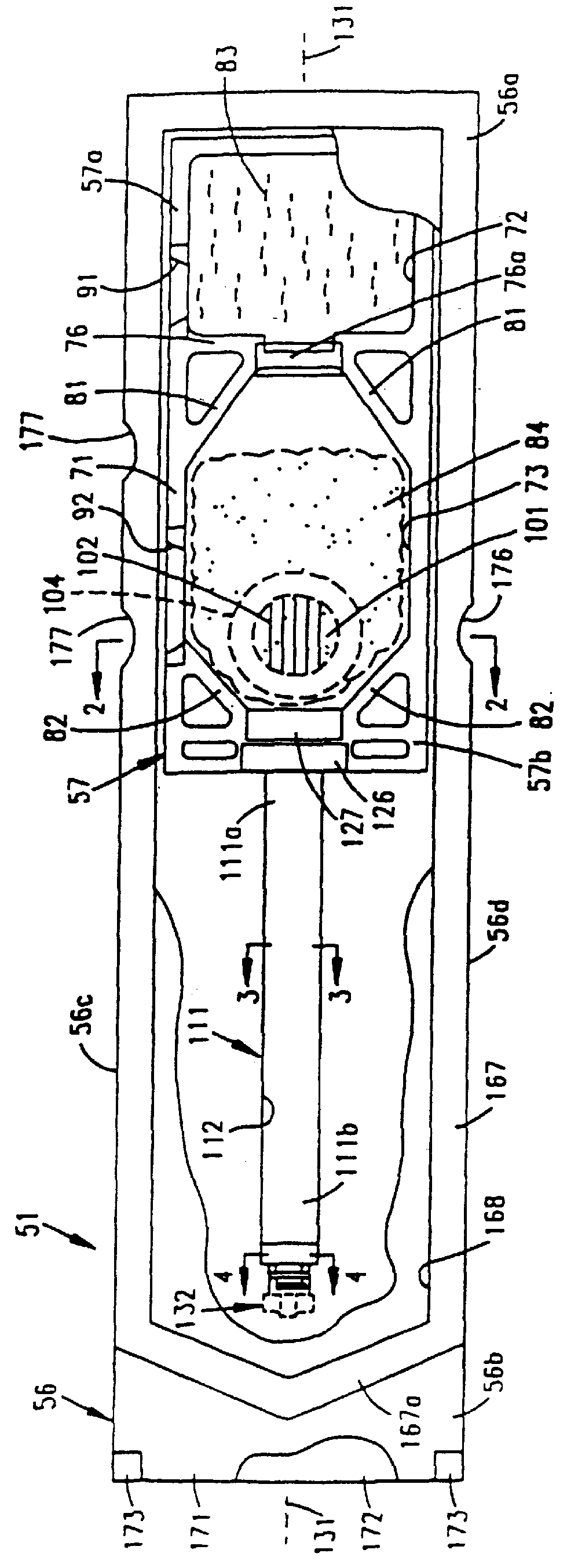

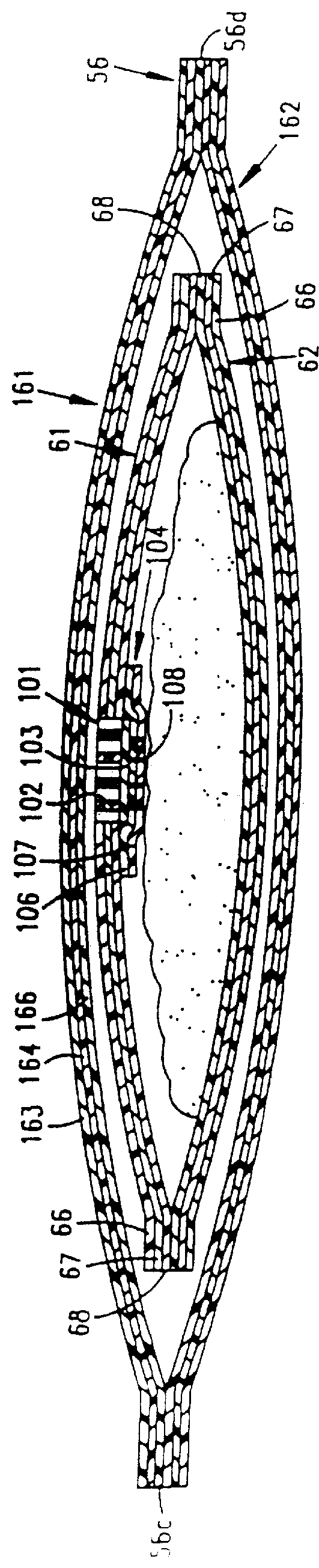

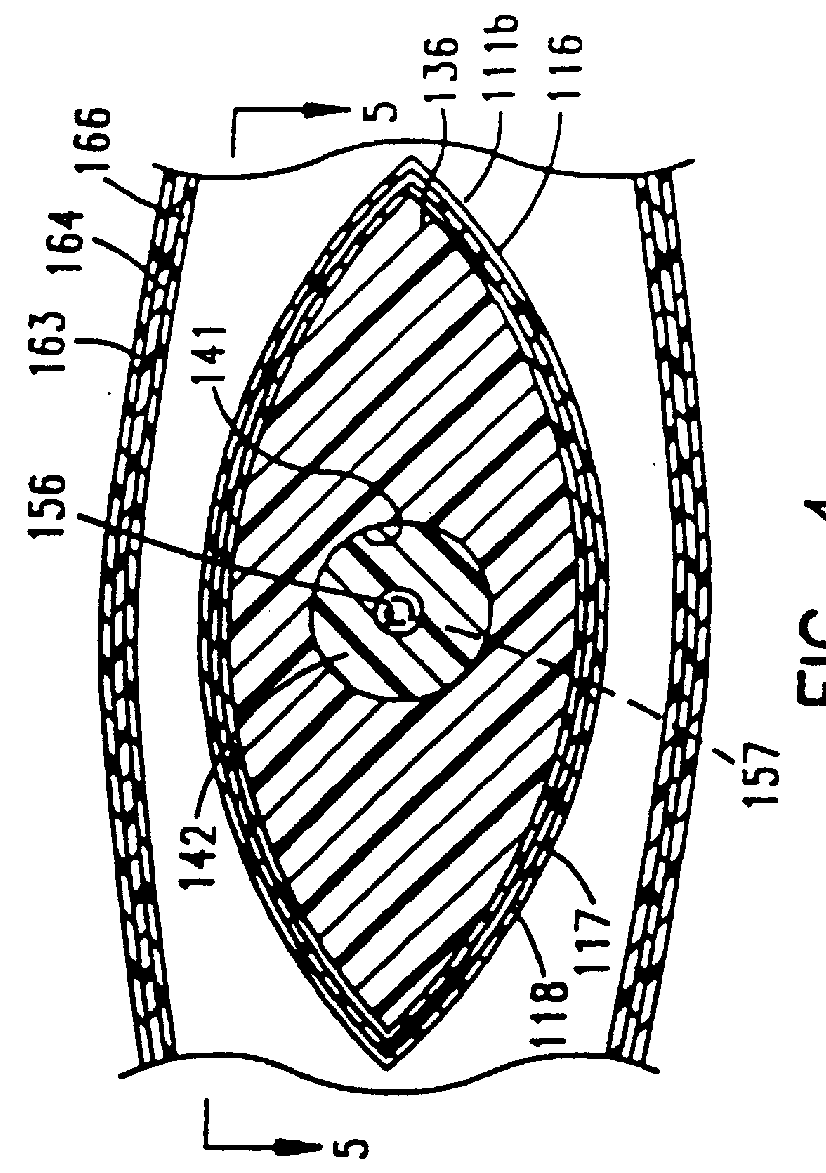

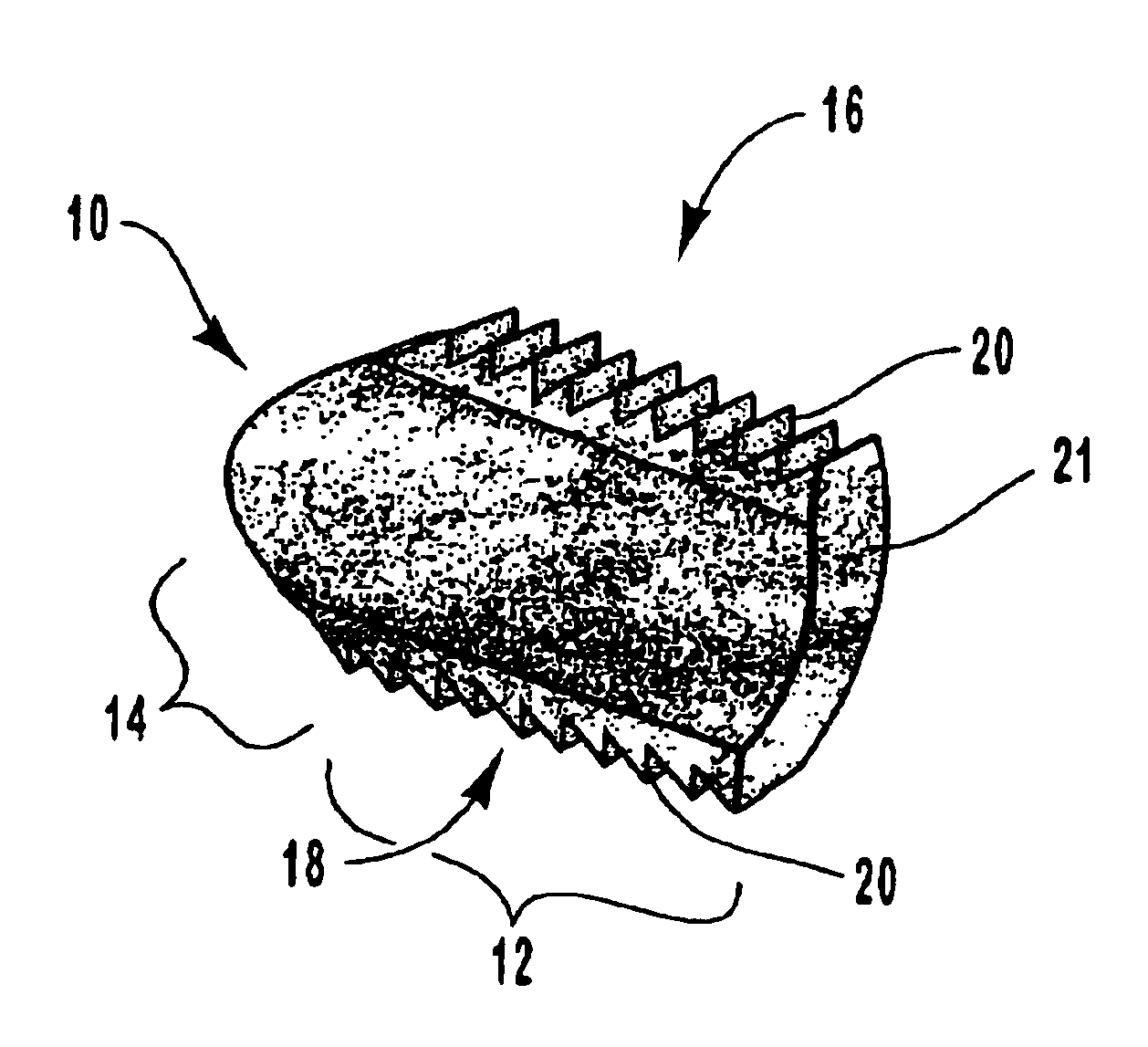

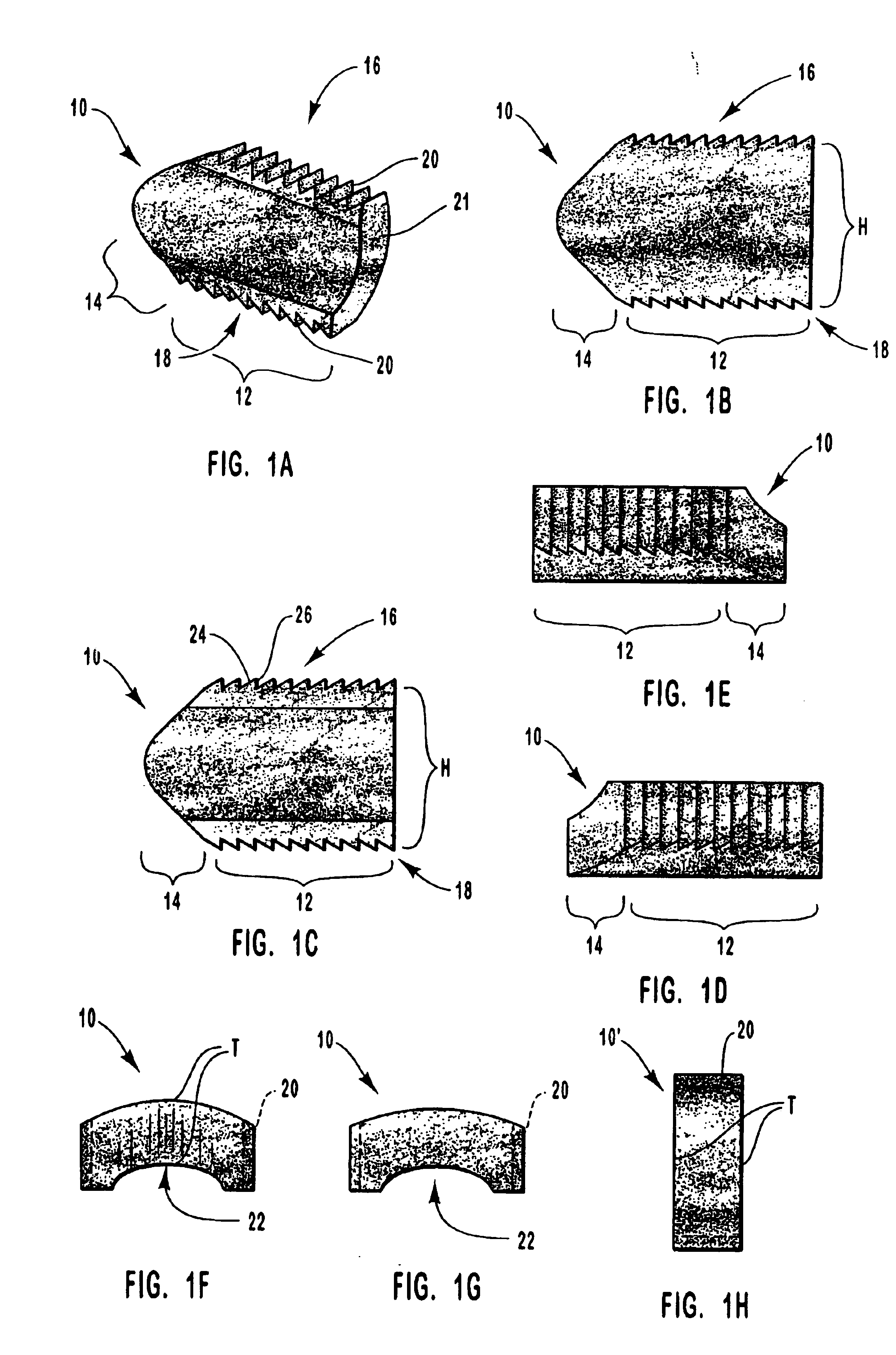

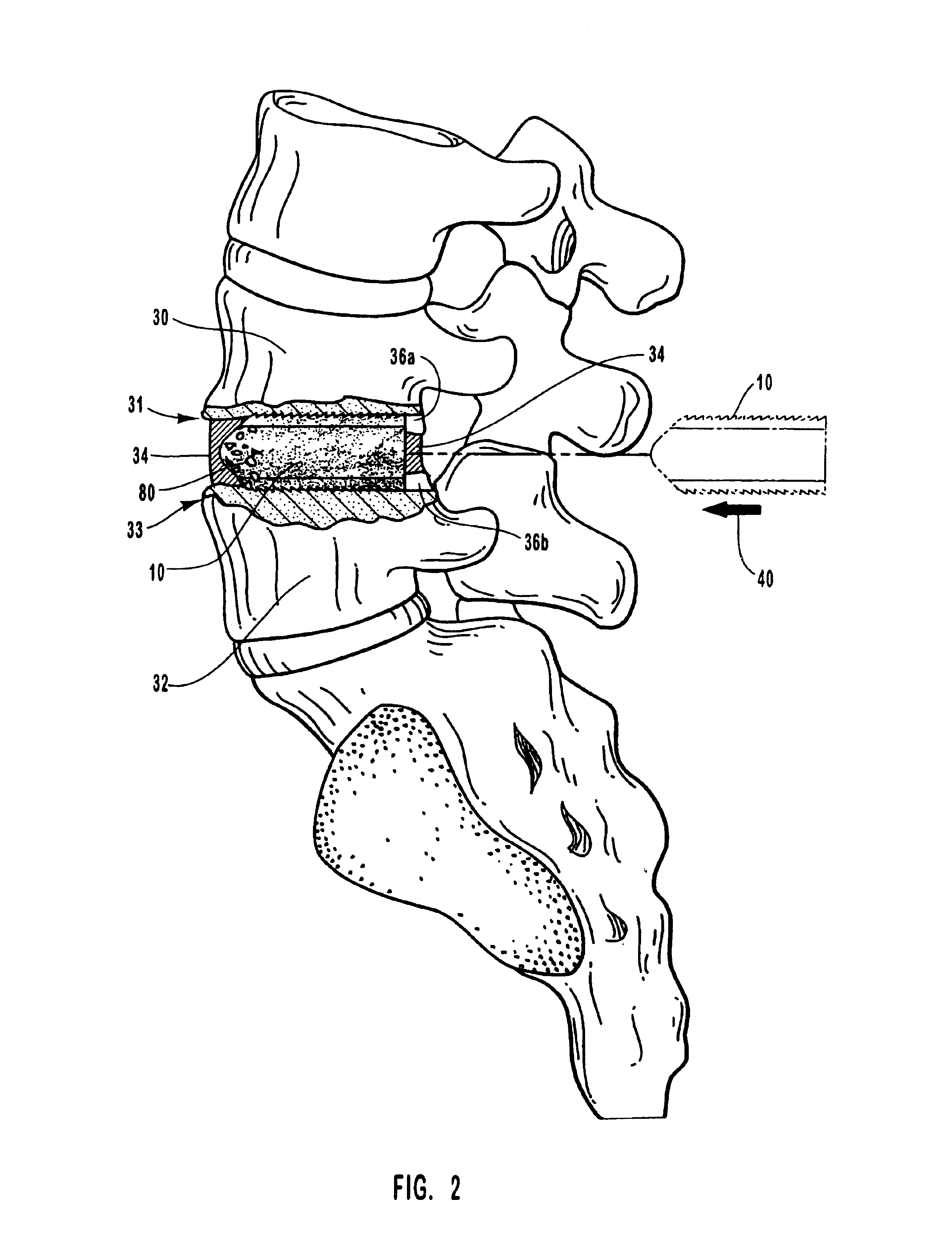

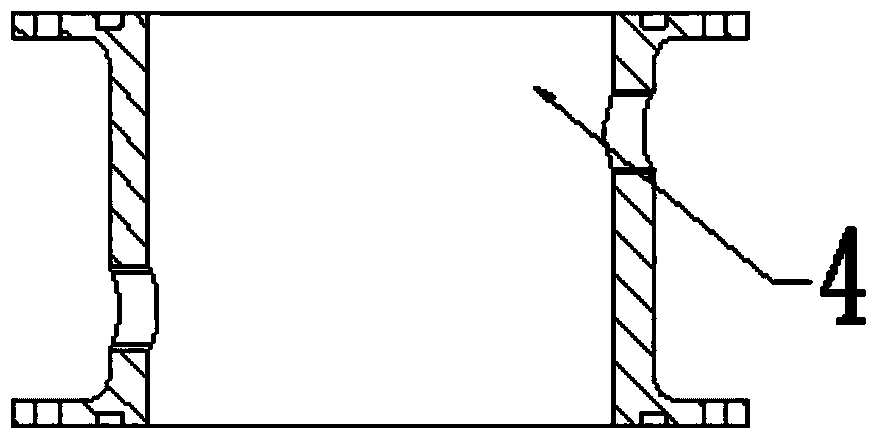

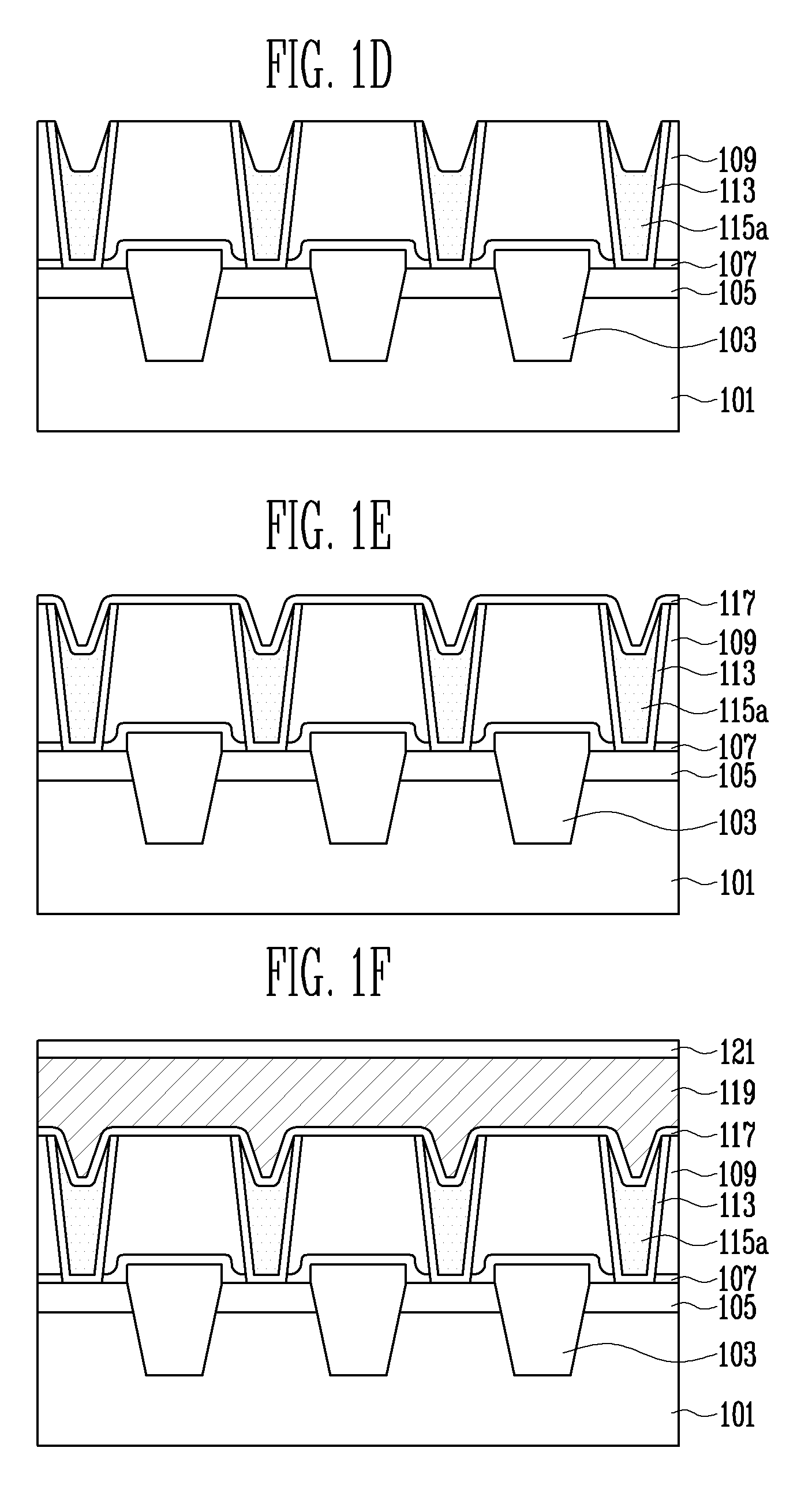

Spinal vertebral implant and methods of insertion

InactiveUS6843804B2Promote bone growthPrevent implantationInternal osteosythesisBone implantNoseIntervertebral space

A spinal vertebral implant includes a substantially rectangular shaped base section made from a solid piece of bone. A nose section extends integrally from the substantially rectangularly shaped base section and preferably has a generally tapering shape to foster entry between adjacent vertebrae. The nose section tapers distally and inwardly from the base section to form a generally pointed or rounded distal tip portion and comprises a solid piece of bone. Serrated sides assist the implant in gripping adjacent upper and lower vertebrae and in being maintained therebetween. The serrated sides are angled in a manner that encourages the implant to be placed between the vertebrae and locked therebetween upon such placement. First and second implants may be placed into respective left and right sides of an intervertebral space. A method for placing one or more implants between the adjacent vertebrae comprises forming a slot configured to receive an implant and inserting the implant into the slot. Each slot is preferably formed from an upper slot portion and a lower slot portion in the posterior portion of adjacent upper and lower vertebrae, respectively. Instruments for performing the method include osteotomes, impactors, and spacers.

Owner:BRYAN DONALD W

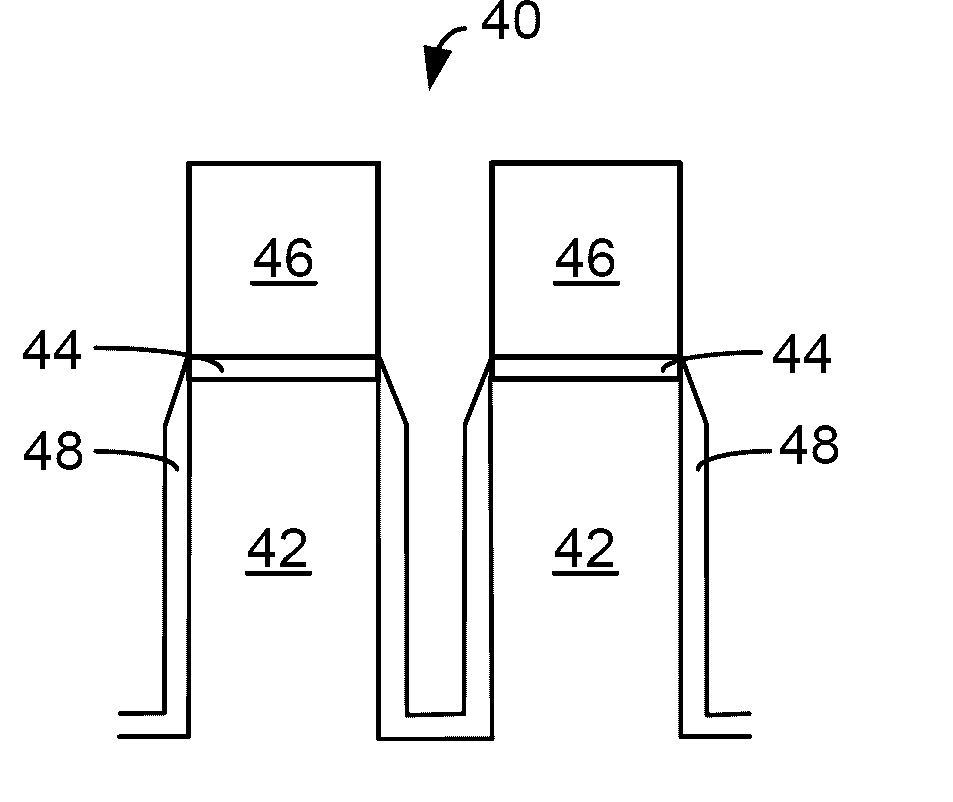

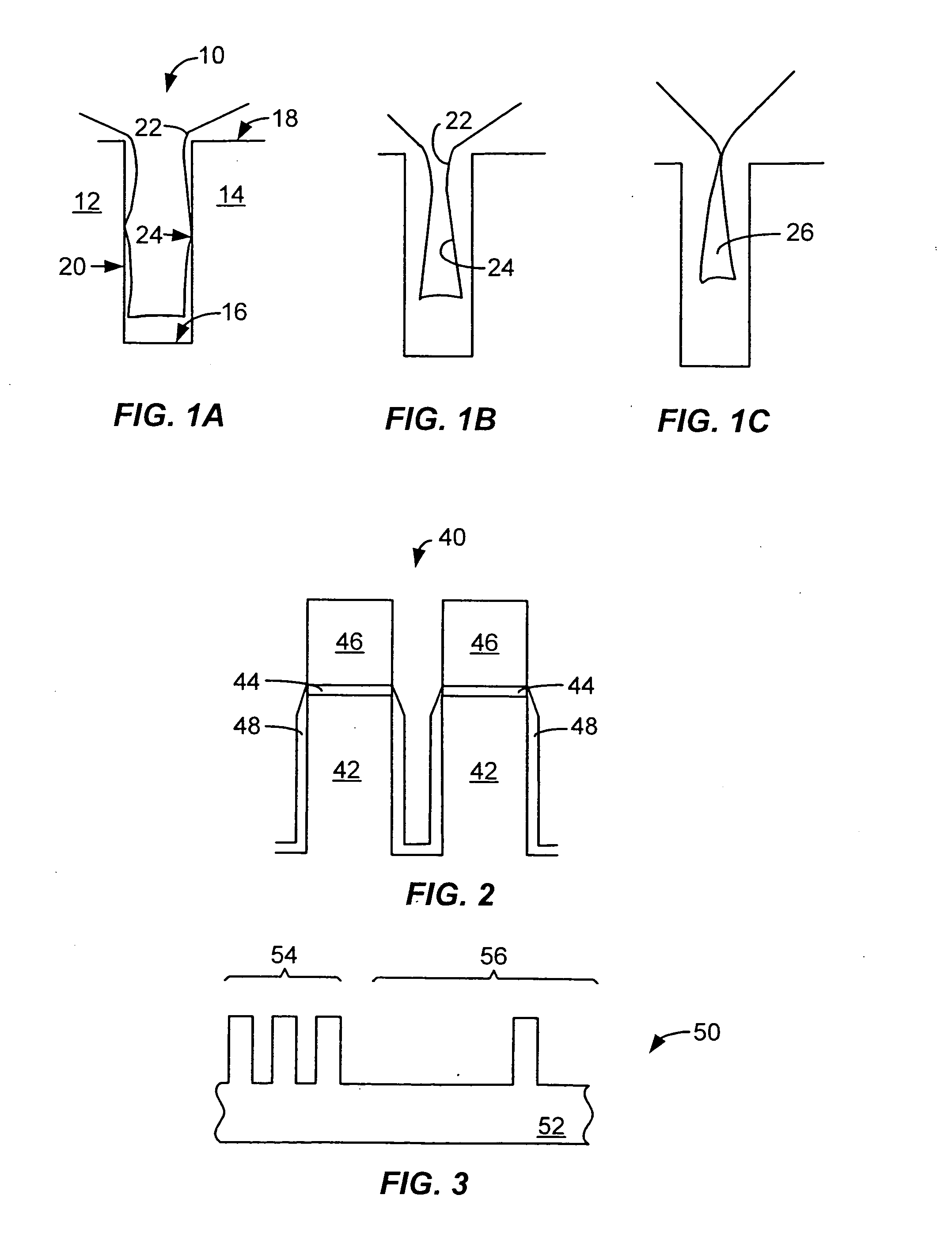

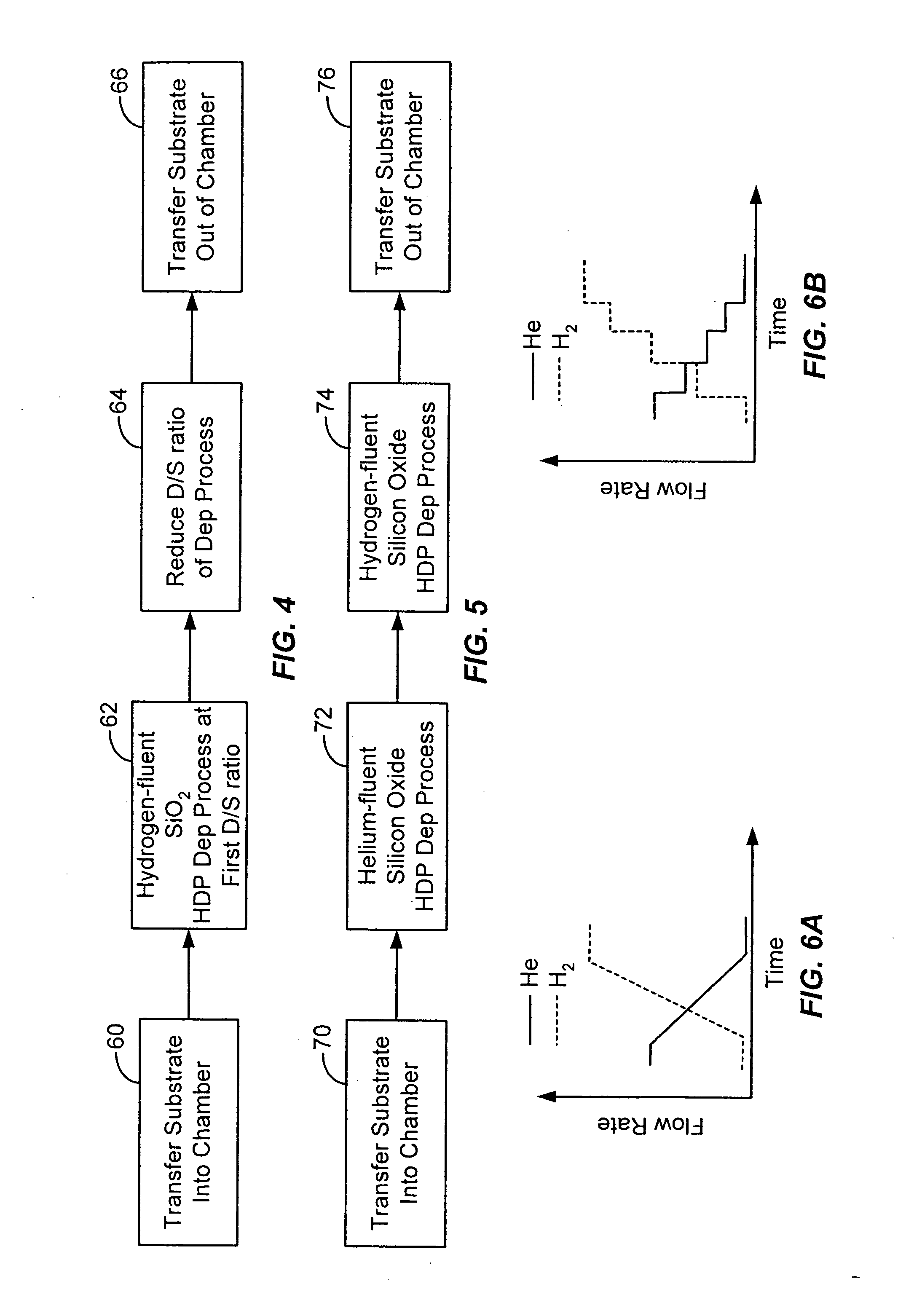

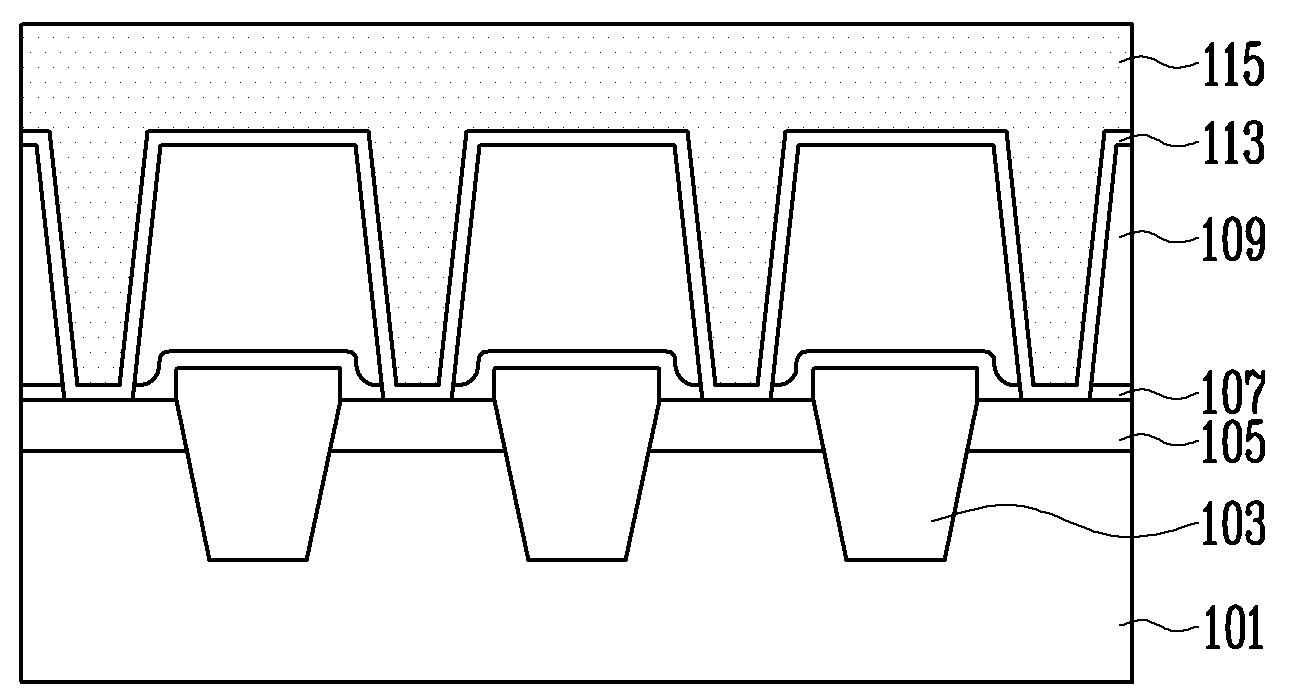

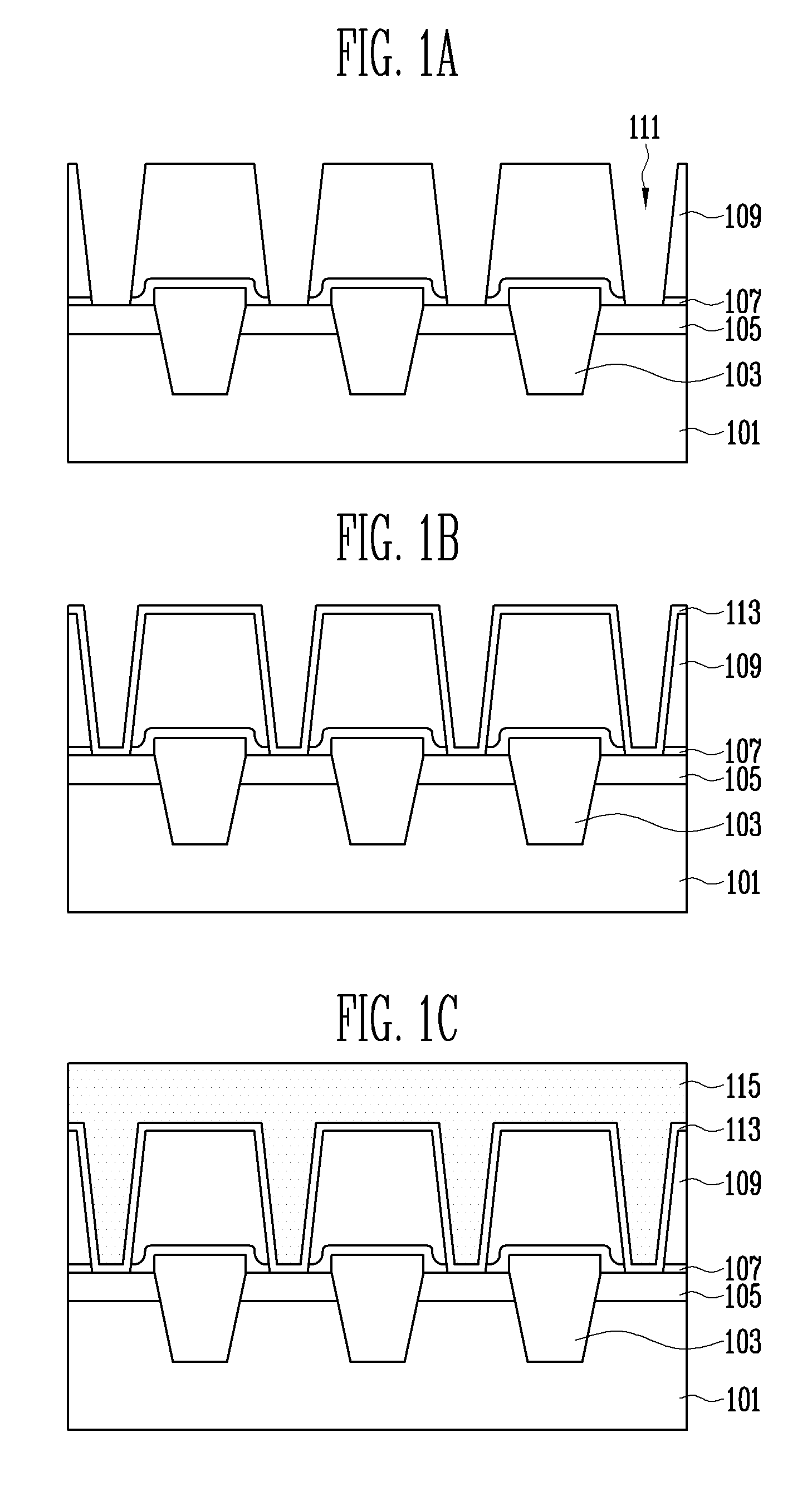

Hydrogen assisted hdp-cvd deposition process for aggressive gap-fill technology

InactiveUS20040146661A1Excellent gap fillingStrong Gap Filling CapabilityElectric discharge tubesVacuum evaporation coatingHigh densityHydrogen

Abstract of the Disclosure A method of depositing a silicon oxide layer over a substrate having a trench formed between adjacent raised surfaces. In one embodiment the silicon oxide layer is formed in a multistep process that includes depositing a first portion of layer over the substrate and within the trench by forming a high density plasma process that has simultaneous deposition and sputtering components from a first process gas comprising a silicon source, an oxygen source and helium and / or molecular hydrogen with high D / S ratio, for example, 10-20 and, thereafter, depositing a second portion of the silicon oxide layer over the substrate and within the trench by forming a high density plasma process that has simultaneous deposition and sputtering components from a second process gas comprising a silicon source, an oxygen source and molecular hydrogen with a lower D / S ratio of, for example, 3-10.

Owner:APPLIED MATERIALS INC

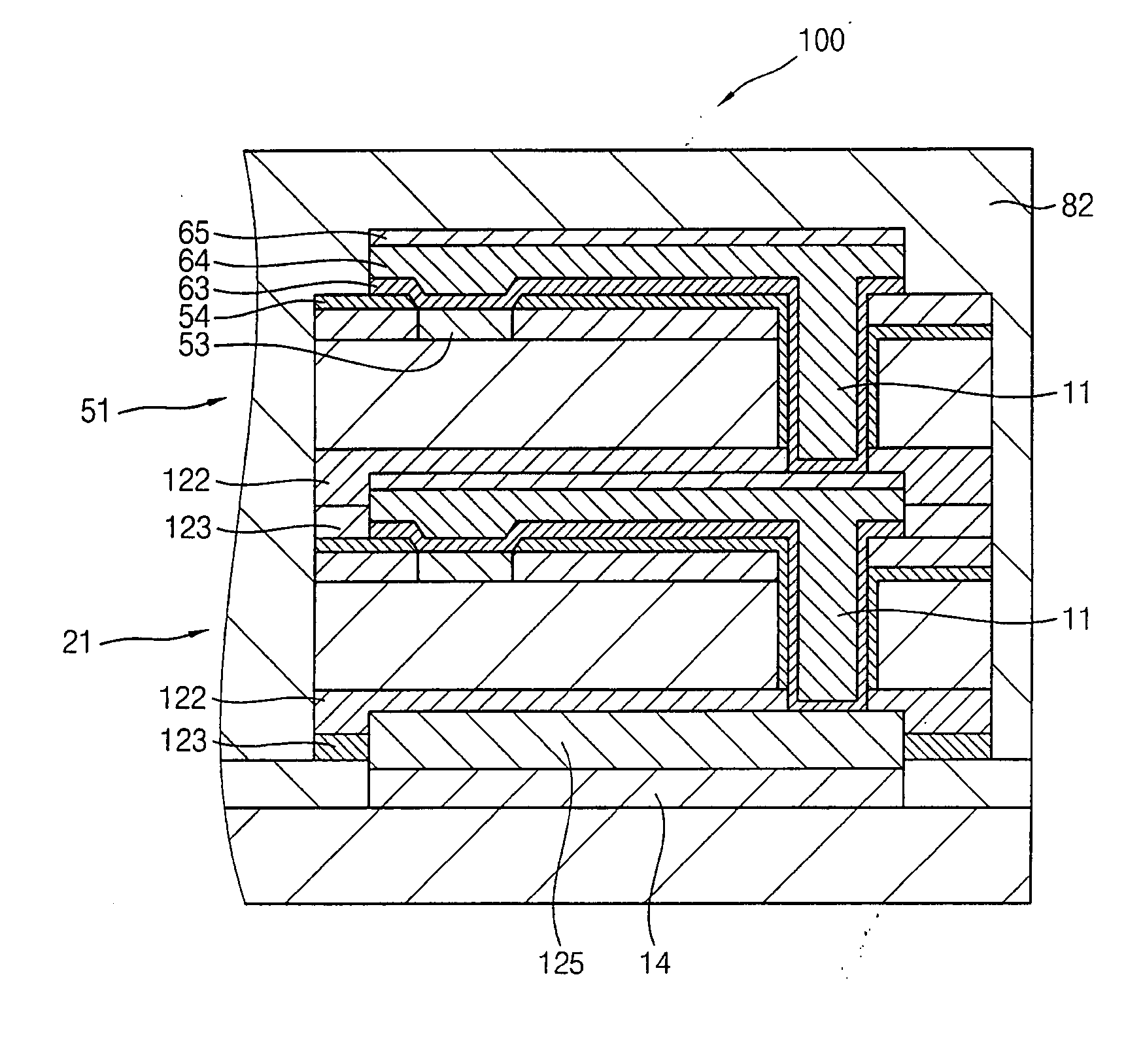

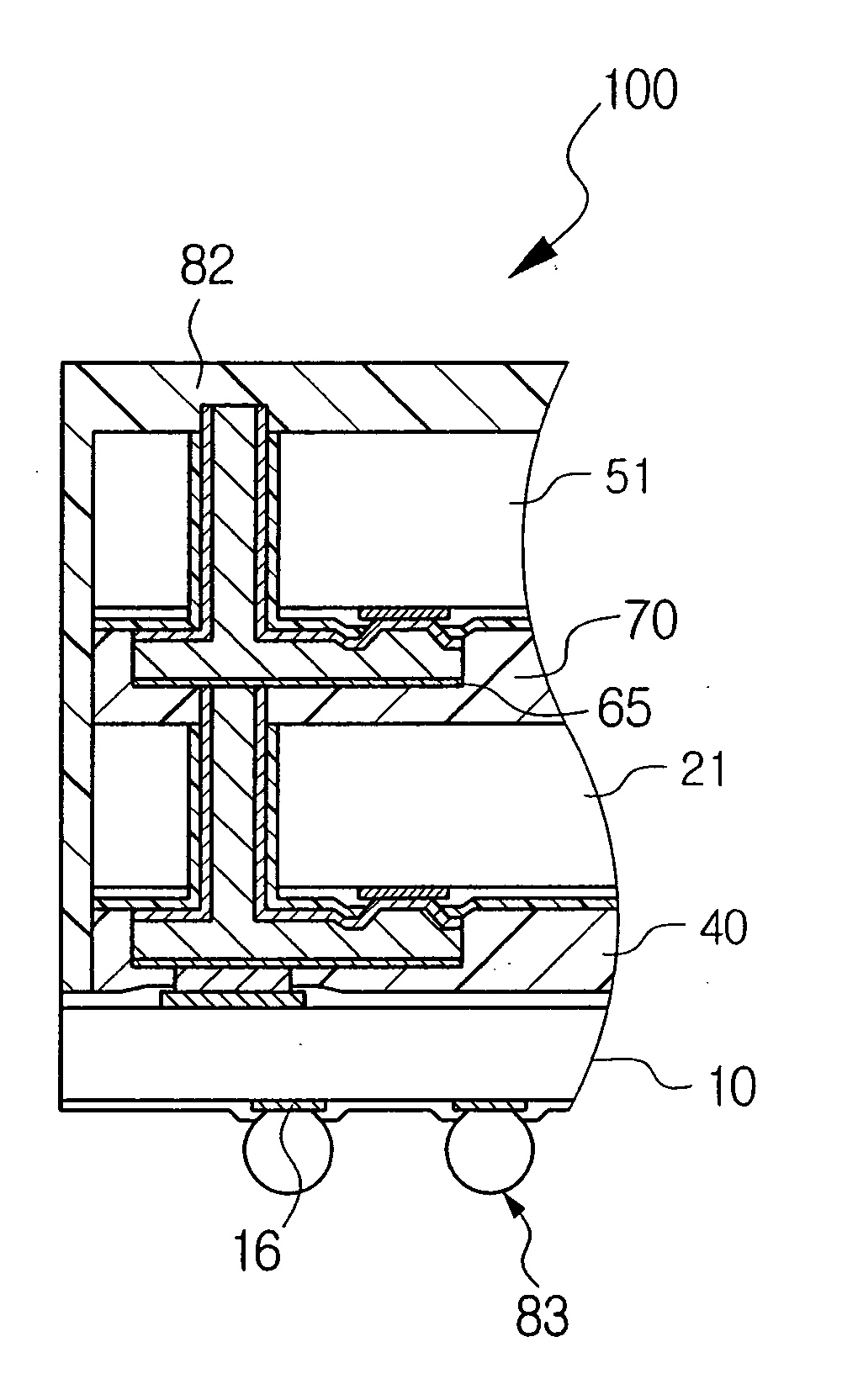

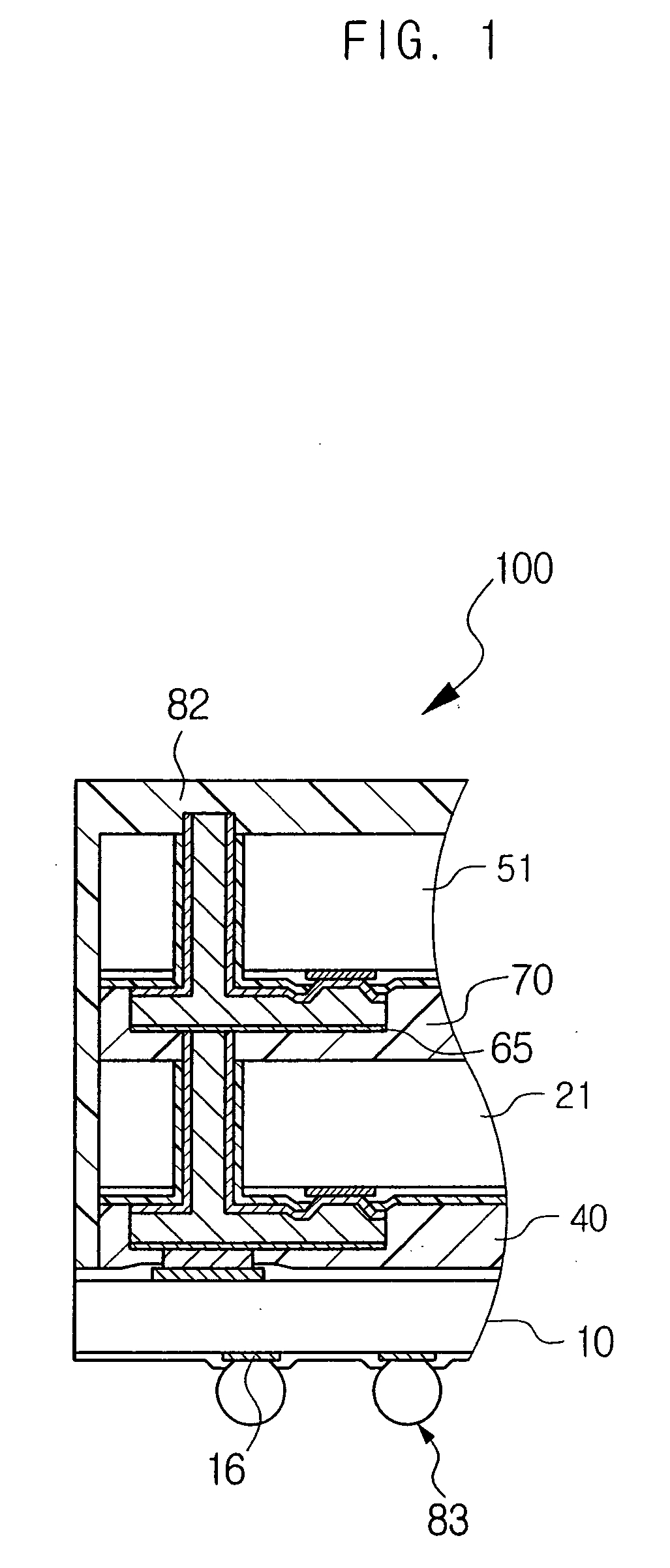

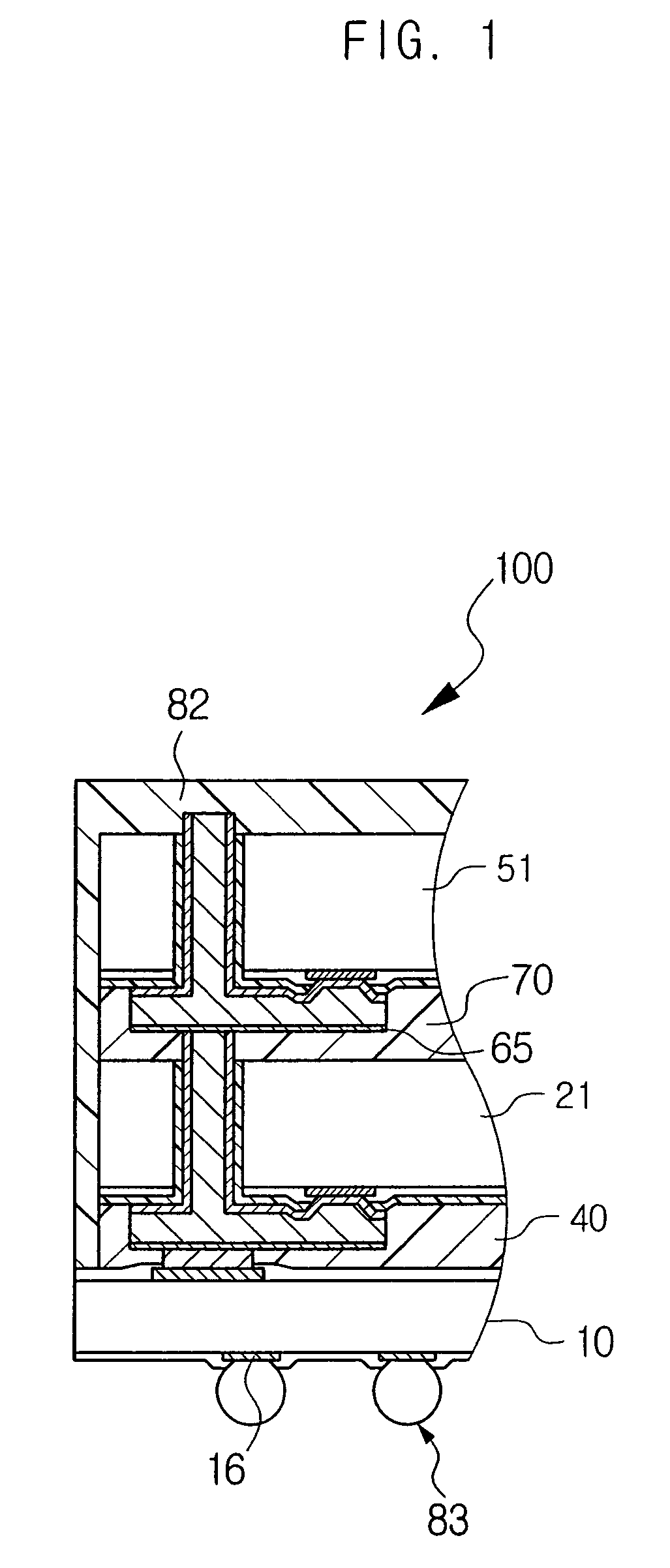

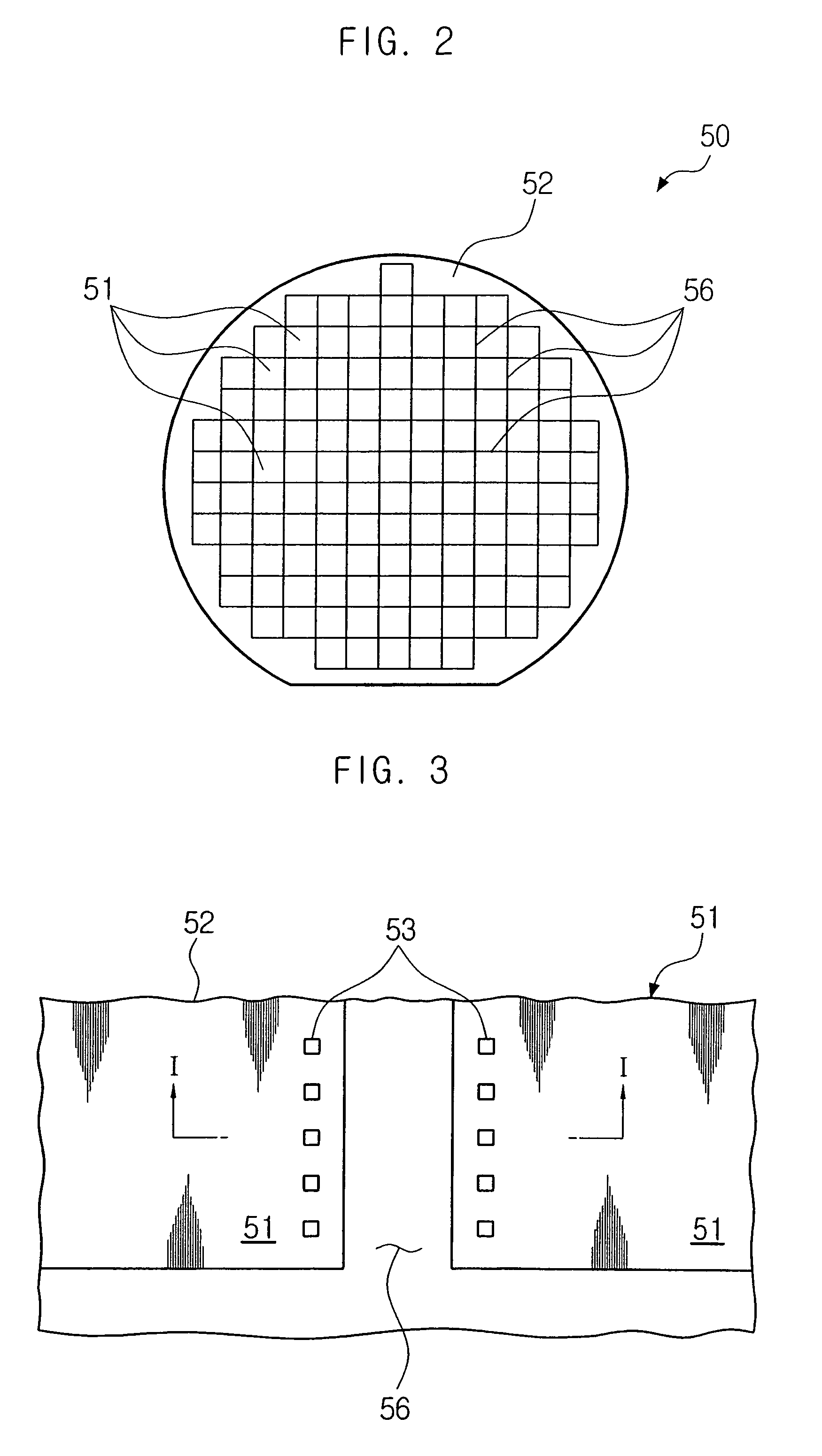

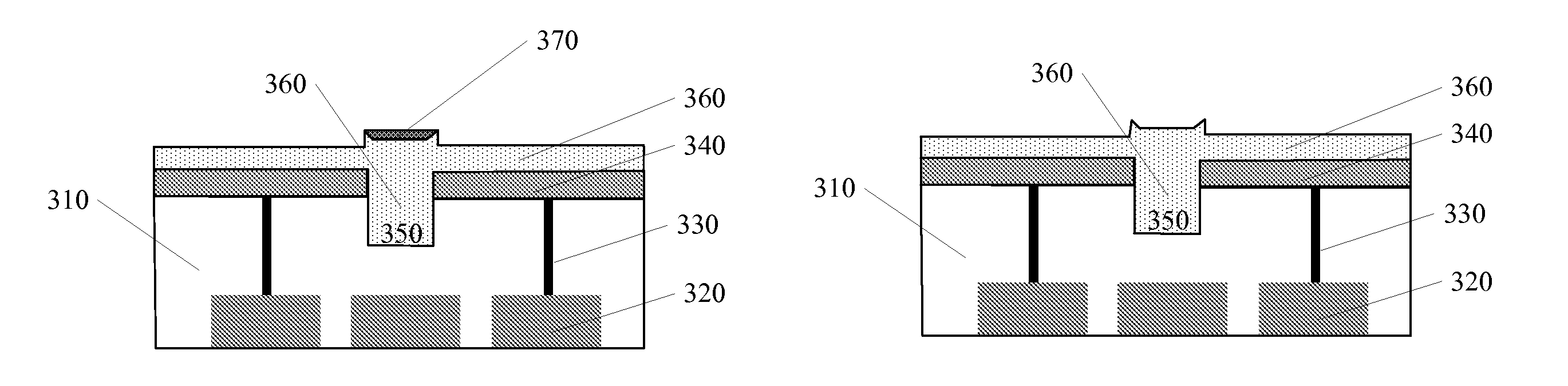

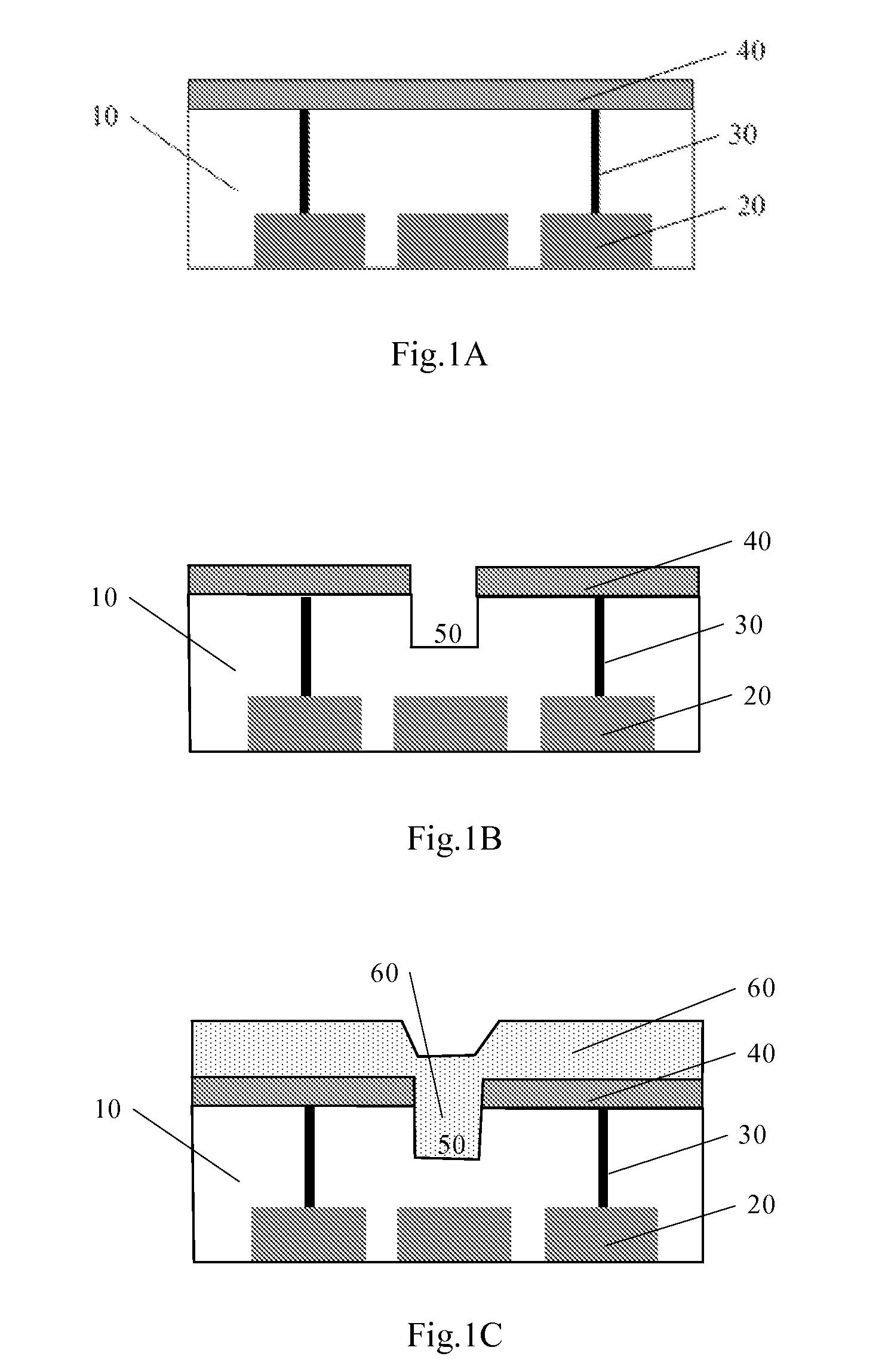

Stacked chip package using warp preventing insulative material and manufacturing method thereof

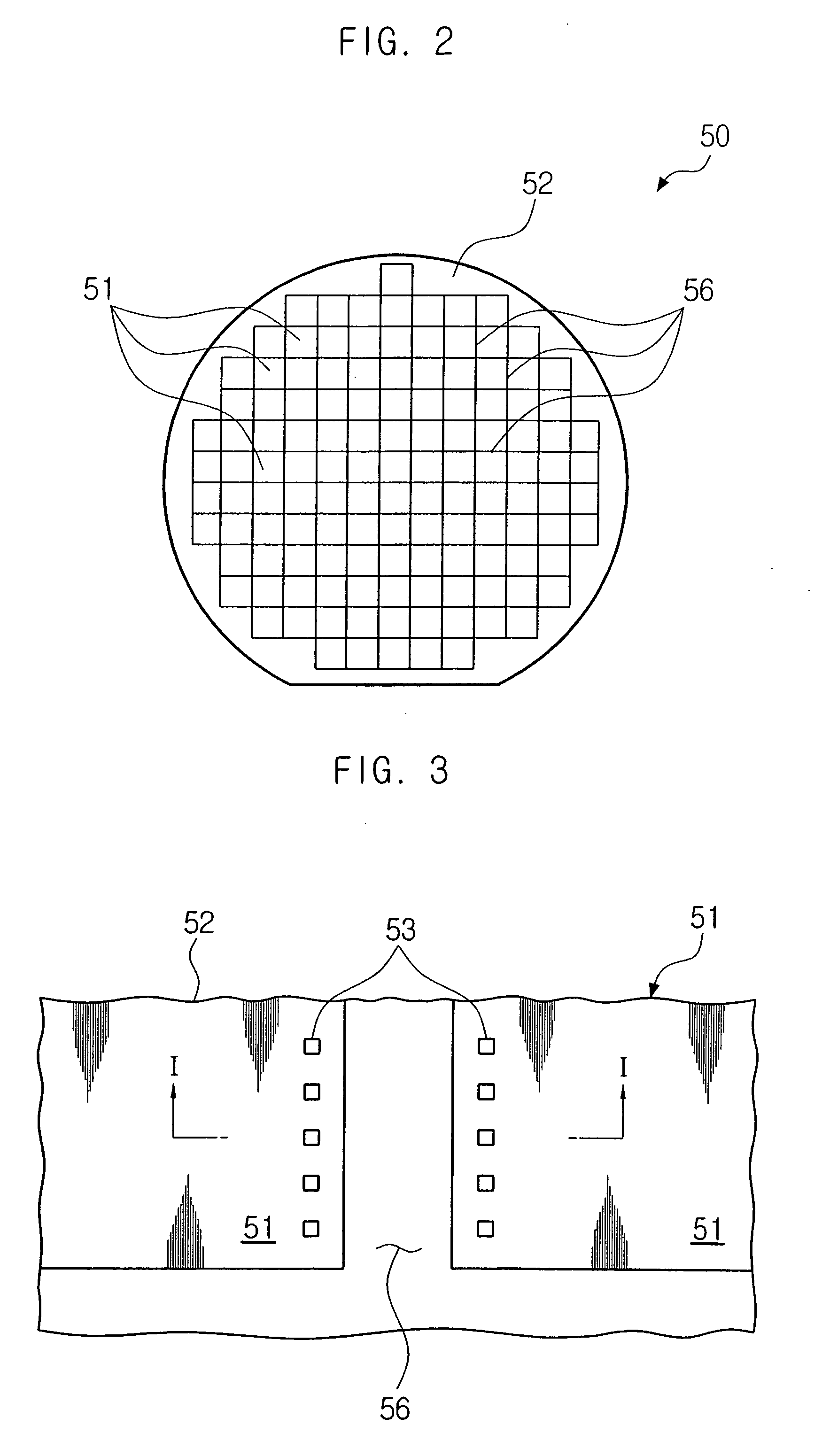

InactiveUS20070045836A1AdhesionHigh mechanical reliabilitySemiconductor/solid-state device detailsSolid-state devicesMechanical reliabilityPhotosensitive polymer

In a stacked chip configuration, and manufacturing methods thereof, the gap between a lower chip and an upper chip is filled completely using a relatively simple process that eliminates voids between the lower and upper chips and the cracking and delamination problems associated with voids. The present invention is applicable to both chip-level bonding and wafer-level bonding approaches. A photosensitive polymer layer is applied to a first chip, or wafer, prior to stacking the chips or stacking the wafers. The photosensitive polymer layer is partially cured, so that the photosensitive polymer layer is made to be structurally stable, while retaining its adhesive properties. The second chip, or wafer, is stacked, aligned, and bonded to the first chip, or wafer, and the photosensitive polymer layer is then cured to fully bond the first and second chips, or wafers. In this manner, adhesion between chips / wafers is greatly improved, while providing complete fill of the gap. In addition, mechanical reliability is improved and CTE mismatch is reduced, alleviating the problems associated with warping, cracking and delamination, and leading to an improvement in device yield and device reliability.

Owner:SAMSUNG ELECTRONICS CO LTD

Stacked chip package using photosensitive polymer and manufacturing method thereof

ActiveUS20070048969A1Reduce decreaseImprove device reliabilitySemiconductor/solid-state device detailsSolid-state devicesMechanical reliabilityPhotosensitive polymer

In a stacked chip configuration, and manufacturing methods thereof, the gap between a lower and an upper chip is filled completely using a relatively simple process that eliminates voids between the lower and upper chips and the cracking and delamination problems associated with such voids. The present invention is applicable to both chip-level bonding and wafer-level bonding approaches. A photosensitive polymer layer is applied to a first chip, or wafer, prior to stacking the chips or stacking the wafers. The photosensitive polymer layer is partially cured, so that the photosensitive polymer layer is made to be structurally stable, while retaining its adhesive properties. The second chip, or wafer, is stacked, aligned, and bonded to the first chip, or wafer, and the photosensitive polymer layer is then cured to fully bond the first and second chips, or wafers. In this manner, adhesion between chips / wafers is greatly improved, while providing complete gap fill. In addition, mechanical reliability is improved, alleviating the problems associated with cracking and delamination, and leading to an improvement in device yield and device reliability.

Owner:SAMSUNG ELECTRONICS CO LTD

Conformal thermal interface material for electronic components

InactiveUS20030207064A1Readily apparentIncrease interface areaLamination ancillary operationsSemiconductor/solid-state device detailsRoom temperatureConductive materials

A thermally-conductive interface for conductively cooling a heat-generating electronic component having an associated thermal dissipation member such as a heat sink. The interface is formed as a self-supporting layer of a thermally-conductive material which is form-stable at normal room temperature in a first phase and substantially conformable in a second phase to the interface surfaces of the electronic component and thermal dissipation member. The material has a transition temperature from the first phase to the second phase which is within the operating temperature range of the electronic component.

Owner:BUNYAN MICHAEL H +1

Conformal layers by radical-component CVD

ActiveUS8563445B2Less pore formationSmall volume shrinkageSemiconductor/solid-state device manufacturingChemical vapor deposition coatingHydrogenOptical property

Methods, materials, and systems are described for forming conformal dielectric layers containing silicon and nitrogen (e.g., a silicon-nitrogen-hydrogen (Si—N—H) film) from a carbon-free silicon-and-nitrogen precursor and radical-nitrogen precursor. The carbon-free silicon-and-nitrogen precursor is predominantly excited by contact with the radical-nitrogen precursor. Because the silicon-and-nitrogen film is formed without carbon, the conversion of the film into hardened silicon oxide is done with less pore formation and less volume shrinkage. The deposited silicon-and-nitrogen-containing film may be wholly or partially converted to silicon oxide which allows the optical properties of the conformal dielectric layer to be selectable. The deposition of a thin silicon-and-nitrogen-containing film may be performed at low temperature to form a liner layer in a substrate trench. The low temperature liner layer has been found to improve the wetting properties and allows flowable films to more completely fill the trench.

Owner:APPLIED MATERIALS INC

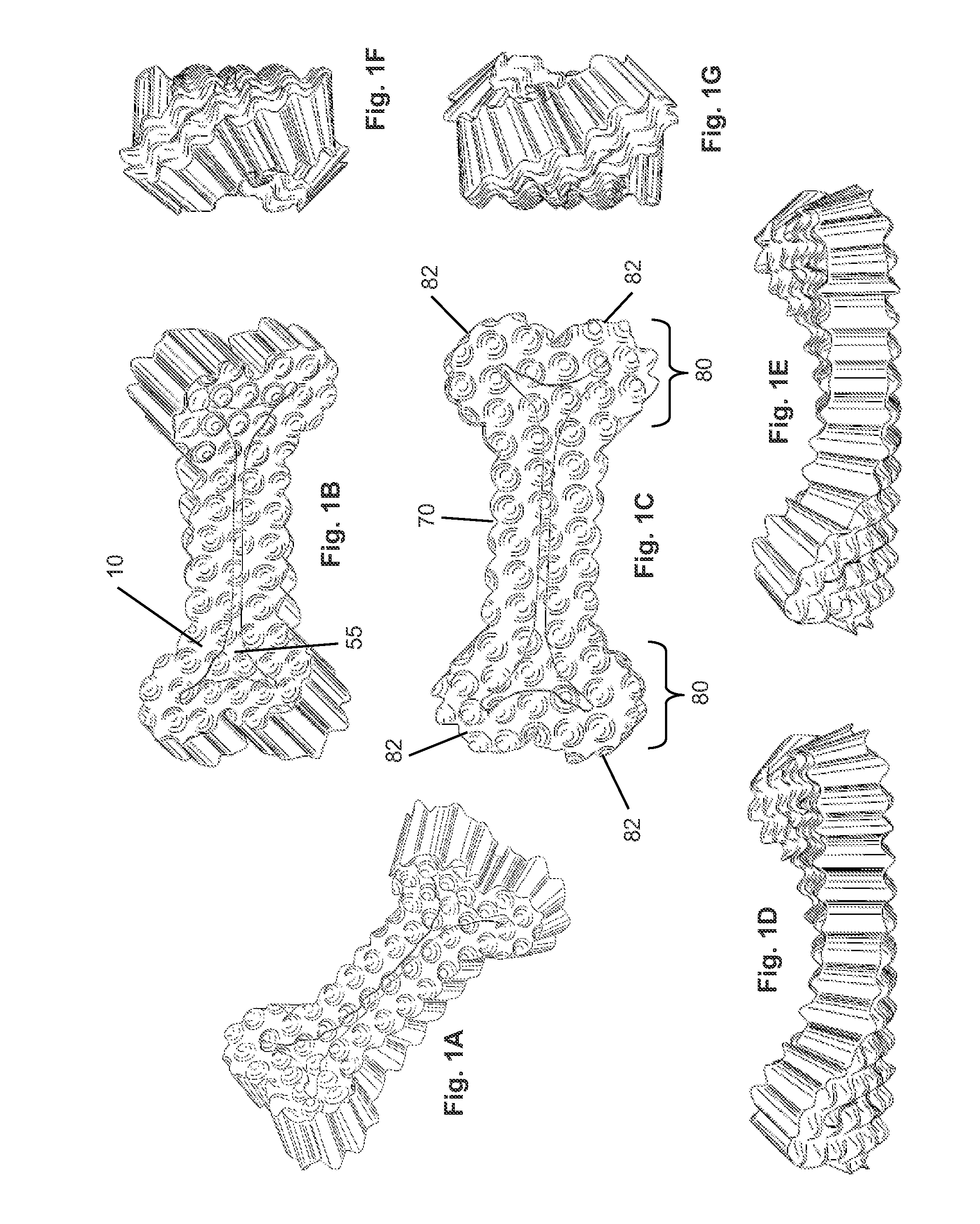

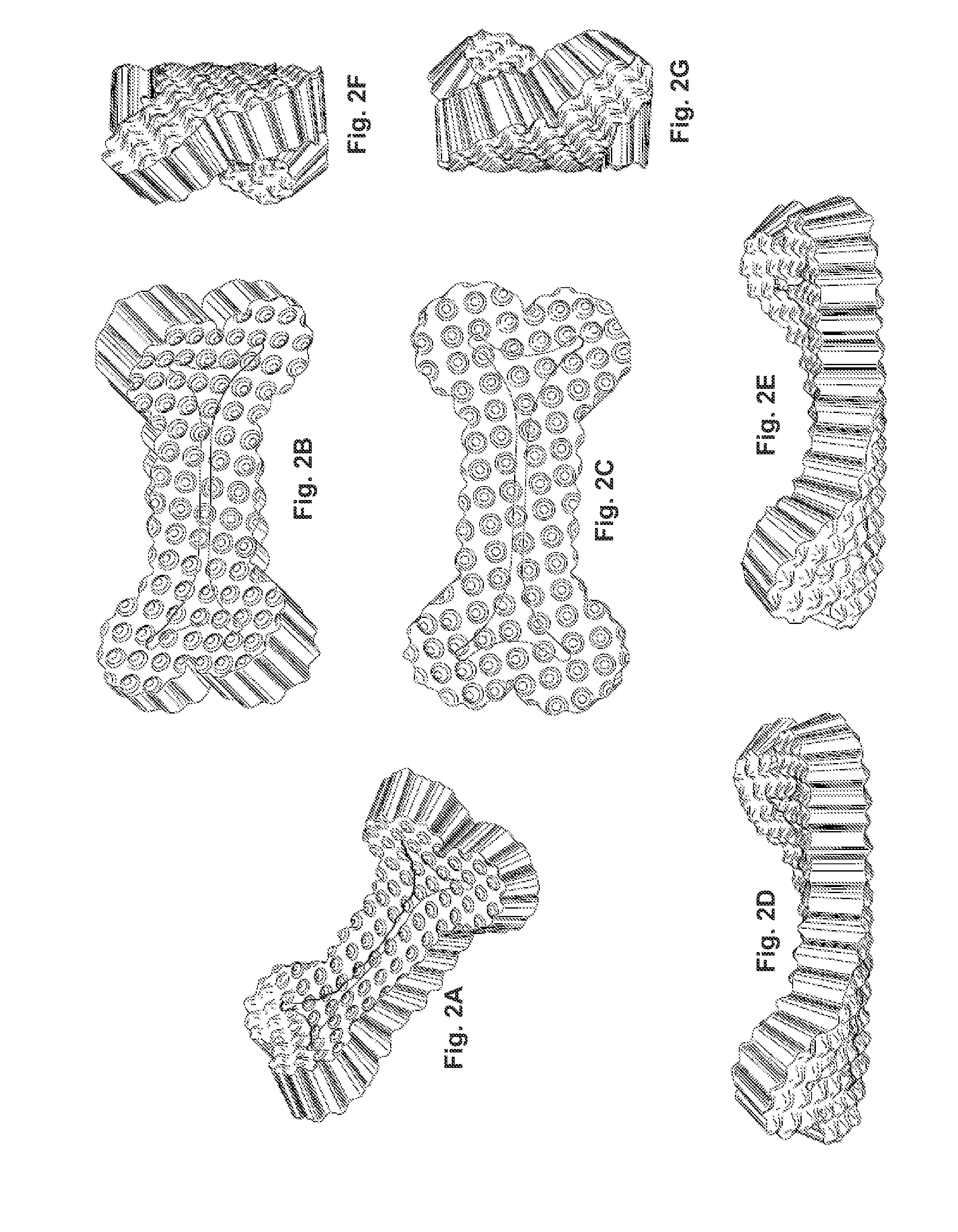

Appetizing and Dentally Efficacious Animal Chews

ActiveUS20130273125A1Effective maintenanceImprove effectivelyCosmetic preparationsFeeding-stuffActive agentDental health

Described herein are chewable articles intended to be provided to animals for purposes including dental cleaning, breath freshening, nutrition, administration to the animal of beneficial agents, satisfaction of the animal's urge to chew, and general enjoyment by the animal. The chews are made to be appetizing to the animal, to satisfy an urge to chew, to effect abrasive cleaning of the animal's teeth, to deliver one or more active agents to the oral cavity of the animal, or a combination of these. The chews have a resilient, chewable texture and are shaped to facilitate dental cleaning, to facilitate oral grasping by the animal, to appeal to human owners of the animal, to enhance the human-animal bond, or a combination of these. Also disclosed are apparatus and methods for making such chewable articles and for formulating and using them to effect dental health in animals.

Owner:BIG HEART PET INC

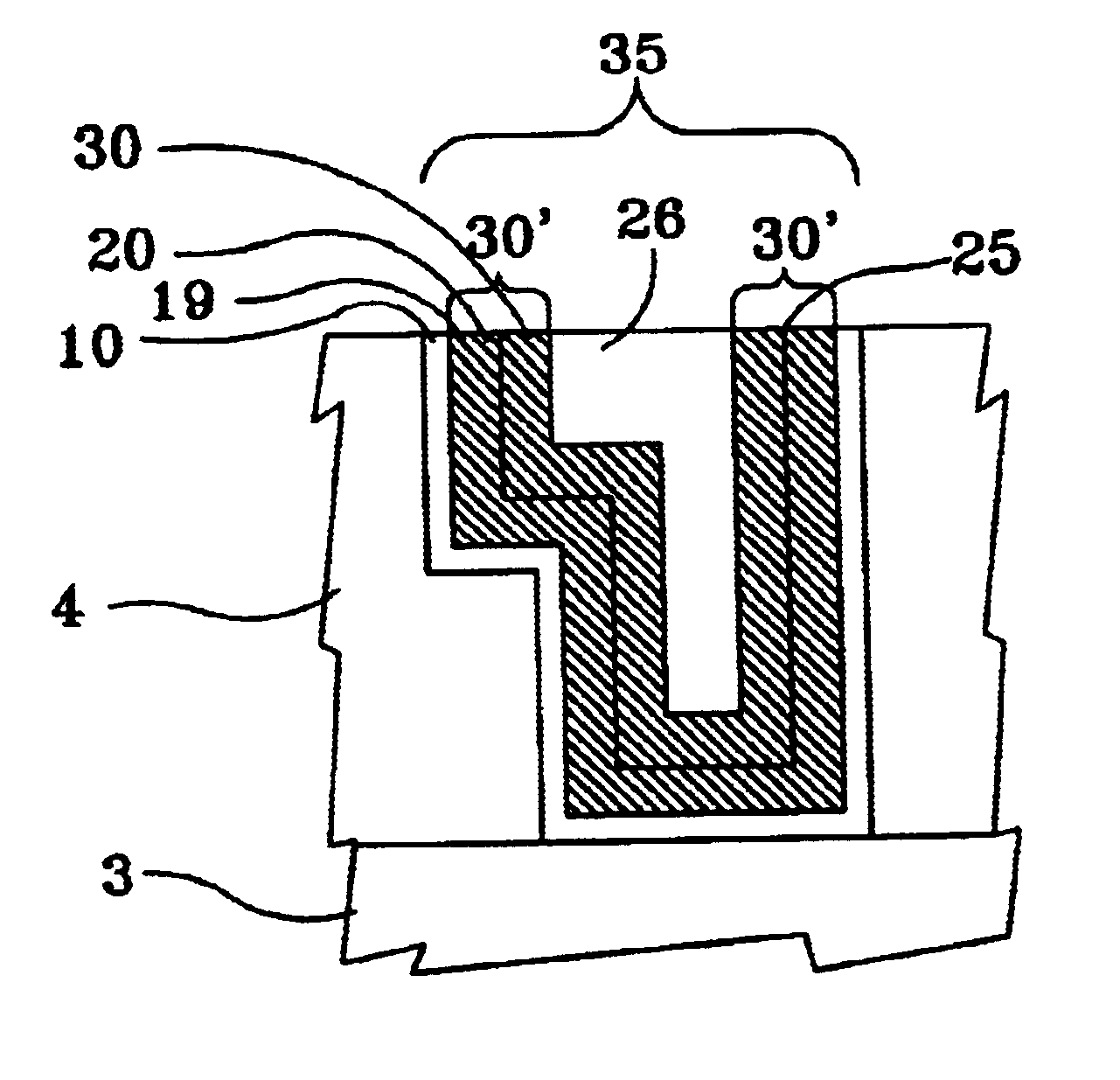

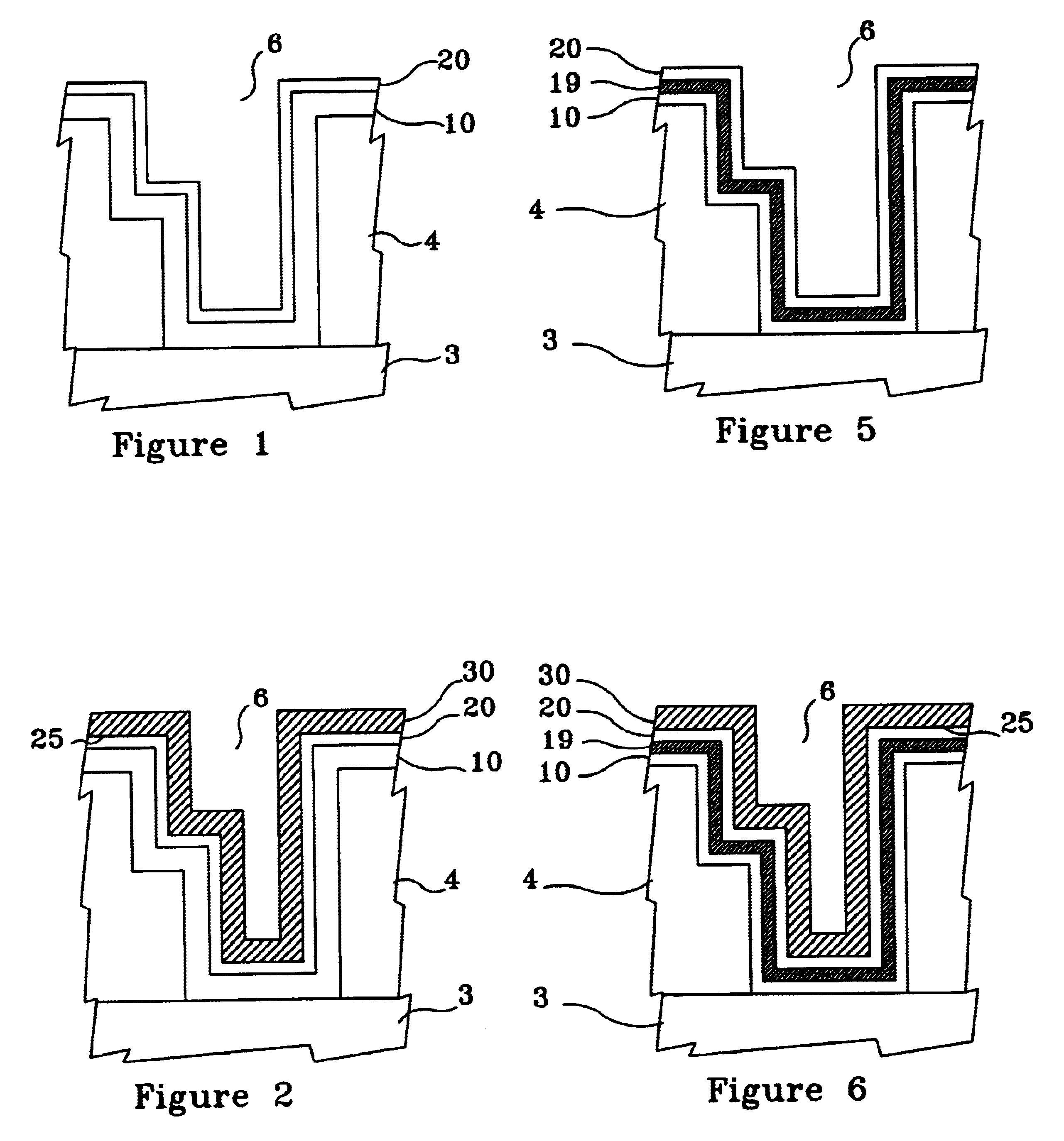

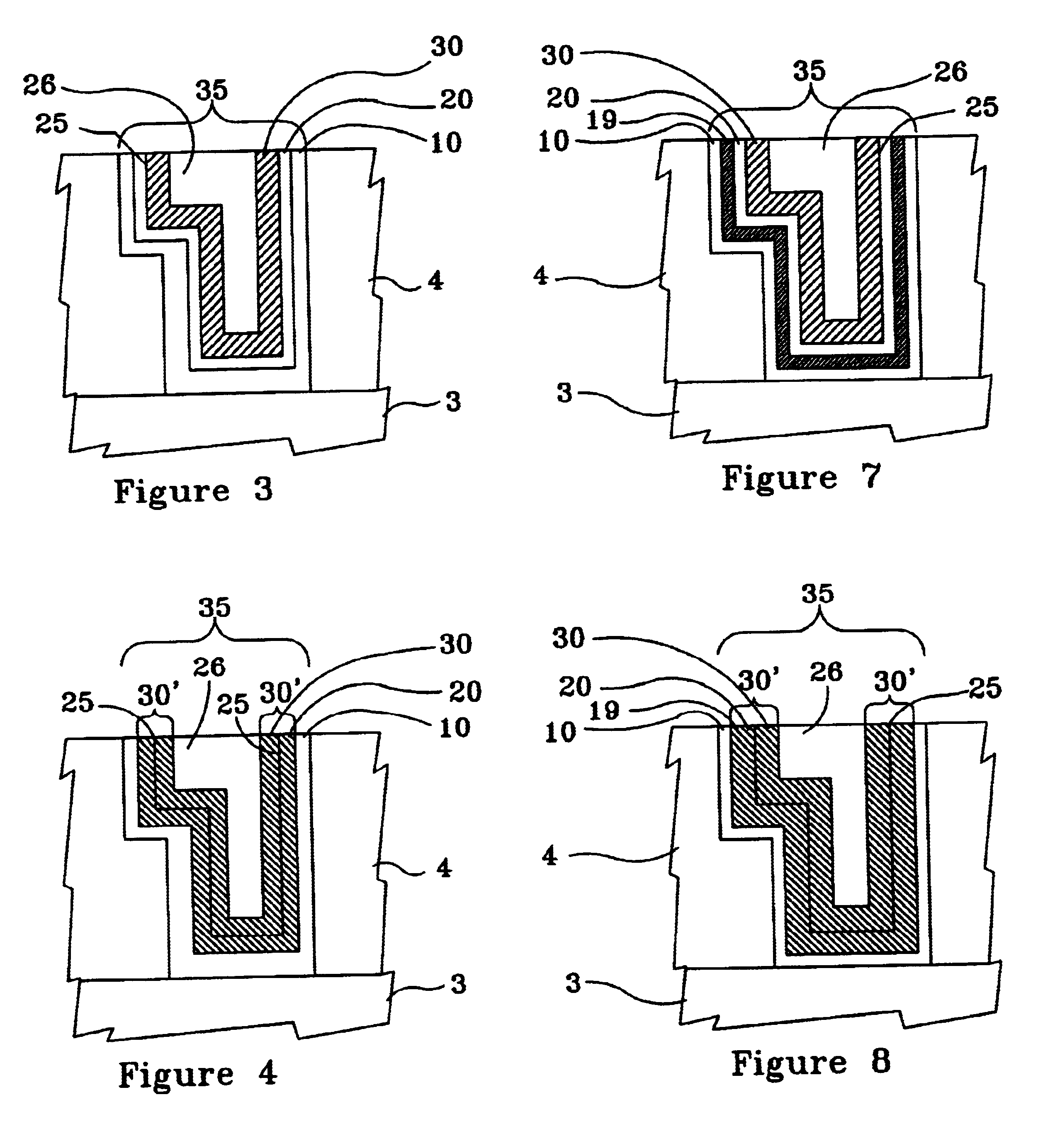

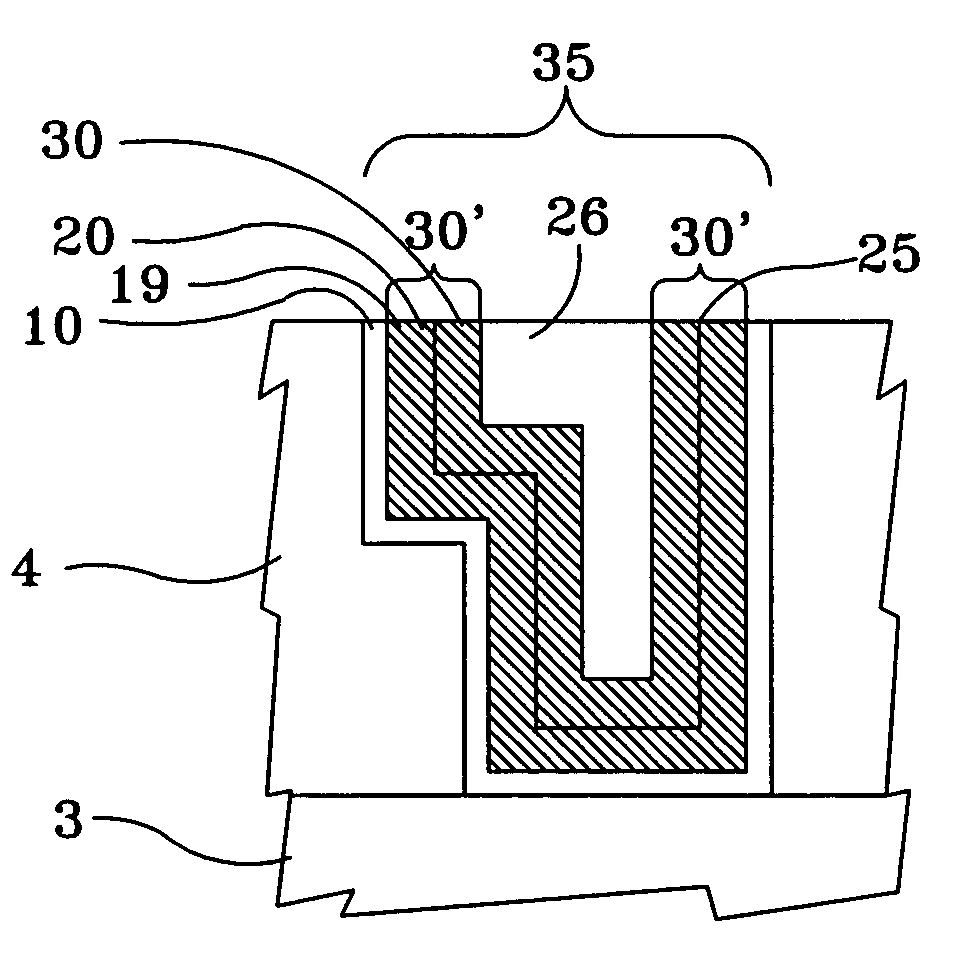

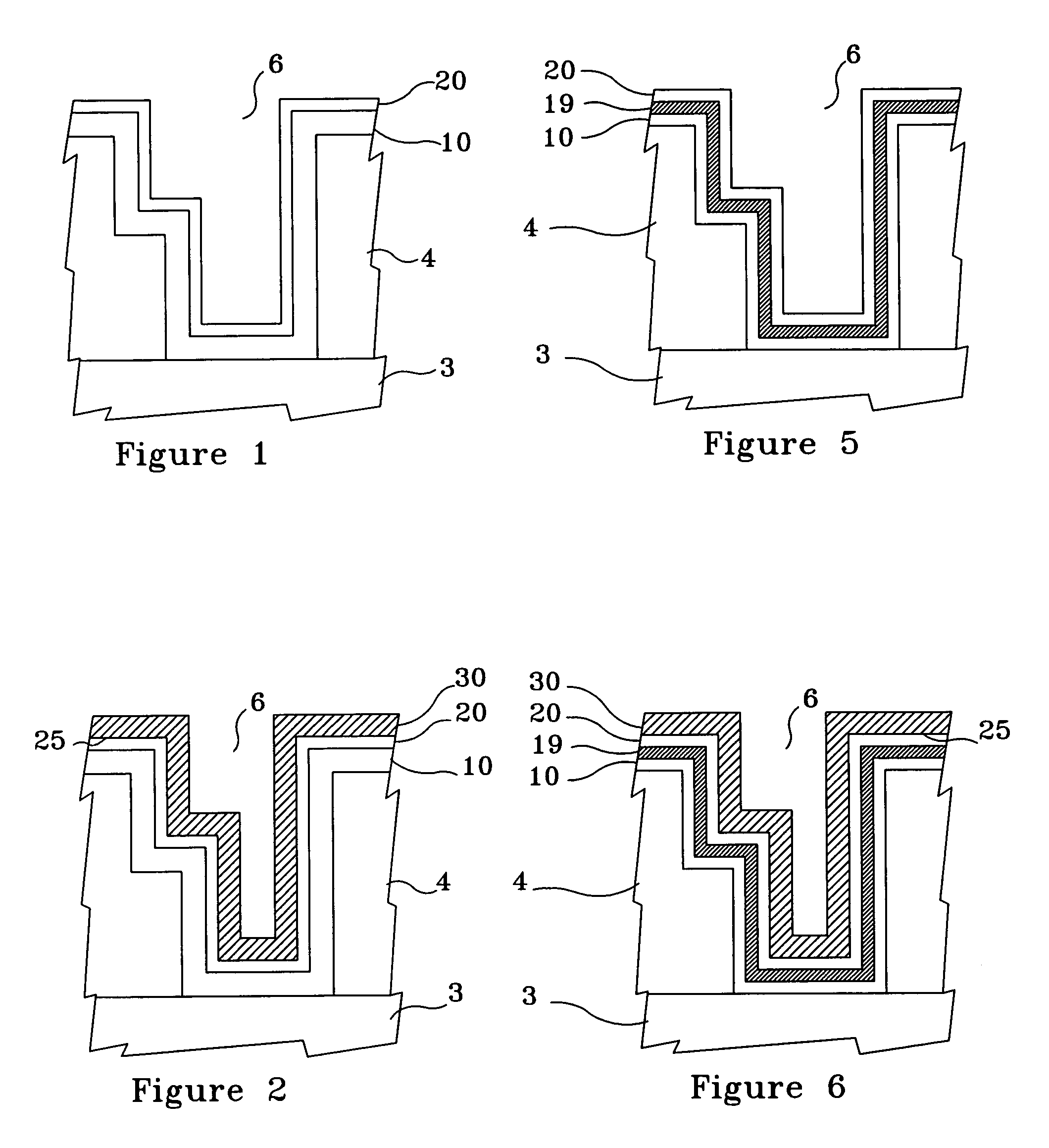

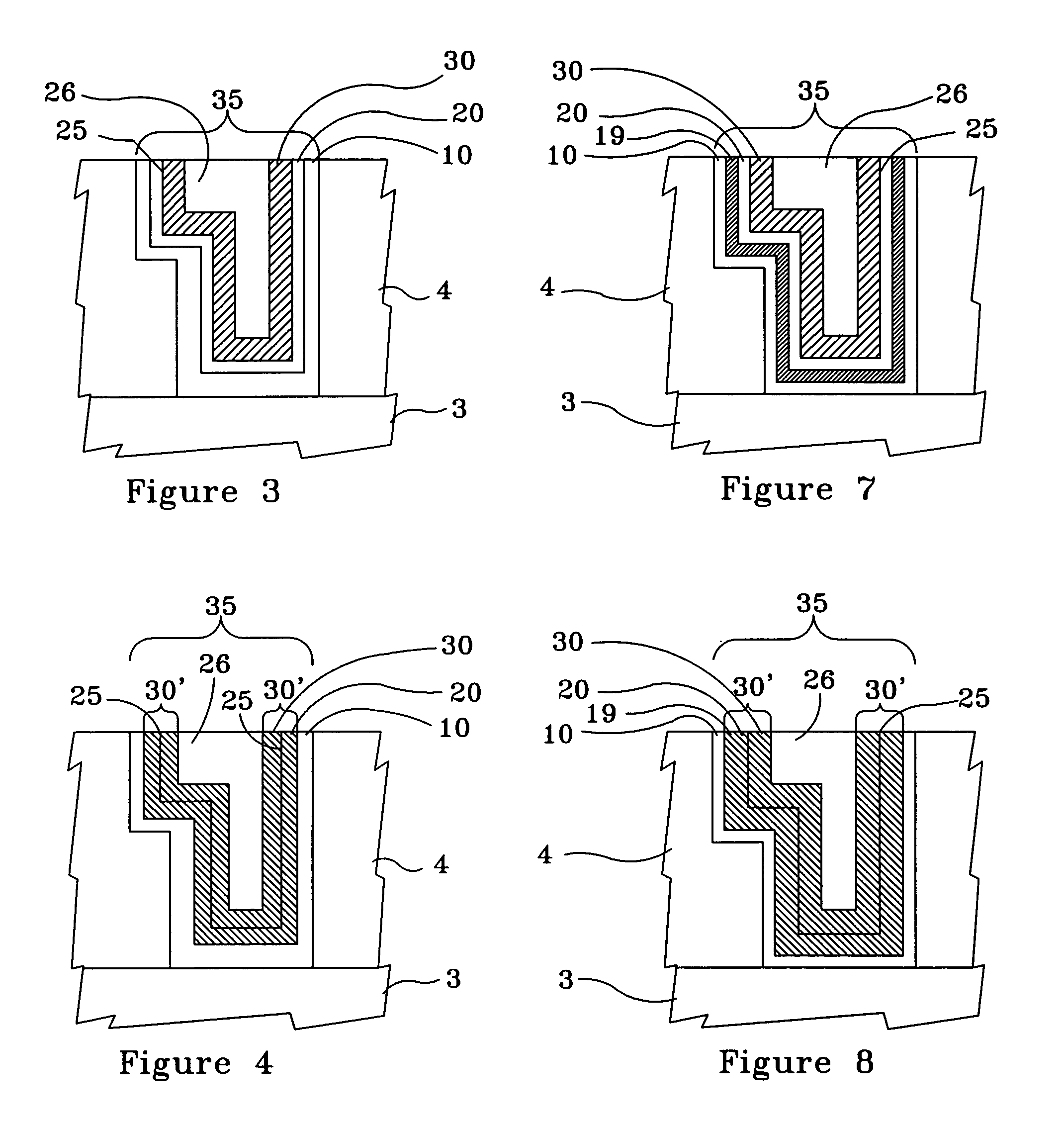

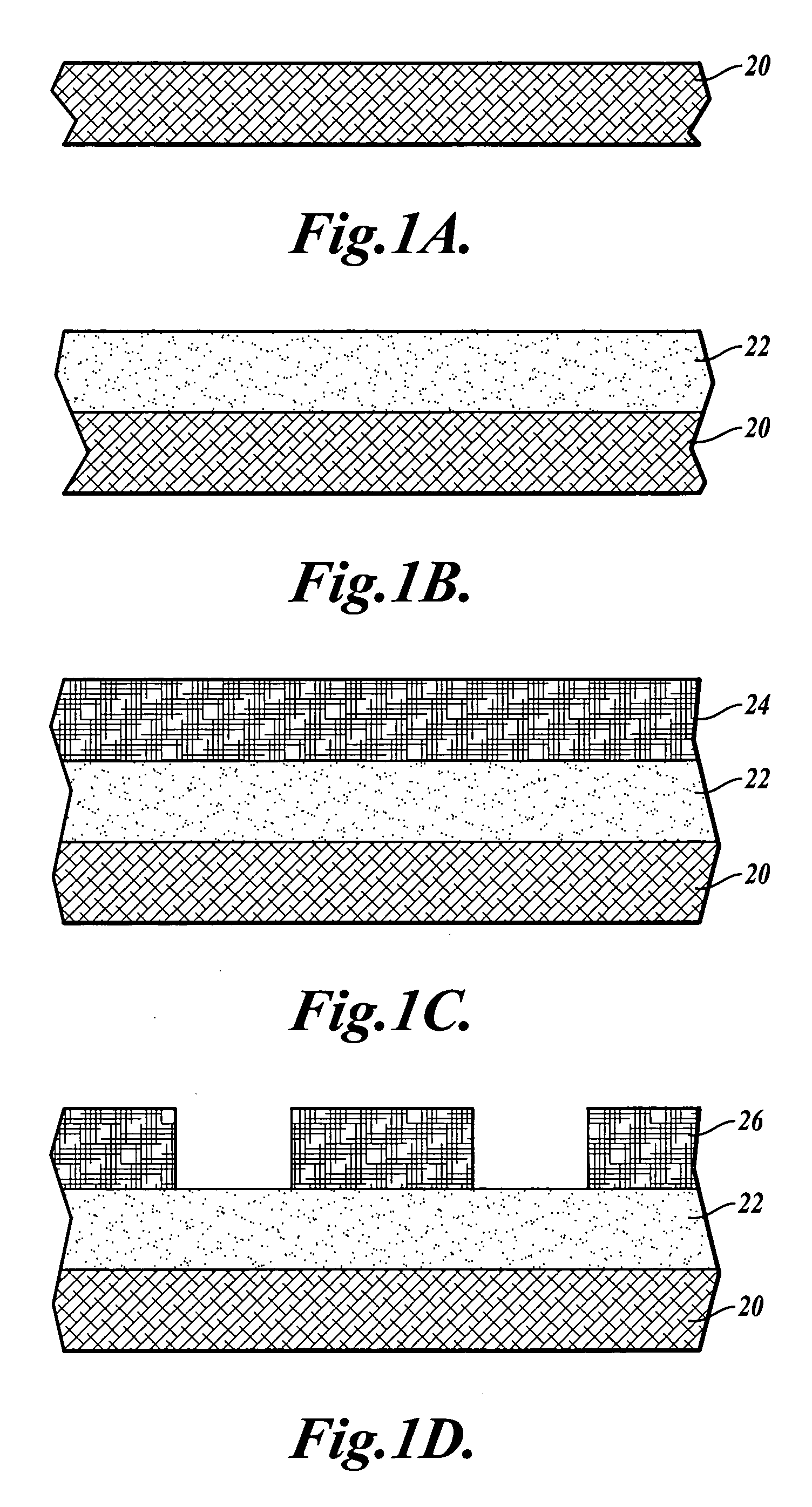

Method of reducing electromigration in a copper line by electroplating an interim copper-zinc alloy thin film on a copper surface and a semiconductor device thereby formed

InactiveUS6660633B1Improves Cu interconnect reliabilityReduce manufacturing costElectrolysis componentsSolid-state devicesCopper interconnectChemical solution

A method of fabricating a semiconductor device, having an interim reduced-oxygen Cu-Zn alloy thin film (30) electroplated on a blanket Cu surface (20) disposed in a via (6) by electroplating, using an electroplating apparatus, the Cu surface (20) in a unique chemical solution containing salts of Zn and Cu, their complexing agents, a pH adjuster, and surfactants; and annealing the interim electroplated Cu-Zn alloy thin film (30); filling the via (6) with further Cu (26); annealing and planarizing the interconnect structure (35); and a semiconductor device thereby formed. The reduction of electromigration in copper interconnect lines (35) is achieved by decreasing the drift velocity in the copper line (35) / via (6), thereby decreasing the copper migration rate as well as the void formation rate, by using an interim conformal Cu-rich Cu-Zn alloy thin film (30) electroplated on a Cu surface (20) from a stable chemical solution, and by controlling the Zn-doping thereof, which improves also interconnect reliability and corrosion resistance.

Owner:GLOBALFOUNDRIES US INC

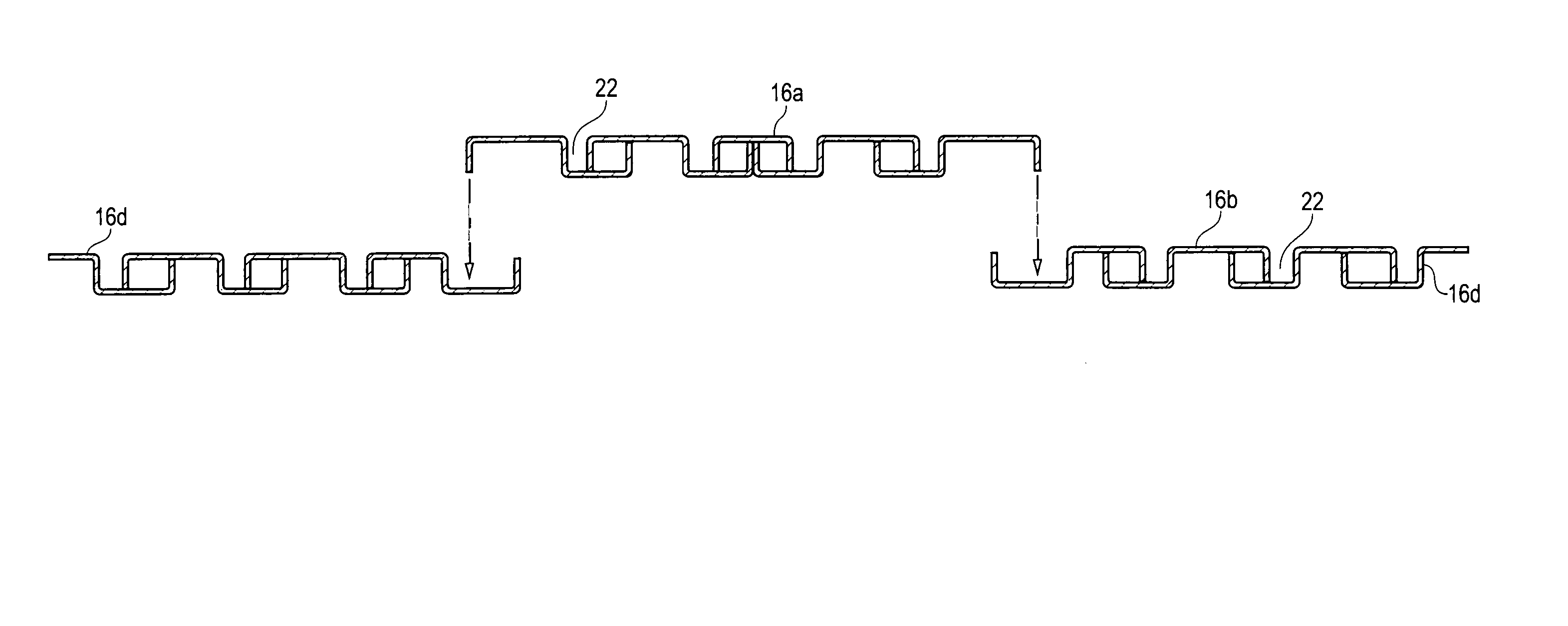

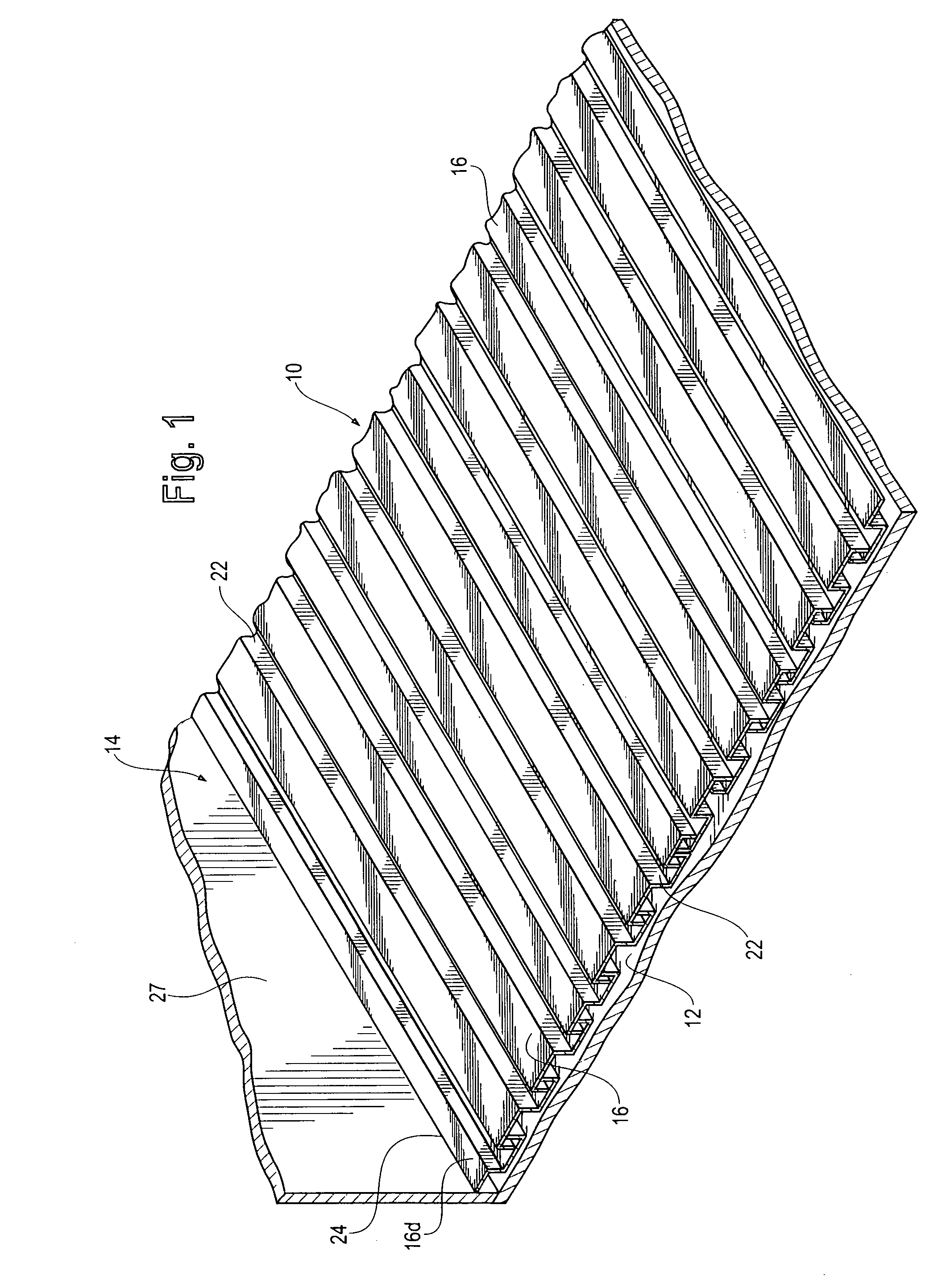

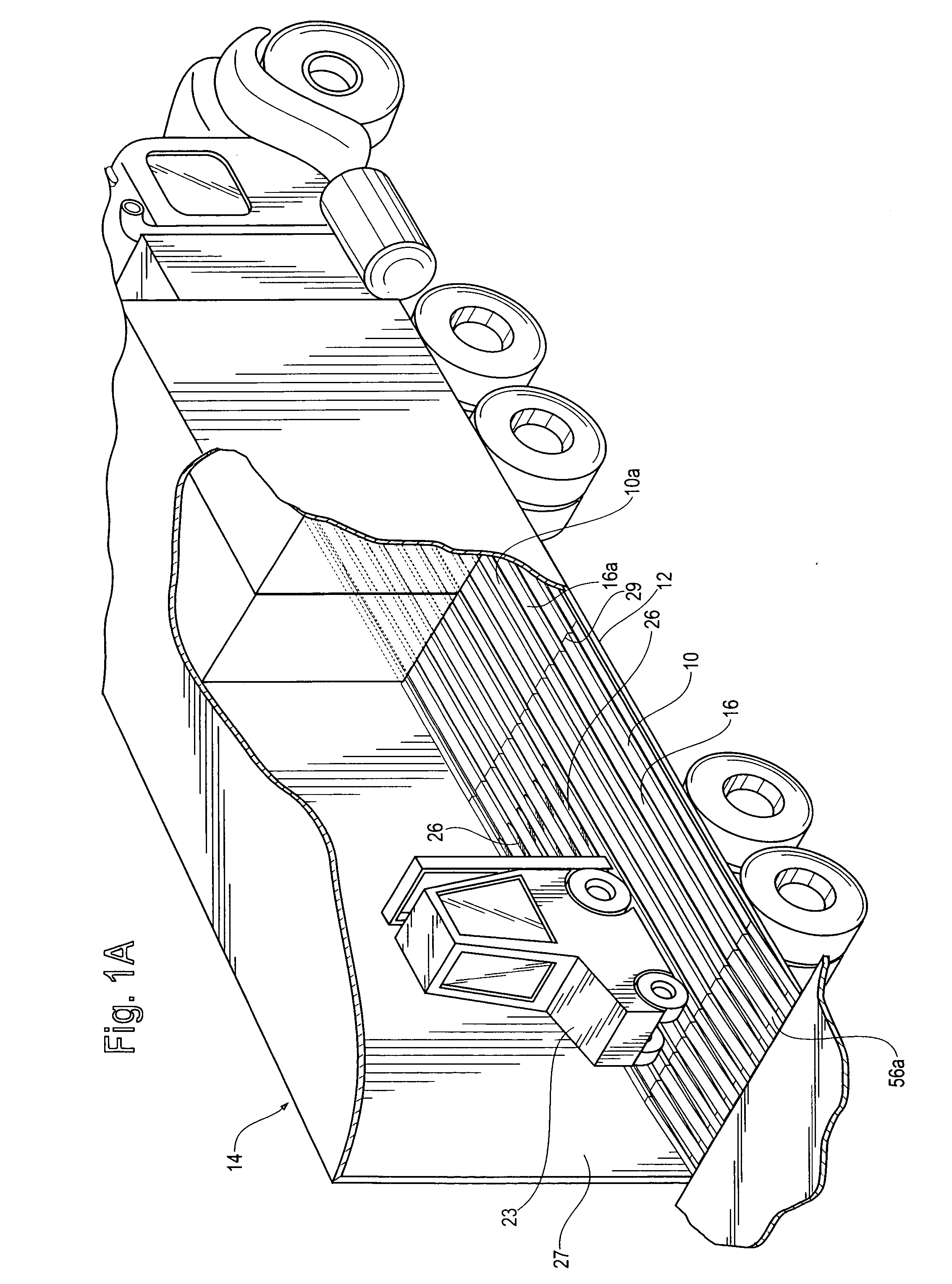

Modular support surface used in the transport of a group of containers

InactiveUS20050152774A1Easy to useComplete fillingRoof covering using tiles/slatesWallsEngineeringSupport surface

A grooved support surface, the support surface being defined by a first plurality of support modules which are held in side-by-side relation together. Individual support modules typically comprise an elongated body having at least a pair of flat segments, joined at a common side edge, and extending transversely to each other. The support modules together define a plurality of spaced, longitudinally extending grooves in the support surface.

Owner:NUNES COMPANY INC THE

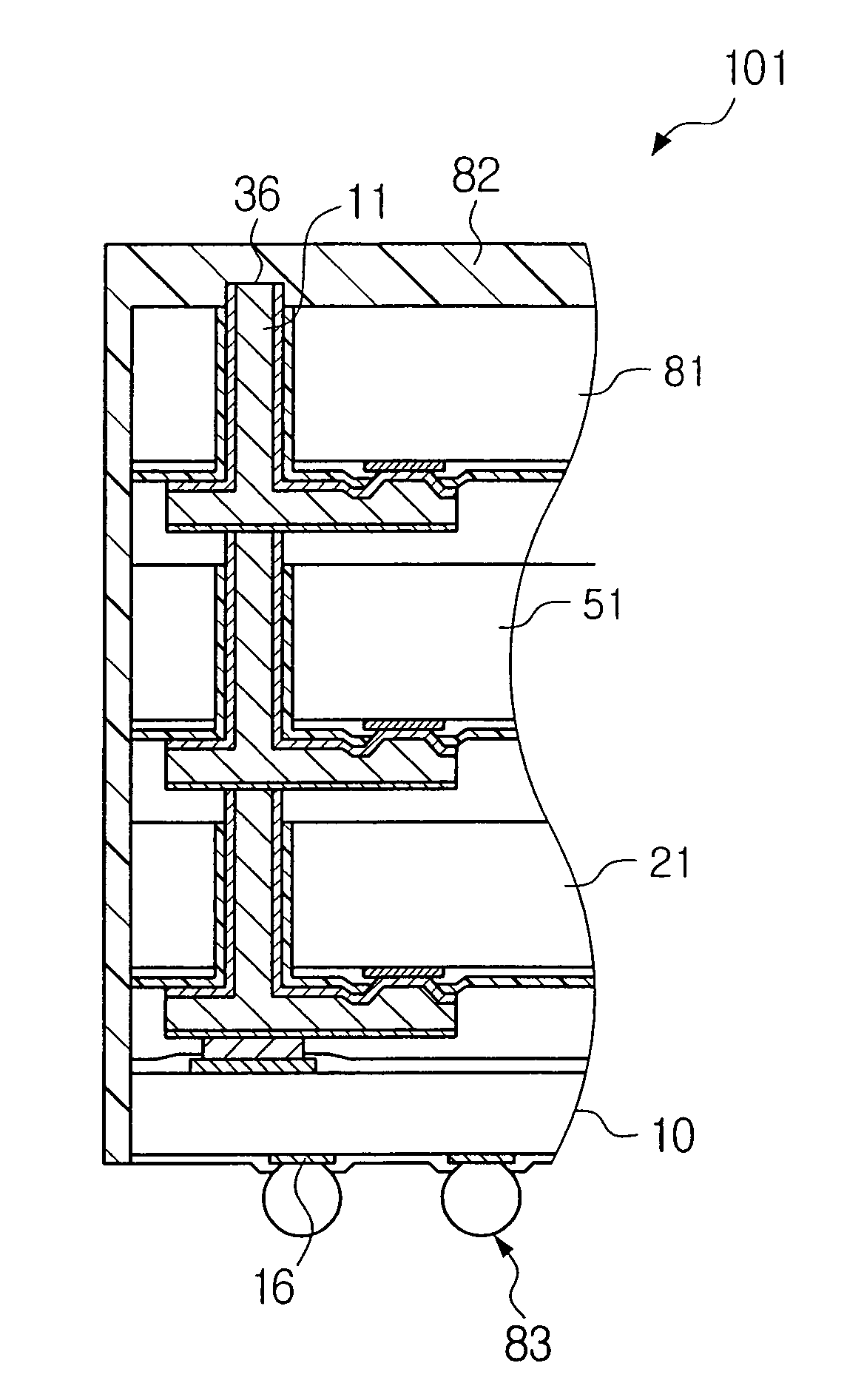

Stacked chip package using photosensitive polymer and manufacturing method thereof

ActiveUS7459774B2AdhesionHigh mechanical reliabilitySemiconductor/solid-state device detailsSolid-state devicesMechanical reliabilityPhotosensitive polymer

In a stacked chip configuration, and manufacturing methods thereof, the gap between a lower and an upper chip is filled completely using a relatively simple process that eliminates voids between the lower and upper chips and the cracking and delamination problems associated with such voids. The present invention is applicable to both chip-level bonding and wafer-level bonding approaches. A photosensitive polymer layer is applied to a first chip, or wafer, prior to stacking the chips or stacking the wafers. The photosensitive polymer layer is partially cured, so that the photosensitive polymer layer is made to be structurally stable, while retaining its adhesive properties. The second chip, or wafer, is stacked, aligned, and bonded to the first chip, or wafer, and the photosensitive polymer layer is then cured to fully bond the first and second chips, or wafers. In this manner, adhesion between chips / wafers is greatly improved, while providing complete gap fill. In addition, mechanical reliability is improved, alleviating the problems associated with cracking and delamination, and leading to an improvement in device yield and device reliability.

Owner:SAMSUNG ELECTRONICS CO LTD

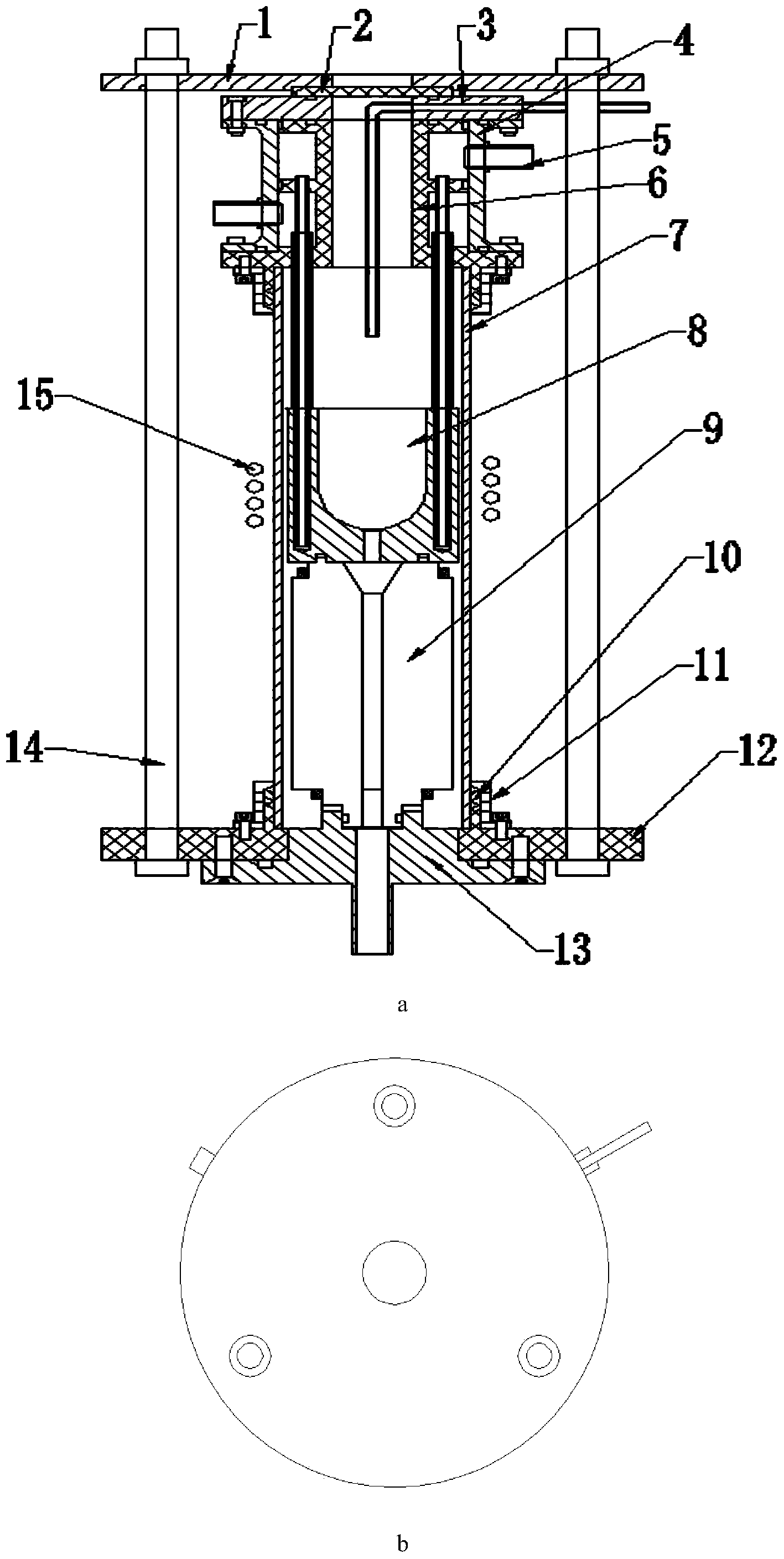

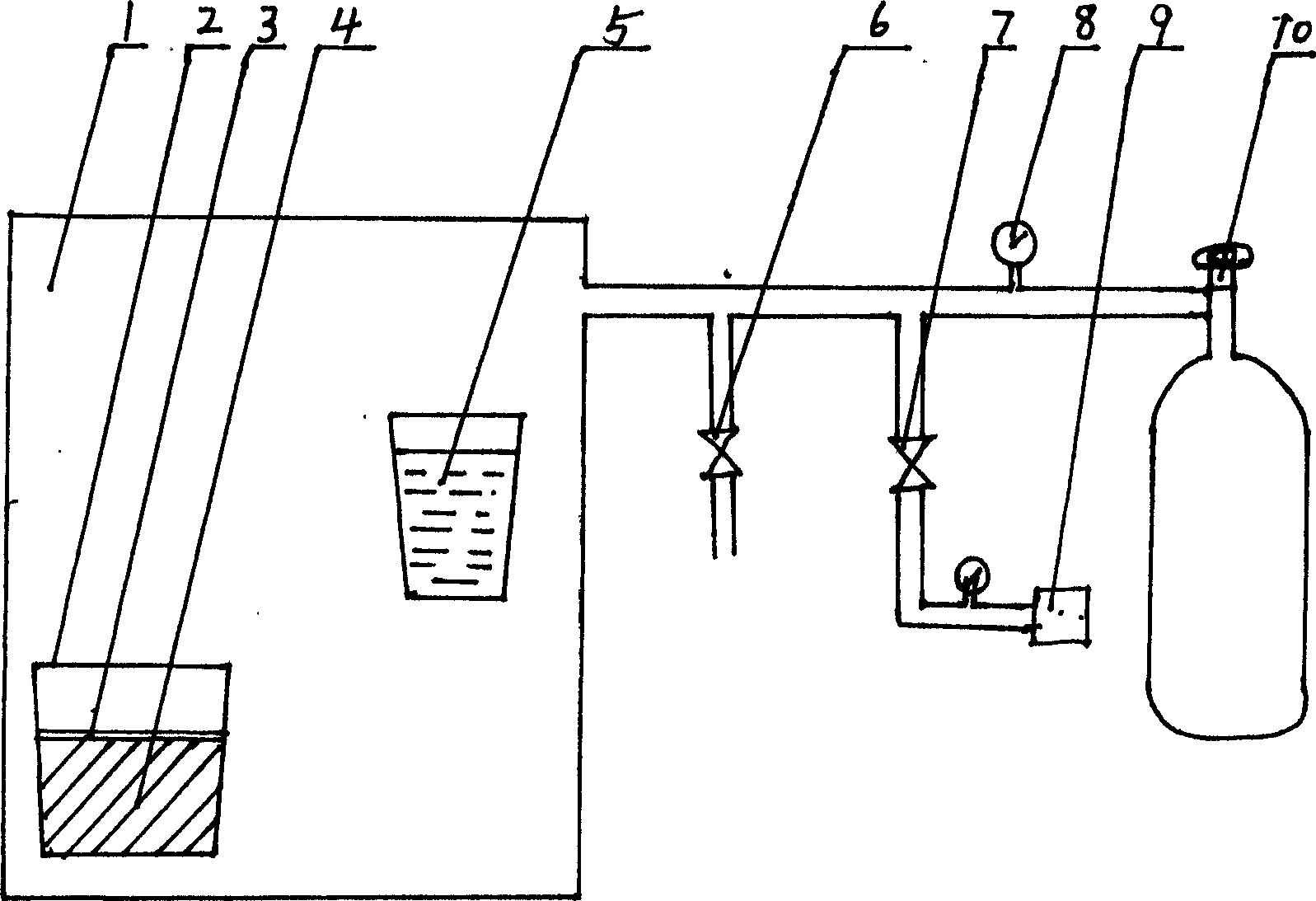

Smelting and casting method and casting device of titanium-based amorphous composite material

ActiveCN103834822AFast fillAvoid pollutionCasting parameters measurement/indication devicesAlloyElectromagnetic induction

The invention discloses a smelting and casting method and a casting device of a titanium-based amorphous composite material. The smelting and casting method has the advantages that the force effect in the electromagnetic induction principle is utilized, alloy in a crucible is suspended in the air for smelting, so that the pollution caused by contact with the crucible is avoided and the control for the alloy heating state is realized; when the smelting process is finished, a heating power supply is switched off, an electromagnetic valve for suction casting or spray casting is opened, so that the rapid mold-filling of alloy solution is realized; in the spray-casting process, the control to the spray-casting speed is realized by changing the level of the air pressure in a gas storage tank, and further the amorphous composite material with different microscopic structures is prepared by controlling the solidification process; the defects in the prior art are overcome, the large-size titanium-based amorphous composite material is obtained by integrating the prior art, the stable control of the process to the organization structure is realized by adjusting process parameters such as temperature, temperature holding time, circular heating times and casting speed, and an ideal optimized design structure is obtained.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

Semiconductor device having copper lines with reduced electromigration using an electroplated interim copper-zinc alloy film on a copper surface

InactiveUS6936925B1Reduce electromigrationLow mobilityElectrolysis componentsSemiconductor/solid-state device detailsCopper interconnectChemical solution

The present invention relates to the semiconductor device fabrication industry. More particularly a semiconductor device, having an interim reduced-oxygen Cu—Zn alloy thin film (30) electroplated on a blanket Cu surface (20) disposed in a via (6) by electroplating, using an electroplating apparatus, the Cu surface (20) in a unique chemical solution containing salts of Zn and Cu, their complexing agents, a pH adjuster, and surfactants; and annealing the interim electroplated Cu—Zn alloy thin film (30); filling the via (6) with further Cu (26); annealing and planarizing the interconnect structure (35). The reduction of electromigration in copper interconnect lines (35) is achieved by decreasing the drift velocity in the copper line (35) / via (6), thereby decreasing the copper migration rate as well as the void formation rate, by using an interim conformal Cu-rich Cu—Zn alloy thin film (30) electroplated on a Cu surface (20) from a stable chemical solution, and by controlling the Zn-doping thereof, which improves also interconnect reliability and corrosion resistance.

Owner:GLOBALFOUNDRIES INC

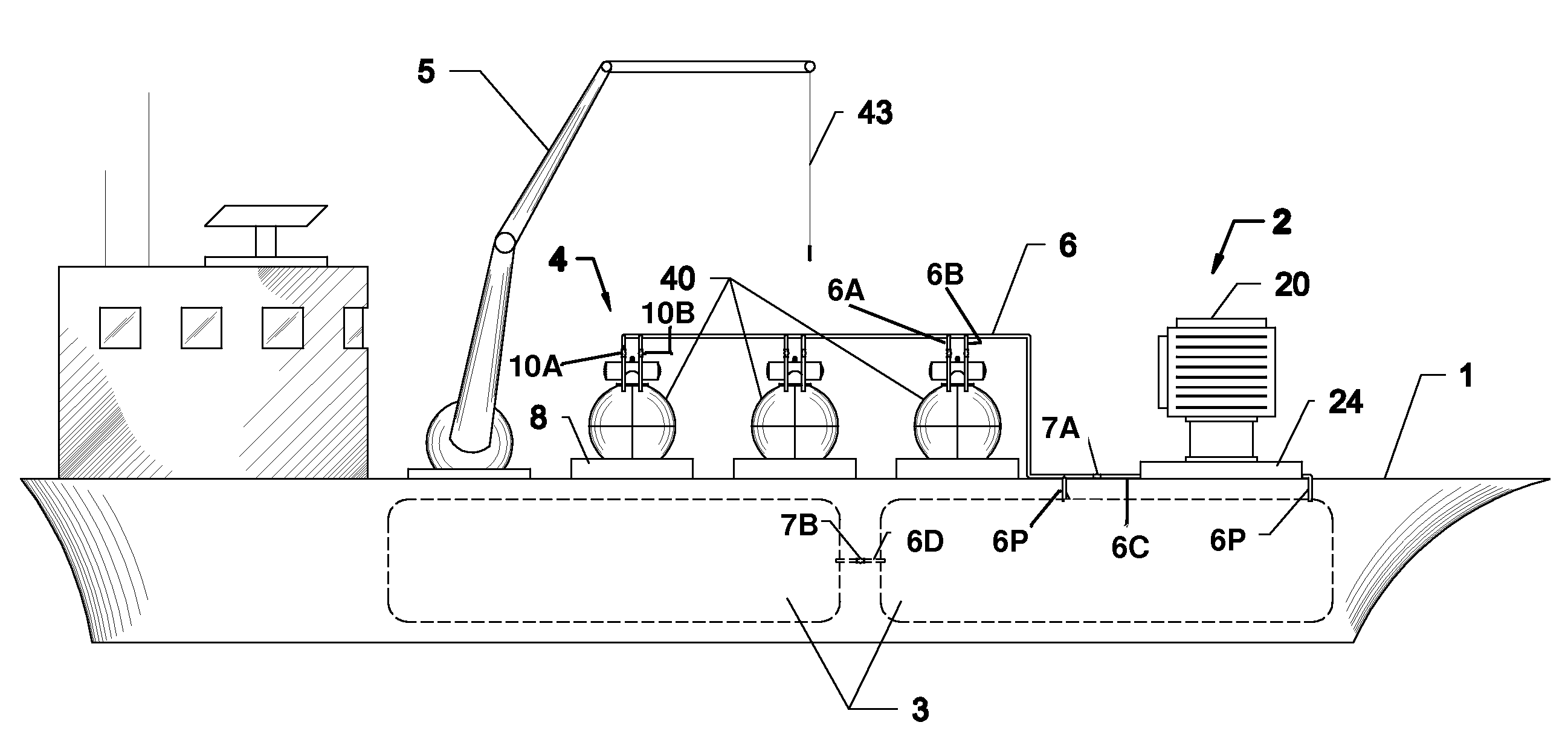

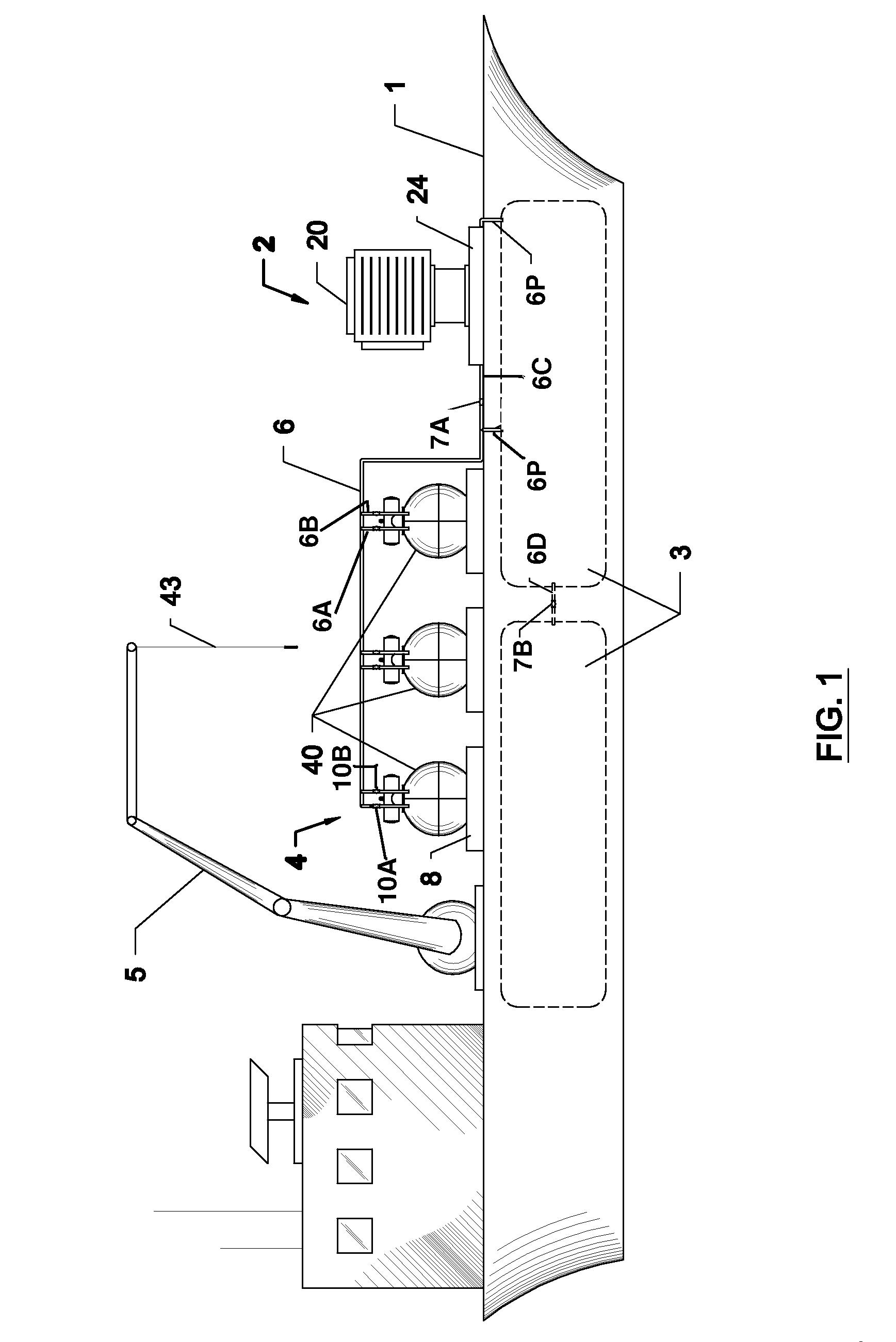

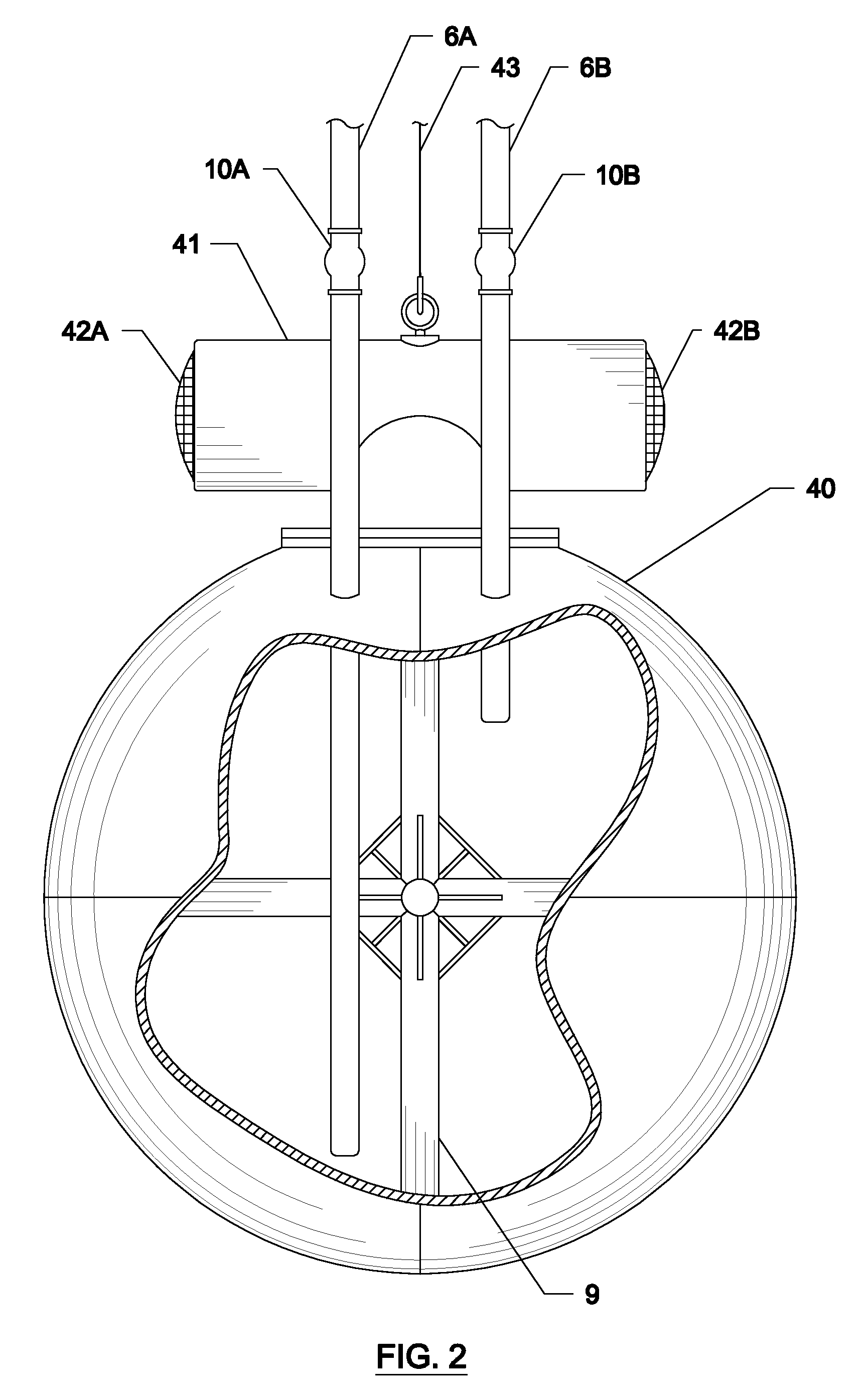

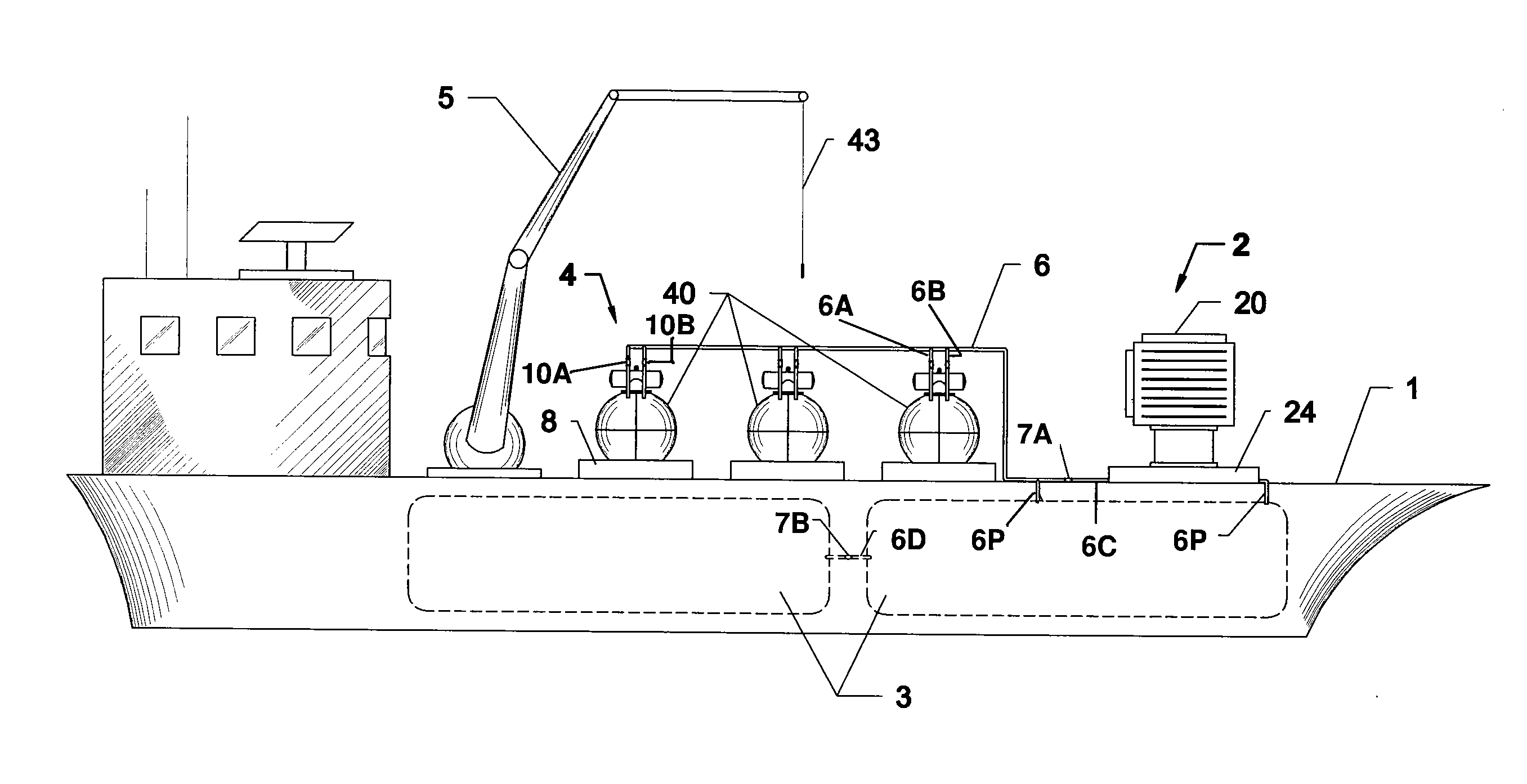

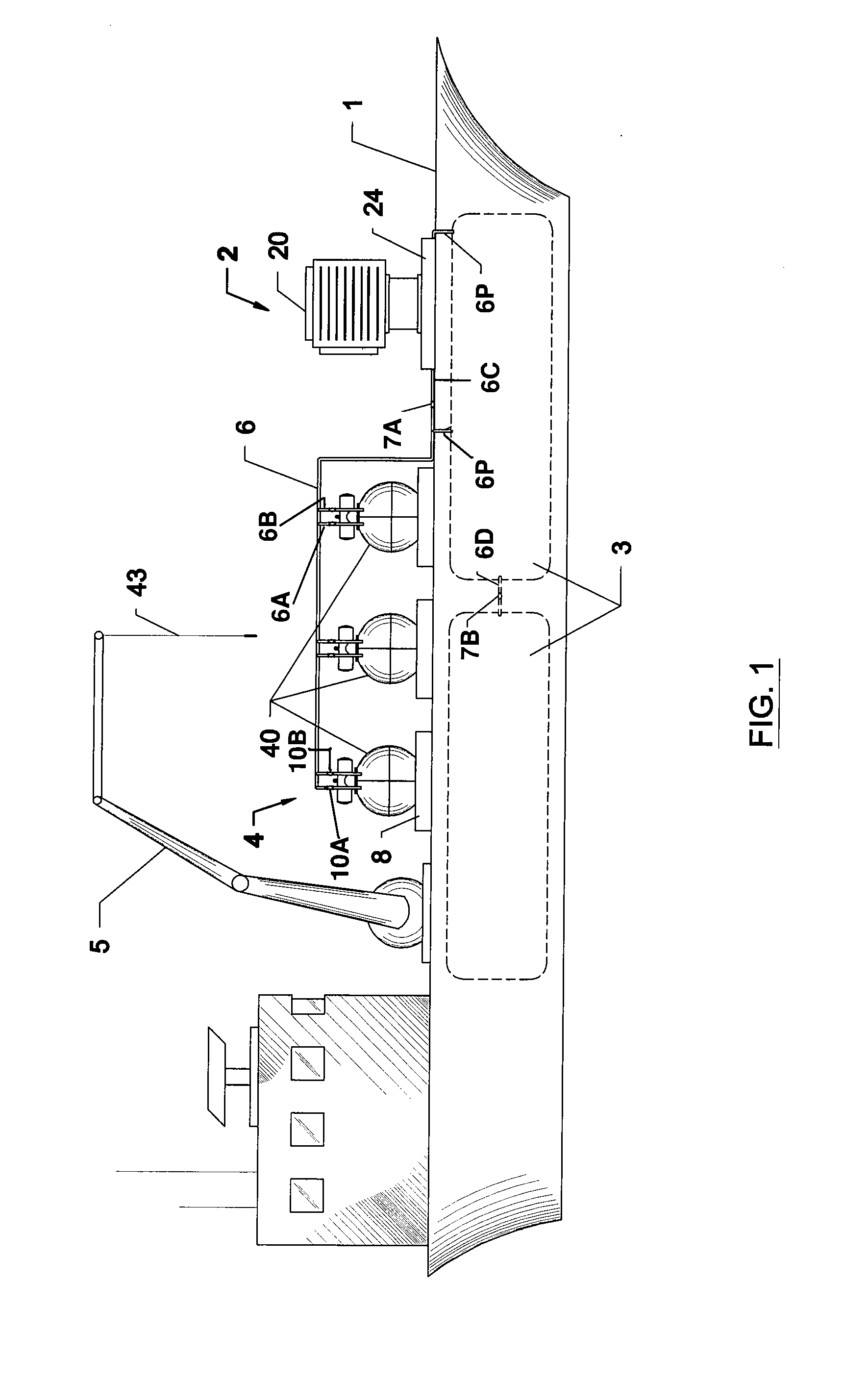

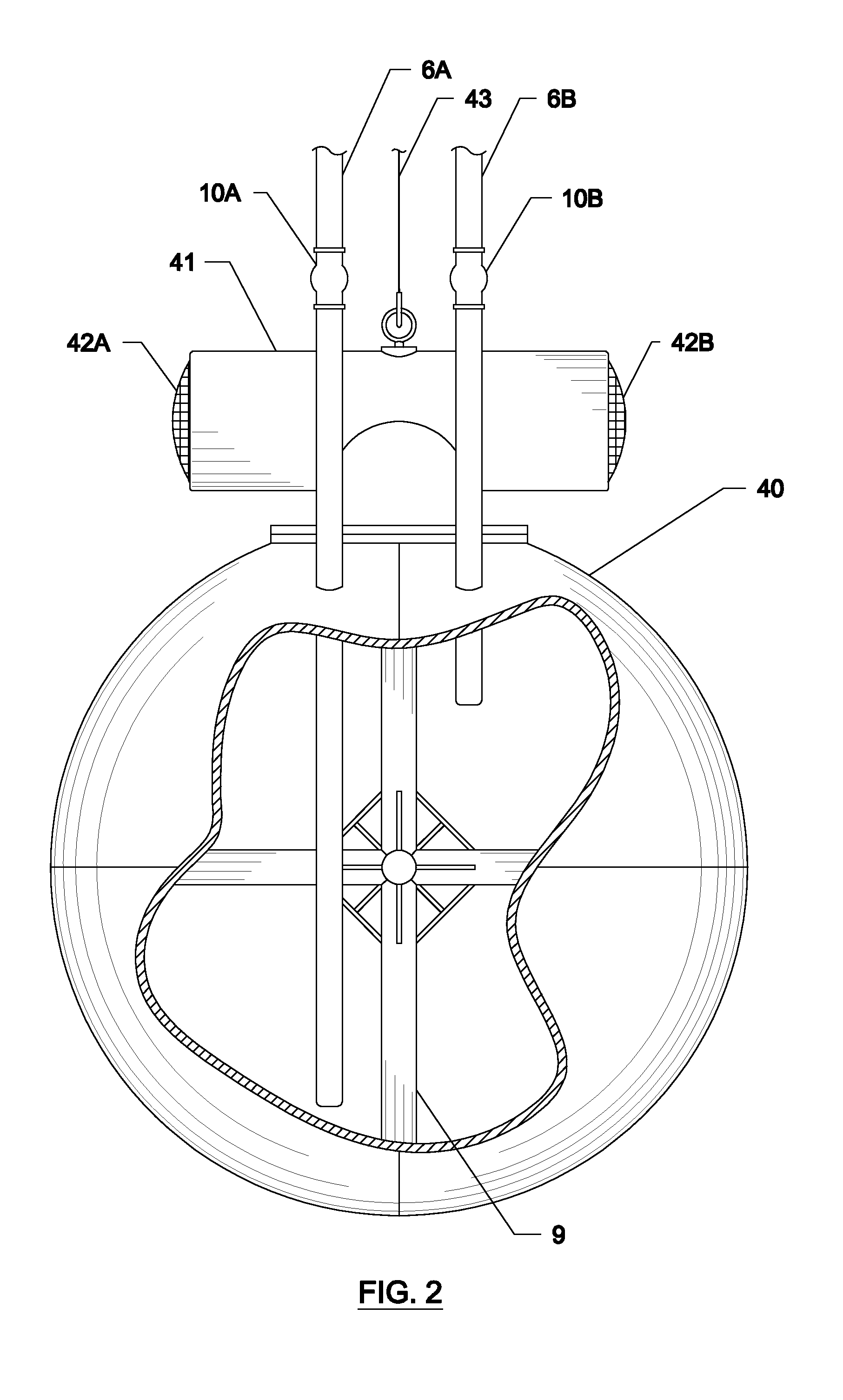

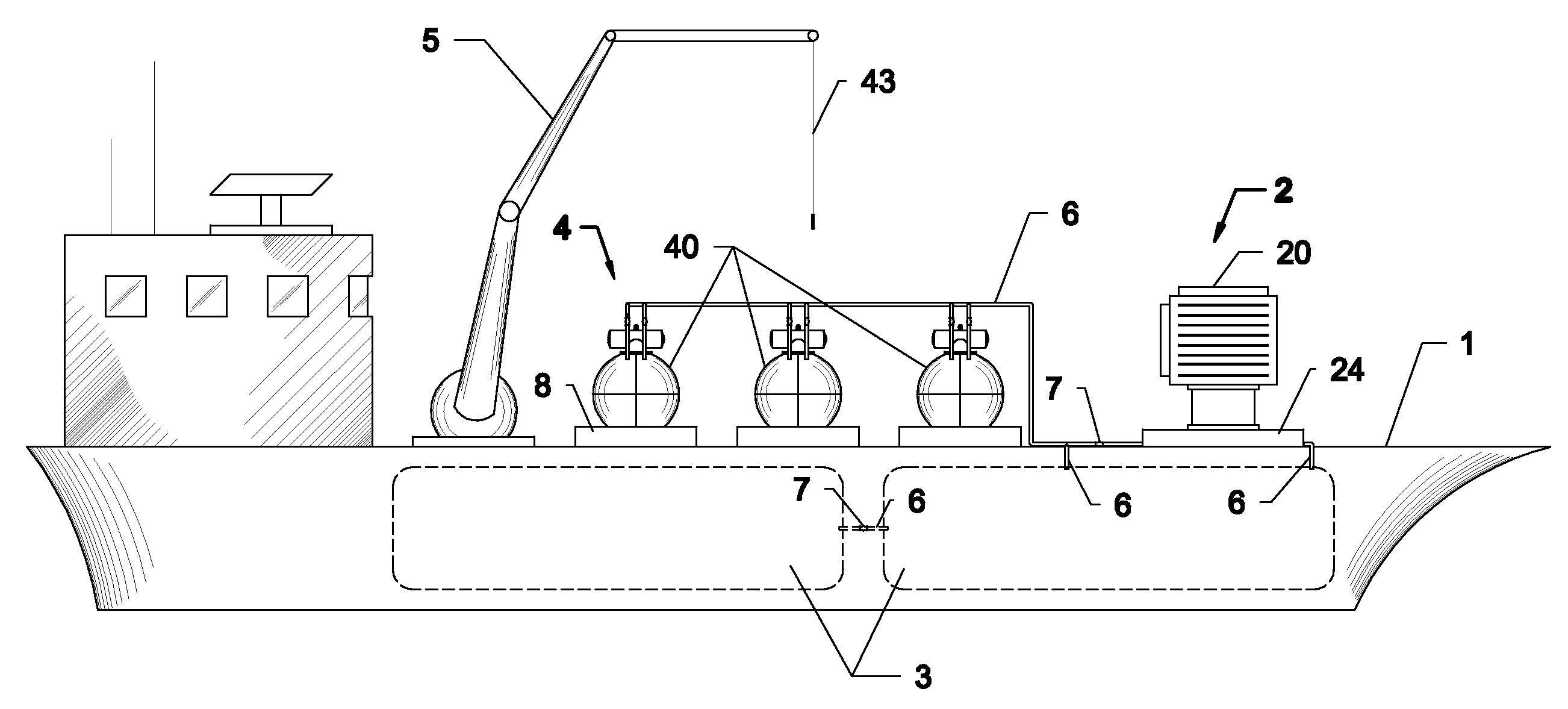

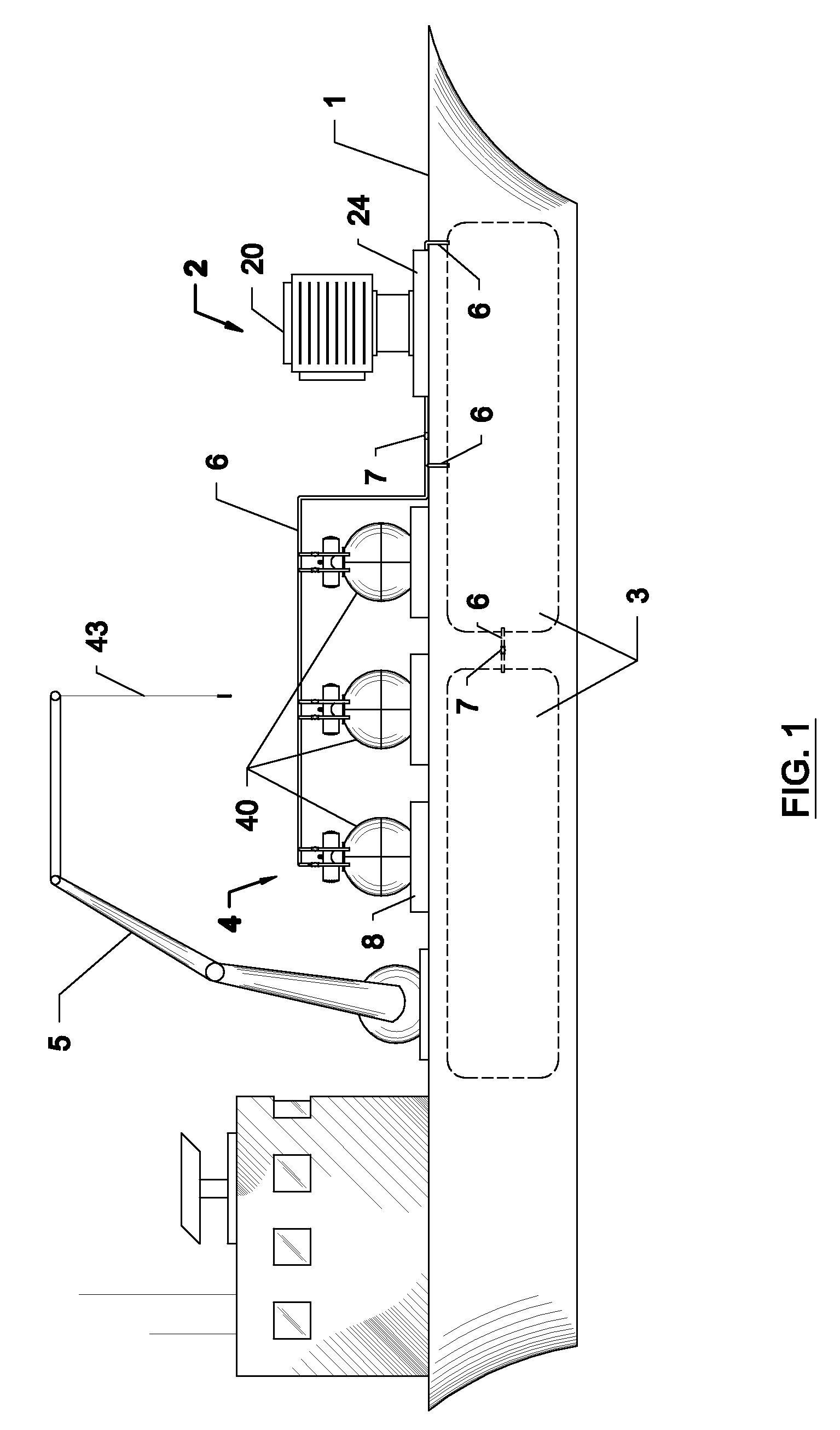

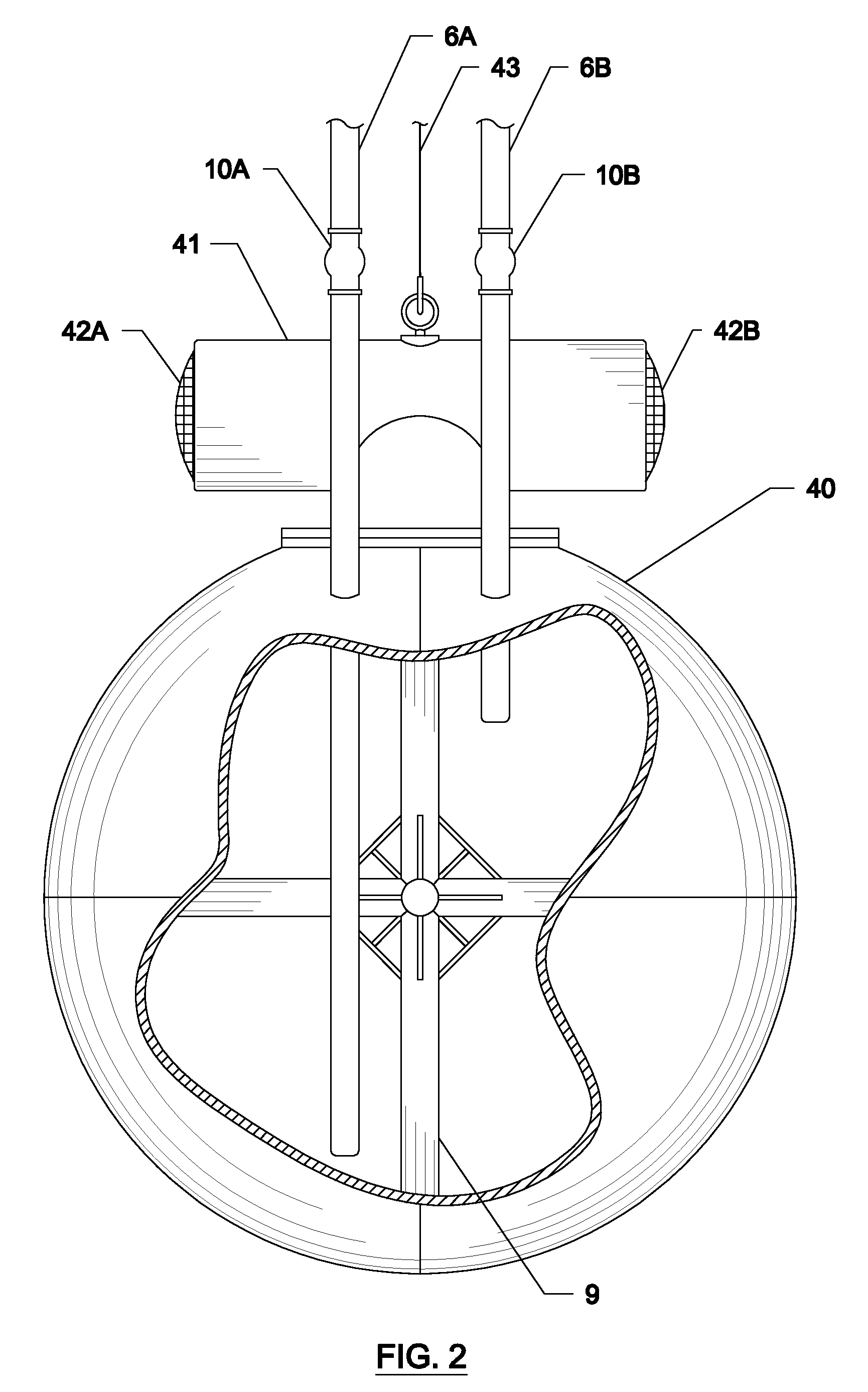

Method, apparatus, and processes for producing potable water utilizing reverse osmosis at ocean depth in combination with shipboard moisture dehumidification

InactiveUS7901580B2Great advantageReduce the possibilityAuxillariesGeneral water supply conservationSaline waterWater source

Devices and methods for producing purified water. The device includes a reverse osmosis subsystem, a dehumidification subsystem and a purified water storage tank fluidly coupled to the subsystems such that purified water produced by each can be locally stored. A vehicular platform, such as a ship, can be used to locate the device adjacent a supply of saline water and humid air. A saline water inlet, membrane and purified water outlet cooperate in the reverse osmosis subsystem to allow preferential passage of water relative to salt in a saline water supply, while the dehumidification subsystem includes a heat exchanger that extracts moisture from the ambient humid air. Purified water produced by each of the subsystems can be used as a potable water source. When used in conjunction with a ship, part or all of the reverse osmosis subsystem can be submersed to a depth sufficient to generate a hydrostatic pressure that is in turn sufficient to passively operate the reverse osmosis membrane such that additional pressurizing equipment, such as a pump, is not needed. Furthermore, the temperature of the water purified by the reverse osmosis subsystem may be low enough to be used as a condensing agent for the ambient humid air passing through the dehumidification subsystem.

Owner:SALYER IVAL O

Hydrogen assisted HDP-CVD deposition process for aggressive gap-fill technology

InactiveUS20050008790A1Strong Gap Filling CapabilityReduce the overall heightElectric discharge tubesSemiconductor/solid-state device manufacturingHigh densityHydrogen

A method of depositing a silicon oxide layer over a substrate having a trench formed between adjacent raised surfaces. In one embodiment the silicon oxide layer is formed in a multistep process that includes depositing a first portion of layer over the substrate and within the trench by forming a high density plasma process that has simultaneous deposition and sputtering components from a first process gas comprising a silicon source, an oxygen source and helium and / or molecular hydrogen with highD / S ratio, for example, 10-20 and, thereafter, depositing a second portion of the silicon oxide layer over the substrate and within the trench by forming a high density plasma process that has simultaneous deposition and sputtering components from a second process gas comprising a silicon source, an oxygen source and molecular hydrogen with a lowerD / S ratio of, for example, 3-10.

Owner:APPLIED MATERIALS INC

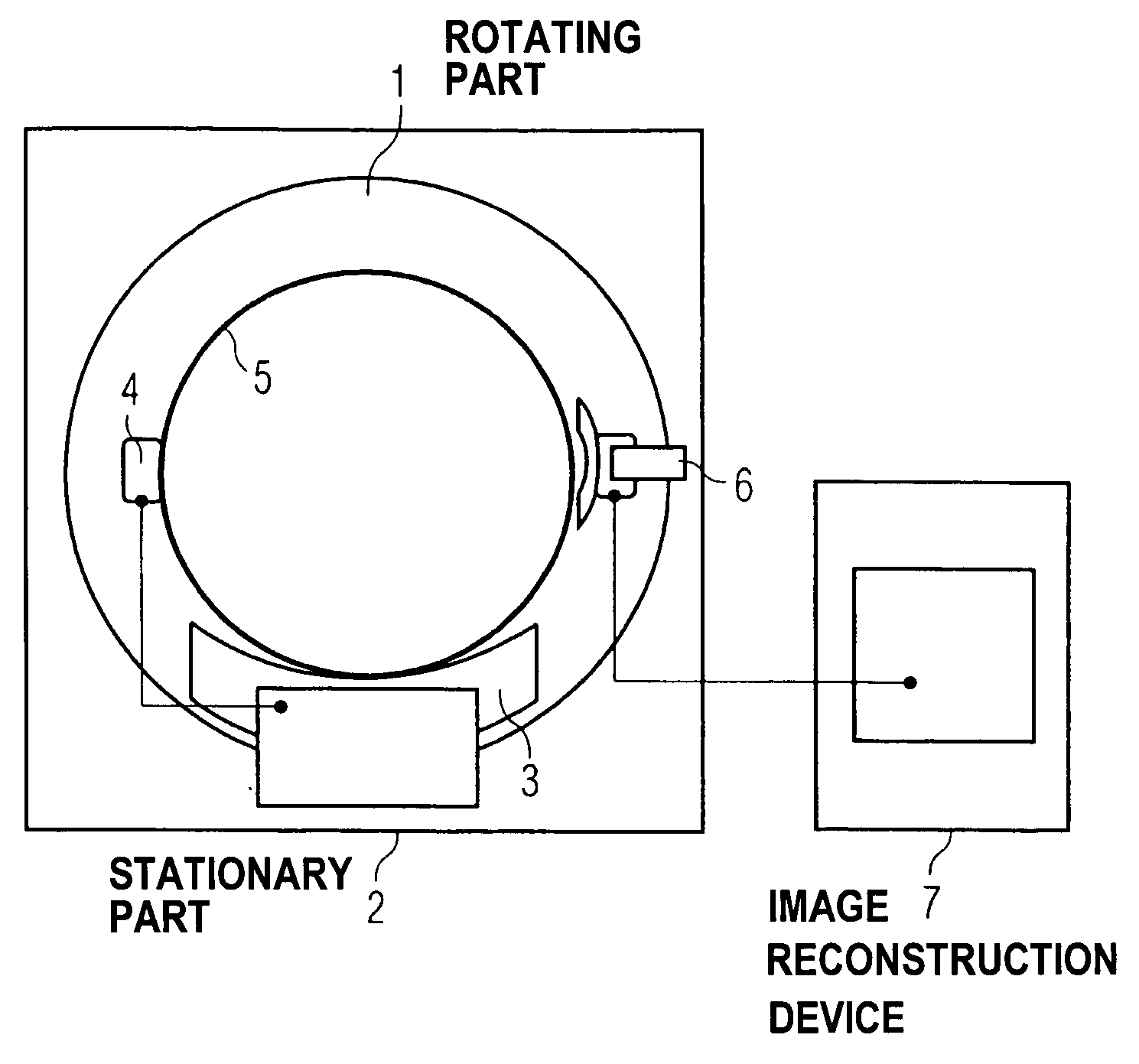

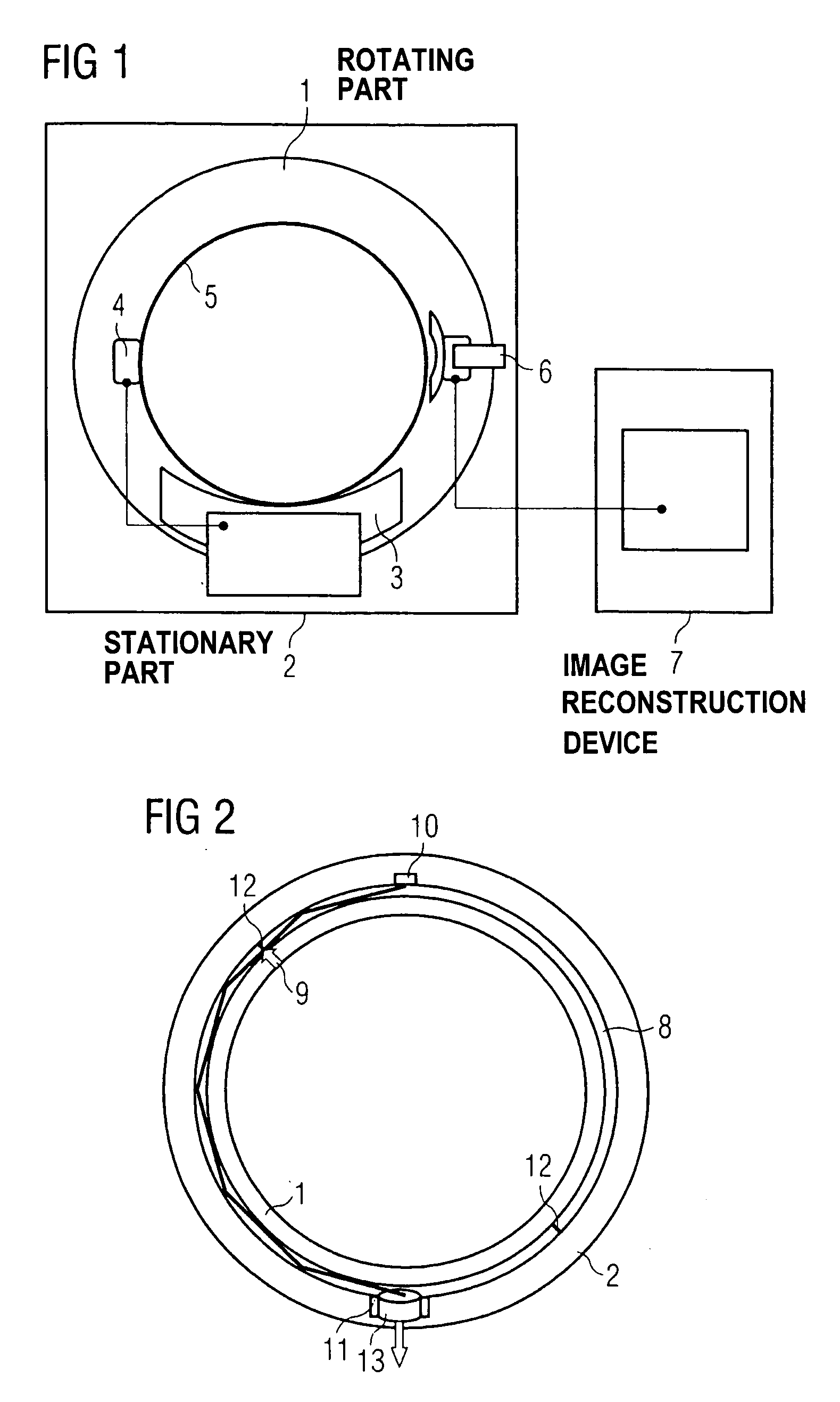

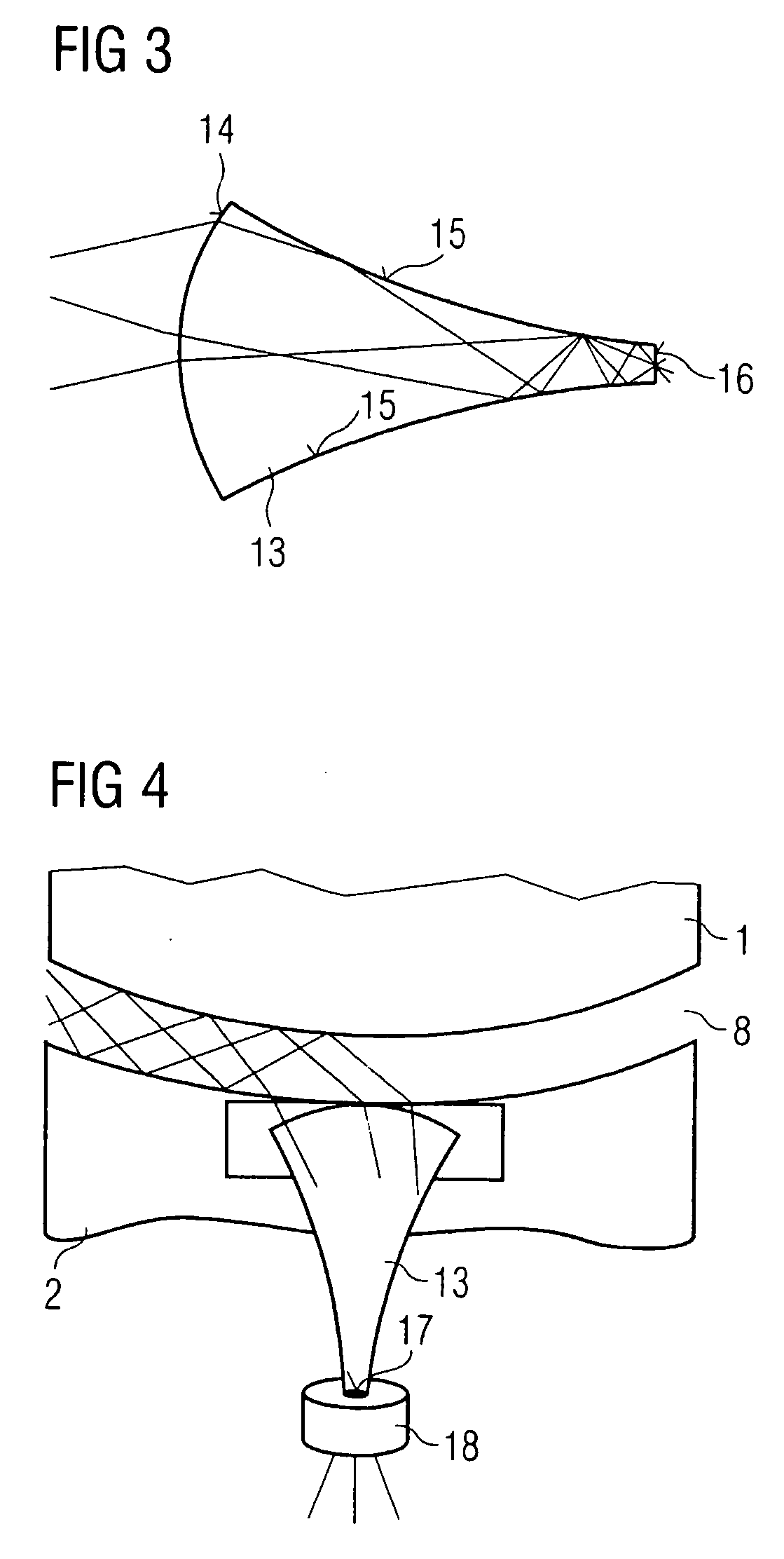

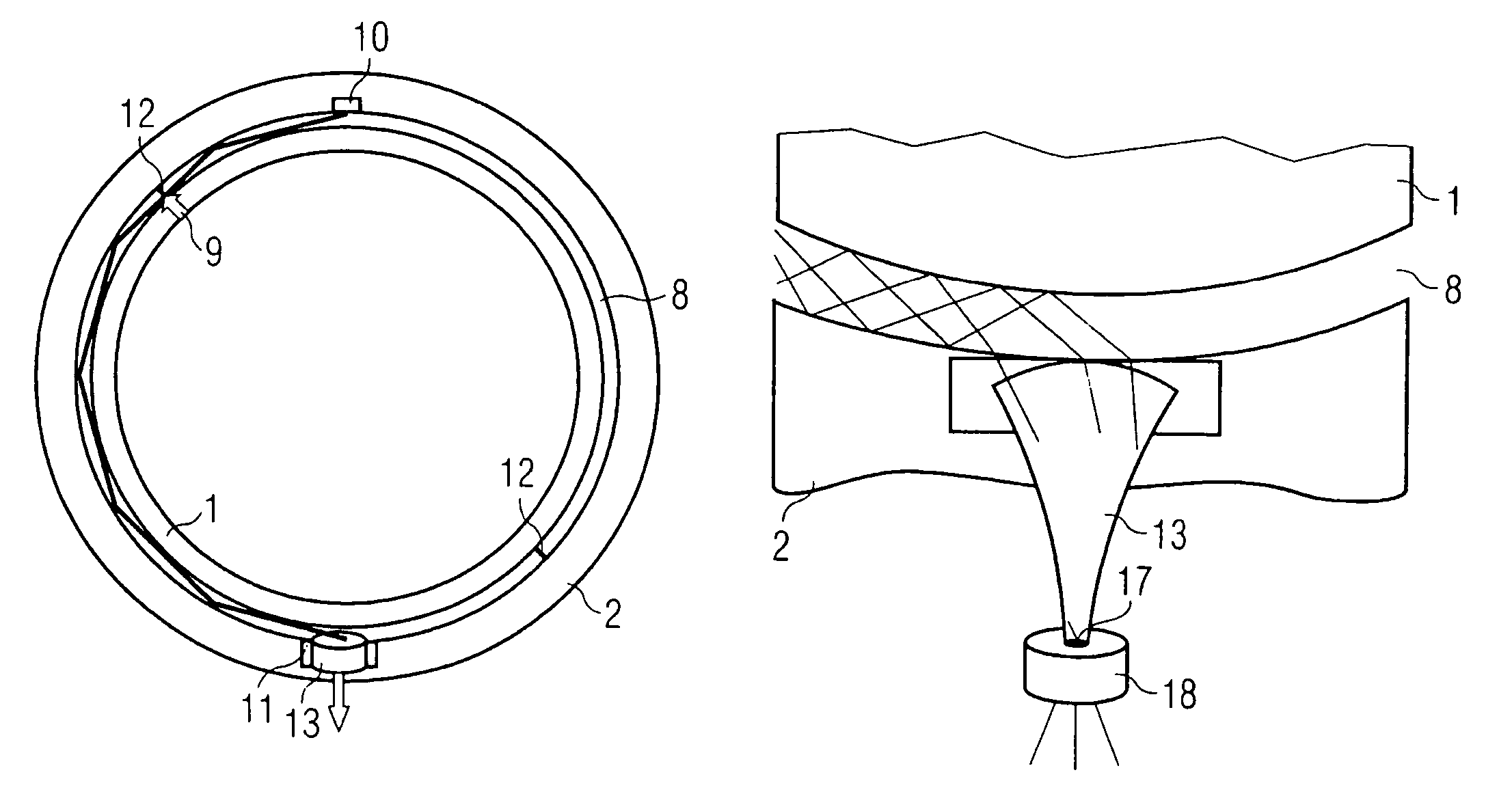

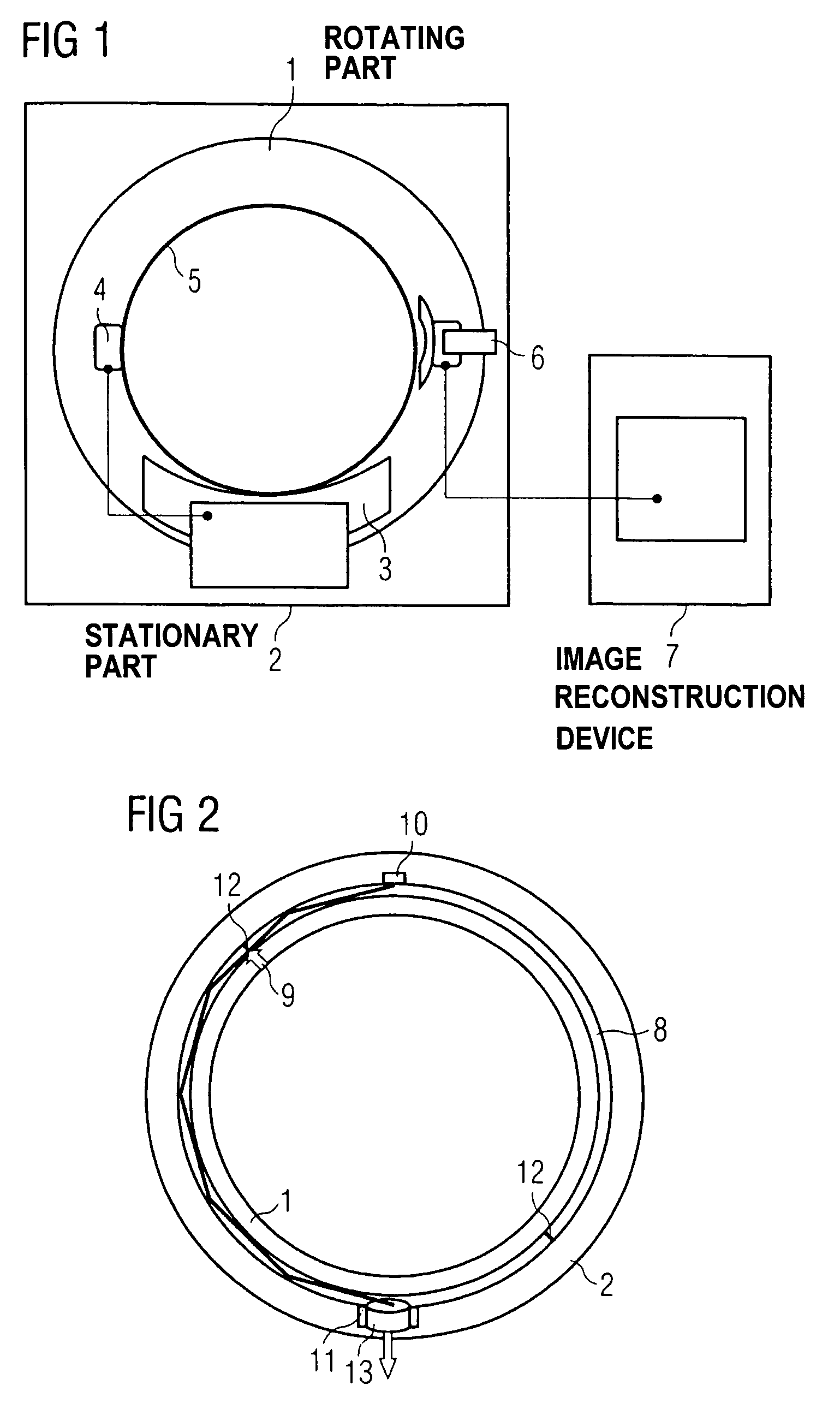

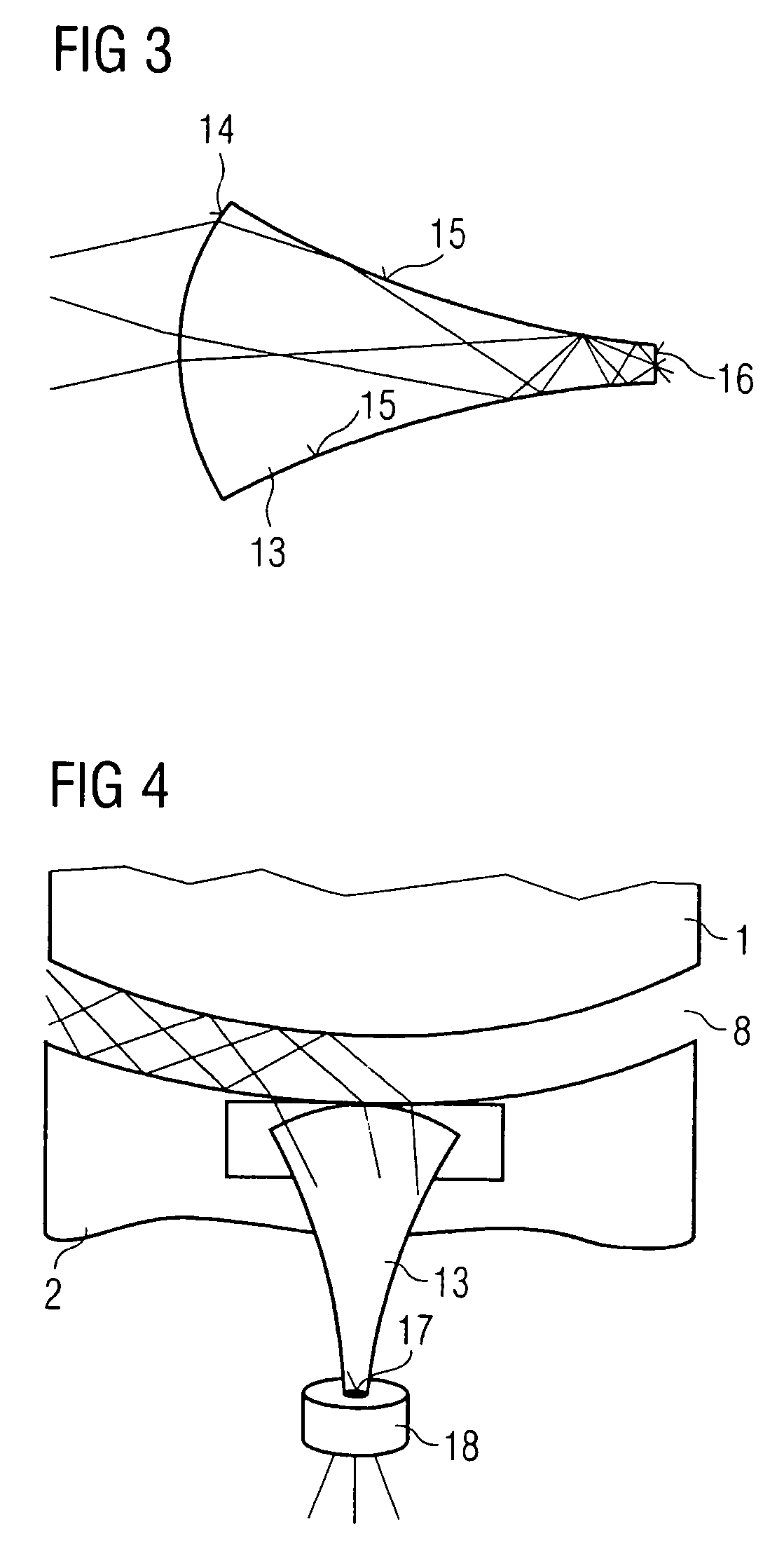

Apparatus to transfer optical signals between a rotating part and a stationary part of a machine

InactiveUS20050013535A1Improve signal-to-noise ratioImprove accuracyRadiation diagnosis data transmissionCladded optical fibreOptical radiationComputed tomography scanner

The present invention concerns an apparatus for transmission of optical signals between a rotating part and a stationary part of a machine, particularly a computer tomograph, in which an optical transmitter is arranged on a first of the two parts and an optical receiver with an optical detector is arranged on a second of the two parts, via which optical signals emitted by the optical transmitter are received, whereby the optical receiver comprises an optical concentrator with an at least approximately horn-shaped geometry that concentrates incident optical radiation via internal reflection on side surfaces of the concentrator onto a detection area of the detector. The optical concentrator is formed from a material filling the entire inner volume of the concentrator and optically transparent for at least one wavelength with which the transmitter transmits. A signal-to-noise ratio improved relative to that of known apparatuses for data transmission can be achieved with the present apparatus.

Owner:SIEMENS HEATHCARE GMBH

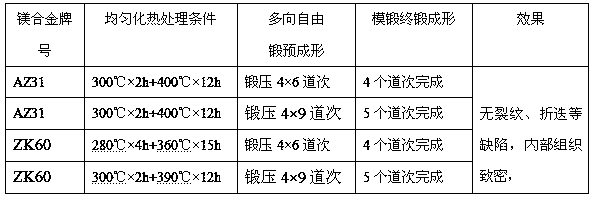

Forging forming method for magnesium alloy rings

The invention relates to a forging forming method for magnesium alloy rings. The method includes the steps of blanking, homogenization treatment of blanks, pretreatment of the blanks and a die before forging, multidirectional free forging performing, die forging and finish forging forming and the like. In order to solve the problems of magnesium alloy ring part forming process complexity, easiness in cracking of forging forming and the like, forged magnesium alloy rings are successfully produced by combining multidirectional free forging performing with die forging and finish forging forming, by means of reasonably selecting technological parameters of forging temperature, press-down rate, deformation and the like, and by mutual linking and matching of processes. Auxiliary processes such as extrusion breakdown and the like are omitted, forming processing of the forged rings can be completed only on one hydraulic press, production efficiency is high, the rings are good in size precision and stability, the produced rings are full in mold filling, free of defects such as cracks, folds and the like, and compact in internal texture.

Owner:CHONGQING UNIV

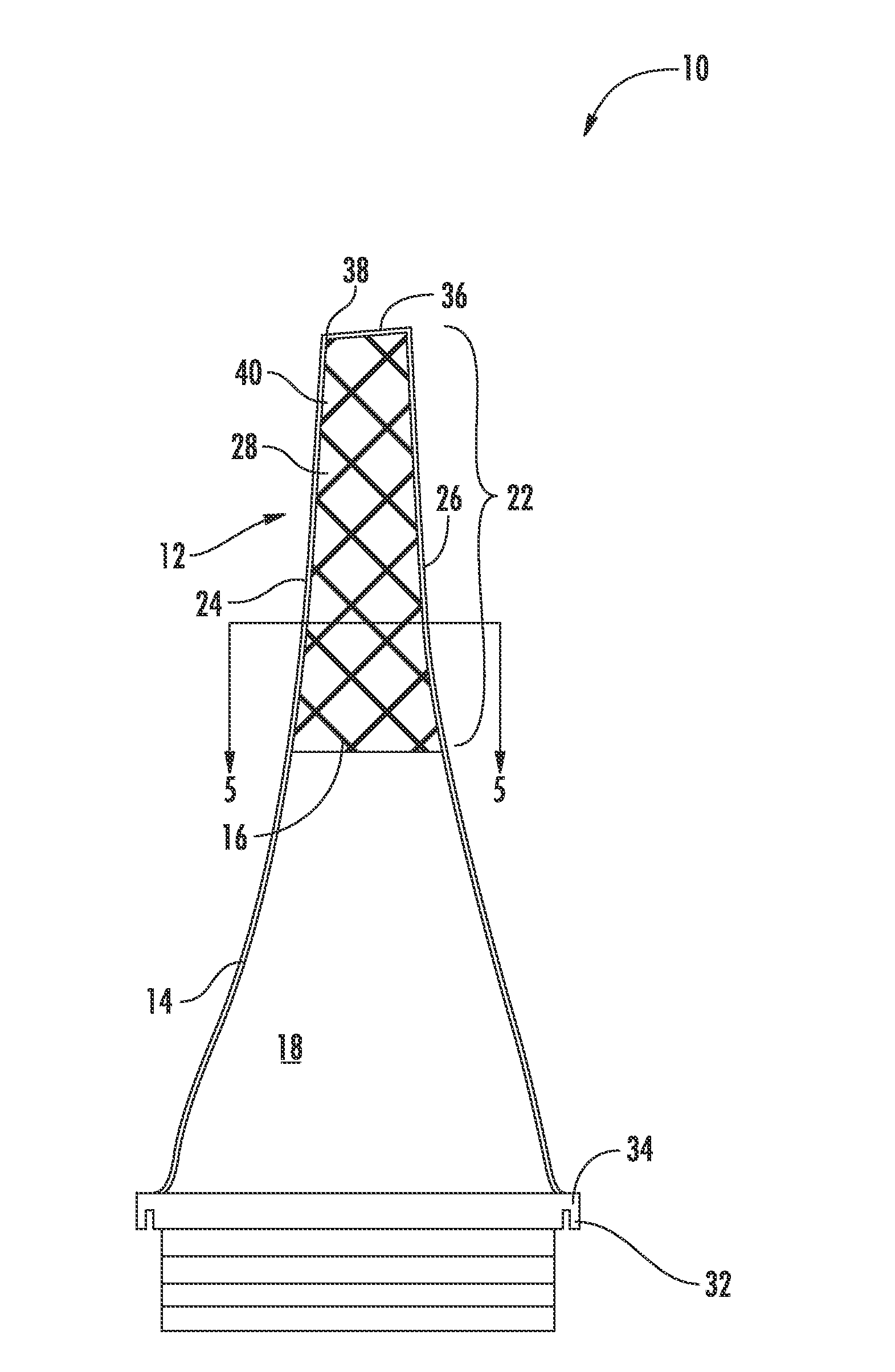

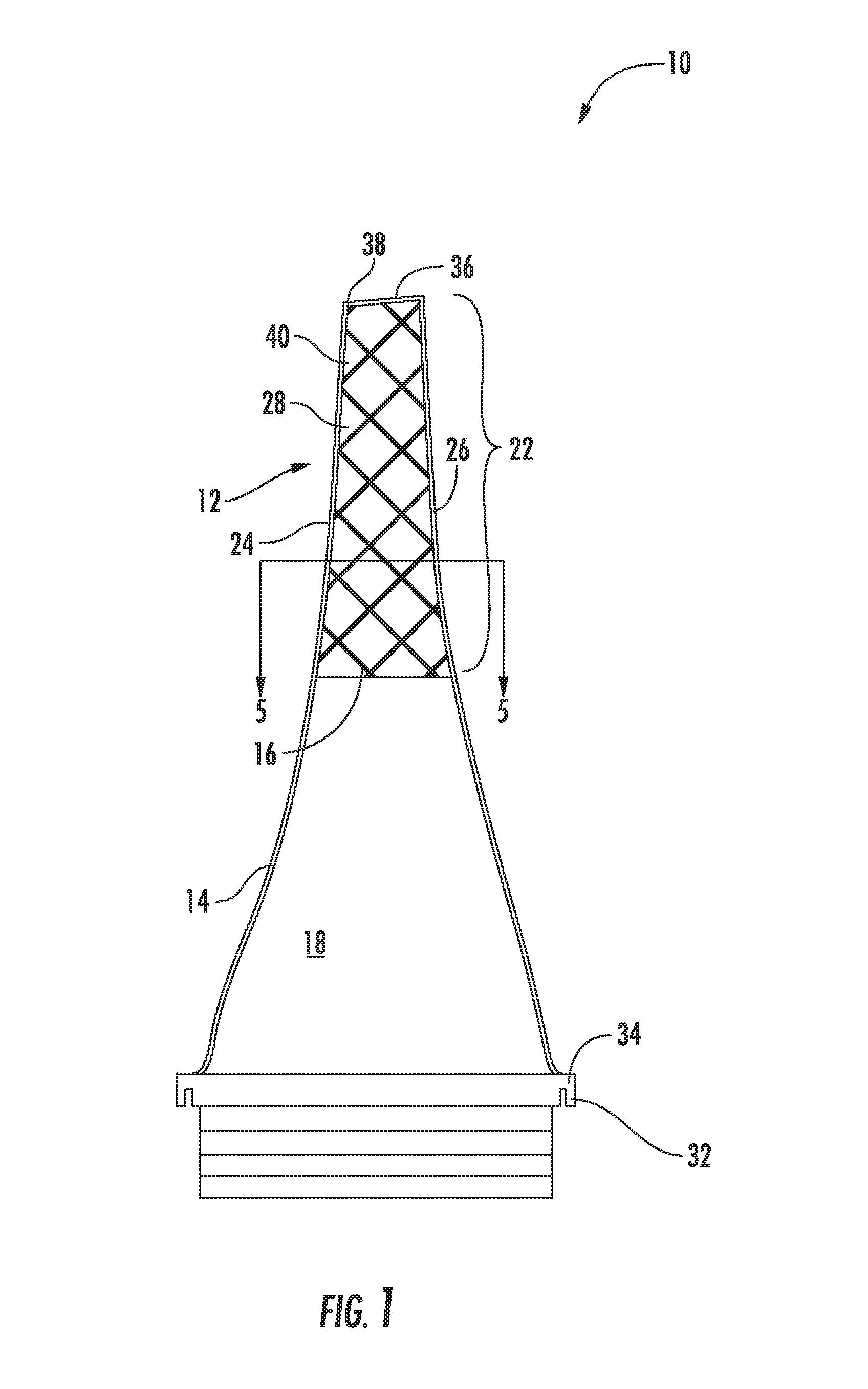

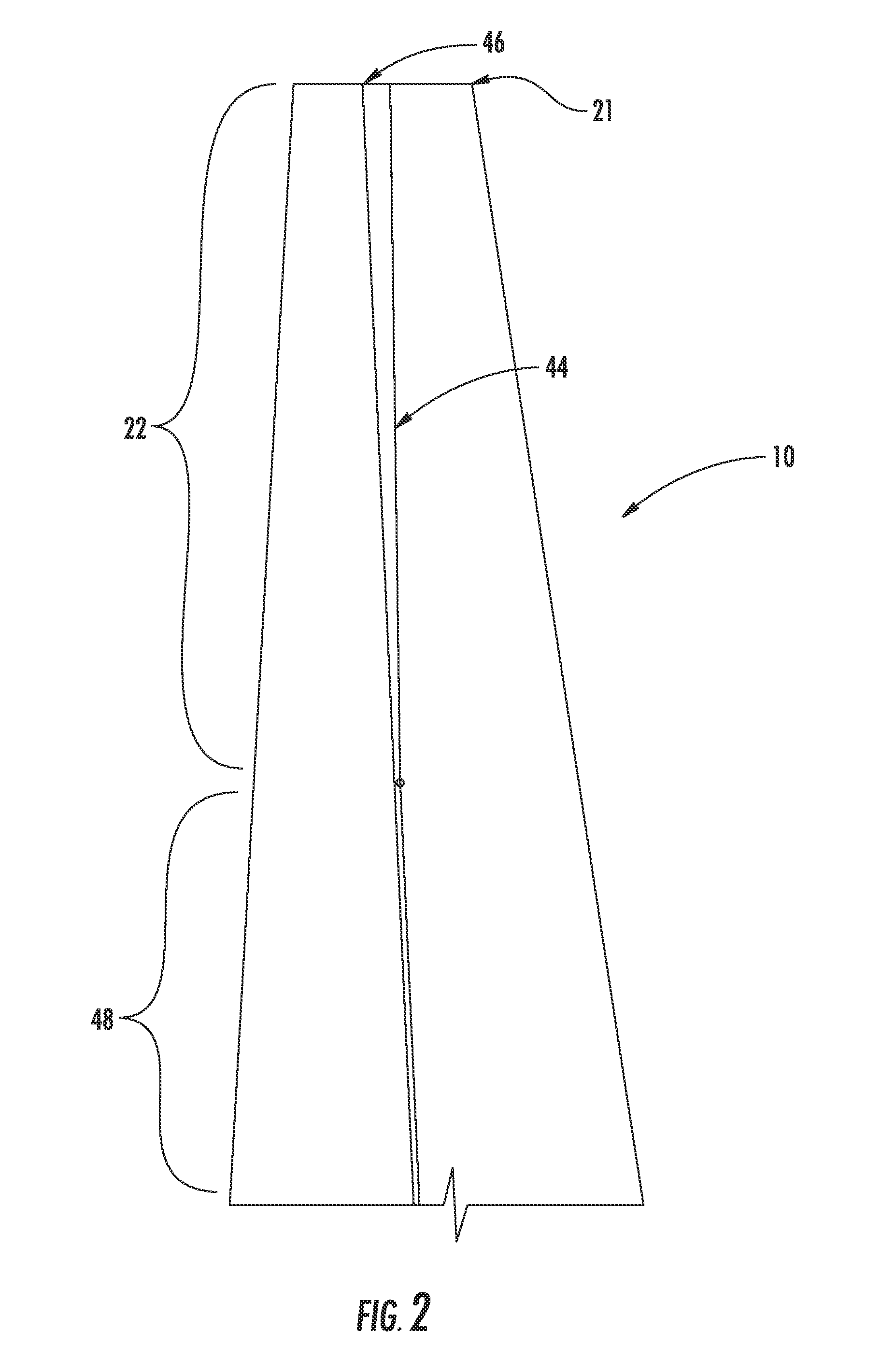

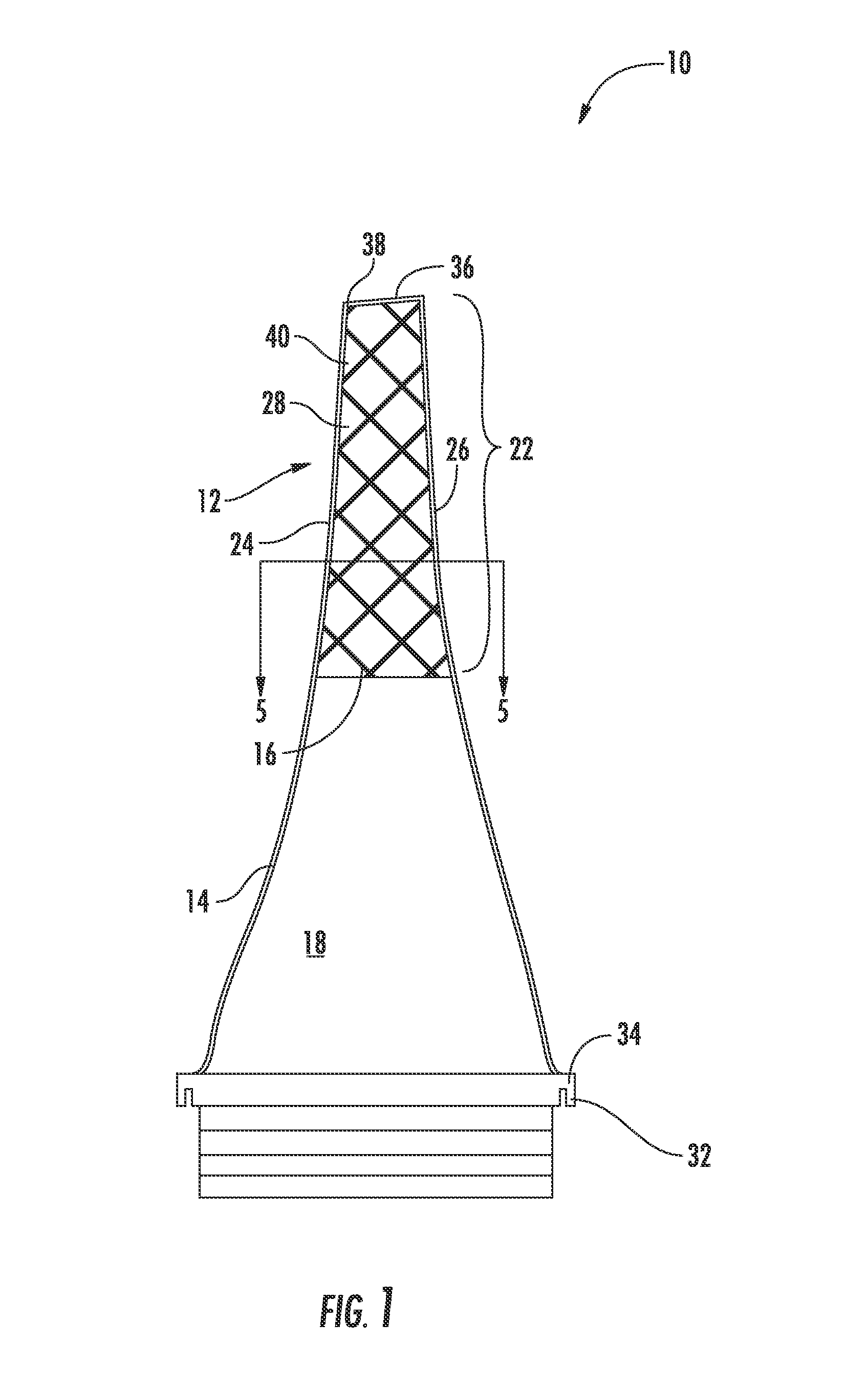

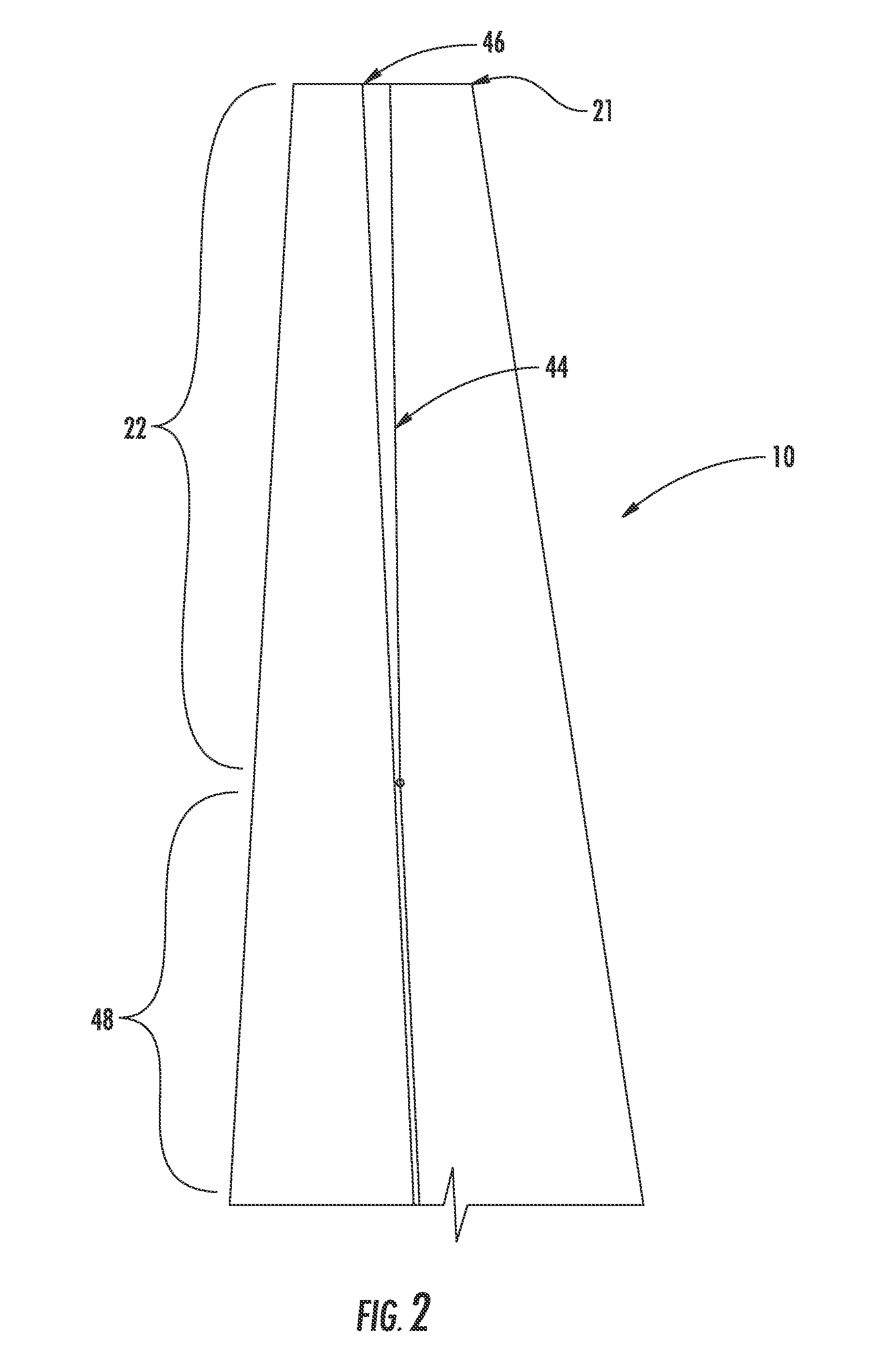

Turbine airfoil with outer wall thickness indicators

InactiveUS20110299990A1Reduce wall thicknessIncreasing structural efficiency of structurePropellersRotary propellersStructural engineeringTurbine

A turbine airfoil usable in a turbine engine and including a depth indicator for determining outer wall blade thickness. The airfoil may include an outer wall having a plurality of grooves in the outer surface of the outer wall. The grooves may have a depth that represents a desired outer surface and wall thickness of the outer wall. The material forming an outer surface of the outer wall may be removed to be flush with an innermost point in each groove, thereby reducing the wall thickness and increasing efficiency. The plurality of grooves may be positioned in a radially outer region of the airfoil proximate to the tip.

Owner:SIEMENS ENERGY INC

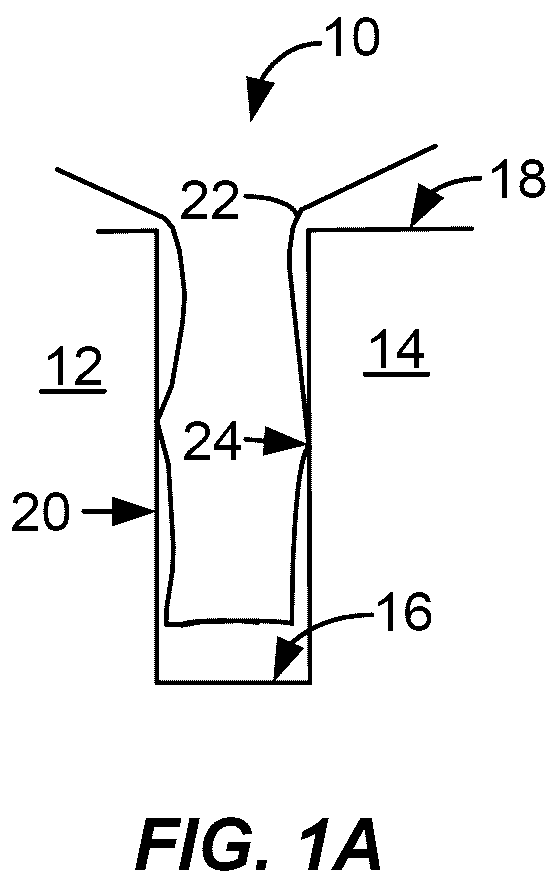

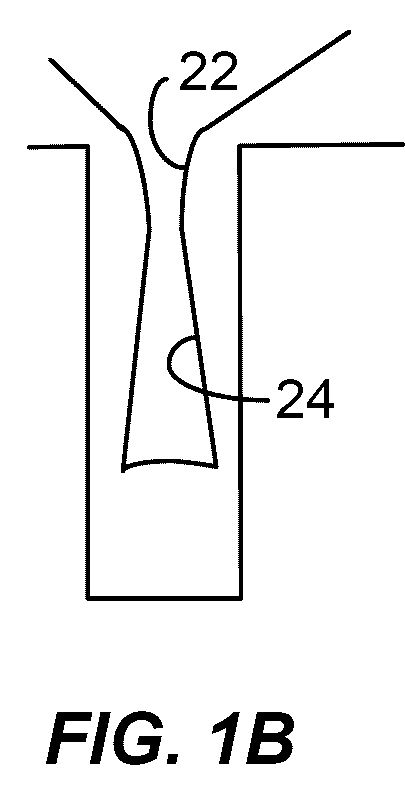

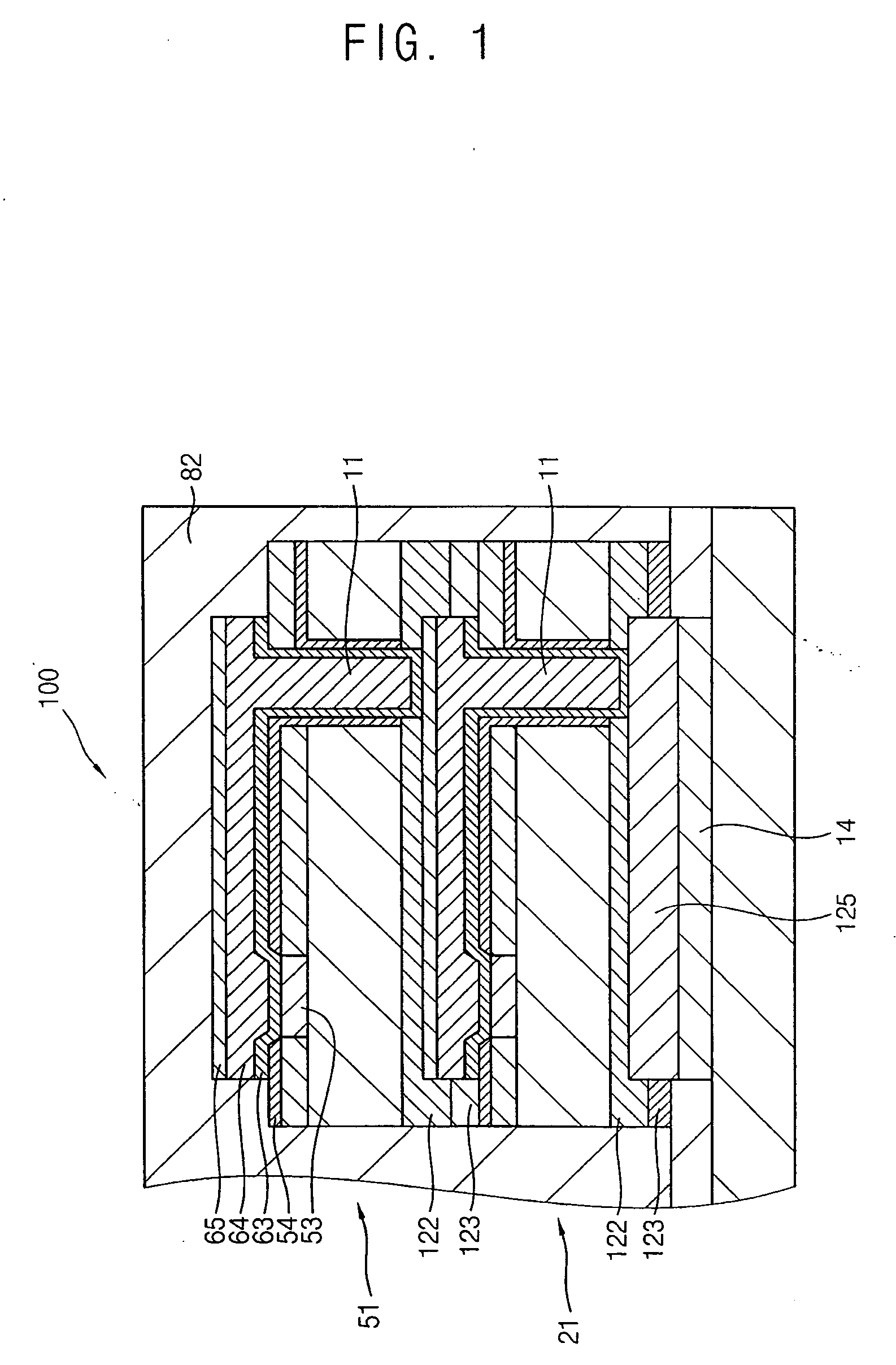

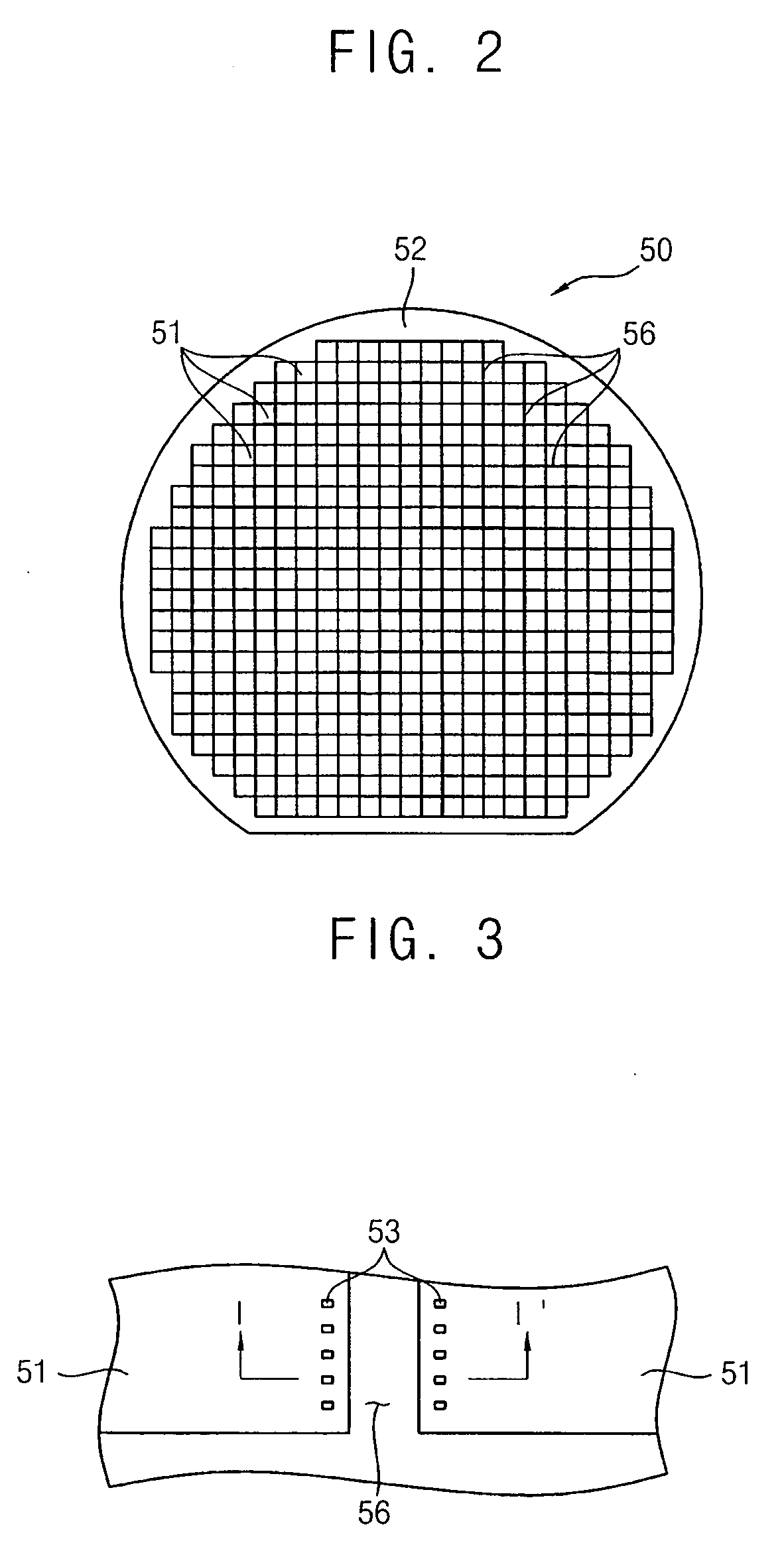

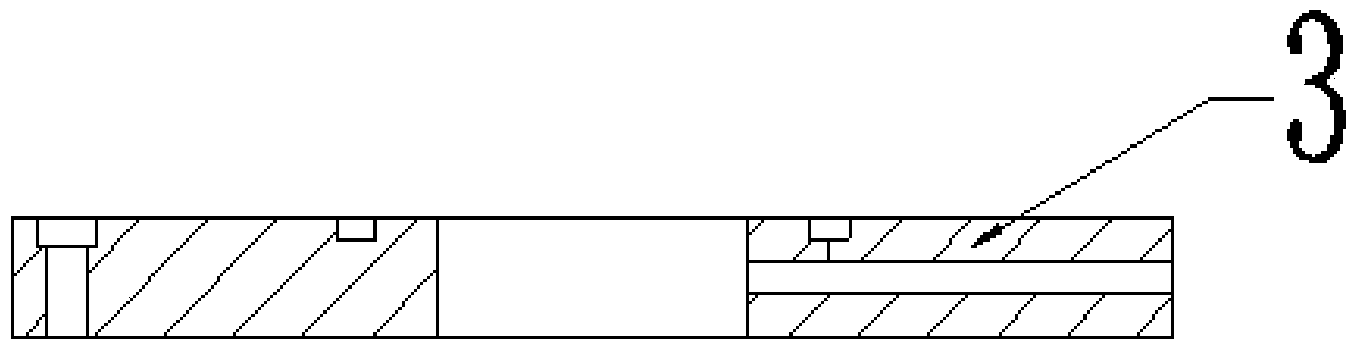

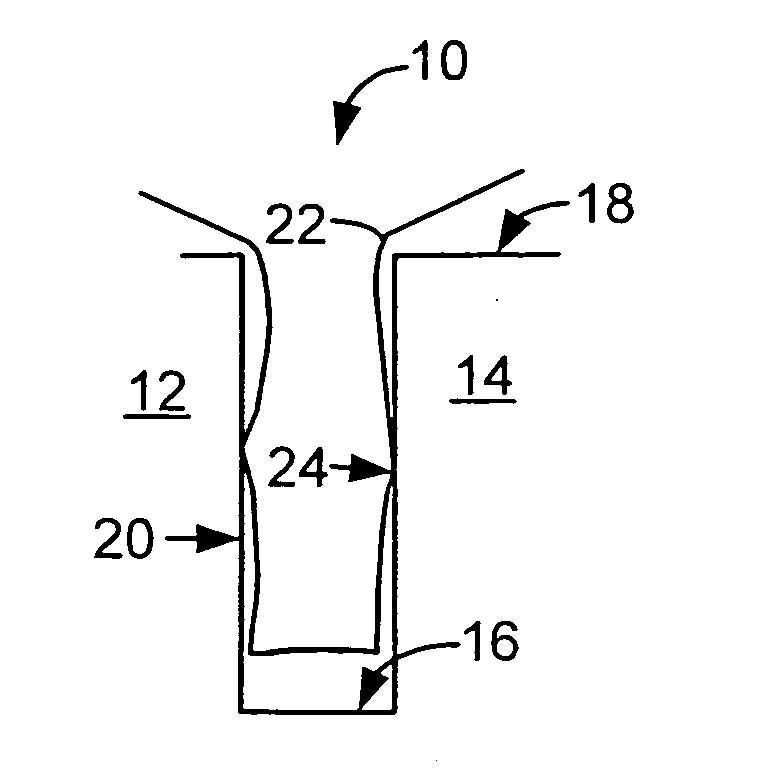

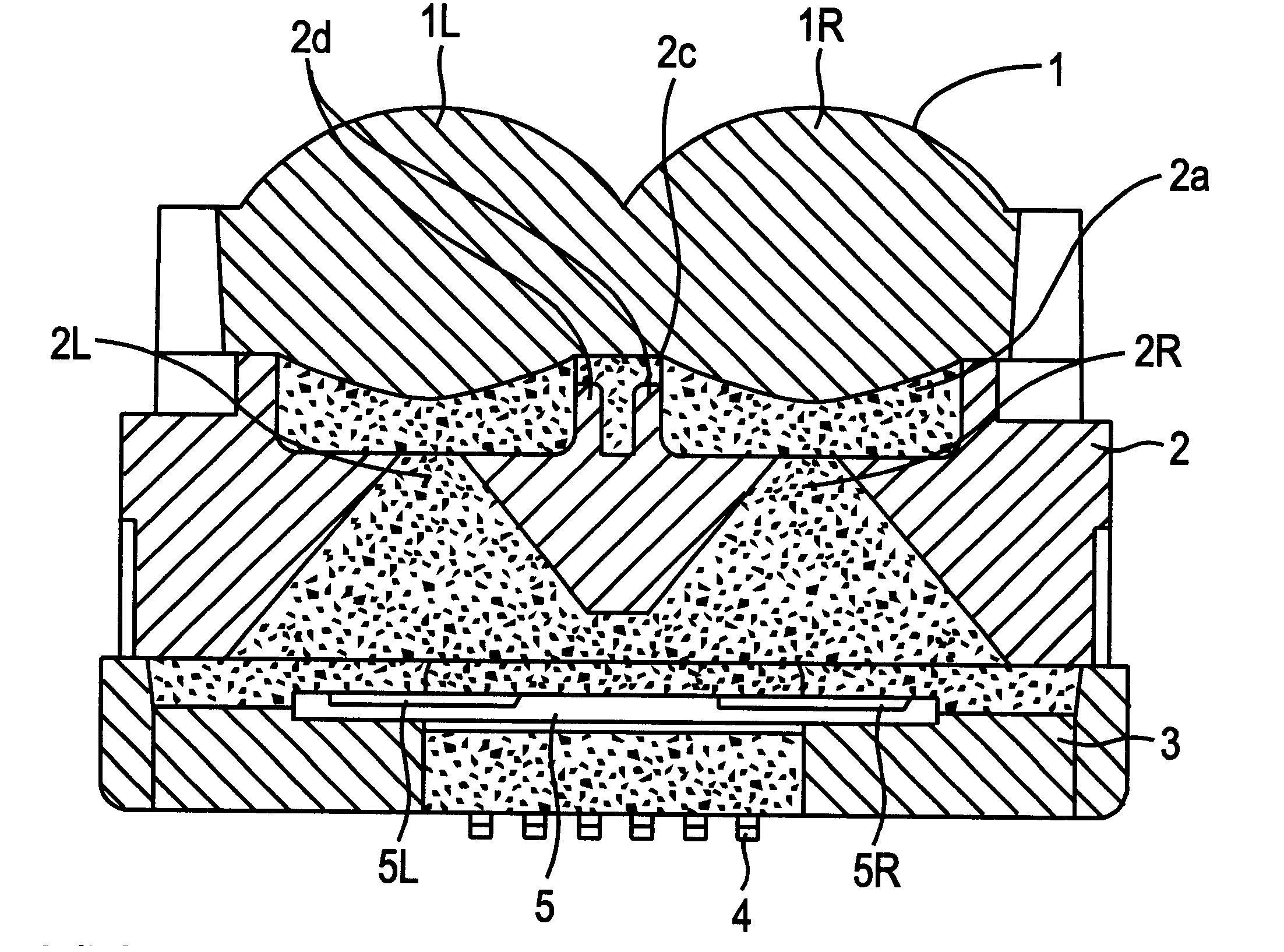

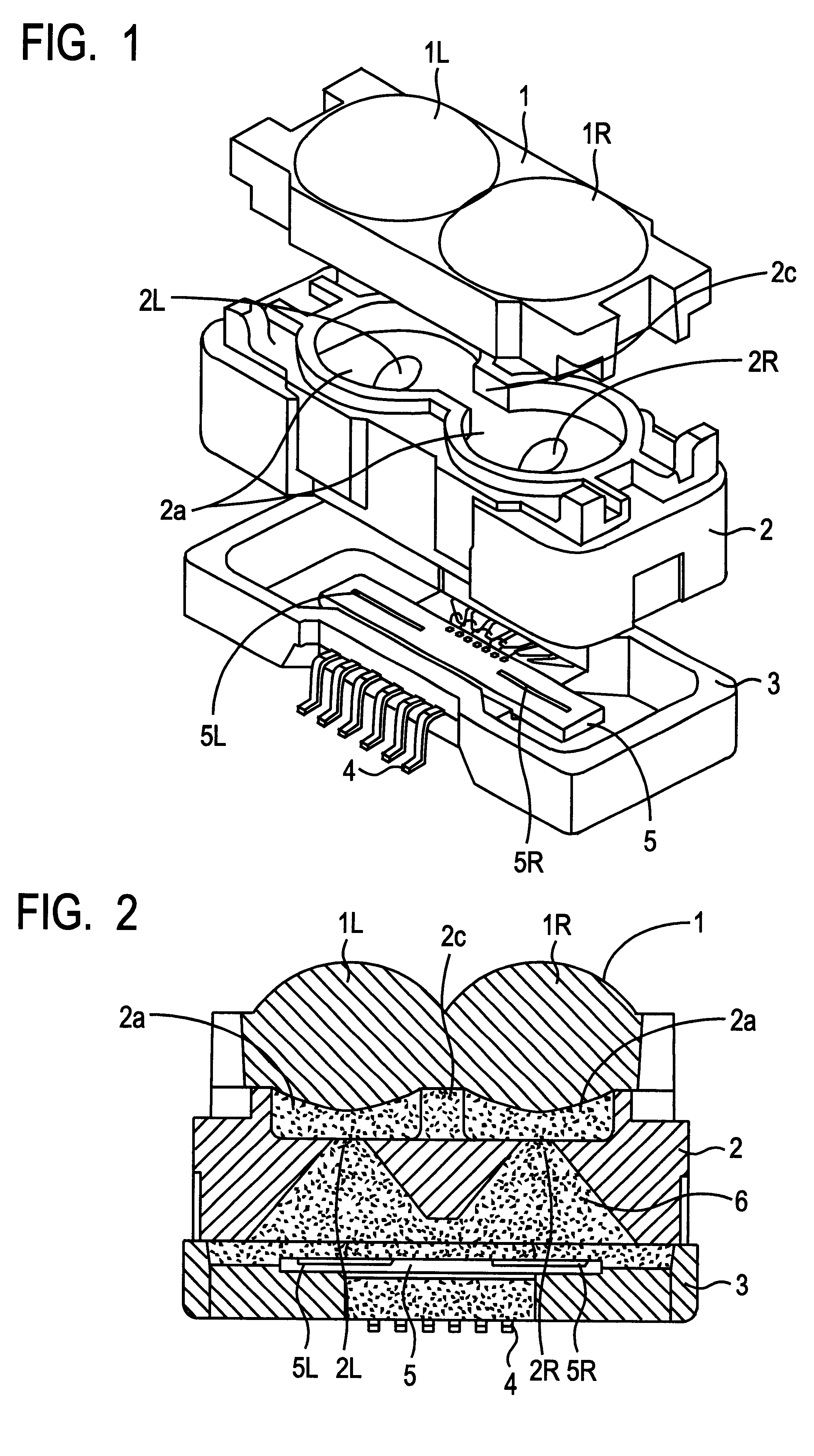

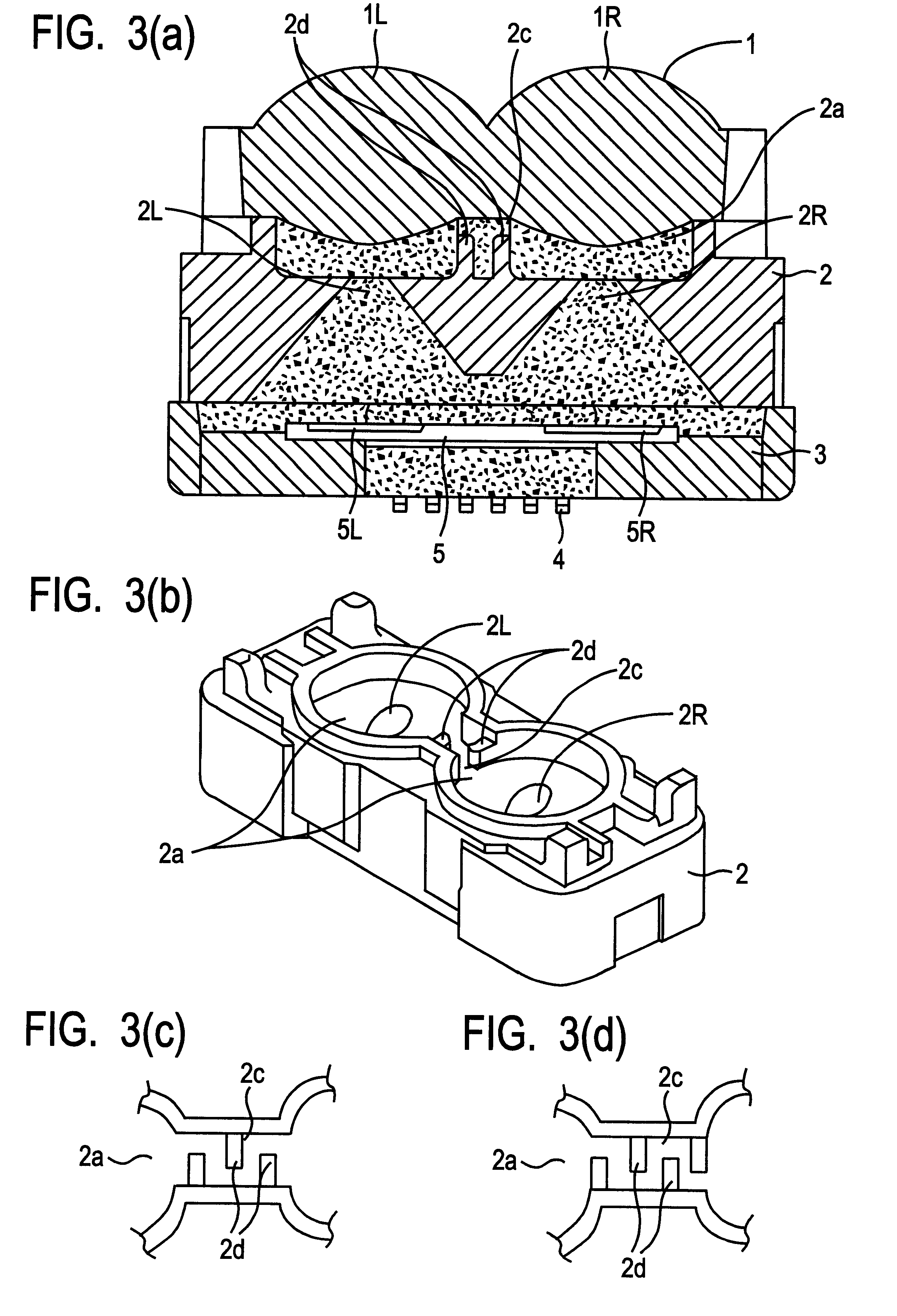

Range finder structure allowing easier filling of the transparent filler

InactiveUS6583433B2Shorten the time periodImprove the level ofOptical rangefindersBeam/ray focussing/reflecting arrangementsLight guideLead frame

A range finder includes an improved module structure, that facilitates injecting a transparent filler uniformly into the entire light guide spaces neither leaving any unfilled region nor impairing the characteristics thereof. A channel of flow (or U-groove) is formed across a partition wall, connecting light guide spaces arranged side by side. This feature allows smooth flow of transparent filler into the range finder module without an unfilled region and consequently no overflow of the transparent filler onto outer wall of the plastic module and onto terminal portion of the lead frame. Another feature of this invention is the presence of shield walls along the channel of flow protruding from the side walls of the channel of flow in an inter-digitated fashion, to prevent the stray light from one light guide space entering the other light guide space through the channel of flow.

Owner:FUJI ELECTRIC CO LTD

Method, apparatus, and processes for producing potable water utilizing reverse osmosis at ocean depth in combination with shipboard moisture dehumidification

InactiveUS20110132842A1Reduce salt contentReduce riskGeneral water supply conservationAuxillariesSaline waterWater source

Devices and methods for producing purified water. The device includes a reverse osmosis subsystem, a dehumidification subsystem and a purified water storage tank fluidly coupled to the subsystems such that purified water produced by each can be locally stored. A vehicular platform, such as a ship, can be used to locate the device adjacent a supply of saline water and humid air. A saline water inlet, membrane and purified water outlet cooperate in the reverse osmosis subsystem to allow preferential passage of water relative to salt in a saline water supply, while the dehumidification subsystem includes a heat exchanger that extracts moisture from the ambient humid air. Purified water produced by each of the subsystems can be used as a potable water source. When used in conjunction with a ship, part or all of the reverse osmosis subsystem can be submersed to a depth sufficient to generate a hydrostatic pressure that is in turn sufficient to passively operate the reverse osmosis membrane such that additional pressurizing equipment, such as a pump, is not needed. Furthermore, the temperature of the water purified by the reverse osmosis subsystem may be low enough to be used as a condensing agent for the ambient humid air passing through the dehumidification subsystem.

Owner:SALYER IVAL O

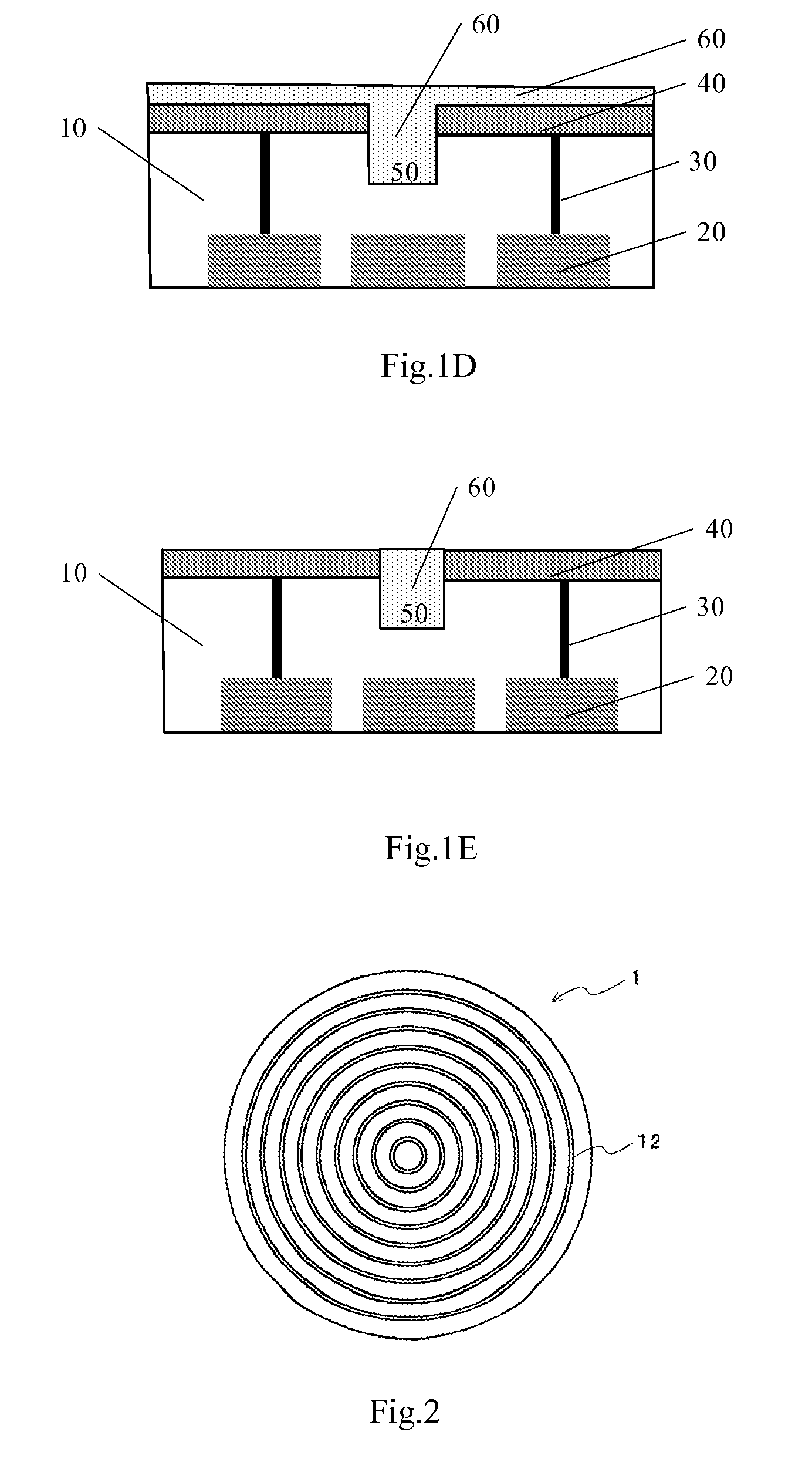

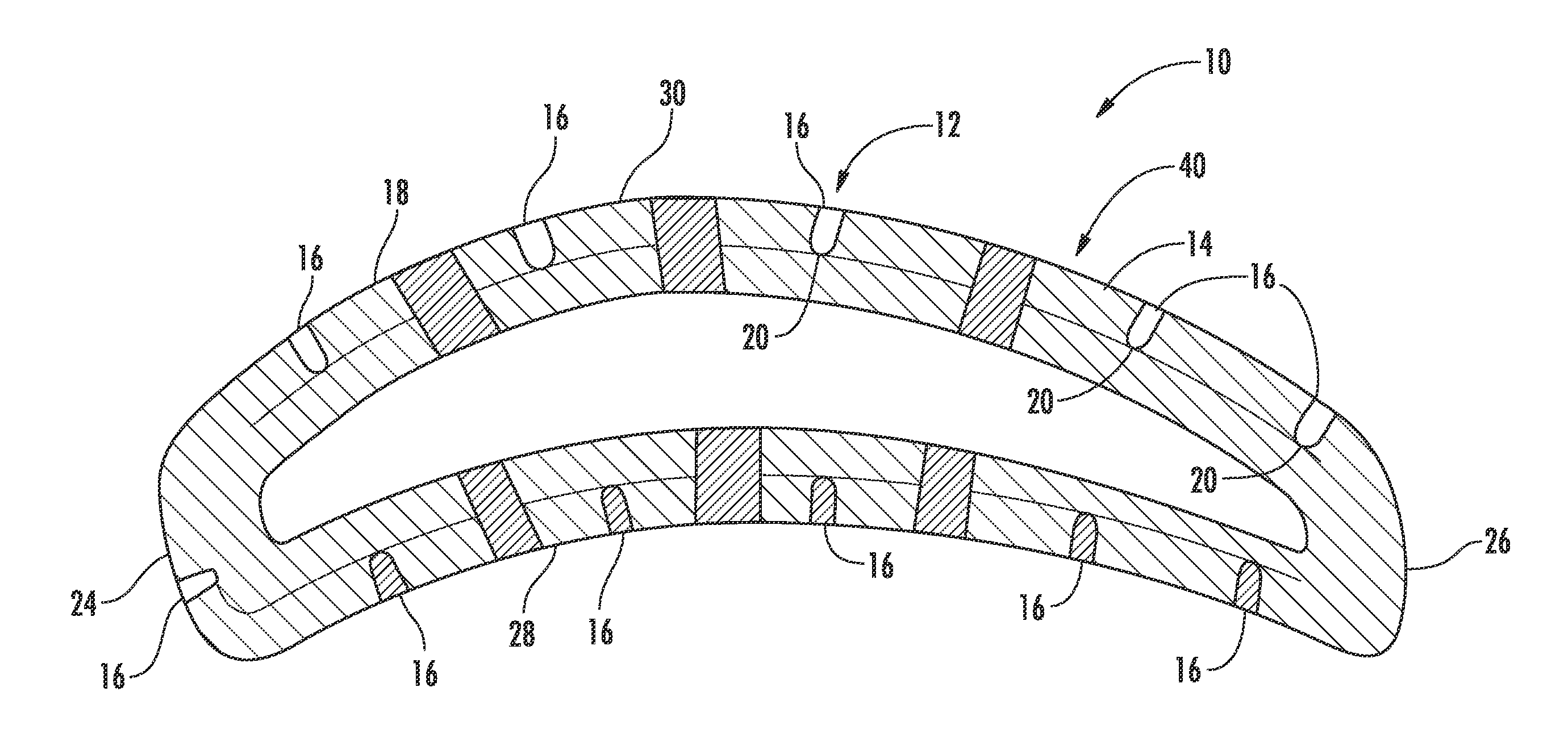

Method for planarization of wafer and method for formation of isolation structure in top metal layer

ActiveUS8058175B2Ensure flatnessImprove display qualityAfter-treatment detailsDecorative surface effectsResistSurface layer

The invention discloses a planarization method for a wafer having a surface layer with a recess, comprises: forming an etching-resist layer on the surface layer to fill the entire recess; etching the etching-resist layer and the surface layer, till the surface layer outside the recess is flush to or lower than the bottom of the recess, the etching speed of the surface layer being higher than that of the etching-resist layer; removing the etching-resist layer; and etching the surface layer to a predetermined depth. The method can avoid concentric ring recesses on the surface of the wafer resulted from a chemical mechanical polishing (CMP) process in the prior art, and can be used to obtain a wafer surface suitable for optical applications.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Baths, methods, and tools for superconformal deposition of conductive materials other than copper

InactiveUS20050092616A1Increase productivityHigh yieldCellsConductive materialEndcappingCarboxylic salt

Superconformal deposition promoters are used to facilitate the superconformal deposition of conductive metals other than copper. Features deposited using the baths, methods, and tools that employ the superconformal deposition promoters are void free. The superconformal deposition promoters include sulfonate terminated alkanethiols, sulfonic acid terminated alkanethiols, carboxylate terminated alkanethiols, carboxylic acid terminated alkanethiols, and sulfonate terminated alkanedisulfide compounds.

Owner:SEMITOOL INC

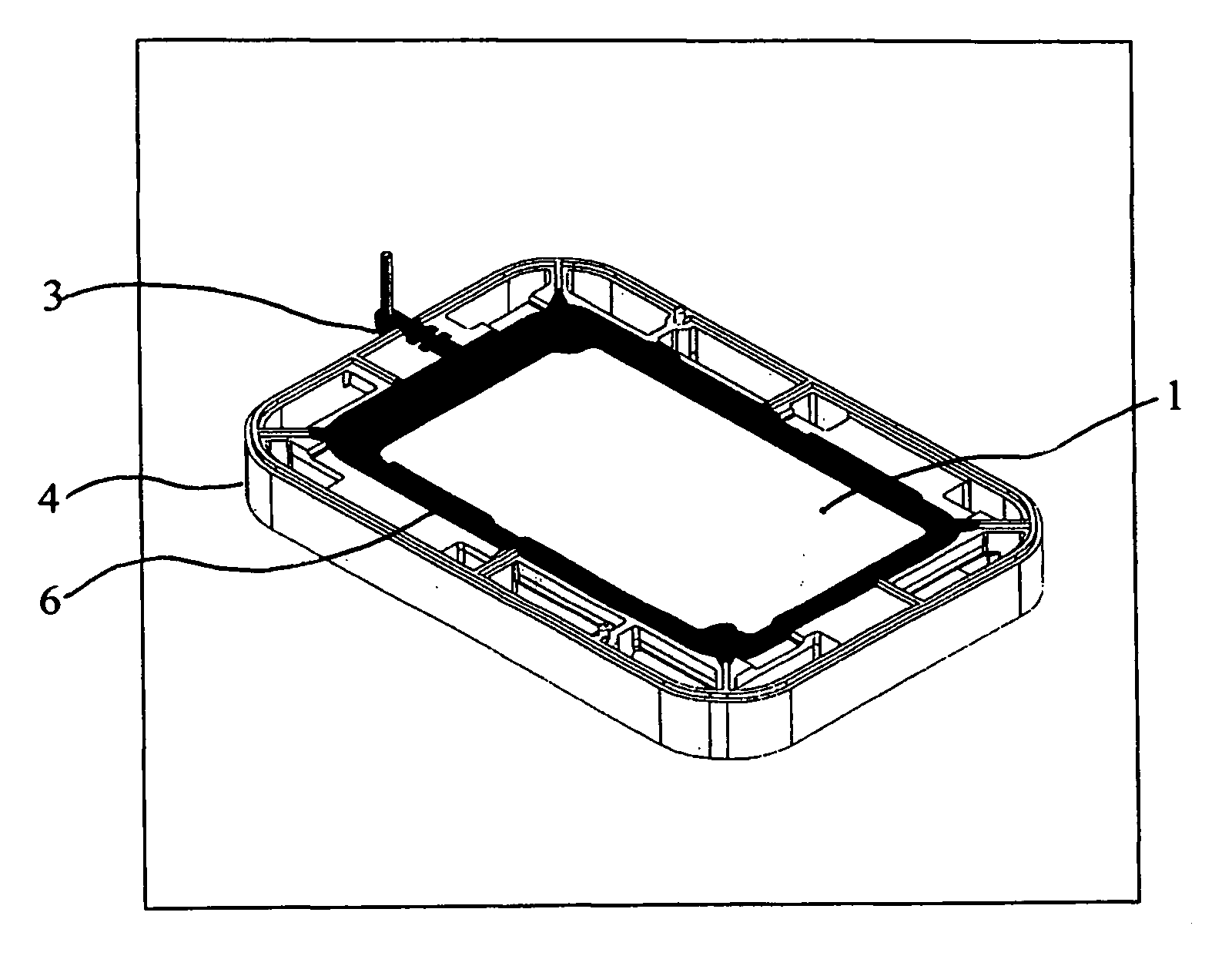

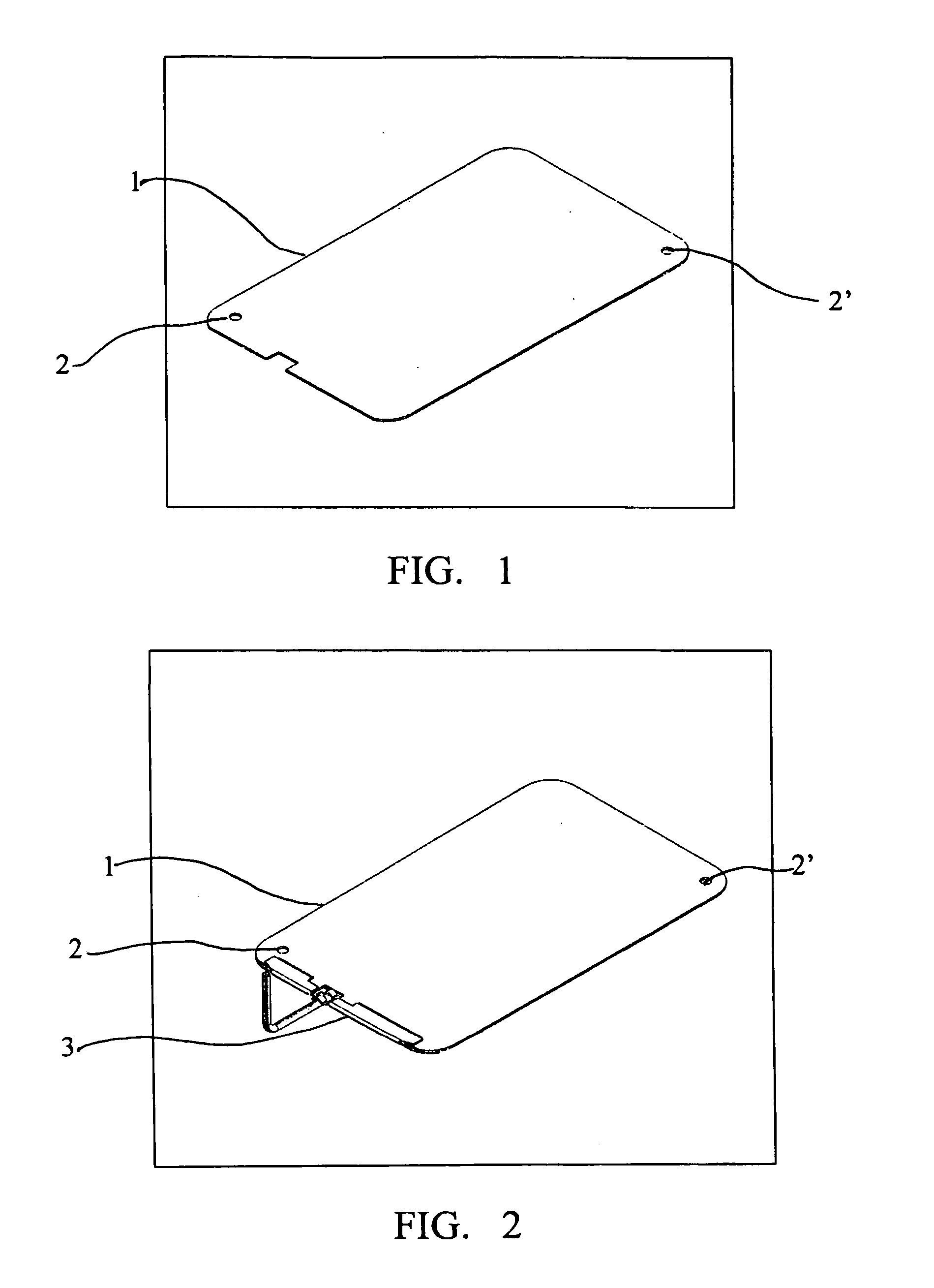

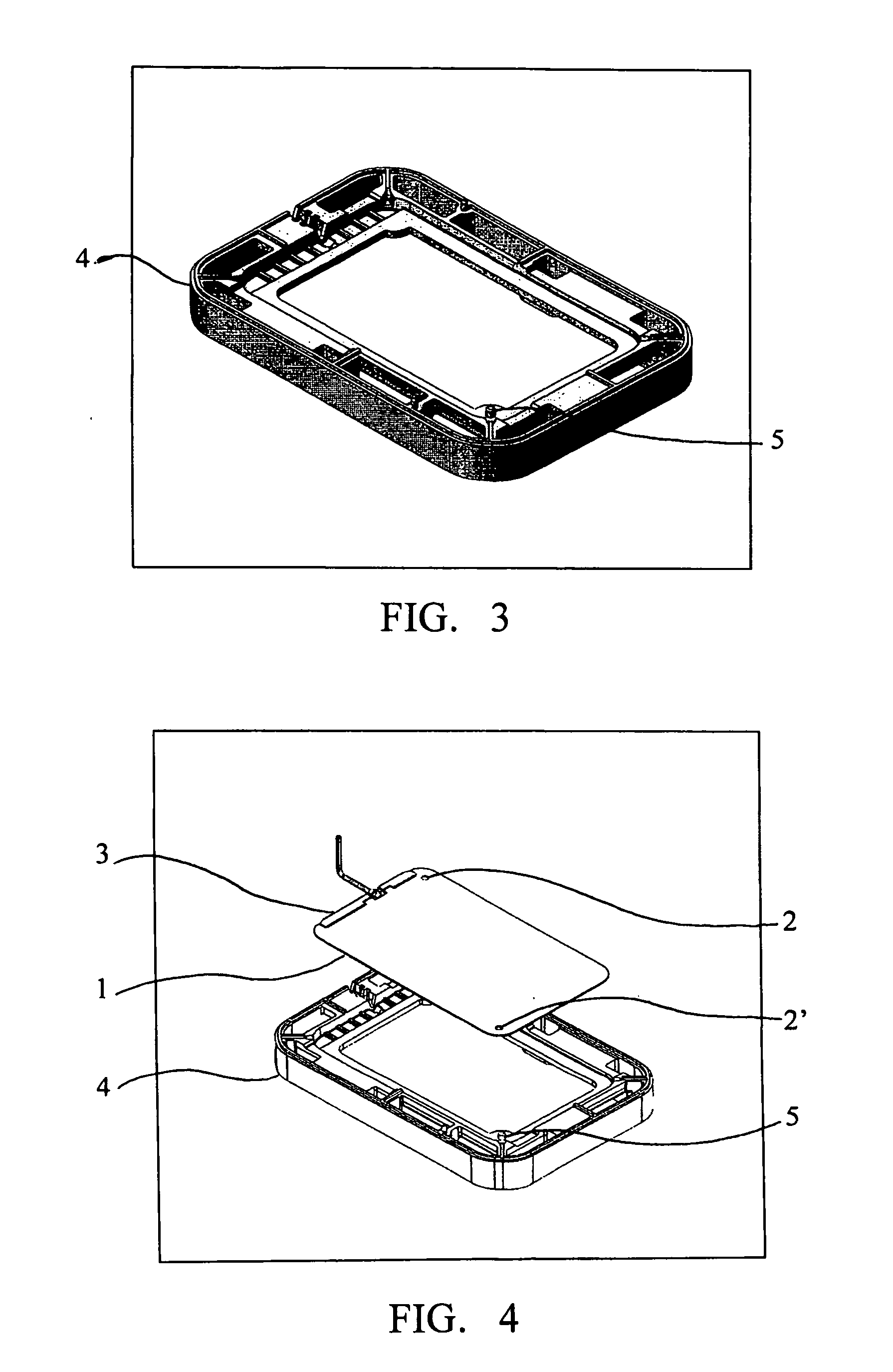

Process for making a framed electrode

InactiveUS20070290404A1Prevent movementComplete fillingFinal product manufactureDomestic articlesEngineeringMechanical engineering

A process for making a framed electrode by injection molding. The process comprises placing a flat piece of electrode material on a shrinkage-free under mold frame and attaching it thereto in a manner which substantially prevents the piece and the frame from moving relative to each other, over molding the resultant assembly by injecting a molten resin into an over molding cavity which contains the assembly, and allowing the resin to solidify. This Abstract is not intended to define the invention disclosed in the specification, nor intended to limit the scope of the invention in any way.

Owner:MORE ENERGY

Casting method of vacuum thin wall

A vacuum casting method for casting thin wall includes such steps as putting mould in a refractory container, making the mould in vacuum condition, surrounding the mould by sufficient molten metal and removing the vacuum condition to fill the molten metal in moulding cavity by atmosphere pressure.

Owner:NANCHANG AERONAUTICAL ENG INST

Apparatus to transfer optical signals between a rotating part and a stationary part of a machine

InactiveUS7043114B2Improve signal-to-noise ratioImprove accuracyRadiation diagnosis data transmissionCladded optical fibreEngineeringLength wave

The present invention concerns an apparatus for transmission of optical signals between a rotating part and a stationary part of a machine, particularly a computer tomograph, in which an optical transmitter is arranged on a first of the two parts and an optical receiver with an optical detector is arranged on a second of the two parts, via which optical signals emitted by the optical transmitter are received, whereby the optical receiver comprises an optical concentrator with an at least approximately horn-shaped geometry that concentrates incident optical radiation via internal reflection on side surfaces of the concentrator onto a detection area of the detector. The optical concentrator is formed from a material filling the entire inner volume of the concentrator and optically transparent for at least one wavelength with which the transmitter transmits. A signal-to-noise ratio improved relative to that of known apparatuses for data transmission can be achieved with the present apparatus.

Owner:SIEMENS HEALTHCARE GMBH

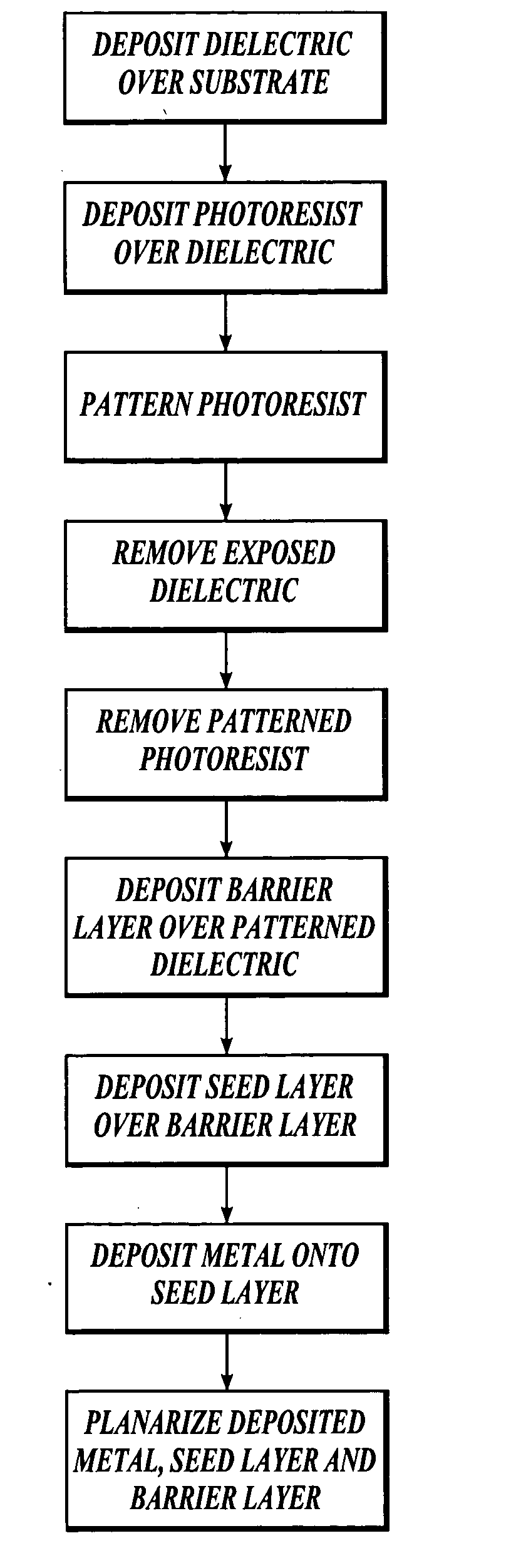

Metal wiring of a semiconductor device and method of forming the same

InactiveUS20090065940A1Reduce processing difficultyComplete fillingSemiconductor/solid-state device detailsSolid-state devicesInsulation layerEngineering

According to a method of forming a metal wiring of a semiconductor device, a contact plug is formed at height lower than the contact hole, which is formed on an interlayer insulation layer, and then a metal wiring is formed over the contact plug and interlayer insulation layer to completely fill inside of the contact hole, decreasing process difficulty, ensuring reproducibility, and improving electrical property.

Owner:SK HYNIX INC

Turbine airfoil with outer wall thickness indicators

InactiveUS8500411B2Reduce wall thicknessSimple structurePropellersPump componentsStructural engineeringEngineering

A turbine airfoil usable in a turbine engine and including a depth indicator for determining outer wall blade thickness. The airfoil may include an outer wall having a plurality of grooves in the outer surface of the outer wall. The grooves may have a depth that represents a desired outer surface and wall thickness of the outer wall. The material forming an outer surface of the outer wall may be removed to be flush with an innermost point in each groove, thereby reducing the wall thickness and increasing efficiency. The plurality of grooves may be positioned in a radially outer region of the airfoil proximate to the tip.

Owner:SIEMENS ENERGY INC

Method, apparatus, and processes for producing potable water utilizing reverse osmosis at ocean depth in combination with shipboard moisture dehumidification

InactiveUS20090236286A1Obstruct passageGreat advantageAuxillariesGeneral water supply conservationSaline waterWater storage tank

Devices and methods for producing purified water. The device includes a reverse osmosis subsystem, a dehumidification subsystem and a purified water storage tank fluidly coupled to the subsystems such that purified water produced by each can be locally stored. A vehicular platform, such as a ship, can be used to locate the device adjacent a supply of saline water and humid air. A saline water inlet, membrane and purified water outlet cooperate in the reverse osmosis subsystem to allow preferential passage of water relative to salt in a saline water supply, while the dehumidification subsystem includes a heat exchanger that extracts moisture from the ambient humid air. Purified water produced by each of the subsystems can be used as a potable water source. When used in conjunction with a ship, part or all of the reverse osmosis subsystem can be submersed to a depth sufficient to generate a hydrostatic pressure that is in turn sufficient to passively operate the reverse osmosis membrane such that additional pressurizing equipment, such as a pump, is not needed. Furthermore, the temperature of the water purified by the reverse osmosis subsystem may be low enough to be used as a condensing agent for the ambient humid air passing through the dehumidification subsystem.

Owner:SALYER IVAL O