Method for manufacturing double-sided PERC high-efficiency crystalline silicon solar cell

A solar cell and manufacturing method technology, which is applied to circuits, photovoltaic power generation, electrical components, etc., can solve the problems of increased production cost, low battery utilization rate, inability to achieve work efficiency, etc., and achieves reduced manufacturing cost, convenient operation, and improved open circuit. The effect of voltage Uoc

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0048] This embodiment provides a method for manufacturing a double-sided PERC high-efficiency crystalline silicon solar cell. The method is suitable for the manufacture of all P-type double-sided PERC high-efficiency crystalline silicon solar cells and includes the following steps:

[0049] (1) The crystalline silicon is textured in advance, and the surface reflectivity of the silicon wafer is controlled at 11% after texturing;

[0050] (2) Diffusion: crystalline silicon diffuses, and the diffusion resistance is 90Ω / □;

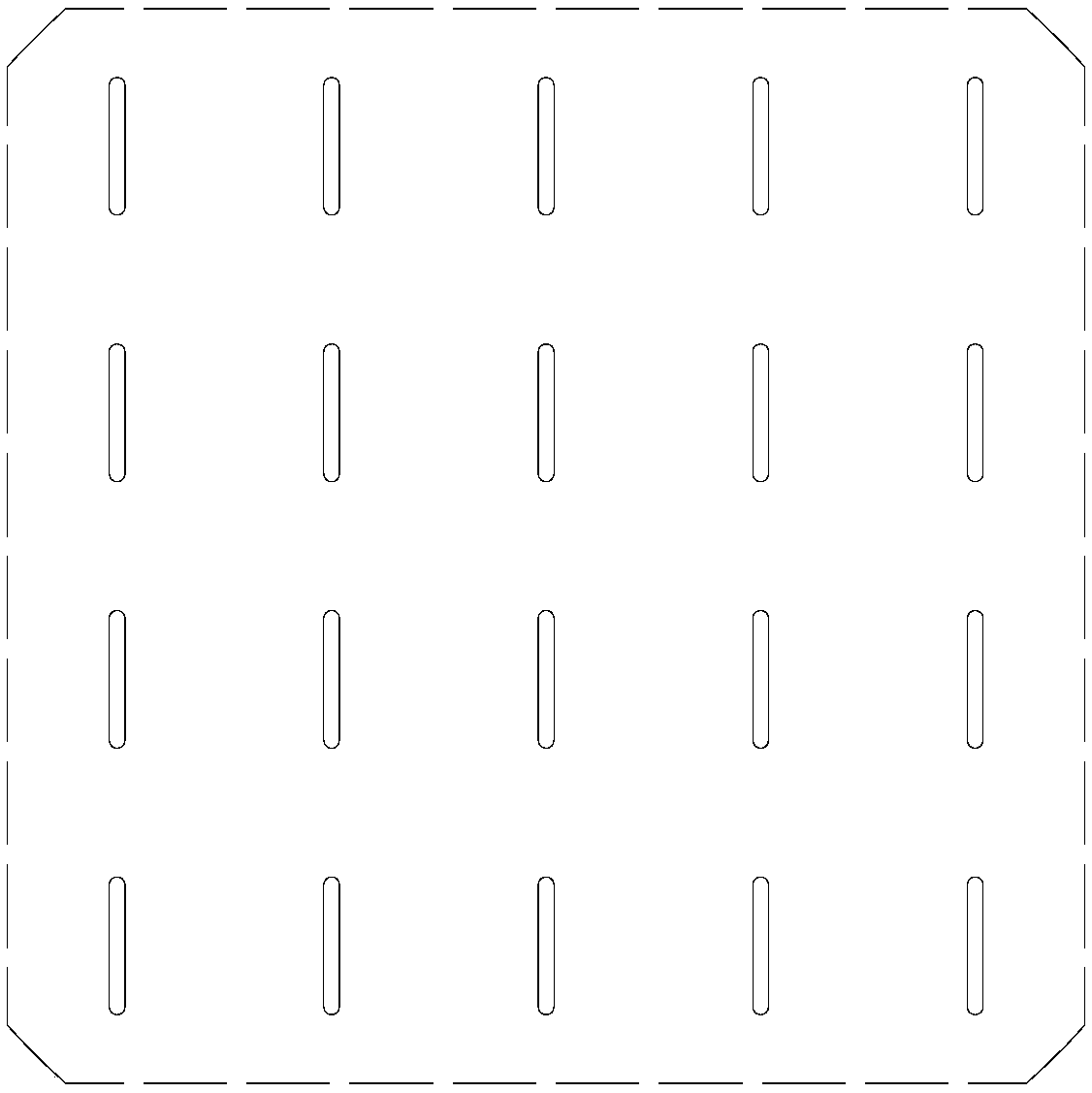

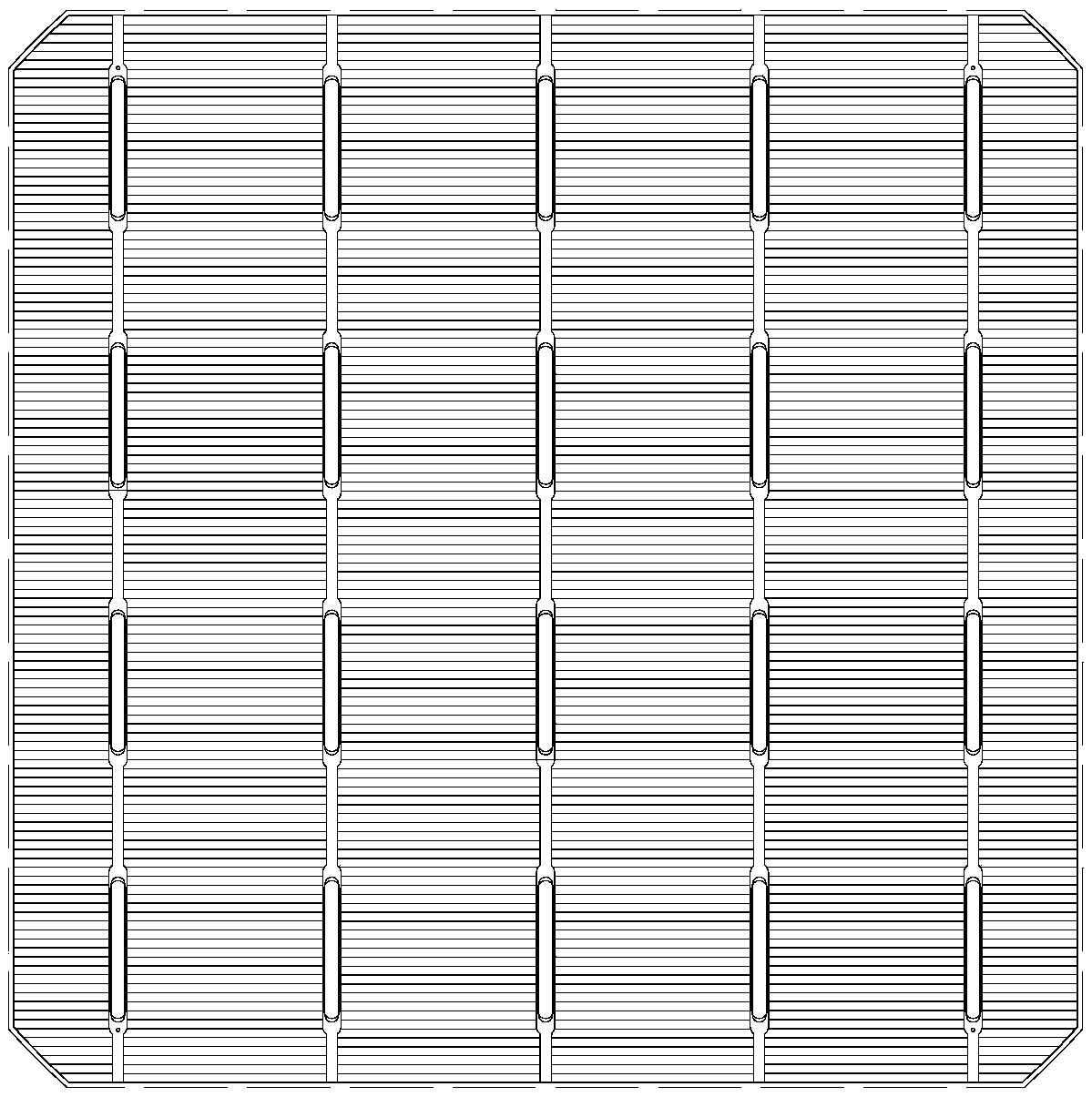

[0051] (3) Laser doping: Laser doping the diffused crystalline silicon to form the corresponding N++ layer. The line width of the secondary gate line in the laser doped area is 70μm, and the number is 108; the main gate line is perpendicular to the secondary gate Line, the width of a single main grid line is 0.7mm;

[0052] (4) Etching: After removing the diffused borophosphosilicate glass, the back reflectivity is controlled at 25%;

[0053] (5) Back passivation: pro...

Embodiment 2

[0058] This embodiment provides a method for manufacturing a double-sided PERC high-efficiency crystalline silicon solar cell. The method is suitable for the manufacture of all P-type double-sided PERC high-efficiency crystalline silicon solar cells and includes the following steps:

[0059] (1) The crystalline silicon is textured in advance, and the surface reflectance of the silicon wafer is controlled at 15% after texturing;

[0060] (2) Diffusion: crystalline silicon diffuses, and the diffusion resistance is 100Ω / □;

[0061] (3) Laser doping: laser doping the diffused crystalline silicon to form the corresponding N++ layer. The line width of the secondary gate line in the laser doped area is 90μm, and the number of lines is 108; the main gate line is perpendicular to the secondary gate Line, the width of a single main grid line is 0.7mm;

[0062] (4) Etching: After removing the diffused borophosphosilicate glass, the back reflectivity is controlled at 28%;

[0063] (5) Back passiva...

Embodiment 3

[0068] This embodiment provides a method for manufacturing a double-sided PERC high-efficiency crystalline silicon solar cell. The method is suitable for the manufacture of all P-type double-sided PERC high-efficiency crystalline silicon solar cells and includes the following steps:

[0069] (1) The crystalline silicon is textured in advance, and the surface reflectance of the silicon wafer is controlled at 13% after texturing;

[0070] (2) Diffusion: crystalline silicon diffuses, and the diffusion resistance is 95Ω / □;

[0071] (3) Laser doping: Laser doping the diffused crystalline silicon to form the corresponding N++ layer. The line width of the secondary gate line in the laser doped area is 80μm, and the number of lines is 108; the main gate line is perpendicular to the secondary gate Line, the width of a single main grid line is 0.7mm;

[0072] (4) Etching: After removing the diffused borophosphosilicate glass, the back reflectivity is controlled at 26%;

[0073] (5) Back passivat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More