Method of forming a transistor having multiple channels

a transistor and channel technology, applied in the field of semiconductor devices, can solve the problems of unfavorable leakage current (i.e. electron or hole flow) between the source and drain, requires significant additional area, and does not offer as much manufacturing control lithographically or spacer defined dimensions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

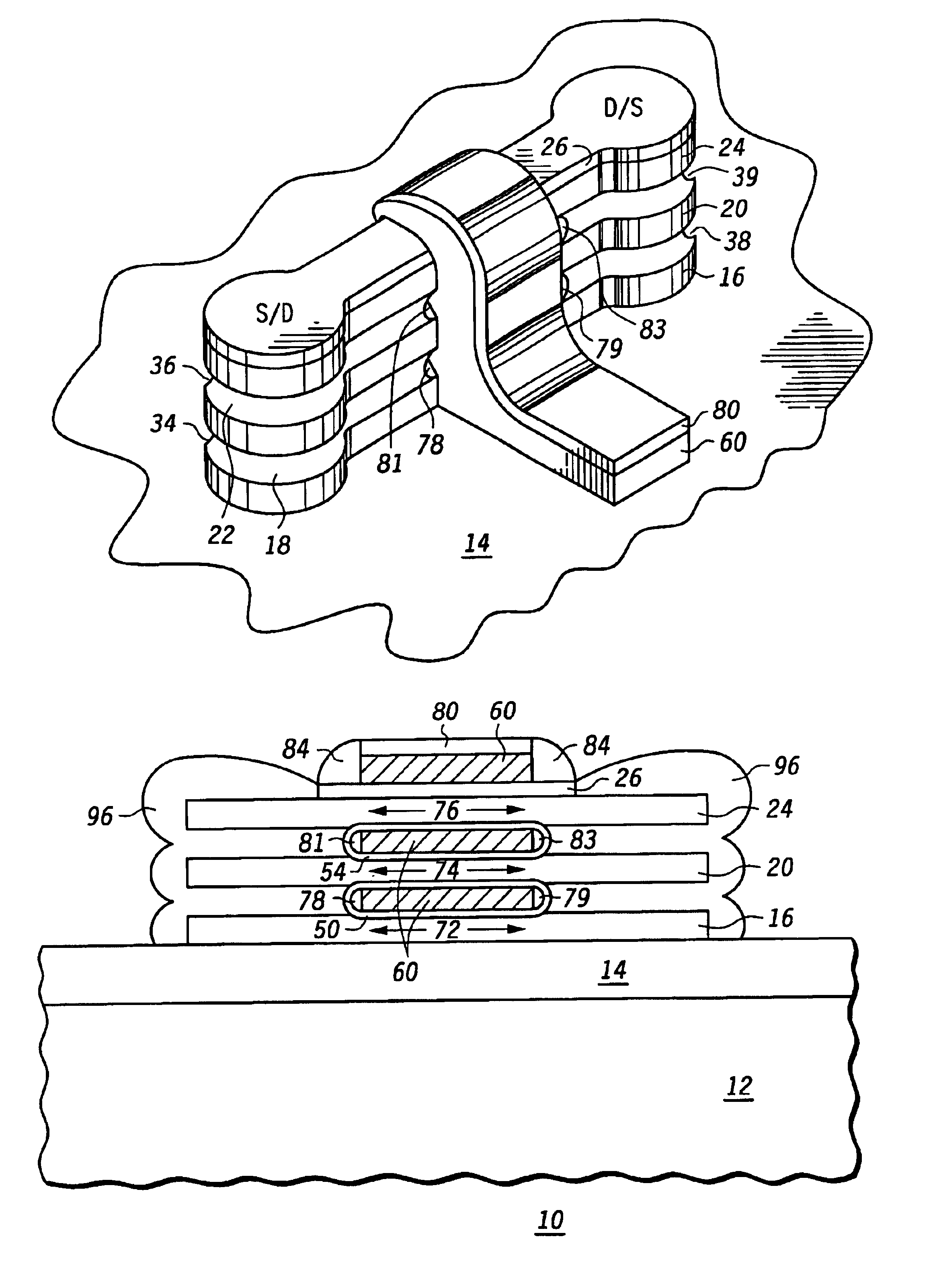

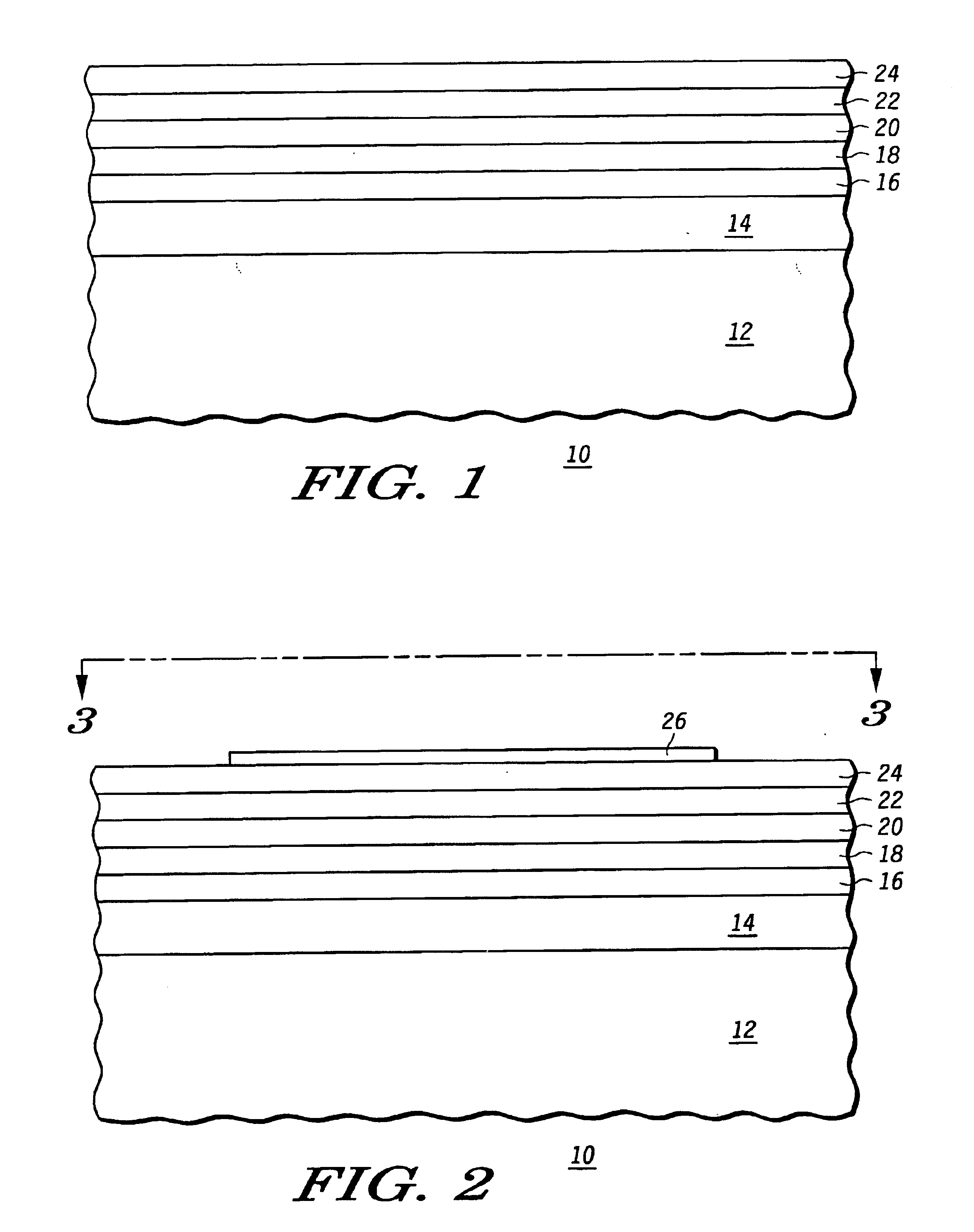

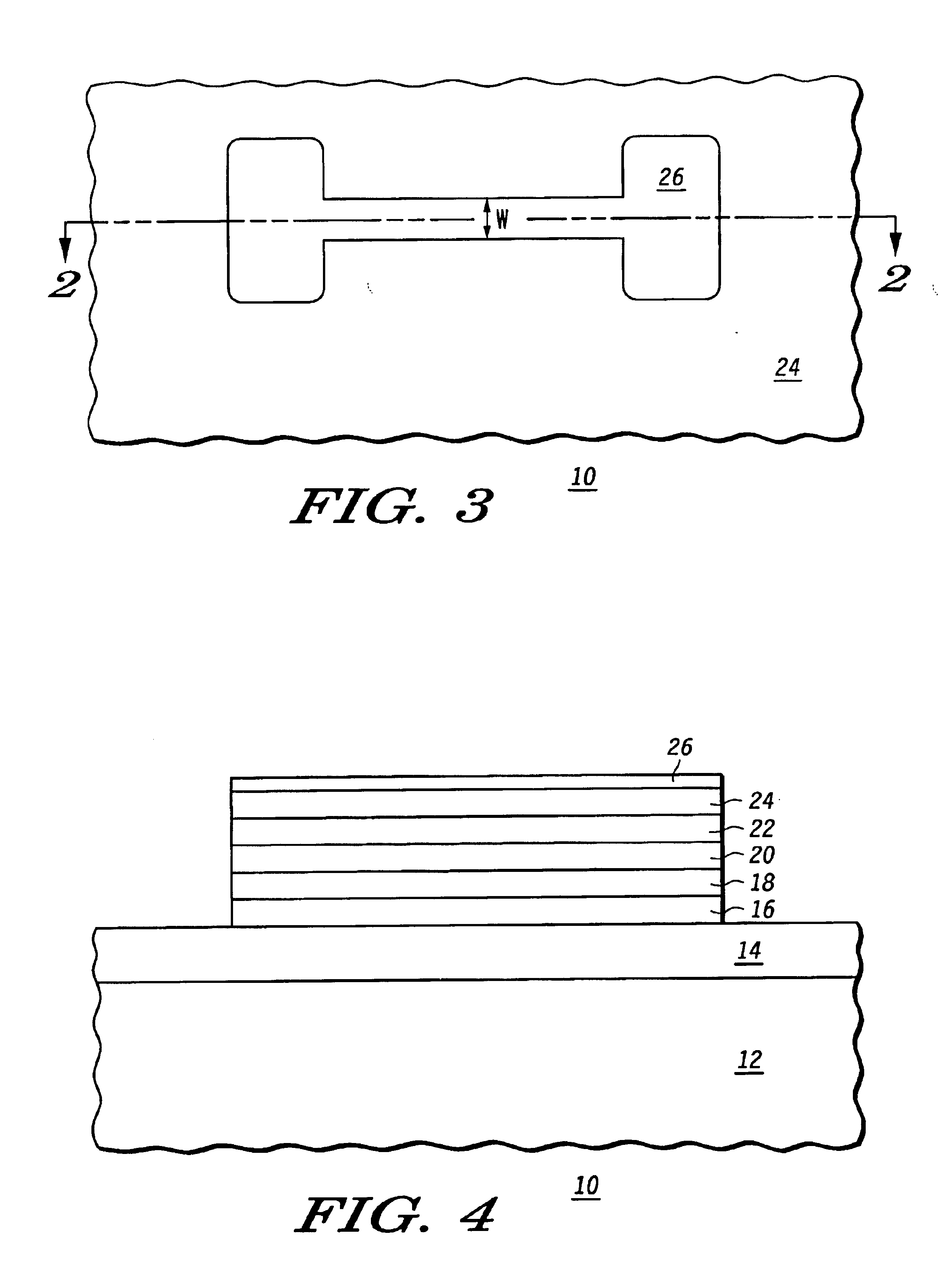

[0019]Illustrated in FIG. 1 is a semiconductor device 10 having a substrate 12. In one form the semiconductor device 10 is an FET (field effect transistor). The substrate 12 may be formed of any type of material, either conductive, semi-conductive or insulative. In one form, substrate 12 is single crystal silicon. Other forms of substrate 12 may include silicon, silicon on insulator, silicon on sapphire, and silicon on nitride. An insulating layer 14 overlies the substrate 12. Insulating layer 14, in one form, is silicon dioxide. Overlying the insulating layer 14 is a semiconductor layer 16. In one form, semiconductor layer 16 is silicon or silicon germanium, but other semiconductor materials may be used. For example, germanium, silicon germanium carbon, gallium arsenide, gallium nitride and indium phosphide are other appropriate material compositions.

[0020]In another form, the integrated circuit substrate 12 is a silicon-on-insulator (SOI) bonded wafer having a silicon layer which ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More