Patents

Literature

45 results about "Silicon on sapphire" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Silicon on sapphire (SOS) is a hetero-epitaxial process for metal-oxide-semiconductor (MOS) integrated circuit (IC) manufacturing that consists of a thin layer (typically thinner than 0.6 µm) of silicon grown on a sapphire (Al₂O₃) wafer. SOS is part of the silicon-on-insulator (SOI) family of CMOS (complementary MOS) technologies. Typically, high-purity artificially grown sapphire crystals are used. The silicon is usually deposited by the decomposition of silane gas (SiH₄) on heated sapphire substrates. The advantage of sapphire is that it is an excellent electrical insulator, preventing stray currents caused by radiation from spreading to nearby circuit elements. SOS faced early challenges in commercial manufacturing because of difficulties in fabricating the very small transistors used in modern high-density applications. This is because the SOS process results in the formation of dislocations, twinning and stacking faults from crystal lattice disparities between the sapphire and silicon. Additionally, there is some aluminum, a p-type dopant, contamination from the substrate in the silicon closest to the interface.

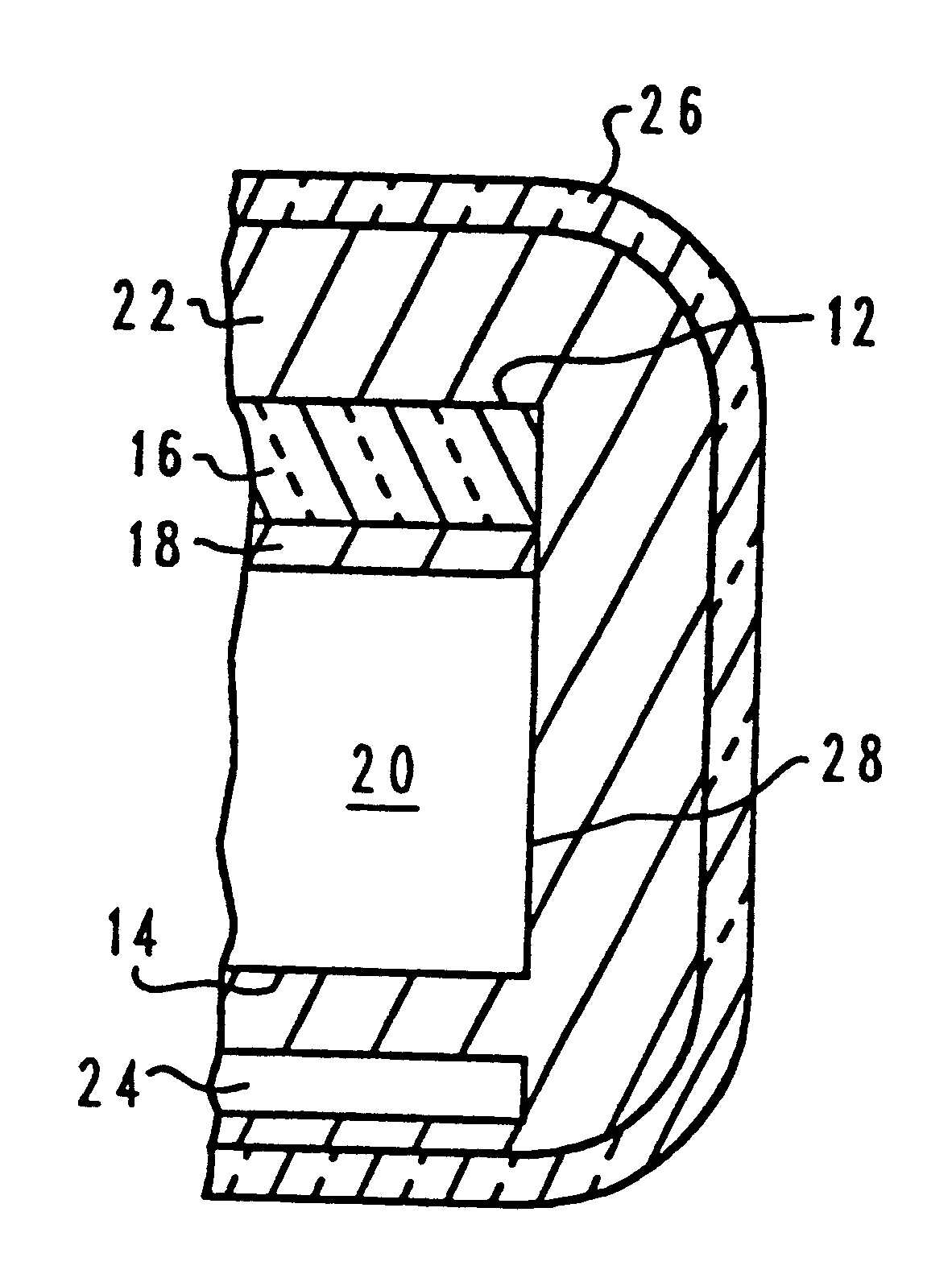

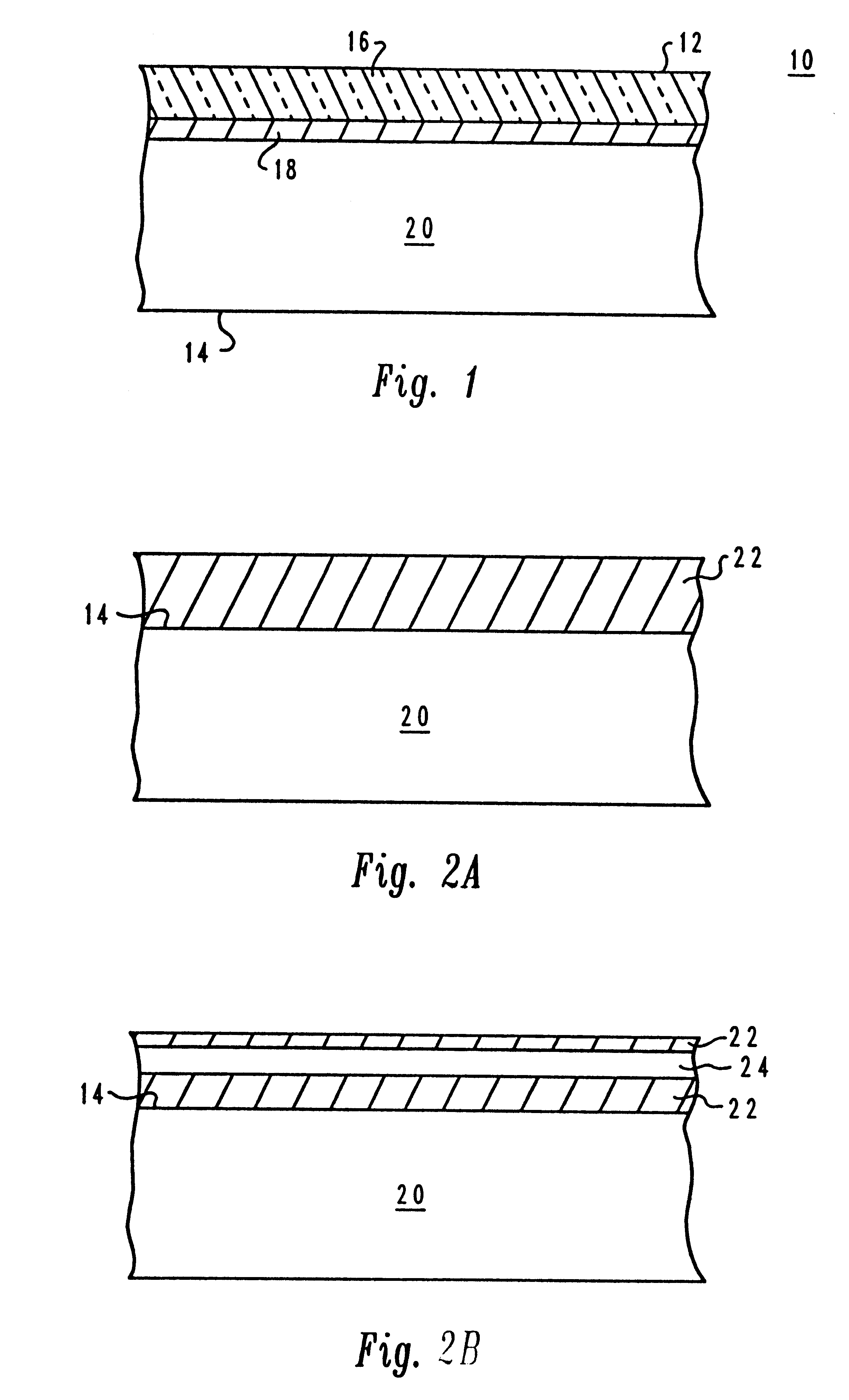

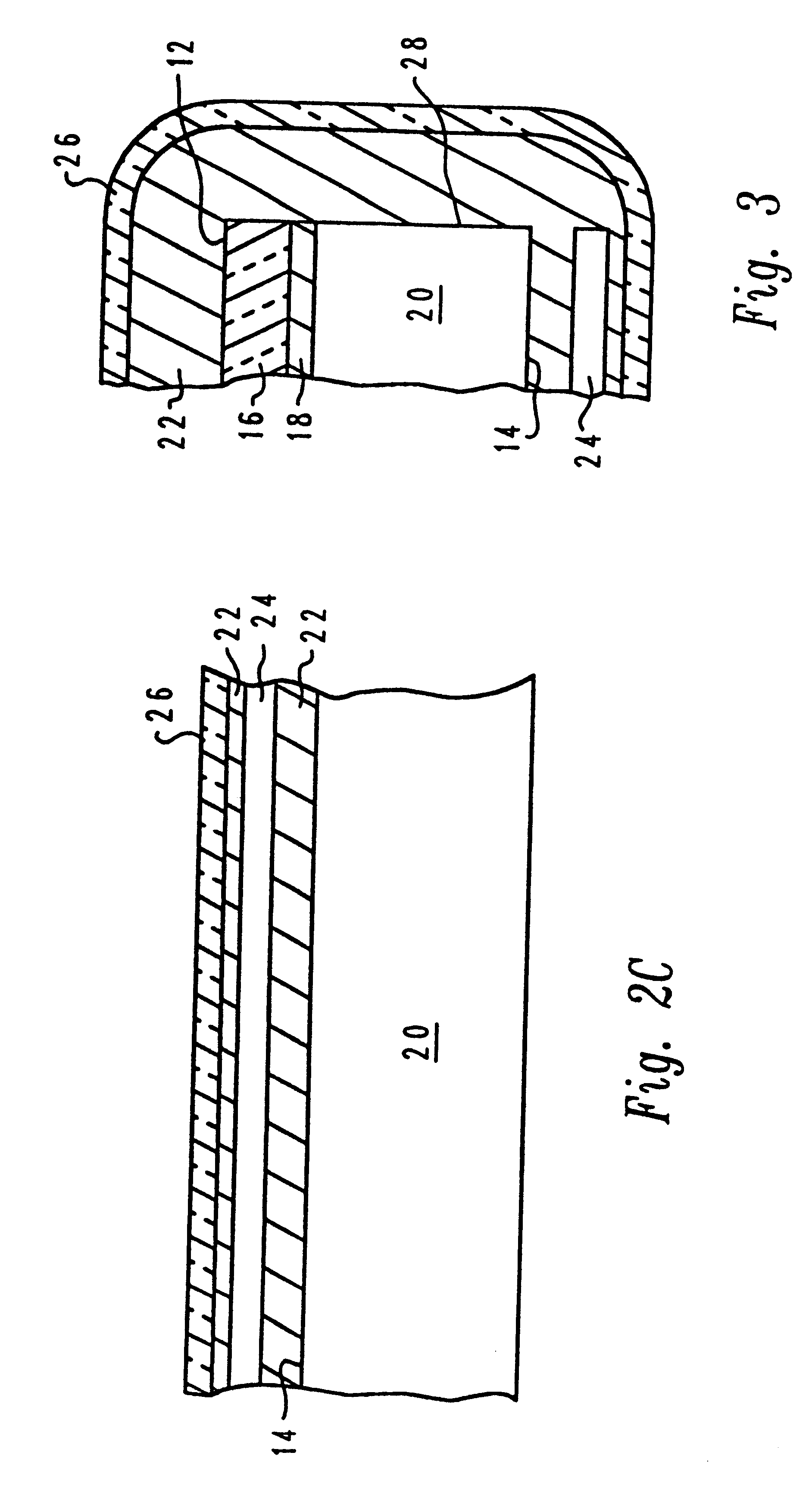

Method of fabricating silicon devices on sapphire with wafer bonding at low temperature

InactiveUS6911375B2Avoid process stepsCost effectiveSolid-state devicesSemiconductor/solid-state device manufacturingWaferingWafer bonding

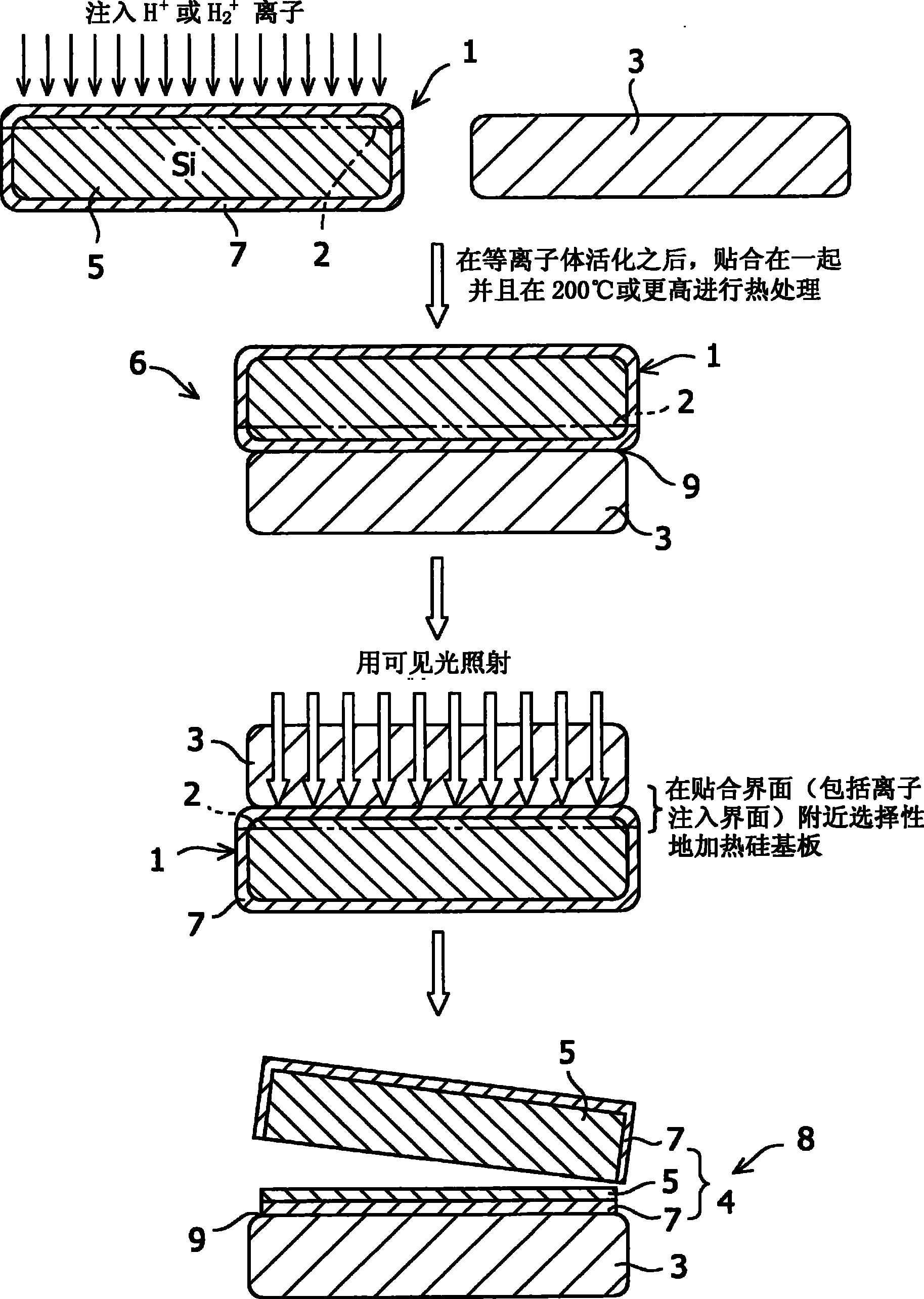

Described is a method for making silicon on sapphire structures, and devices therefrom. The inventive method of forming integrated circuits on a sapphire substrate comprises the steps of providing a device layer on an oxide layer of a temporary substrate; bonding the device layer to a handling substrate; removing the temporary substrate to provide a structure containing the device layer between the oxide layer and the handling substrate; bonding a sapphire substrate to the oxide layer; removing the handling substrate from the structure; and annealing the final structure to provide a substrate comprising the oxide layer between the device layer and the sapphire substrate. The sapphire substrate may comprise bulk sapphire or may be a conventional substrate material with an uppermost sapphire layer.

Owner:IBM CORP

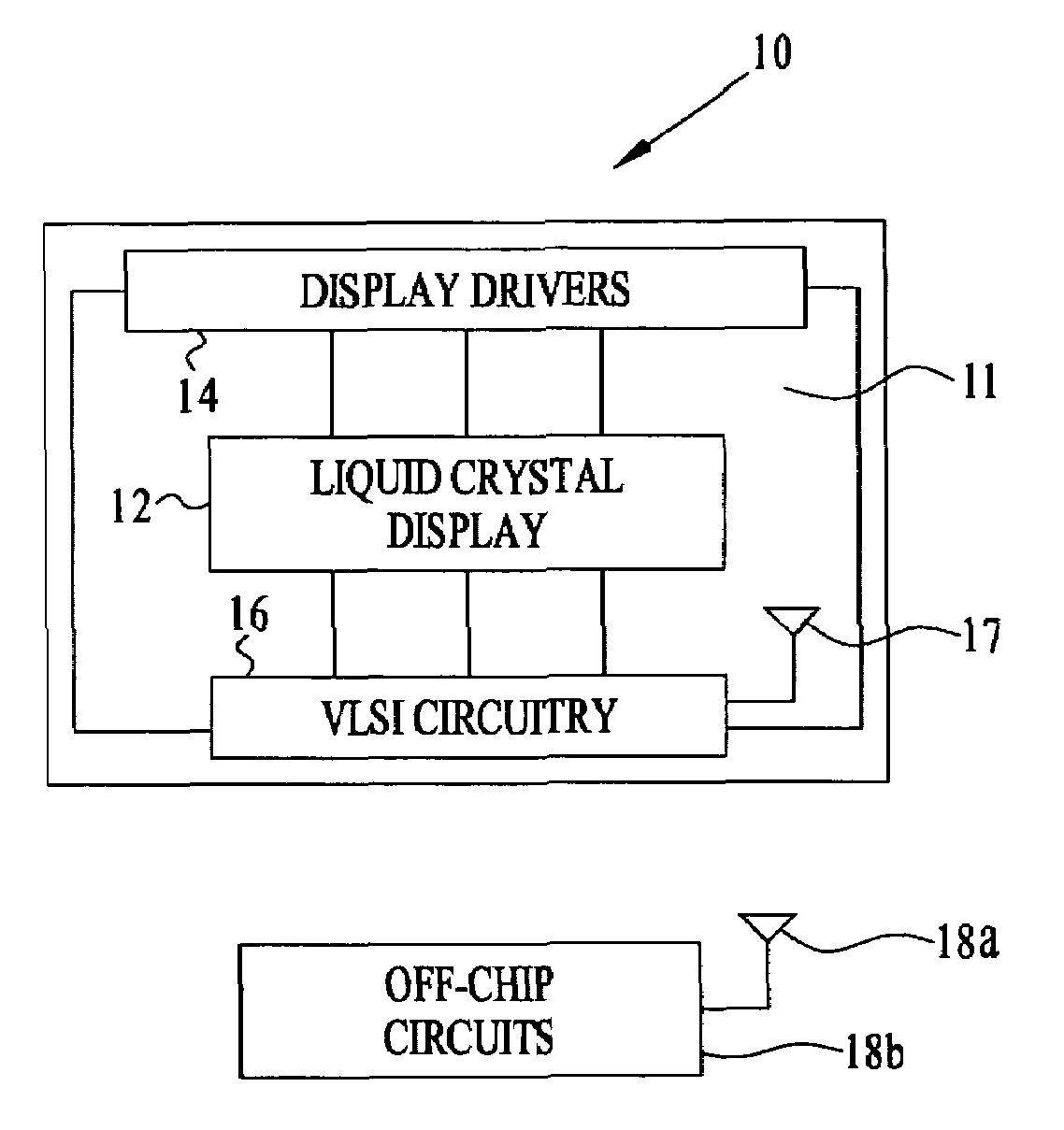

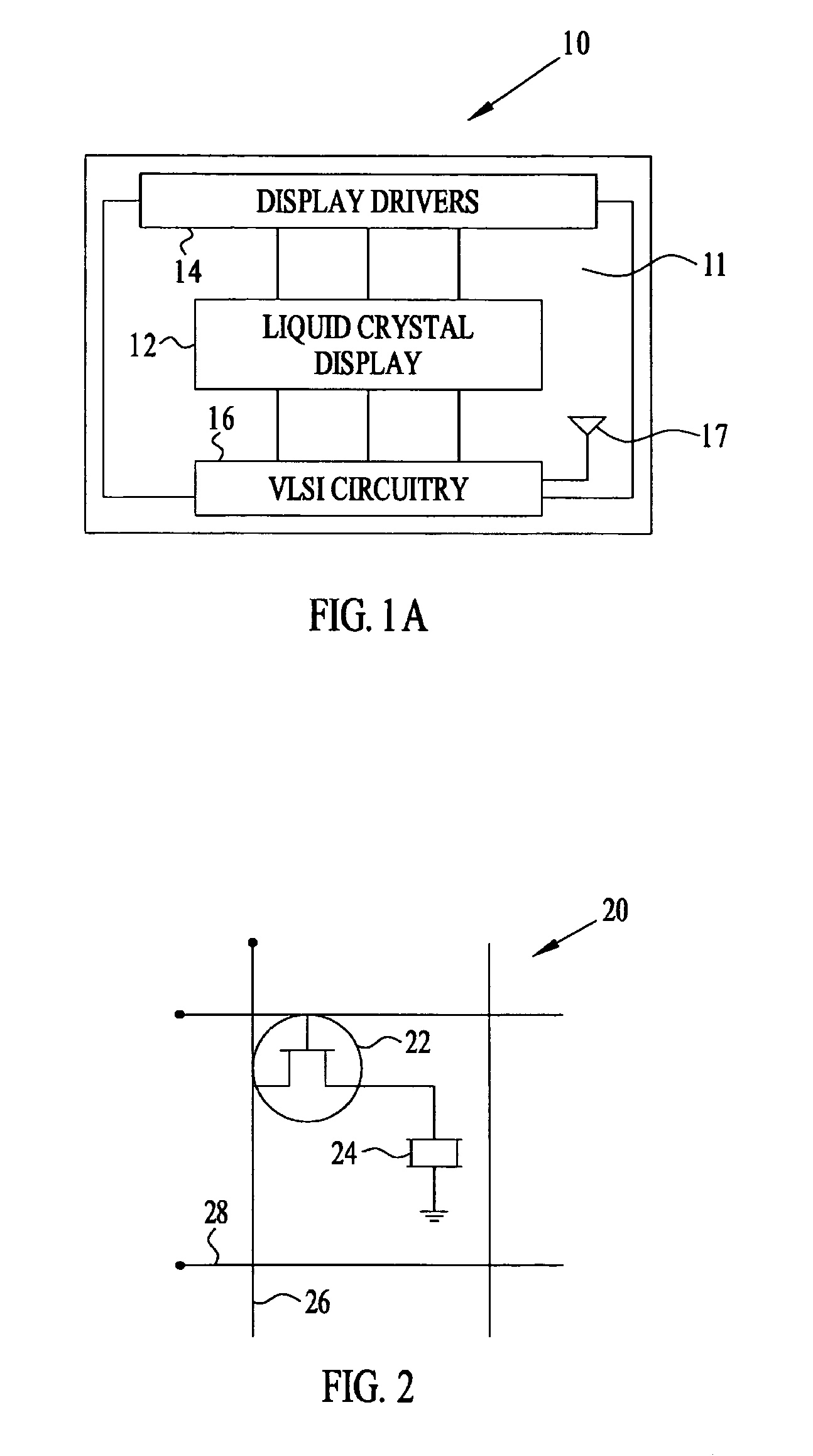

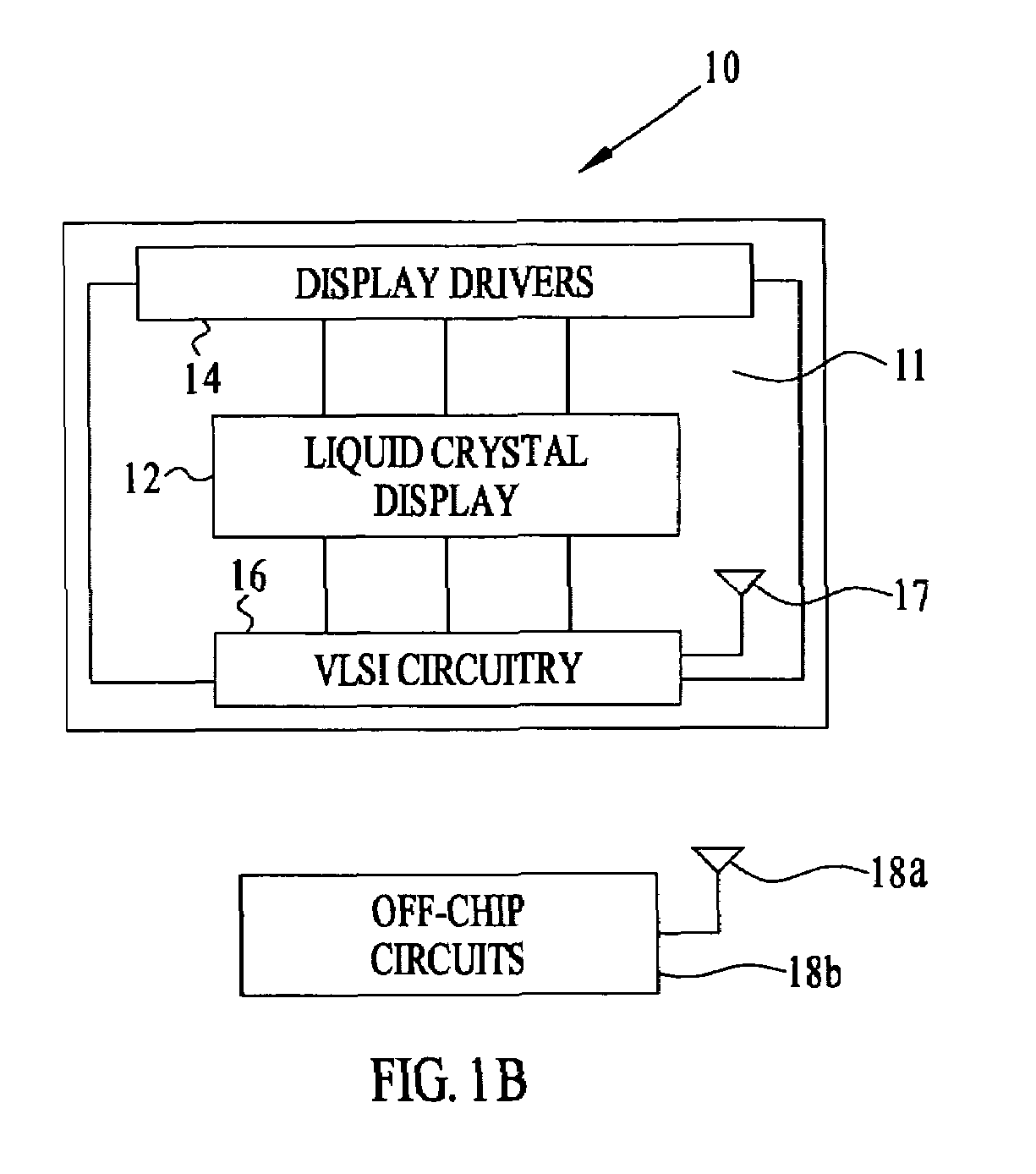

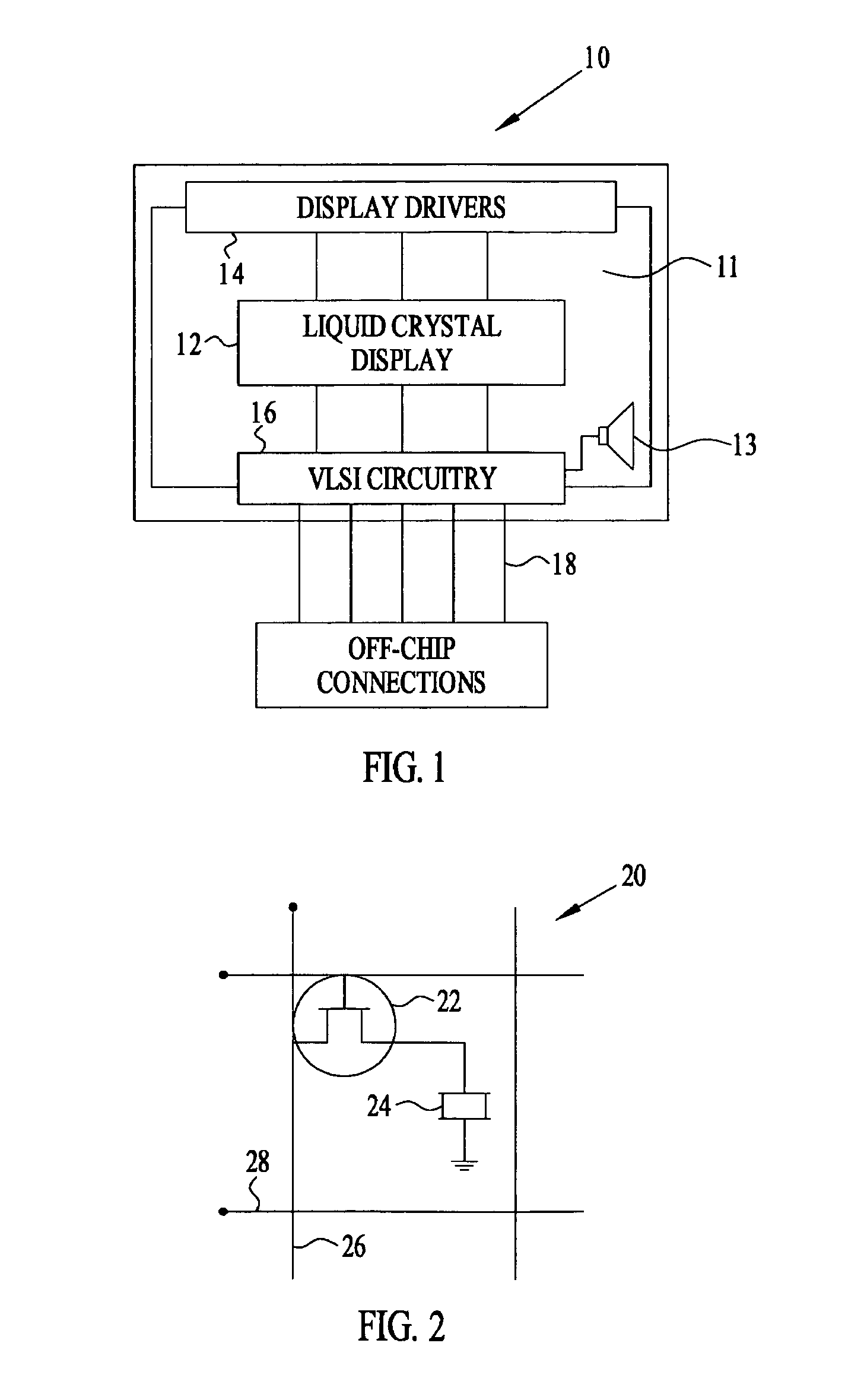

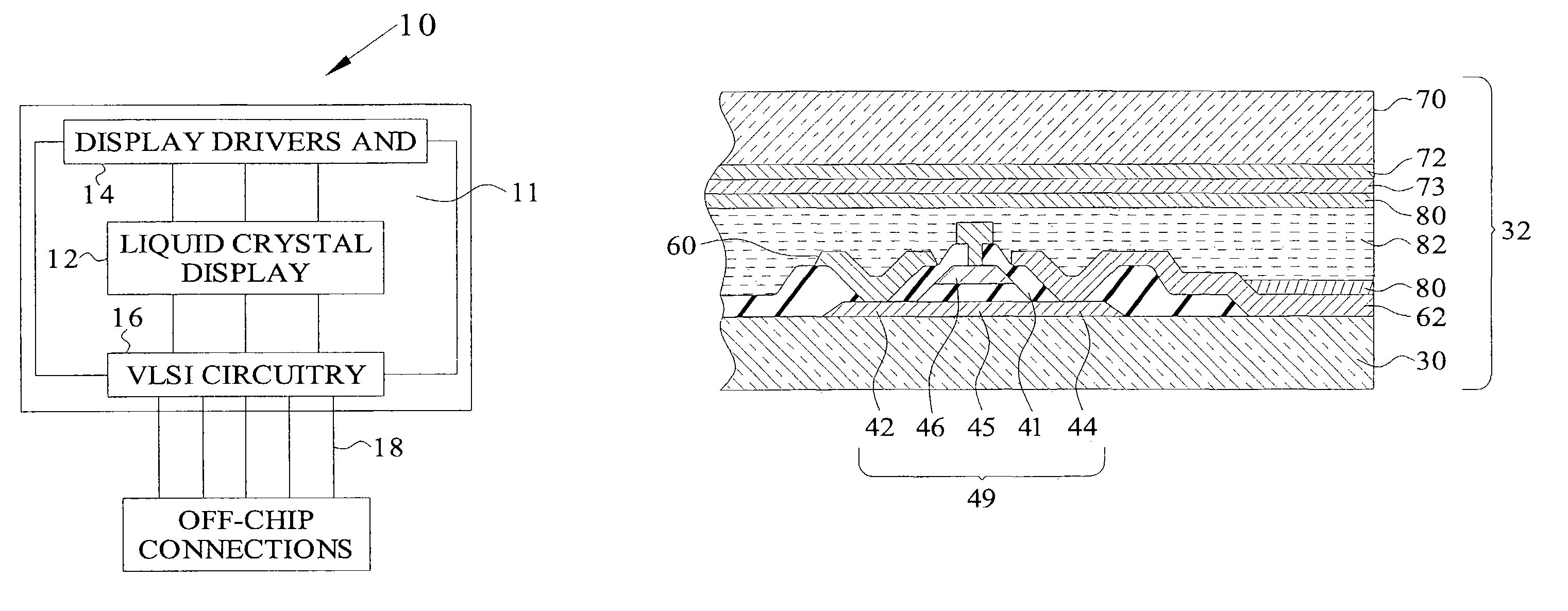

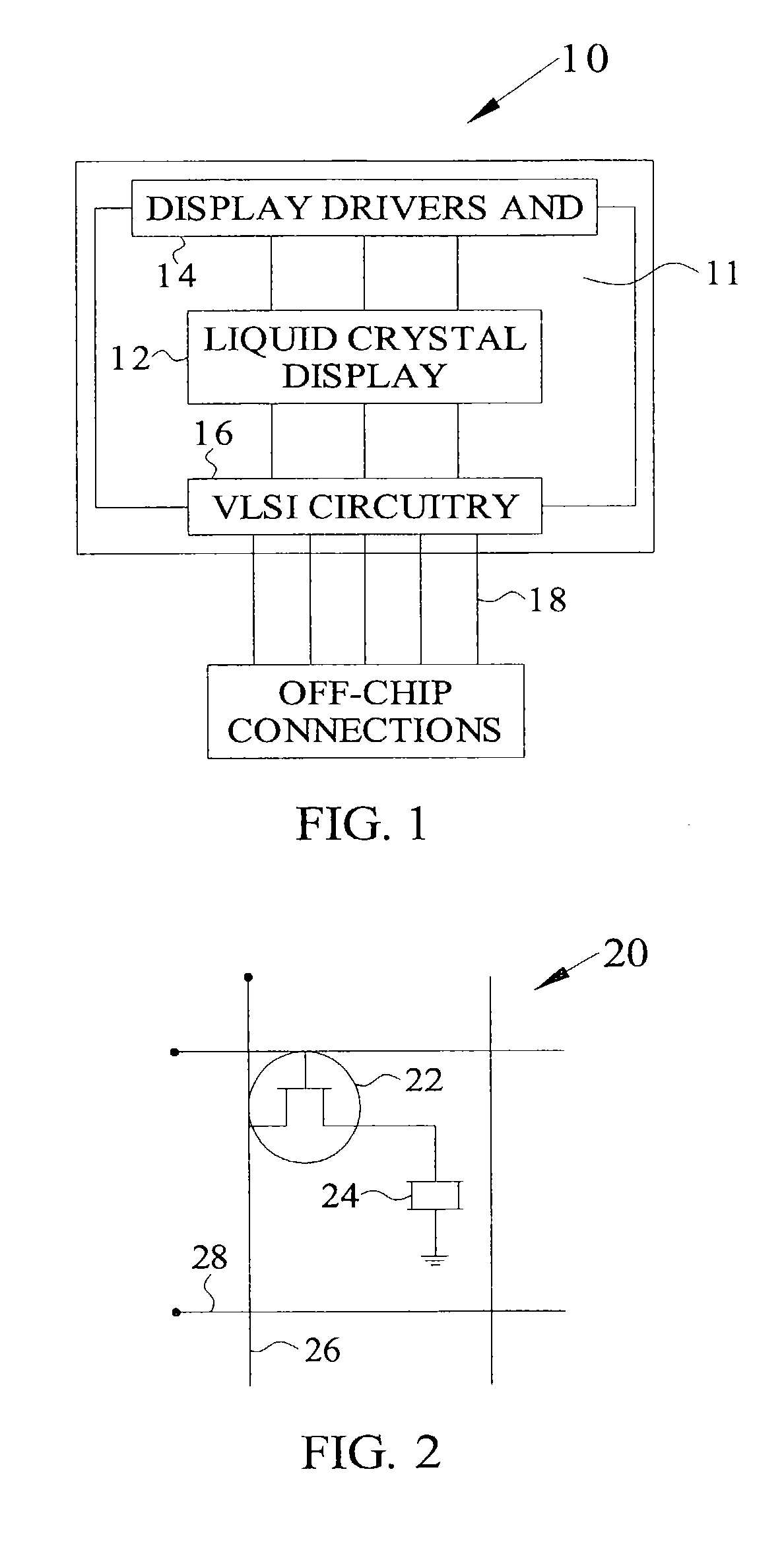

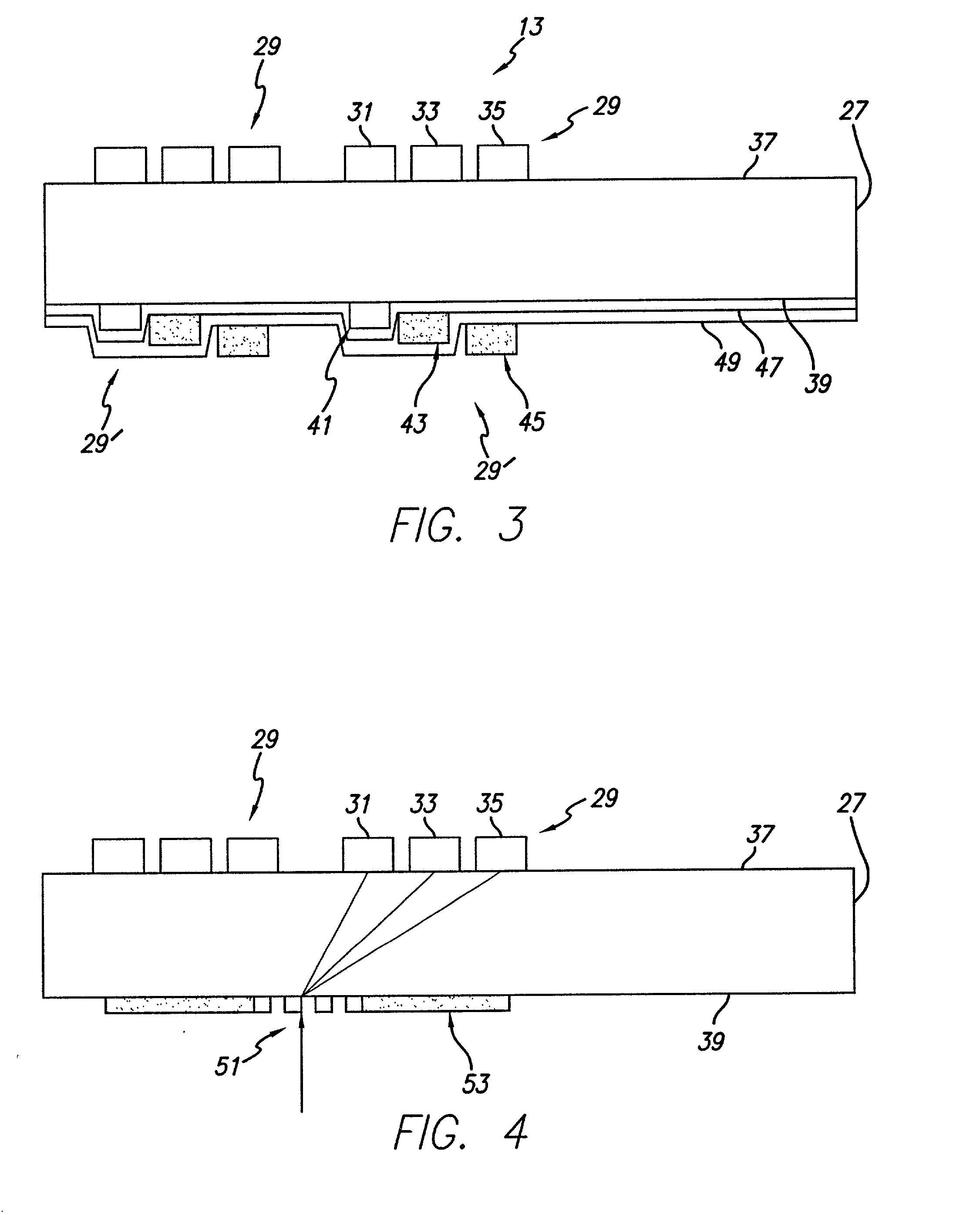

Silicon-on-sapphire display with wireless interconnections and method of fabricating same

A liquid crystal display includes: a) a sapphire substrate; b) a single crystal silicon structure disposed on the sapphire substrate to create a silicon-on-sapphire structure; c) a plurality of liquid crystal capacitors disposed on the silicon-on-sapphire structure; d) integrated self-aligned circuitry formed from the crystal silicon structure, where the circuitry modulates the liquid crystal capacitors in response to an input control signal; and e) a receiver disposed on the silicon-on-sapphire structure for receiving electromagnetic radiation and generating the input control signal responsive to the received electromagnetic radiation.

Owner:THE UNITED STATES OF AMERICA AS REPRESENTED BY THE SECRETARY OF THE NAVY

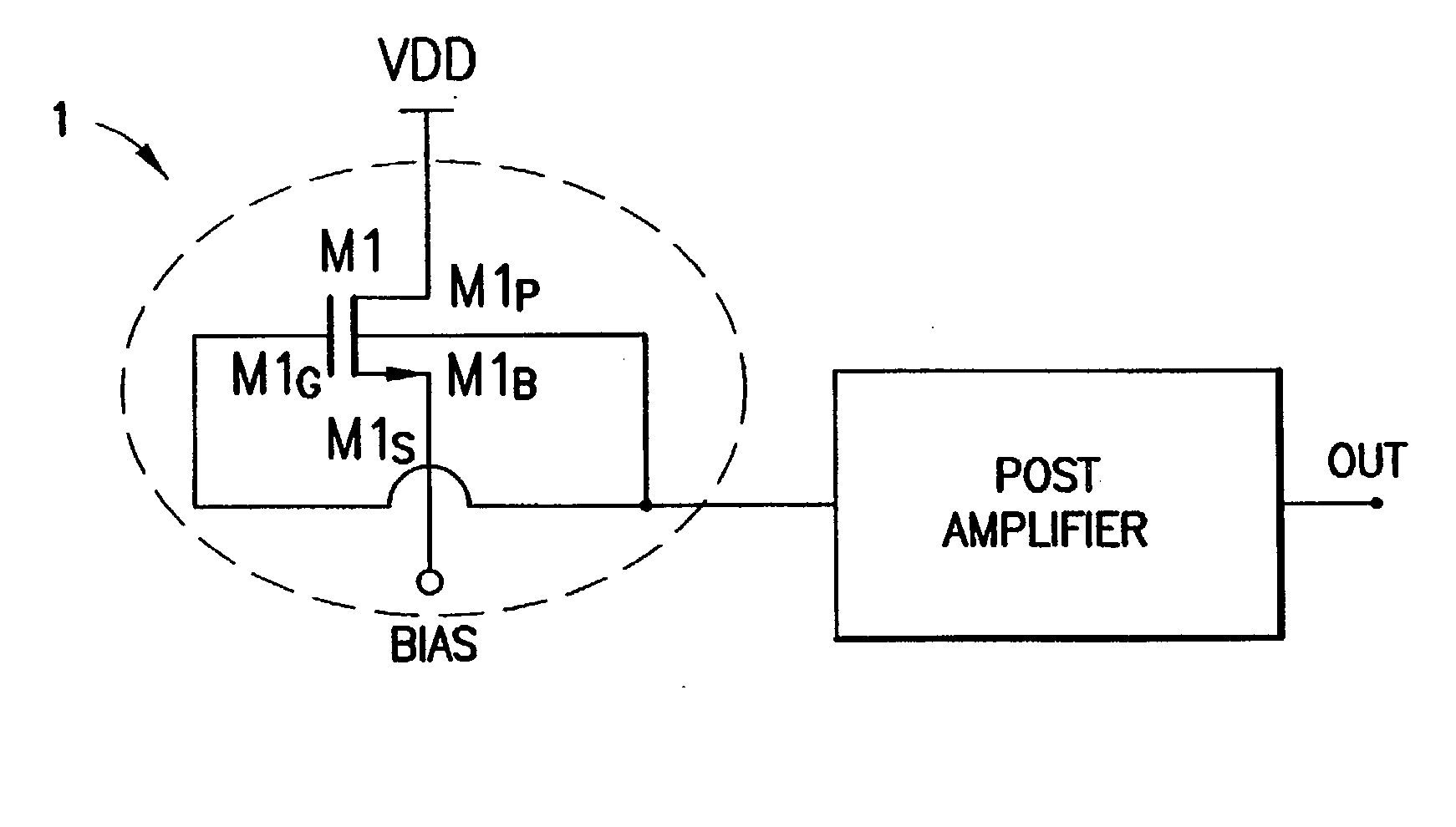

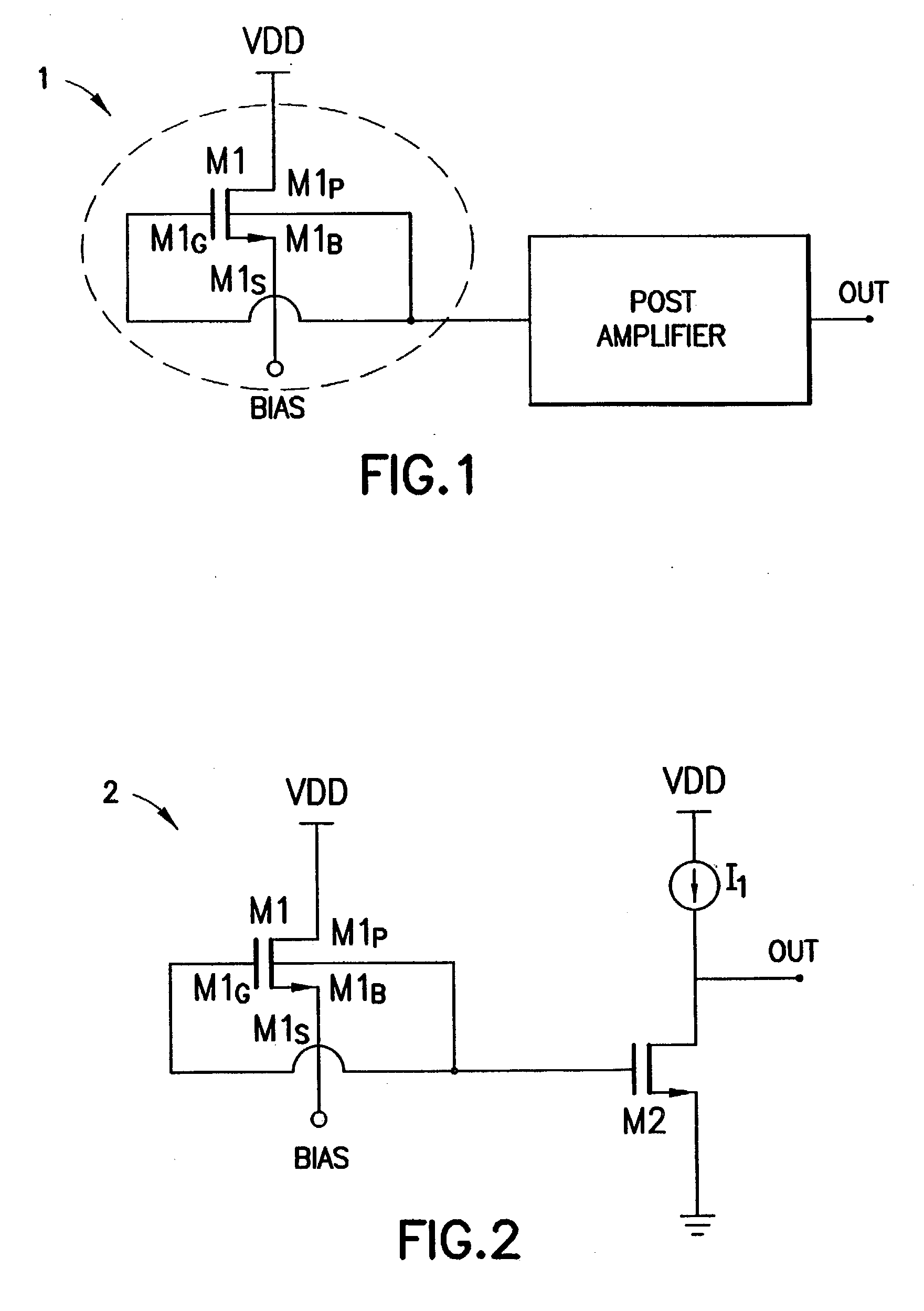

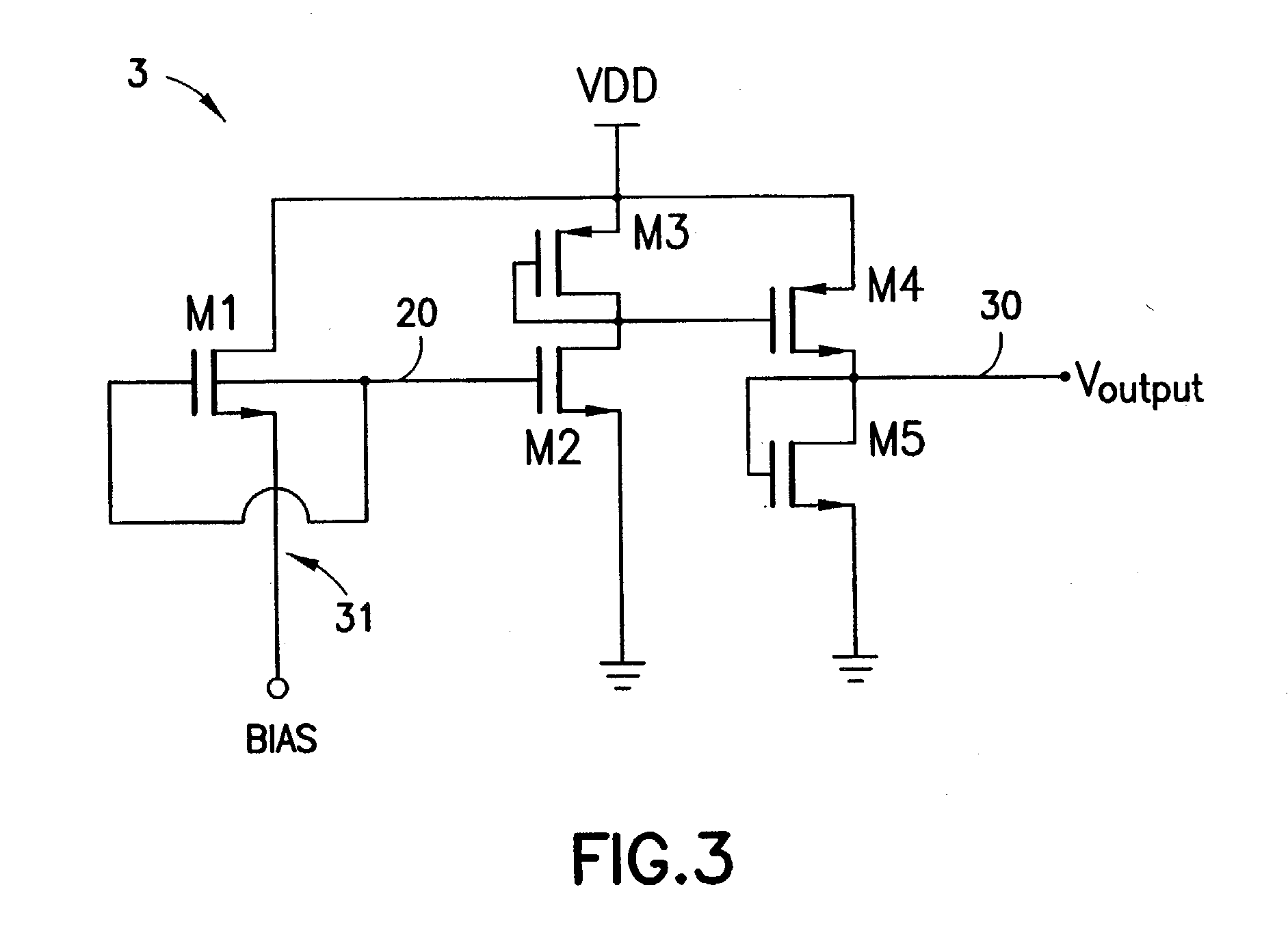

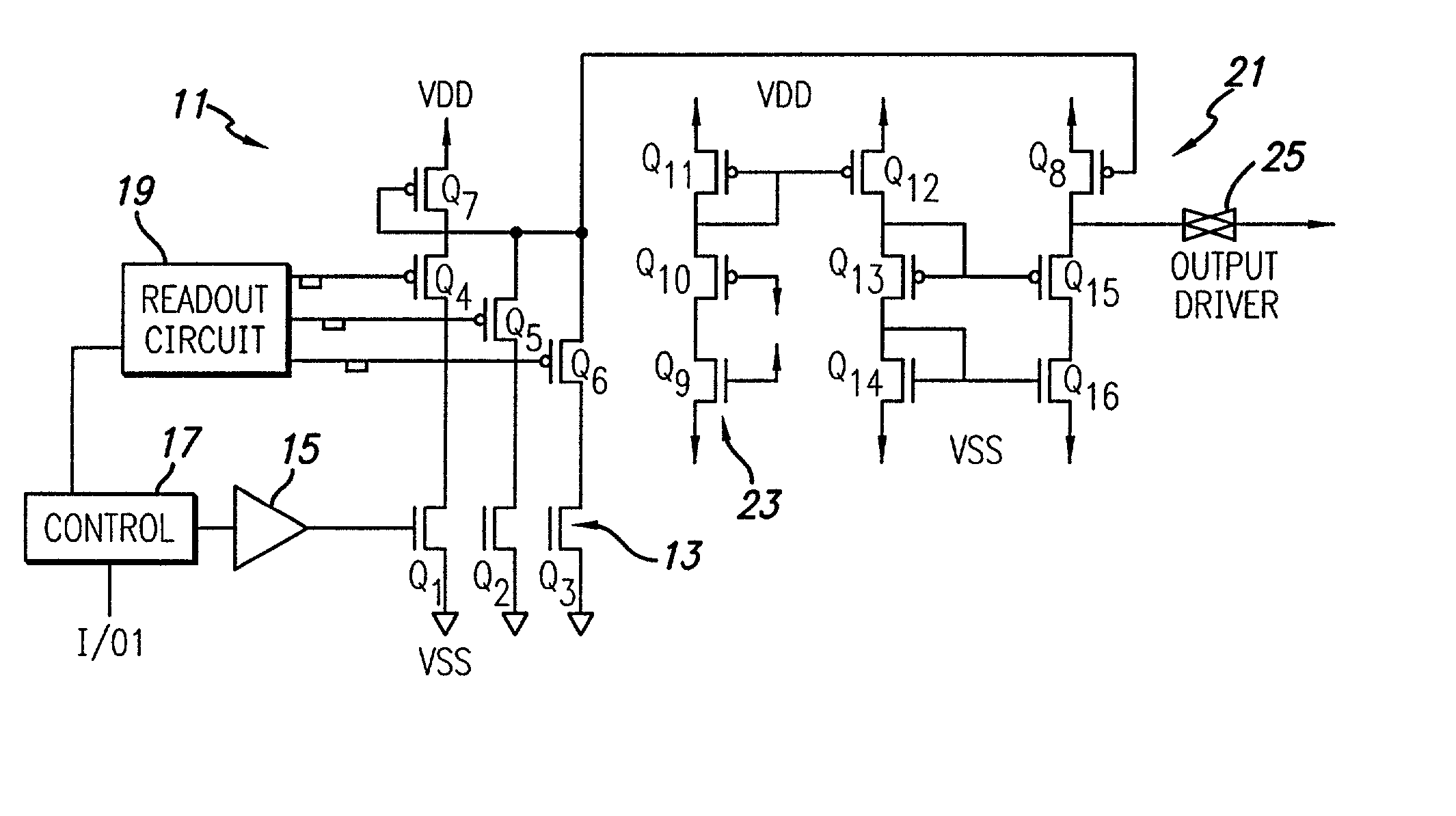

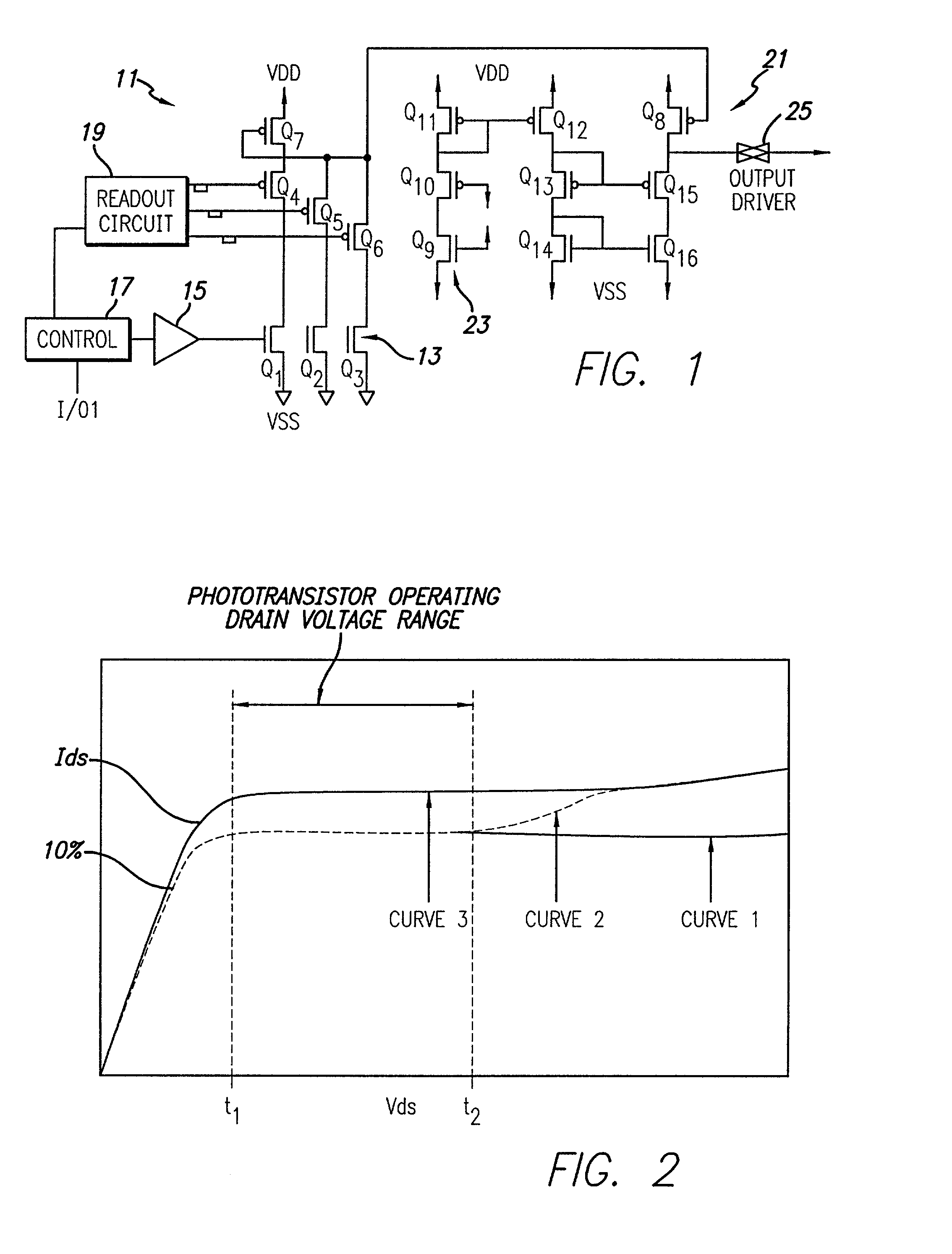

Integrated photodetector for VCSEL feedback control

InactiveUS20030109142A1Semiconductor/solid-state device manufacturingCoupling light guidesDriver circuitPhotovoltaic detectors

An integrated photodetector means for controlling the output of a light source, where the control means is a photodetector formed on a silicon-on-insulator substrate. The integrated photodetector senses the optical power from the light source and provides an electrical feedback signal which can be used to adjust the DC bias levels of the light source control driver circuit. The approach readily lends itself to large arrays of light sources bonded to silicon-on-sapphire driver circuits and is especially suitable for controlling light sources such as VCSELs in arrays such as are found in communications systems.

Owner:PEREGRINE SEMICONDUCTOR

Coupled optical and optoelectronic devices, and method of making the same

InactiveUS6869229B2Easy to manufactureSacrifice power performanceSolid-state devicesCoupling light guidesCouplingRefractive index

An optical-optoelectronic coupling structure comprising a flip-chip optoelectronic / ultrathin silicon-on-sapphire device mounted on a V-groove, optical-fiber-bearing carrier substrate, including light-reflective structures for launching light into the optical fiber core or transmitting light emitted by the optical fiber core to the optoelectronic device. The optical fiber may be immobilized in the V-groove using a curable resin adhesive characterized by a refractive index substantially similar to the refractive index of the optical fiber.

Owner:PSEMI CORP

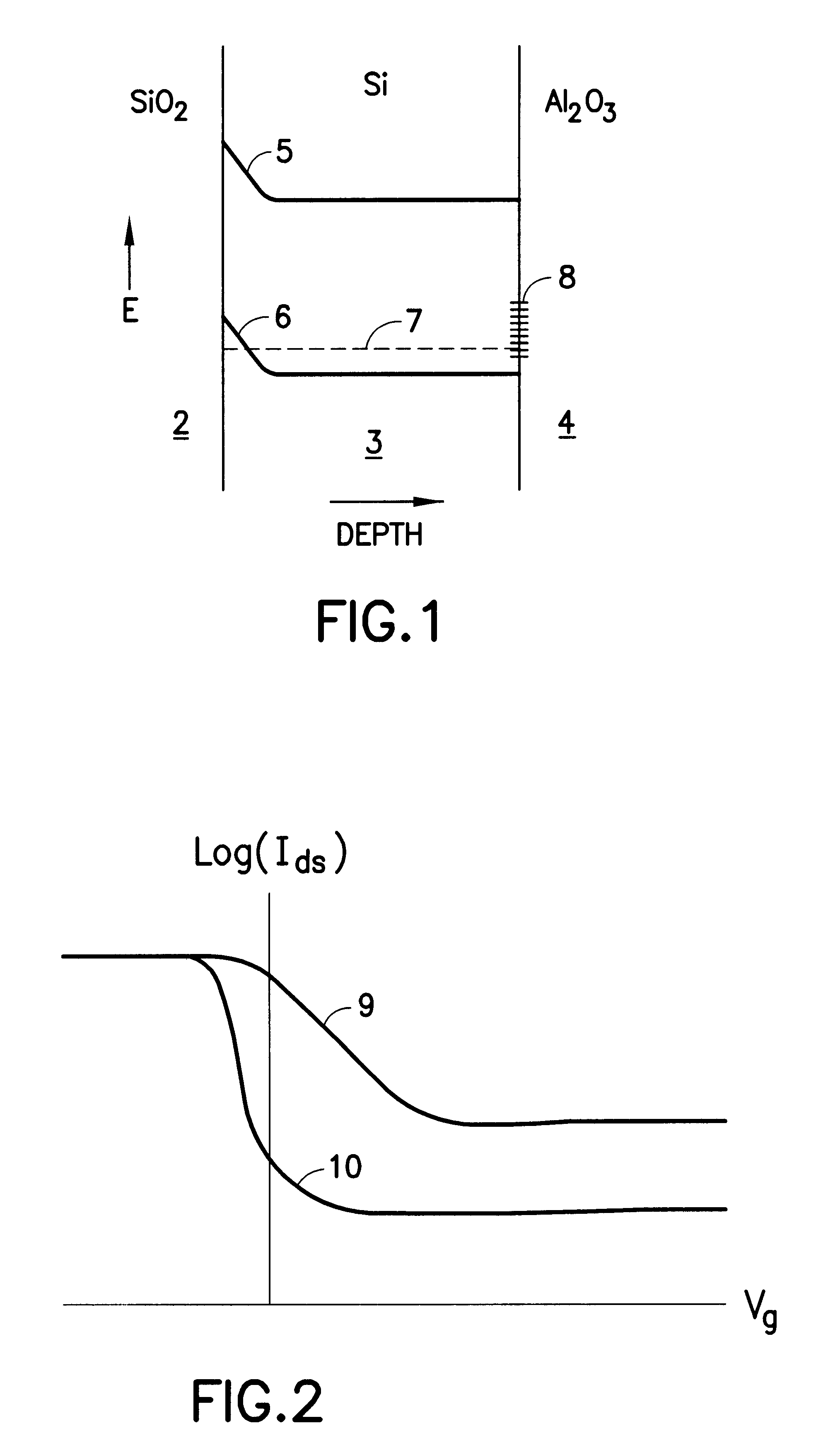

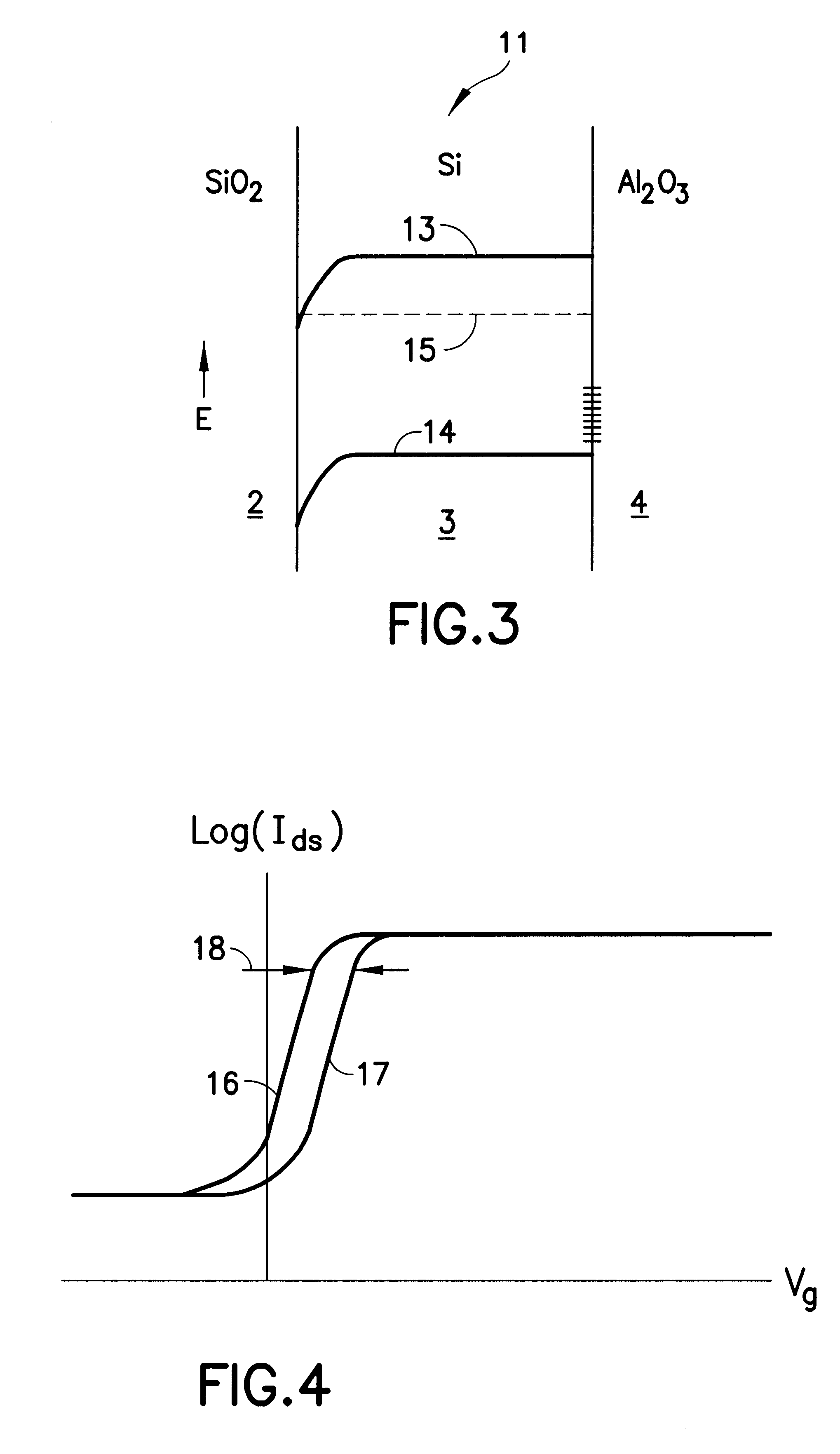

Radiation-hardened silicon-on-insulator CMOS device, and method of making the same

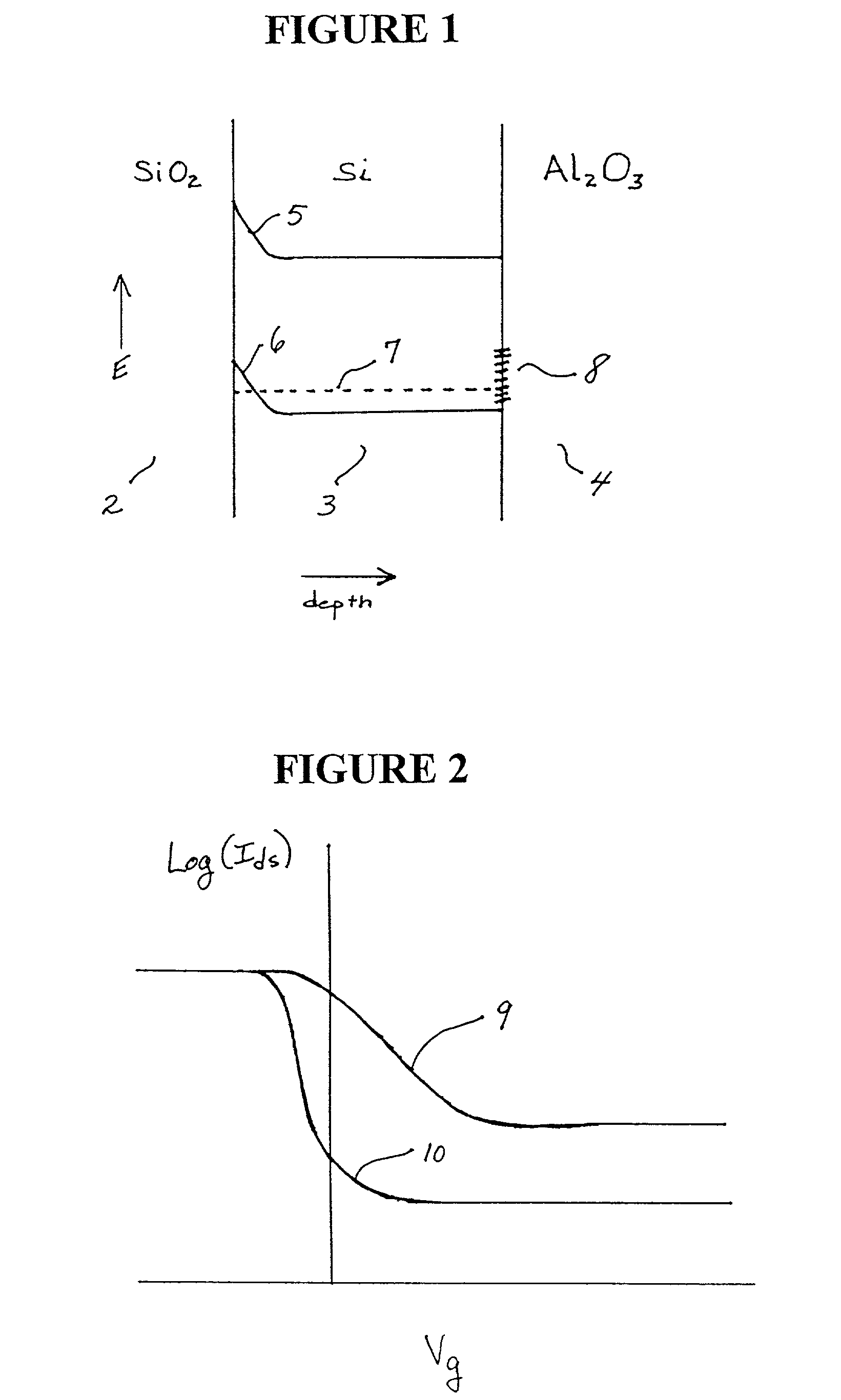

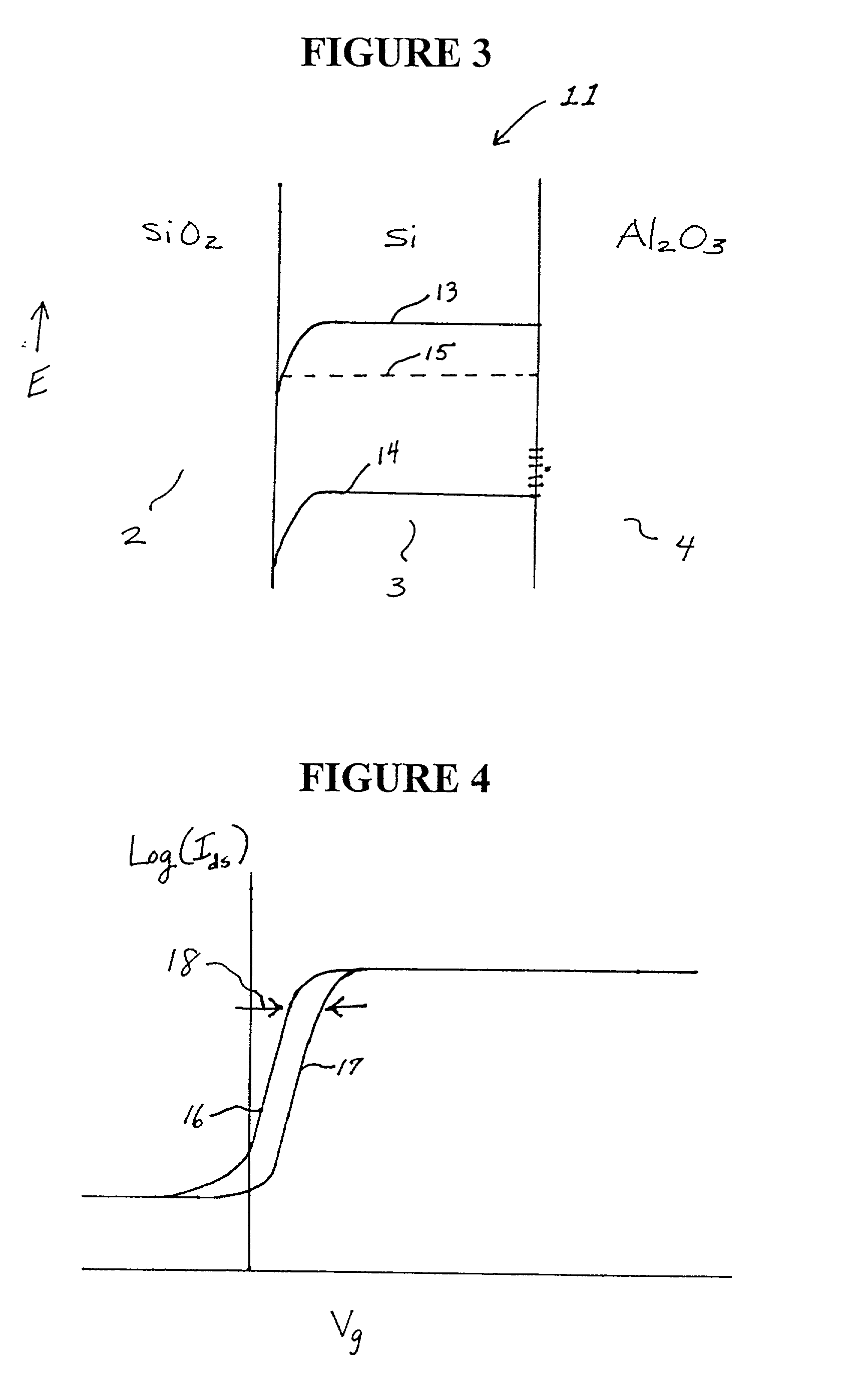

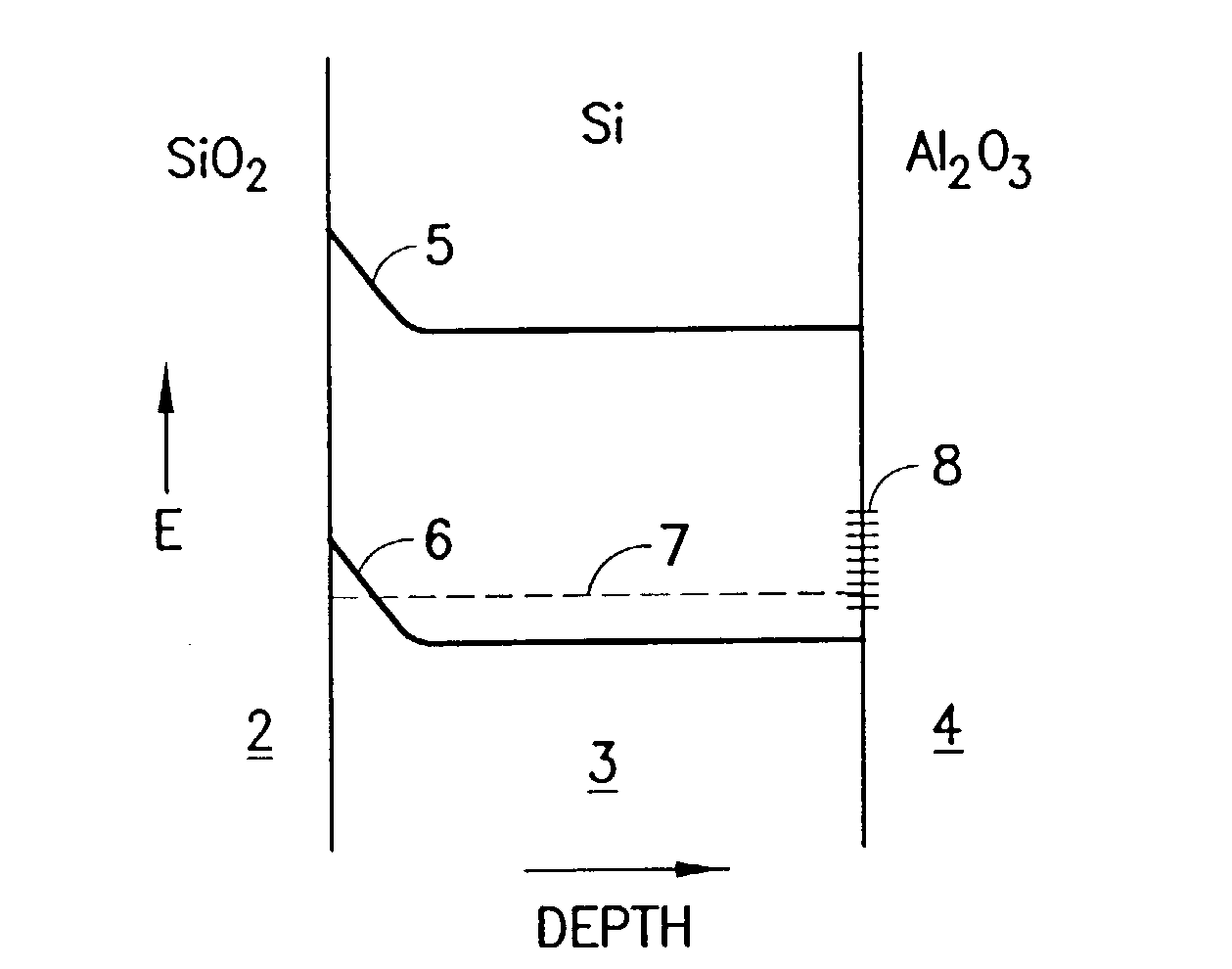

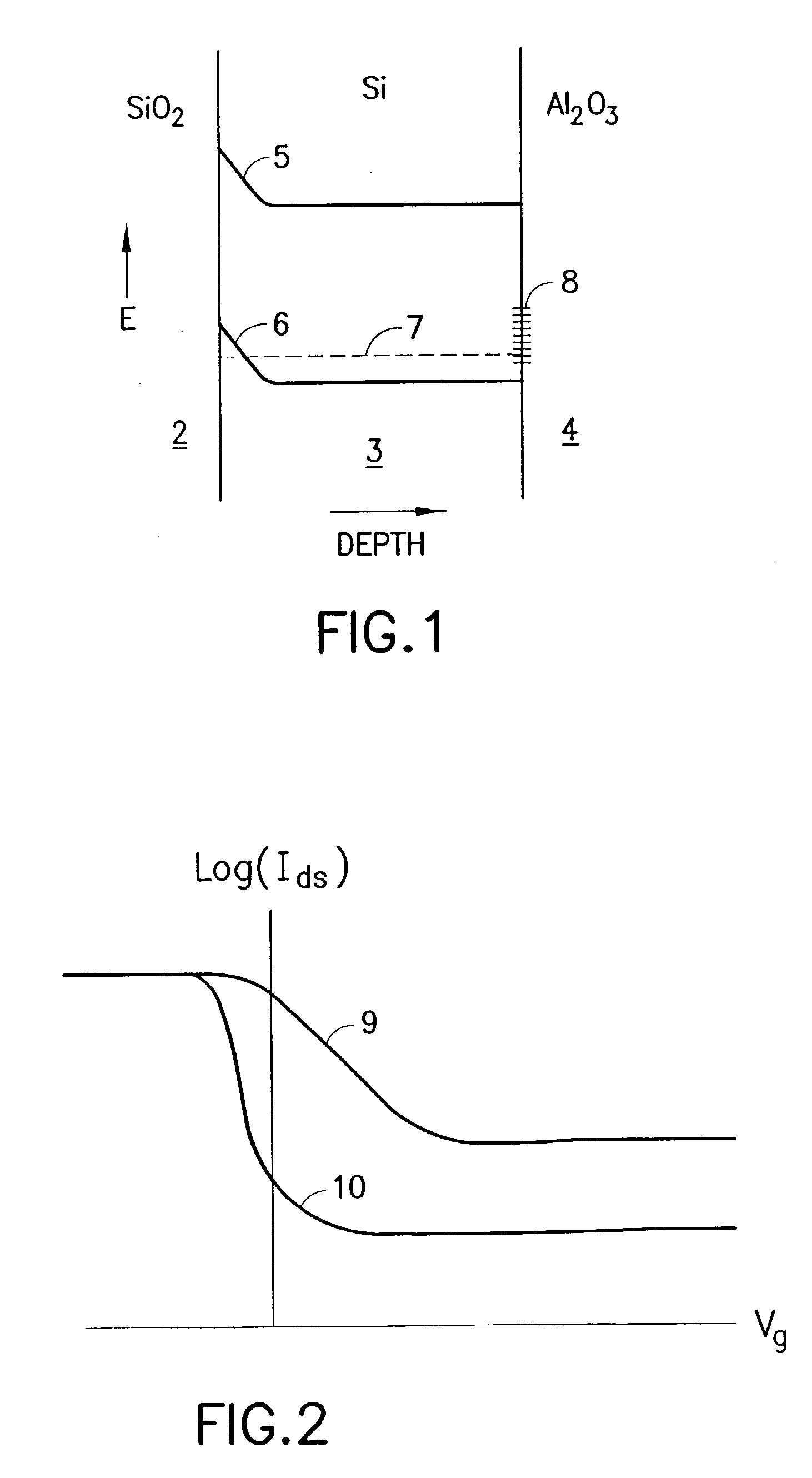

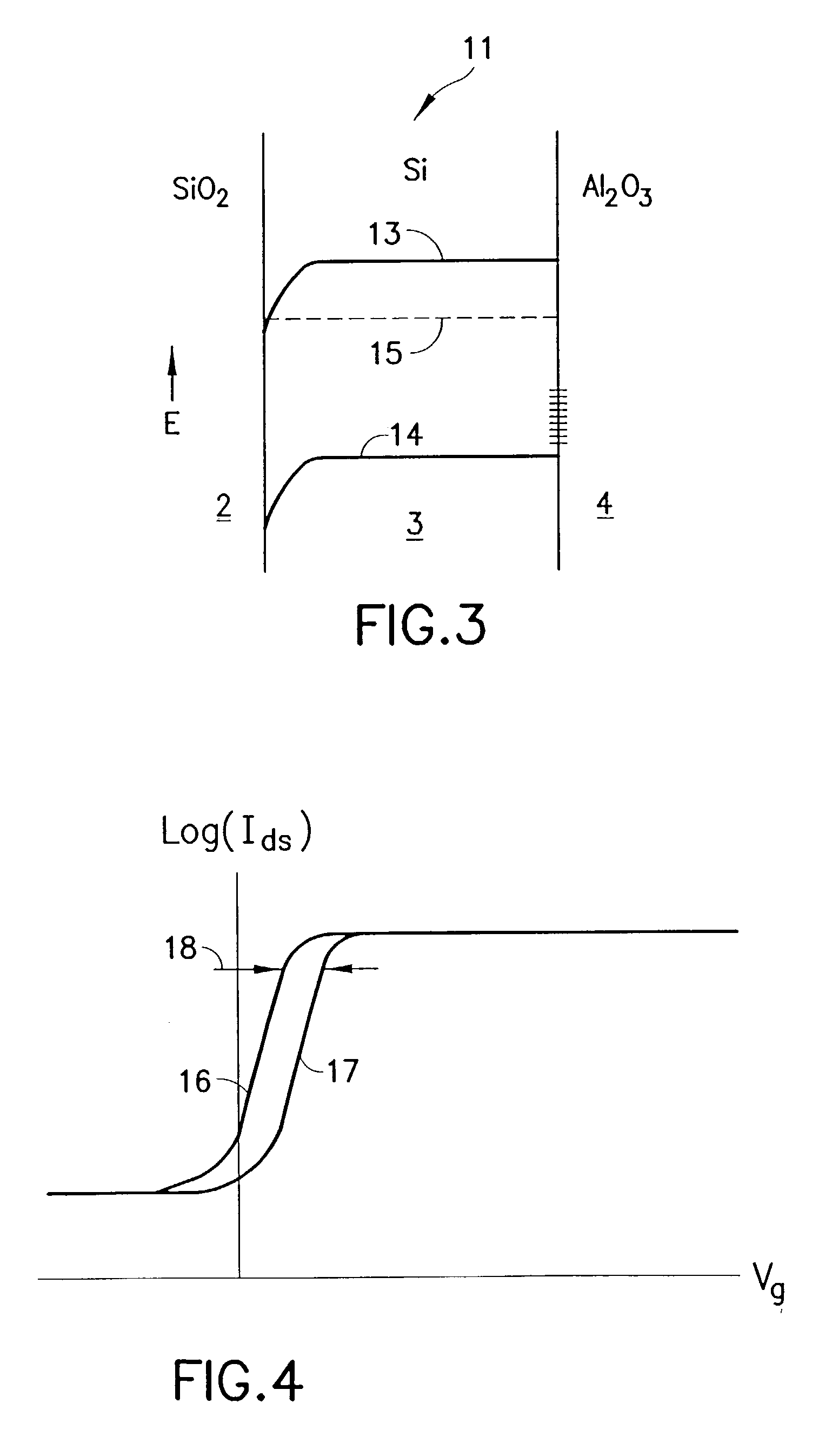

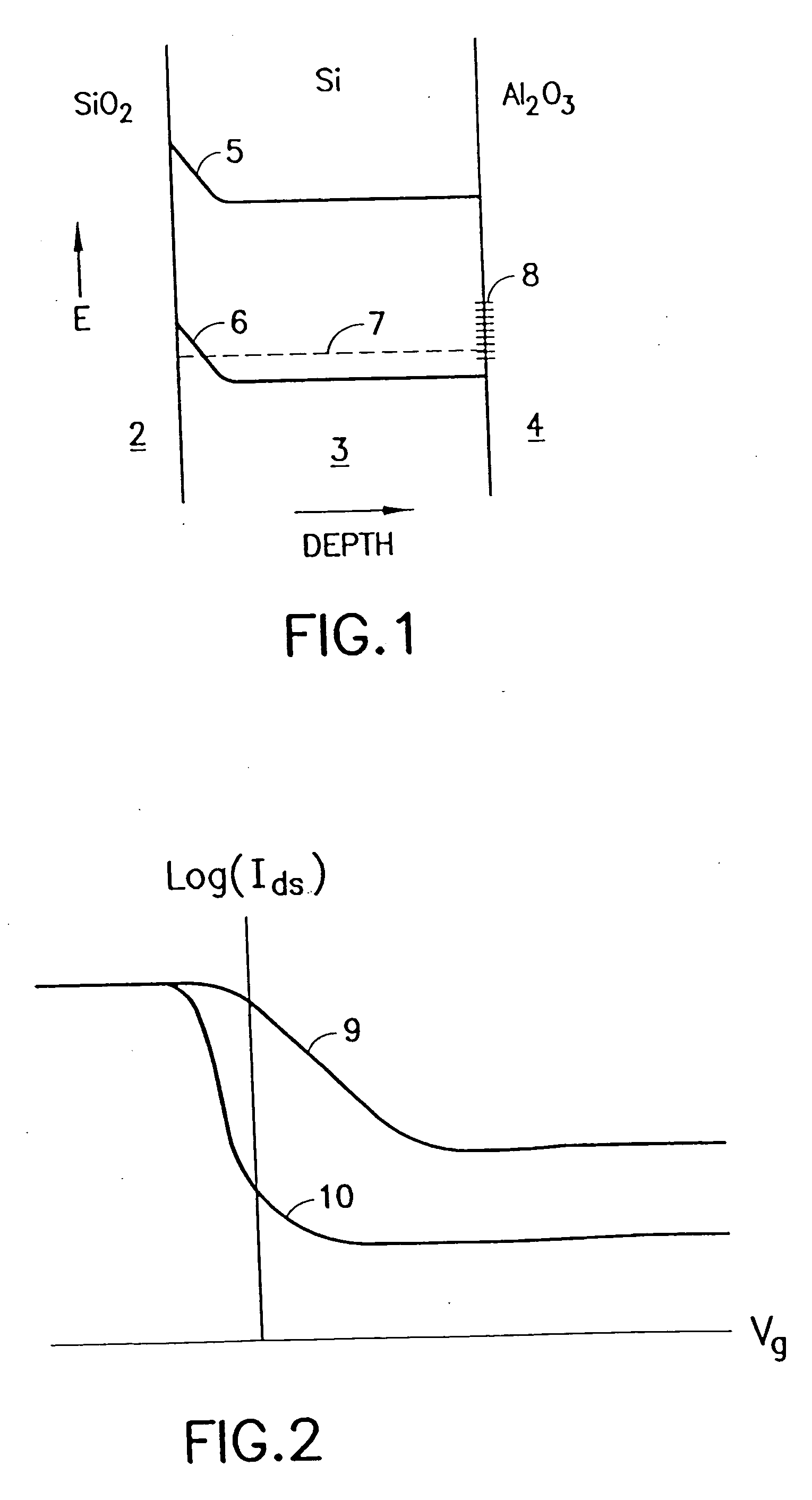

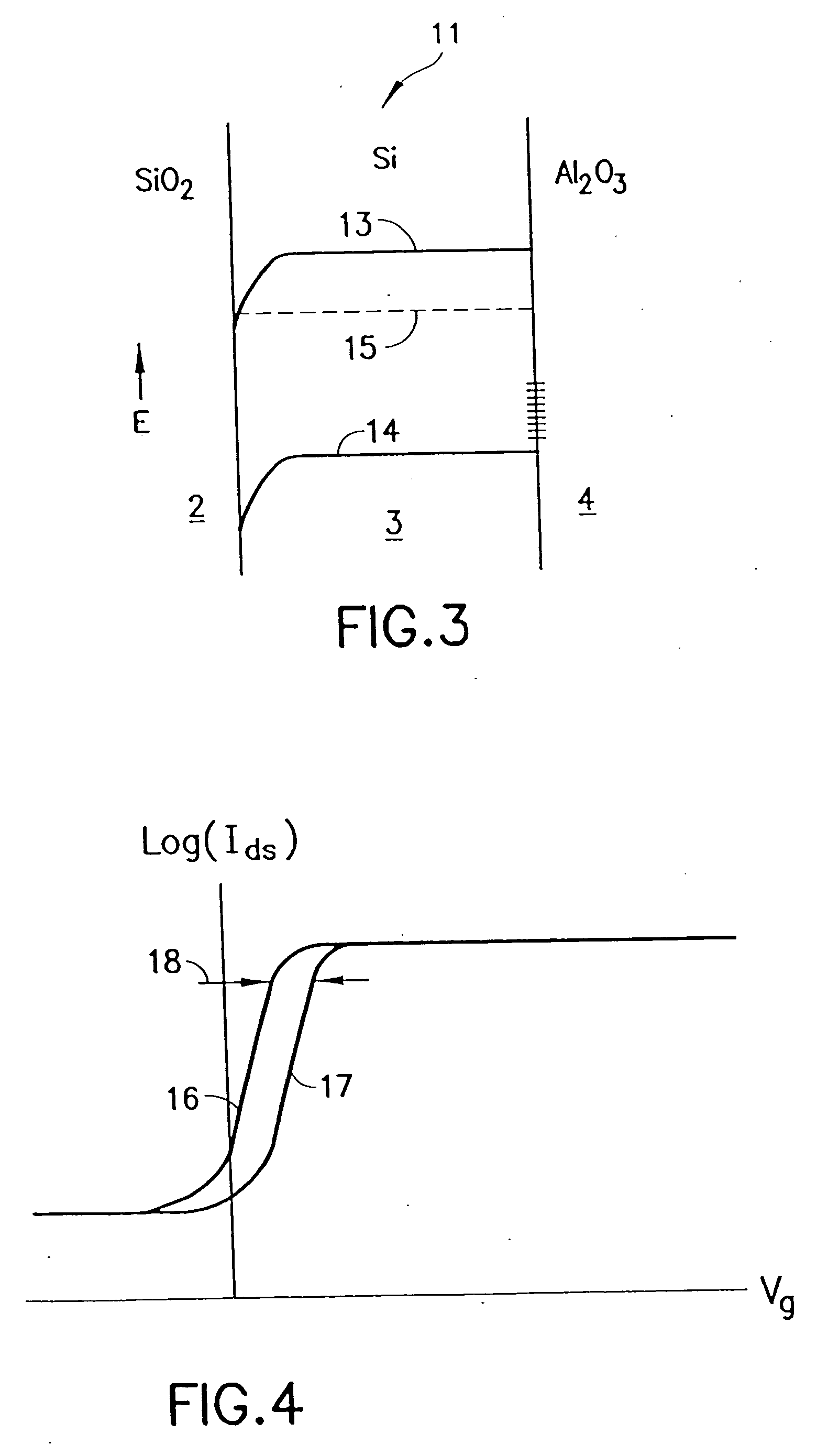

A method for eliminating the radiation-induced off-state current in the P-channel ultrathin silicon-on-sapphire transistor, by providing a retrograde dopant concentration profile that has the effect of moving the Fermi level at the back of the device away from that part of the bandgap where the interface states are located. When the Fermi level does not swing through this area in any region of operation of the device, subthreshold stretchout of the I-V curves does not occur.

Owner:PSEMI CORP

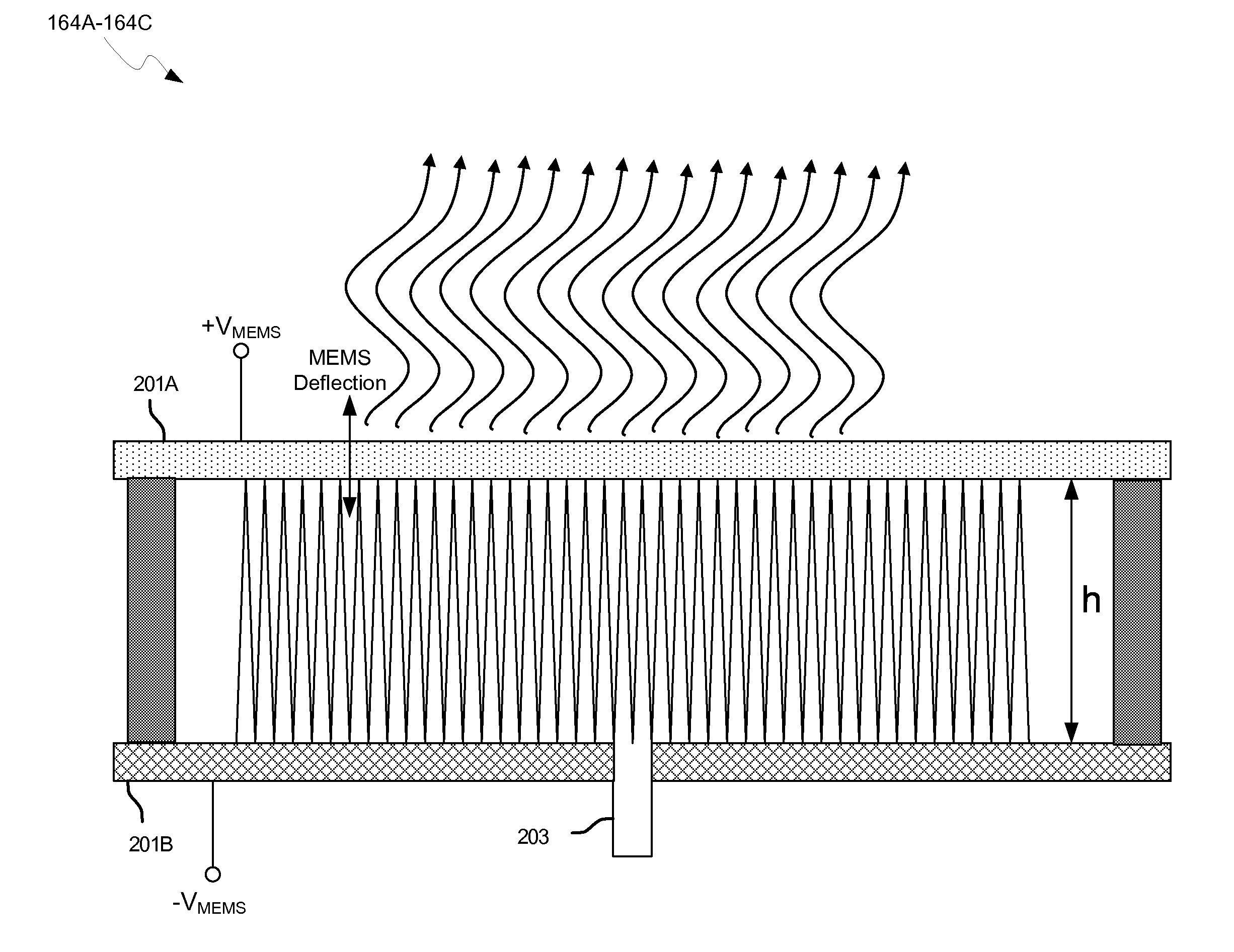

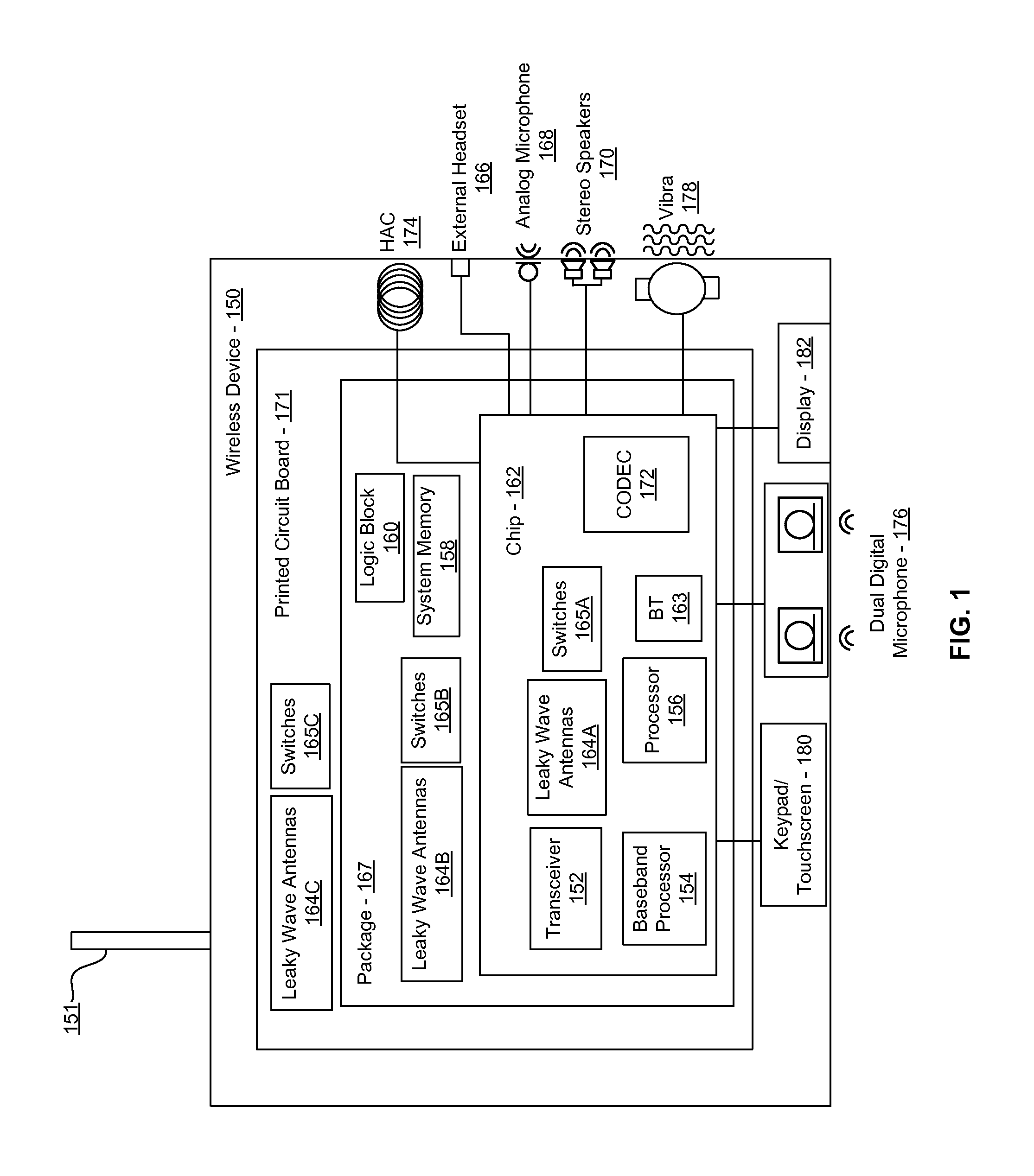

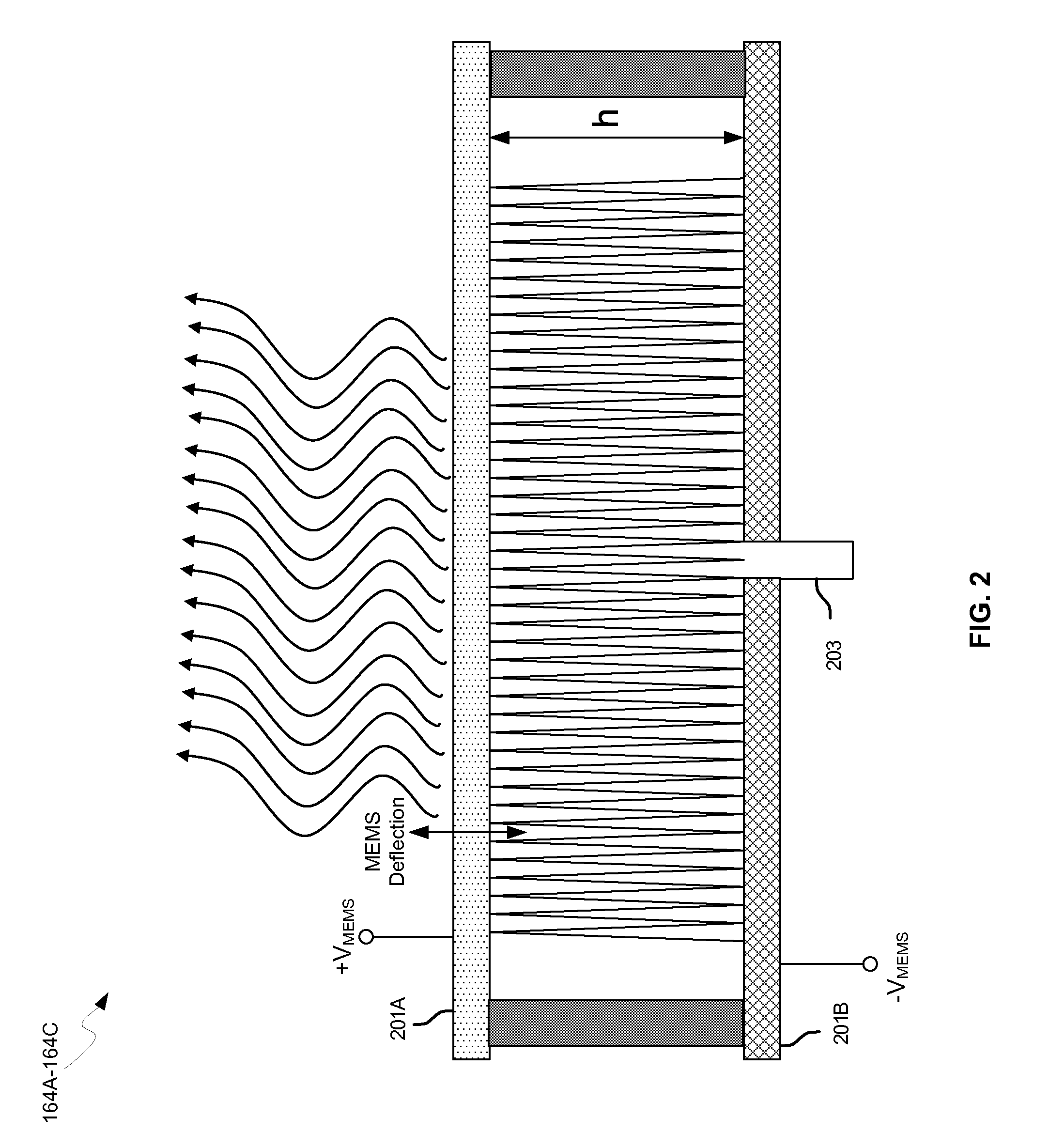

Method and system for communicating via leaky wave antennas on high resistivity substrates

Methods and systems for communicating via leaky wave antennas (LWAs) on high resistivity substrates are disclosed and may include communicating RF signals using one or more LWAs that may be integrated in an integrated circuit (chip) comprising a high resistivity substrate, which may include a silicon-on-sapphire substrate. The LWAs integrated in the chip may be configured to transmit the RF signals at a desired angle from the surface of the chip. The RF signals may be communicated between regions within the chip. The LWAs may include microstrip or coplanar waveguides where the cavity height of the one or more of the LWAs may be configured by controlling spacing between conductive lines in the waveguides. The RF signals may be communicated from the LWAs integrated in the chip to LWAs in a package to which the chip is bonded or in a printed circuit board to which the package is bonded.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Silicon-on-sapphire display with audio transducer and method of fabricating same

A liquid crystal display includes: a) a sapphire substrate; b) a single crystal silicon structure disposed on the sapphire substrate to create a silicon-on-sapphire structure; c) a plurality of liquid crystal capacitors disposed on the silicon-on-sapphire structure; d) integrated self-aligned circuitry formed from the crystal silicon structure, where the circuitry modulates the liquid crystal capacitors such that a video image is generated; and e) an integrated audio transducer disposed on the silicon-on-sapphire structure for generating an audible signal.

Owner:NAVY UNITED STATES OF AMERICA AS REPRESENTATED BY THE SEC OF THE THE

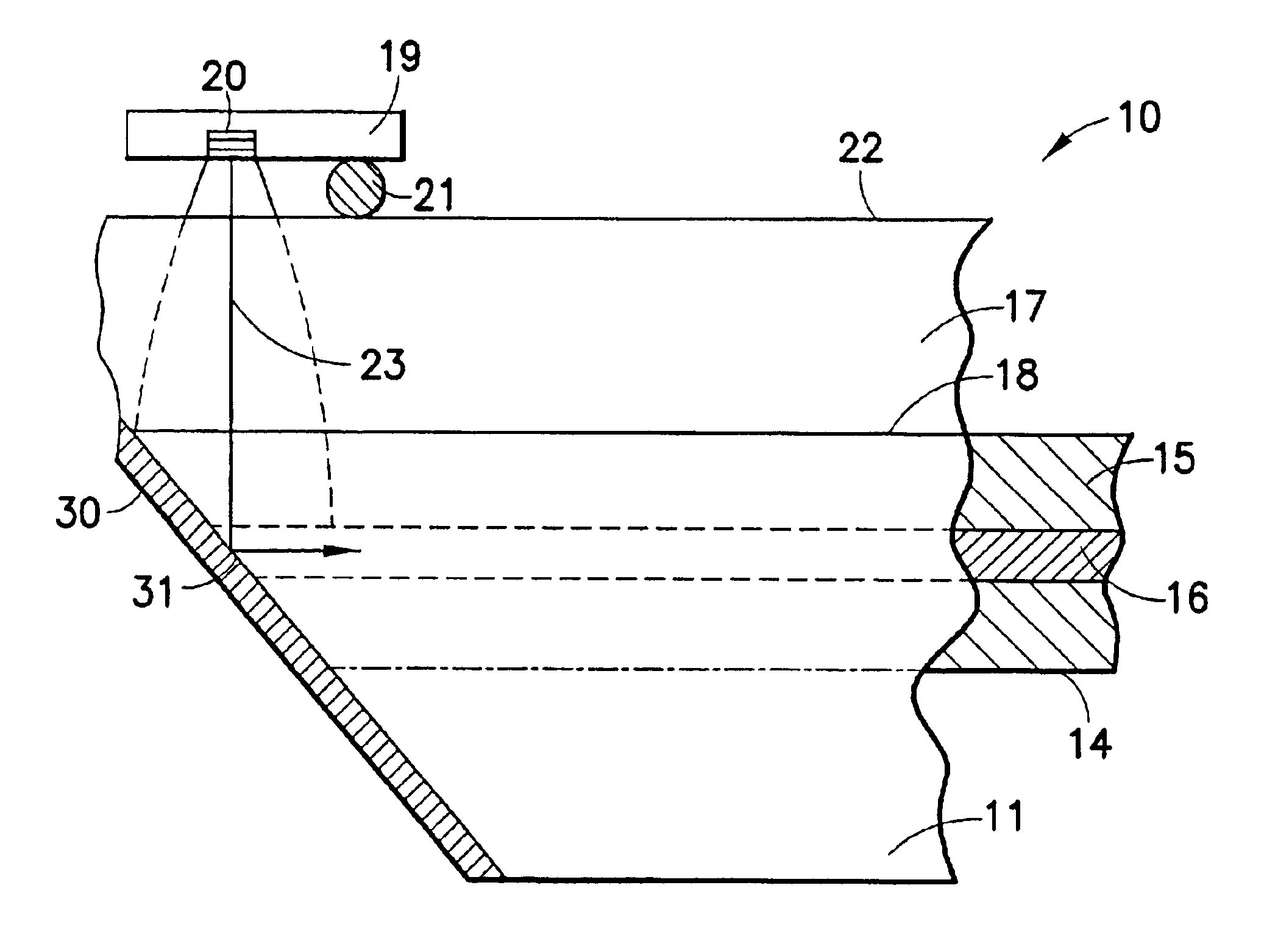

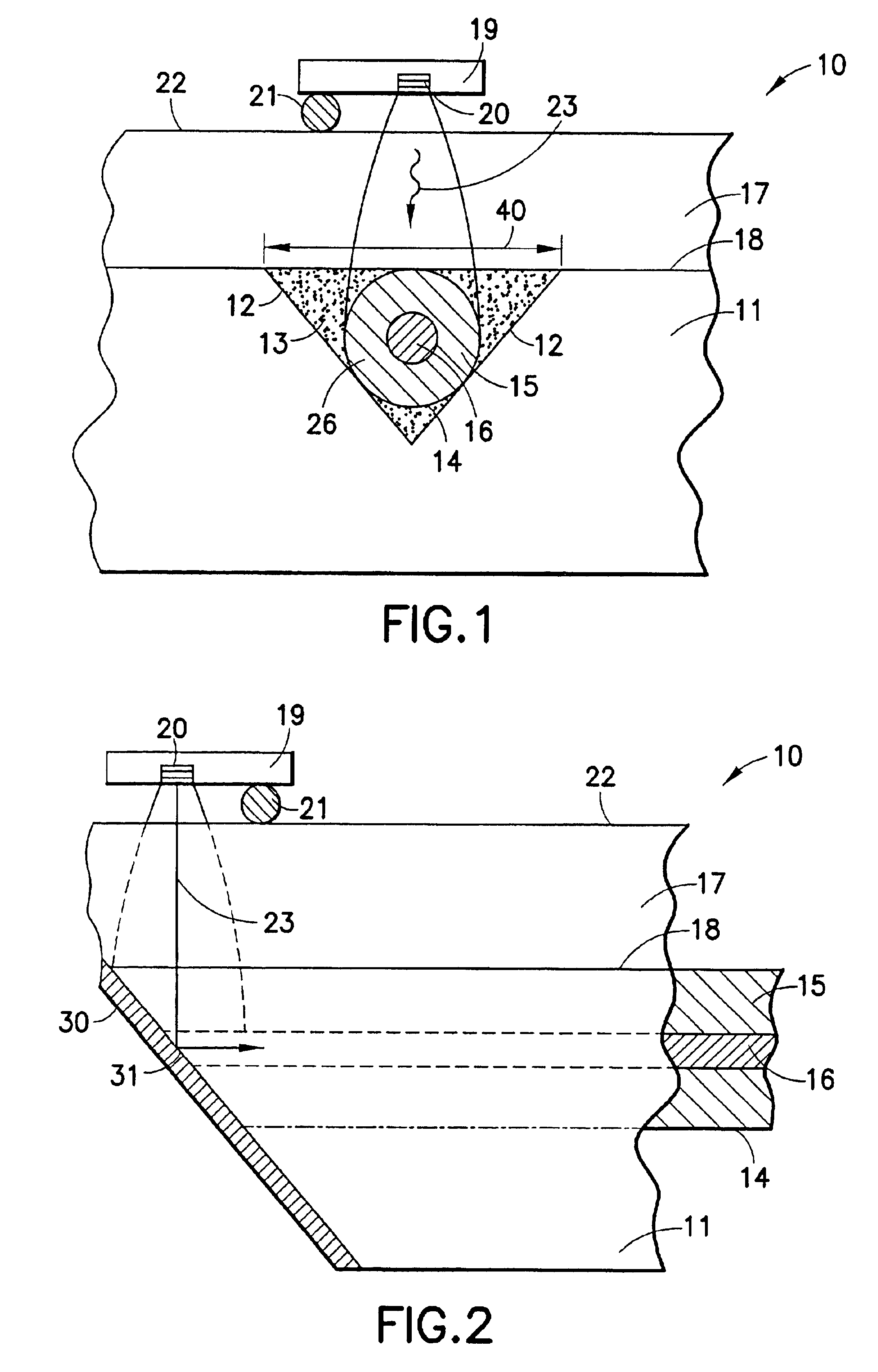

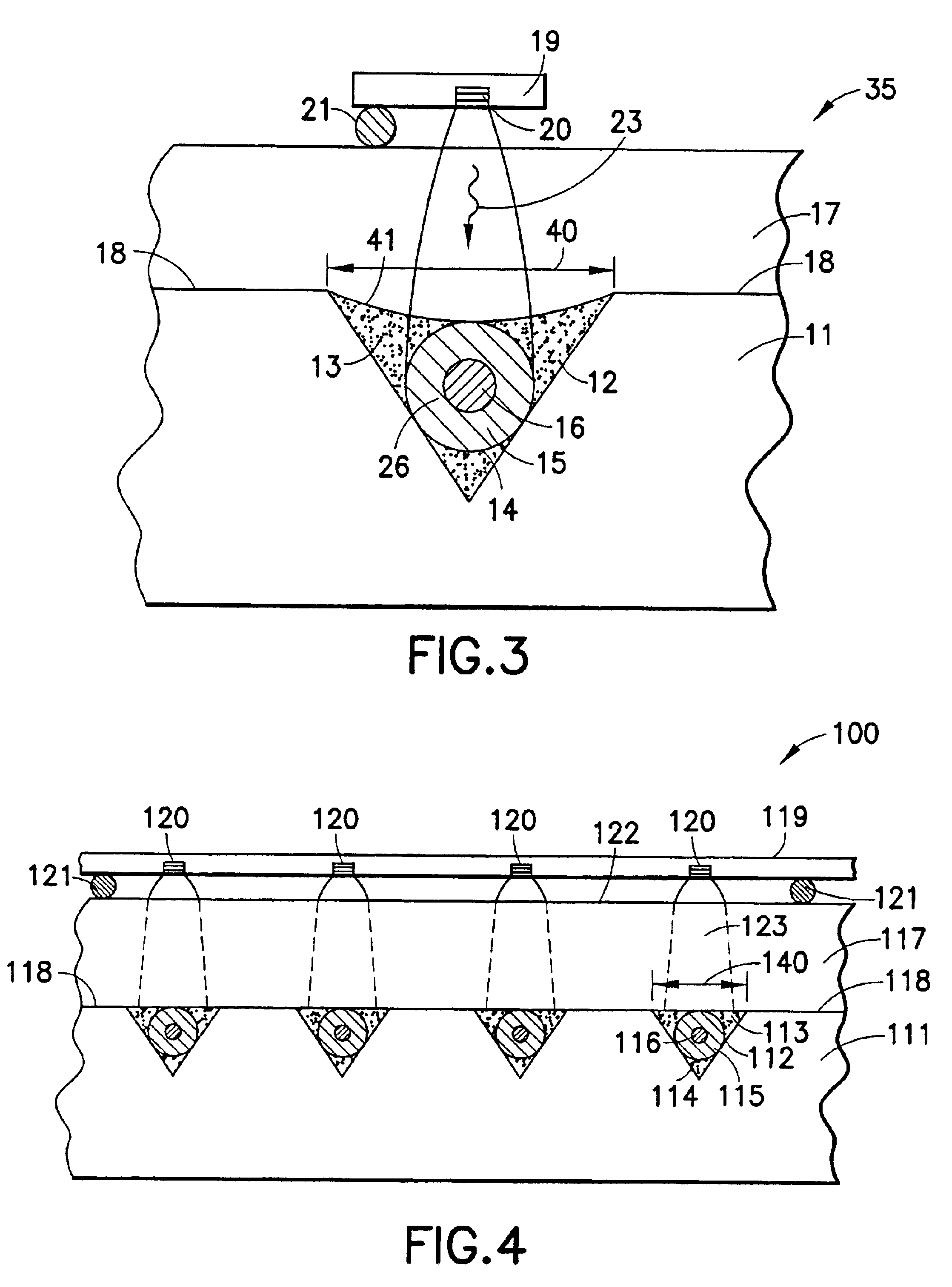

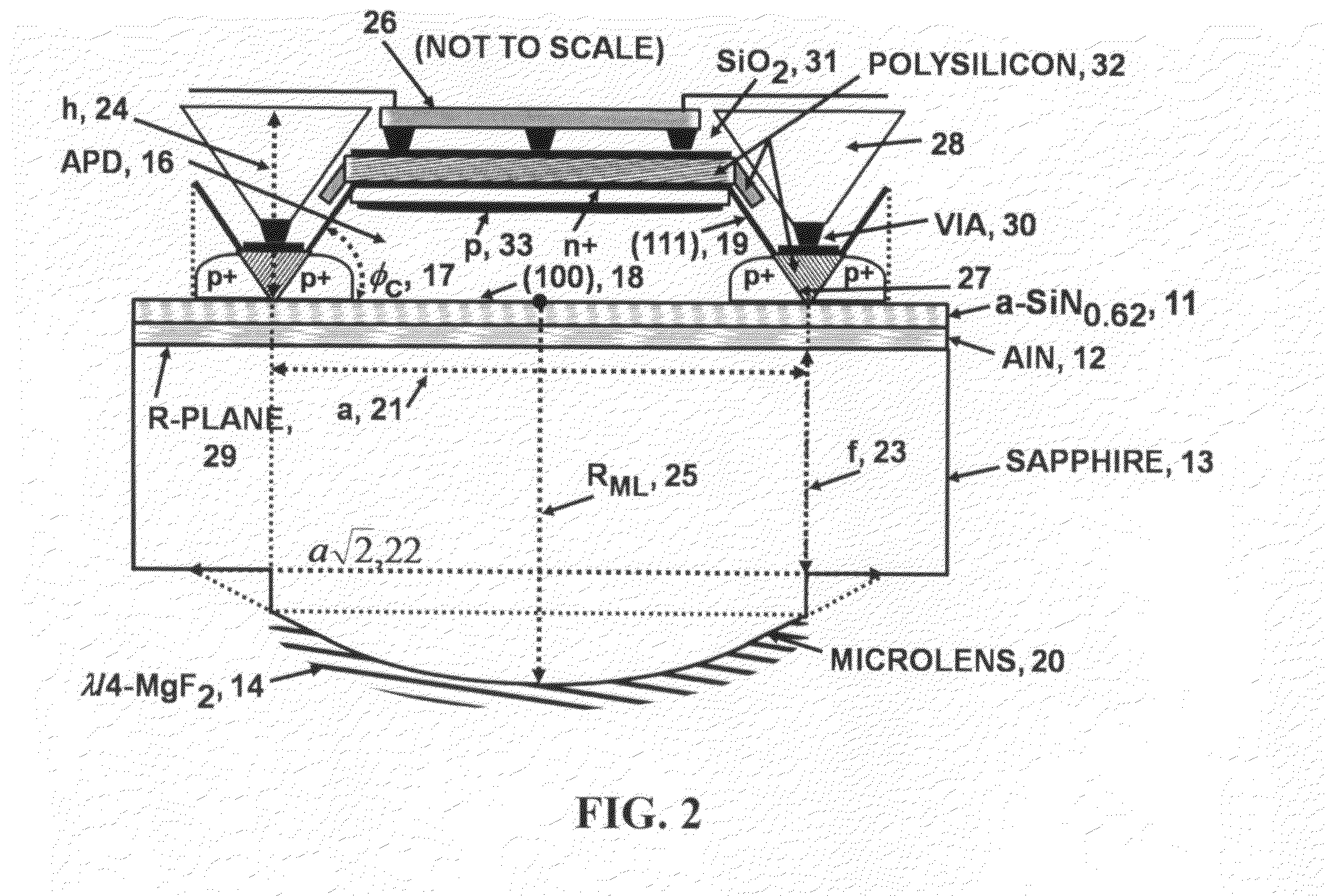

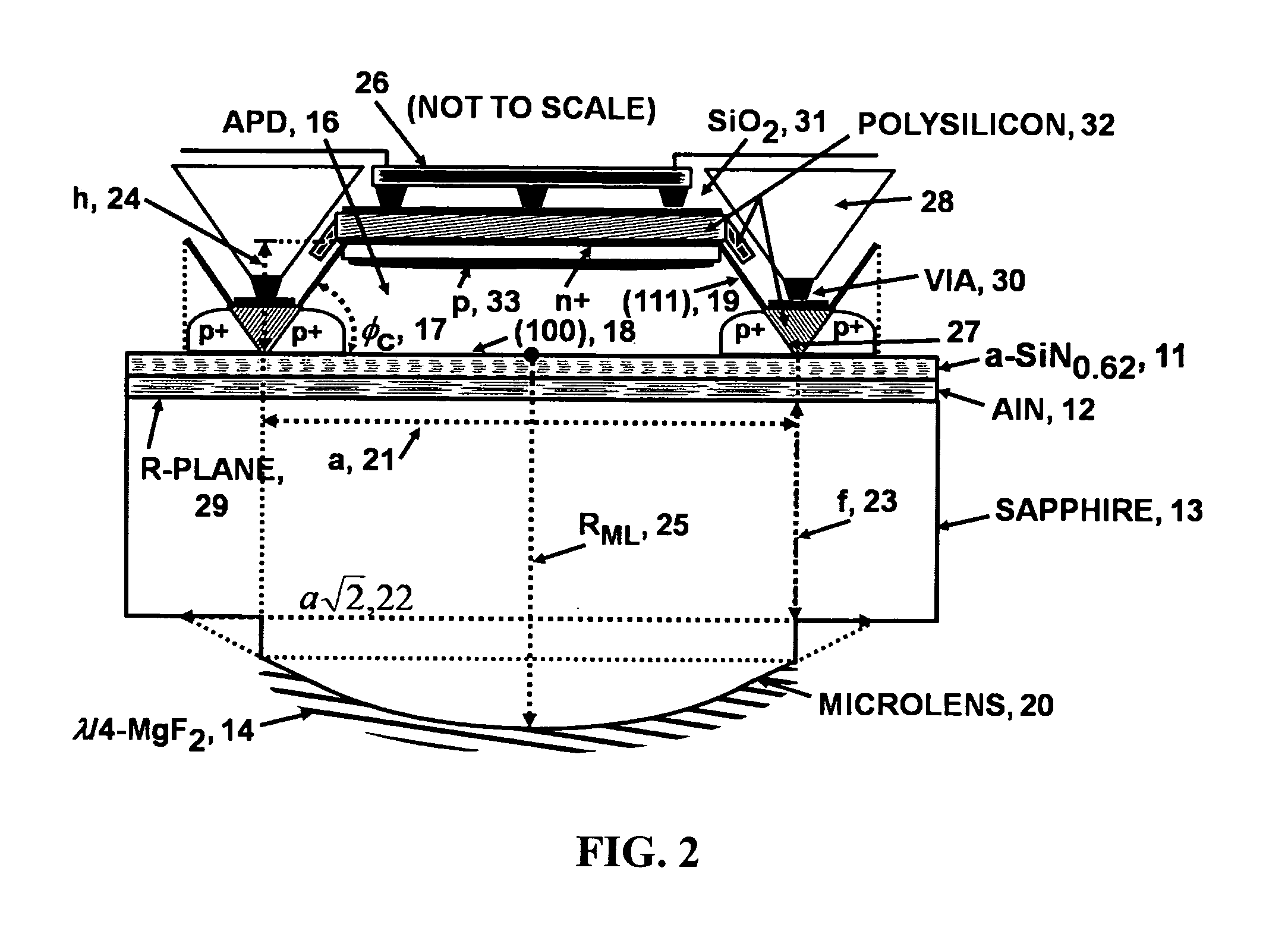

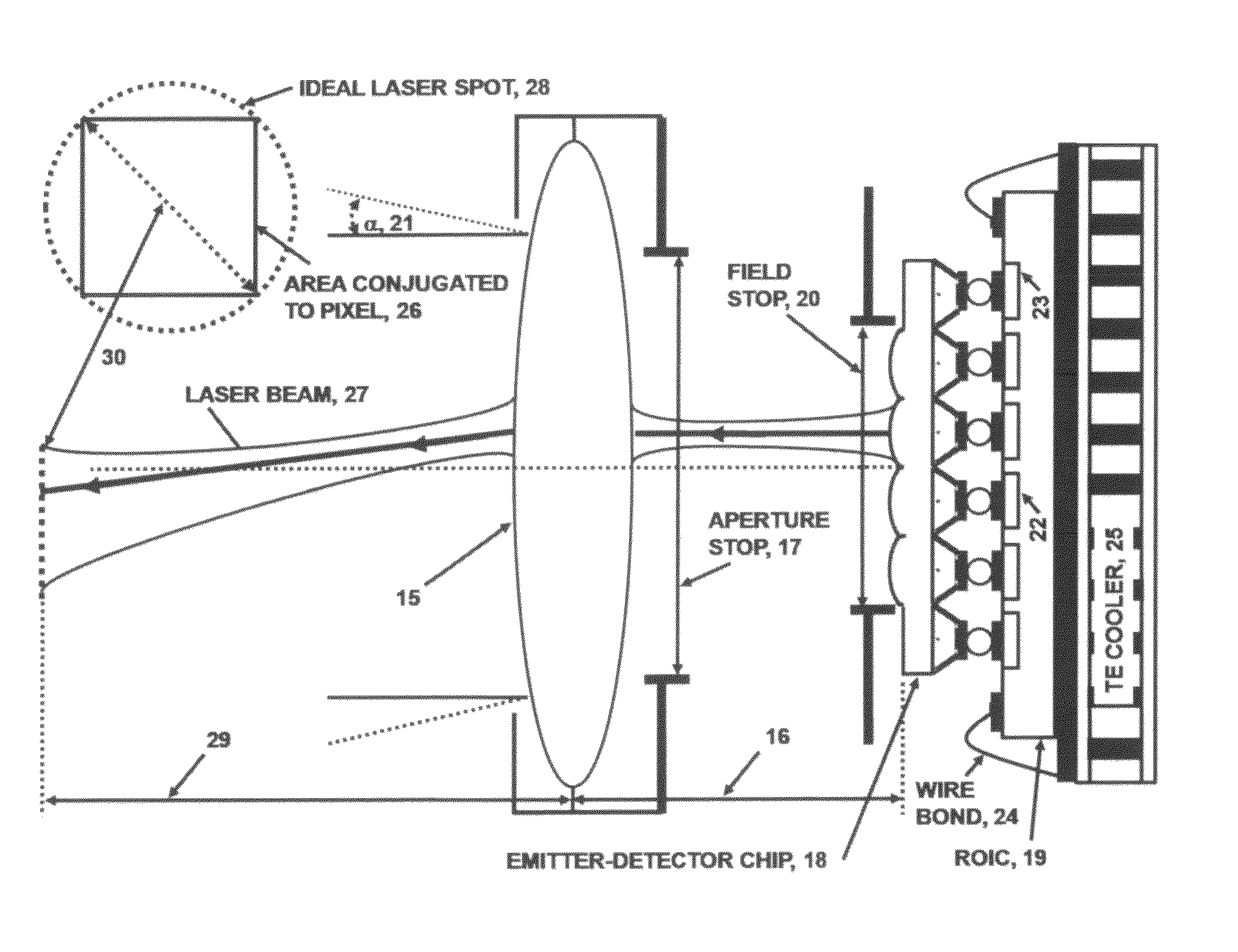

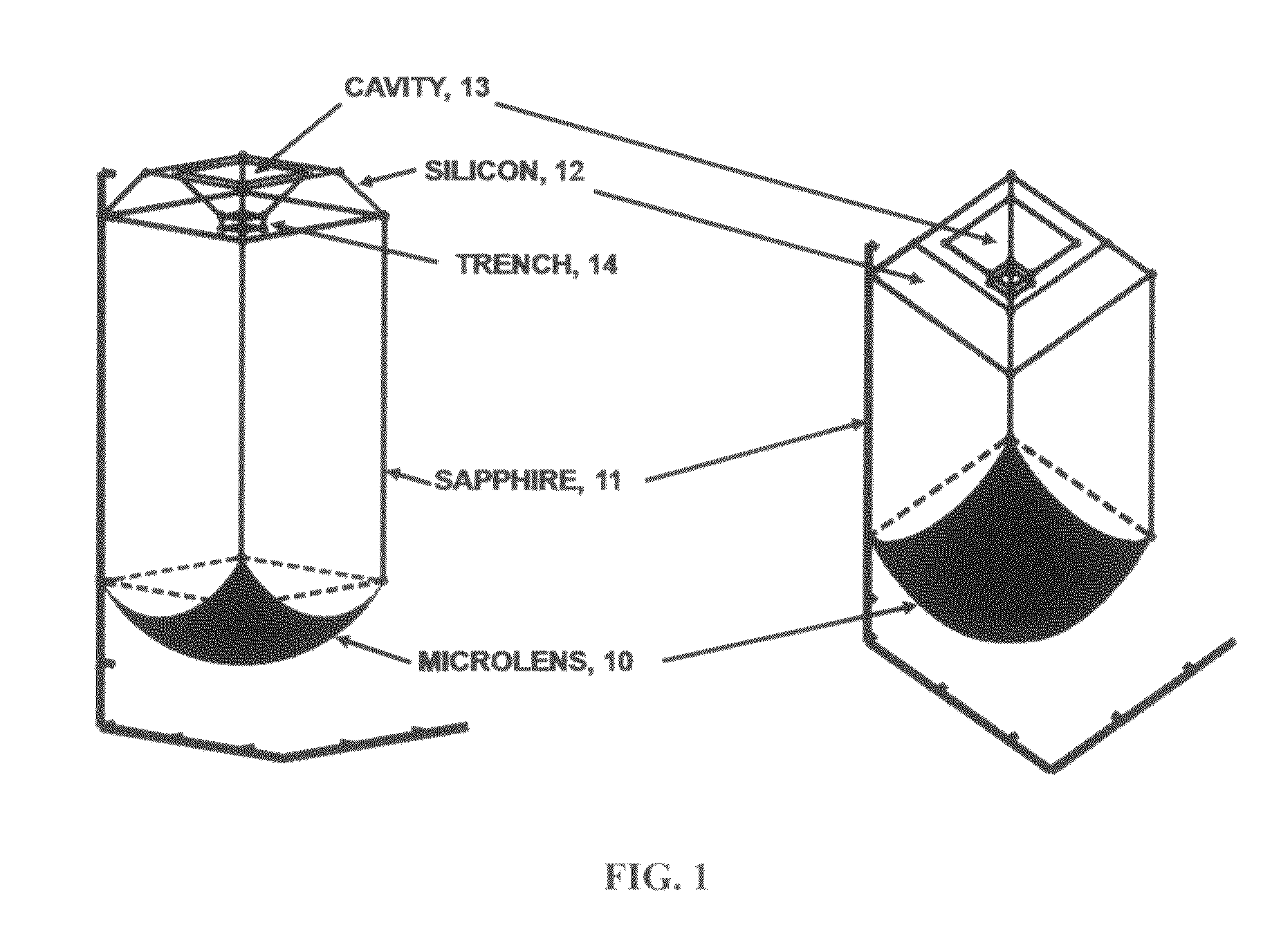

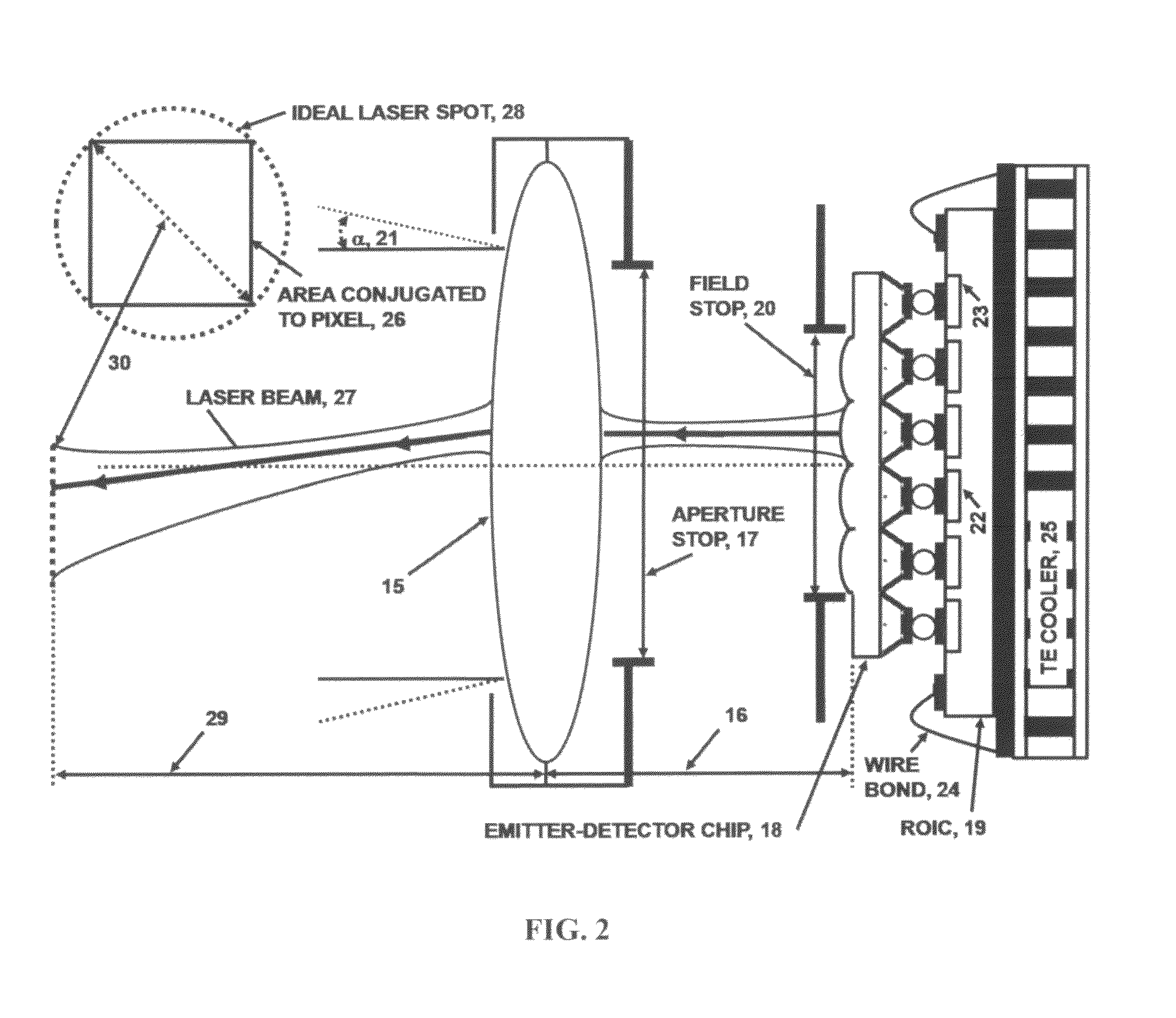

Compact, all solid-state, avalanche photodiode emitter-detector pixel with electronically selectable, passive or active detection mode, for large-scale, high resolution, imaging focal plane arrays

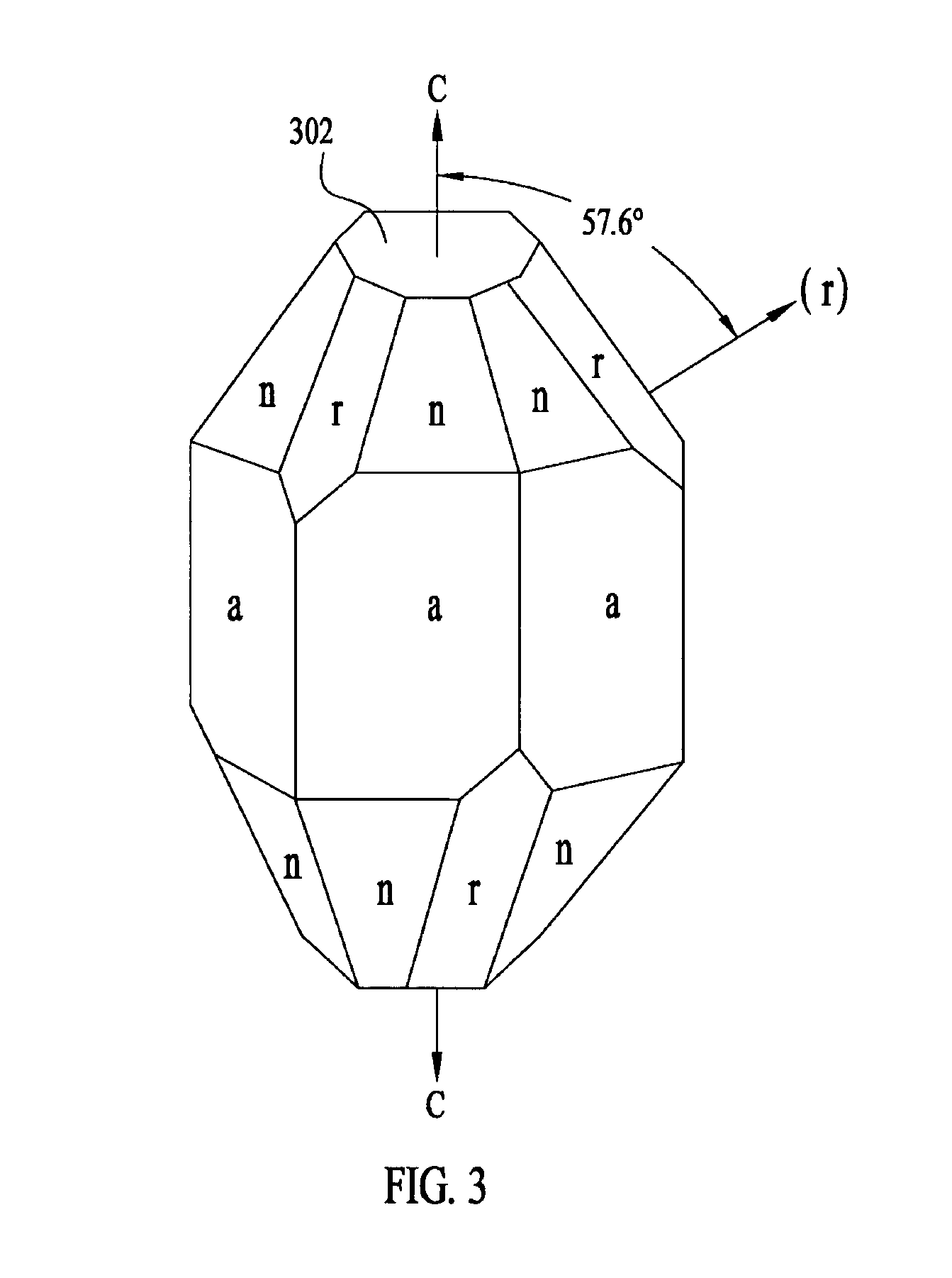

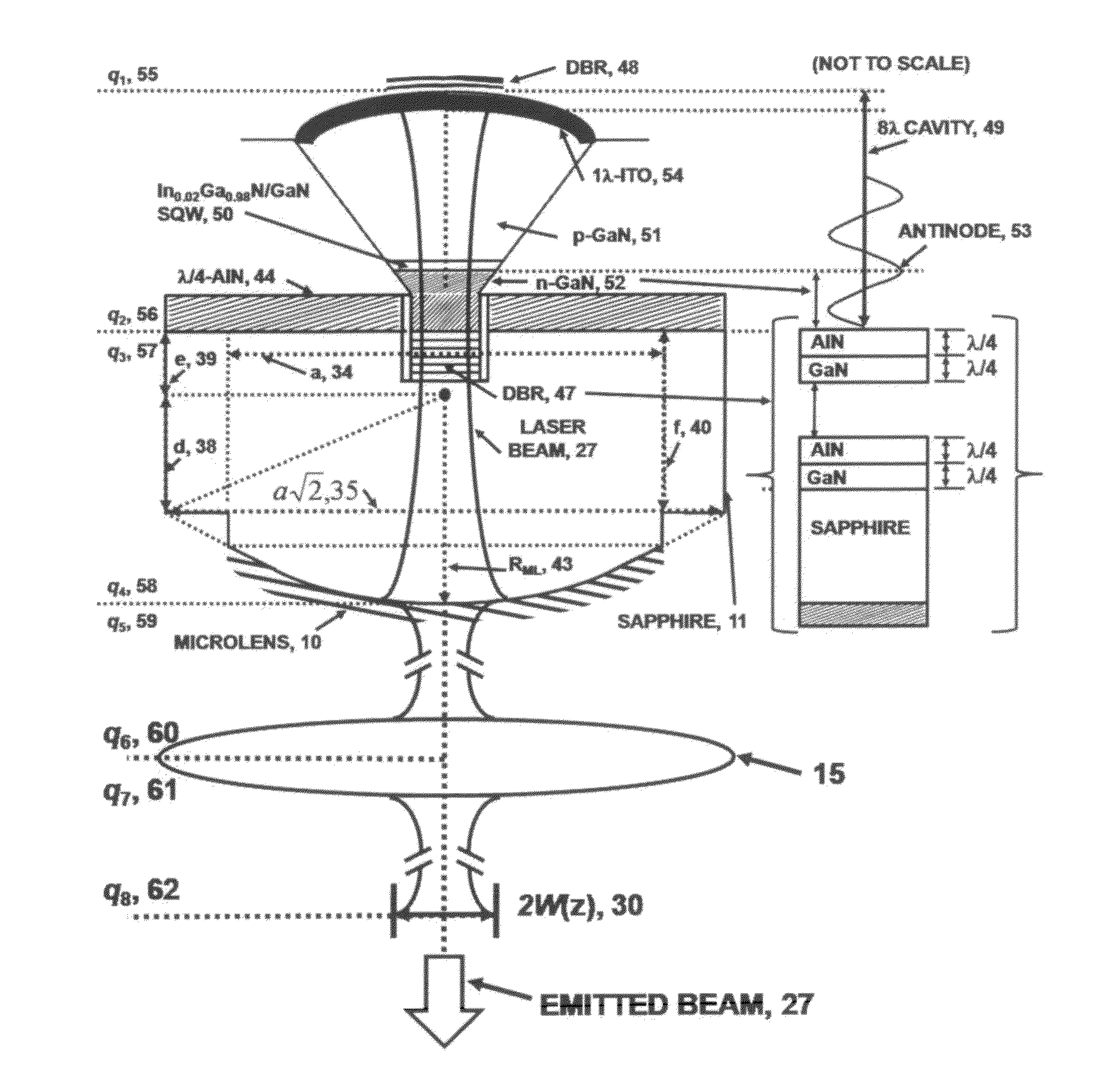

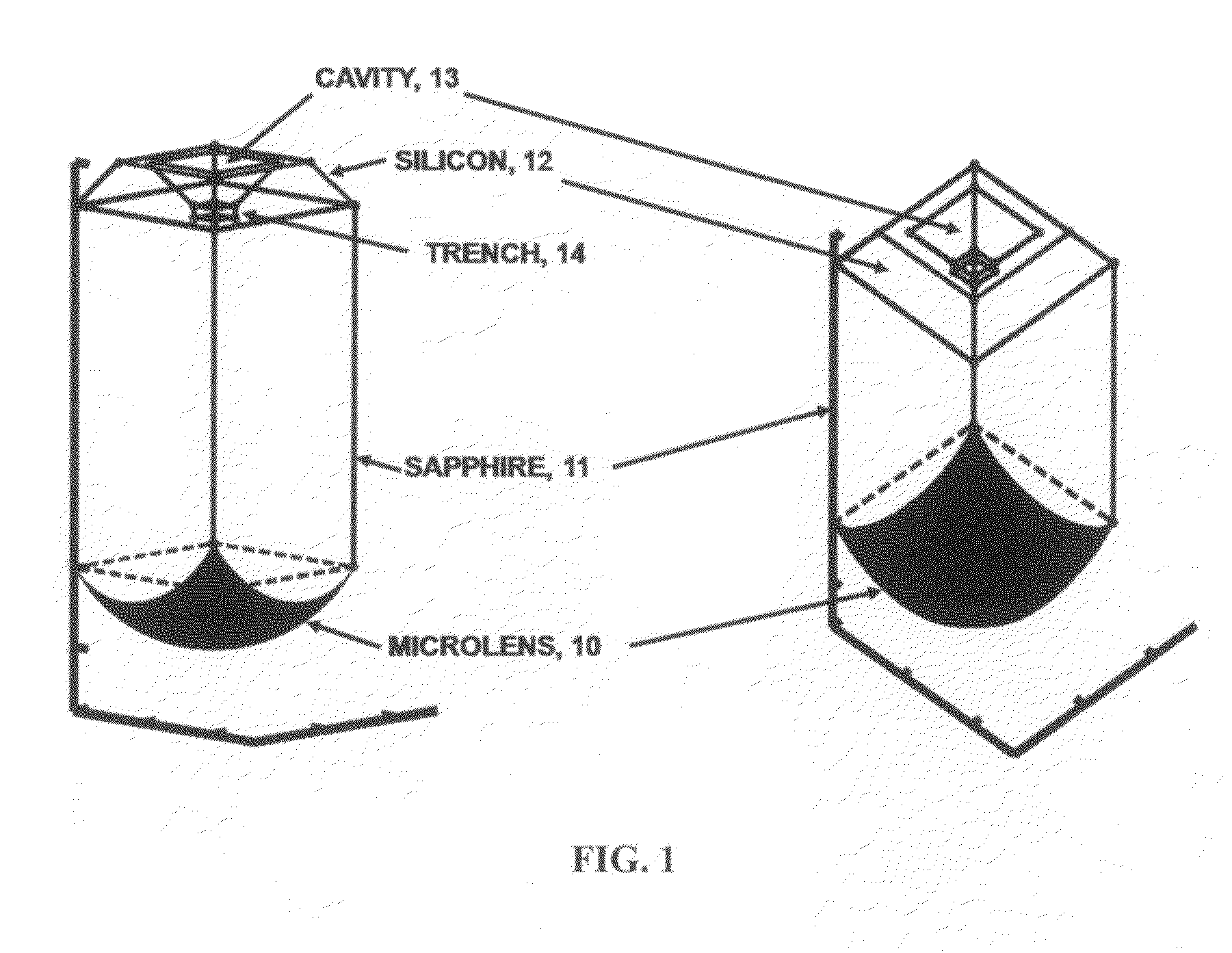

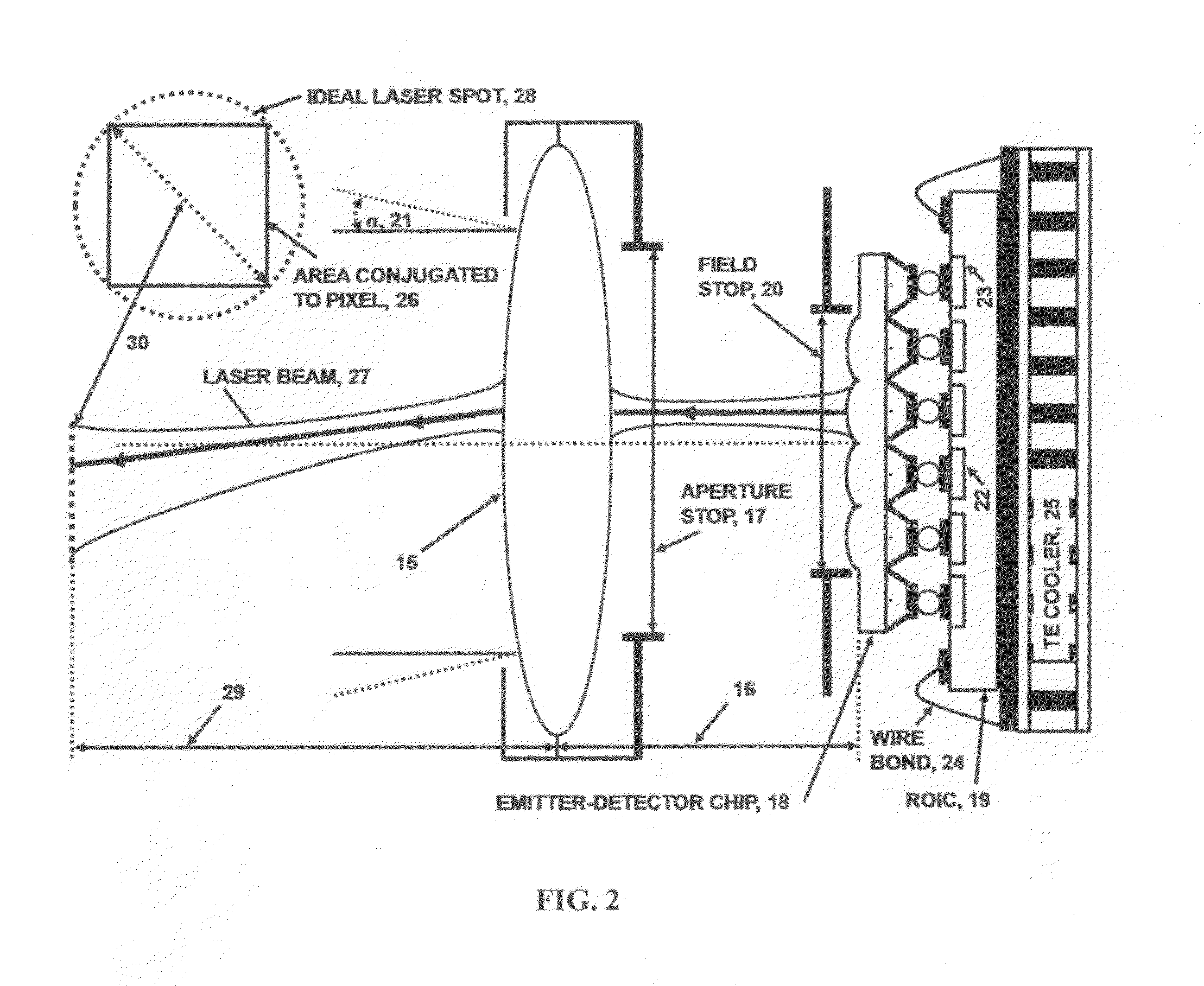

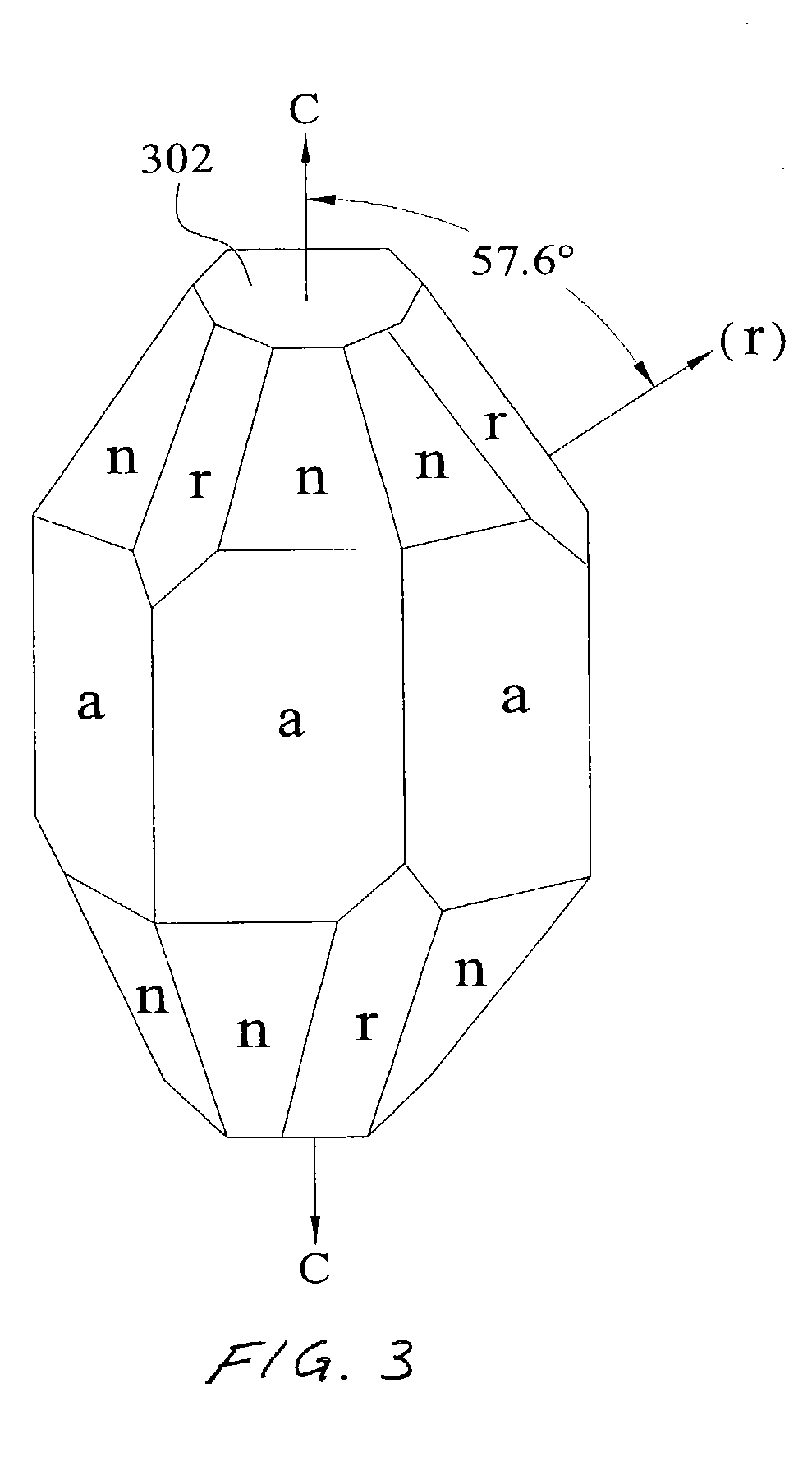

An advanced, back-illuminated, silicon avalanche photodiode (APD) design is presented using silicon-on-sapphire with a novel crystalline aluminum nitride (AlN) antireflective layer between the silicon and R-plane sapphire. The substrate supports optical and electrical integration of a high quantum efficiency silicon APD with a gallium nitride (GaN)-VCSEL diode in each pixel to form a novel, compact, emitter-detector pixel for passive and active 2-D and 3-D high resolution, imaging focal plane arrays. Silicon mesa pixels are anisotropically etched with a central inverted mesa frustum cavity. The APD detector is fabricated in the silicon mesa and the GaN-VCSEL diode is grown epitaxially in the center of the mesa. A sapphire microlens below each pixel collimates the VCSEL beam and focuses optical returns into the APD detector. APDs share a common front-side anode, and VCSELs share a common cathode. The APD cathode is electrically connected to the VCSEL diode anode in each emitter-detector pixel.

Owner:STERN ALVIN GABRIEL

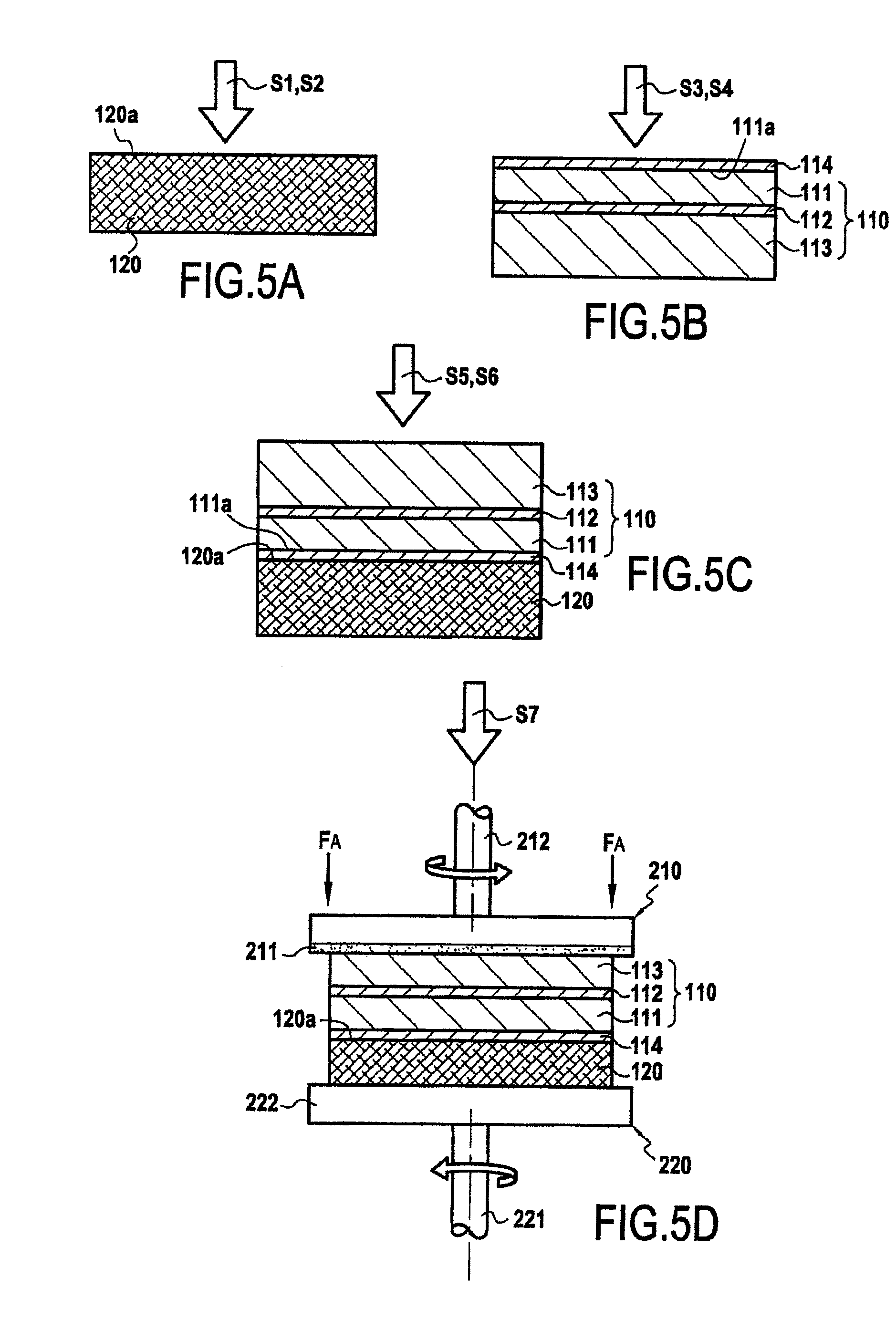

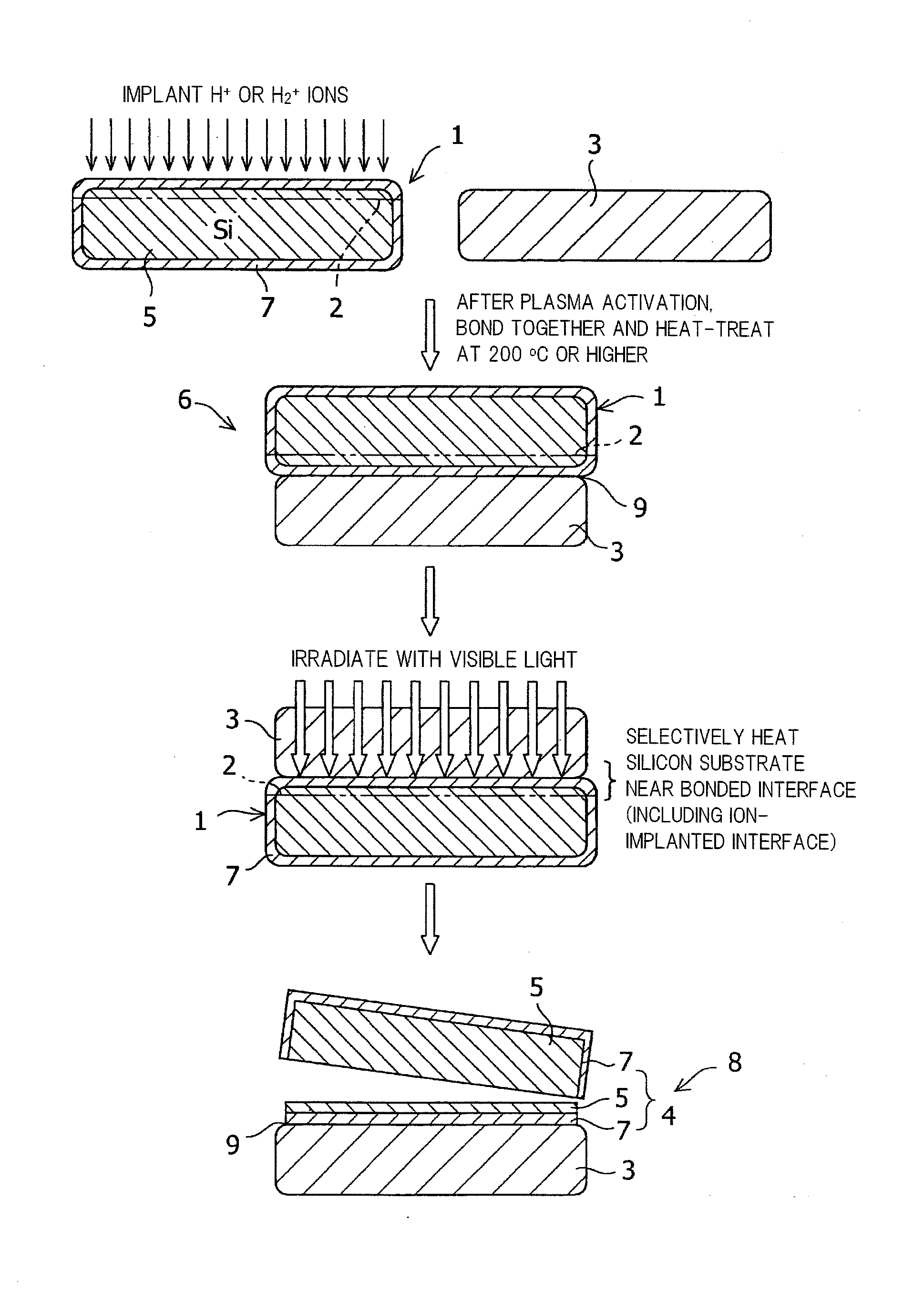

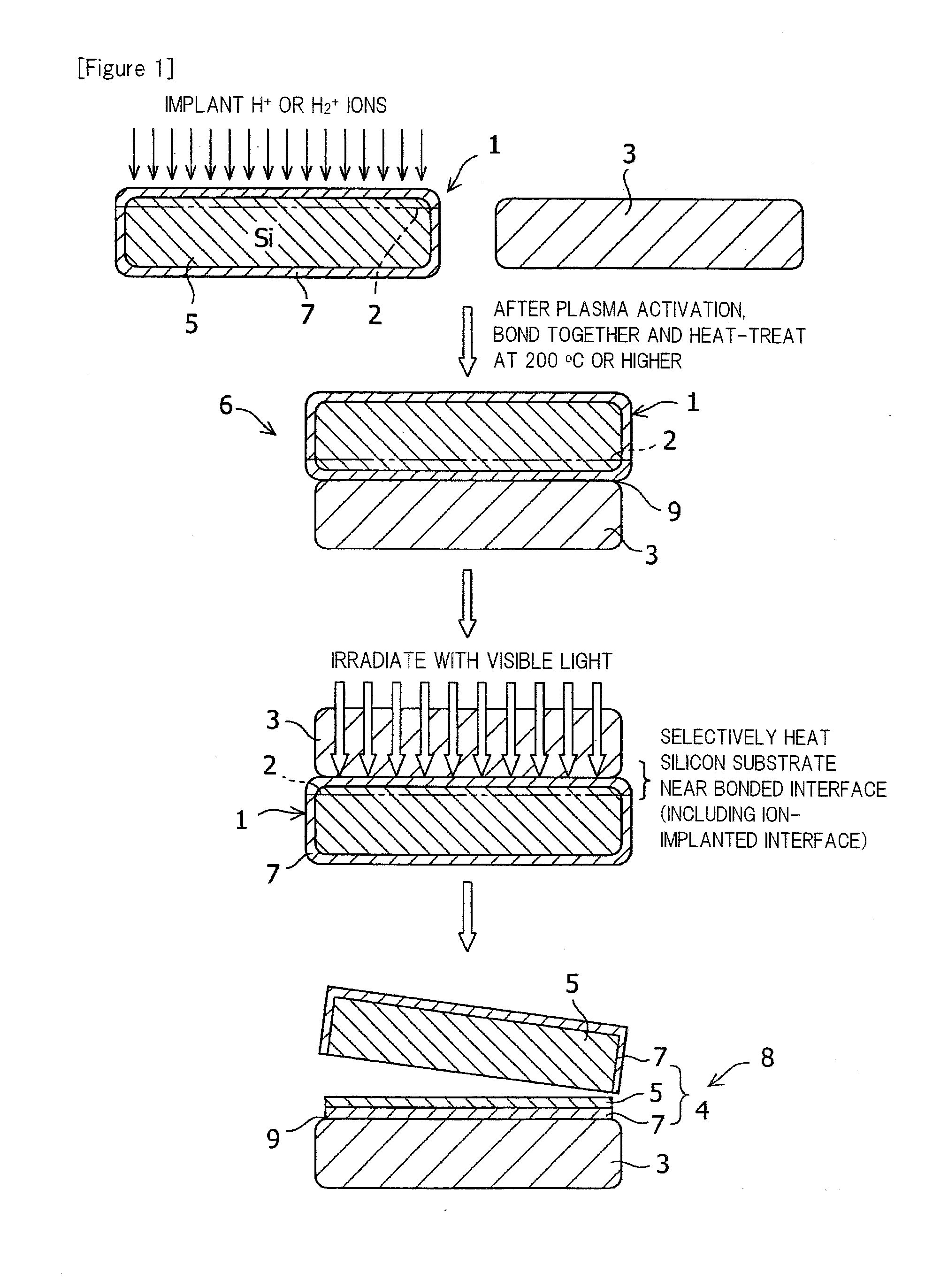

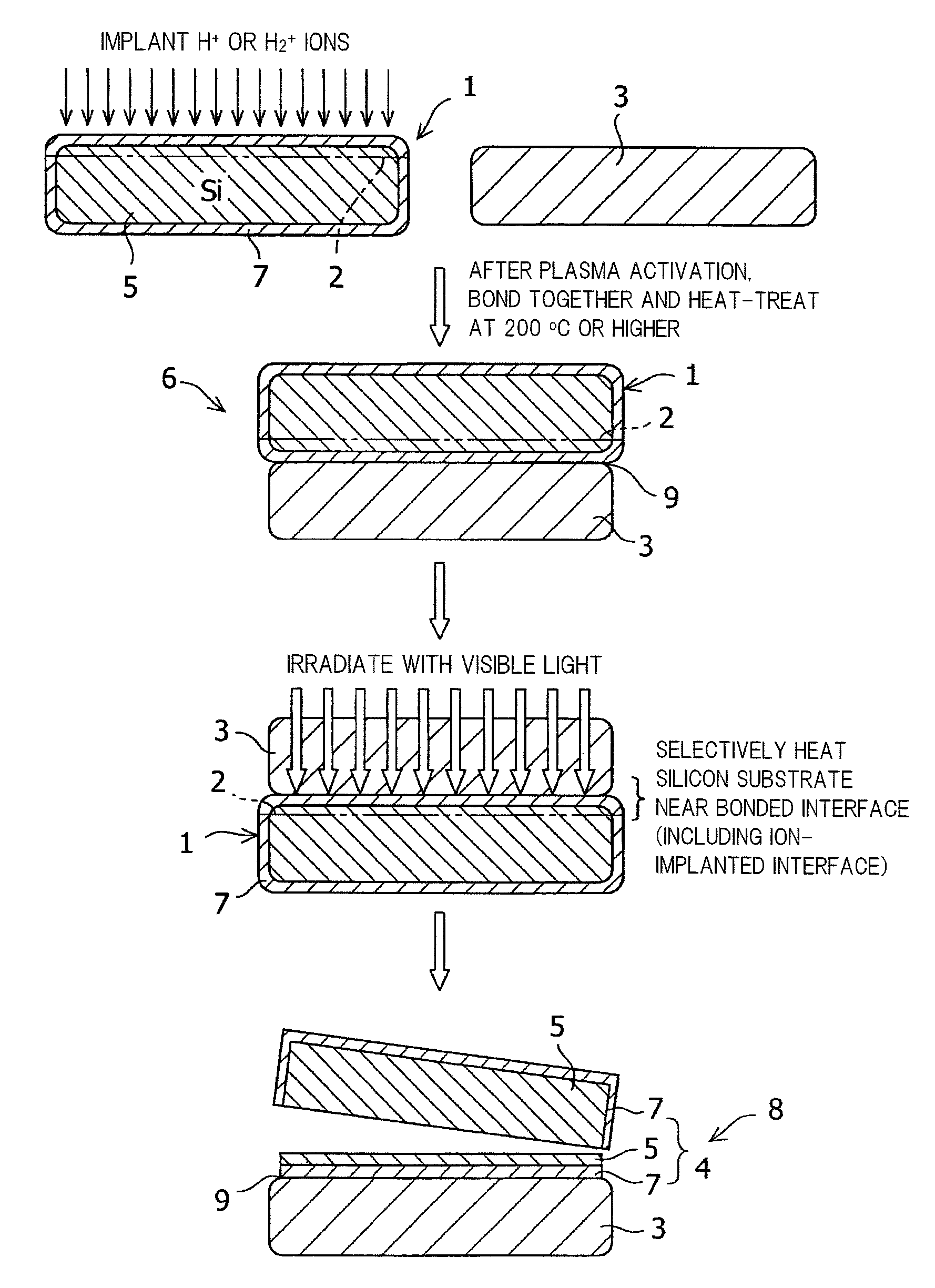

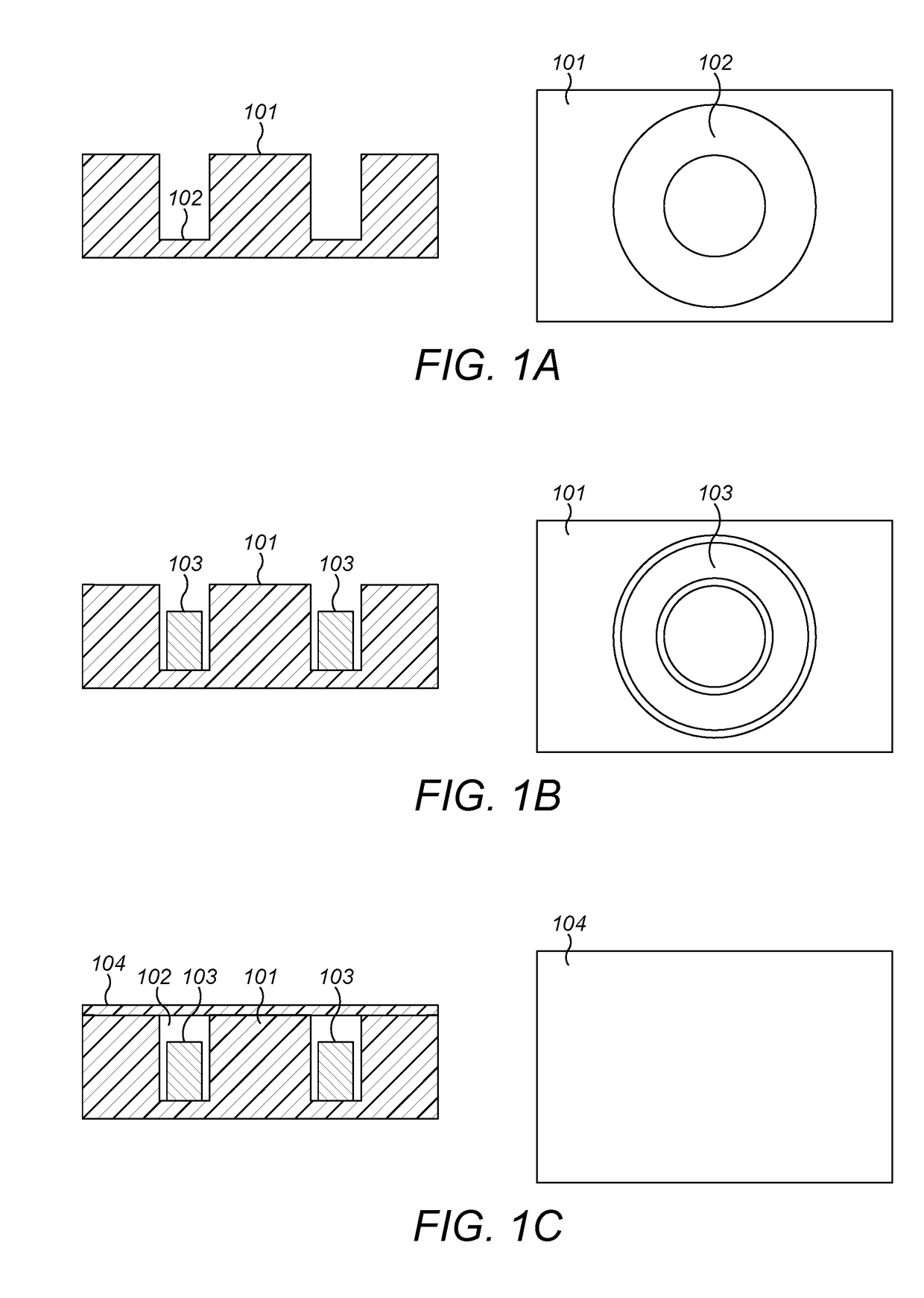

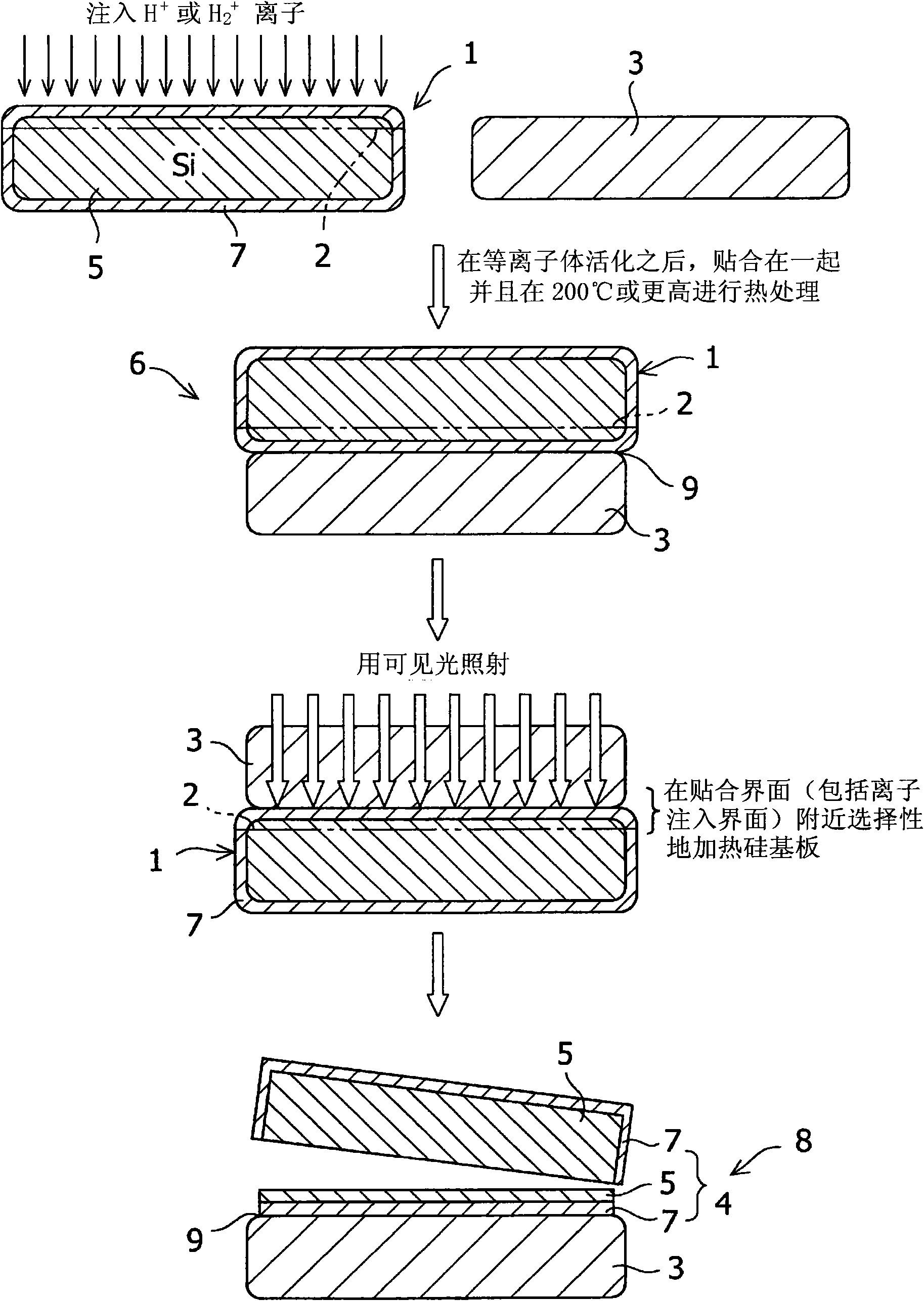

Method of producing a silicon-on-sapphire type heterostructure

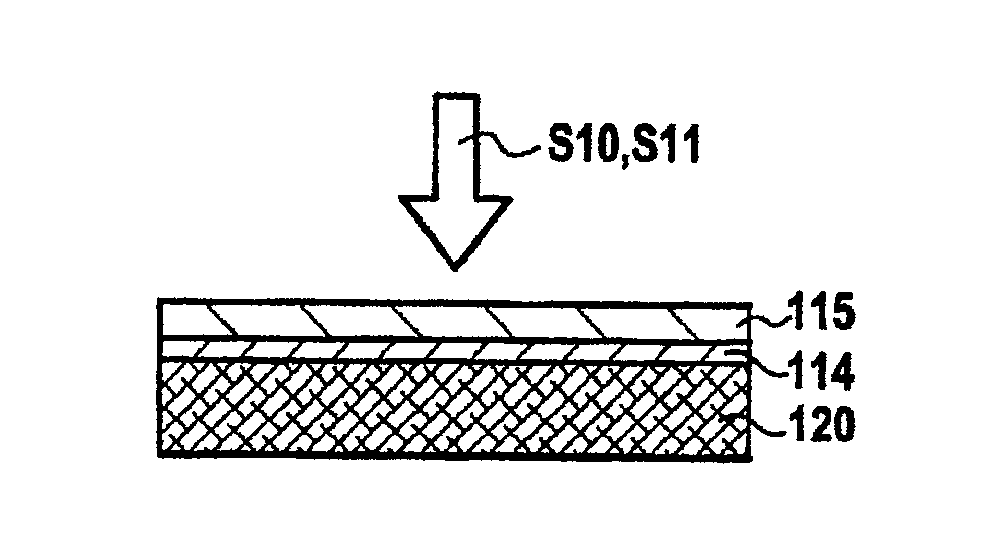

InactiveUS20110195560A1Limiting appearance of defectControlling the riskSemiconductor/solid-state device manufacturingMetallurgySoi substrate

The invention provides a method of producing a heterostructure of the silicon-on-sapphire type, comprising bonding an SOI substrate onto a sapphire substrate and thinning the SOI substrate, thinning being carried out by grinding followed by etching of the SOI substrate. In accordance with the method, grinding is carried out using a wheel with a grinding surface that comprises abrasive particles having a mean dimension of more than 6.7 μm; further, after grinding and before etching, the method comprises a step of post-grinding annealing of the heterostructure carried out at a temperature in the range of 150° C. to 170° C.

Owner:S O I TEC SILICON ON INSULATOR THECHNOLOGIES

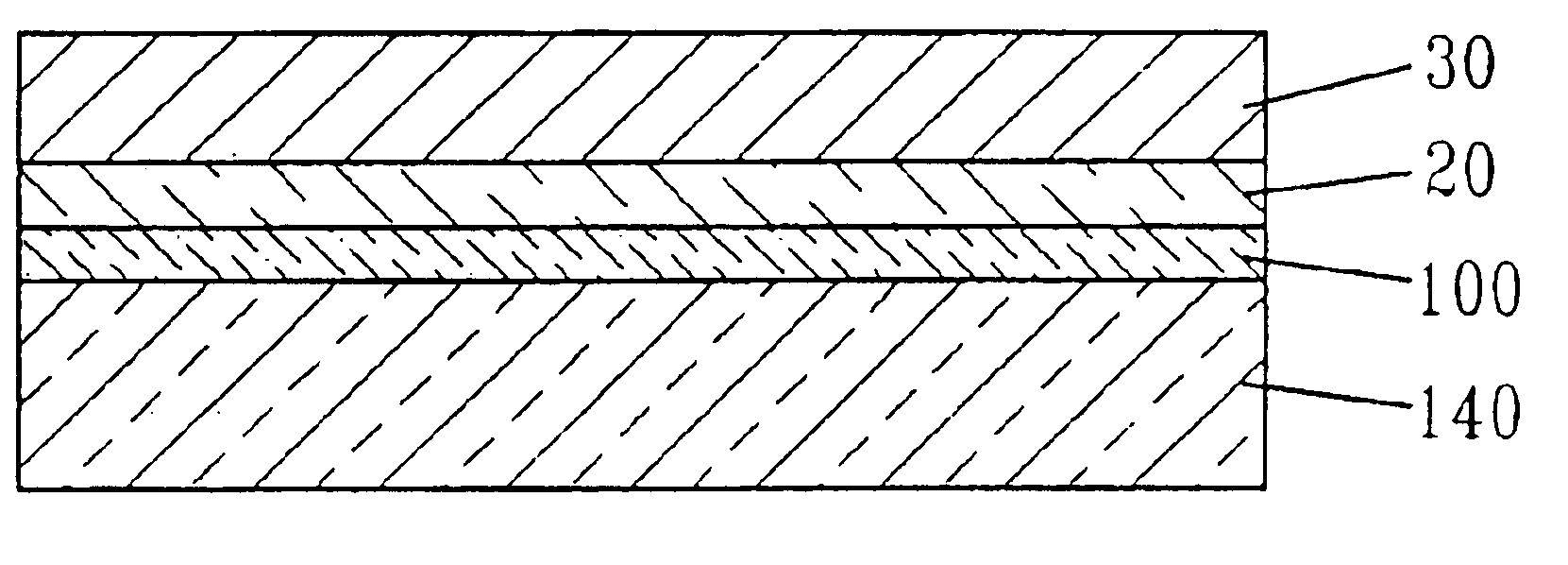

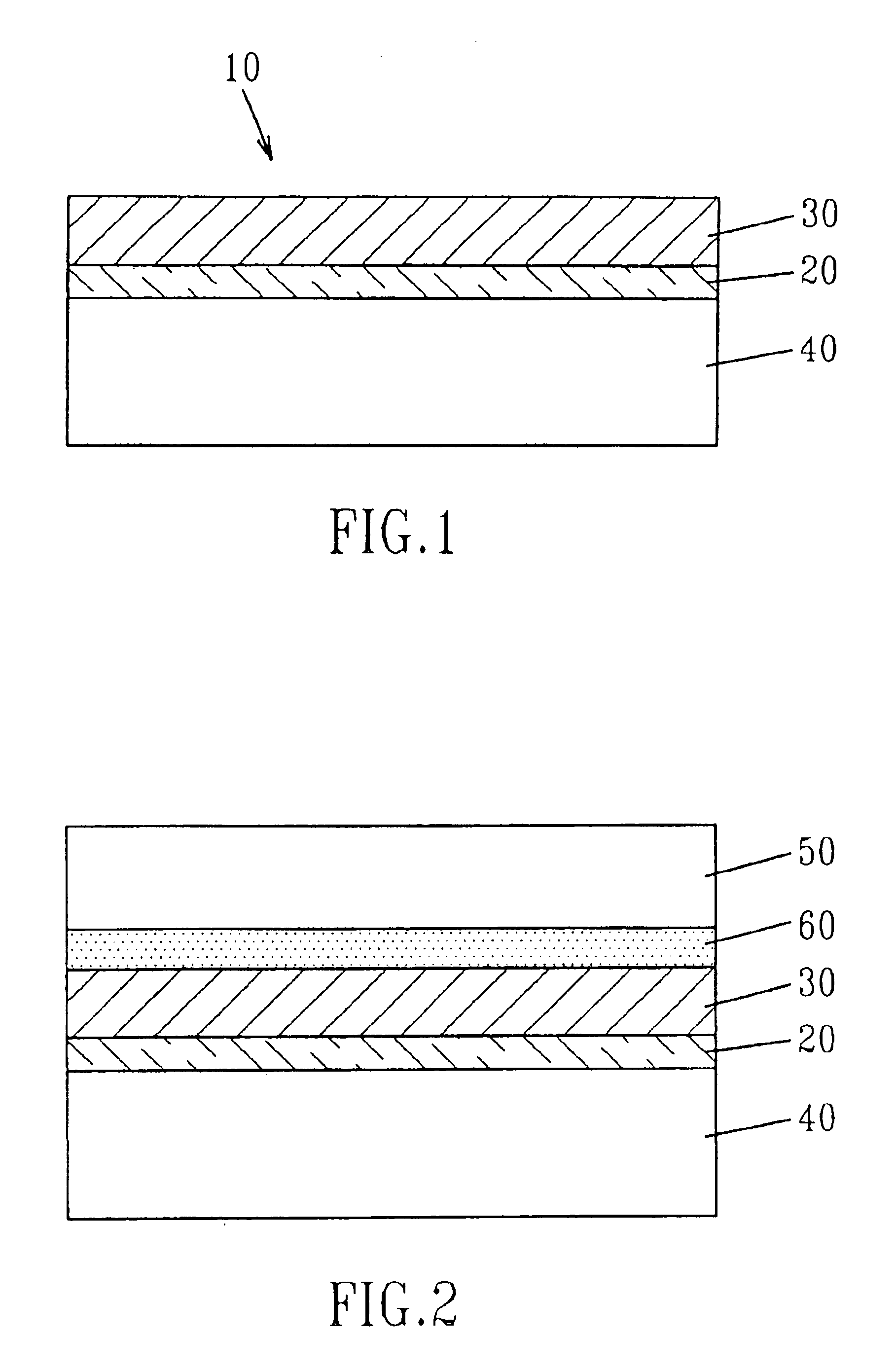

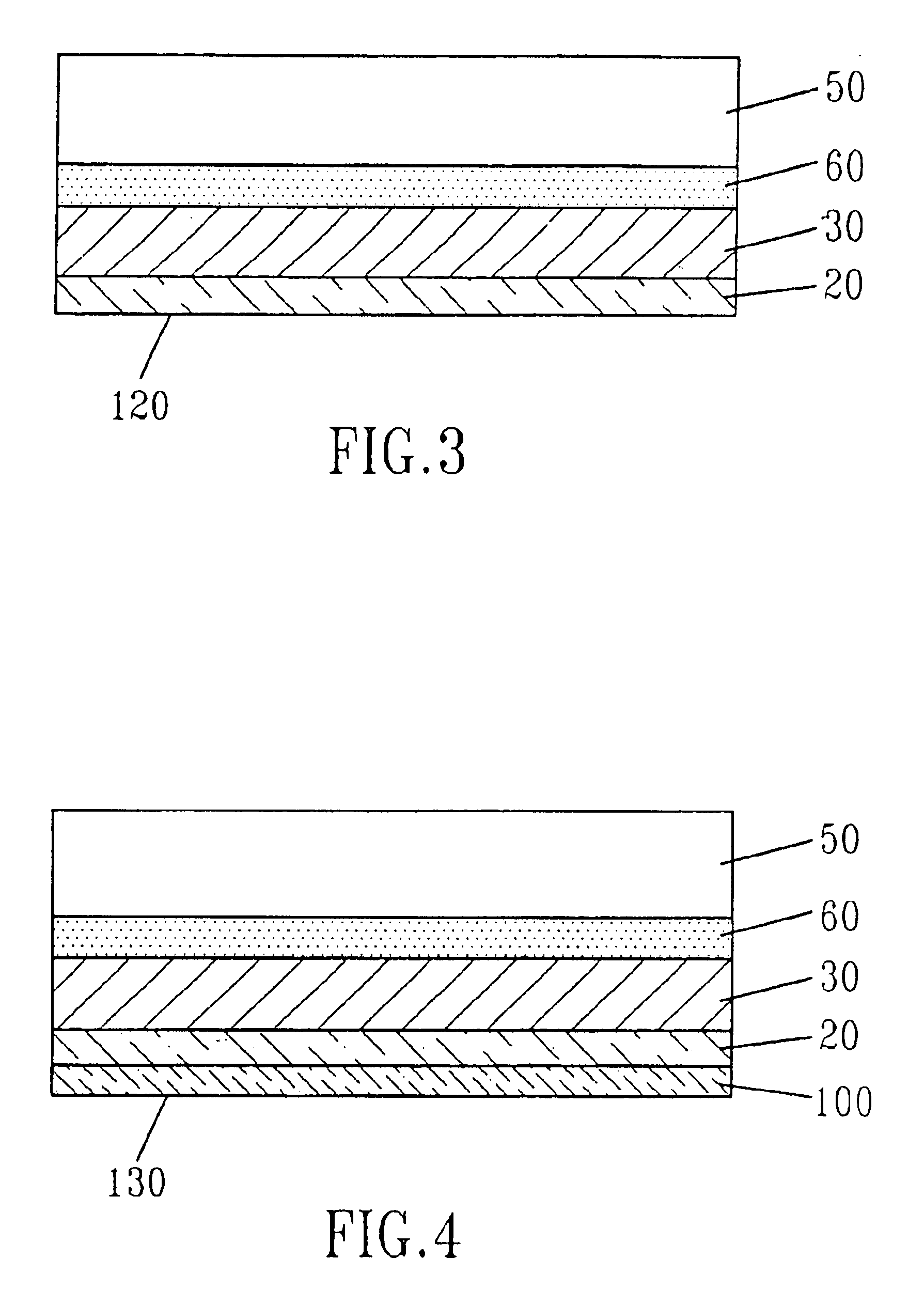

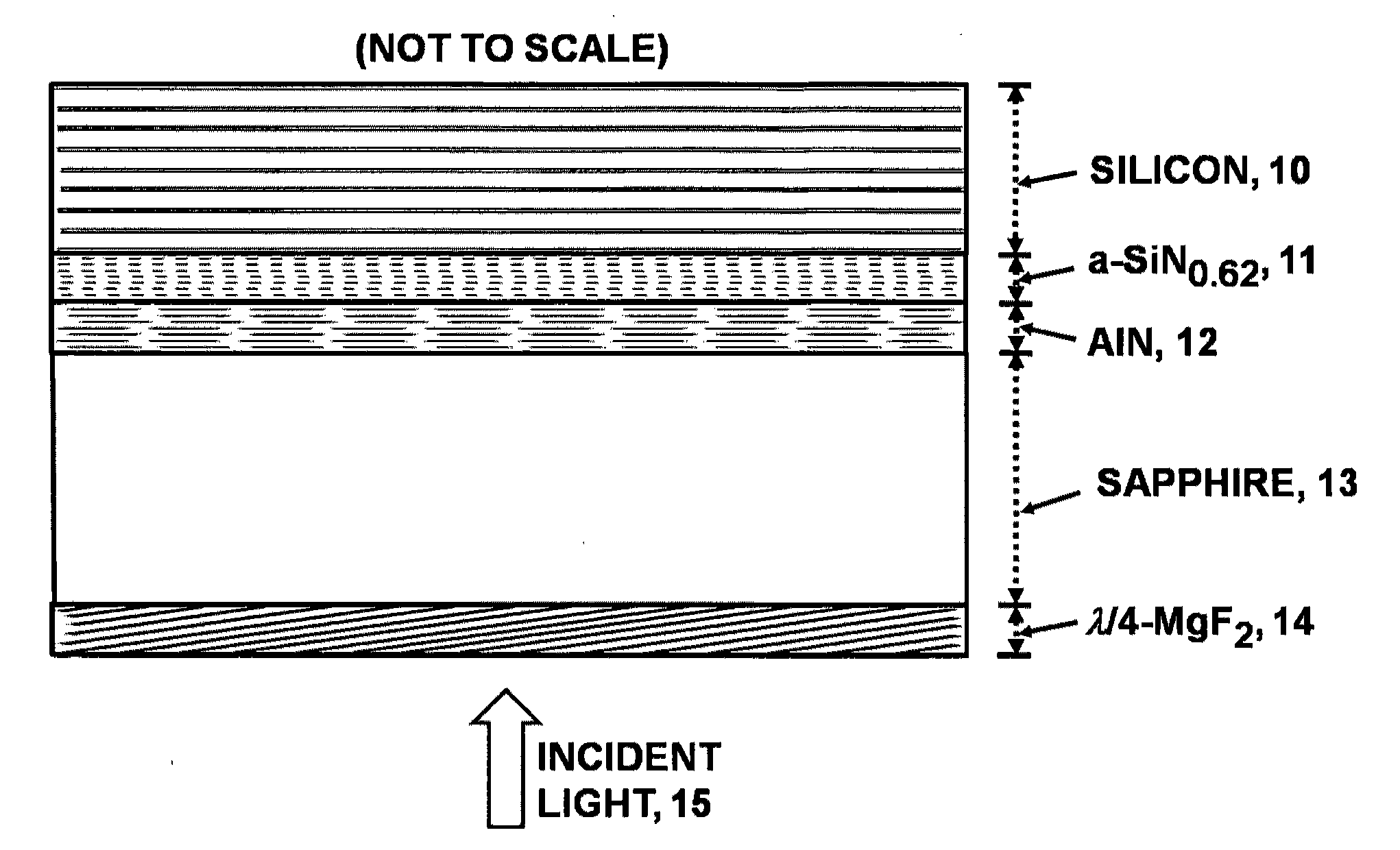

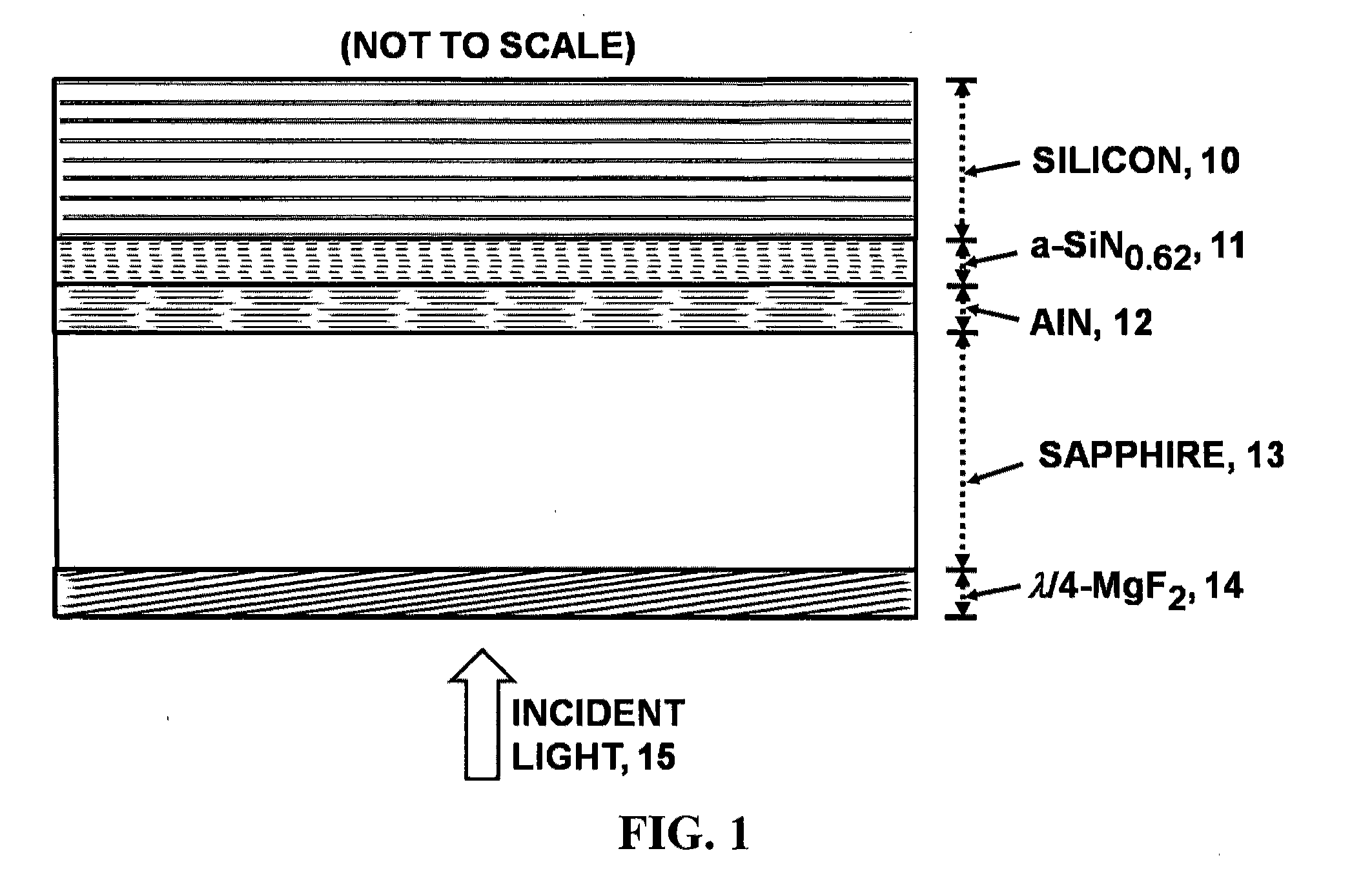

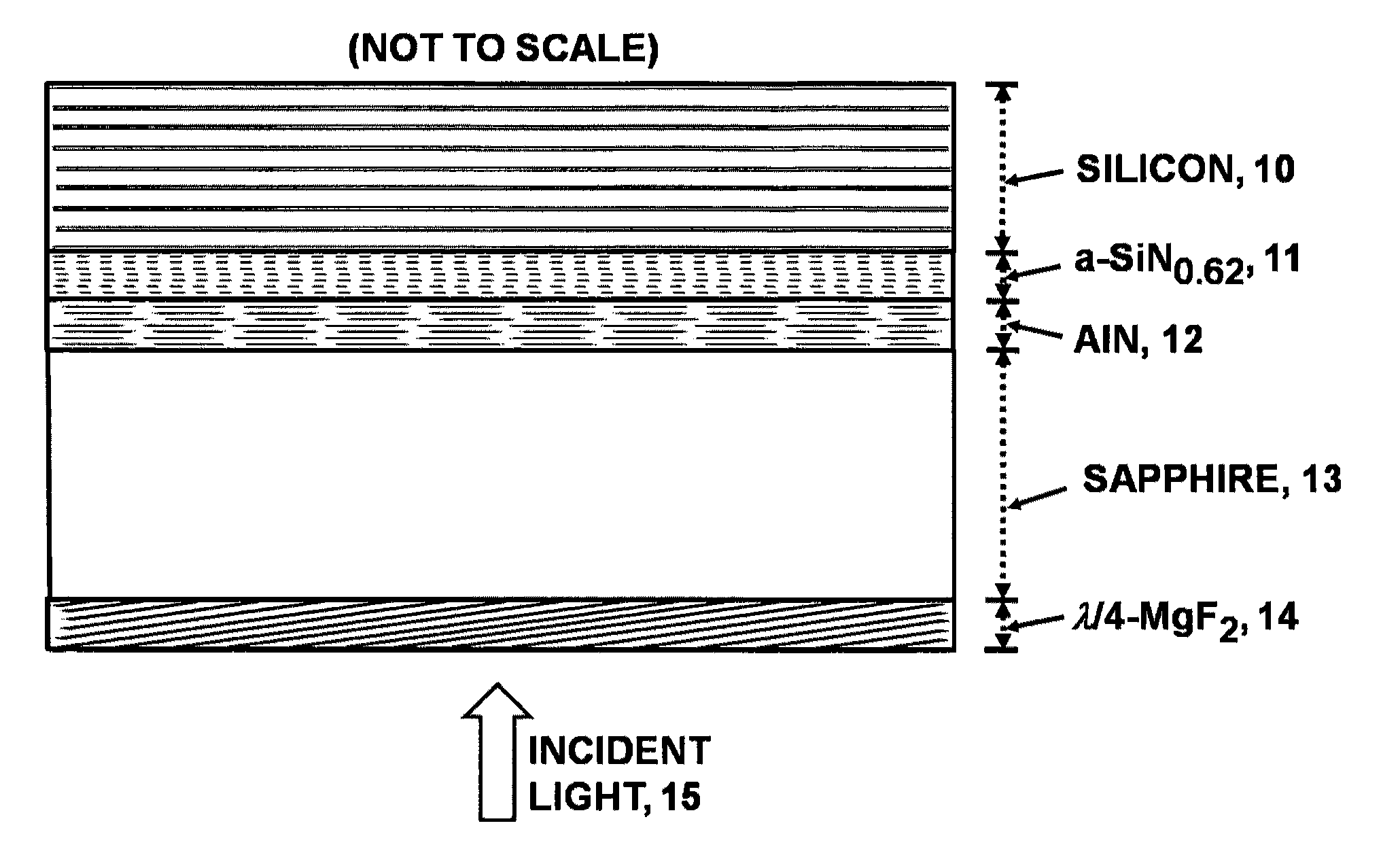

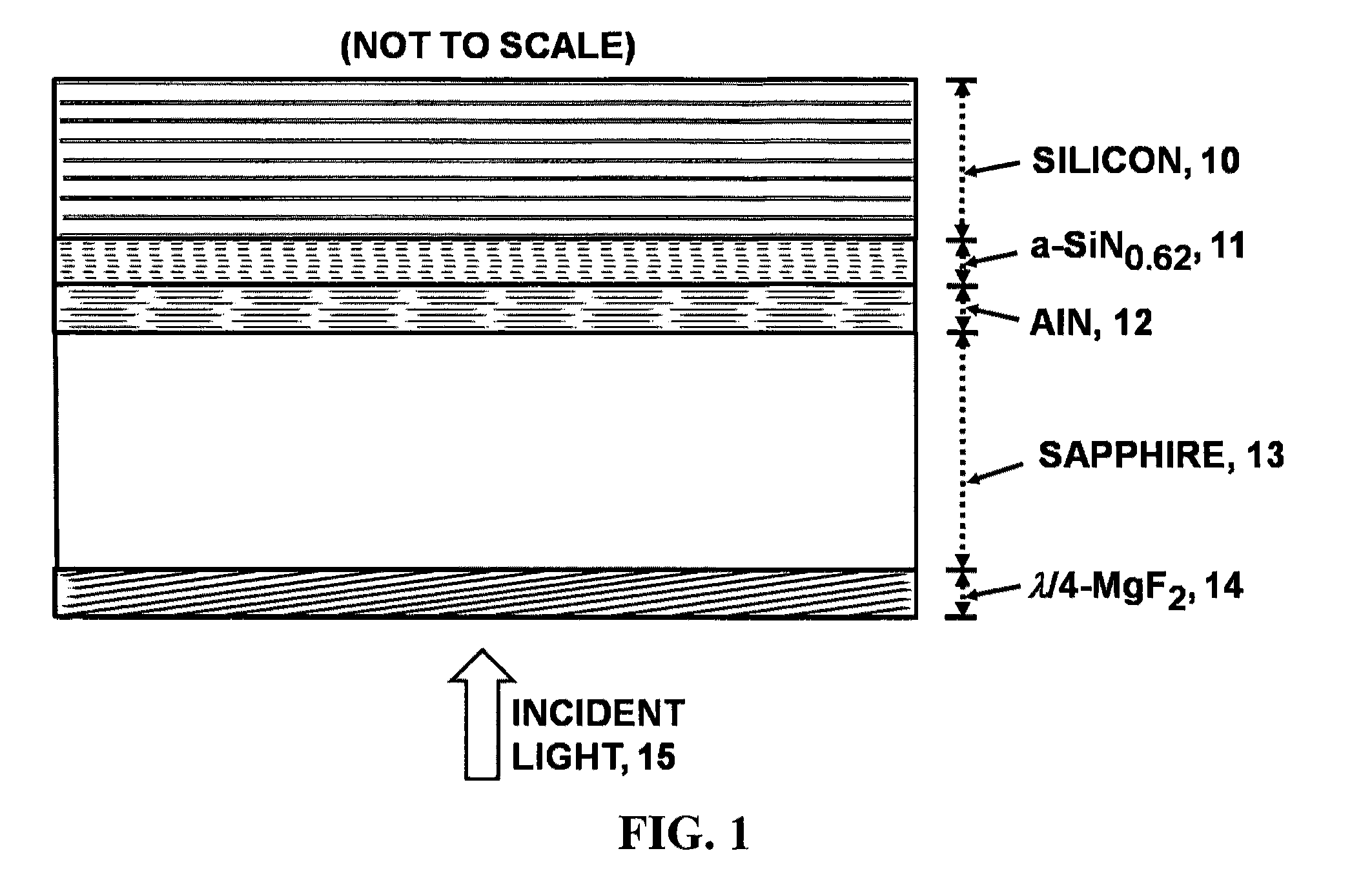

Very high transmittance, back-illuminated, silicon-on-sapphire semiconductor wafer substrate for high quantum efficiency and high resolution, solid-state, imaging focal plane arrays

InactiveUS20120193636A1High light transmittanceImprove quantum efficiencyLaser detailsSolid-state devicesSingle crystalRefractive index matching

An advanced, very high transmittance, back-illuminated, silicon-on-sapphire wafer substrate design is presented for enabling high quantum efficiency and high resolution, silicon or silicon-germanium avalanche photodiode detector arrays. The wafer substrate incorporates a stacked antireflective bilayer between the sapphire and silicon layers, comprised of single crystal aluminum nitride (AlN) and non-stoichiometric, silicon rich, amorphous silicon nitride (a-SiNX<1.33), that provides optimal refractive index matching between sapphire and silicon. A one quarter wavelength, magnesium fluoride (λ / 4-MgF2) antireflective layer deposited on the back surface of the thinned sapphire provides refractive index matching at the air-sapphire interface. Selecting a composition of x=0.62 for a-SiNX, tunes an optimal refractive index for the layer. Selecting design thicknesses of 52 nm for single crystal AlN, 30 nm for a-SiN0.62, and 120 nm for λ / 4-MgF2 yields a back-illuminated optical transmittance T>50% for 250-300 nm, T>70% for 300-400 nm and T>90% for 400-1100 nm.

Owner:STERN ALVIN GABRIEL

Very high transmittance, back-illuminated, silicon-on-sapphire semiconductor wafer substrate for high quantum efficiency and high resolution, solid-state, imaging focal plane arrays

InactiveUS8354282B2High light transmittanceGreat index of refractionLaser detailsSolid-state devicesSingle crystalRefractive index matching

An advanced, very high transmittance, back-illuminated, silicon-on-sapphire wafer substrate design is presented for enabling high quantum efficiency and high resolution, silicon or silicon-germanium avalanche photodiode detector arrays. The wafer substrate incorporates a stacked antireflective bilayer between the sapphire and silicon layers, comprised of single crystal aluminum nitride (AlN) and non-stoichiometric, silicon rich, amorphous silicon nitride (a-SiNX<1.33), that provides optimal refractive index matching between sapphire and silicon. A one quarter wavelength, magnesium fluoride (λ / 4-MgF2) antireflective layer deposited on the back surface of the thinned sapphire provides refractive index matching at the air-sapphire interface. Selecting a composition of x=0.62 for a-SiNX, tunes an optimal refractive index for the layer. Selecting design thicknesses of 52 nm for single crystal AlN, 30 nm for a-SiN0.62, and 120 nm for λ / 4-MgF2 yields a back-illuminated optical transmittance T>50% for 250-300 nm, T>70% for 300-400 nm and T>90% for 400-1100 nm.

Owner:STERN ALVIN GABRIEL

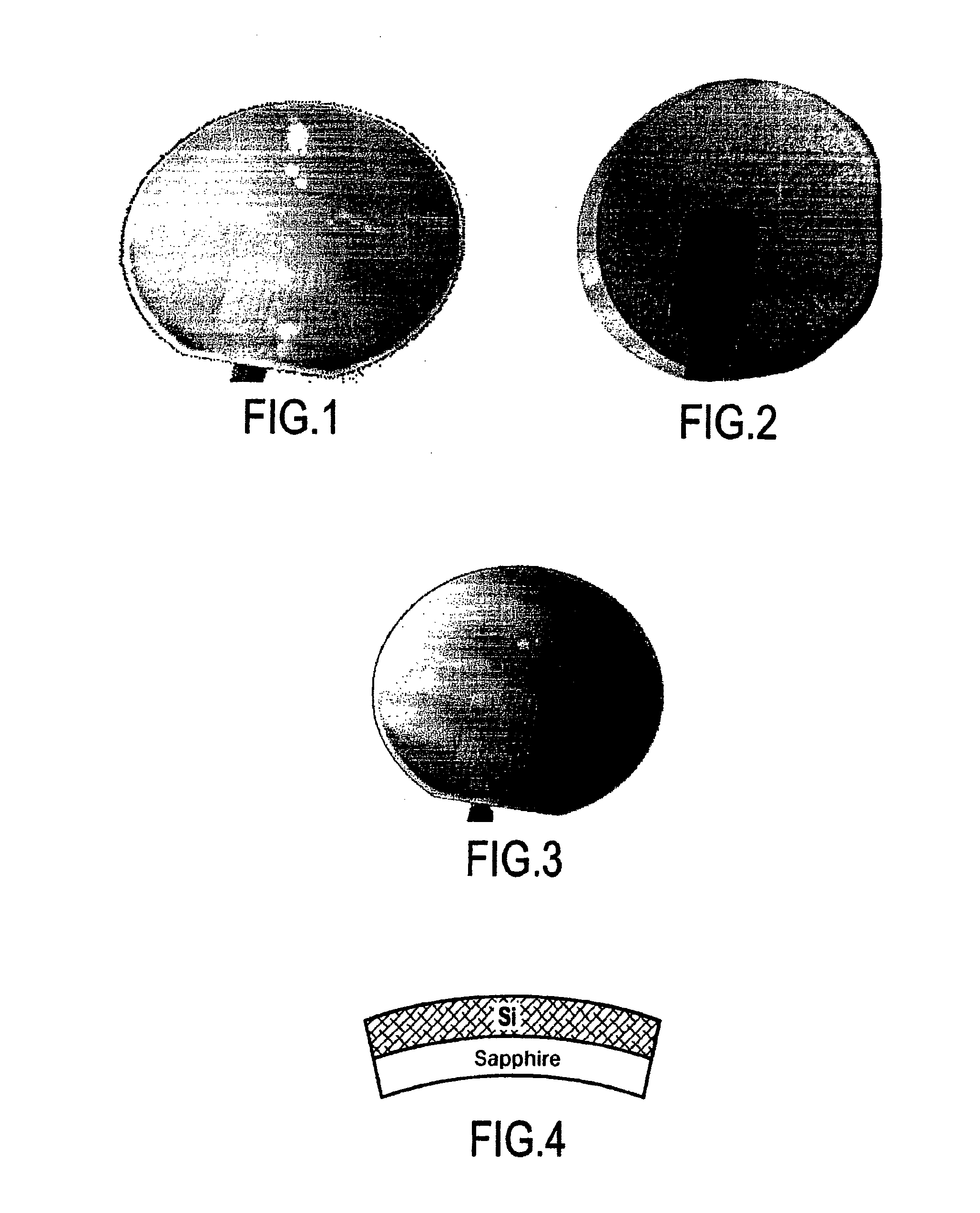

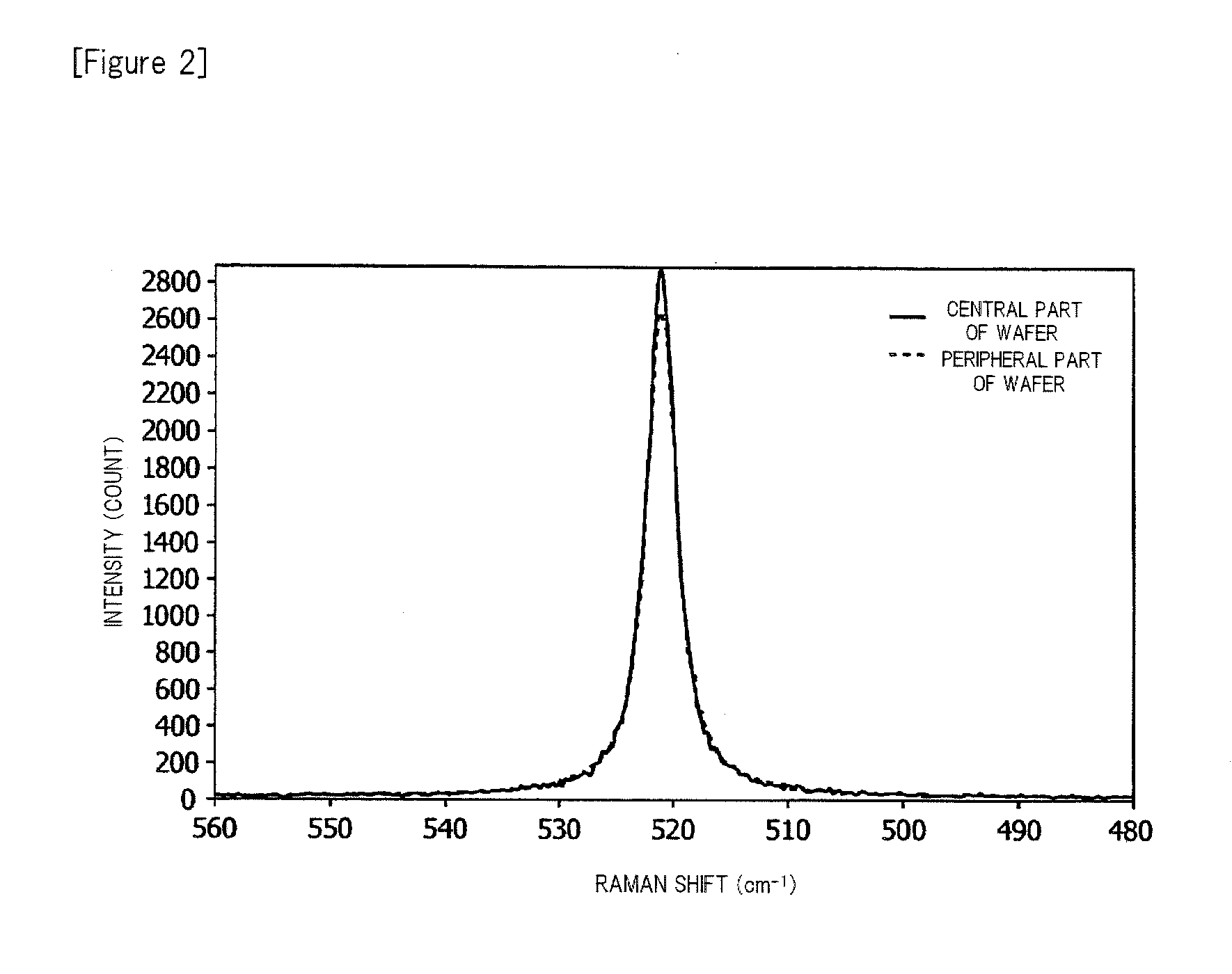

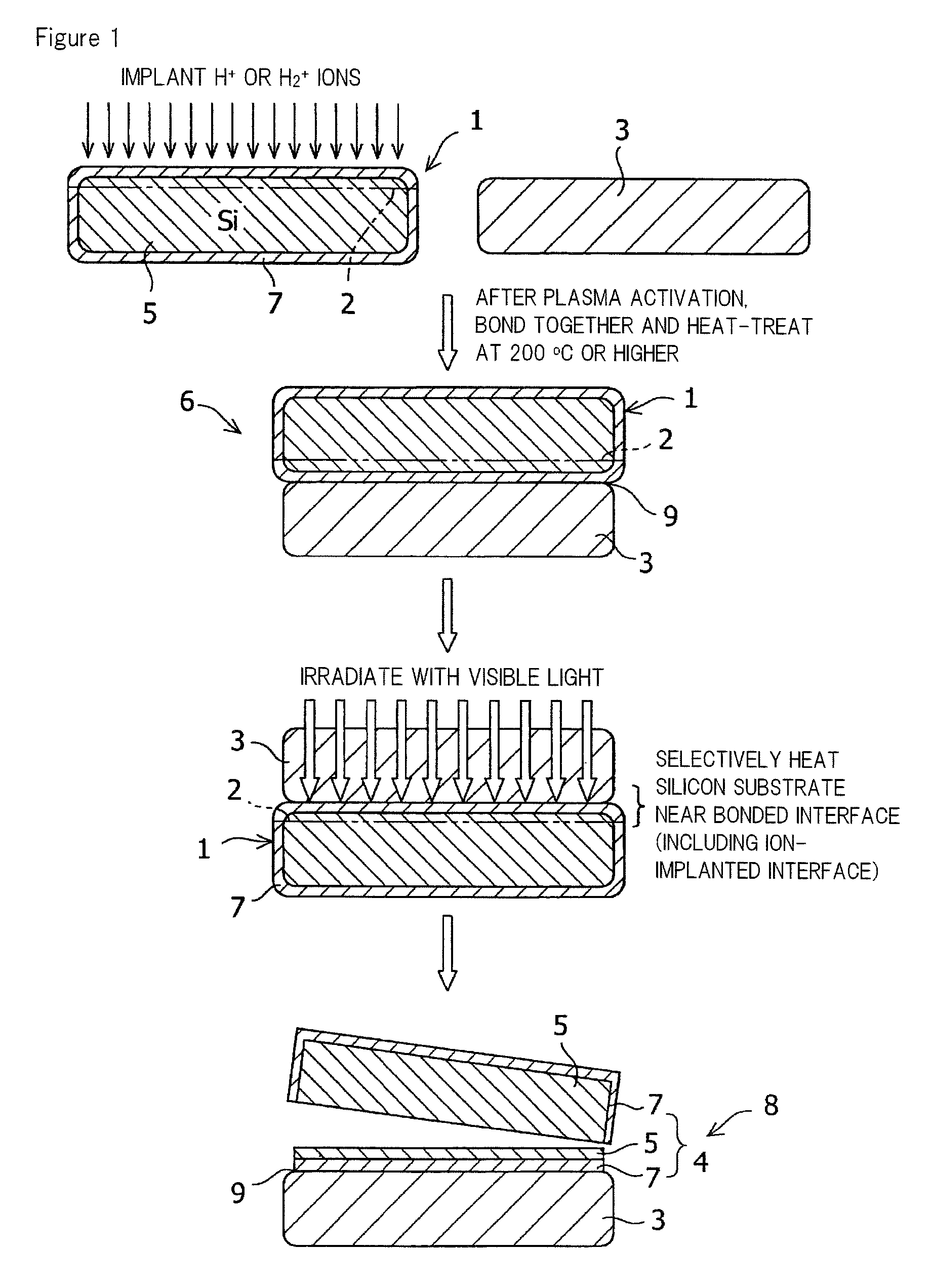

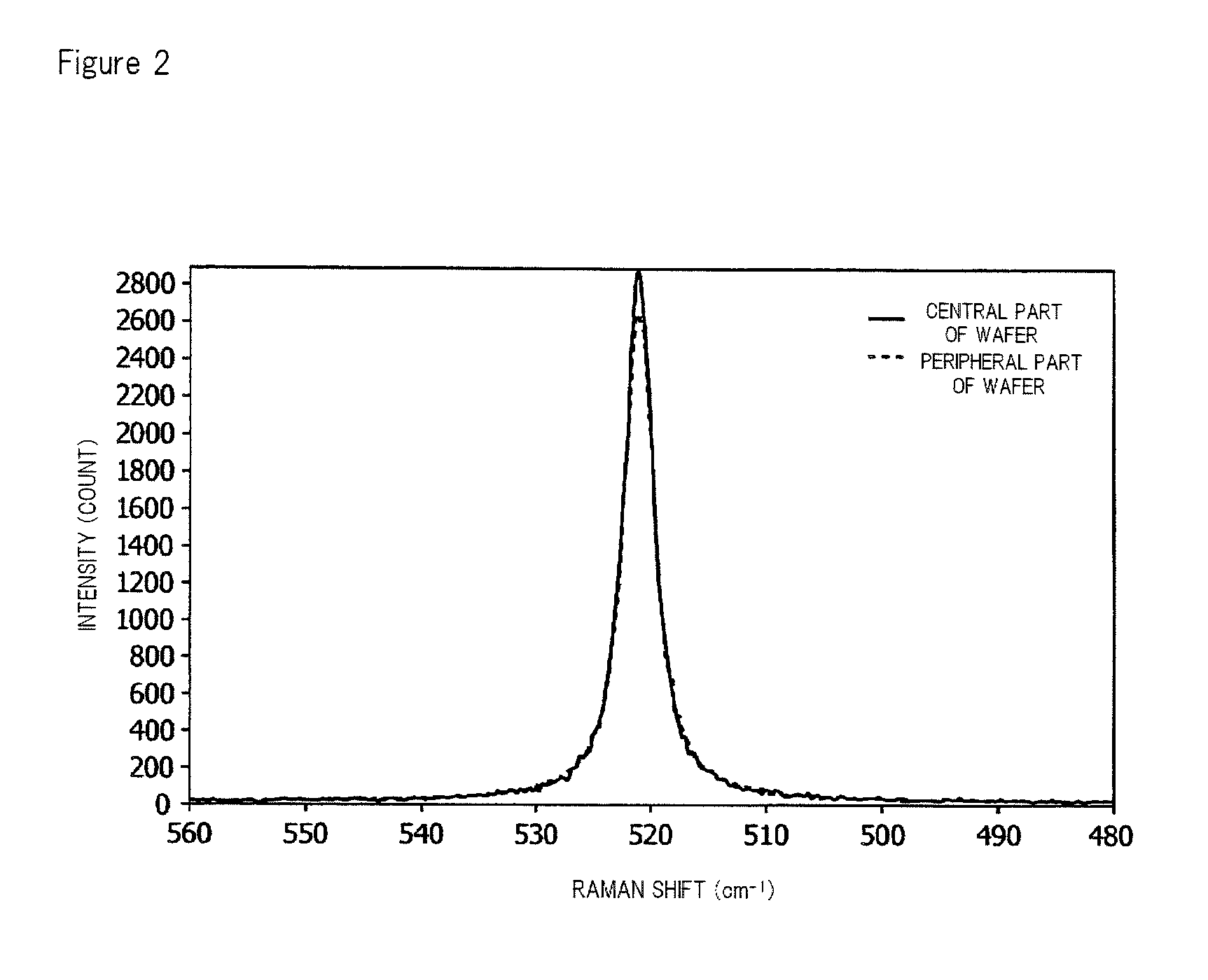

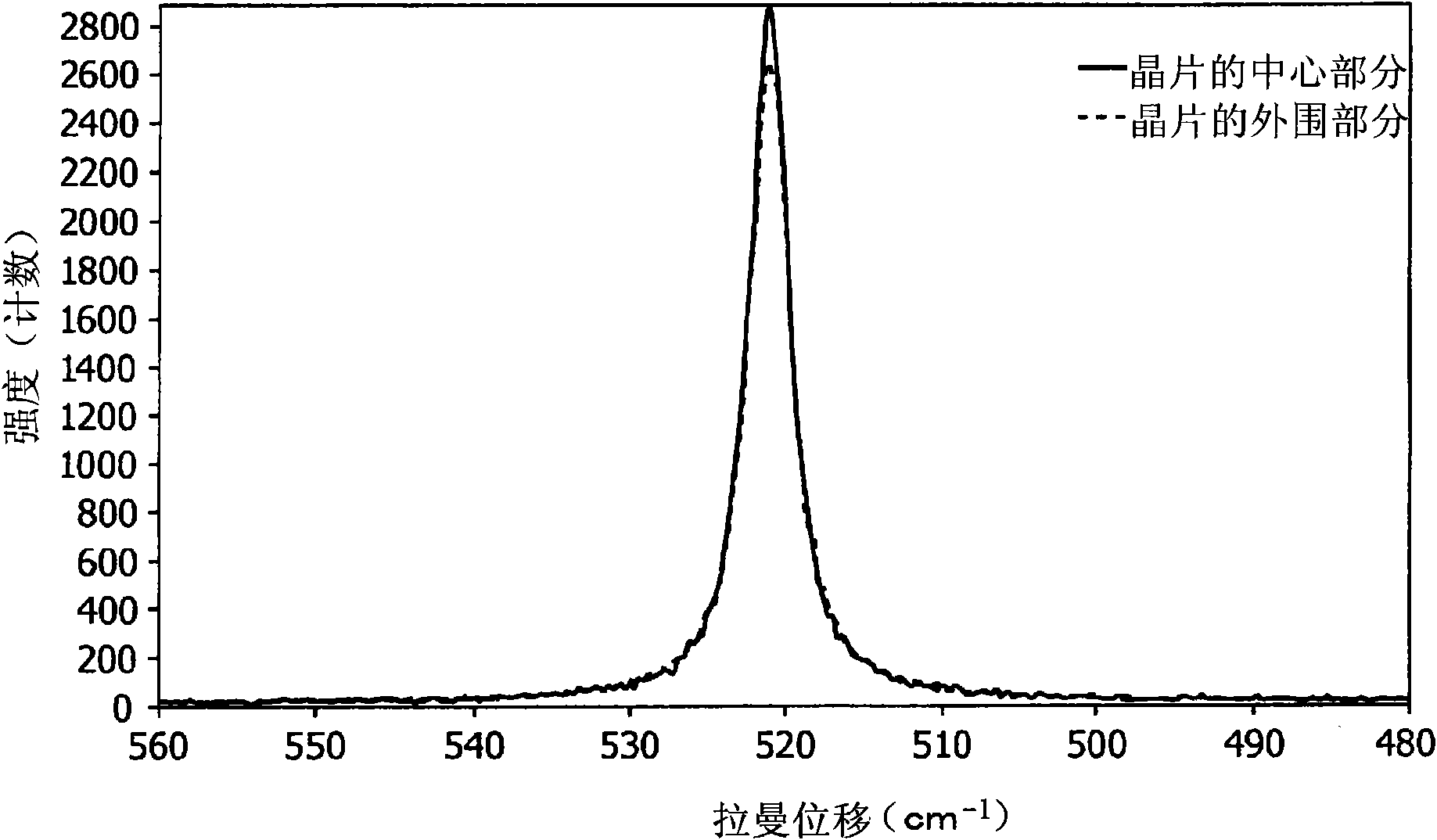

Sos substrate with reduced stress

InactiveUS20120280355A1Relieve pressureSolid-state devicesSemiconductor/solid-state device manufacturingIn planeSilicon on sapphire

There is provided an SOS substrate with reduced stress. The SOS substrate is a silicon-on-sapphire (SOS) substrate comprising a sapphire substrate and a monocrystalline silicon film on or above the sapphire substrate. The stress of the silicon film of the SOS substrate as measured by a Raman shift method is 2.5×108 Pa or less across an entire in-plane area of the SOS substrate.

Owner:SHIN ETSU CHEM IND CO LTD

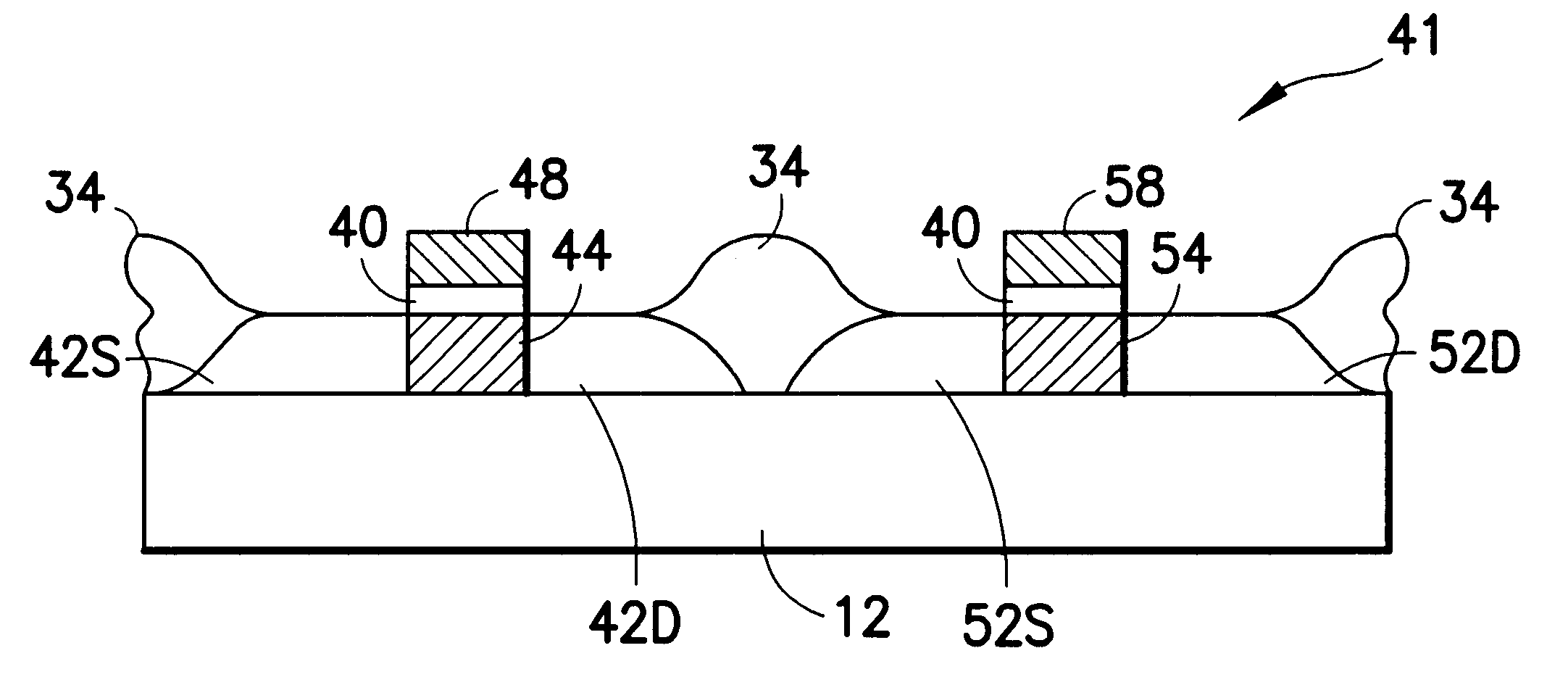

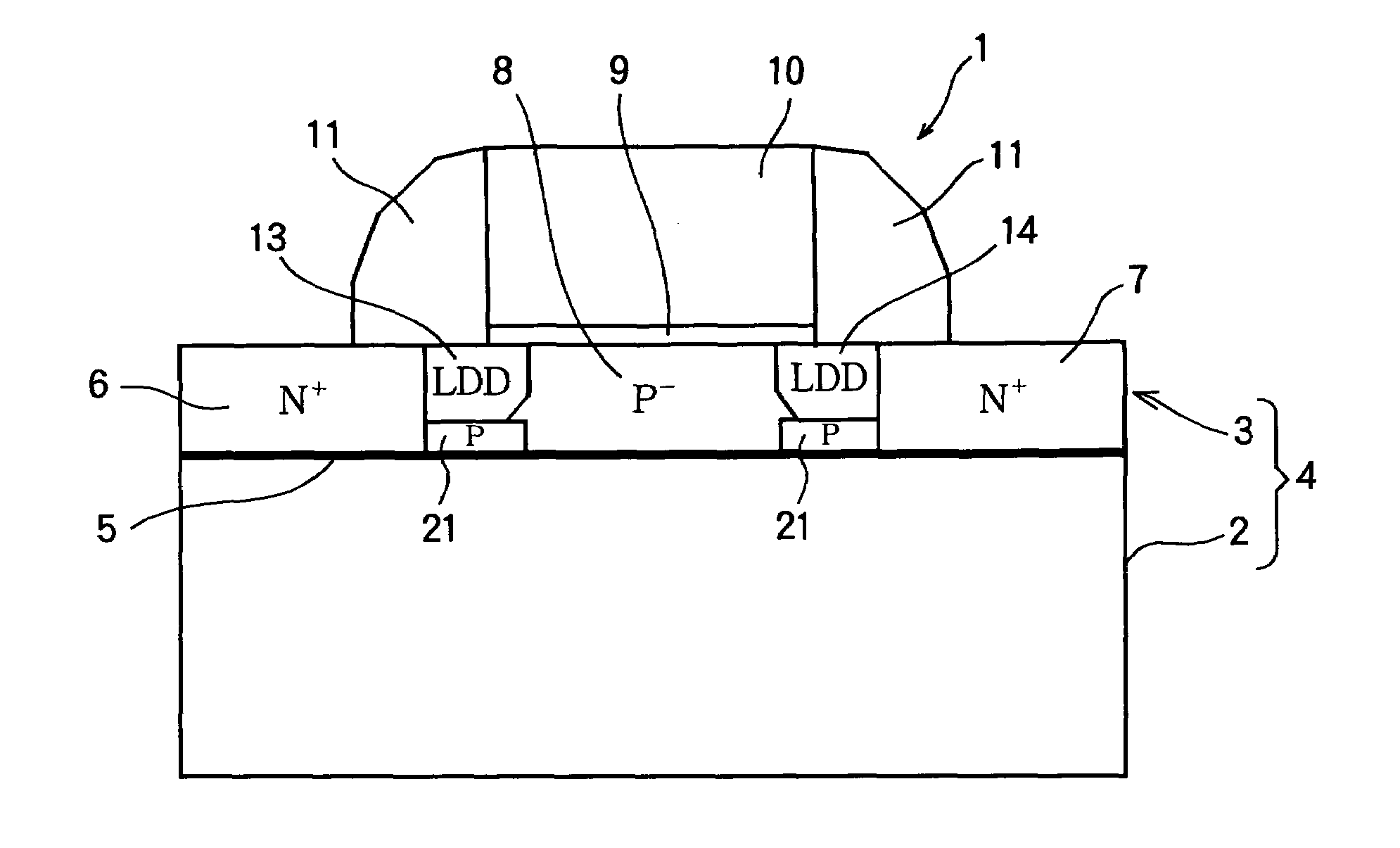

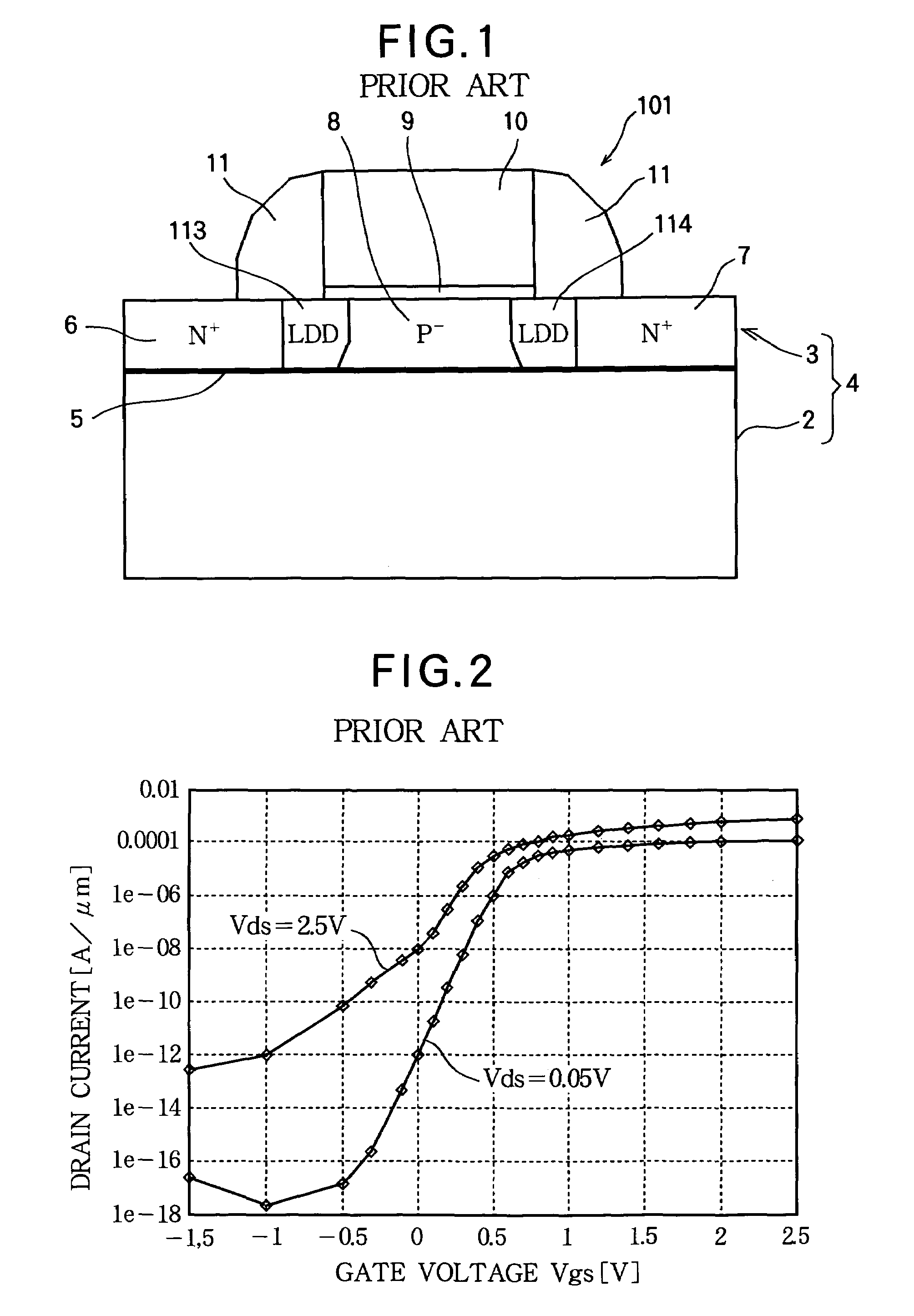

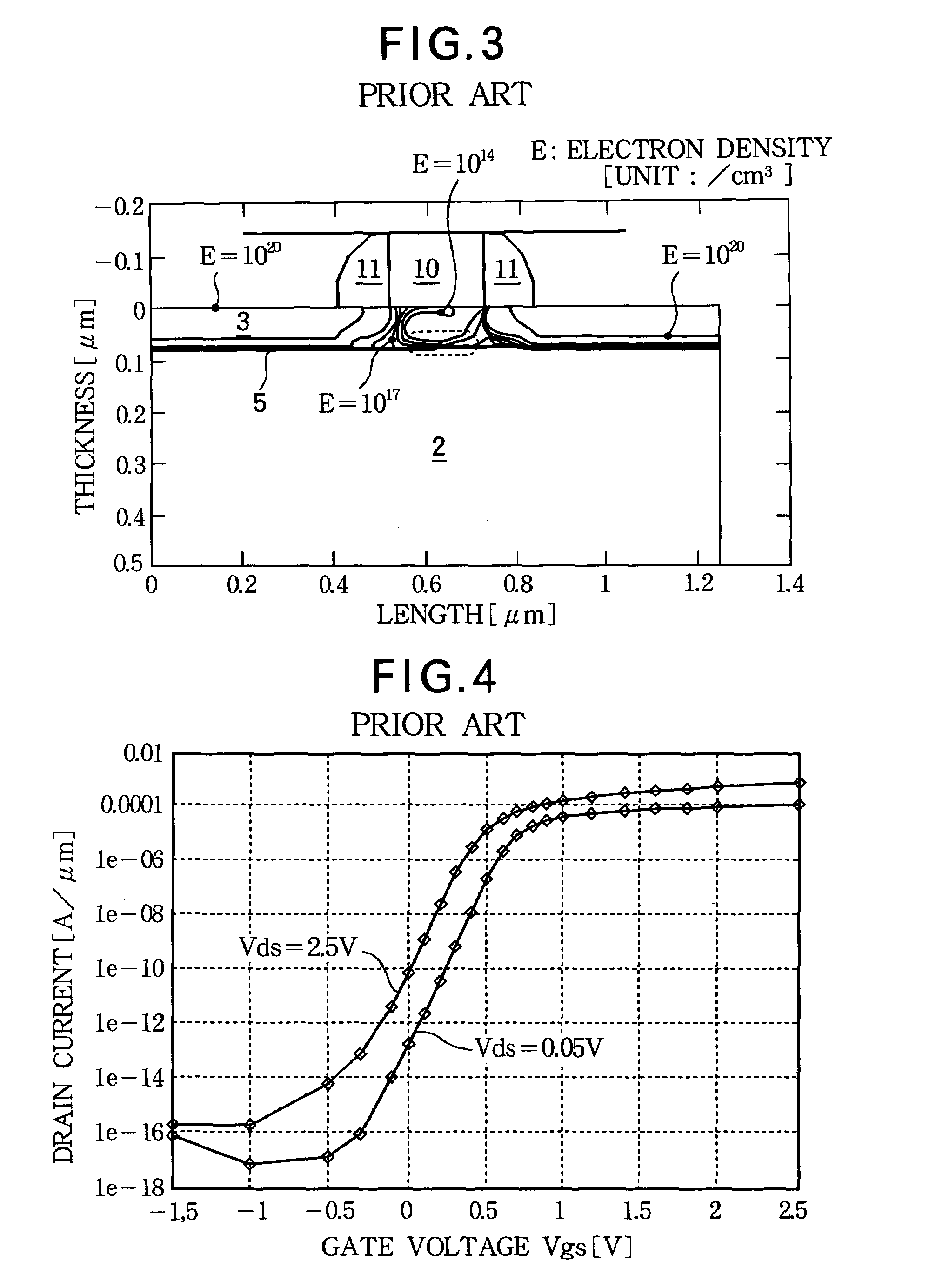

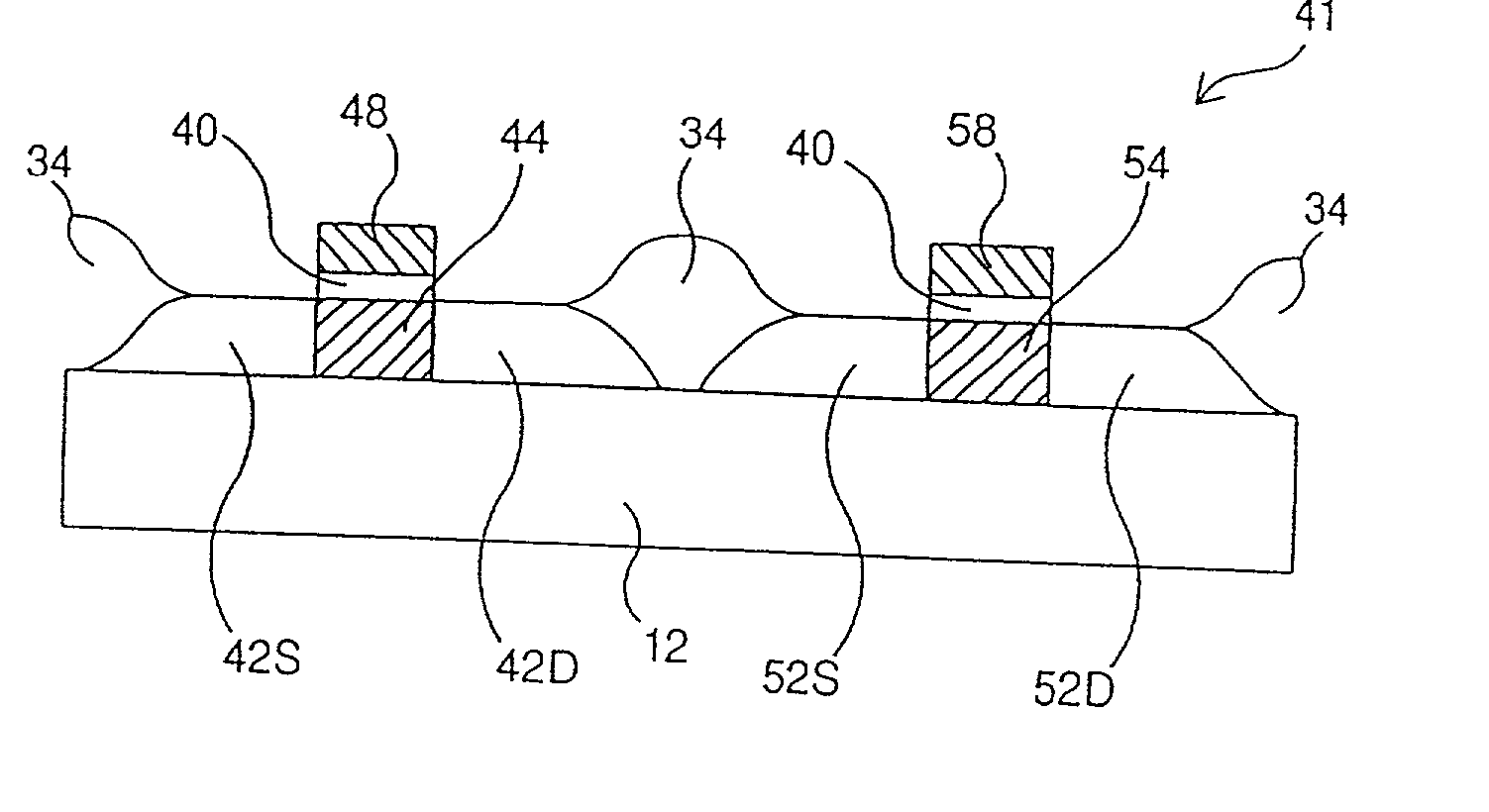

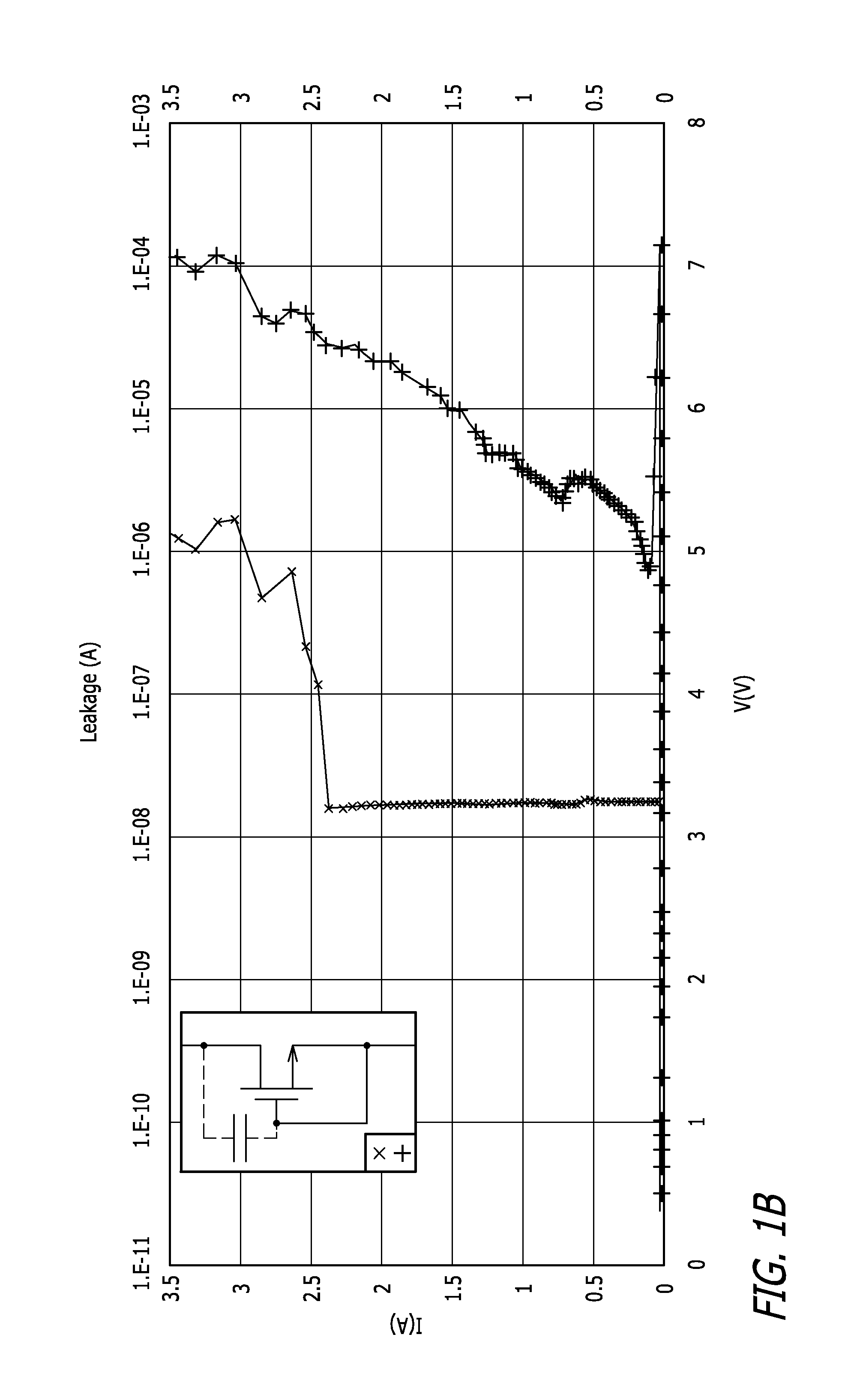

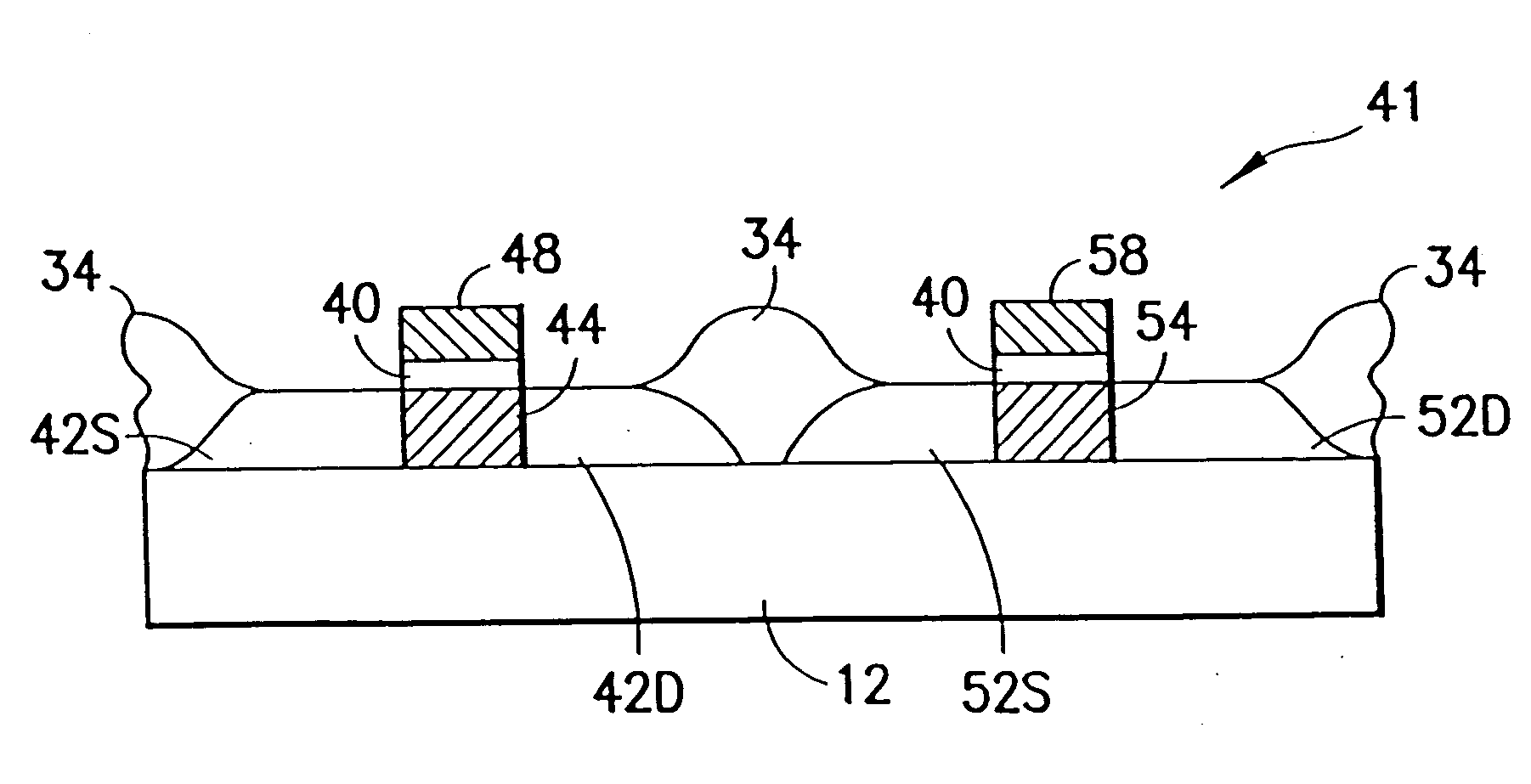

Silicon-on-sapphire semiconductor device with shallow lightly-doped drain

InactiveUS7663189B2Inhibit currentSolid-state devicesSemiconductor/solid-state device manufacturingMicrometerSilicon on sapphire

A semiconductor device is created in a doped silicon layer at most one-tenth of a micrometer thick formed on and having an interface with a sapphire substrate. An oppositely doped source region is formed in the silicon layer. A gate electrode is formed above part of the silicon layer. A diffusion layer doped with the same type of impurity as the source region but at a lower concentration is formed in the silicon layer, extending into a first area beneath the gate electrode, functioning as a drain region or as a lightly-doped extension of a more heavily doped drain region. The depth of this diffusion layer is less than the thickness of the silicon layer. This comparatively shallow diffusion depth reduces current leakage by inhibiting the formation of a back channel.

Owner:LAPIS SEMICON CO LTD

Radiation-hardened silicon-on-insulator CMOS device, and method of making the same

A method for eliminating the radiation-induced off-state current in the P-channel ultrathin silicon-on-sapphire transistor, by providing a retrograde dopant concentration profile that has the effect of moving the Fermi level at the back of the device away from that part of the bandgap where the interface states are located. When the Fermi level does not swing through this area in any region of operation of the device, subthreshold stretchout of the I-V curves does not occur.

Owner:PSEMI CORP

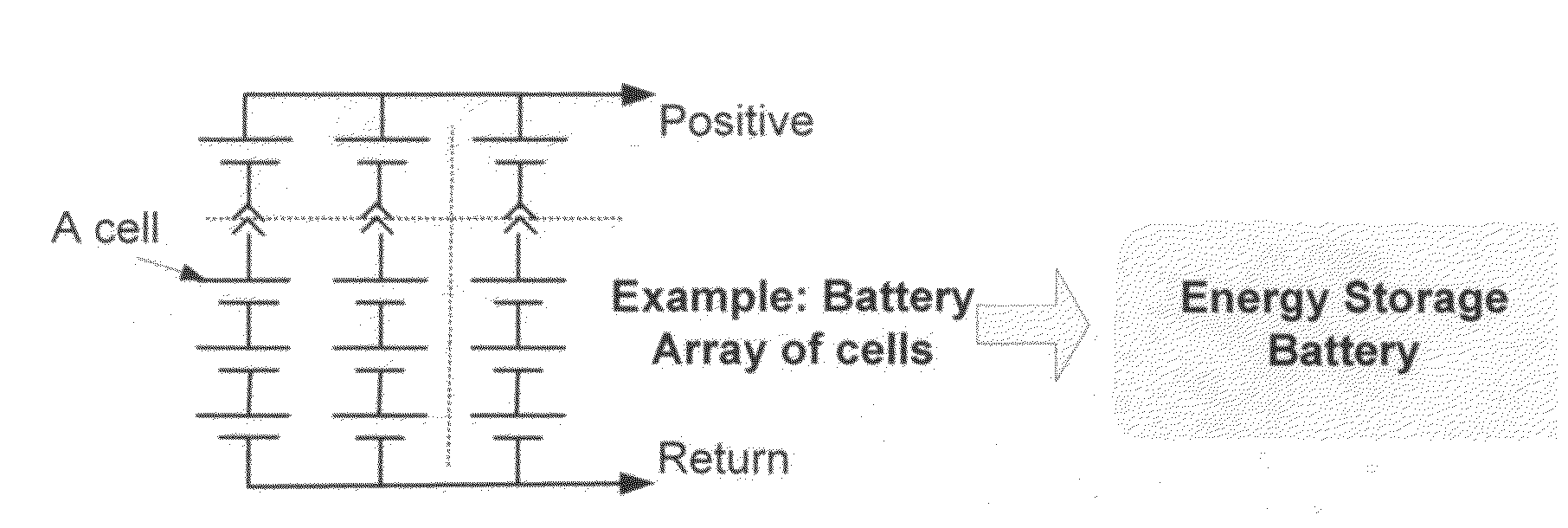

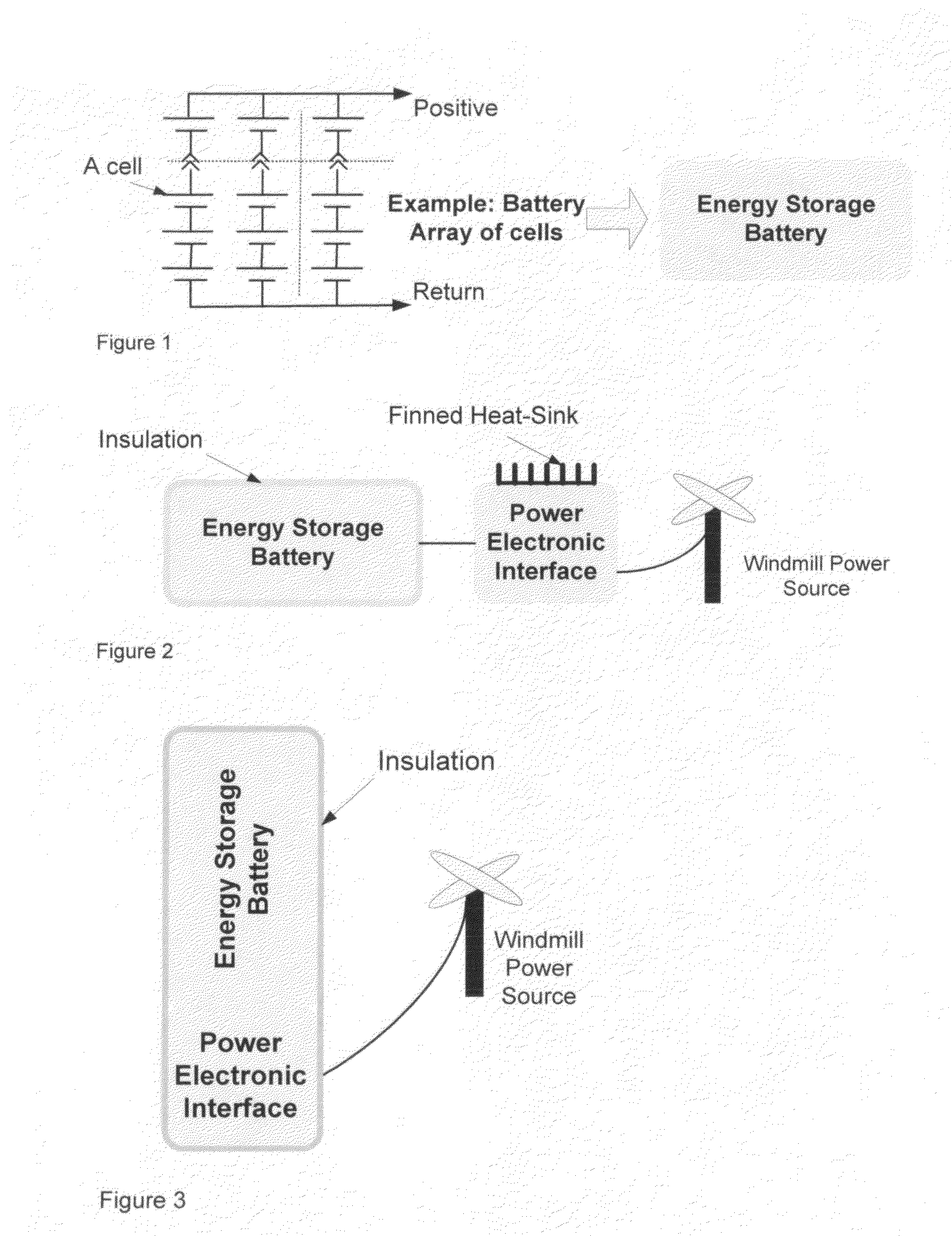

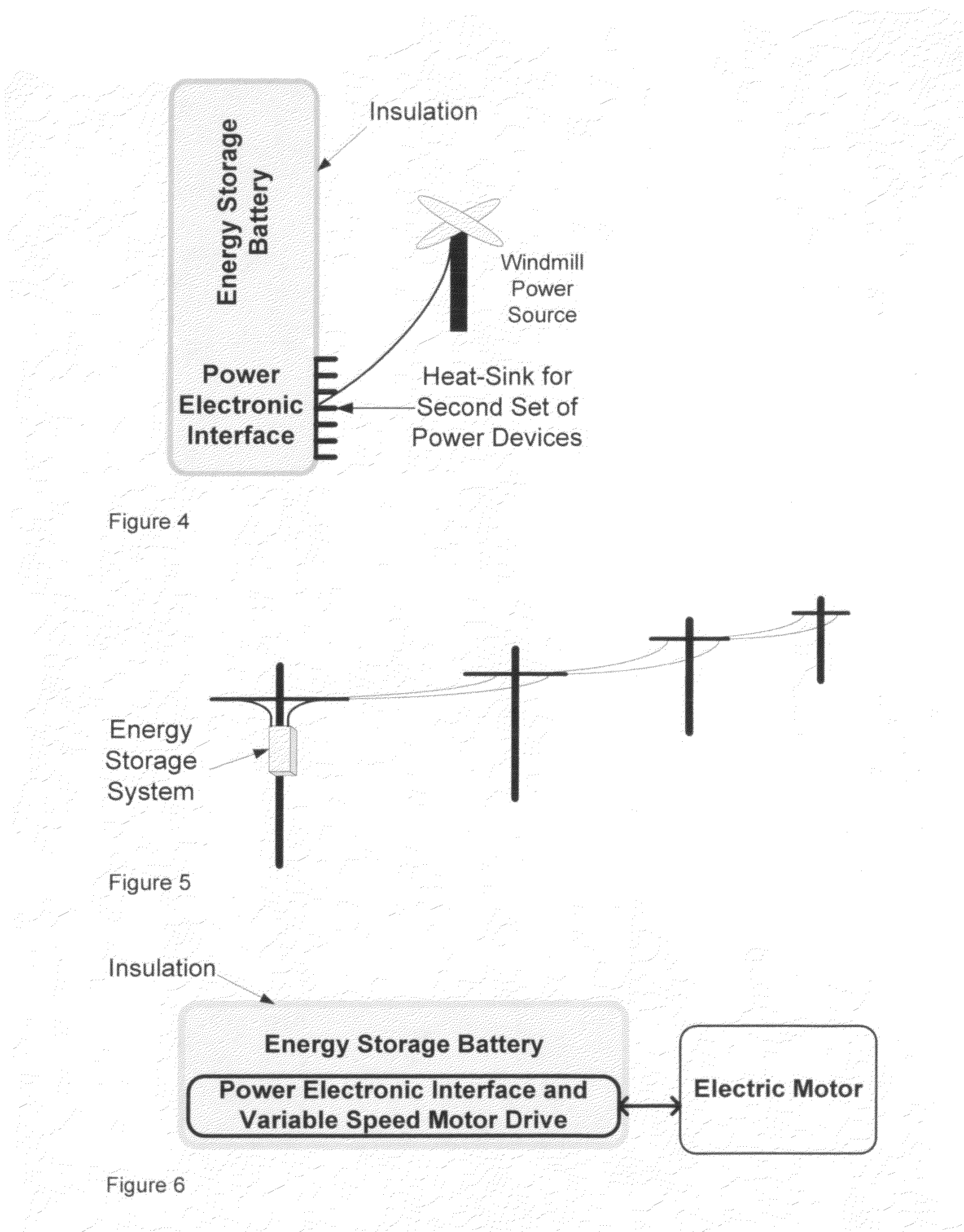

Coupling waste heat into batteries

InactiveUS20100330403A1Improved thermal managementReduce eliminateFinal product manufactureCell temperature controlInternal resistanceGallium nitride

A system for maintaining battery temperatures for energy storage systems using heat created by power electronic device needed to interface the batteries to external power sources or loads is described. Waste heat is a product of internal resistance found in all electronic devices passing current. High-temperature electronics comprised of, silicon-on-insulator, silicon-on-sapphire, silicon-carbide, gallium-nitride or in conjunction with or combination of other wide bandgap semiconductors can used to monitor, charge or discharge the battery array. A thermal system where heat generated by power electronics is used to assist the thermal management of battery energy storage system increases overall system efficiency.

Owner:NORMANN RANDY ALLEN

Silicon-on-insulator wafer having conductive layer for detection with electrical sensors

InactiveUS6238935B1Semiconductor/solid-state device testing/measurementSolid-state devicesSilicon on sapphirePhysics

A method for fabricating a silicon-on-sapphire wafer for processing by silicon-wafer-processing equipment. A layer is deposited on a backside of a silicon-on-sapphire wafer, the layer having optical and electrical properties of silicon, wherein the silicon-on-sapphire wafer may be sensed by a sensor designed to sense a presence of a silicon wafer.

Owner:IBM CORP

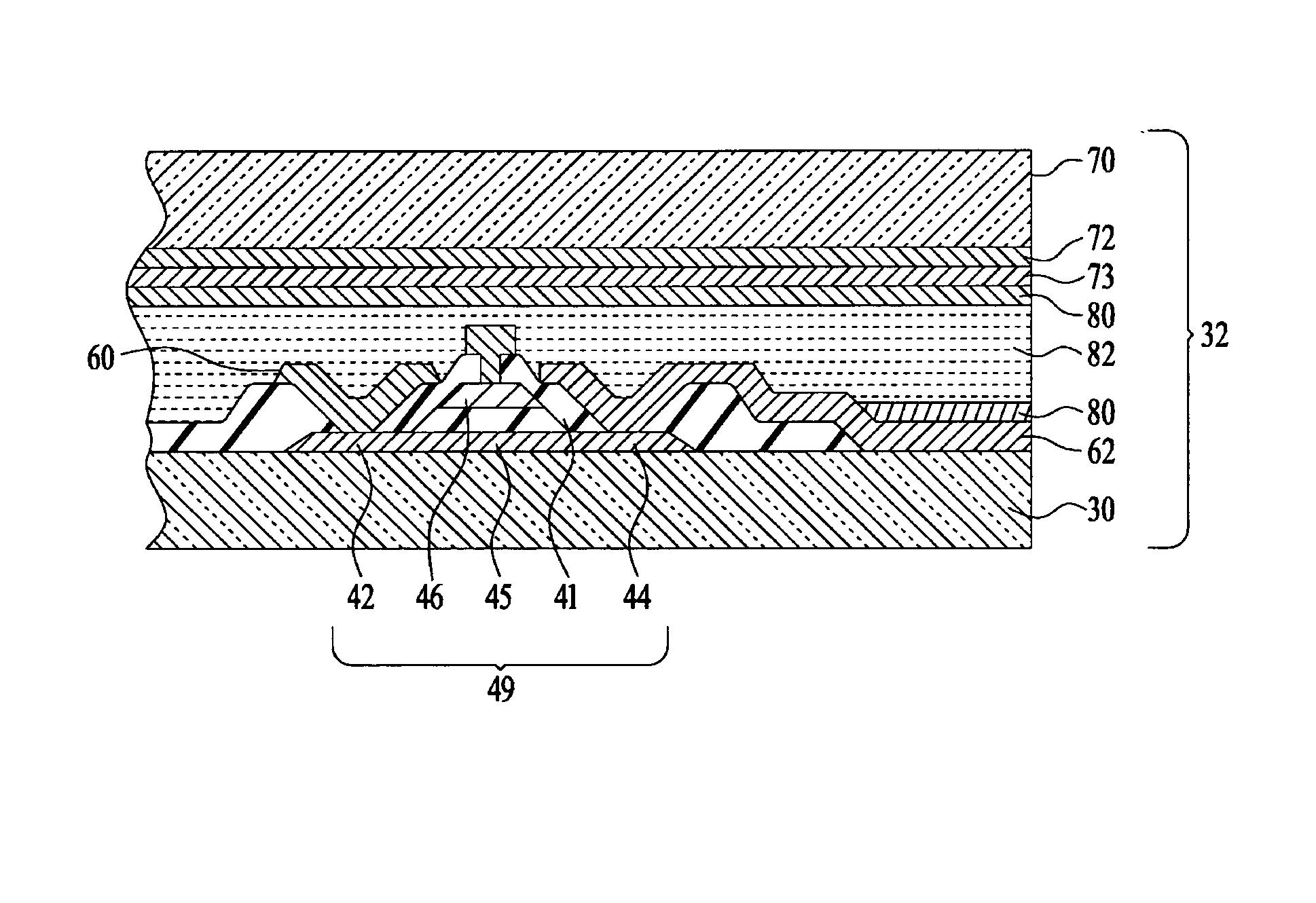

Silicon-on-sapphire display apparatus and method of fabricating same

A liquid crystal display includes: a) a sapphire substrate having a first crystal lattice structure; b) a single crystal silicon structure having a thickness no greater than about 100 nanometers affixed to the sapphire substrate to create a silicon-on-sapphire structure, and a second crystal lattice structure oriented by the first crystal lattice structure; c) an array of liquid crystal capacitors formed on the silicon-on-sapphire structure; and d) integrated self-aligned circuitry formed from the silicon layer which is operably coupled to modulate the liquid crystal capacitors. The liquid crystals capacitors may include nematic or ferroelectric liquid crystal material.

Owner:NAVY SEC OF THE UNITED STATES

Imaging system

A detector with a transistor sensitive to electromagnetic energy. In accordance with the present teachings, the transistor is biased such that the output thereof is responsive to the electromagnetic energy. The inventive imager includes an array of the novel detectors. Each of the detectors being an n-channel metal-oxide semiconductor transistor with a floating body. The transistors are biased for selective activation and sequential readout. The transistor outputs are read by a differential current sense amplifier. A color filter is disclosed to provide a color sense capability. As an alternative, a grating is provided for this purpose. The present invention allows a very dense imager to be built on using conventional silicon on sapphire or silicon on insulator complementary metal-oxide semiconductor processes. The use of standard CMOS processes allows for low manufacturing costs.

Owner:RAYTHEON CO

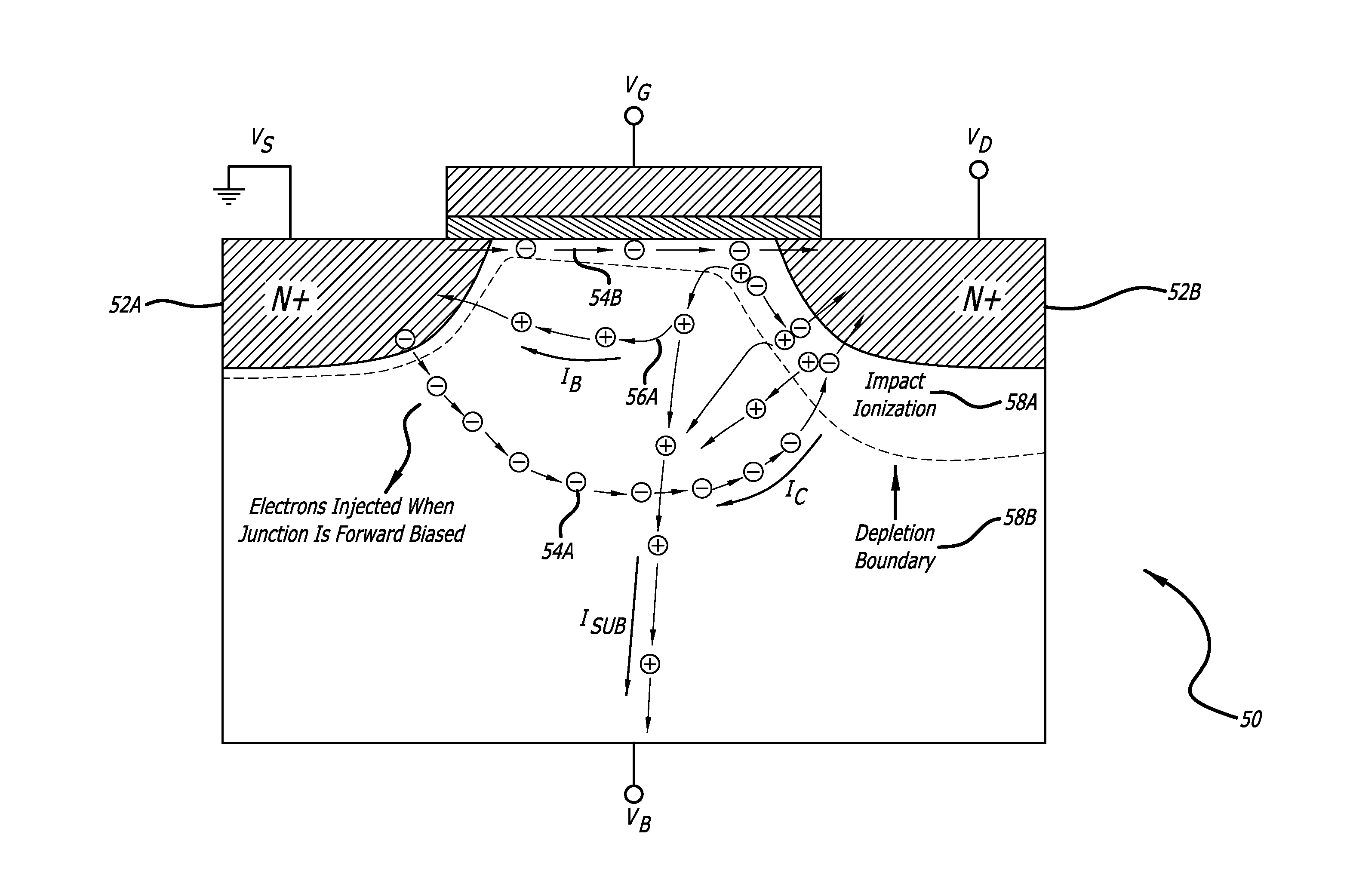

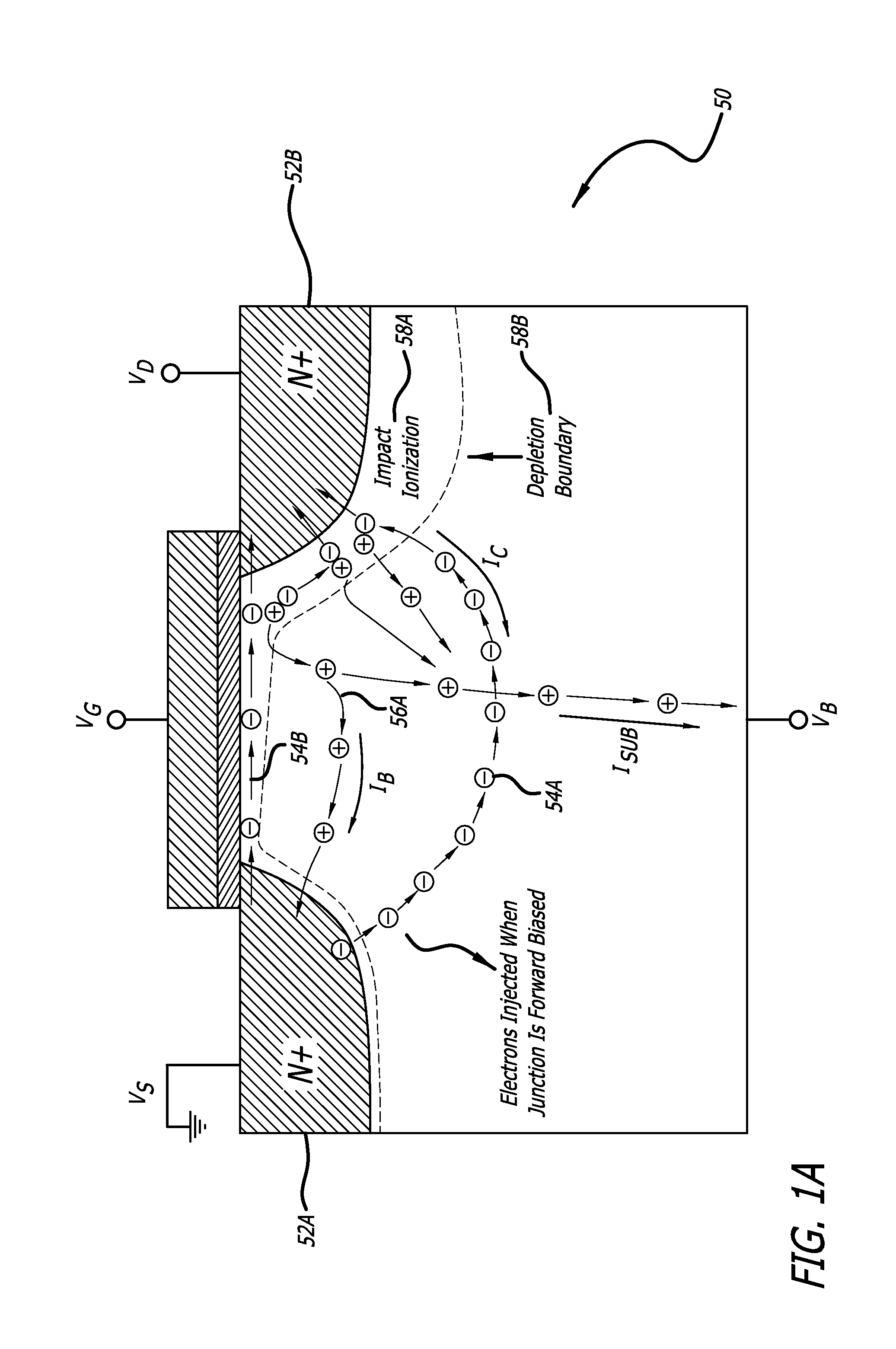

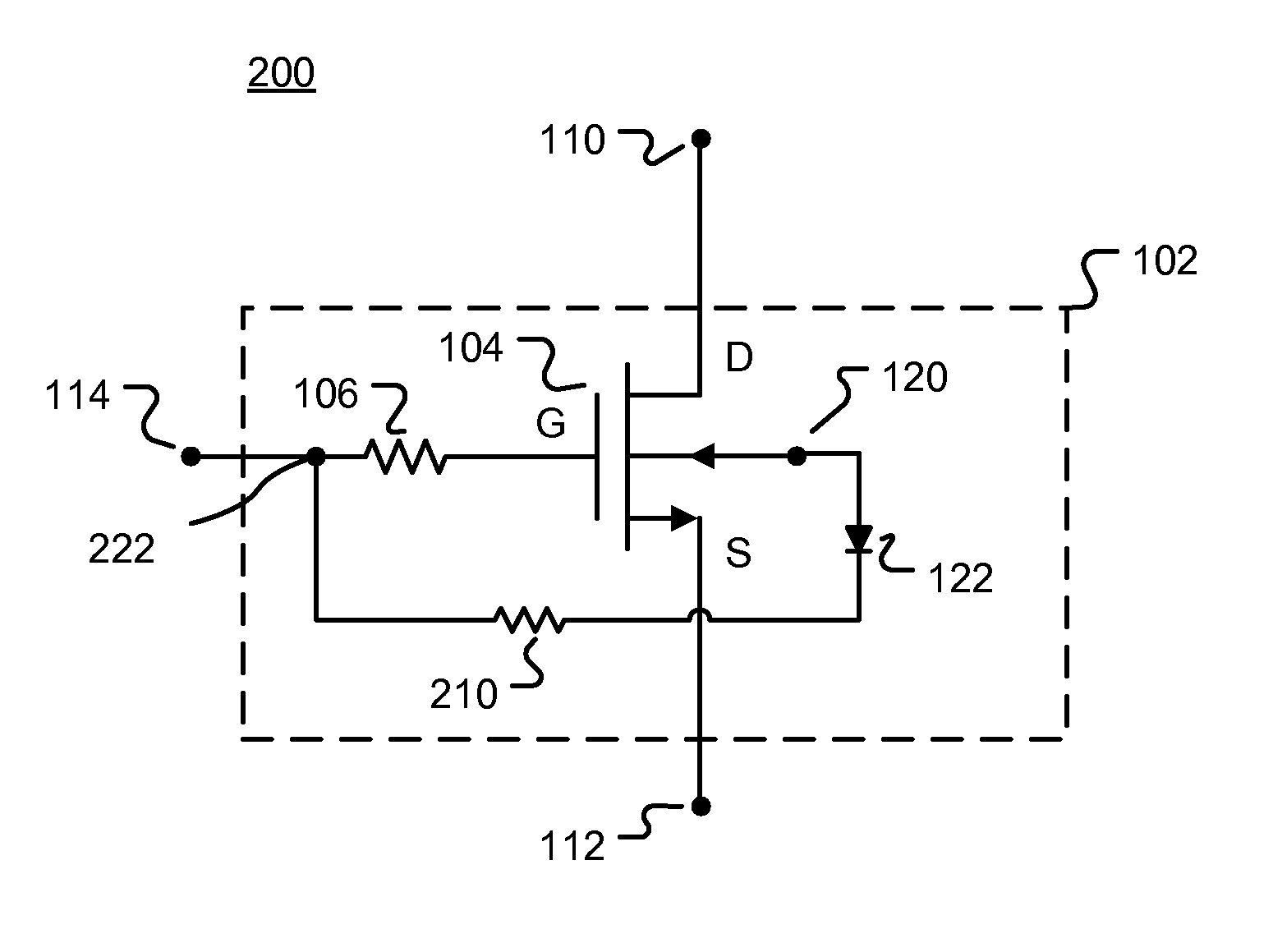

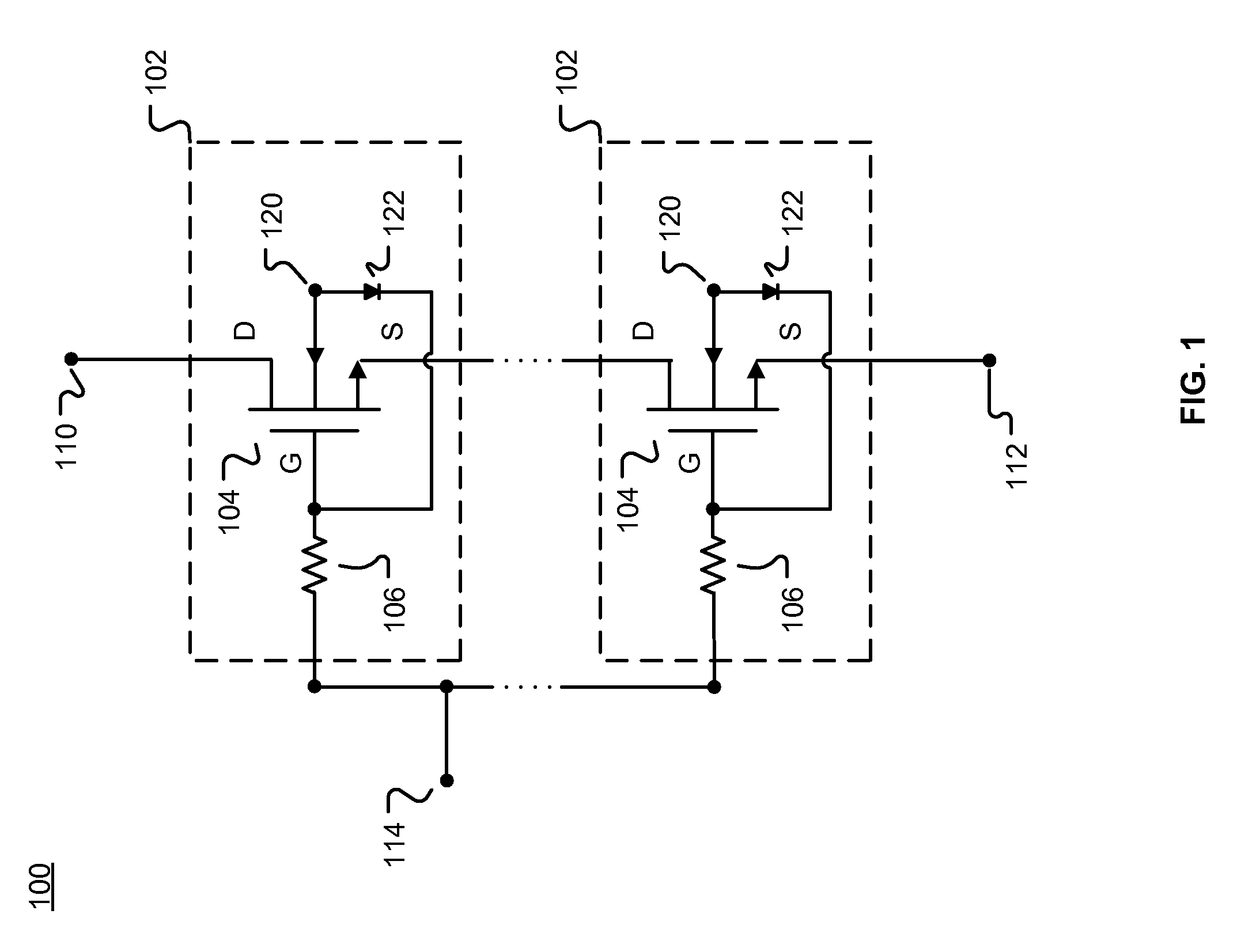

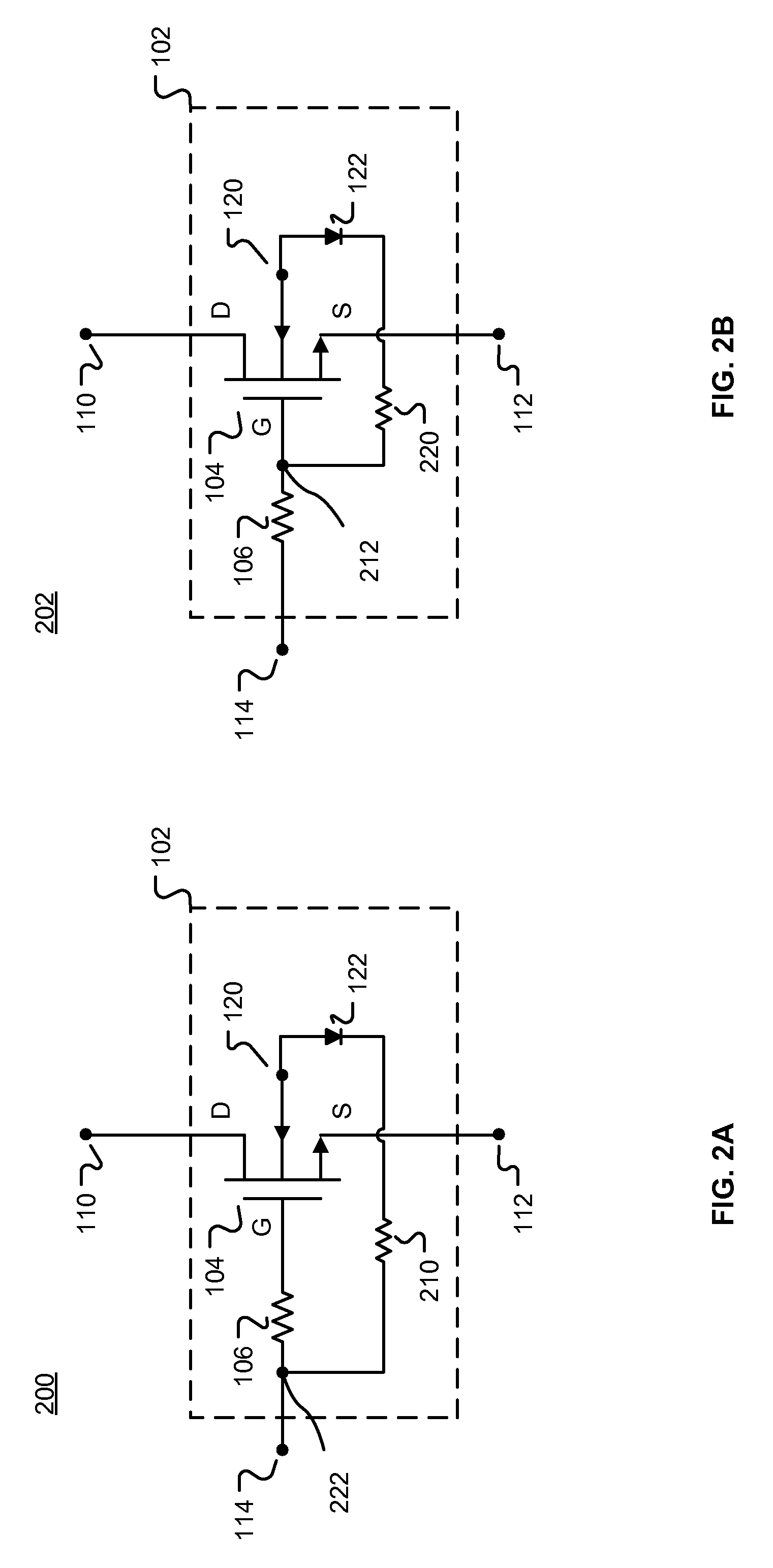

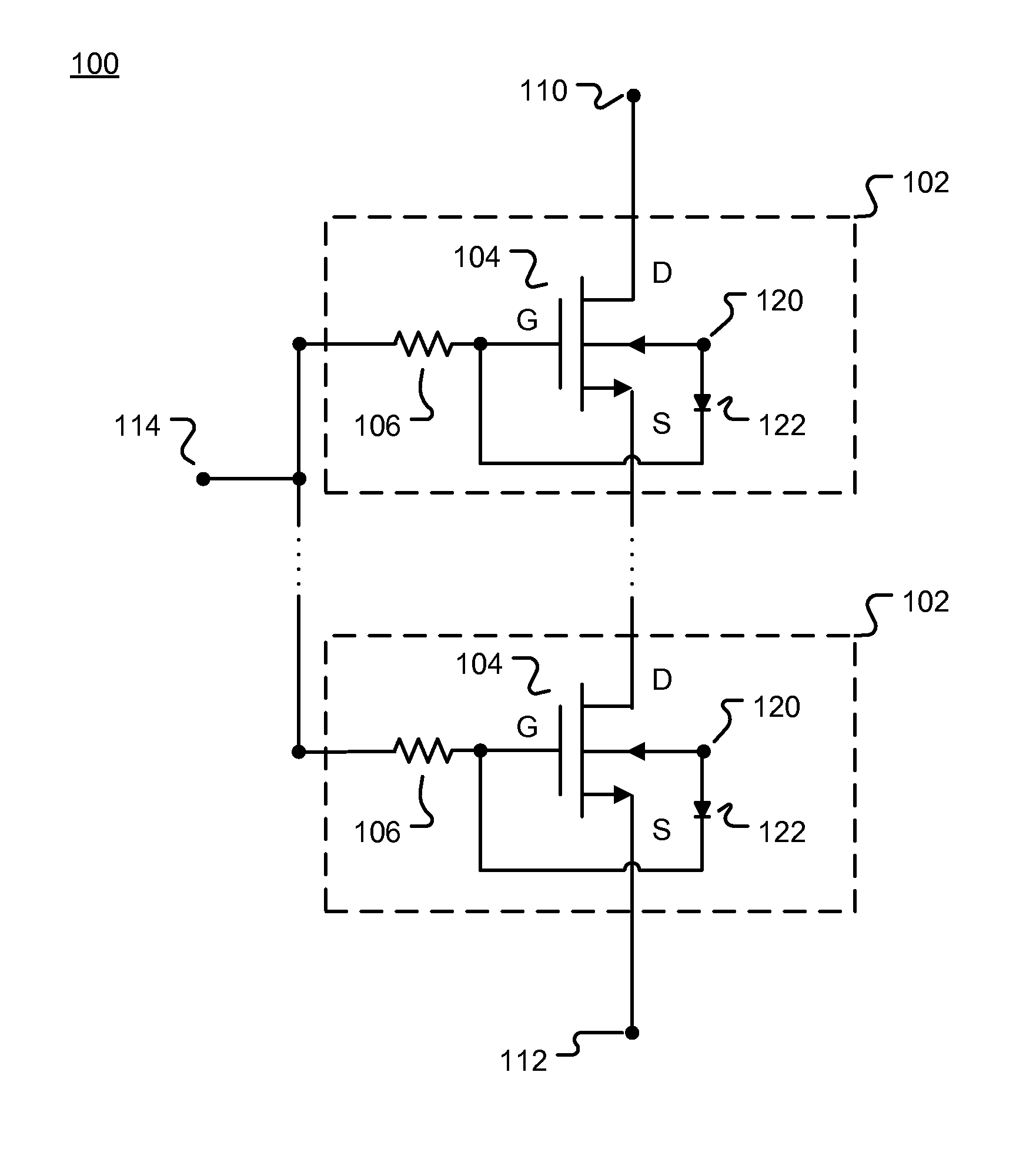

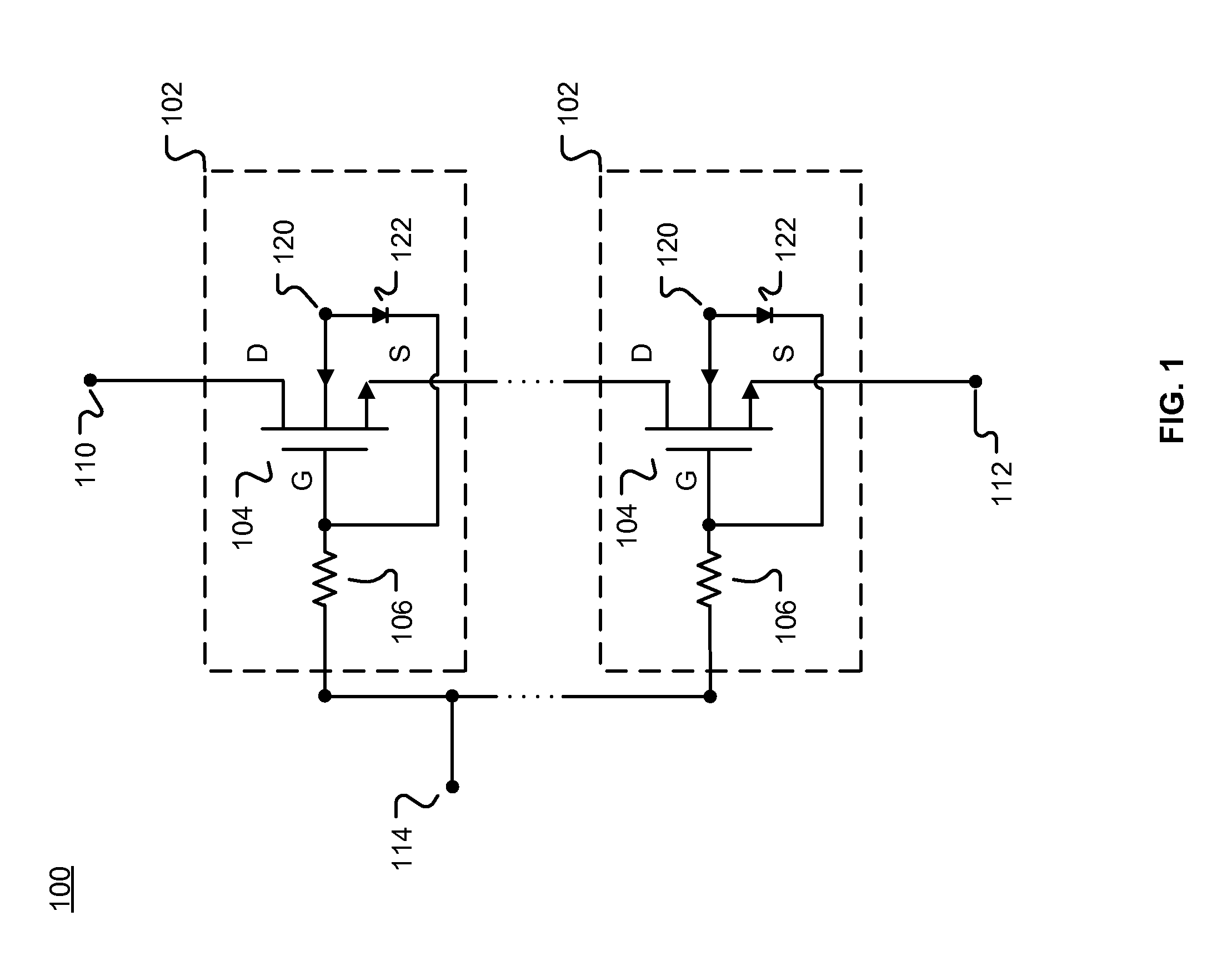

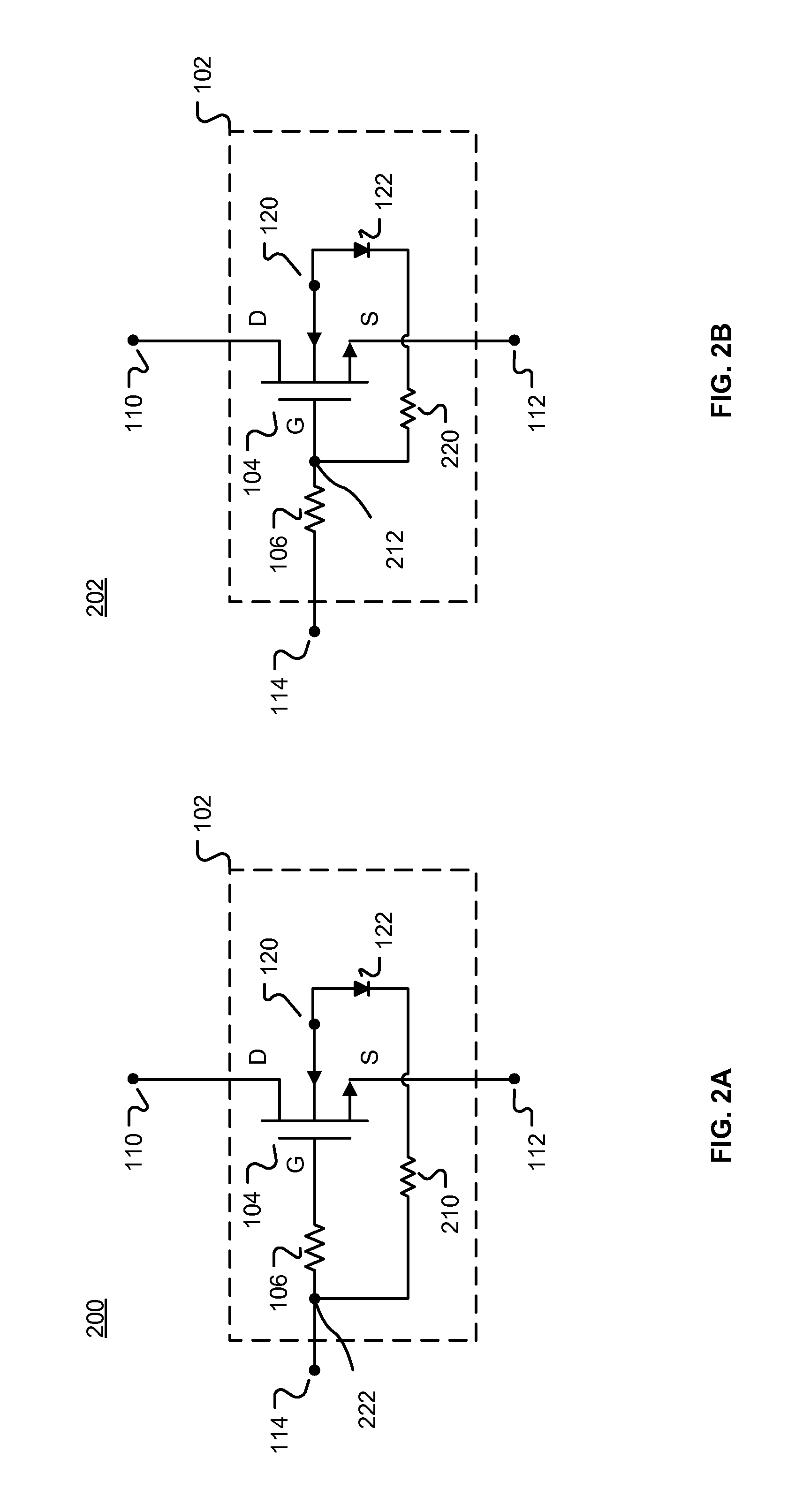

ESD Protection System, Apparatus, and Method with Adjustable Trigger Voltage Decoupled from DC Breakdown Voltage

Systems, methods, and apparatus for ESD protection with adjustable trigger voltage decoupled from DC breakdown voltage for semiconductor devices including field effect transistors (FETs), and particularly to metal-oxide-semiconductors (MOSFETs) fabricated on silicon-on-insulator (“SOI”) and silicon-on-sapphire (“SOS”) substrates are described. The apparatus and method are configured to change reverse biased drain junctions which in turn can control the DC breakdown voltage and the trigger voltage.

Owner:PSEMI CORP

SOS substrate with reduced stress

InactiveUS8748294B2Relieve pressureSolid-state devicesSemiconductor/solid-state device manufacturingIn planeSilicon on sapphire

There is provided an SOS substrate with reduced stress. The SOS substrate is a silicon-on-sapphire (SOS) substrate comprising a sapphire substrate and a monocrystalline silicon film on or above the sapphire substrate. The stress of the silicon film of the SOS substrate as measured by a Raman shift method is 2.5×108 Pa or less across an entire in-plane area of the SOS substrate.

Owner:SHIN ETSU CHEM CO LTD

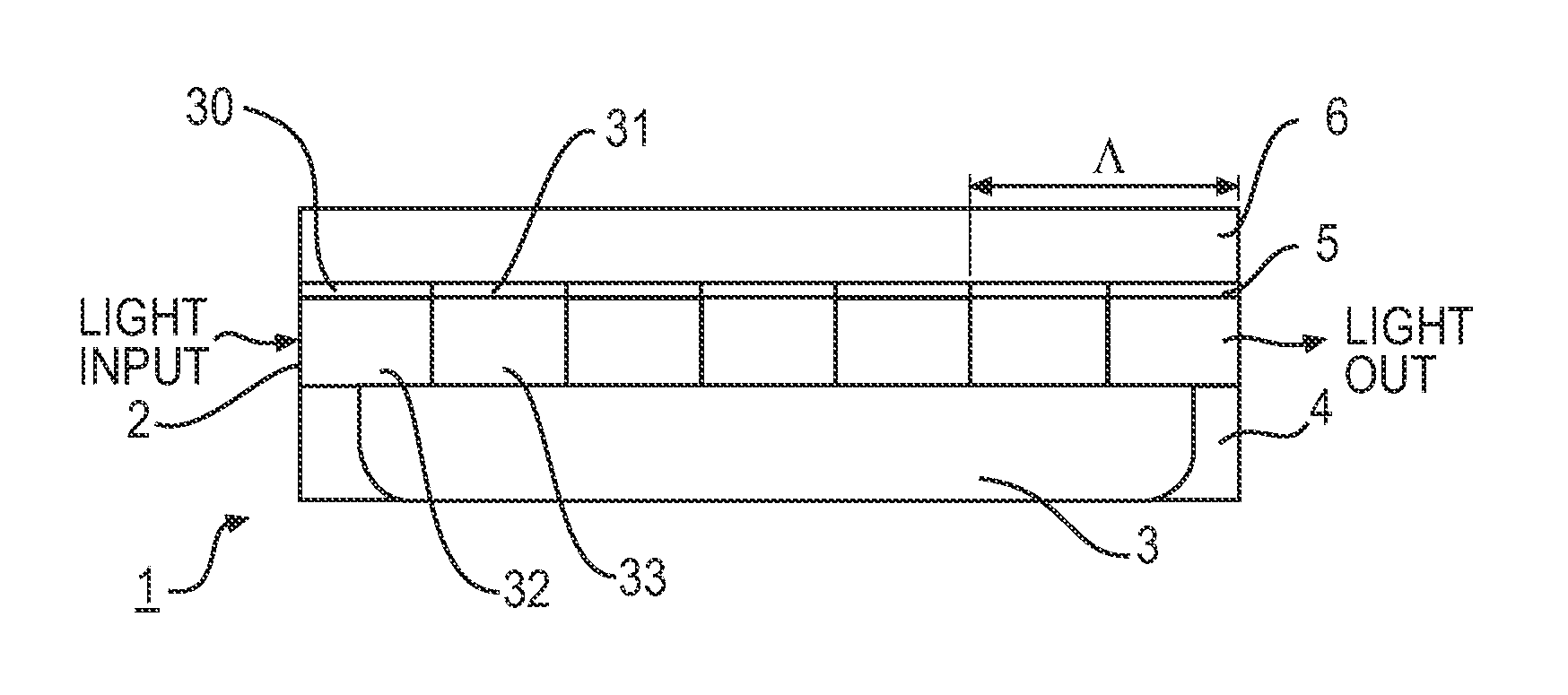

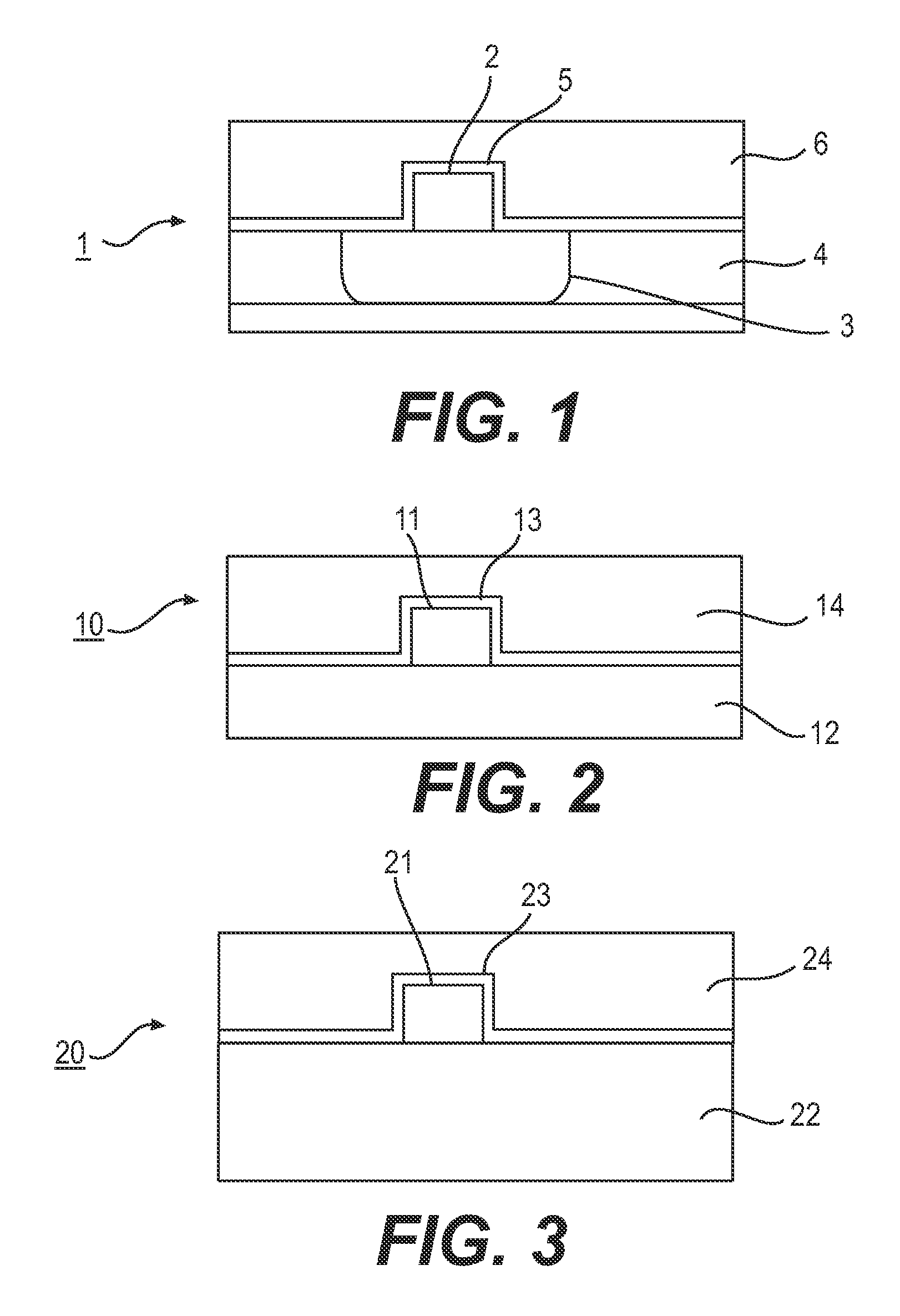

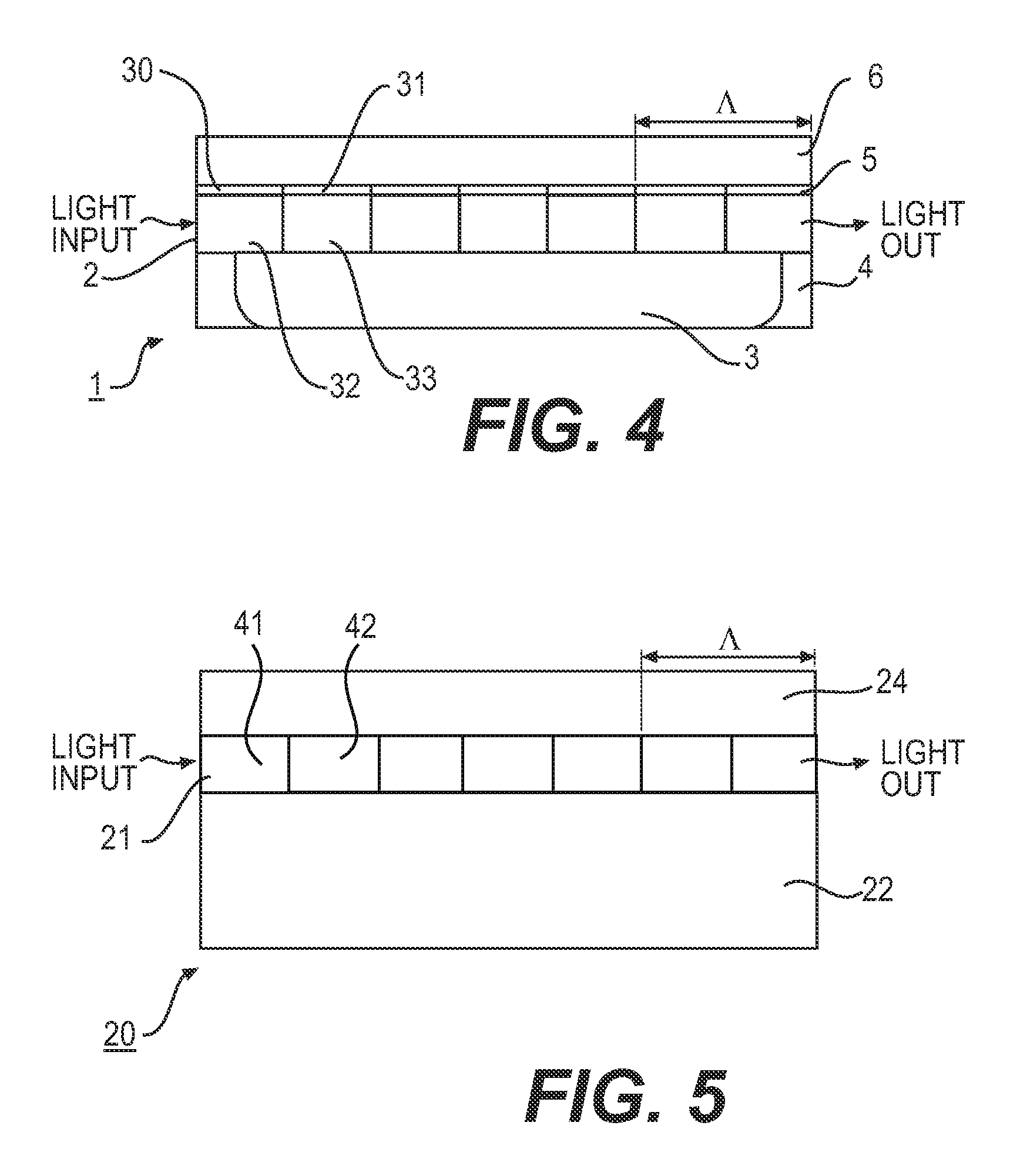

Methods of producing strain in a semiconductor waveguide and related devices

ActiveUS9261647B1Increase strainLow sectionOptical waveguide light guideNon-linear opticsPhotonicsWaveguide

Quasi-phase matched (QPM), semiconductor photonic waveguides include periodically-poled alternating first and second sections. The first sections exhibit a high degree of optical coupling (abbreviated “X2”), while the second sections have a low X2. The alternating first and second sections may comprise high-strain and low-strain sections made of different material states (such as crystalline and amorphous material states) that exhibit high and low X2 properties when formed on a particular substrate, and / or strained corrugated sections of different widths. The QPM semiconductor waveguides may be implemented as silicon-on-insulator (SOI), or germanium-on-silicon structures compatible with standard CMOS processes, or as silicon-on-sapphire (SOS) structures.

Owner:NAT TECH & ENG SOLUTIONS OF SANDIA LLC

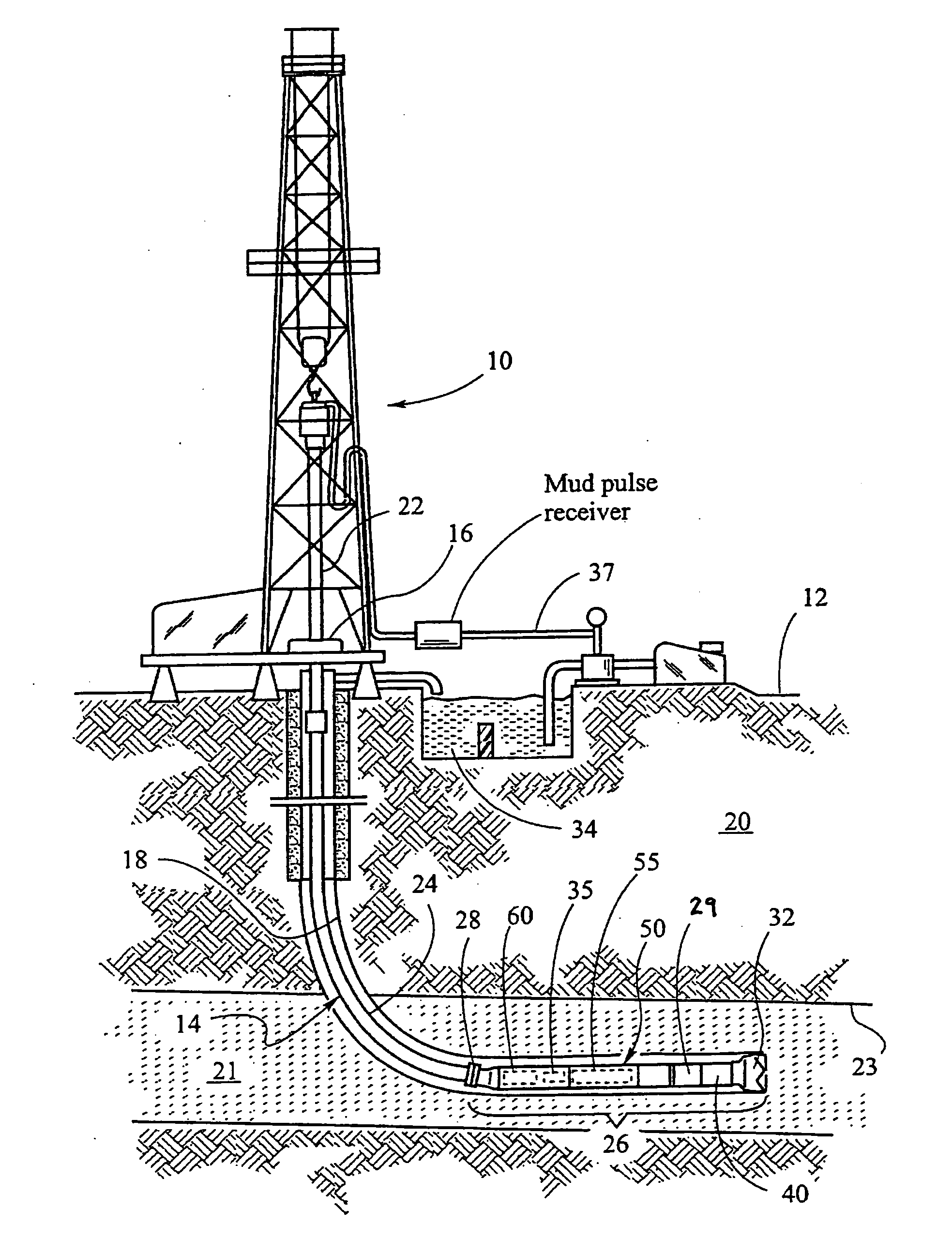

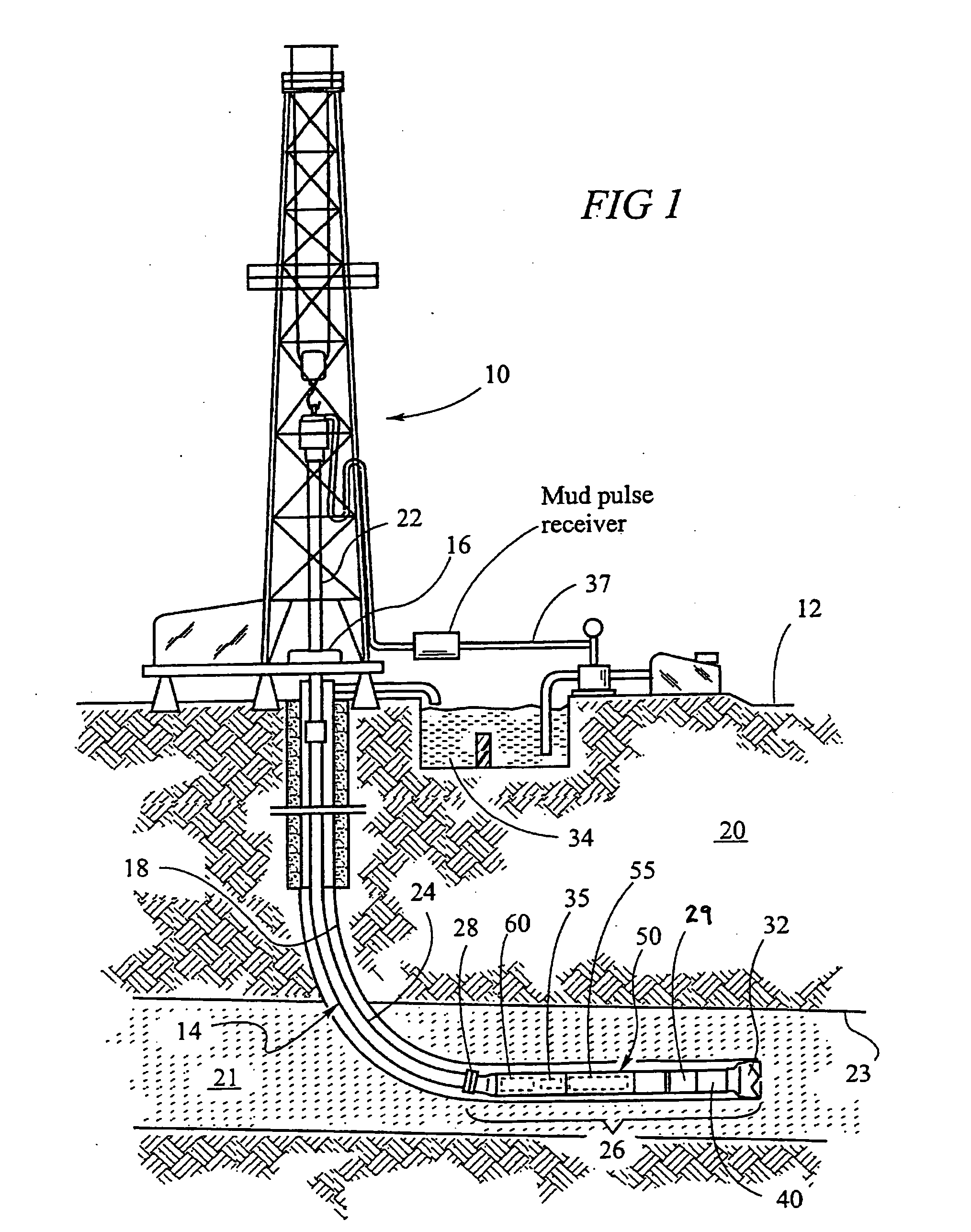

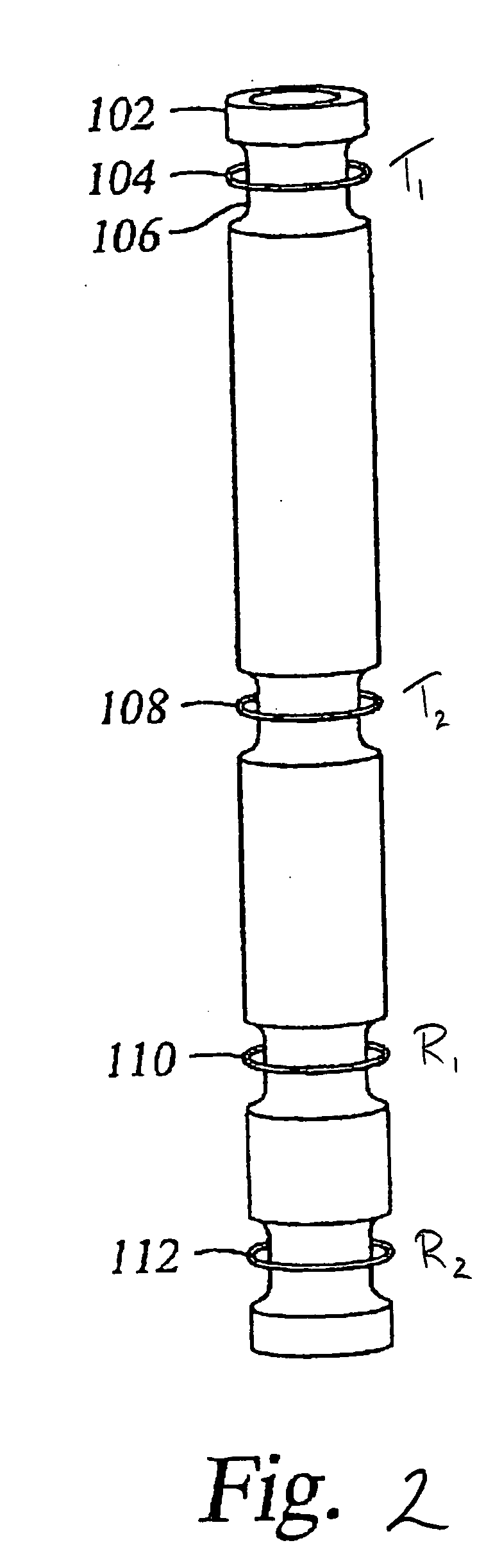

Receiver electronics proximate antenna

ActiveUS20050168224A1Increase in sizeImprove energy consumptionConstructionsSemiconductor/solid-state device detailsSignal-to-noise ratio (imaging)Proximate

A resistivity tool includes receiver electronics near each receiver antenna loop. Placement of the electronics in this position such as at the circuit card between the terminal ends of the receiver antenna loop improves signal to noise ratio by reducing or eliminating interference, noise, and cross-talk of transmissions from the receiver to a remote microprocessor. By using material such as silicon-on-sapphire, electronics can be miniaturized and operate reliably at when exposed to high temperatures, even for long periods.

Owner:HALLIBURTON ENERGY SERVICES INC +1

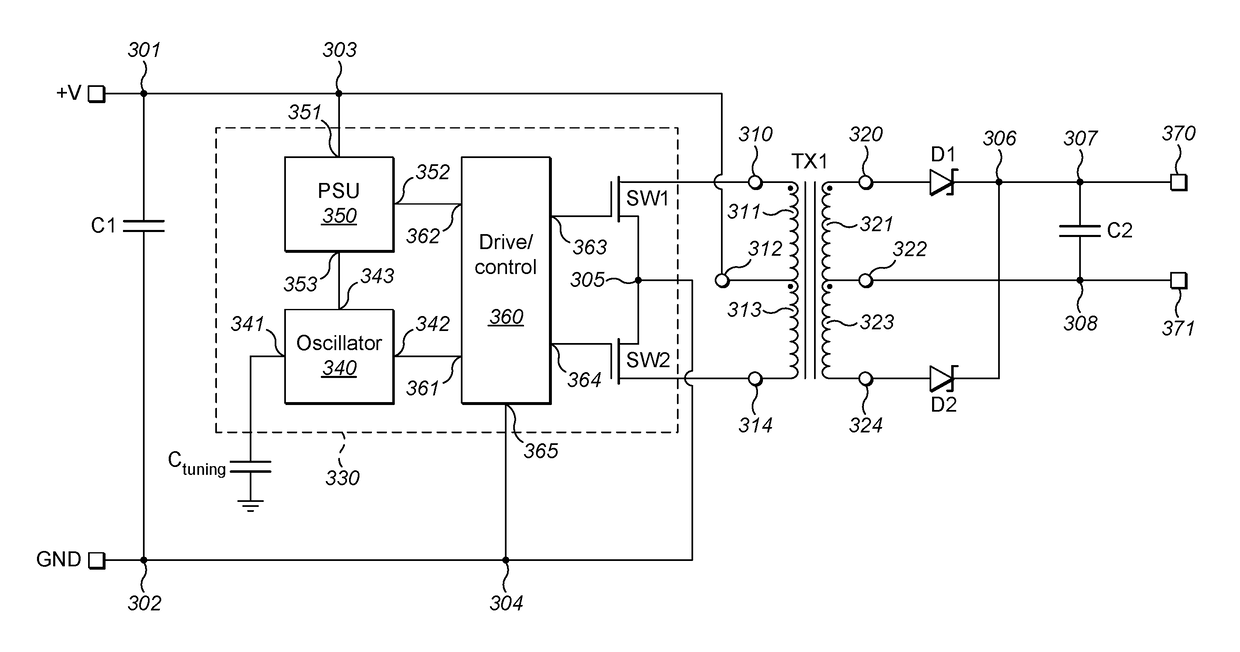

Dc-dc converter device

ActiveUS20180076704A1Less input powerReduce lossesEfficient power electronics conversionConversion constructional detailsDc dc converterSwitching signal

A DC-DC converter includes an insulating substrate; a magnetic core embedded in the insulating substrate, the magnetic core having non-zero x, y and z dimensions of less than or equal to about 5.4 mm by about 5.4 mm by about 1.8 mm; separate primary and secondary transformer windings surrounding first and second regions of the magnetic core; and a control circuit including: an oscillator; a drive circuit coupled to the oscillator; and one or more switches coupled to the drive circuit; the drive circuit providing a switching signal to the one or more switches and energizing the one or more switches to provide a drive voltage to the primary transformer winding. The one or more switches are Field Effect Transistors implemented in a Silicon-on-Insulator configuration or as a Silicon-on-Sapphire configuration.

Owner:MURATA MFG CO LTD

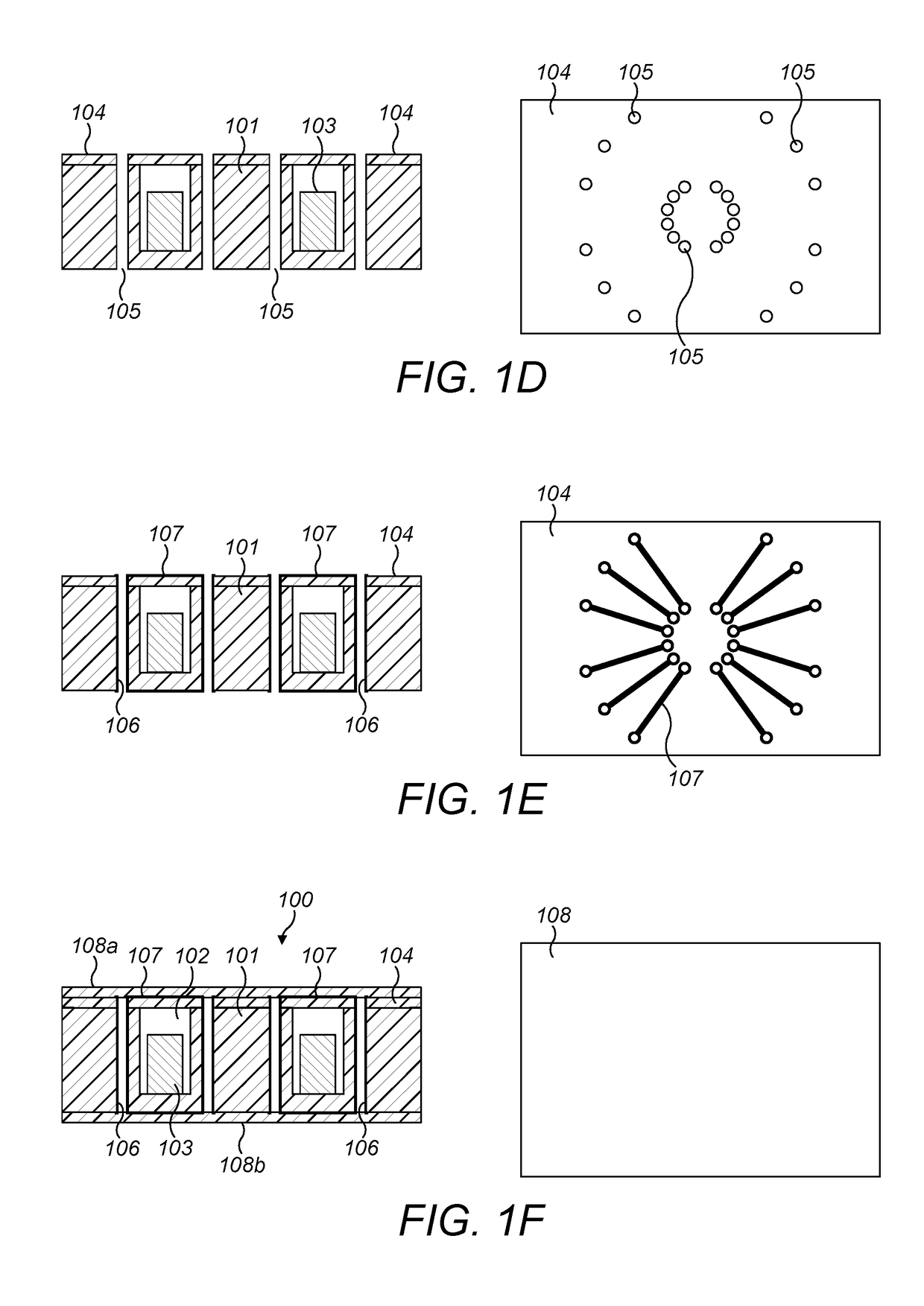

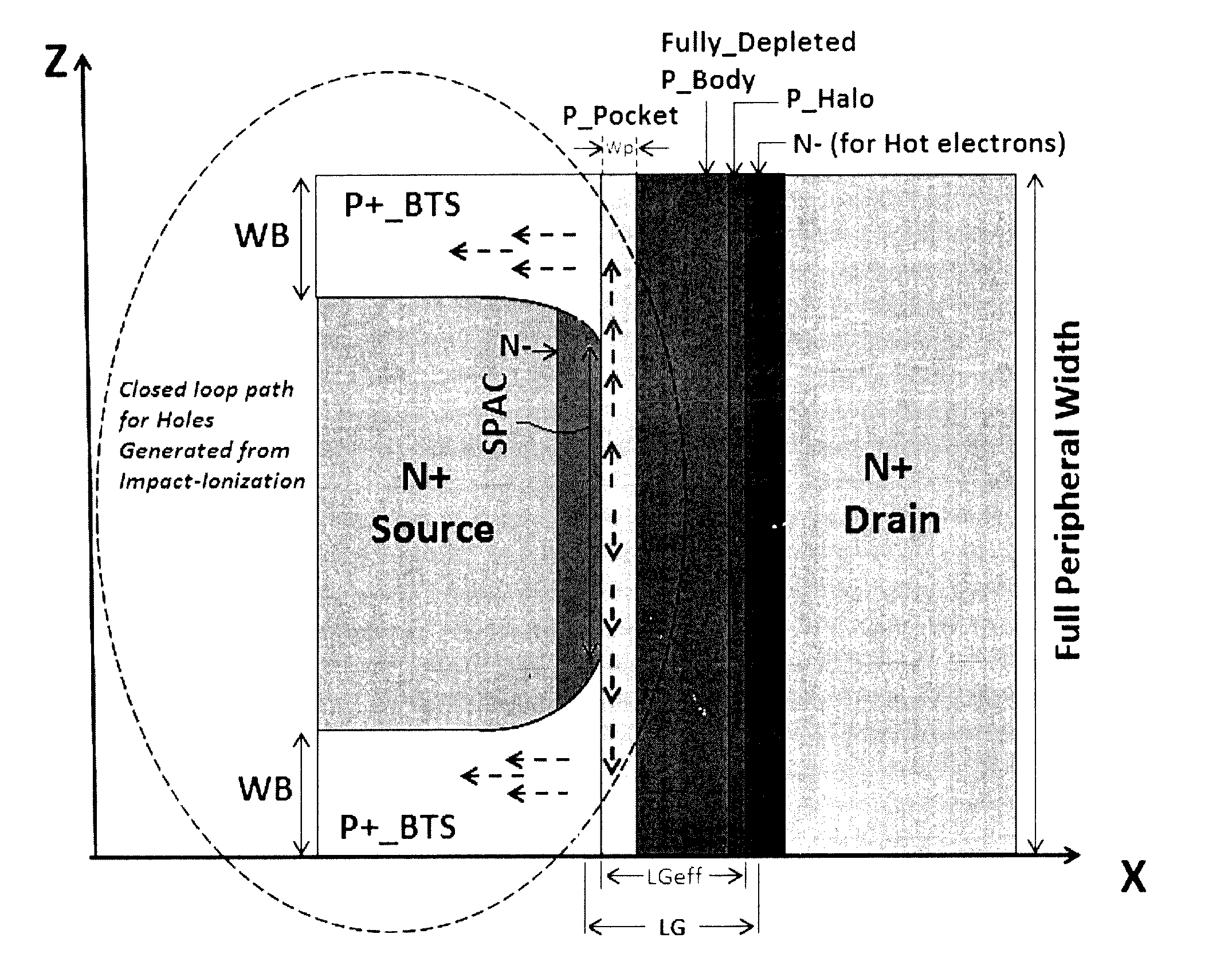

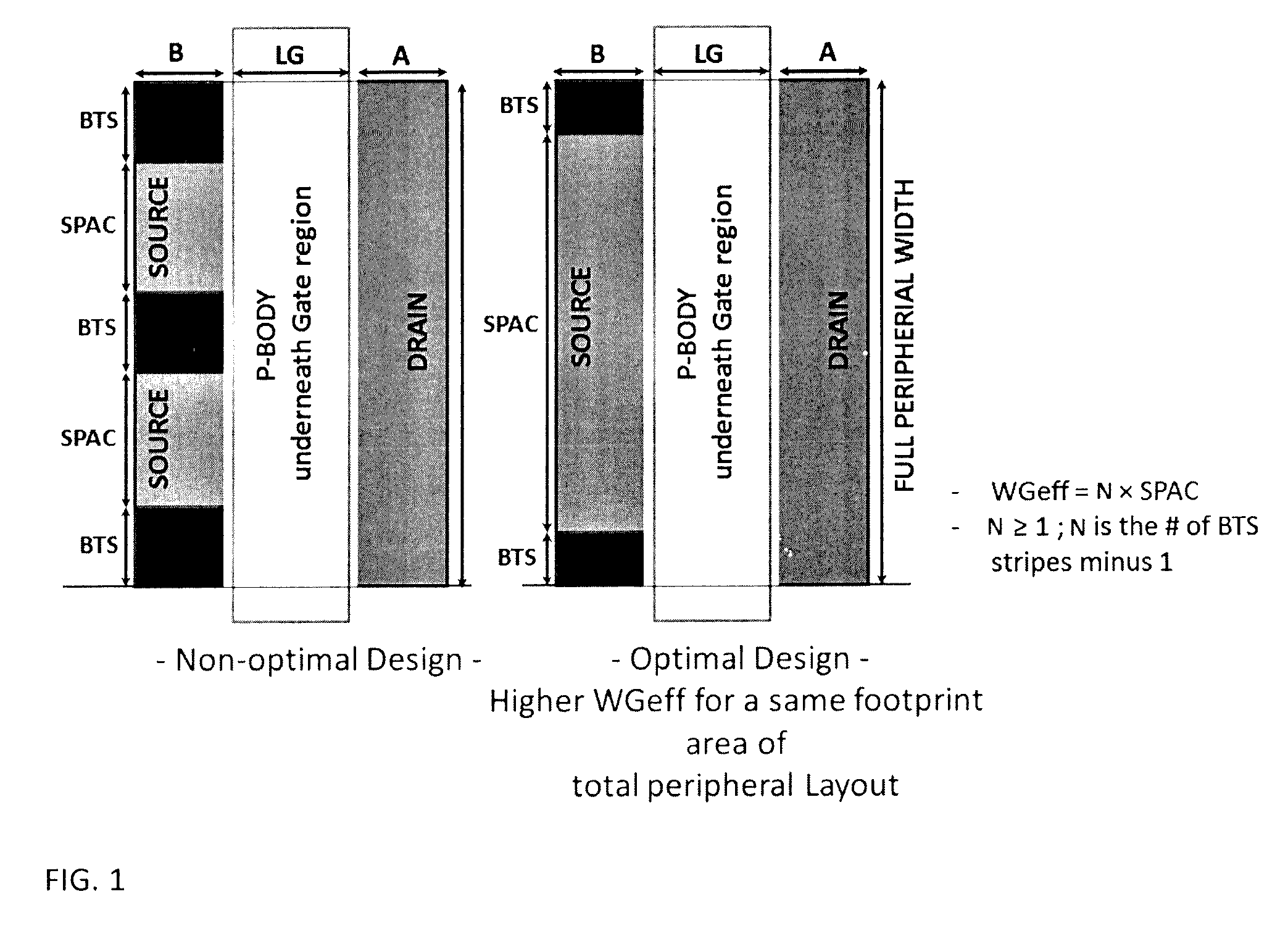

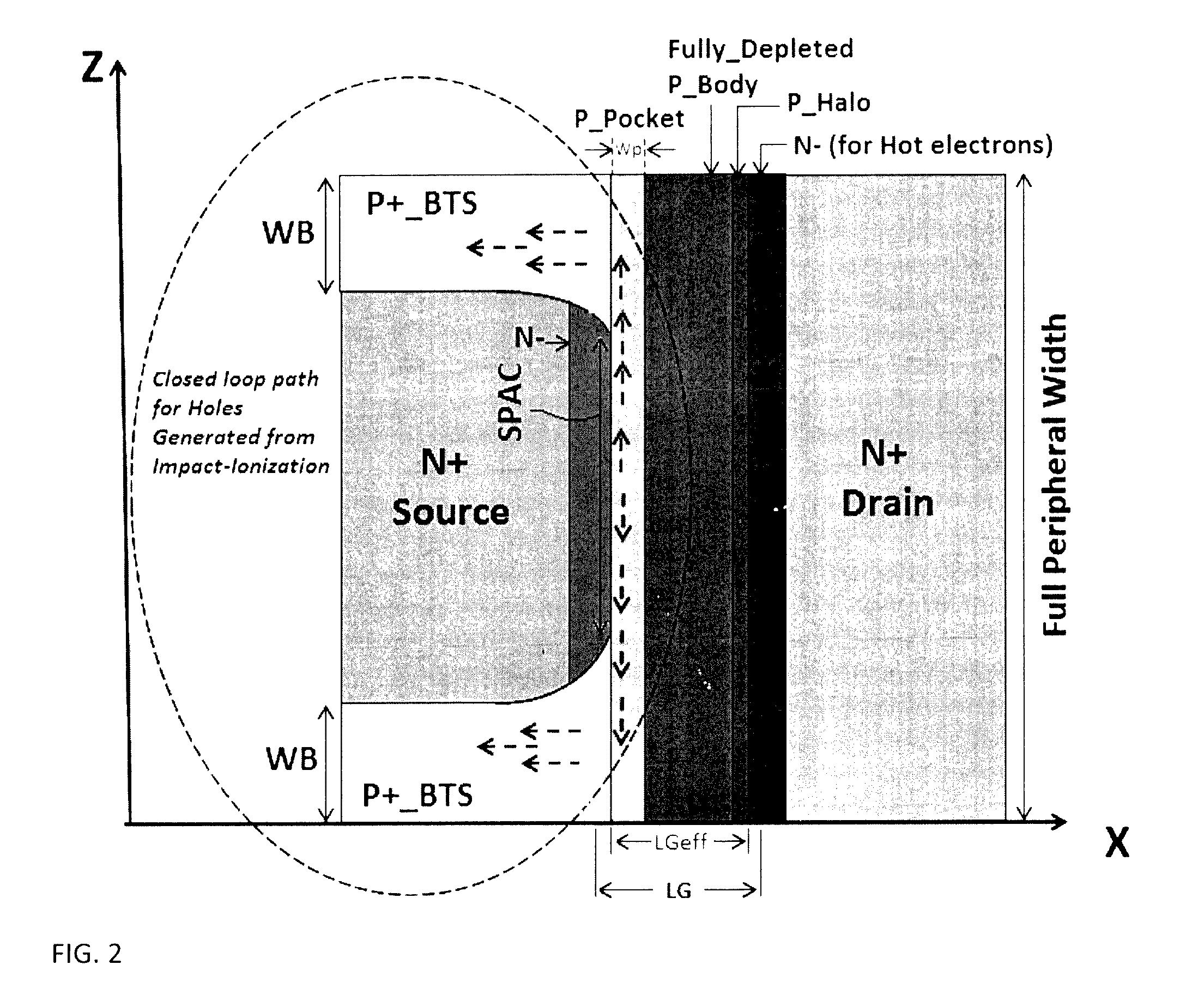

Approach for an Area-Efficient and Scalable CMOS Performance Based on Advanced Silicon-On-Insulator (SOI), Silicon-On-Sapphire (SOS) and Silicon-On-Nothing (SON) Technologies

InactiveUS20170040461A1High dopingReduce decreaseTransistorSolid-state devicesSilicon on sapphireCMOS

The invention provides the guided design approach to optimize the device performance for a best area-efficient layout footprint in a single-leg MOS device that is based on any of the SOI, SOS or SON technologies. The design methodology depends on a new proprietary device architecture that is also being claimed in this patent and that allows the implementations of the design equations of our methodology.

Owner:TARAKJI AHMAD

Compact, all solid-state, avalanche photodiode emitter-detector pixel with electronically selectable, passive or active detection mode, for large-scale, high resolution, imaging focal plane arrays

An advanced, back-illuminated, silicon avalanche photodiode (APD) design is presented using silicon-on-sapphire with a novel crystalline aluminum nitride (AlN) antireflective layer between the silicon and R-plane sapphire. The substrate supports optical and electrical integration of a high quantum efficiency silicon APD with a gallium nitride (GaN)-VCSEL diode in each pixel to form a novel, compact, emitter-detector pixel for passive and active 2-D and 3-D high resolution, imaging focal plane arrays. Silicon mesa pixels are anisotropically etched with a central inverted mesa frustum cavity. The APD detector is fabricated in the silicon mesa and the GaN-VCSEL diode is grown epitaxially in the center of the mesa. A sapphire microlens below each pixel collimates the VCSEL beam and focuses optical returns into the APD detector. APDs share a common front-side anode, and VCSELs share a common cathode. The APD cathode is electrically connected to the VCSEL diode anode in each emitter-detector pixel.

Owner:STERN ALVIN GABRIEL

Circuit and method for improving ESD tolerance and switching speed

Embodiments of systems, methods, and apparatus for improving ESD tolerance and switching time for semiconductor devices including metal-oxide-semiconductor (MOS) field effect transistors (FETs), and particularly to MOSFETs fabricated on semiconductor-on-insulator and silicon-on-sapphire substrates. Embodiments provide an improved FET structure having an accumulated charge sink (ACS) circuit, fast switching times, and improved ESD tolerance.

Owner:PSEMI CORP

SOS substrate with reduced stress

There is provided an SOS substrate with reduced stress. The SOS substrate is a silicon-on-sapphire (SOS) substrate comprising a sapphire substrate and a monocrystalline silicon film on or above the sapphire substrate. The stress of the silicon film of the SOS substrate as measured by a Raman shift method is 2.5*10 <8> Pa or less across an entire in-plane area of the SOS substrate.

Owner:SHIN ETSU CHEM CO LTD

Radiation-hardened silicon-on-insulator CMOS device, and method of making the same

A method for eliminating the radiation-induced off-state current in the P-channel ultrathin silicon-on-sapphire transistor, by providing a retrograde dopant concentration profile that has the effect of moving the Fermi level at the back of the device away from that part of the bandgap where the interface states are located. When the Fermi level does not swing through this area in any region of operation of the device, subthreshold stretchout of the I-V curves does not occur.

Owner:CABLE JAMES S +3

Circuit and Method for Improving ESD Tolerance and Switching Speed

ActiveUS20150145052A1Fast switching timeImprove ESD toleranceTransistorSemiconductor/solid-state device detailsMOSFETEngineering

Embodiments of systems, methods, and apparatus for improving ESD tolerance and switching time for semiconductor devices including metal-oxide-semiconductor (MOS) field effect transistors (FETs), and particularly to MOSFETs fabricated on semiconductor-on-insulator and silicon-on-sapphire substrates. Embodiments provide an improved FET structure having an accumulated charge sink (ACS) circuit, fast switching times, and improved ESD tolerance.

Owner:PSEMI CORP

Radiation-hardened silicon-on-insulator CMOS device, and method of making the same

InactiveUS20050006703A1Improve radiation hardnessPerformance advantageSolid-state devicesSemiconductor/solid-state device manufacturingCMOSP channel

A silicon-on-insulator metal oxide semiconductor device comprising ultrathin silicon-on-sapphire substrate; at least one P-channel MOS transistor formed in the ultrathin silicon layer; and N-type impurity implanted within the ultrathin silicon layer and the sapphire substrate such that peak N-type impurity concentration in the sapphire layer is greater than peak impurity concentration in the ultrathin silicon layer.

Owner:PSEMI CORP