Approach for an Area-Efficient and Scalable CMOS Performance Based on Advanced Silicon-On-Insulator (SOI), Silicon-On-Sapphire (SOS) and Silicon-On-Nothing (SON) Technologies

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

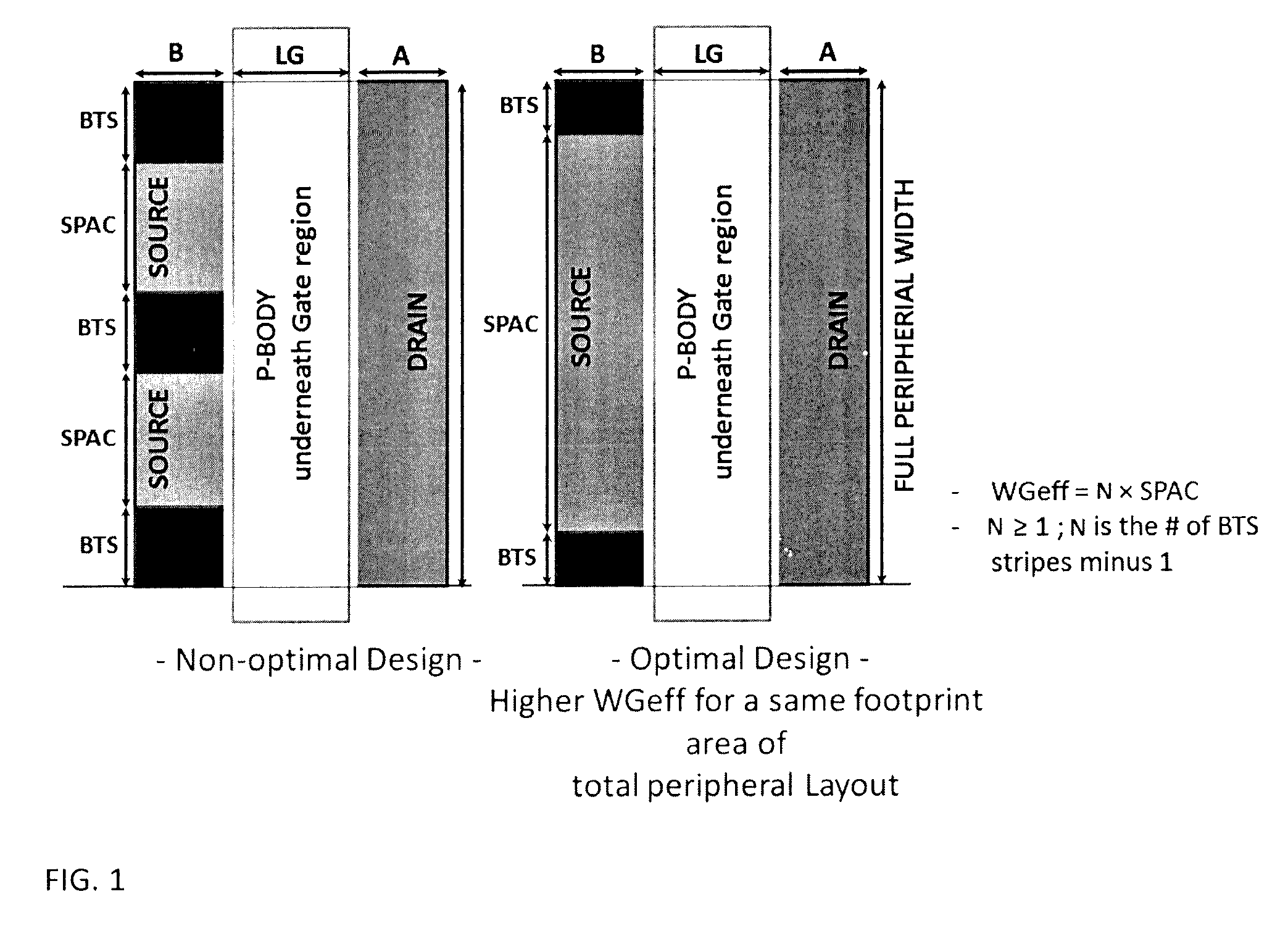

[0074]Today, the total Silicon area consumed by BTS in an IC based on SOI (and similarly based on either the SOS or the SON) is being determined through trial-and-errors such to ensure a fully functional IC that meets some targeted specifications. Consequently, such un-optimized total area of BTS in the IC does lead to larger peripheral footprint of the layout that is not necessary needed. That is not to mention the added time and the higher manufacturing costs that are associated with such repetitive trial-and-errors routines.

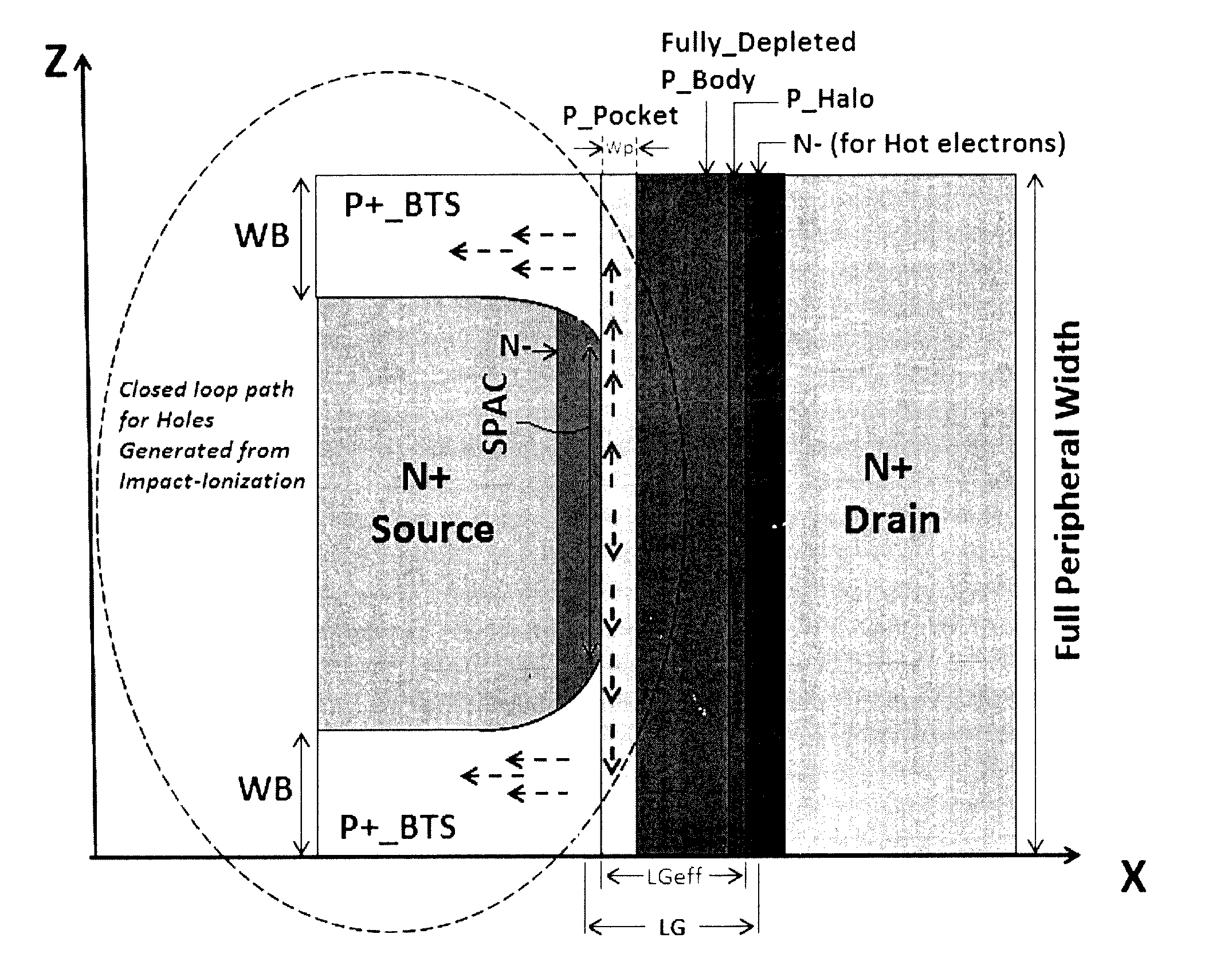

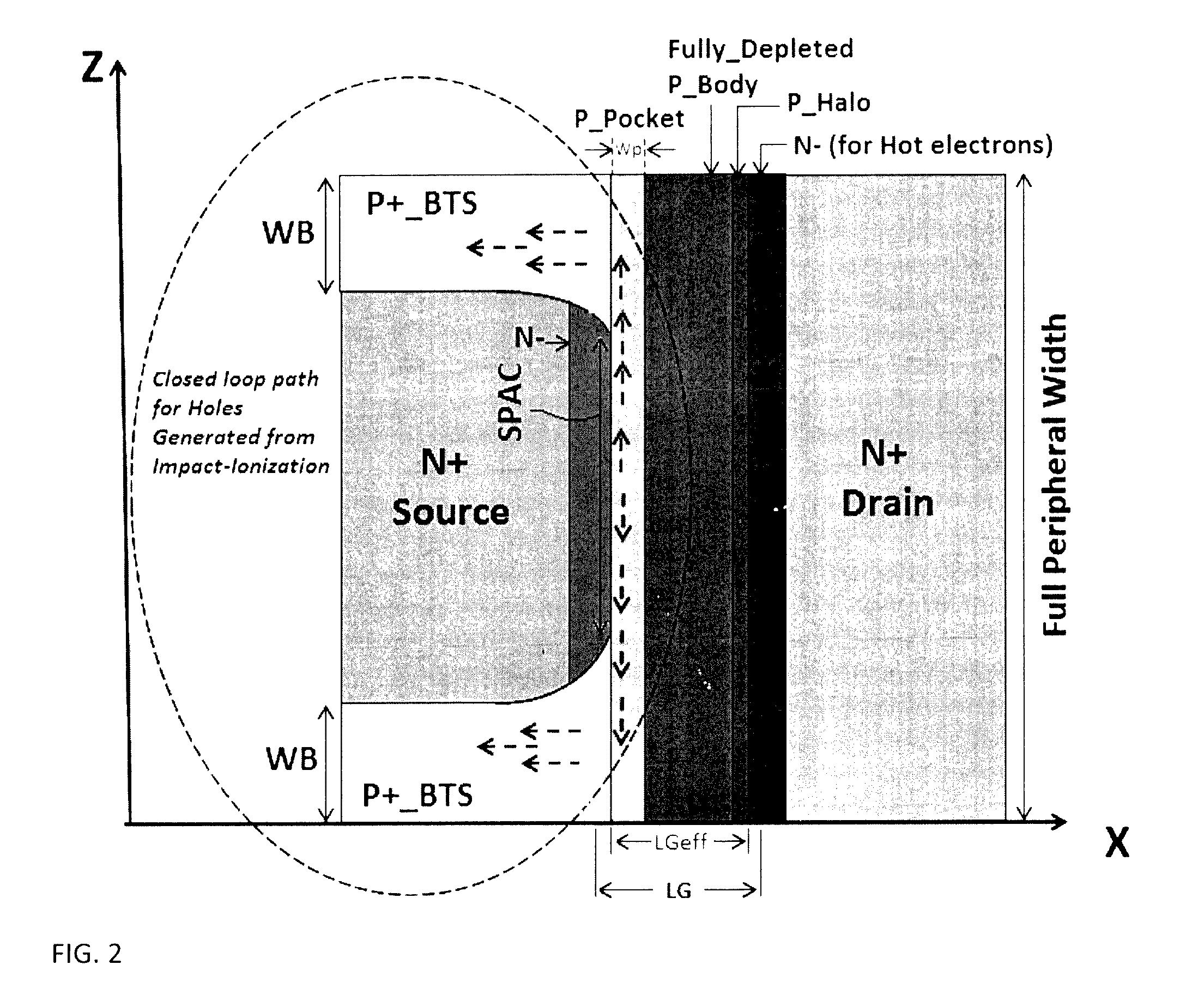

[0075]Our well defined and demonstrated design methodology and that is being claimed through this patent application, relies on our unique and proprietary architecture of the 1-legged SOI MOS basis device of FIG. 2, FIG. 3 A, FIG. 3 B and FIG. 3 C that accommodates our design methodology. Our proprietary basis structure is distinct through the tunable (calculated) dimension (Wp) of its P_Pocket alongside the Gate-length, through its analytically defined (calcu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More