Manufacturing method of novel printed circuit board

A technology of printed circuit board and manufacturing method, which is applied in the direction of electrical connection formation of printed components, etc., can solve the problems of poor thermal reliability performance, poor bonding force between conductive layer and dielectric layer, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

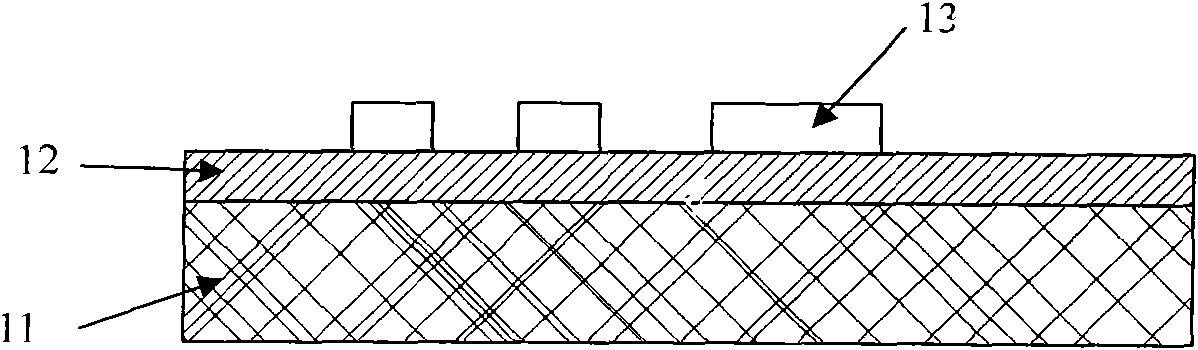

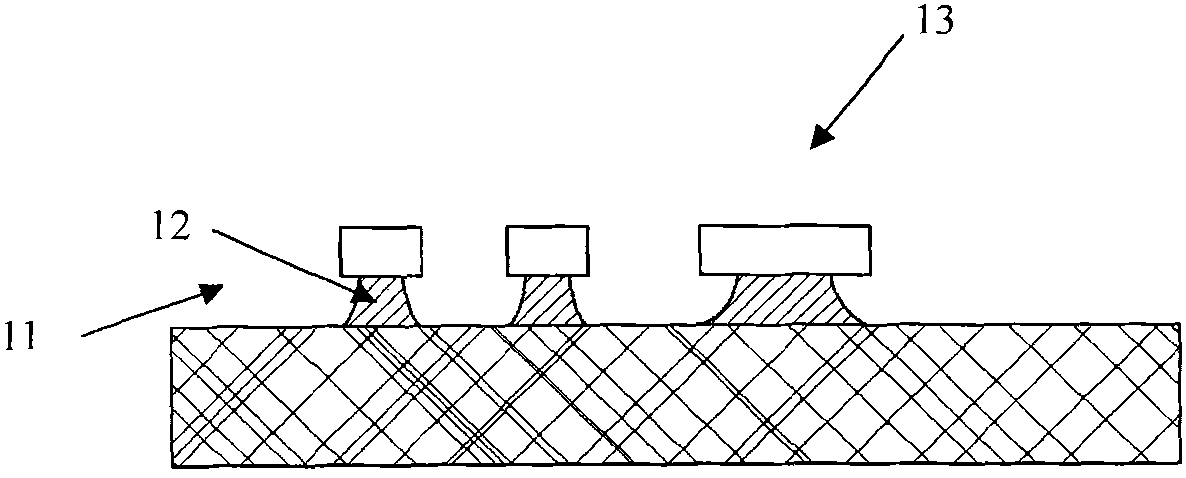

[0046] The manufacturing method of the present invention will be further described below in conjunction with the accompanying drawings.

[0047] see Figure 5a ~ Figure 5h , the present invention adopts the improved semi-additive method to combine with the hole-filling process under pattern electroplating to manufacture the concrete steps of the printed circuit board as follows:

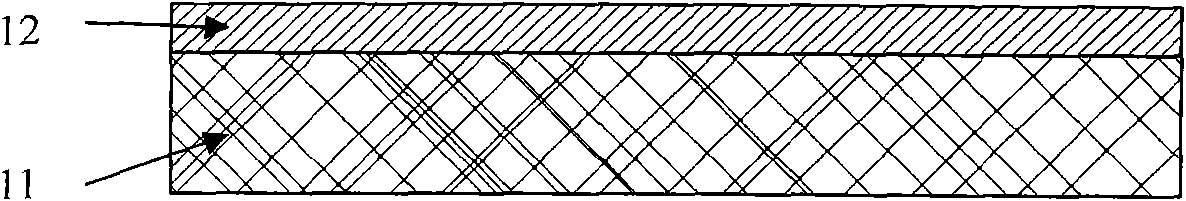

[0048] Step 1, such as Figure 5a As shown, first a dielectric layer 52 is prepared, and a conductive layer 51 is thermally pressed on the dielectric layer. The dielectric layer can be fabricated on a composite substrate including an insulating carrier and a surface conductive layer, or can be directly fabricated on the conductive layer. In this embodiment, the dielectric layer 52 and the conductive layer 51 are laminated and formed on the substrate 53 including the dielectric layer and the conductive layer. The dielectric layer 52 is epoxy resin material containing glass cloth, and the conductive...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More