Array substrate, display panel, display device and manufacturing method of array substrate

A technology of array substrate and substrate substrate, applied in semiconductor/solid-state device manufacturing, instruments, semiconductor devices, etc., can solve problems such as product yield decline

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

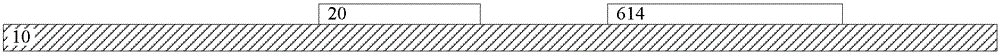

[0105] combined below figure 2 , Figure 3a and Figure 3b The array substrate 1 according to the first embodiment of the present disclosure is described. figure 2 is a schematic top view of the array substrate 1 according to the first embodiment, Figure 3a is the edge of the array substrate 1 figure 2 A schematic cross-sectional view of the A-B line, and Figure 3b is the edge of the array substrate 1 figure 2 Schematic cross-sectional view of line C-D.

[0106] The array substrate 1 of the display panel includes gate lines 20 and data lines which are insulated from each other on the base substrate 10 and intersect to define a plurality of sub-pixel units 30 . A thin film transistor 40 and a pixel electrode 50 are formed in each sub-pixel unit 30 . The thin film transistor 40 includes a gate electrode 40a, a source electrode 40b, and a drain electrode 40c. The data lines include a first data line 61 and a second data line 62 arranged side by side between every tw...

no. 2 example

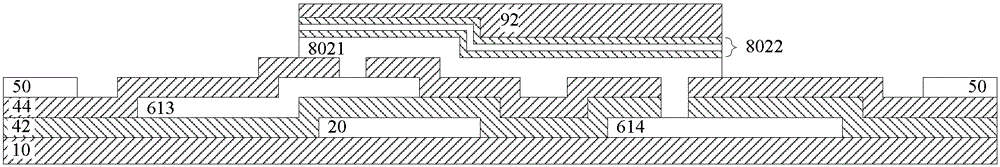

[0114] combined below Figure 4 , Figure 5a and Figure 5b An array substrate 2 according to a second embodiment of the present disclosure is described. Figure 4 is a schematic top view of the array substrate 2 according to the second embodiment, Figure 5a is the edge of the array substrate 2 Figure 4 A schematic cross-sectional view of the A-B line, and Figure 5b is the edge of the array substrate 2 Figure 4 Schematic cross-sectional view of line C-D.

[0115] The difference between the second embodiment and the first embodiment is that the first segment of the first data line is set on the same layer as the source / drain electrode of the thin film transistor, instead of being on the same layer as the gate electrode of the thin film transistor as in the first embodiment. layer settings.

[0116] Such as Figure 4 As shown, the first data line 61 includes a plurality of first segments 613 and second segments 614 arranged alternately. The first segment 613 is resp...

no. 3 example

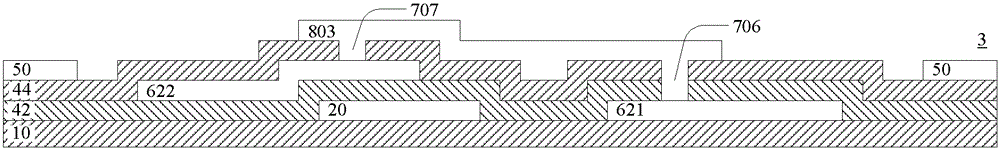

[0122] combined below Figure 6 , Figure 7a , Figure 7b , Figure 7c and Figure 7d An array substrate 3 according to a third embodiment of the present disclosure is described. Figure 6 is a schematic top view of the array substrate 3 according to the third embodiment, Figure 7a is the edge of the array substrate 3 Figure 6 A schematic cross-sectional view of the A-B line, Figure 7b is the edge of the array substrate 3 Figure 6 A schematic cross-sectional view of the G-H line, Figure 7c is the edge of the array substrate 3 Figure 6 A schematic cross-sectional view of line C-D, and Figure 7d is the edge of the array substrate 3 Figure 6 Schematic cross-sectional view of line E-F.

[0123] The difference between the third embodiment and the second embodiment is that the second data line includes segments arranged in a staggered manner, and each segment is arranged in a staggered layer with a corresponding segment of the first data line.

[0124] Such as ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More