Patents

Literature

105 results about "Power dissipation minimization" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

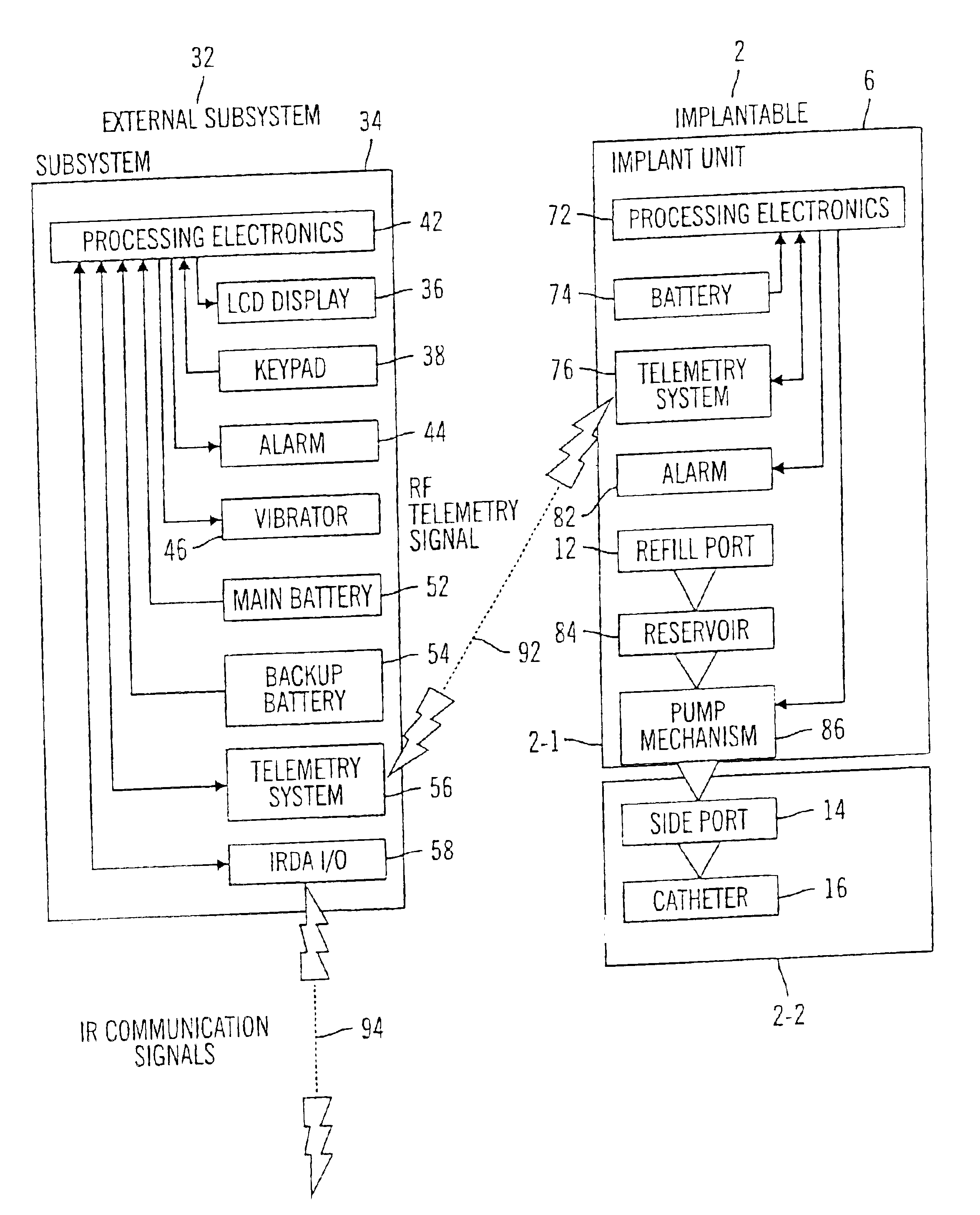

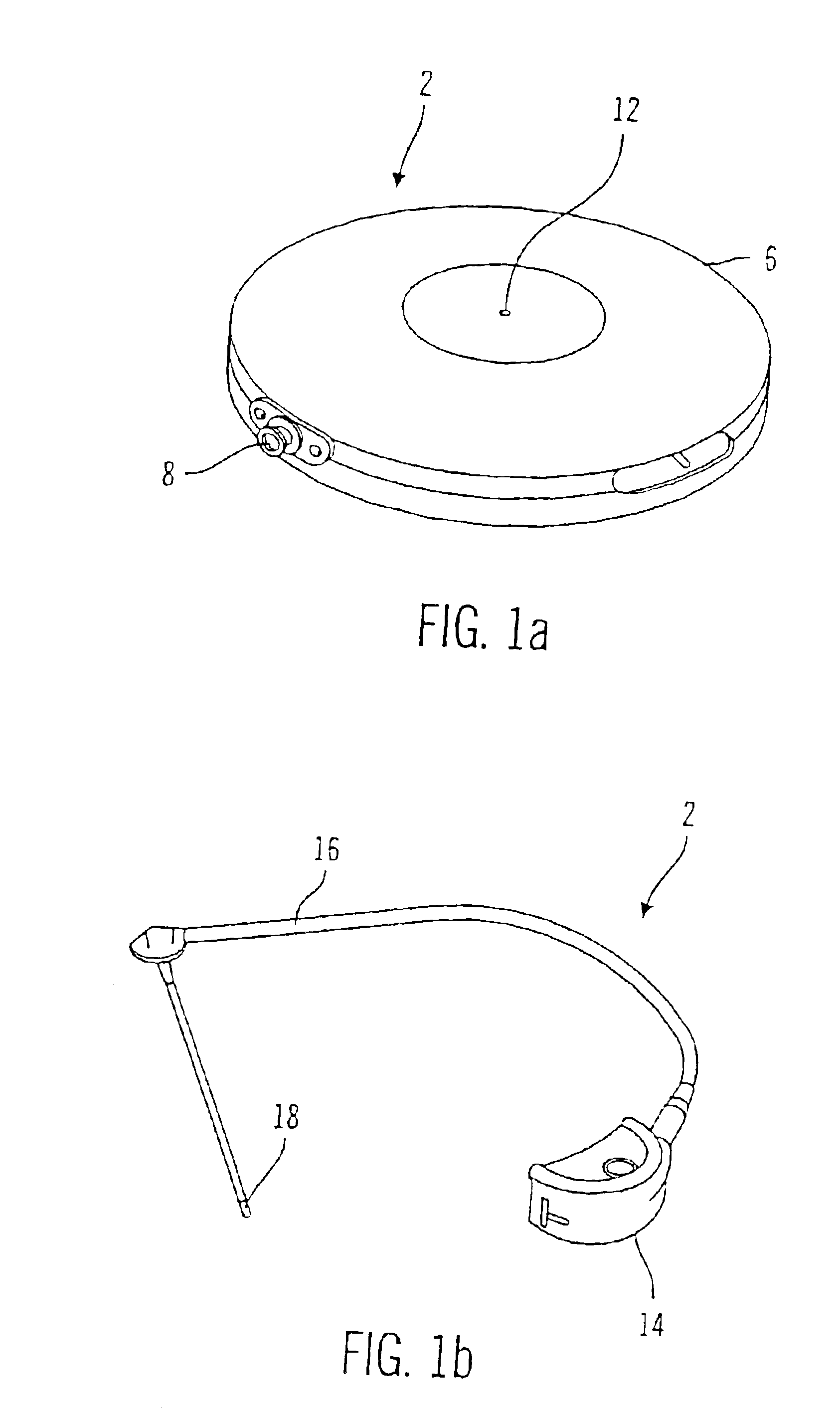

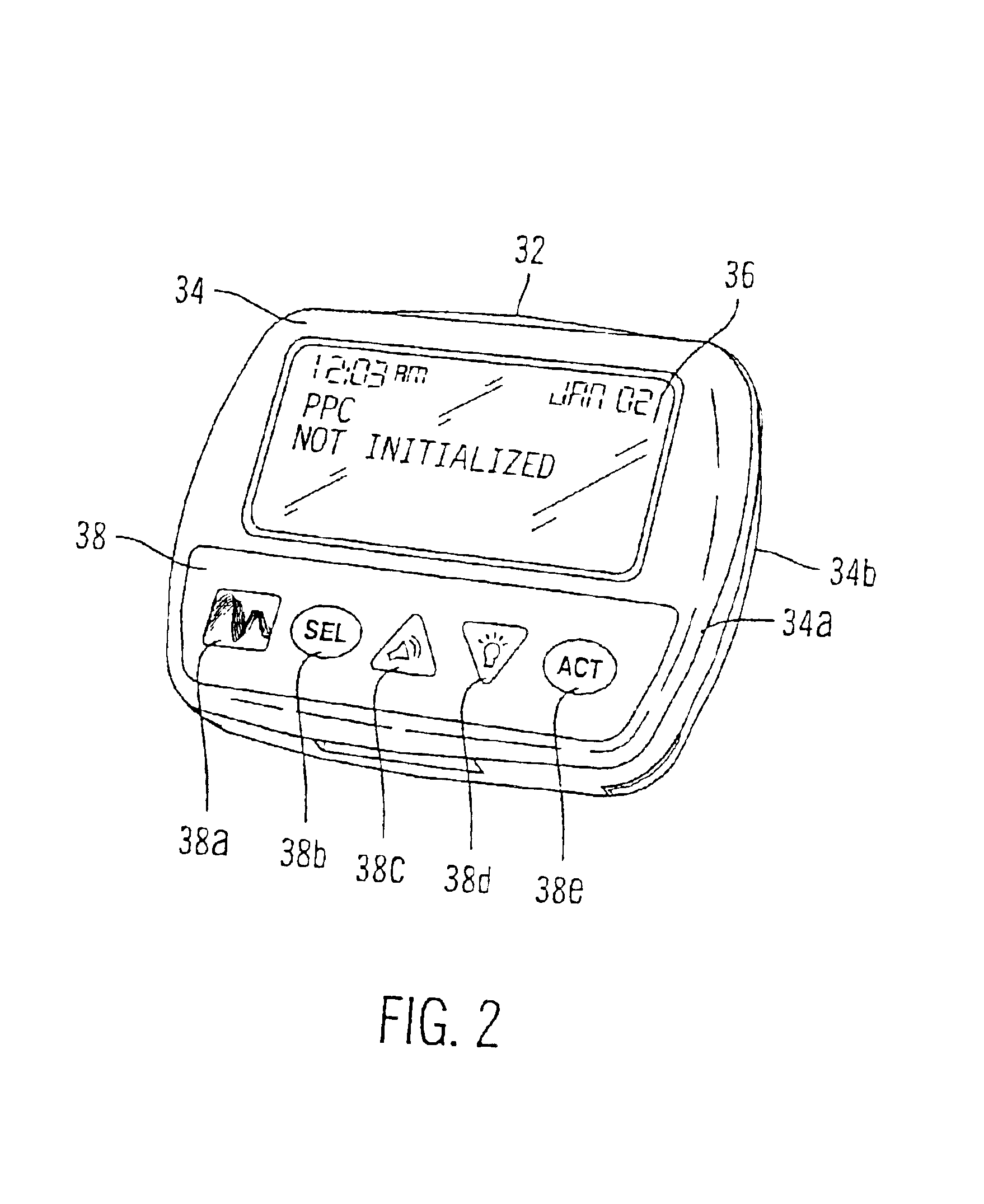

Ambulatory medical apparatus and method using a telemetry system with predefined reception listening

InactiveUS6950708B2Reduce power consumptionConsuming and burdensomeEnergy efficient ICTElectrotherapyAmbulatoryStart time

An implanted medical device (e.g. infusion pump) and an external device communicate with one another via telemetry messages that are receivable only during windows or listening periods. Each listening period is open for a prescribed period of time and is spaced from successive listening periods by an interval. The prescribed period of time is typically kept small to minimize power consumption. To increase likelihood of successful communication, the window may be forced to an open state, by use of an attention signal, in anticipation of an incoming message. To further minimize power consumption, it is desirable to minimize use of extended attention signals, which is accomplished by the transmitter maintaining an estimate of listening period start times and attempting to send messages only during listening periods. In the communication device, the estimate is updated as a result of information obtained with the reception of each message from the medical device.

Owner:MEDTRONIC MIMIMED INC

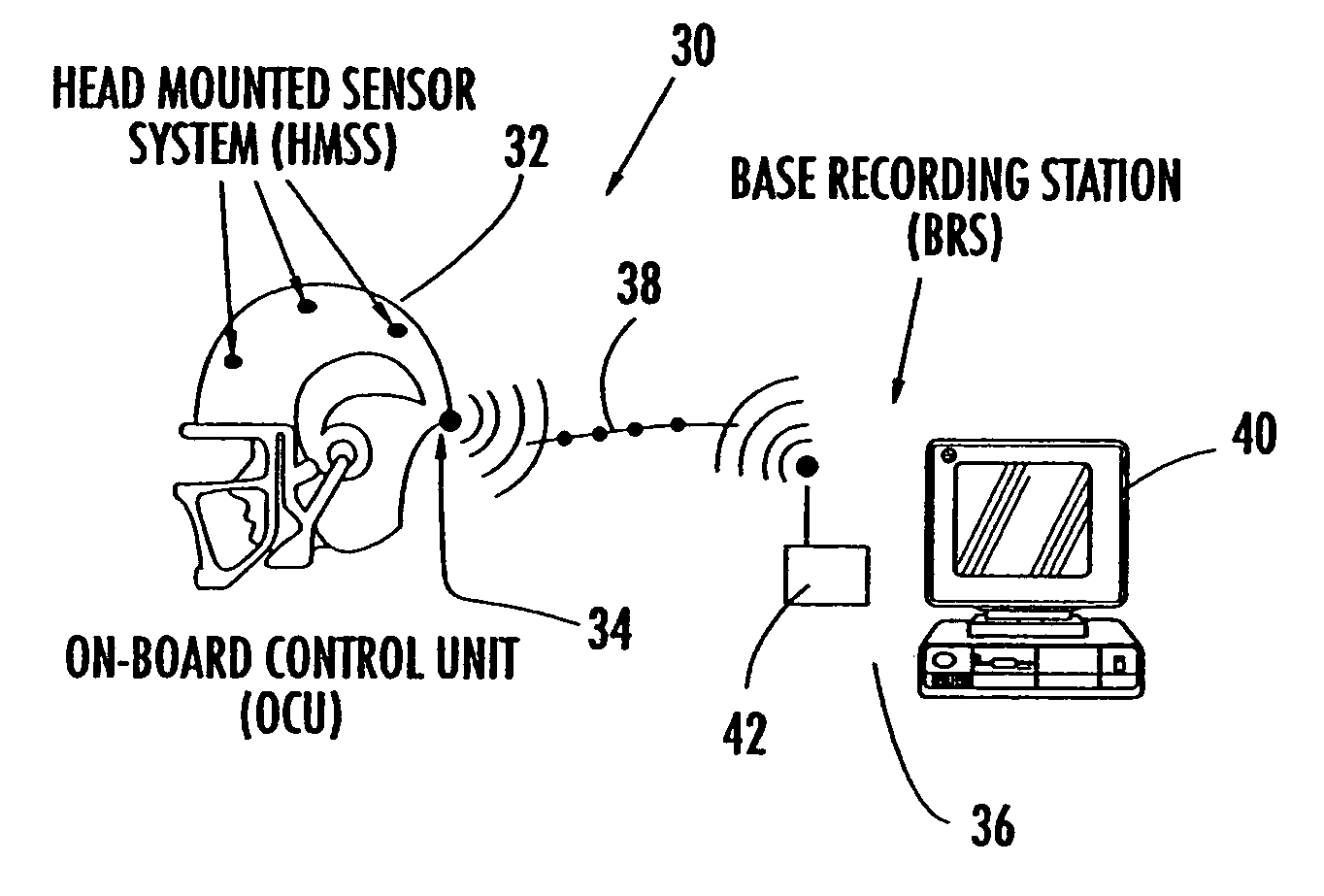

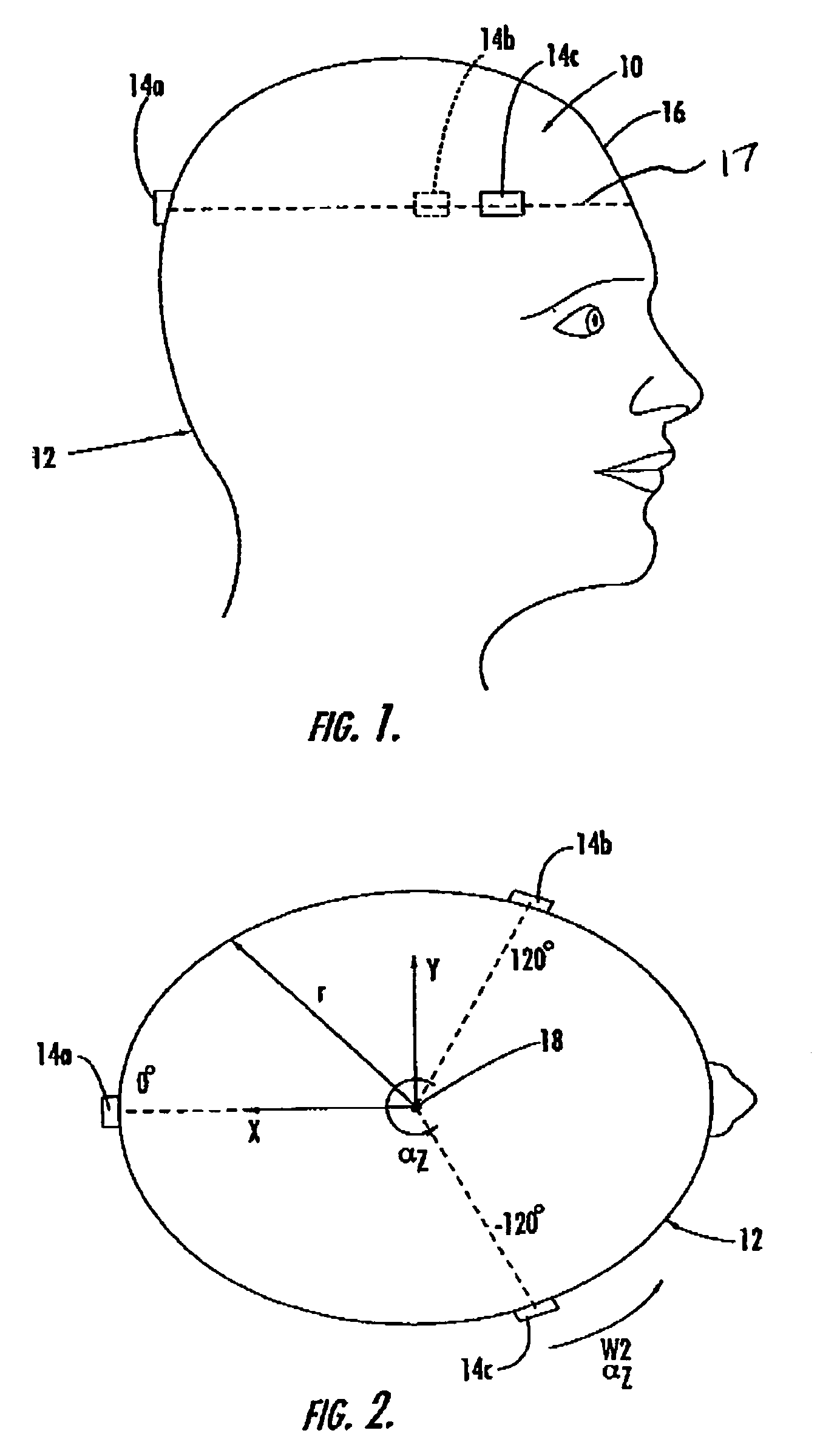

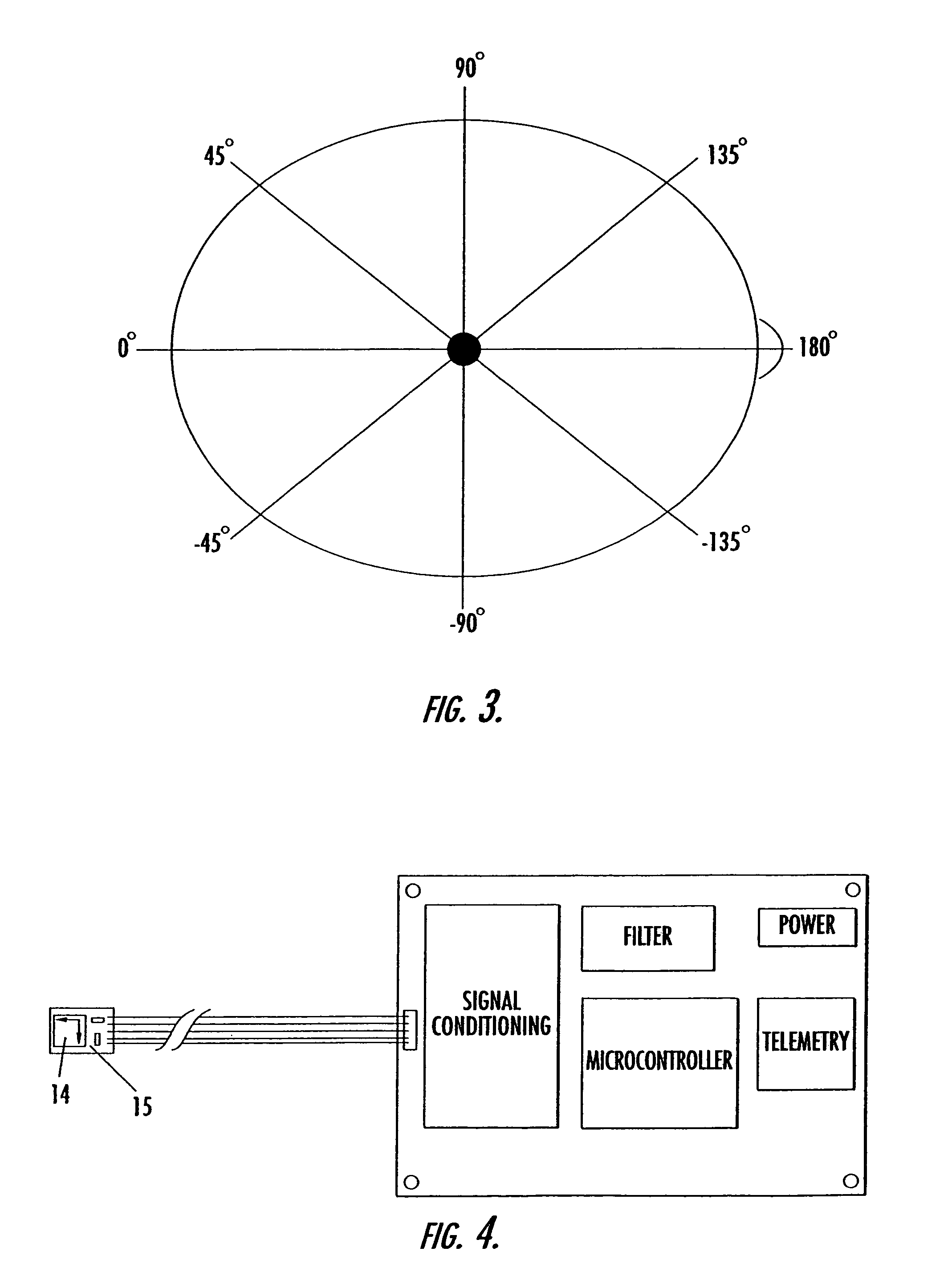

Power management of a system for measuring the acceleration of a body part

InactiveUS7526389B2Small sizeConvenient lightingFlow propertiesInertial sensorsAccelerometerProximate

Owner:RIDDELL

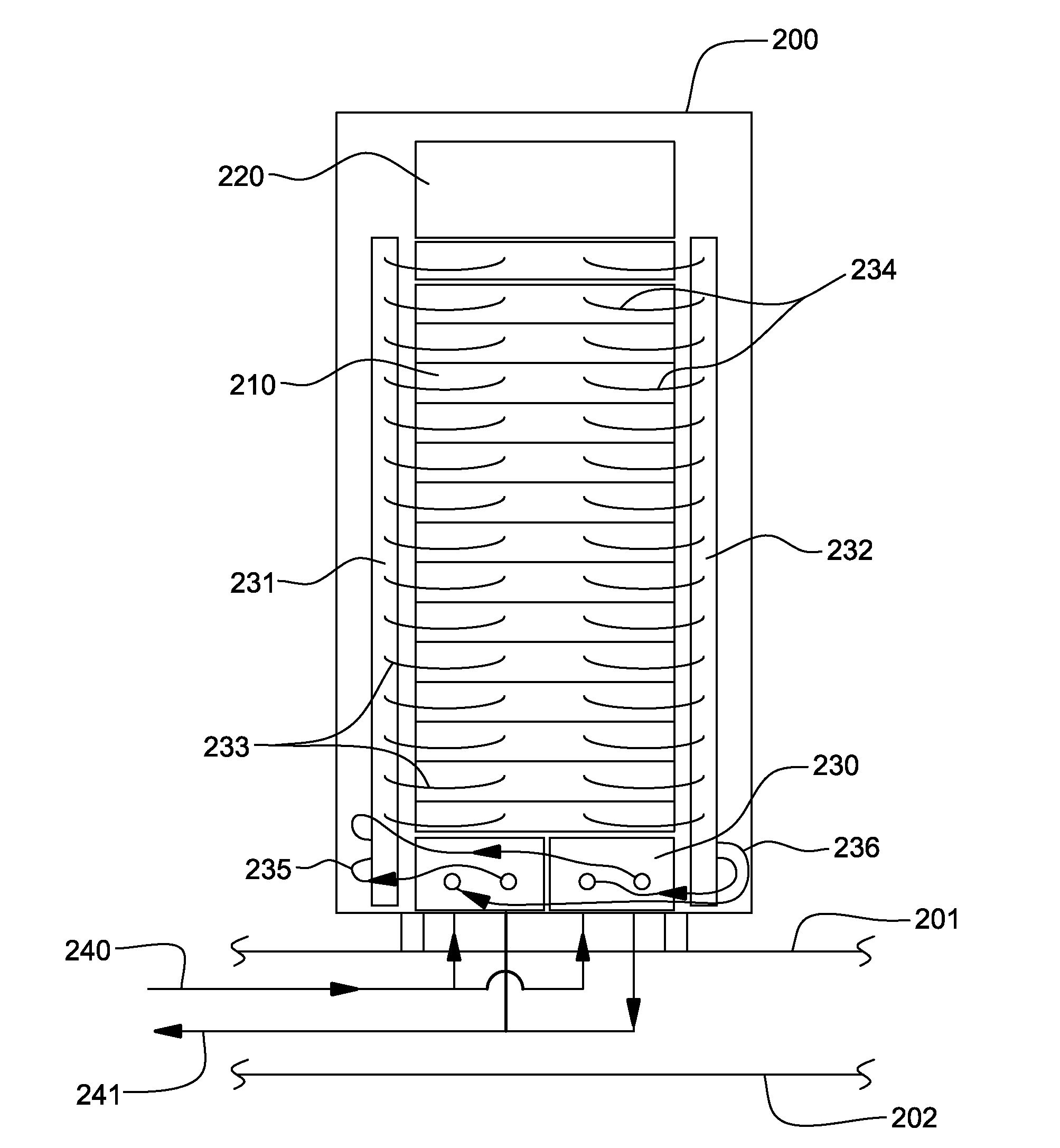

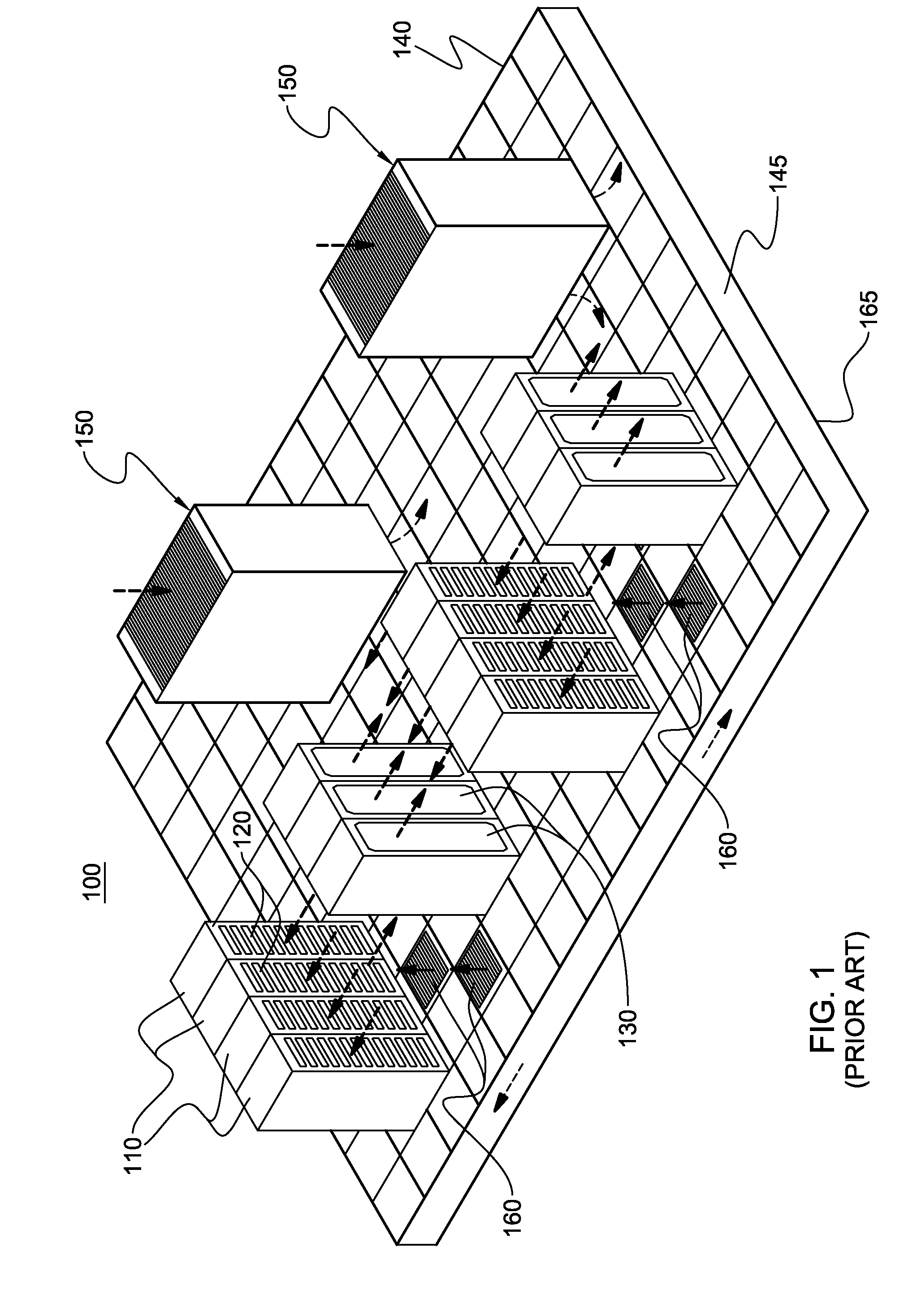

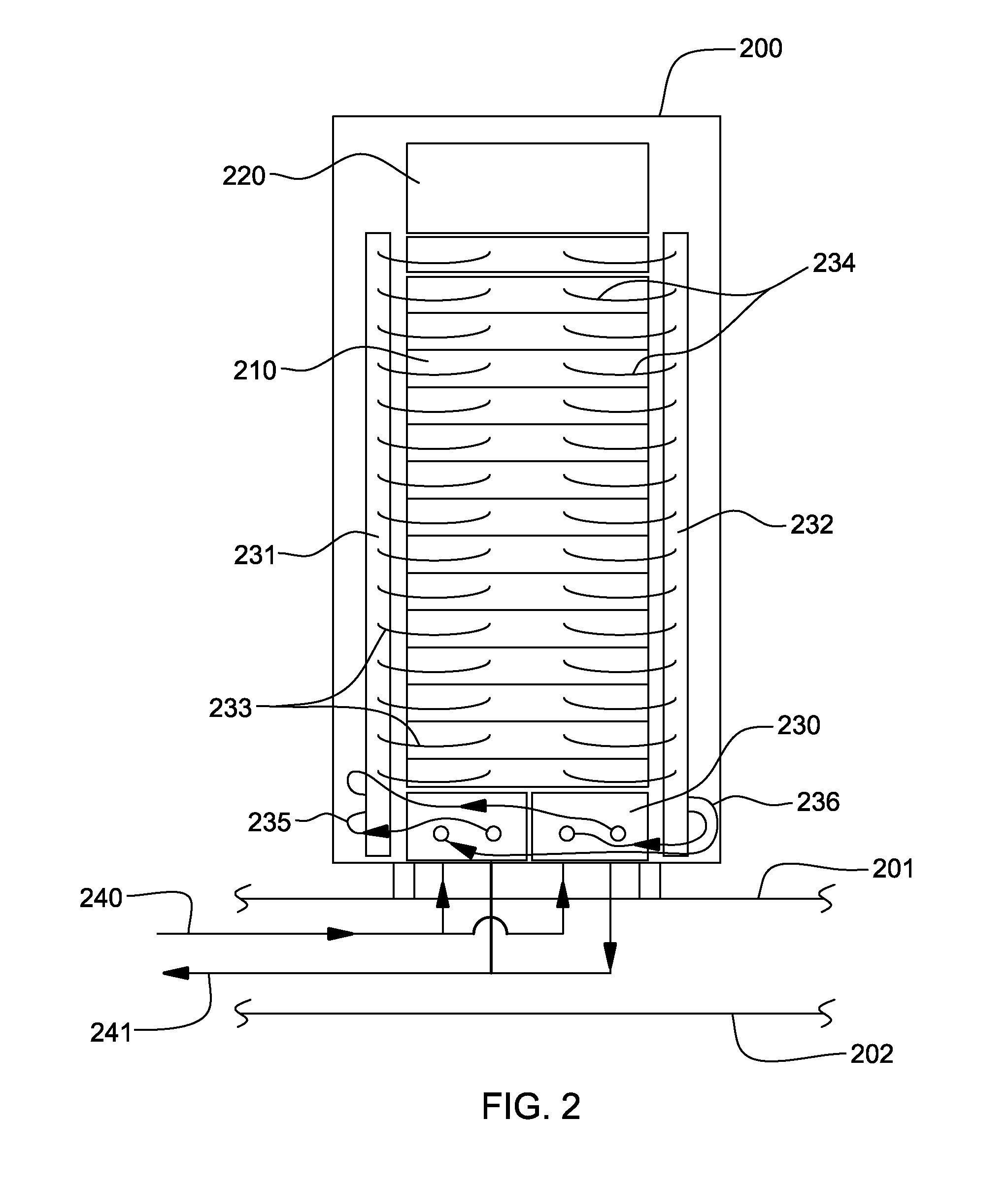

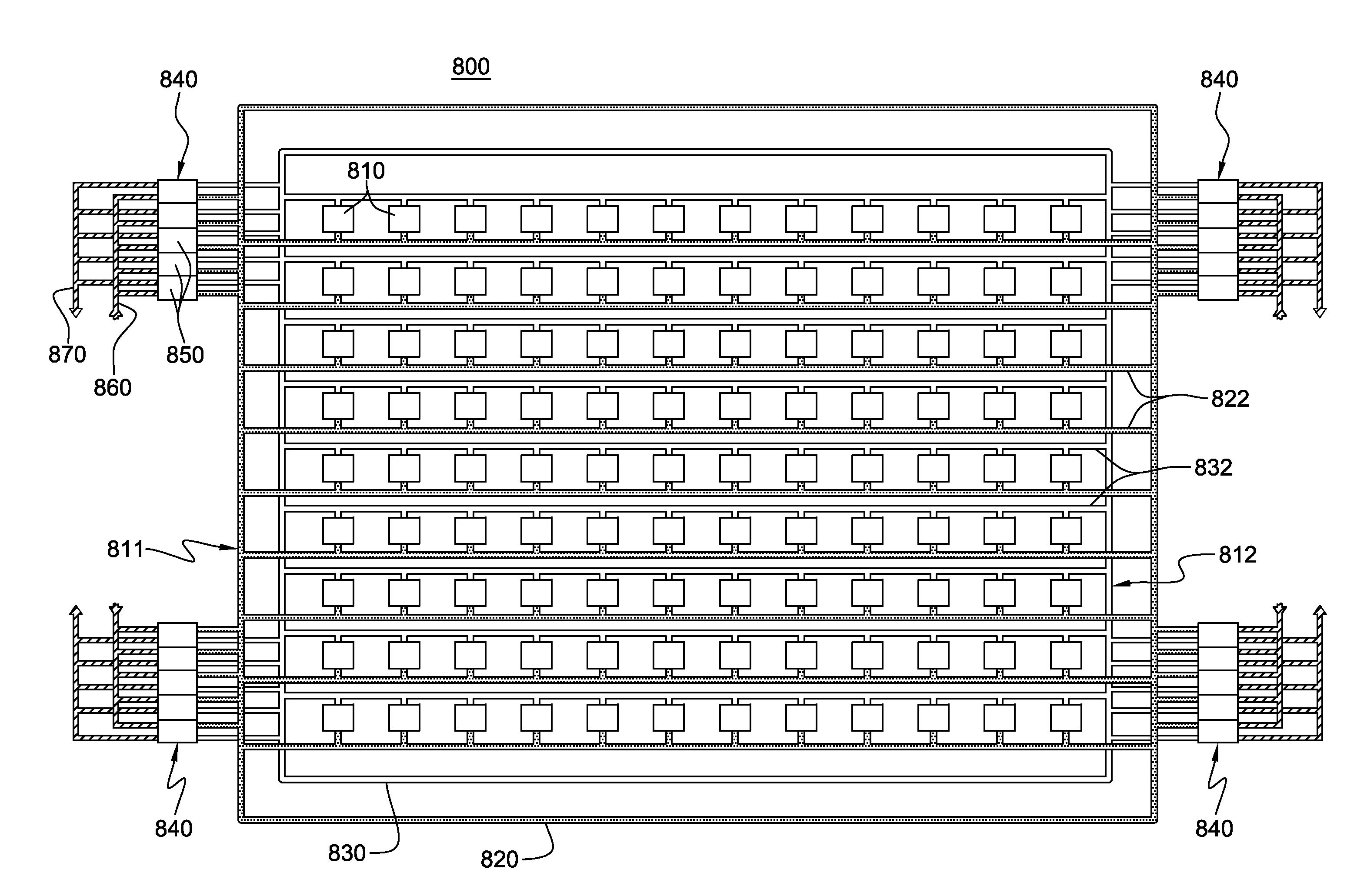

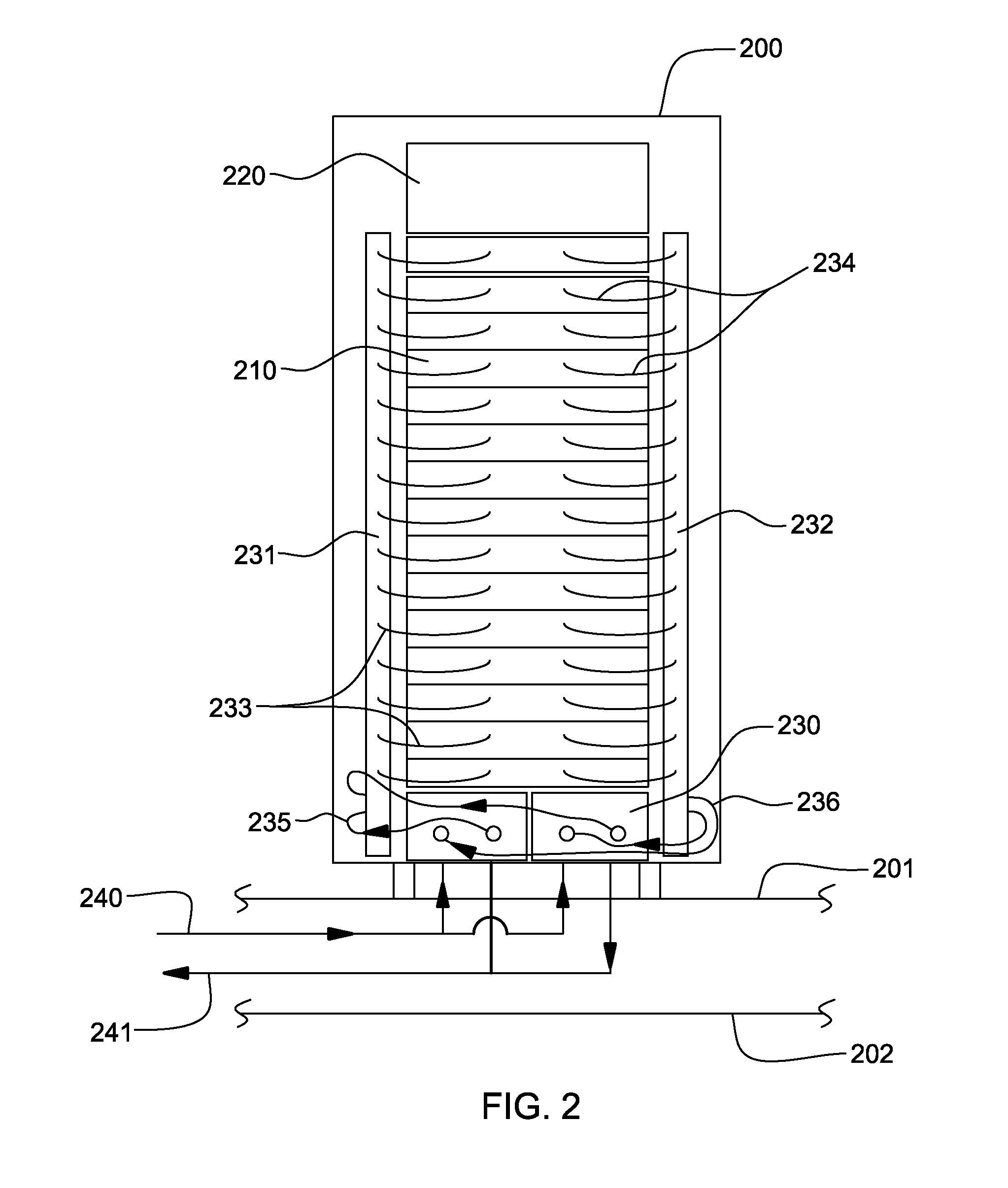

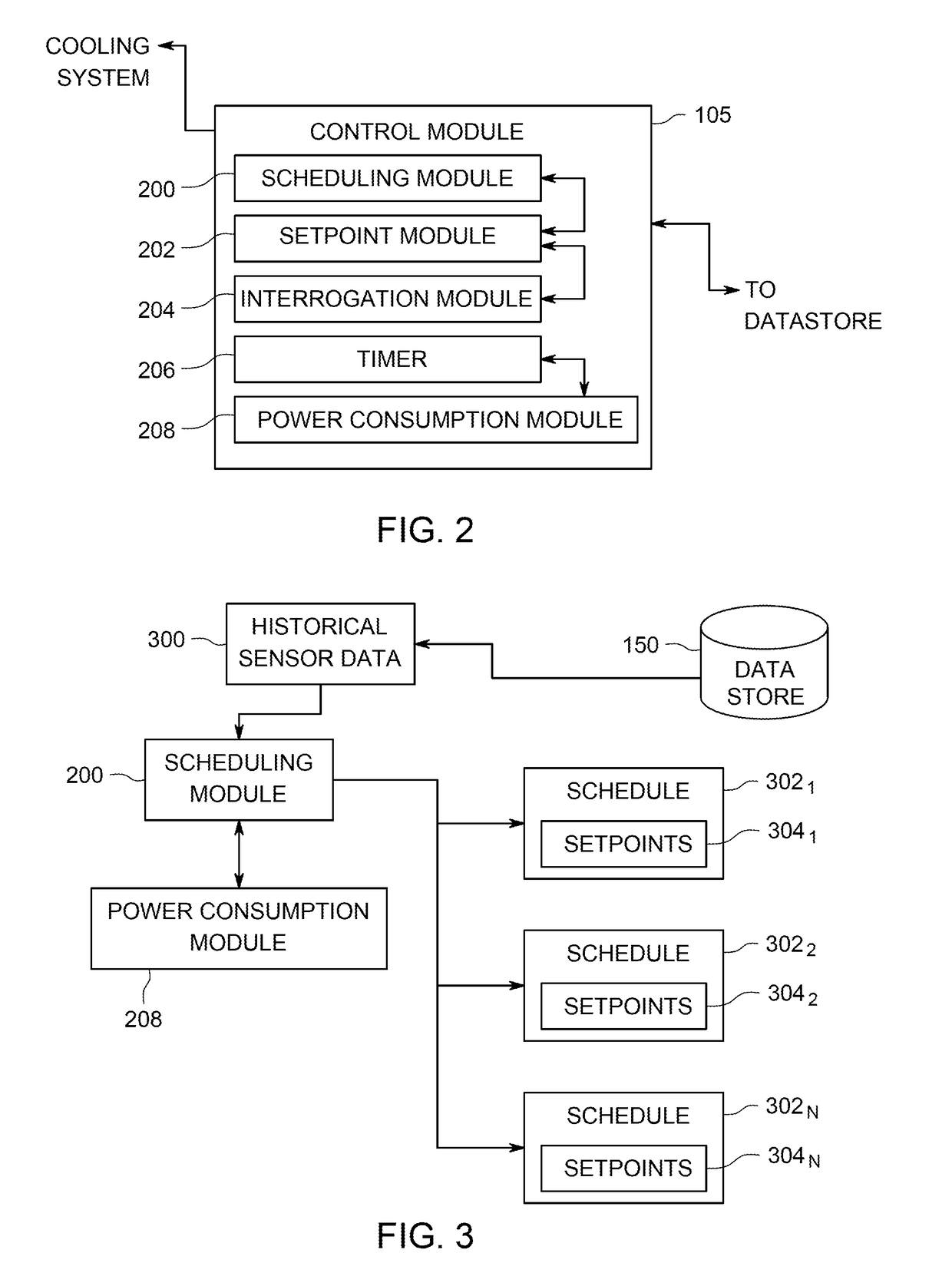

Cooling system and method minimizing power consumption in cooling liquid-cooled electronics racks

InactiveUS20110060470A1Reduce power consumptionOvercomes shortcomingMechanical power/torque controlEnergy efficient ICTControl flowPower dissipation minimization

A cooling system and method are provided for facilitating cooling of a liquid-cooled electronics rack. The cooling system includes a coolant flow controller, a modular cooling unit and a pressure controller. The flow controller is associated with a respective electronics rack and controls flow of coolant through that electronics rack based on its changing cooling requirements. The cooling unit includes an adjustable coolant pump for facilitating supply of coolant to the rack. The pressure controller is associated with the cooling unit for controlling pressure of coolant at an output of the cooling unit via control of pump speed of the pump. Responsive to adjusting coolant flow through the electronics rack, the pressure controller automatically adjusts pump speed of the adjustable pump to maintain pressure about a constant coolant pressure set point at an output of the cooling unit, thereby conserving power while still cooling the liquid-cooled electronics rack.

Owner:IBM CORP

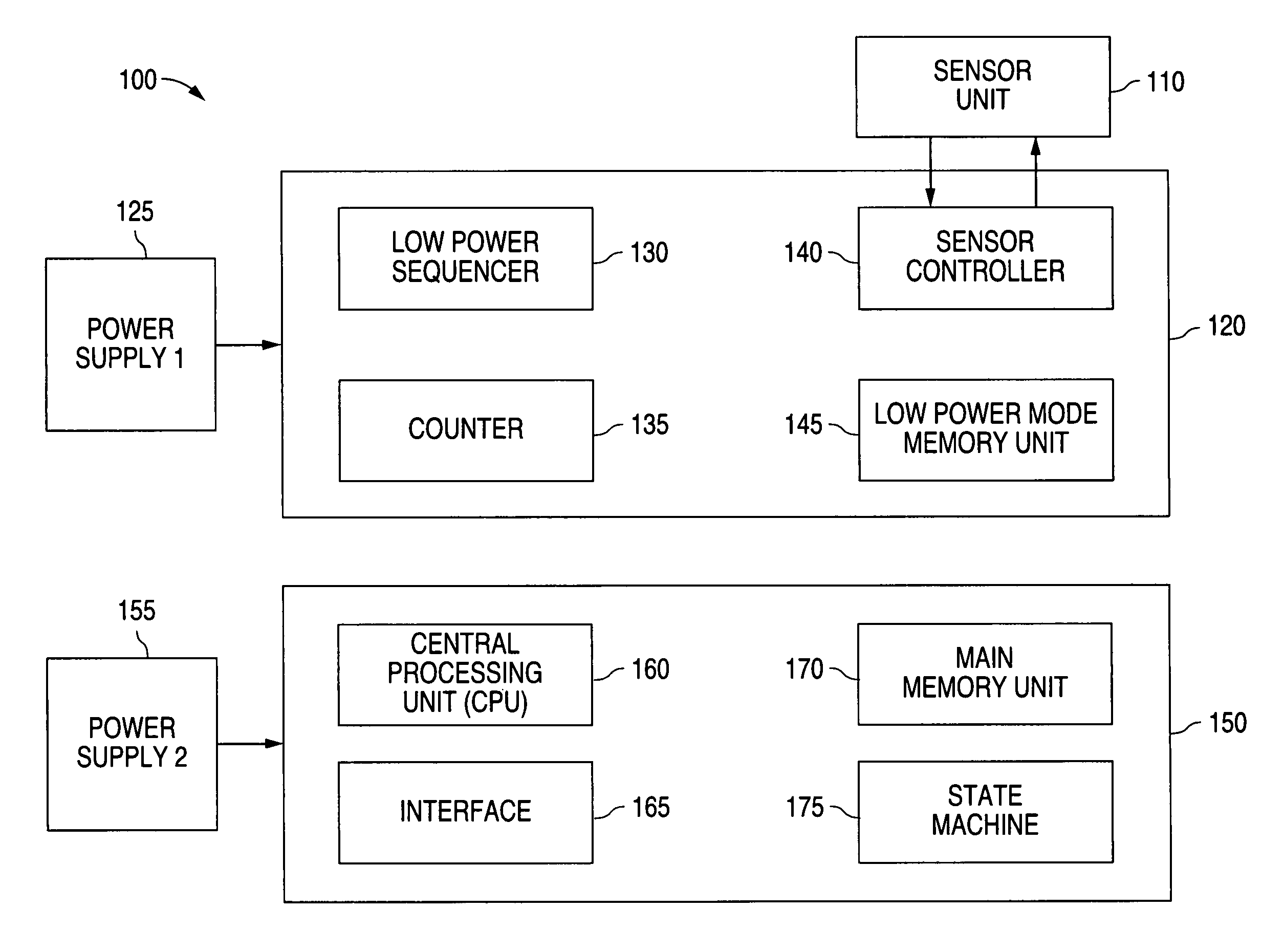

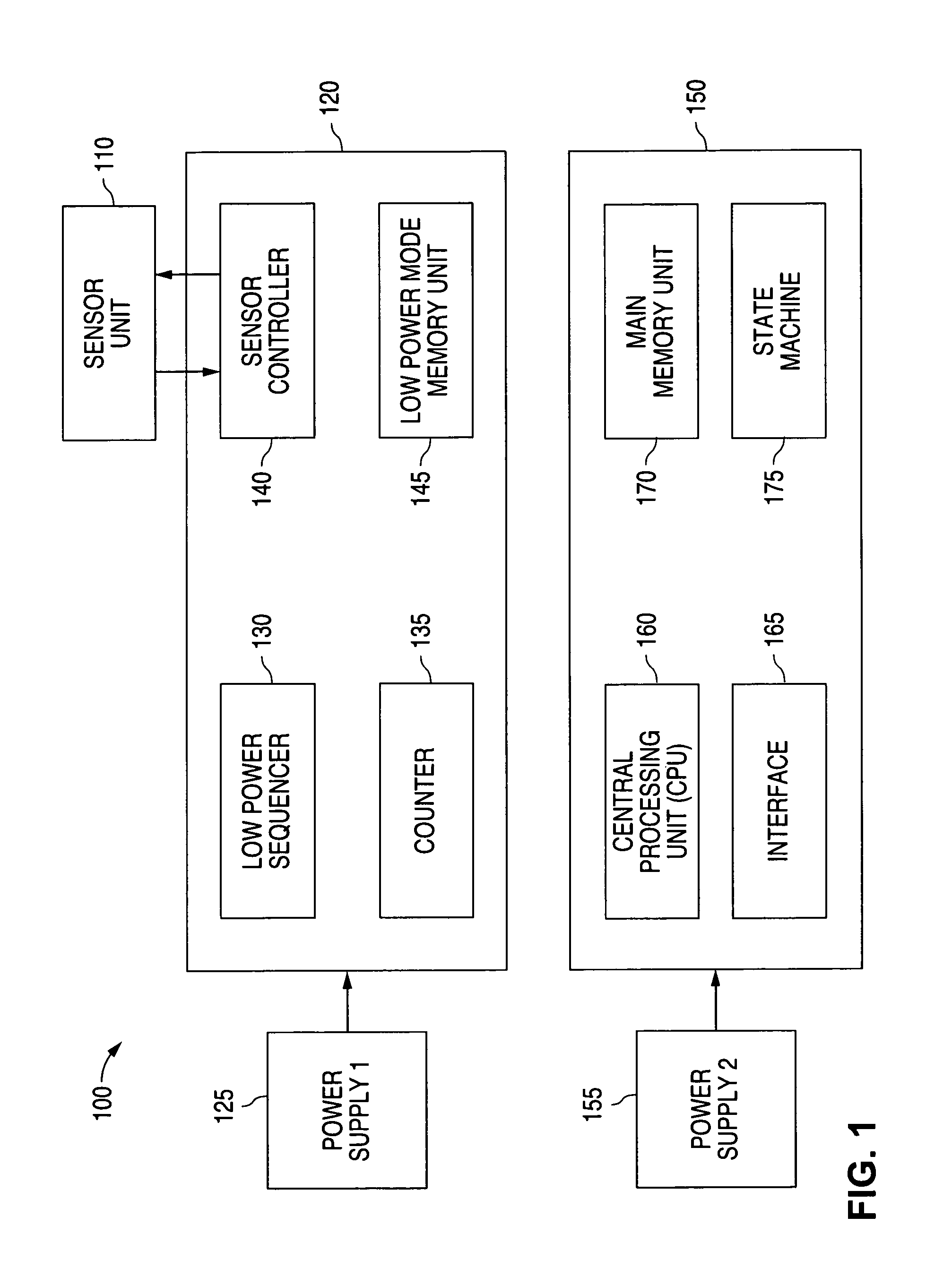

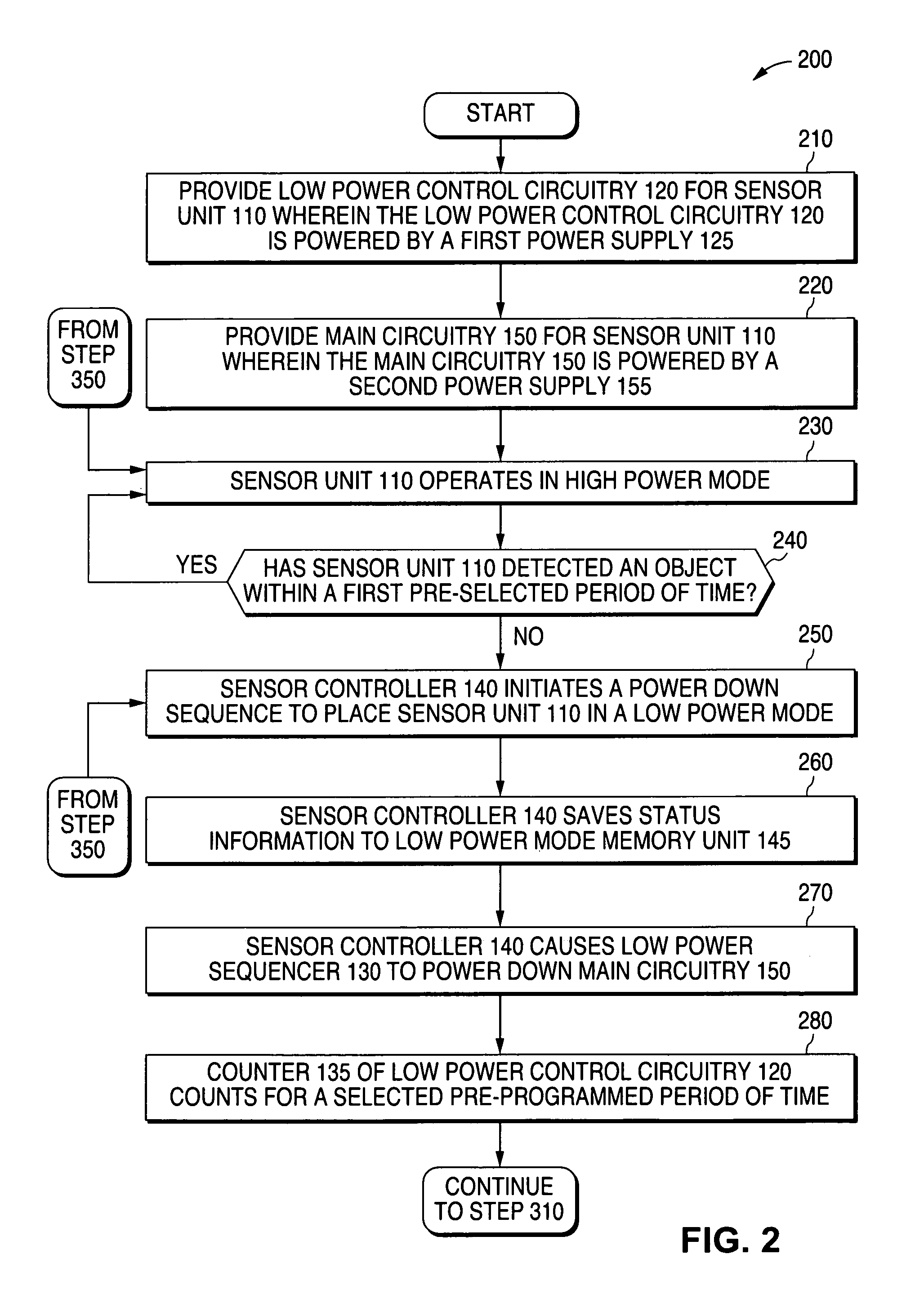

System and method for minimizing power consumption for an object sensor

A system and method is disclosed for minimizing power consumption of a sensor unit that is capable of detecting an object. Main circuitry operates the sensor unit in a high power mode of operation when the sensor unit detects an object. Low power control circuitry operates the sensor unit in a low power mode of operation when the sensor unit does not detect an object within a pre-determined period of time. The low power control circuitry also comprises a counter to periodically determine when to restore the sensor unit to a high power mode of operation. One advantageous embodiment of the sensor unit is a fingerprint sensor unit for detecting a finger to obtain fingerprint information.

Owner:SYNAPTICS INC +1

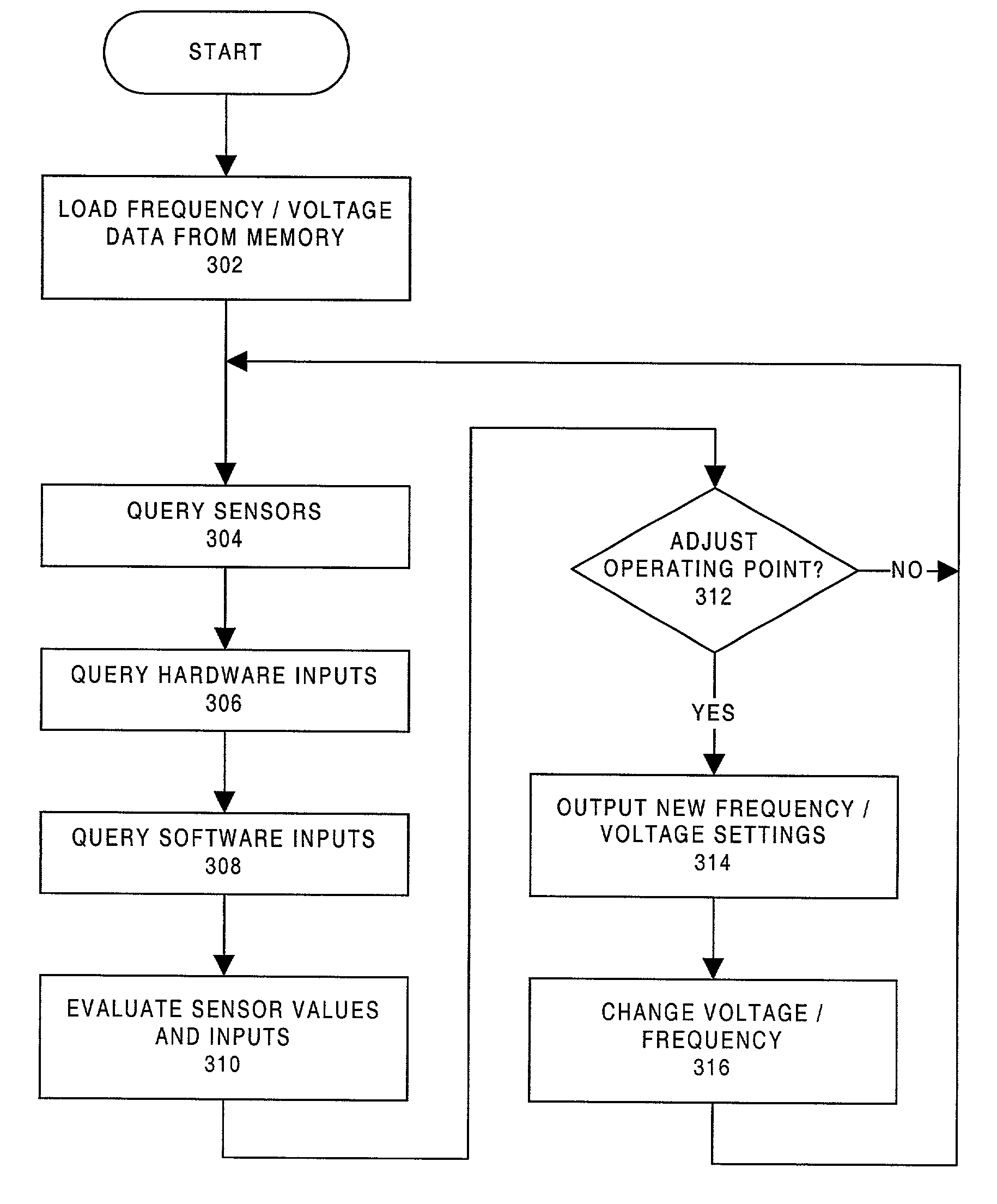

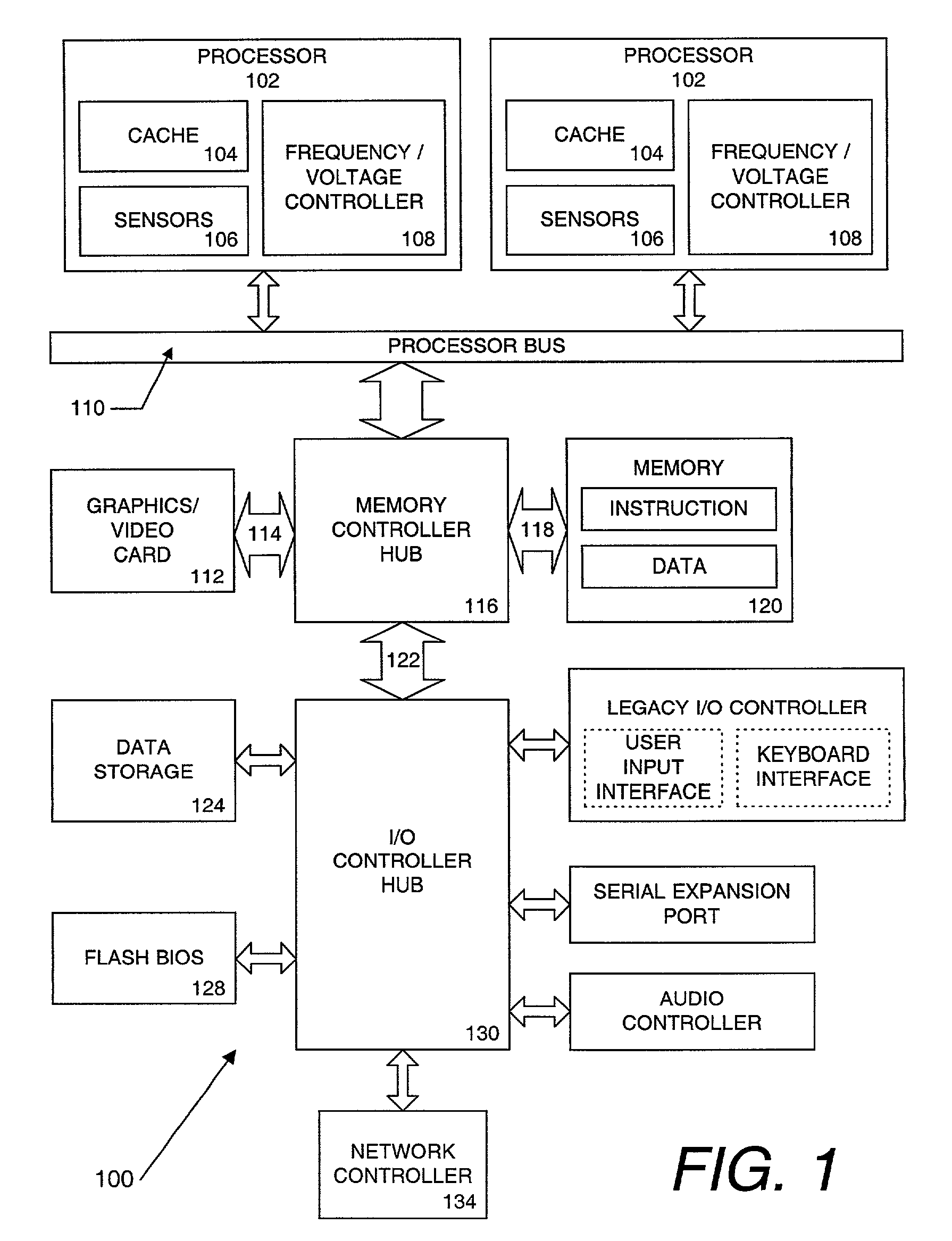

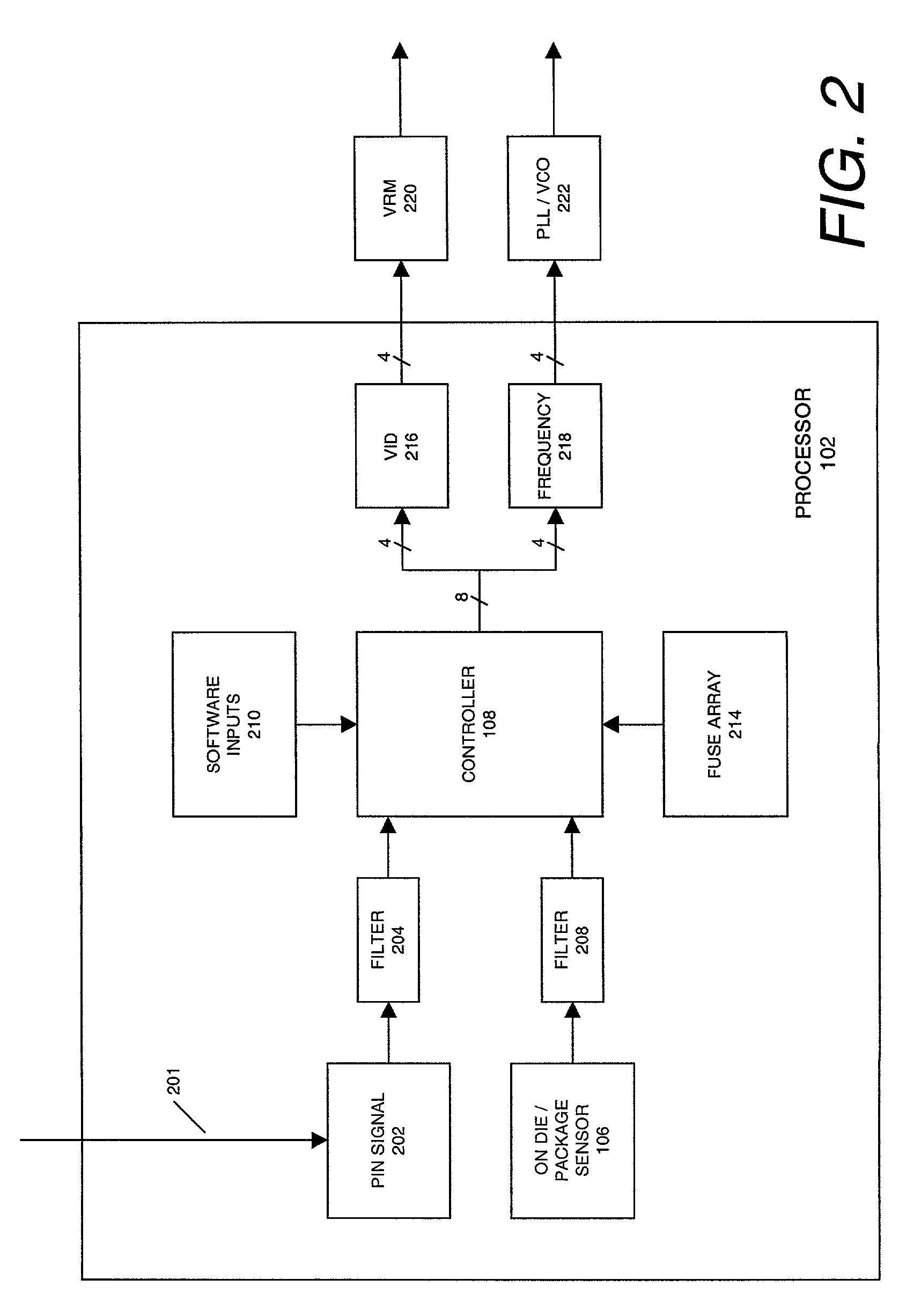

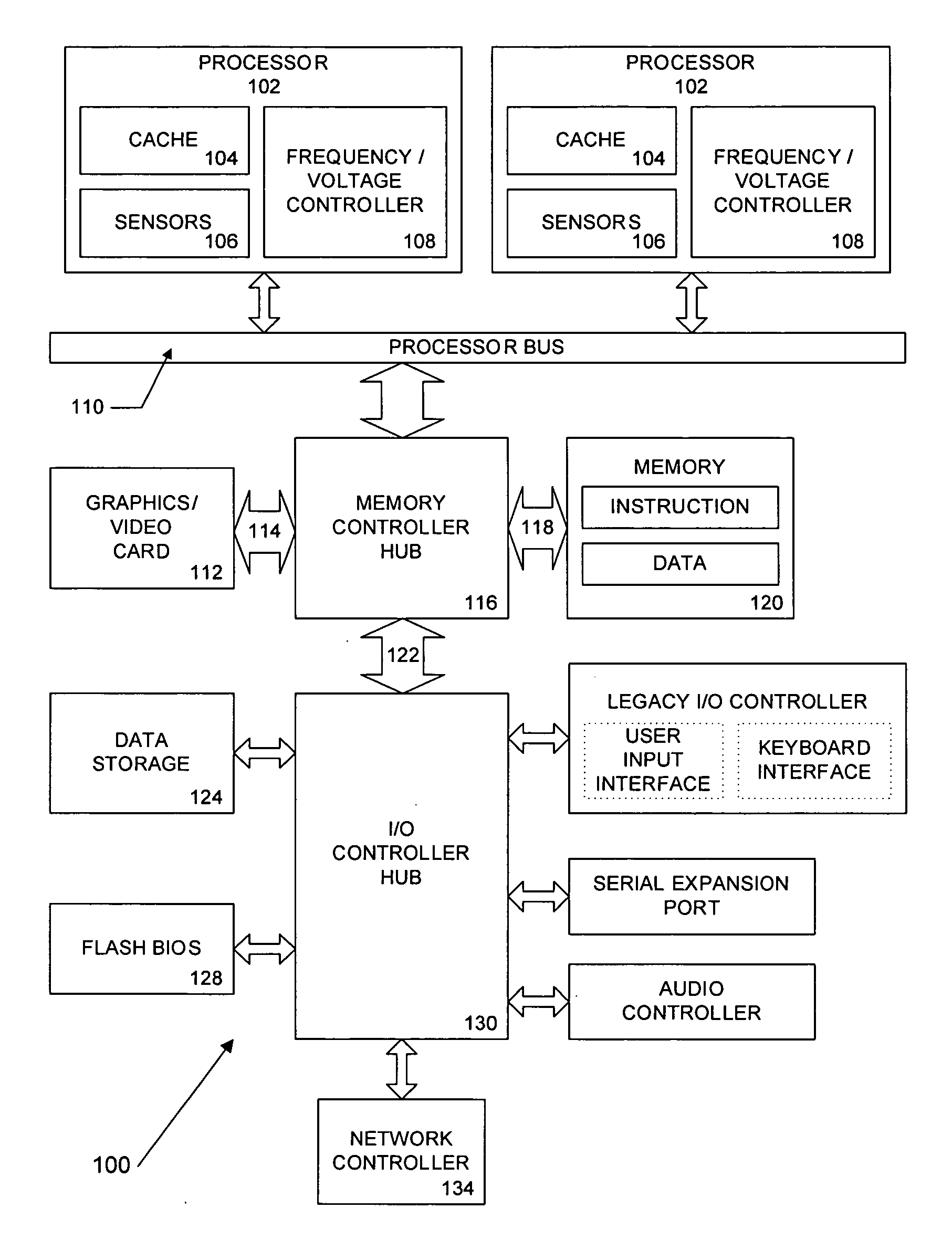

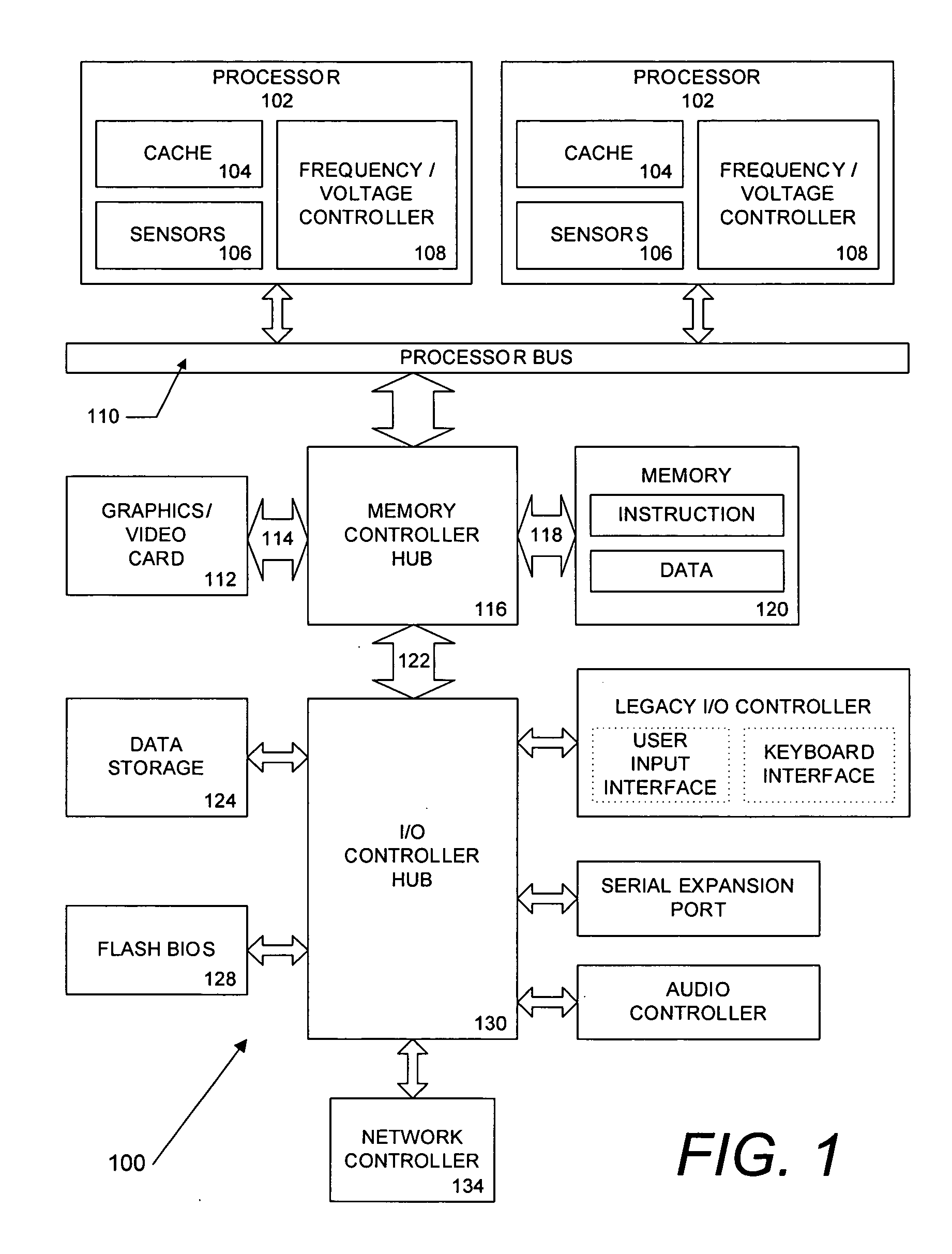

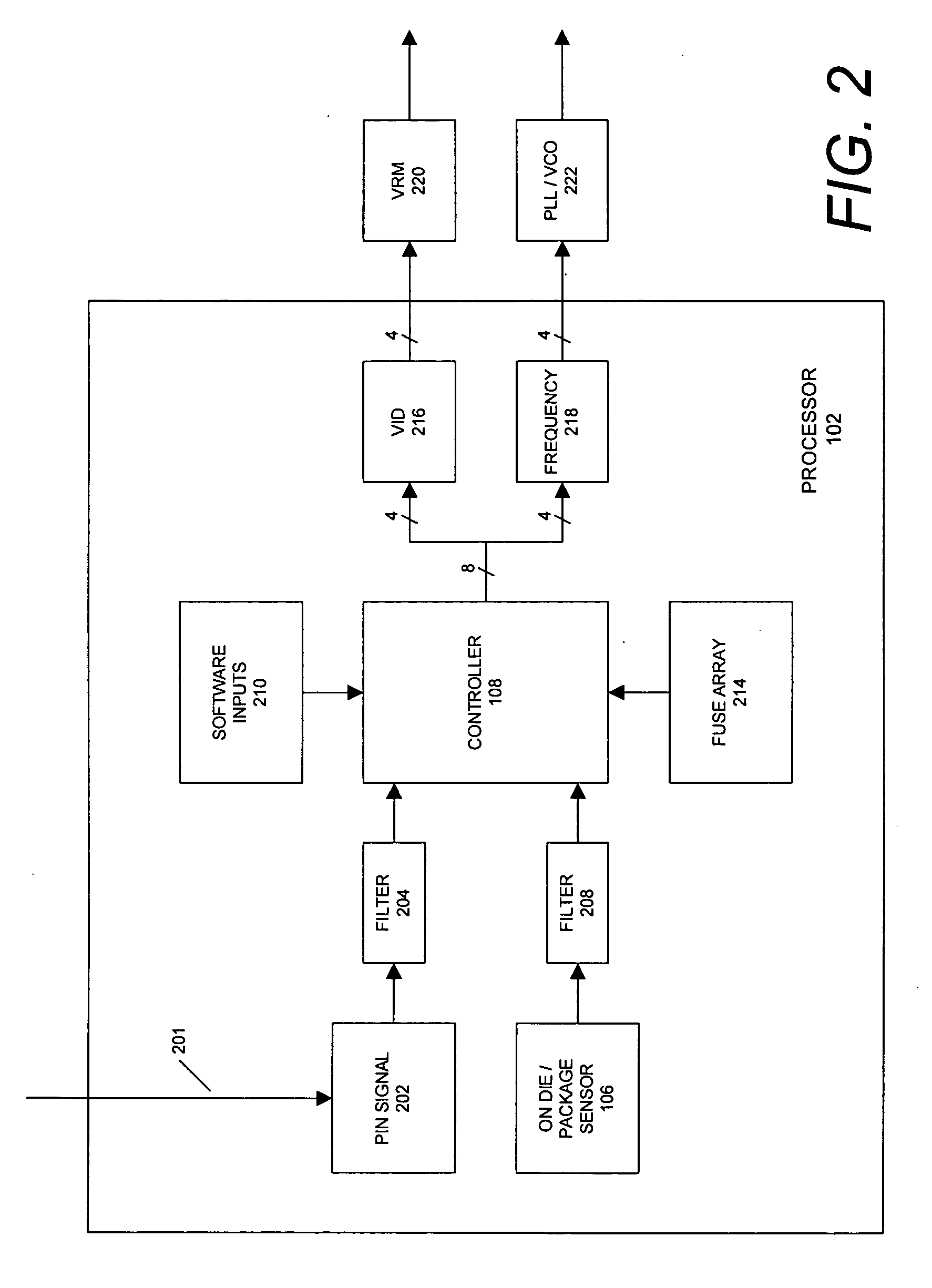

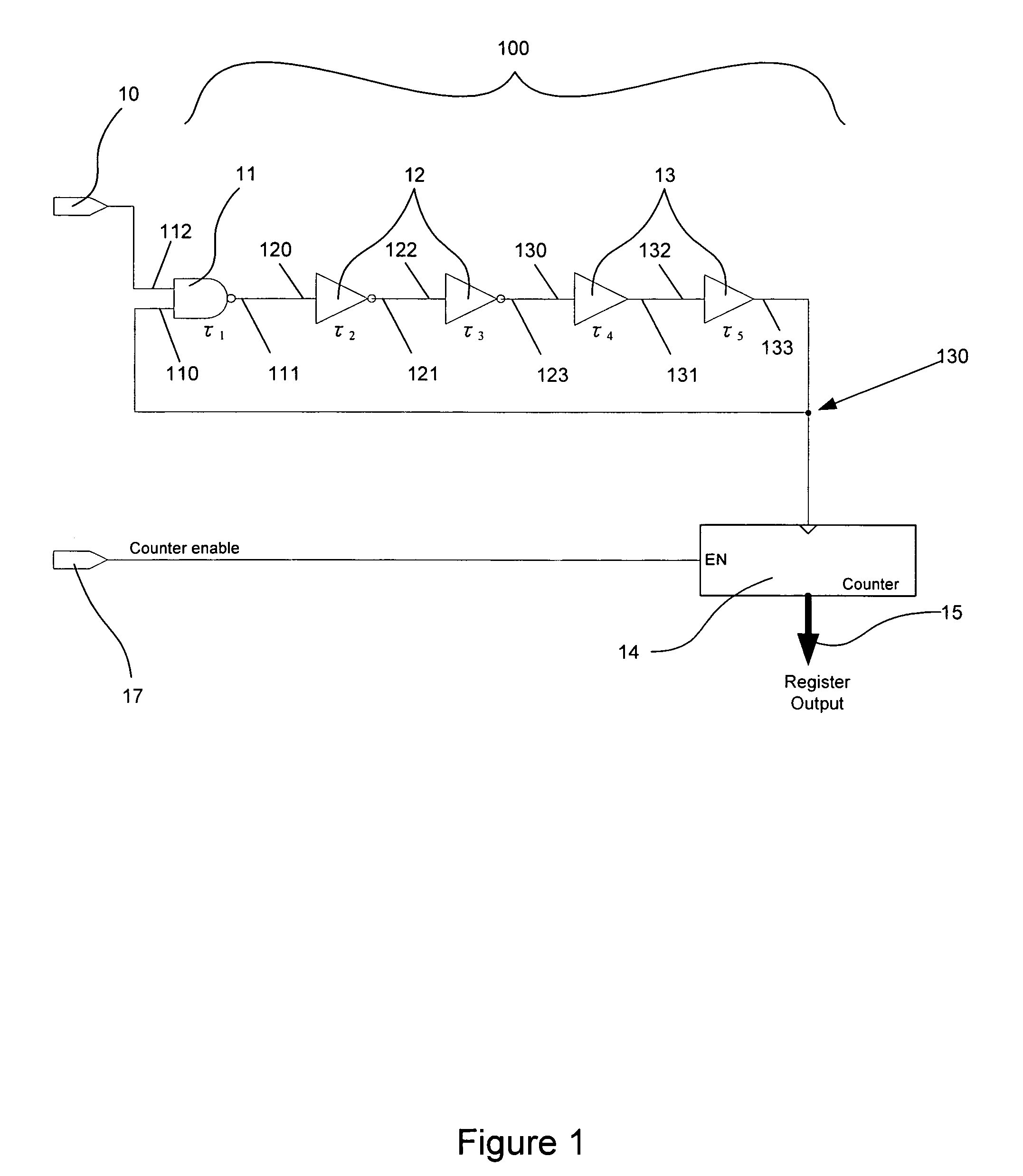

Method and apparatus for adjusting the voltage and frequency to minimize power dissipation in a multiprocessor system

InactiveUS7111178B2Minimize power consumptionIncreasing processor densityTransmitters monitoringEnergy efficient ICTOperating pointMulti processor

A method for adjusting the voltage and frequency to minimize power dissipation in a processor. The method of one embodiment comprises determining a power consumption value. The power consumption value is evaluated to obtain a new operating point. The new operating point is compared with a present operating point. A frequency setting and a voltage setting are adjusted to correspond to the new operating point if the new operating point is different from the present operating point.

Owner:SONY CORP OF AMERICA

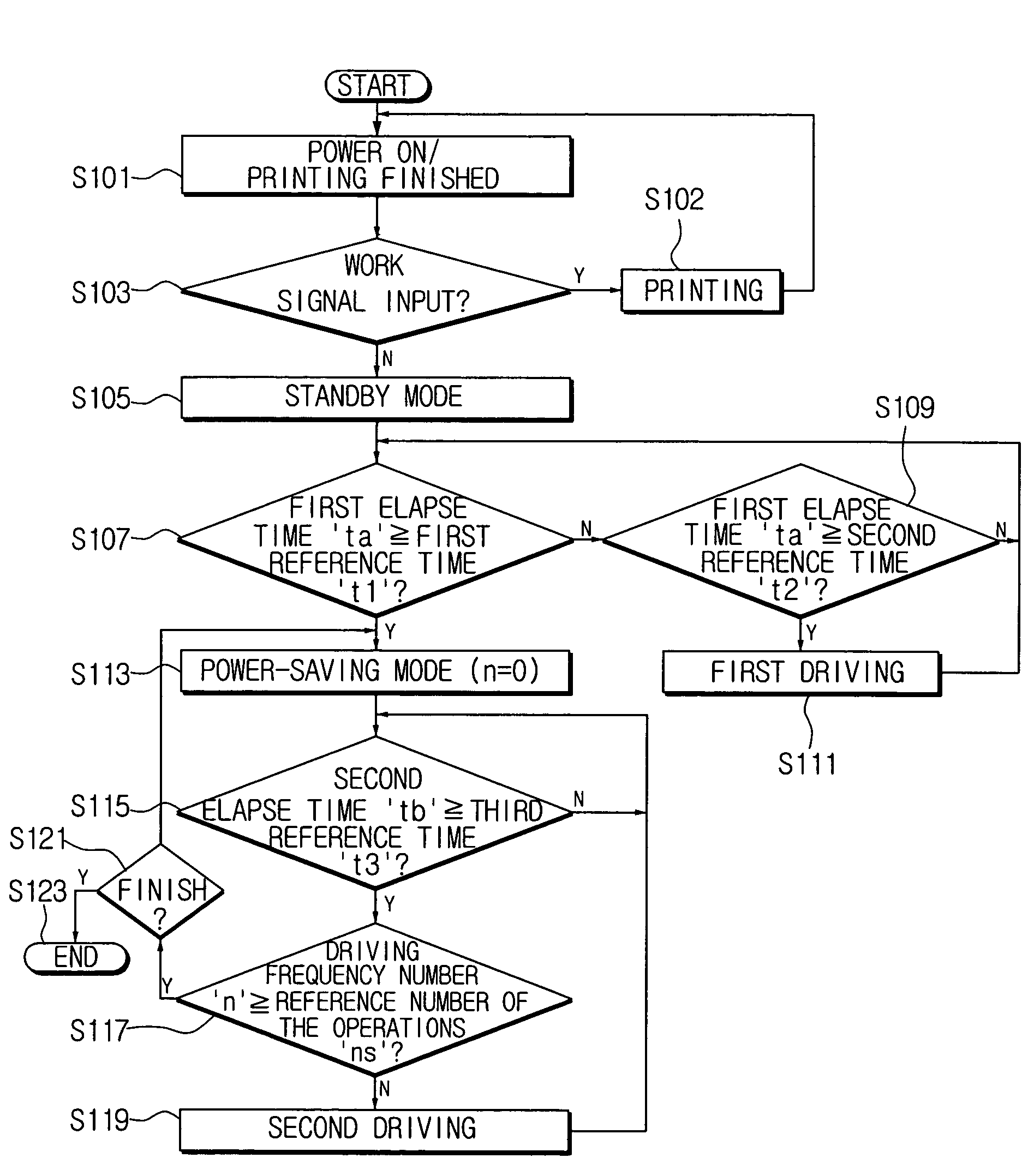

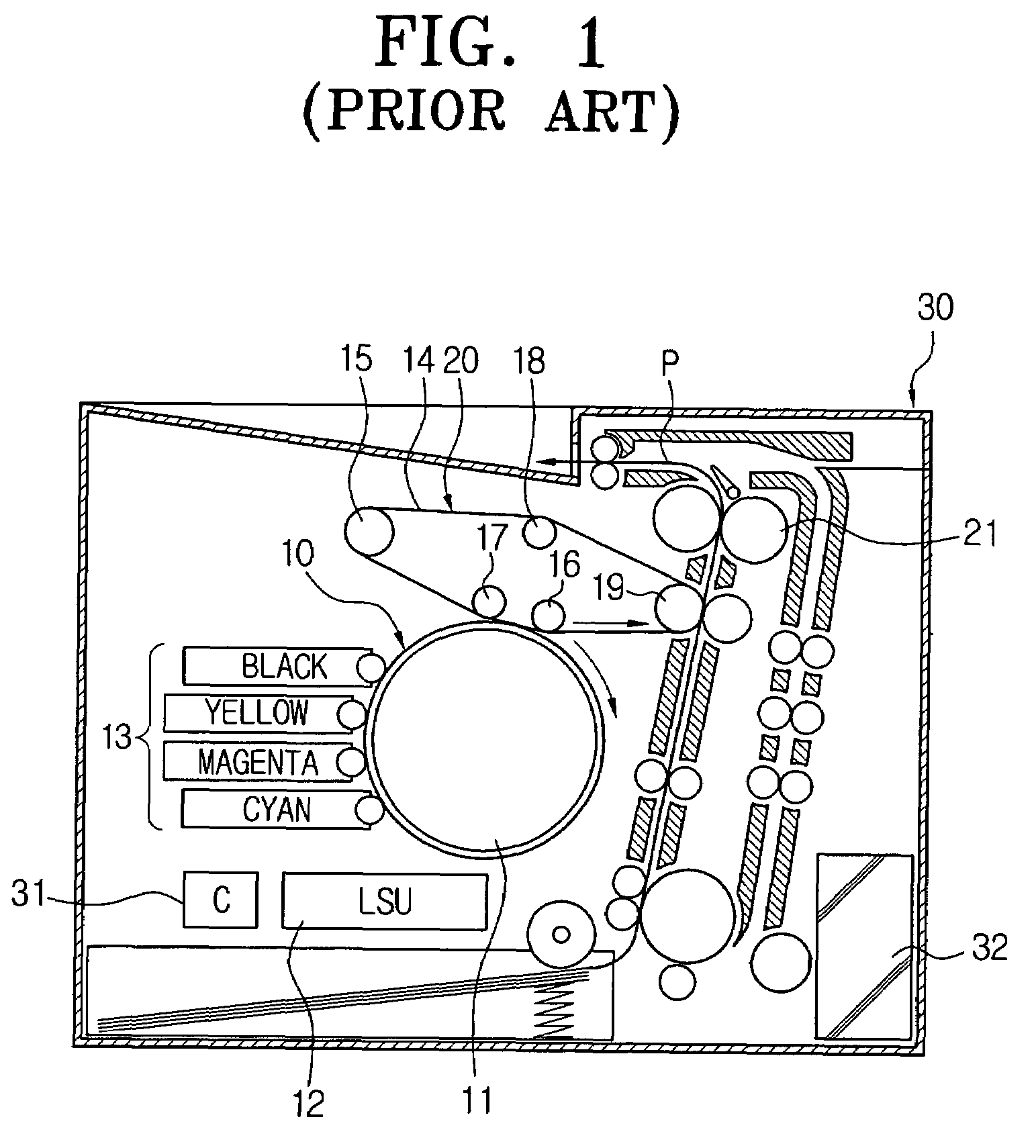

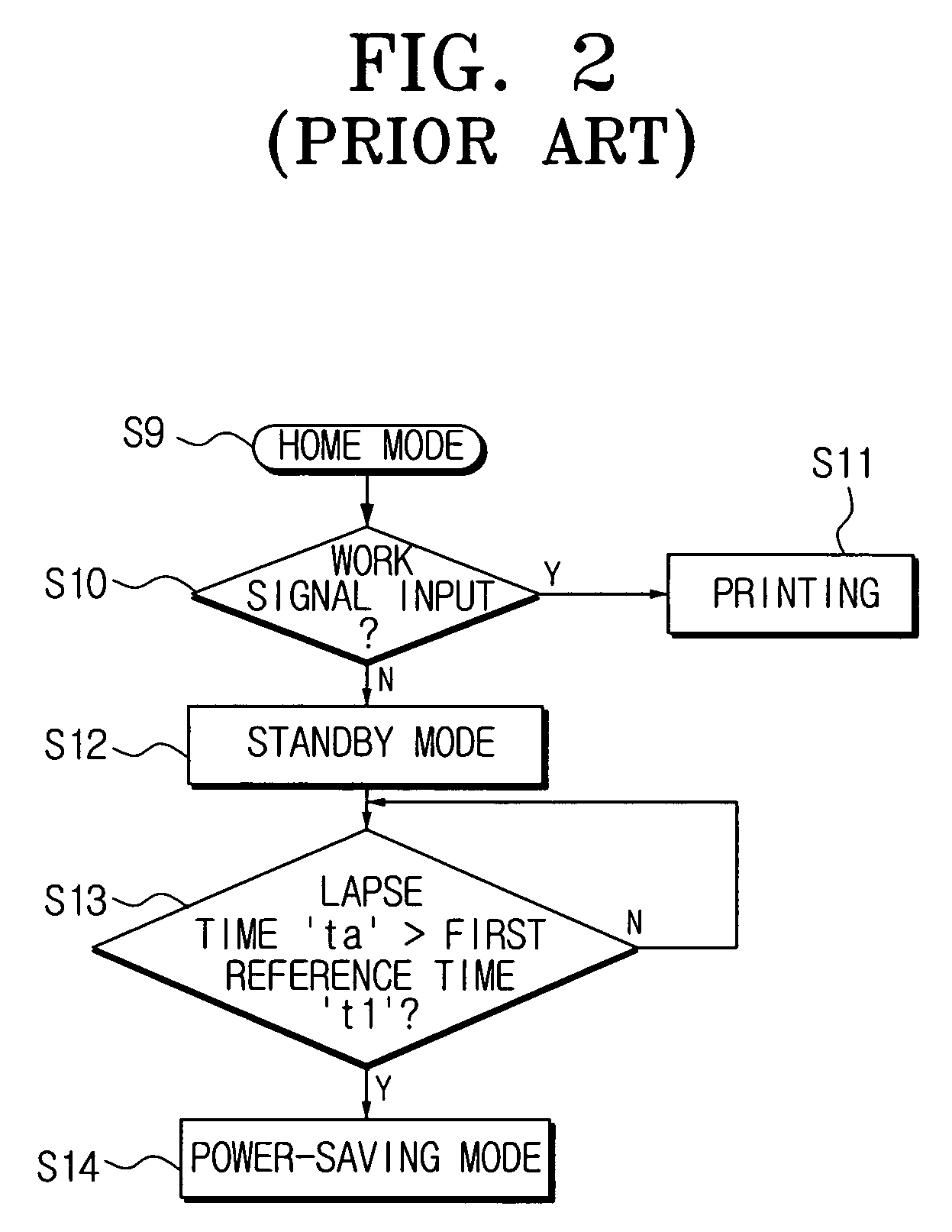

Apparatus and method of driving a transfer belt

Owner:HEWLETT PACKARD DEV CO LP

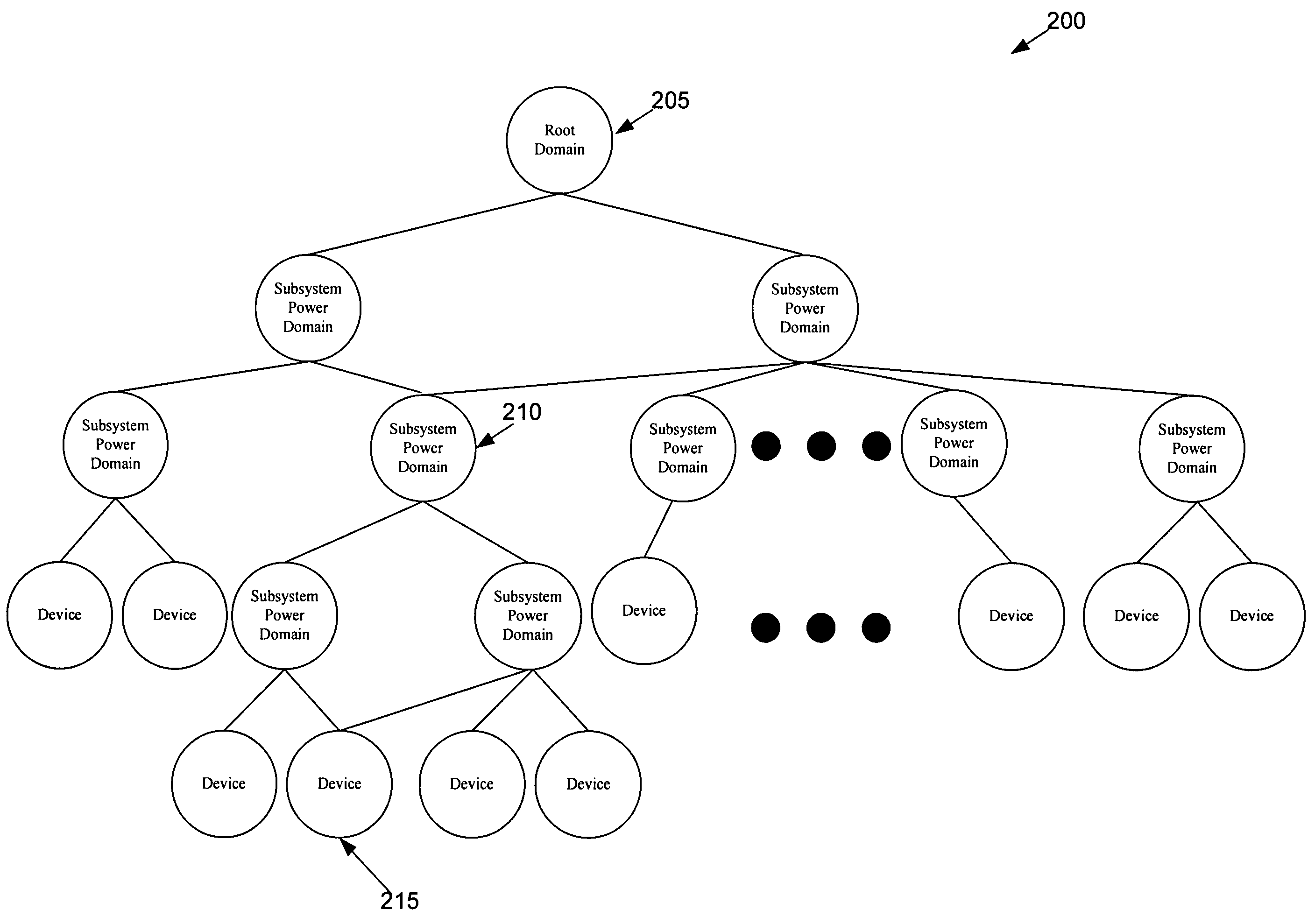

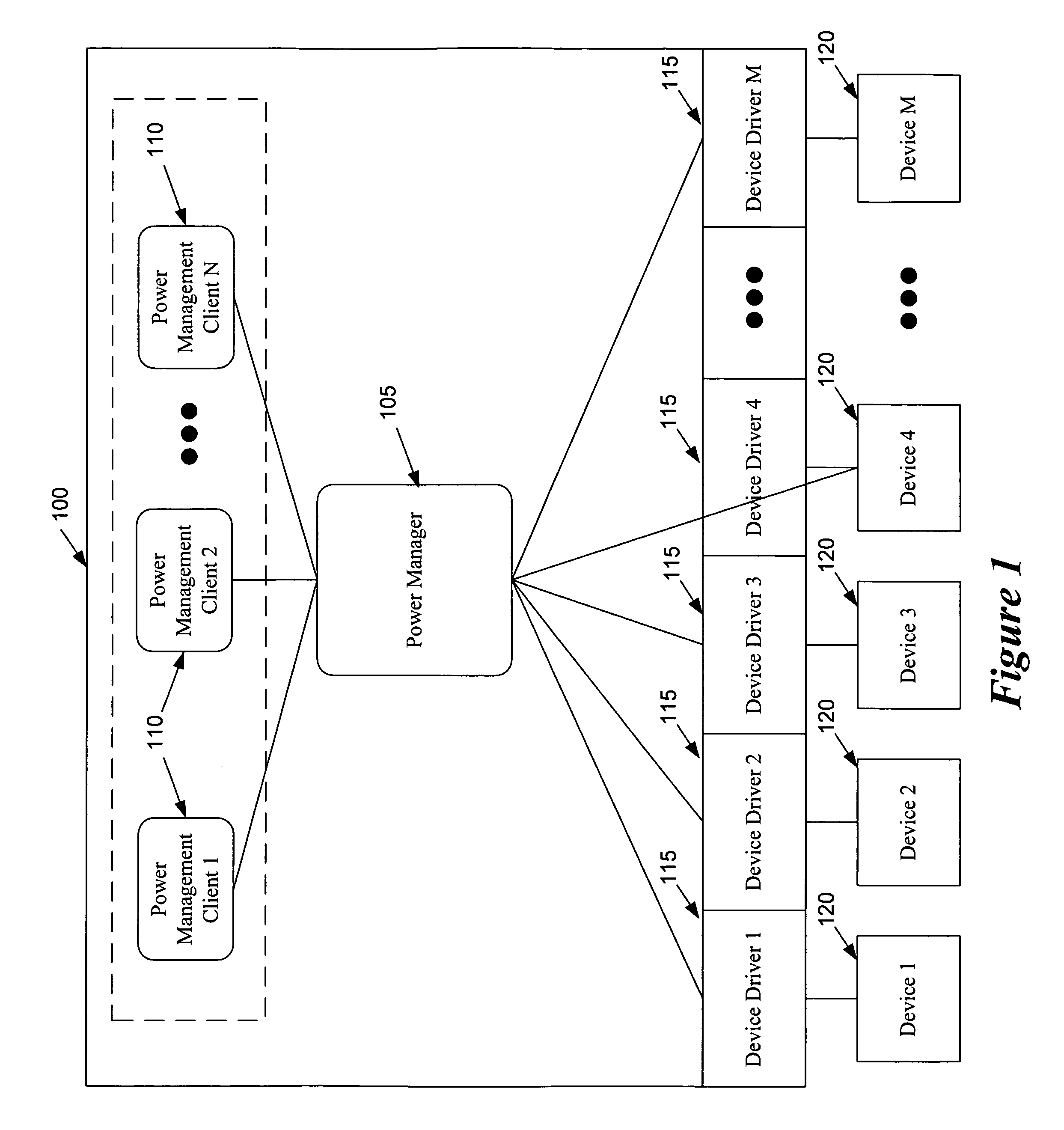

Method and apparatus for managing power in computer systems

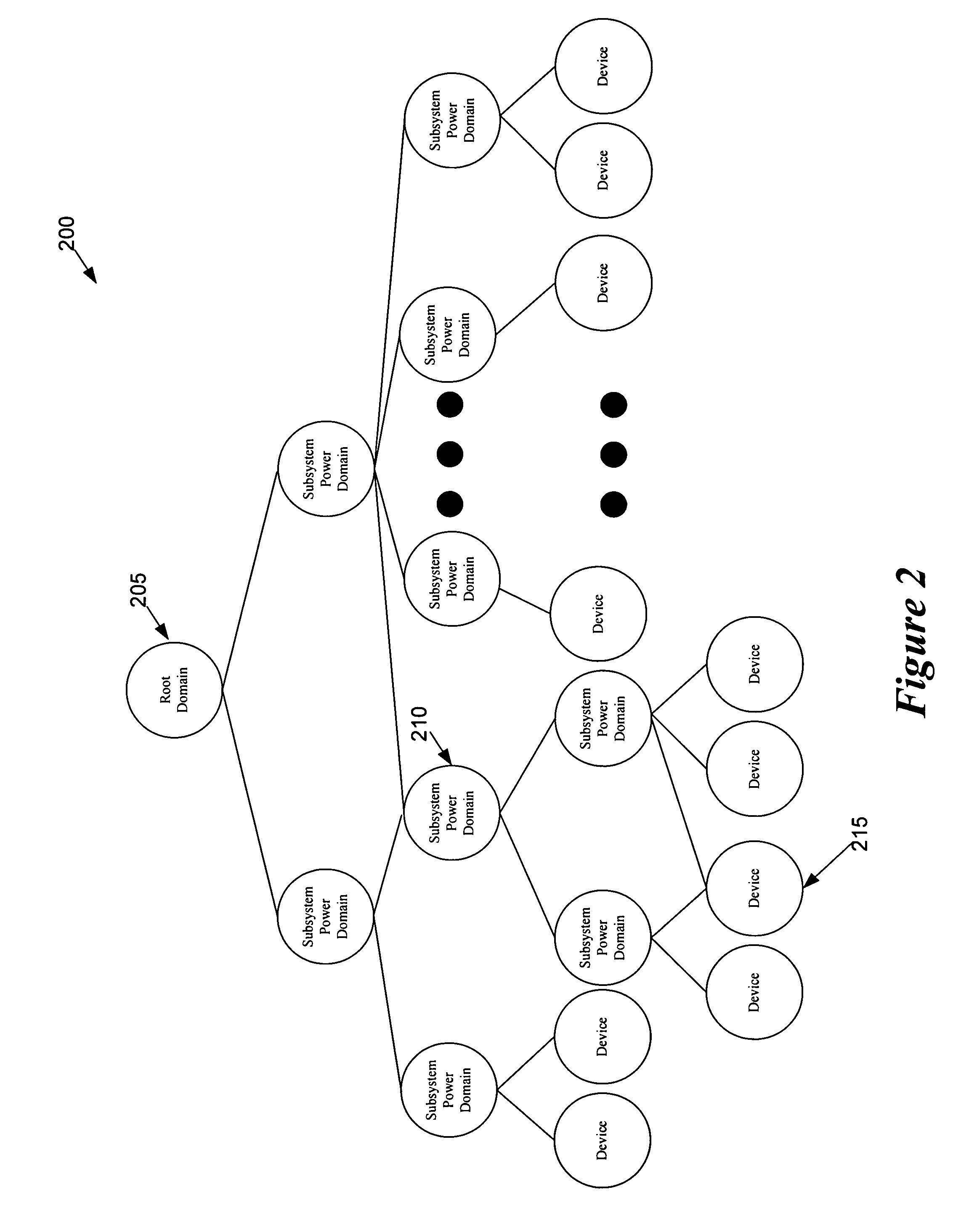

InactiveUS7519838B1Energy efficient ICTVolume/mass flow measurementSoftware engineeringPower domains

The invention is directed towards minimizing power consumption in computer systems. One embodiment of the invention is a power management system that is used for a computer system that has at least one device and one power domain. This embodiment uses two different power managers to manage the power consumption of the device and the power domain. Specifically, this embodiment has (1) a first power manager that determines when to change power state of the device, and (2) a second power manager that determines when to change power state of the power domain. Each of these power managers decides to change the power state of its corresponding device or domain based on information from several different sources. These sources can include power-management clients and power managers of related domains or devices.

Owner:APPLE INC

Cooling system and method minimizing power consumption in cooling liquid-cooled electronics racks

InactiveUS8583290B2Reduce power consumptionOvercomes shortcomingEnergy efficient ICTMechanical power/torque controlControl flowCoolant flow

A cooling system and method are provided for facilitating cooling of a liquid-cooled electronics rack. The cooling system includes a coolant flow controller, a modular cooling unit and a pressure controller. The flow controller is associated with a respective electronics rack and controls flow of coolant through that electronics rack based on its changing cooling requirements. The cooling unit includes an adjustable coolant pump for facilitating supply of coolant to the rack. The pressure controller is associated with the cooling unit for controlling pressure of coolant at an output of the cooling unit via control of pump speed of the pump. Responsive to adjusting coolant flow through the electronics rack, the pressure controller automatically adjusts pump speed of the adjustable pump to maintain pressure about a constant coolant pressure set point at an output of the cooling unit, thereby conserving power while still cooling the liquid-cooled electronics rack.

Owner:IBM CORP

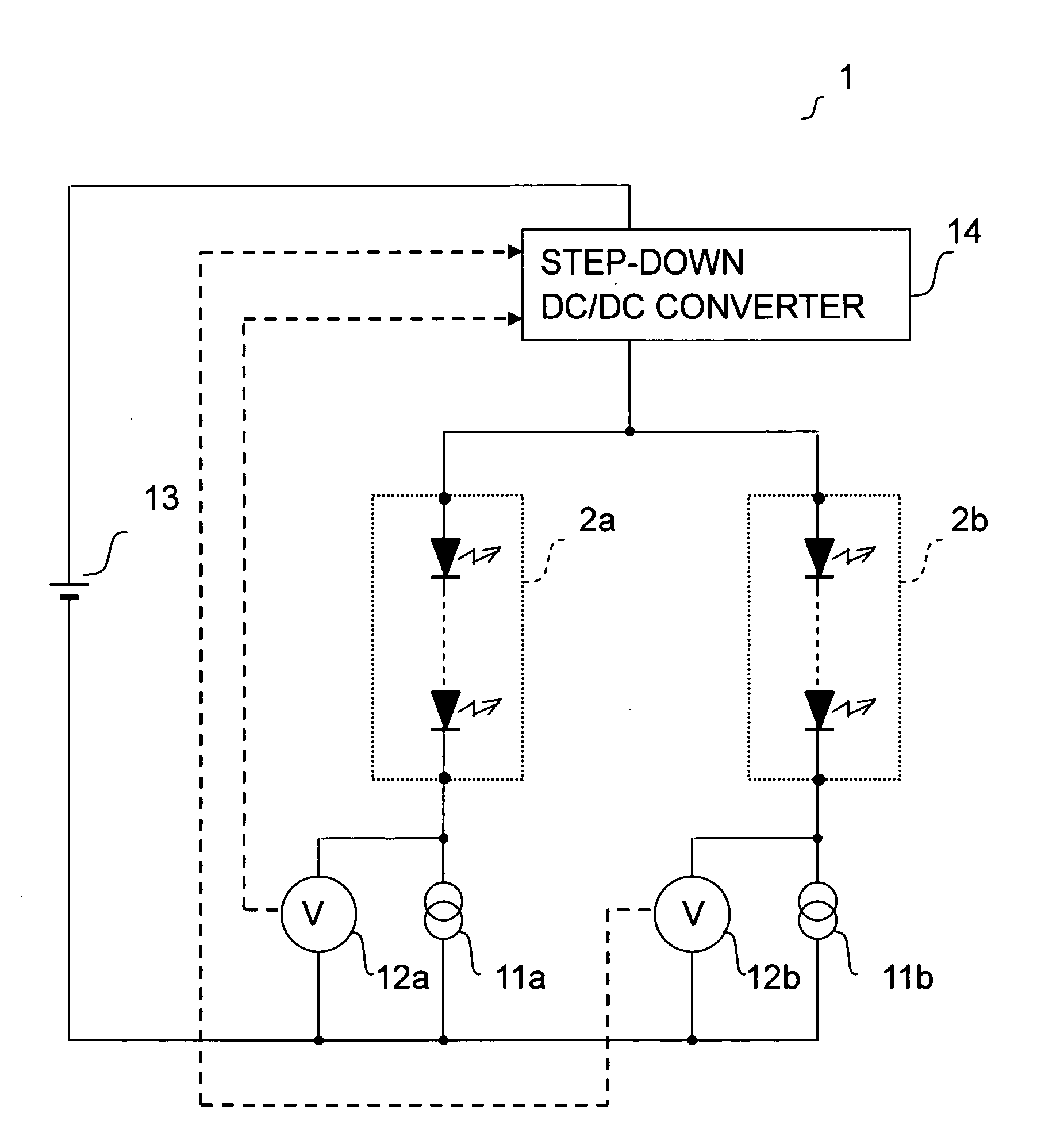

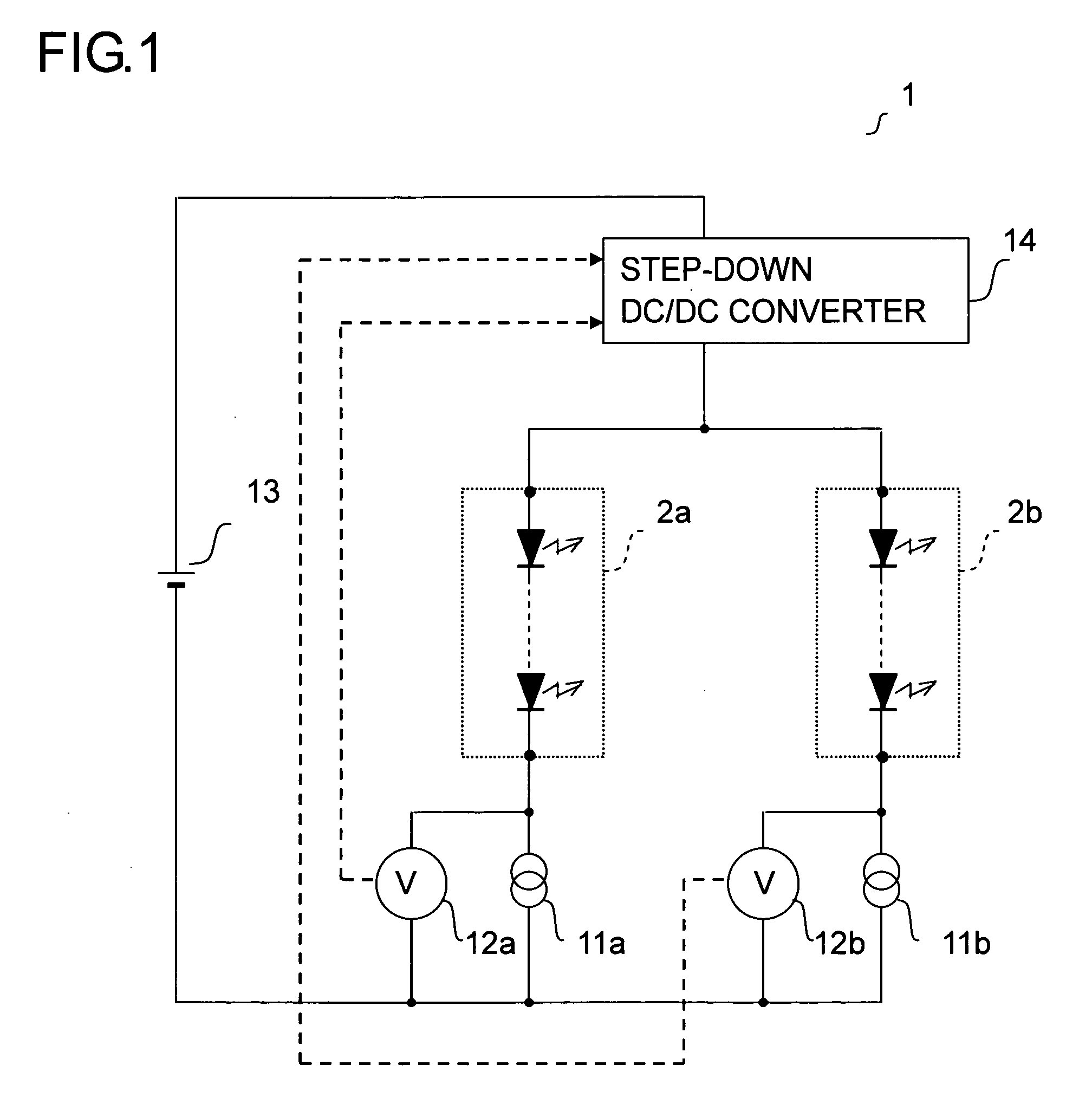

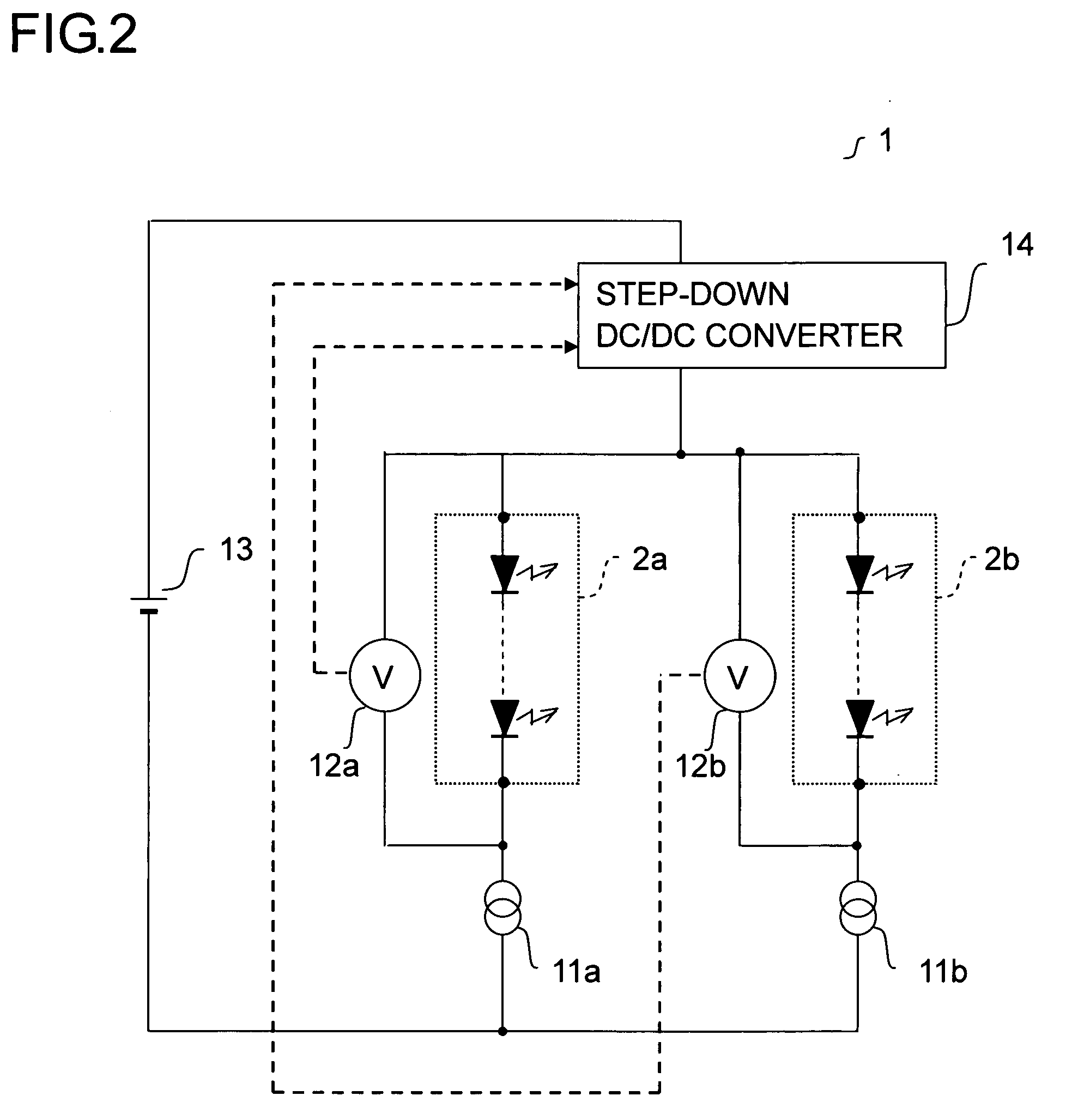

Led driver

InactiveUS20080122383A1Reduce unnecessary power consumptionStatic indicating devicesElectroluminescent light sourcesPotential differenceVoltage regulation

An LED driver according to the present invention feeds an electric power to an LED circuit, which is either of a single LED or a plurality of LEDs serially connected together. The LED driver includes: a constant current circuit part serially connected to the LED circuit and adjusting a current flowing from an upstream to a downstream side thereof to a predetermined value; and a voltage adjustment part serially connected to the constant current circuit part and adjusting a potential difference between the upstream and downstream sides with a switching regulator. This therefore permits providing an LED driver capable of, while adopting a constant current driving method using a constant current circuit, easily minimizing unnecessary power consumption and respecting the permitted loss at the constant current circuit.

Owner:SHARP KK

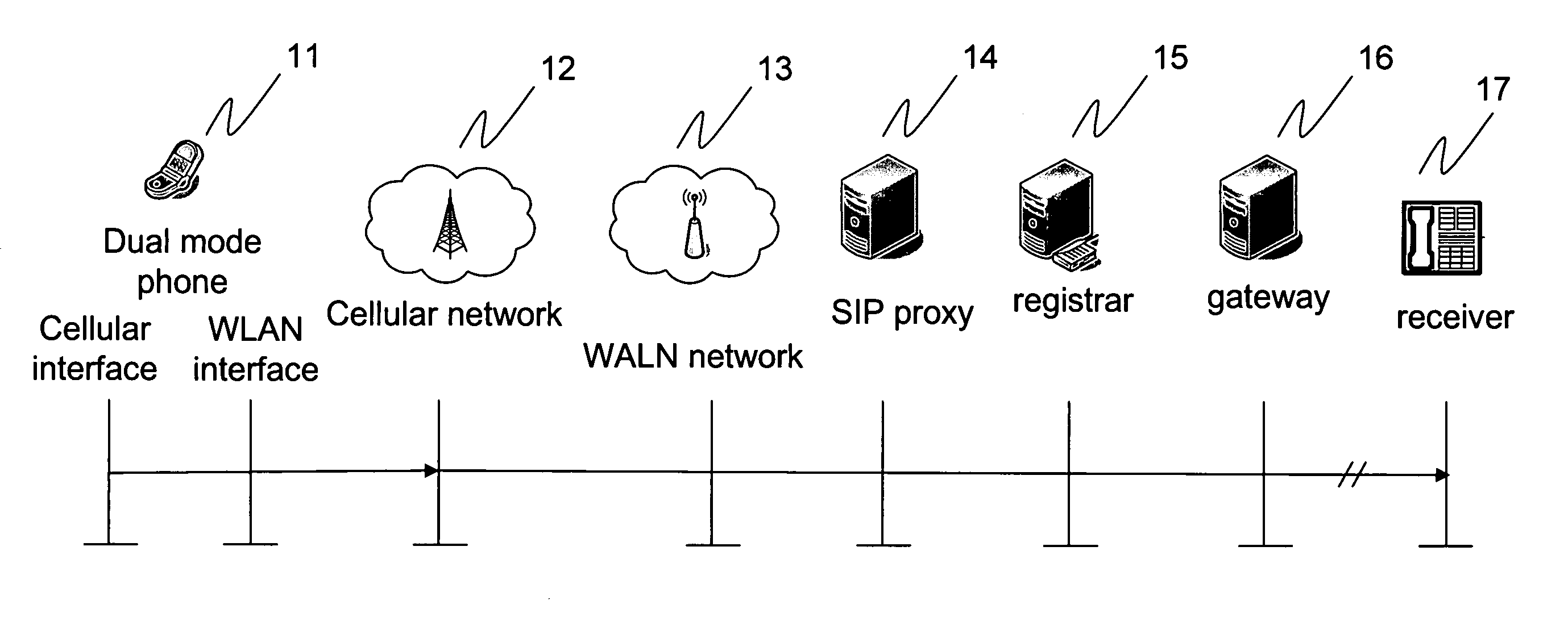

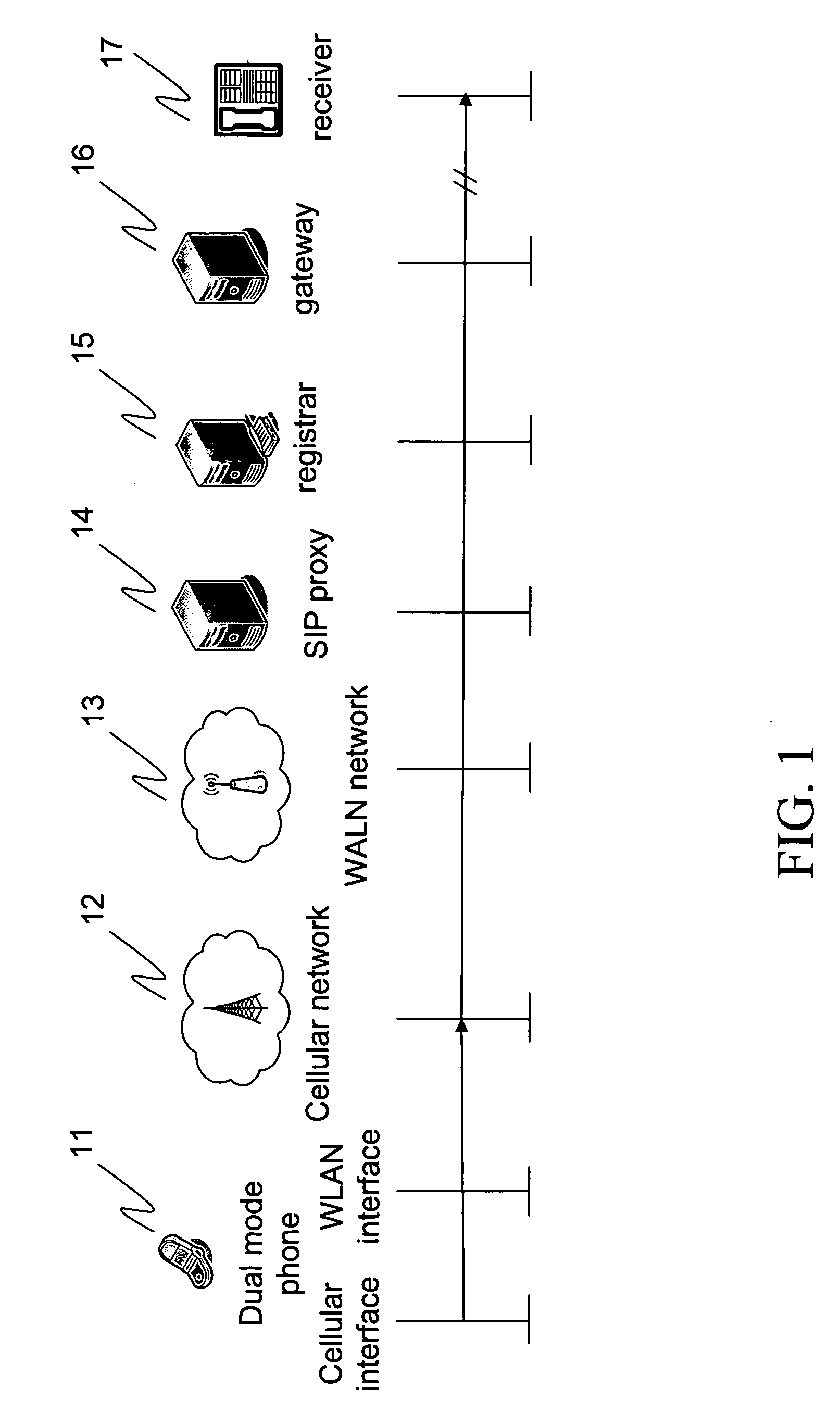

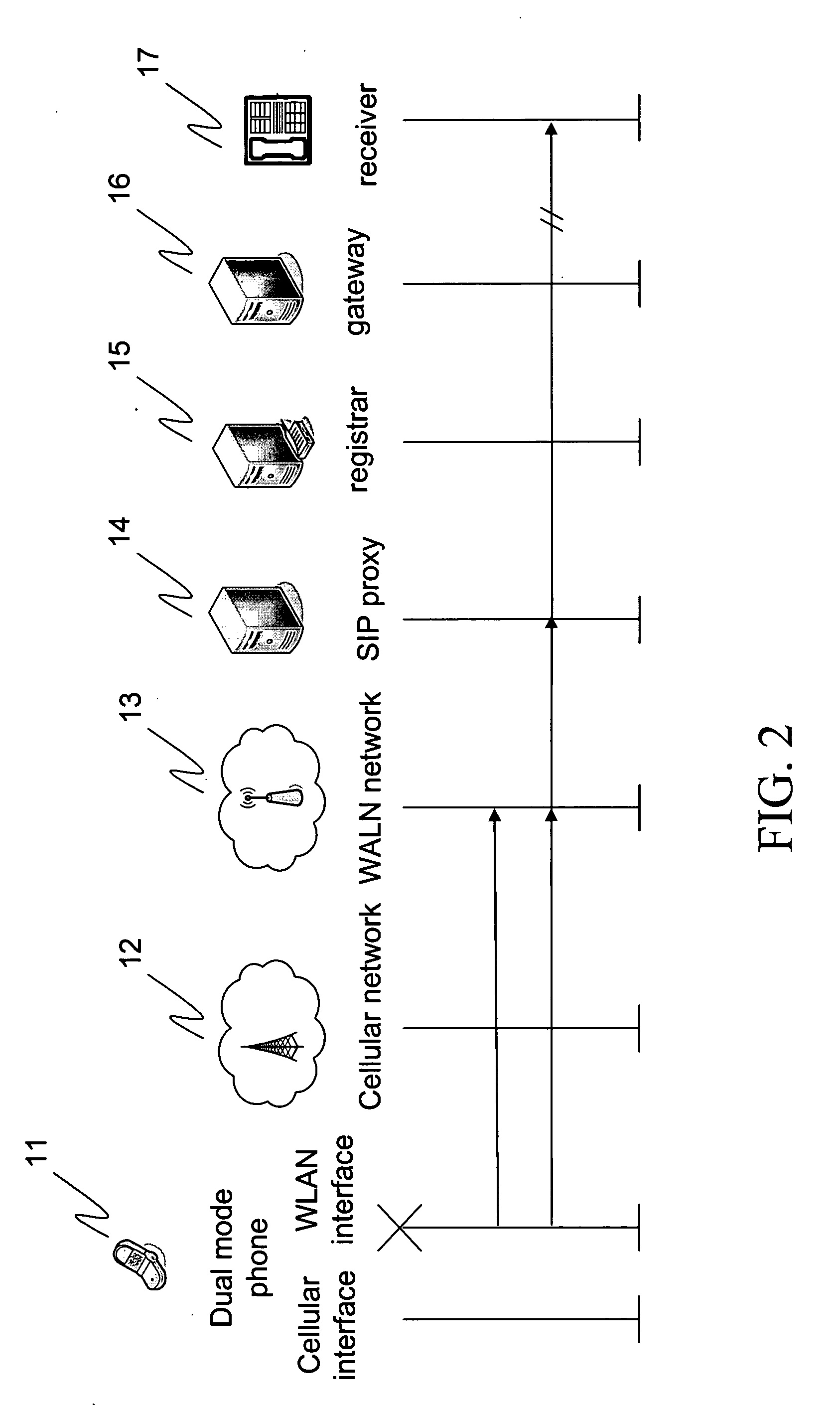

Method and system of providing cellular/WLAN dual mode telecommunication services

InactiveUS20060089169A1Minimize power consumptionPower managementNetwork topologiesDual modeNetworked system

A method and a system of providing cellular / wireless network dual mode communication services are provided. The wireless network interface normally stays in the standby mode, and the cellular interface is closed. When receiving calls, the cellular system receives the calls and wakes up the wireless network system to communicate to the calls. Hence, the power consumption of the dual mode phone is minimized.

Owner:IND TECH RES INST

Method and apparatus for adjusting the voltage and frequency to minimize power dissipation in a multiprocessor system

InactiveUS20070016814A1Minimize power consumptionIncreasing processor densityTransmitters monitoringEnergy efficient ICTOperating pointMulti processor

A method for adjusting the voltage and frequency to minimize power dissipation in a processor. The method of one embodiment comprises determining a power consumption value. The power consumption value is evaluated to obtain a new operating point. The new operating point is compared with a present operating point. A frequency setting and a voltage setting are adjusted to correspond to the new operating point if the new operating point is different from the present operating point.

Owner:SONY CORP OF AMERICA

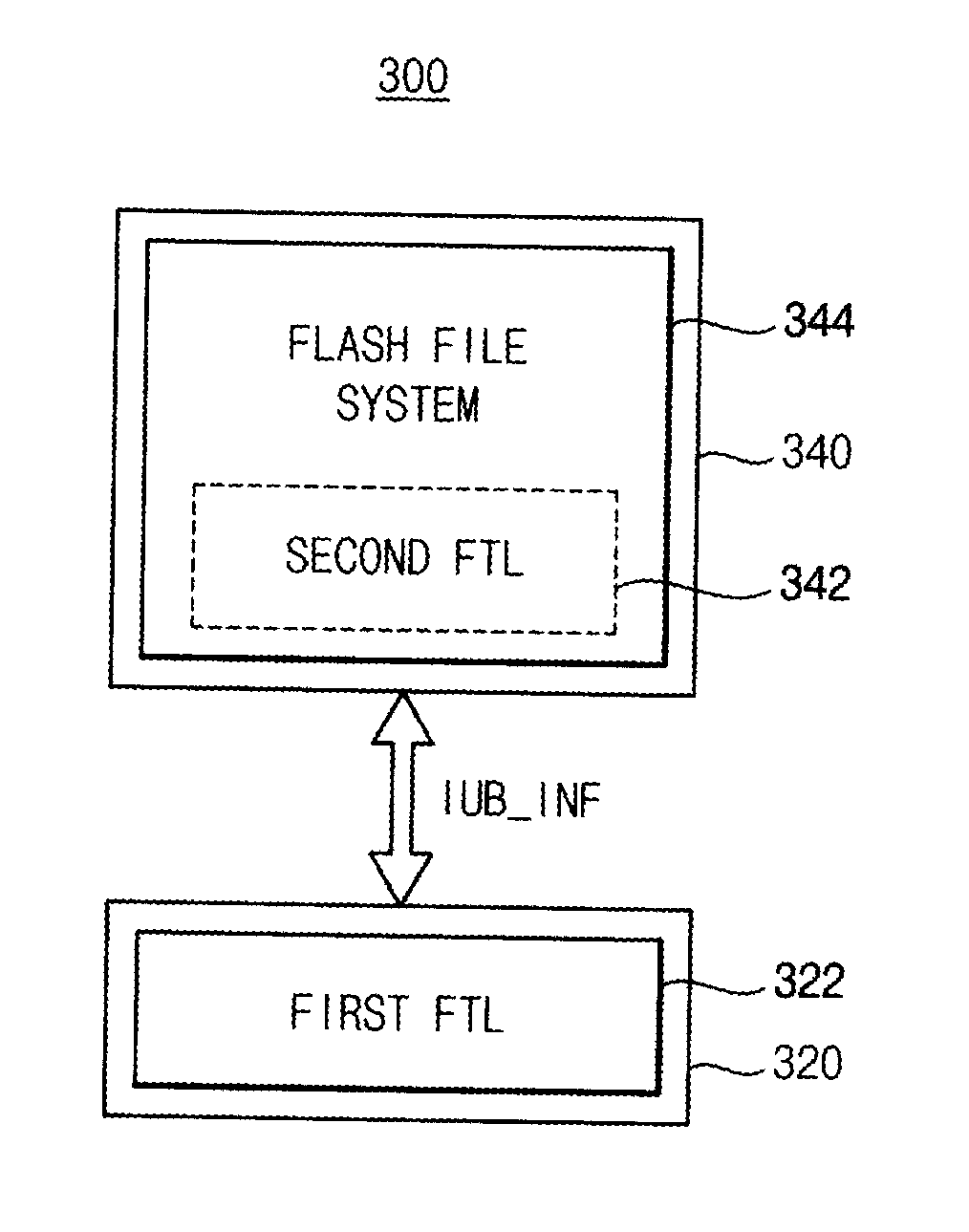

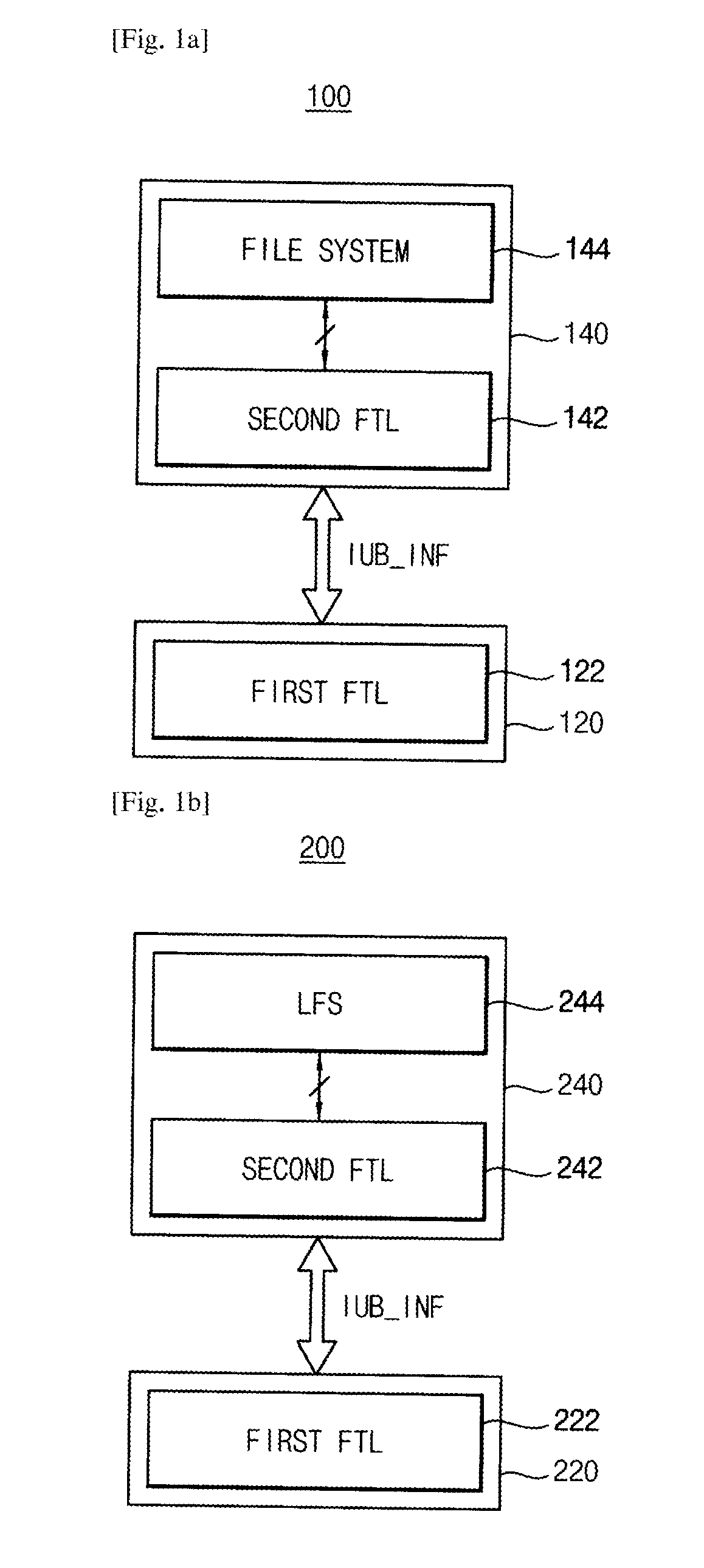

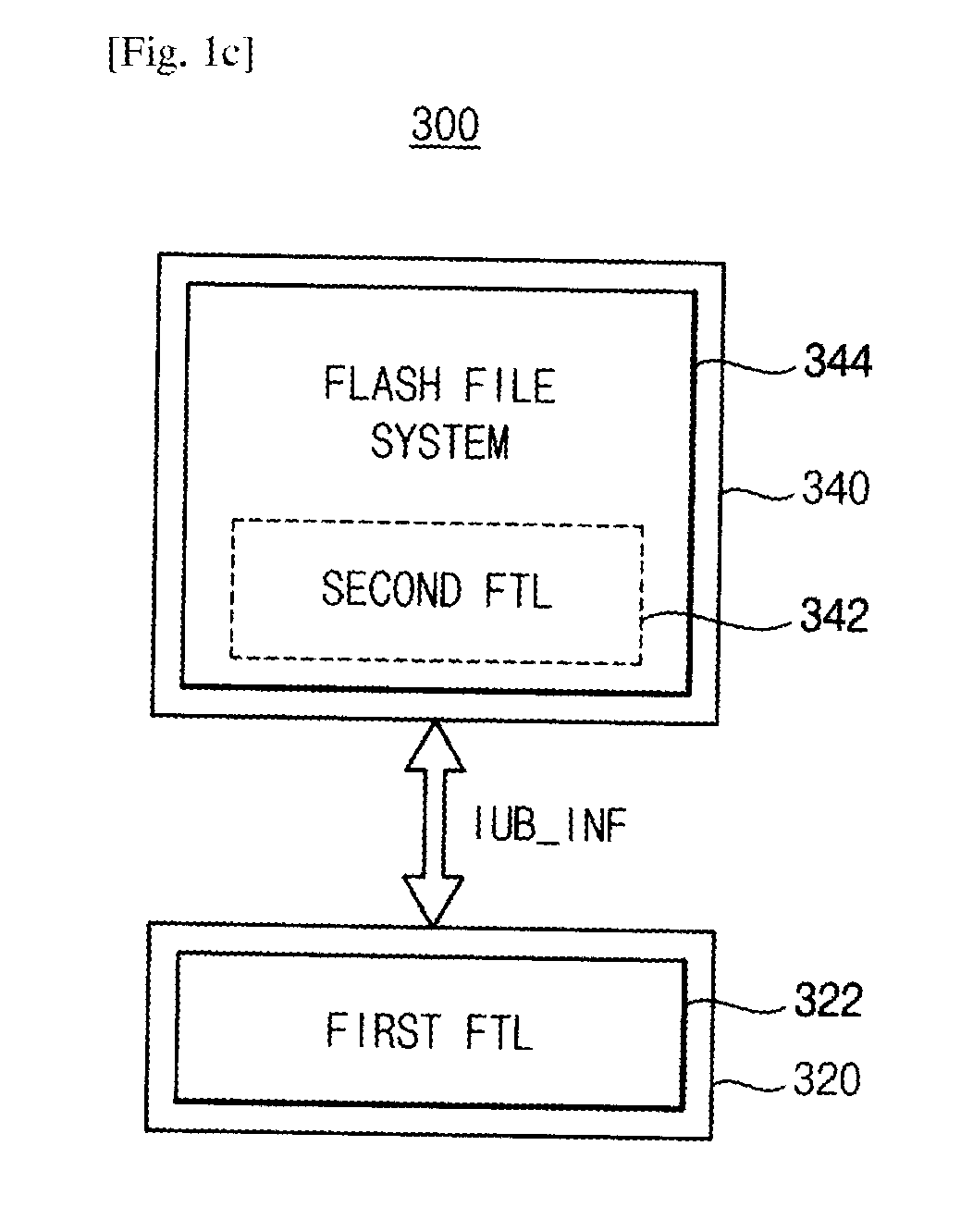

Nonvolatile memory system

InactiveUS20150127889A1Accurately knowEffective controlMemory architecture accessing/allocationMemory adressing/allocation/relocationFile systemOrder form

A non-volatile memory system includes a NAND flash memory device including a first flash translation layer that performs a garbage collection operation, and a host device including a file system and a second flash translation layer that controls an operation of the NAND flash memory device by interacting with the file system. Here, the host device provides application data in an in-ordered form to the NAND flash memory device. Thus, the non-volatile memory system can perform a random write operation at high speed, and can minimize power consumption due to unnecessary data transfer.

Owner:THE AIO

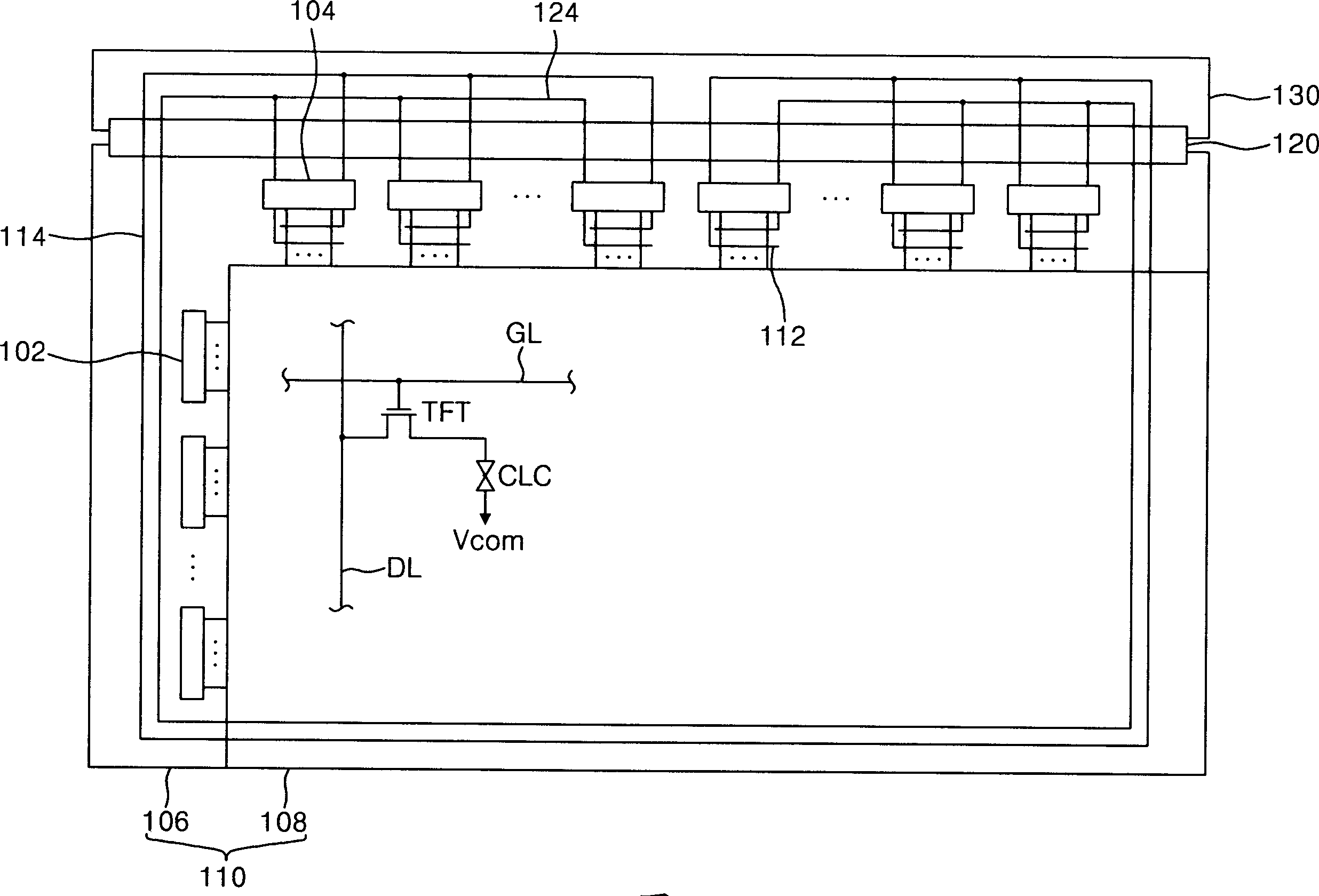

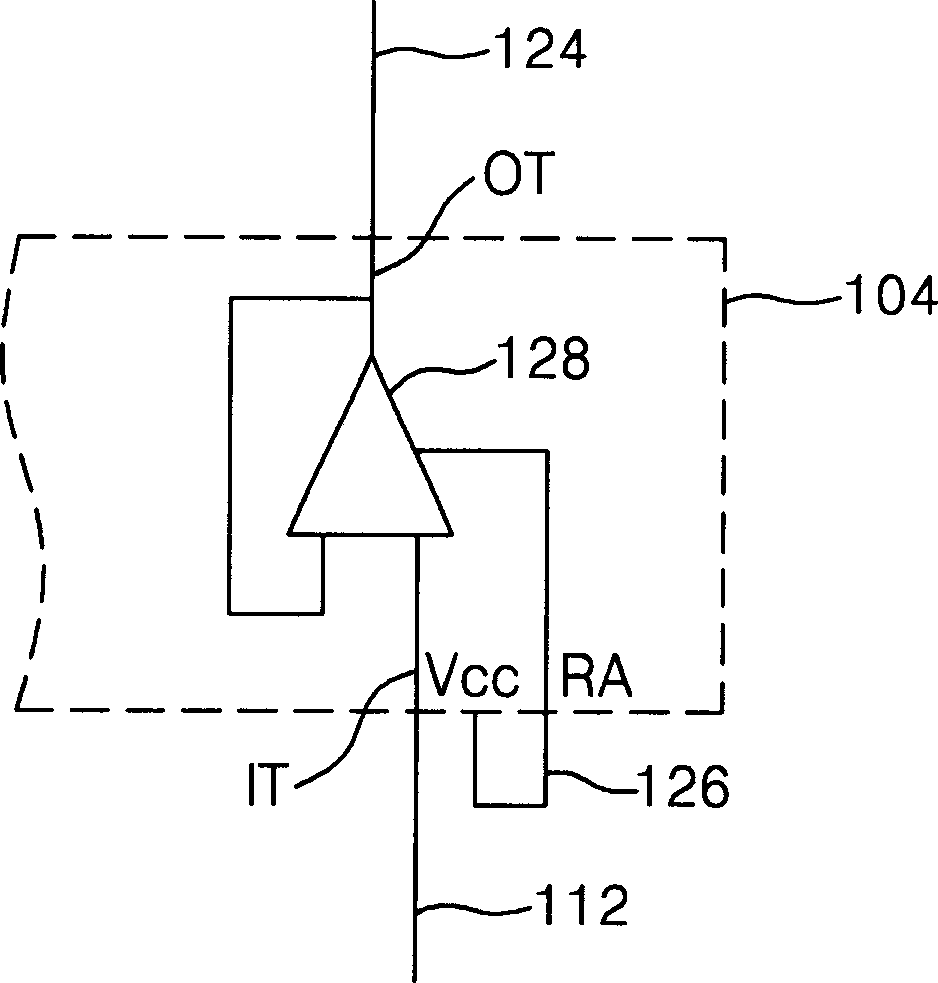

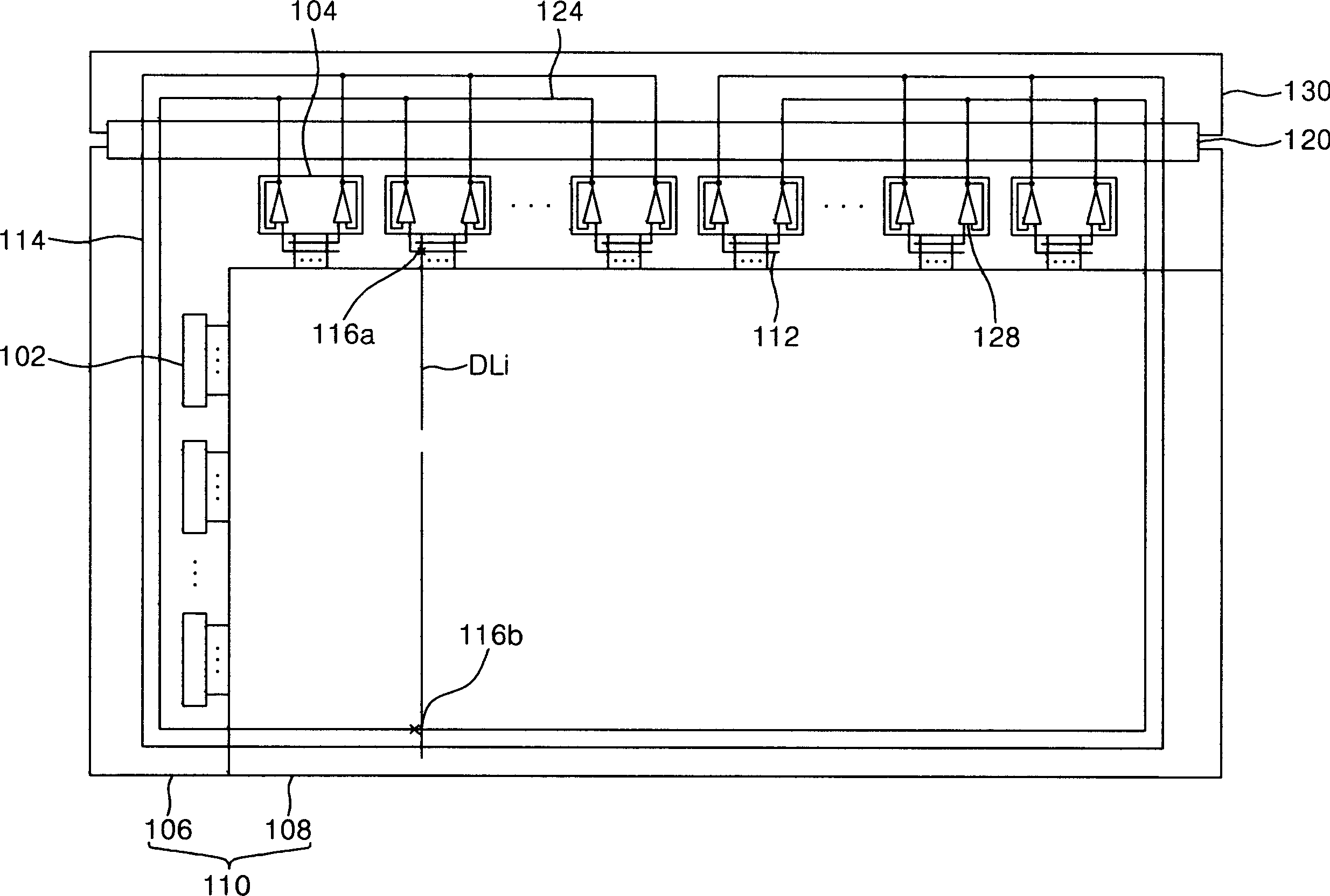

Liquid crystal display device repair system and method thereof

InactiveCN1916700AStatic indicating devicesNon-linear opticsAudio power amplifierLiquid-crystal display

Owner:SAMSUNG ELECTRONICS CO LTD

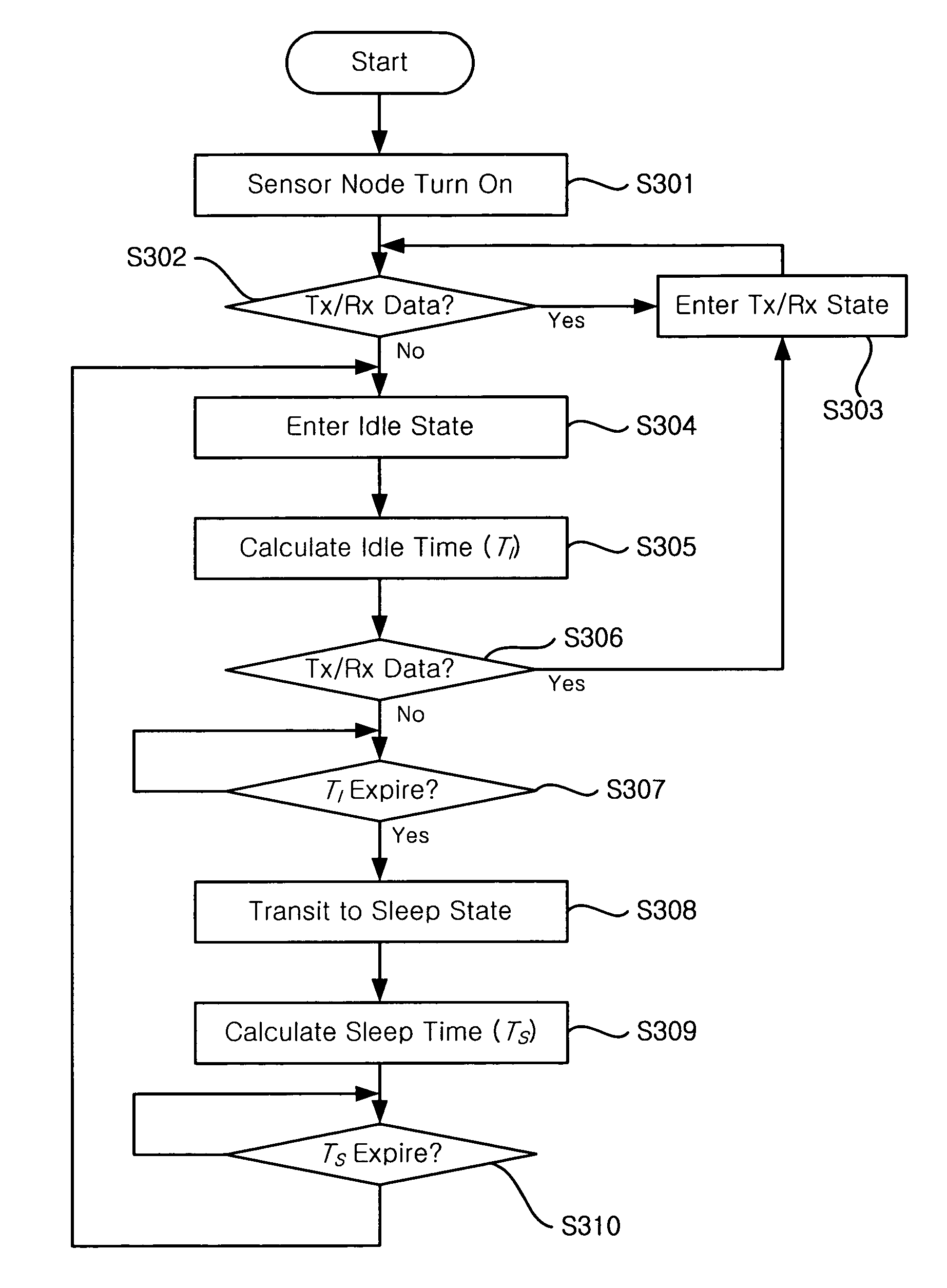

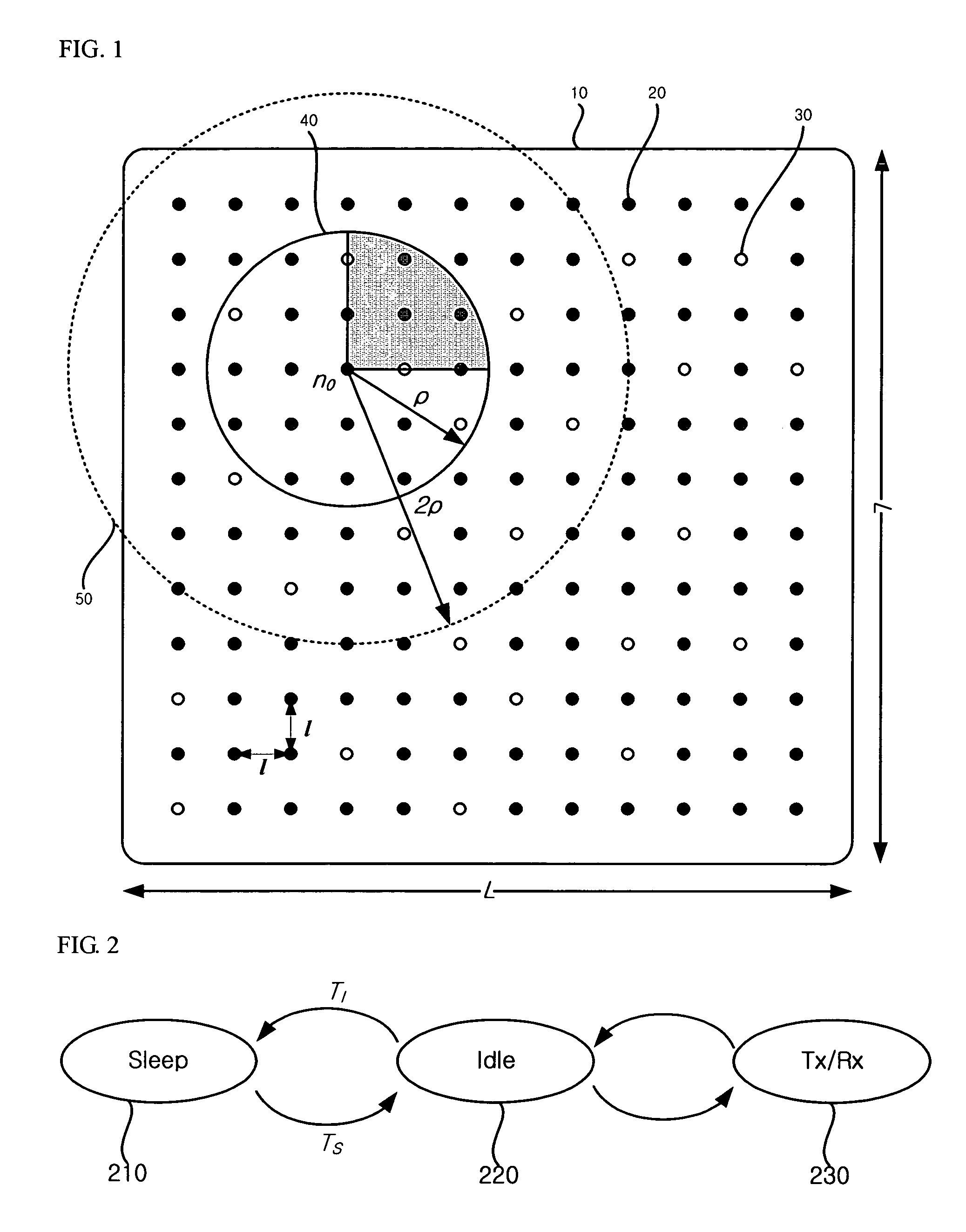

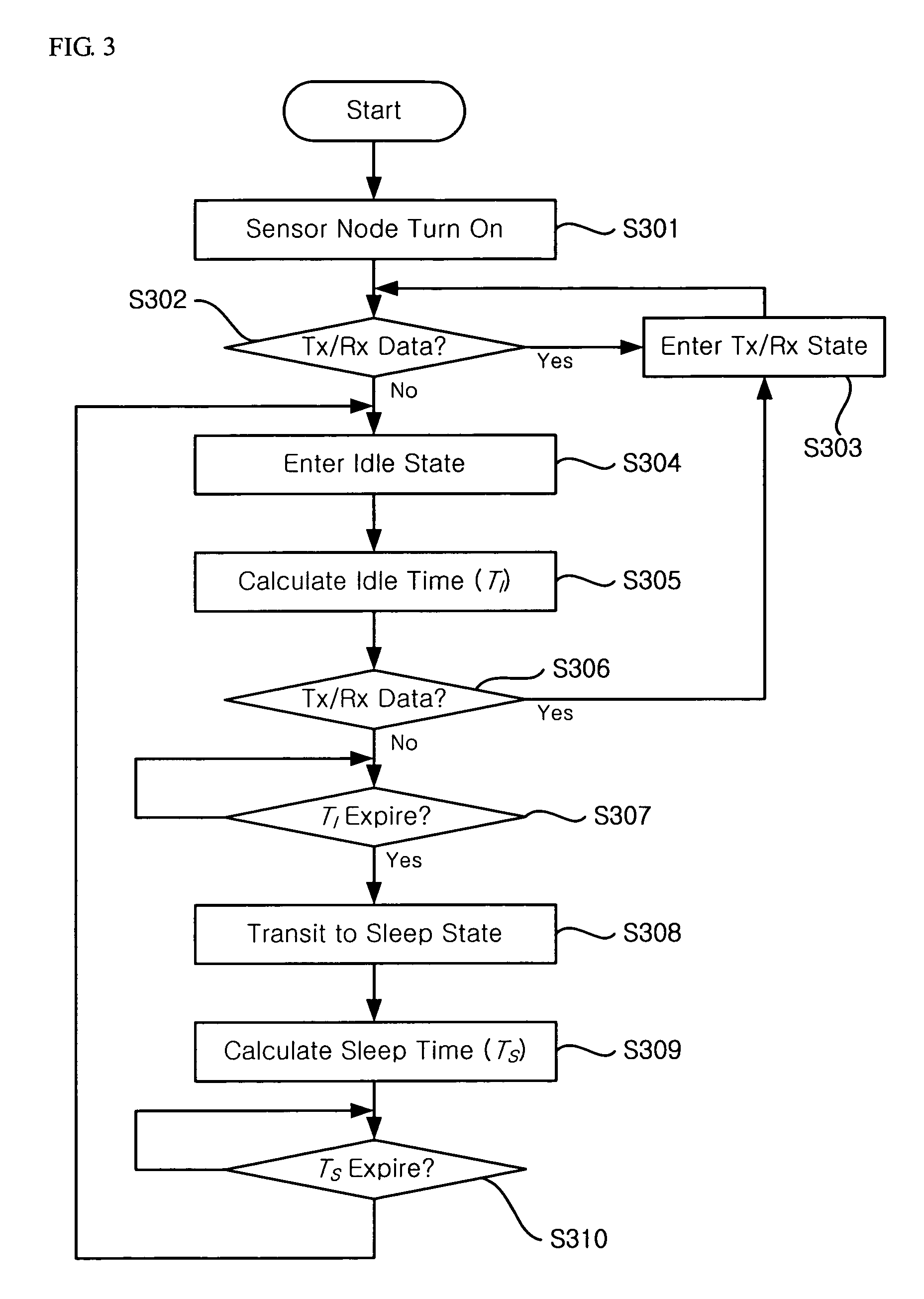

Power-saving method for wireless sensor network

ActiveUS7447526B2Improve power efficiencyLife maximizationEnergy efficient ICTPower managementControl powerSignal-to-noise ratio (imaging)

A power saving method of the present invention is provide for a wireless sensor network including a plurality of sensor nodes each transiting between a power saving mode and a transmit / receive mode, determines whether or not there is no transmit or receive data, enters the power saving mode if there is no transmit or receive data, and controls power consumption on the basis of signal-to-noise ratios in the power saving mode. In the power saving method of the present invention, it is possible to minimize the power consumption regardless of nodes density and without an adverse effect on the connectivity of the network, since the sojourn times of the sleep and idle states are determined adaptive to the interference level from neighboring nodes.

Owner:SAMSUNG ELECTRONICS CO LTD +1

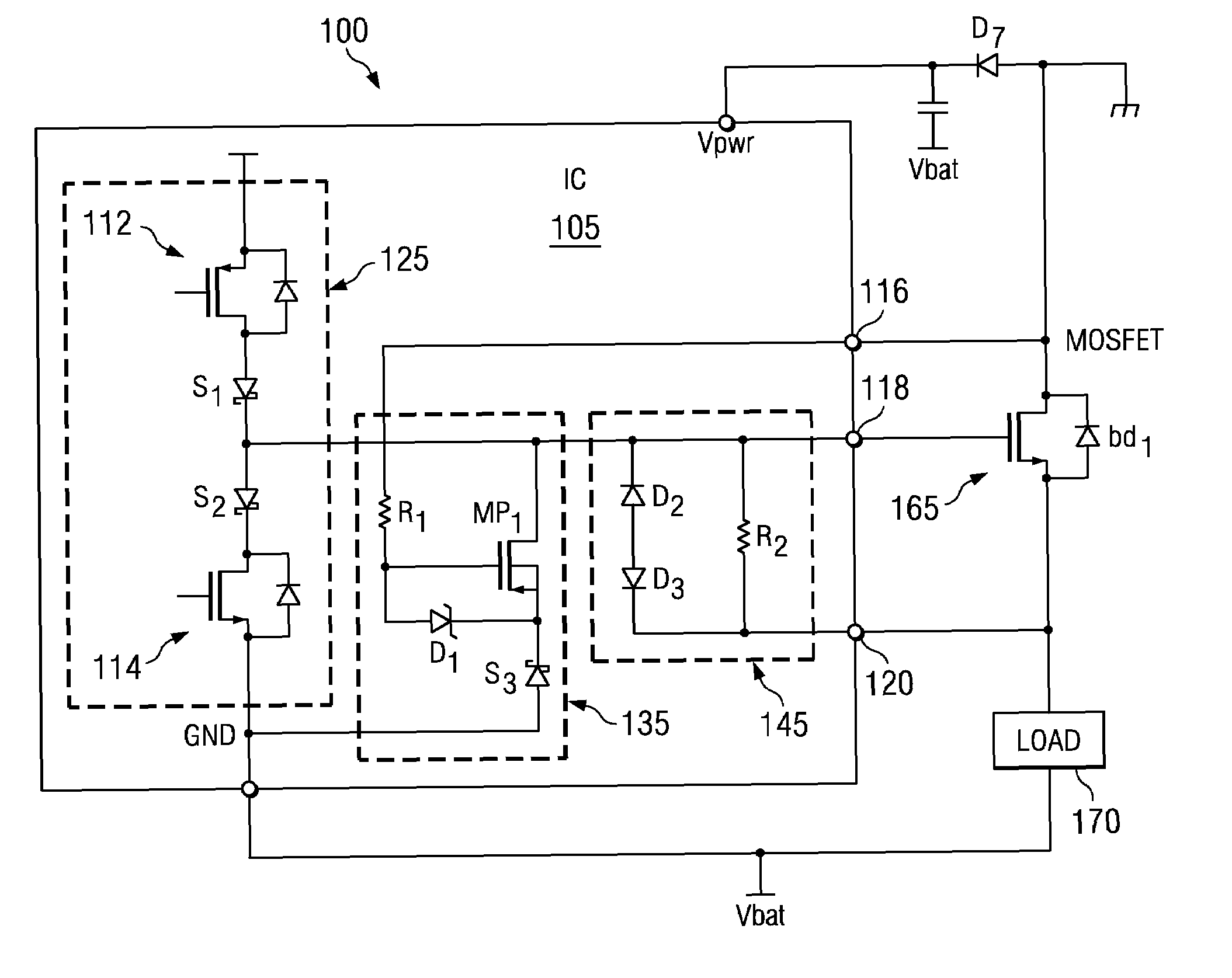

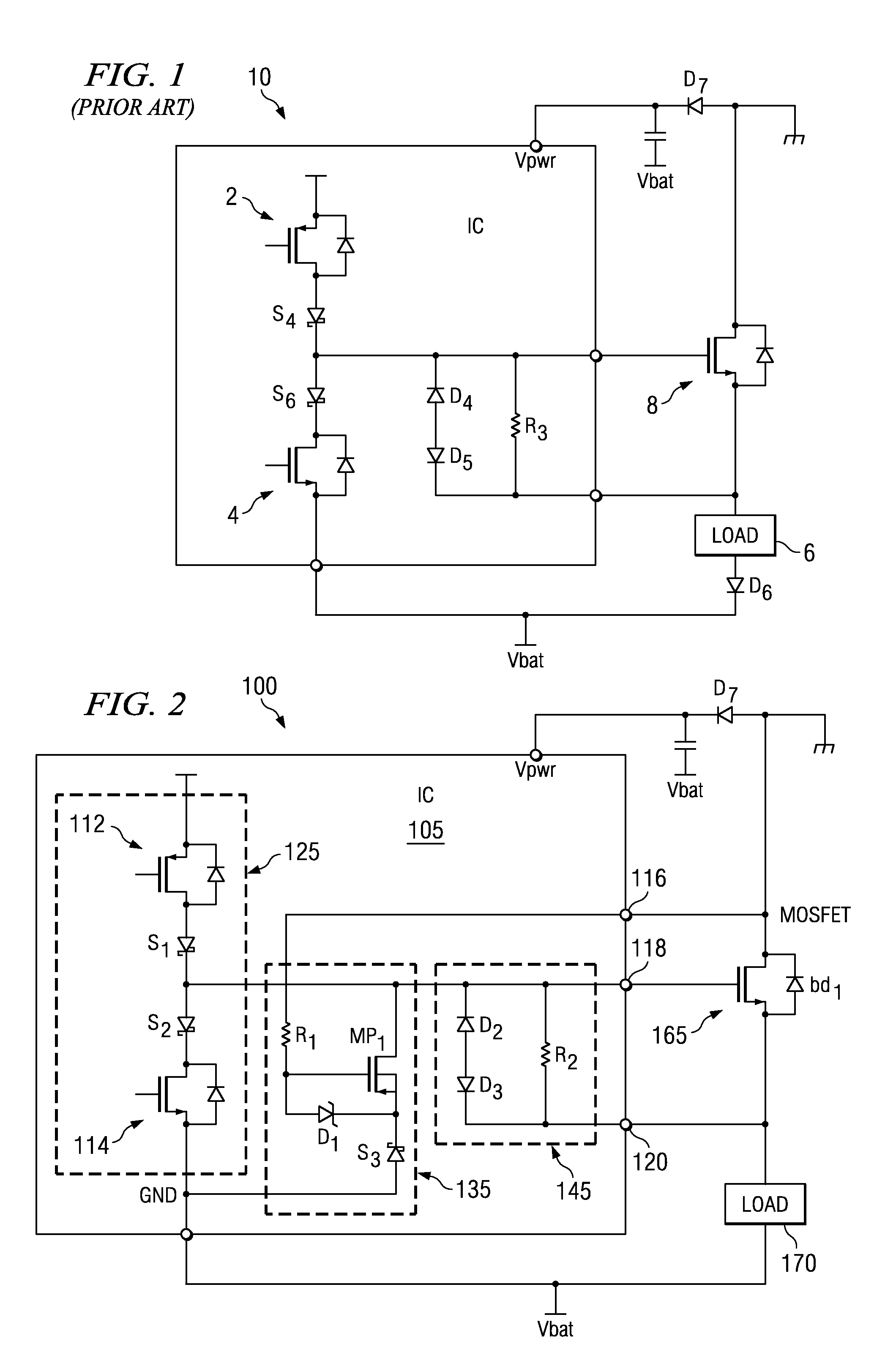

Integrated reverse battery protection circuit for an external MOSFET switch

ActiveUS7283343B2Minimize power consumptionLower resistanceEmergency protective arrangements for automatic disconnectionMOSFETPush pull

A reverse battery protection circuits that provides an integrated reverse battery condition solution for protection of external NMOS switches during the reverse battery condition is disclosed herein. This reverse battery protection circuit minimizes power consumption during a reverse battery event wherein there is no need for mechanical adjustments such as heat sinking and clamping to extract the heat away from the silicon and not destroy the device. Specifically, the reverse battery protection circuit includes a push-pull gate drive circuit coupled between the first and second power supply rail. A protection subcircuit portion connects between a first output node and the second power supply rail to turn the external FET ‘on’ during the reverse battery condition. In particular, the protection subcircuit portion connects to the external FET device and includes a p-channel device connected between a second output node that biases the external FET device and a first diode. A resistor connects between a first output node of the reverse battery protection circuit to provide a voltage drop between the drain terminal and the gate of the p-channel device. A second diode connects between the gate and the source of the p-channel device. In addition, a clamping circuit connects between the second output node and the third output node to provide clamping in the instance where the voltage at the second output node momentarily rises too high.

Owner:TEXAS INSTR INC

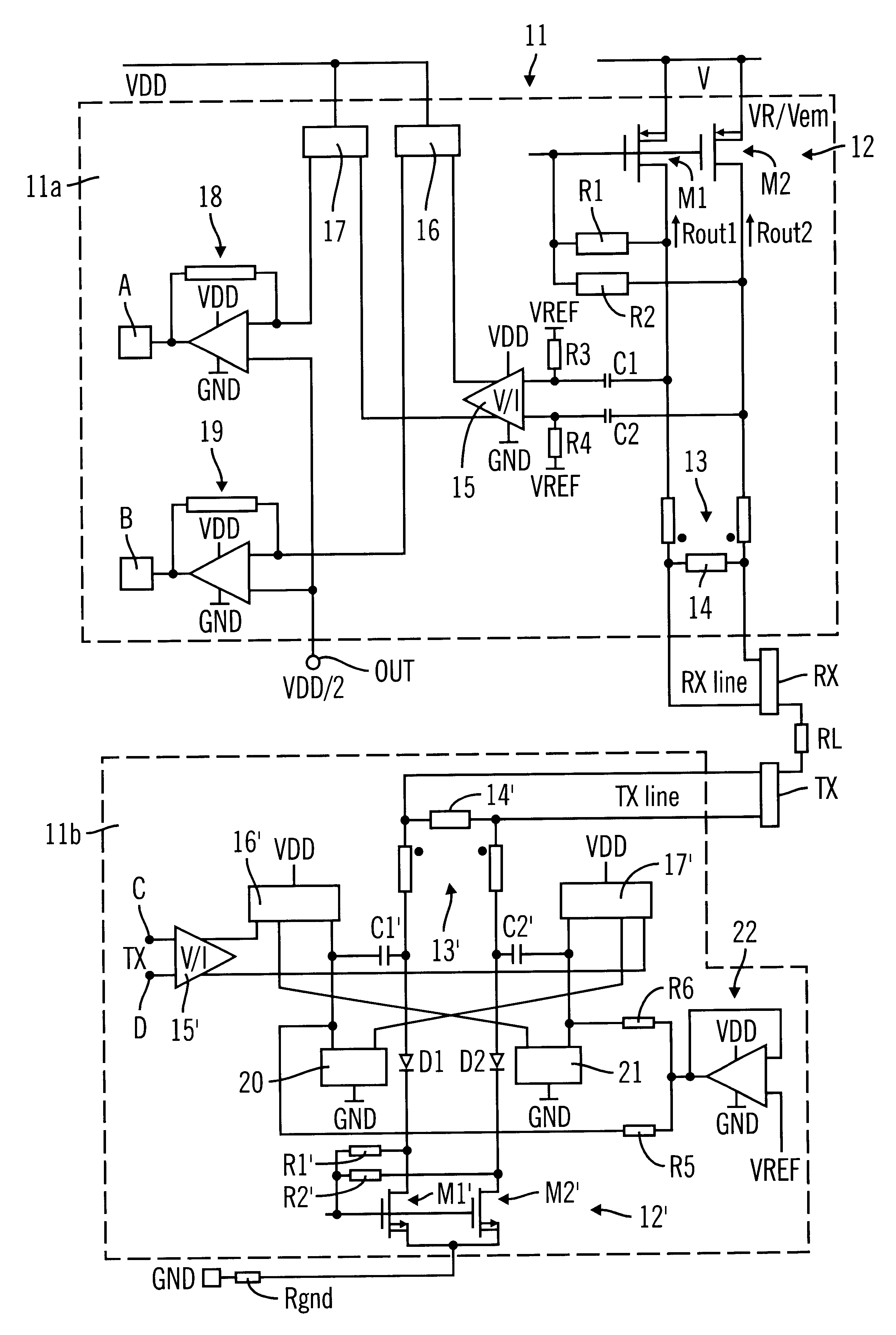

MOS transistors substitute circuit having a transformer/data interface function, particularly for ISDN networks and corresponding control and driving switch configuration

InactiveUS6560333B1Interconnection arrangementsCurrent supply arrangementsNetwork terminationControl signal

The invention relates to a MOS transistors substitutive circuit having a transformer / data interface function, in particular for ISDN networks, comprising first (11a) and second (11b) power supply / transmitter blocks, the first power supply / transmitter block (11a) being connected between a voltage reference (V) and a first data interface (RX), and the second power supply / transmitter block (11b) being connected between a ground potential reference (GND) and a second data interface (TX), both power supply / transmitter blocks being connected to a supply voltage reference (VDD). The MOS transistors substitutive circuit according to the invention comprises first (12) and second (12') MOS transistor pairs connected to the voltage reference (V), the MOS transistors being diode configured and held in their saturation range, so as to have a high A.C. impedance and virtually zero D.C. impedance, thereby minimizing power dissipation through the substitutive circuit.The invention also concerns a control and driving switch configuration for a network termination of at least first (11) and second (11') MOS transistors substitutive circuits according to the invention, operating respectively in a first condition ("normal condition") of operation of the network termination characterized by the presence of the polarity reverse control signal (Scrp), and a second condition ("RM emergency condition") of operation of the network termination characterized by the absence of the polarity reverse control signal (Scrp). The control configuration selects the voltage reference being applied to the power supply / transmitter blocks.

Owner:STMICROELECTRONICS SRL

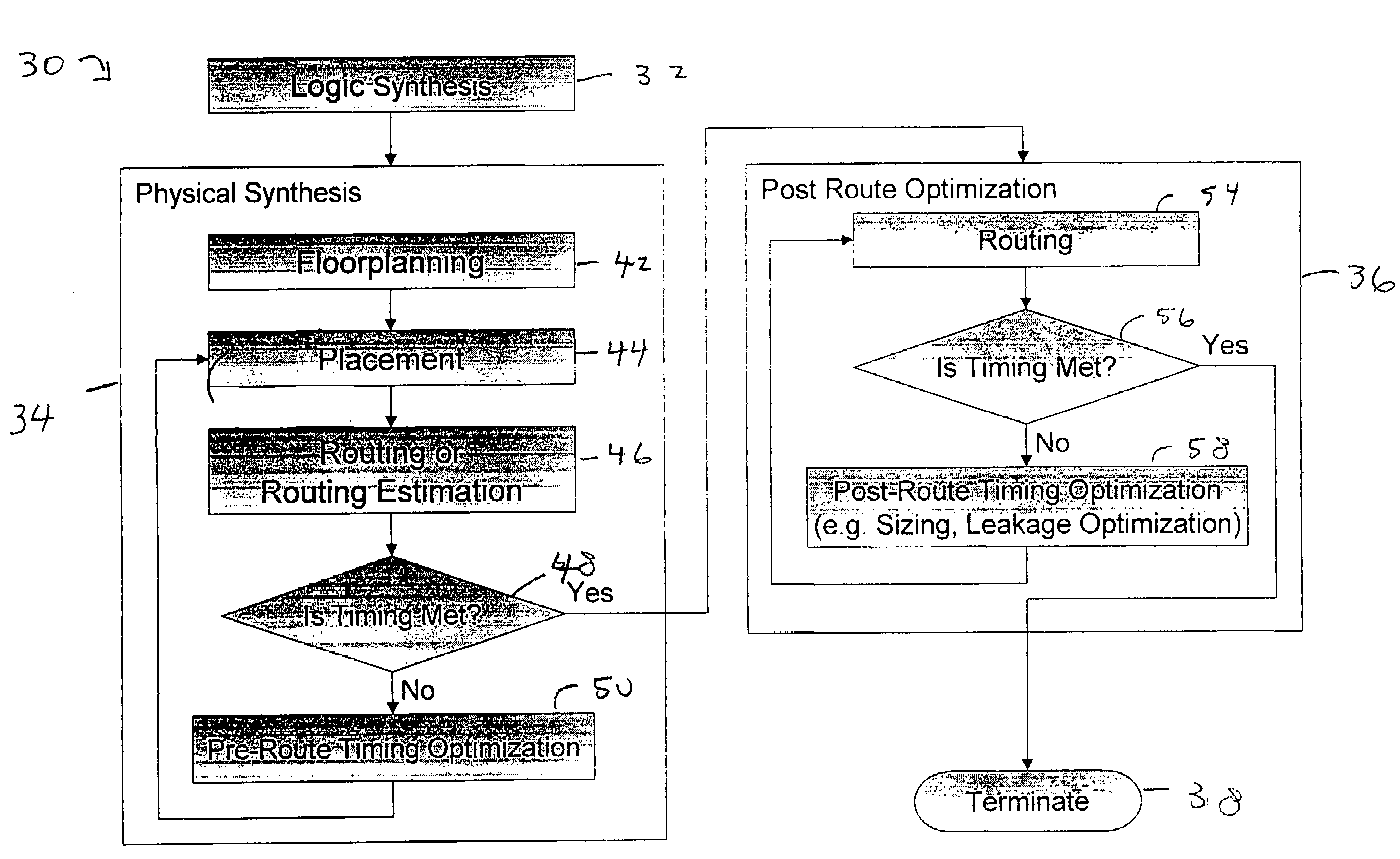

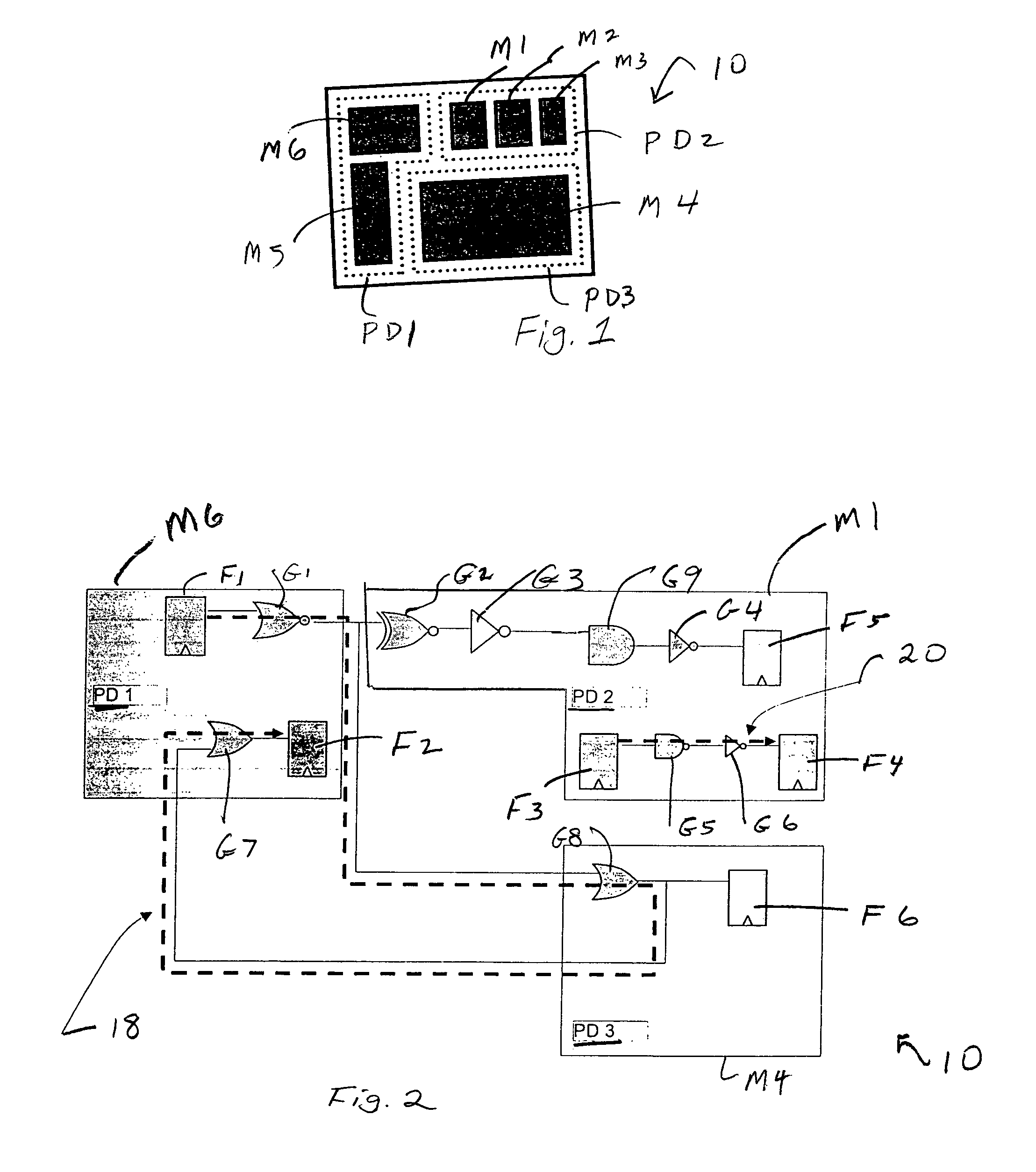

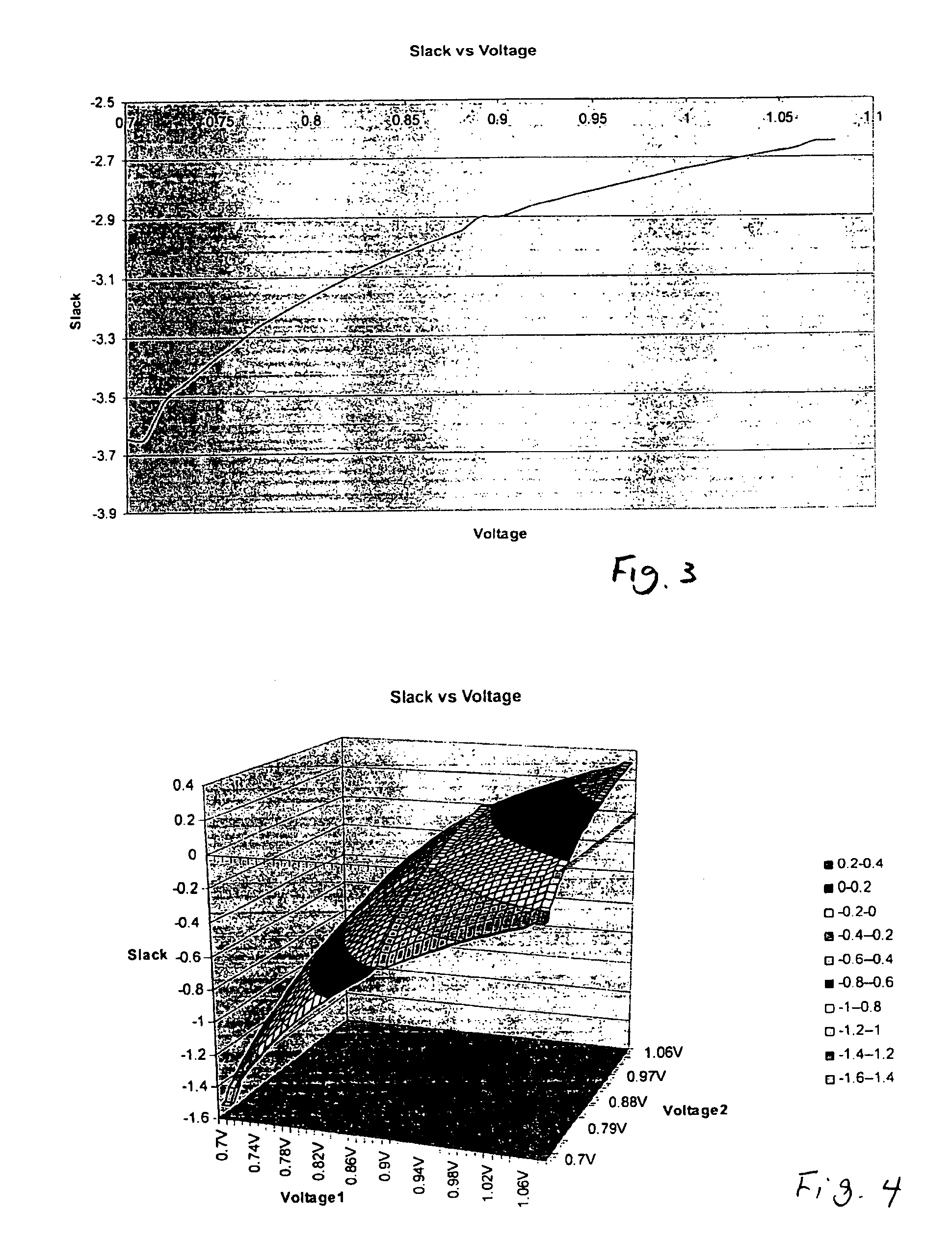

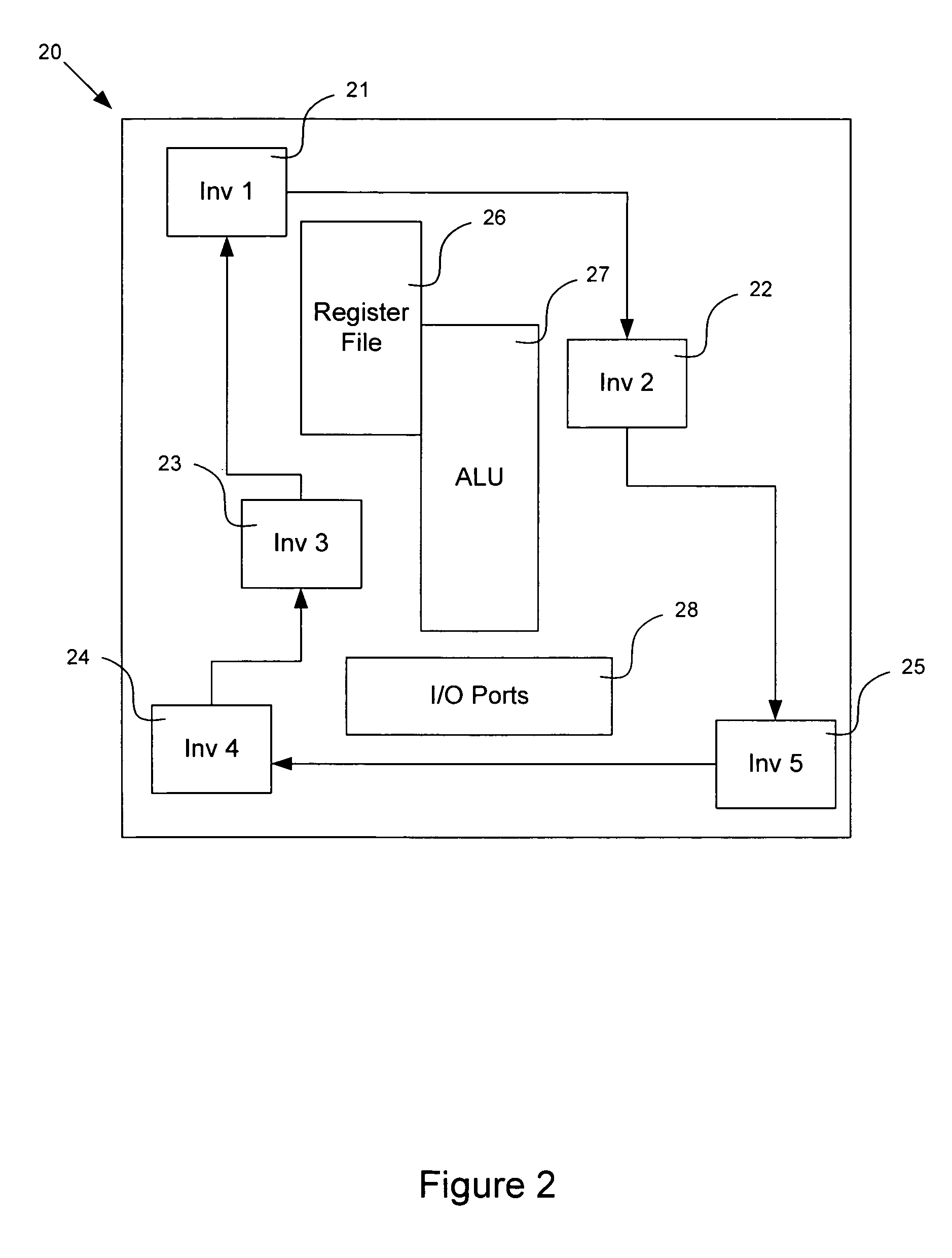

Method and apparatus for power consumption optimization for integrated circuits

InactiveUS7551985B1Minimize power consumptionMeet Timing RequirementsMechanical power/torque controlLevel controlEngineeringIntegrated circuit layout

Method and apparatus for finding an assignment of voltages to all power domains of an integrated circuit such that the power consumption of an integrated circuit design is minimized and timing requirements (signal propagation delay or slack) are met. This is done by modeling both internal and external signal paths in an integrated circuit which has a number of power domains. The relationship between slack and voltage for the external and internal signal propagation paths is modeled, typically as a linear approximation. The integrated circuit design is then abstracted to a simplified form in terms of power domain relations and a model is created and solved iteratively using, e.g., linear programming, of different voltage levels for each power domain and including the slack values and their relationship between the changes in voltage and slack, for both the internal and external paths.

Owner:CADENCE DESIGN SYST INC

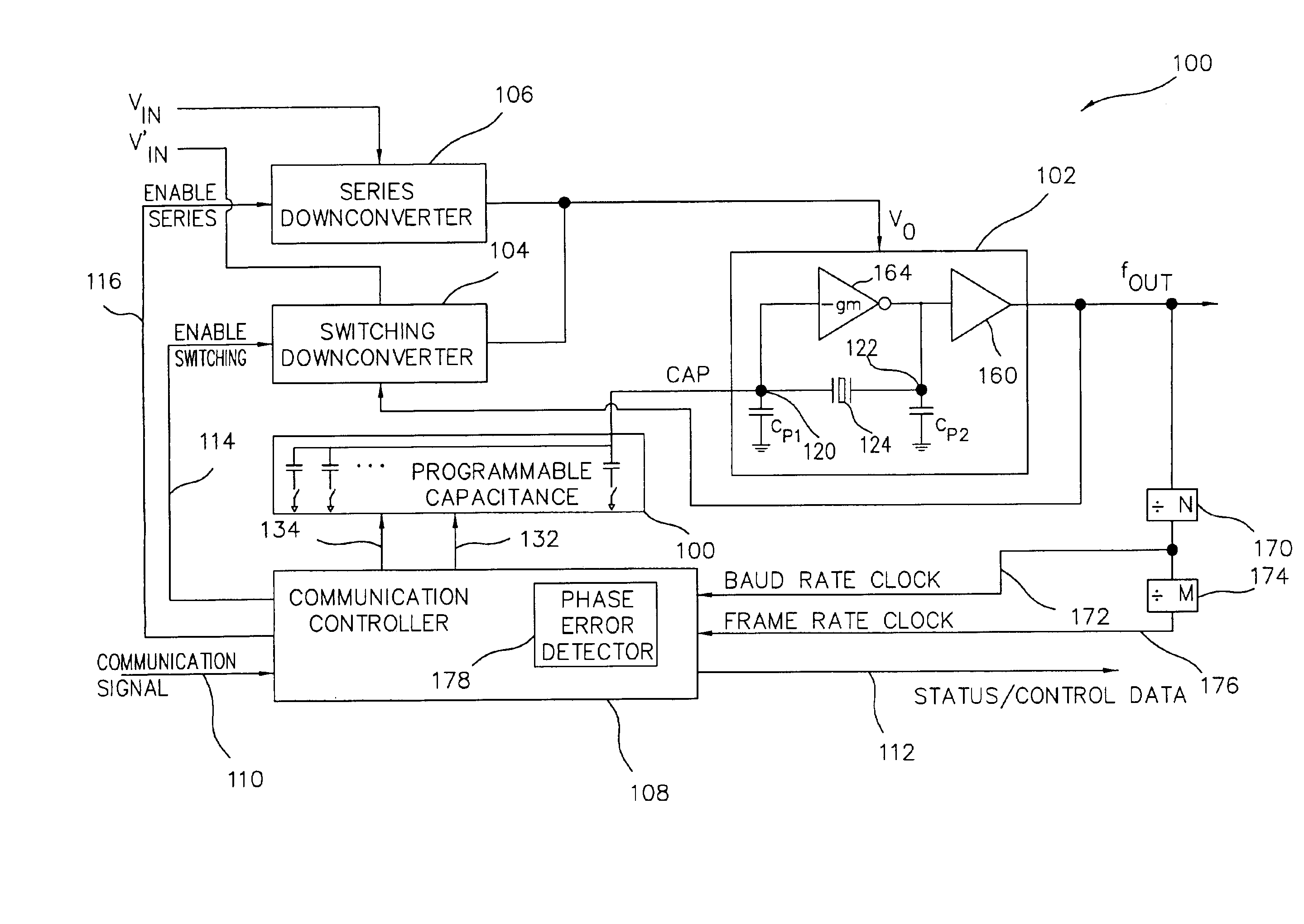

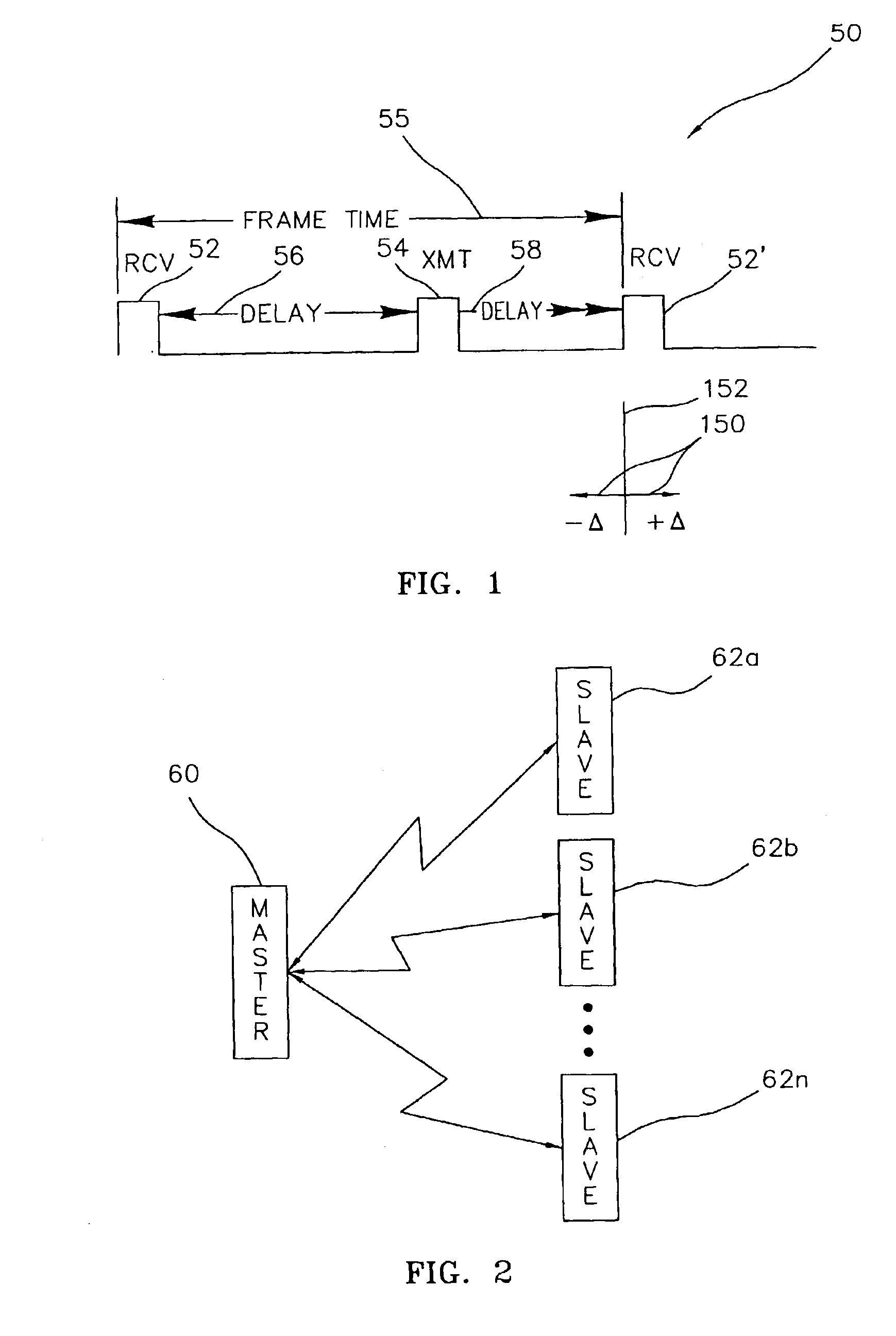

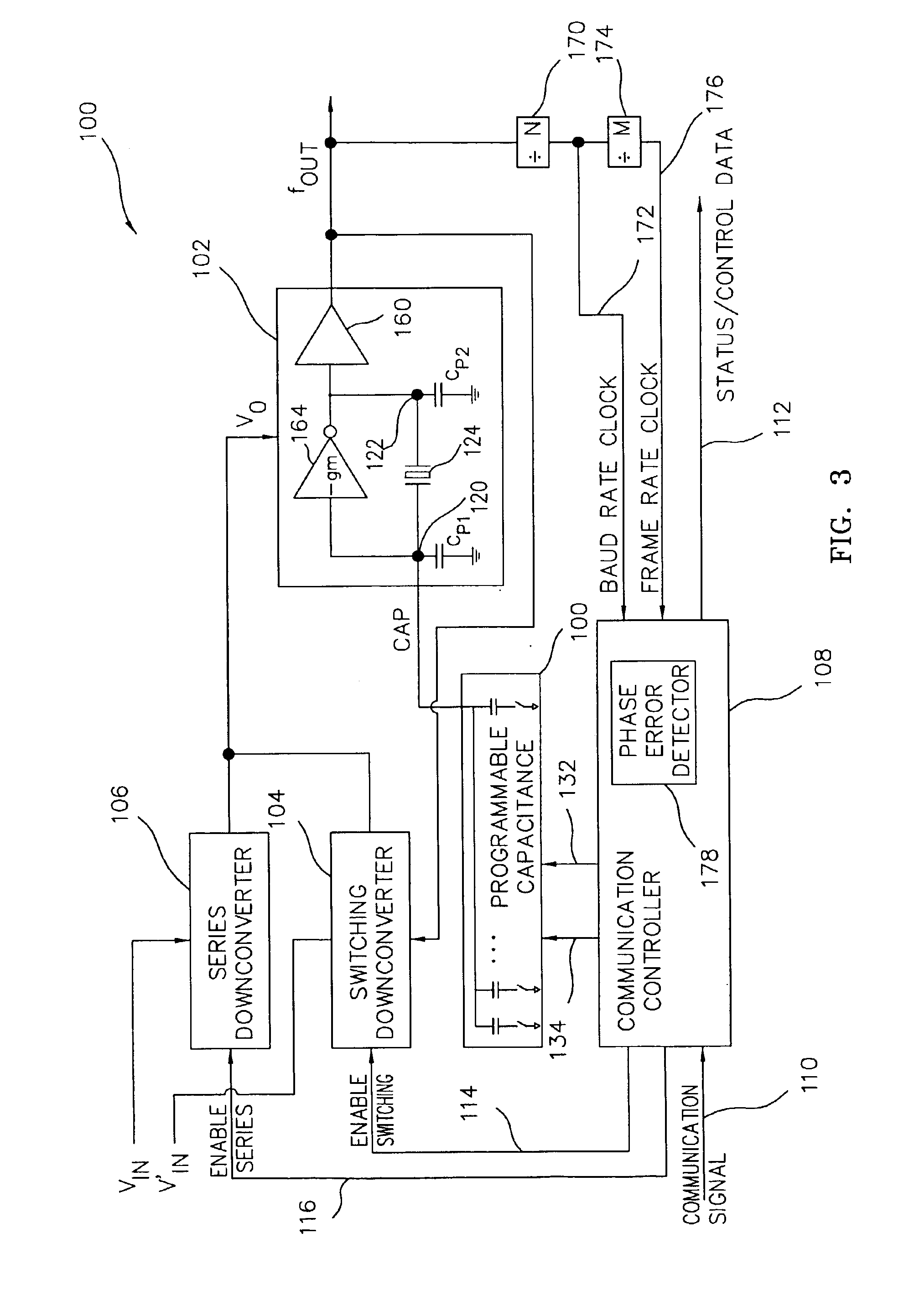

Multi-mode crystal oscillator system selectively configurable to minimize power consumption or noise generation

ActiveUS6959217B2Limited amountNoise minimizationElectrotherapyPulse automatic controlNoise generationSignal-to-noise ratio (imaging)

The present invention is directed to a multi-mode crystal oscillator system selectively configurable to minimize power consumption or noise generation. Such a system is particularly applicable to the communication system of an implantable device, e.g., the microstimulator / sensor device described in U.S. Pat. Nos. 6,164,284 and 6,185,452. In such devices, their small size limits the size of the battery contained within and thus makes it essential to minimize power consumption. Additionally, the small size and battery capacity result in a limited transmission power. Furthermore, the small size limits the antenna efficiency which makes it desirable to limit any noise generation to maximize the signal-to-noise level of the resulting receive signal. Accordingly, embodiments of the present invention alternatively supply power to the oscillator in either a first mode that minimizes power consumption or a second mode that minimizes noise generation.

Owner:ALFRED E MANN FOUND FOR SCI RES

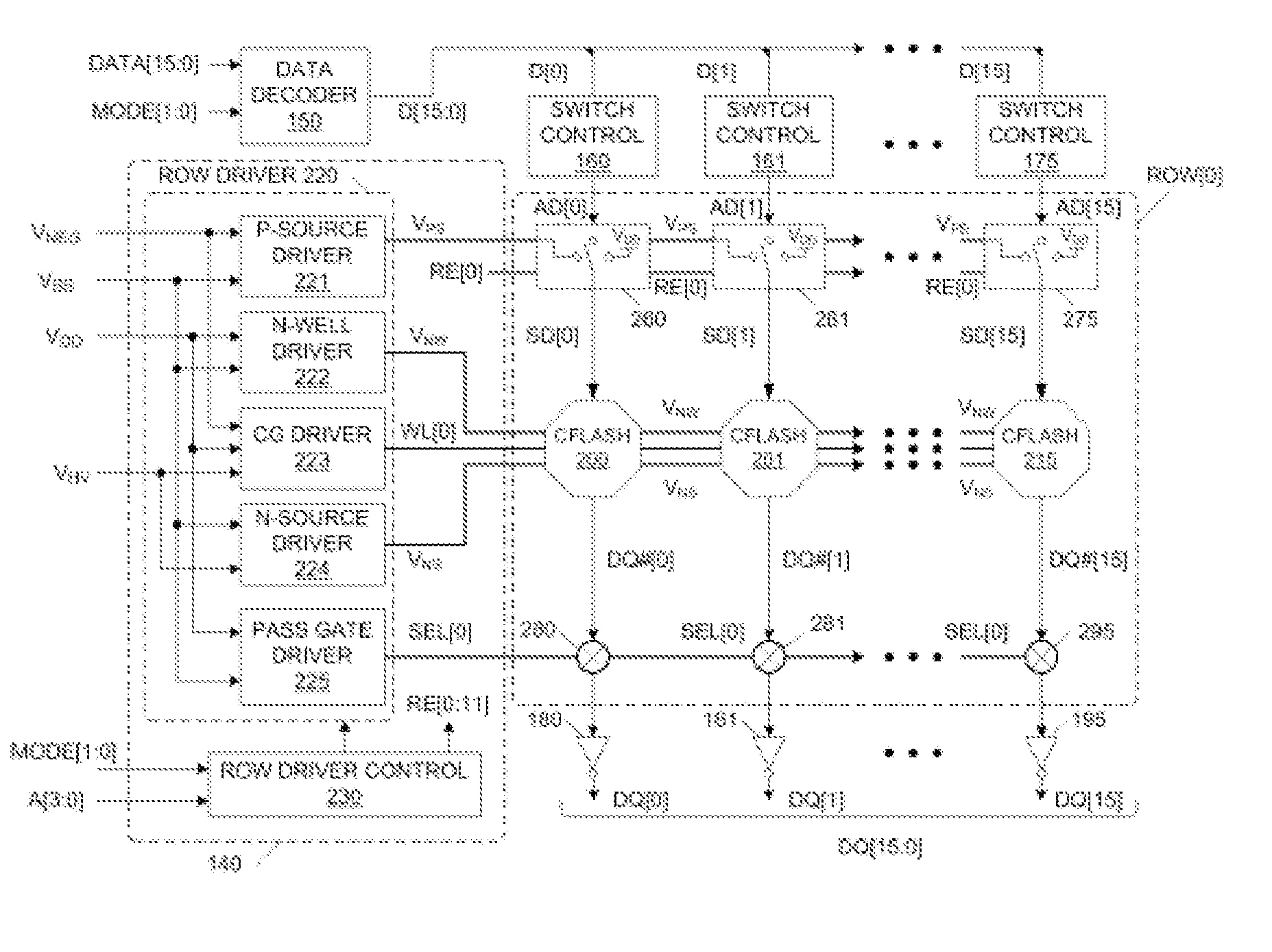

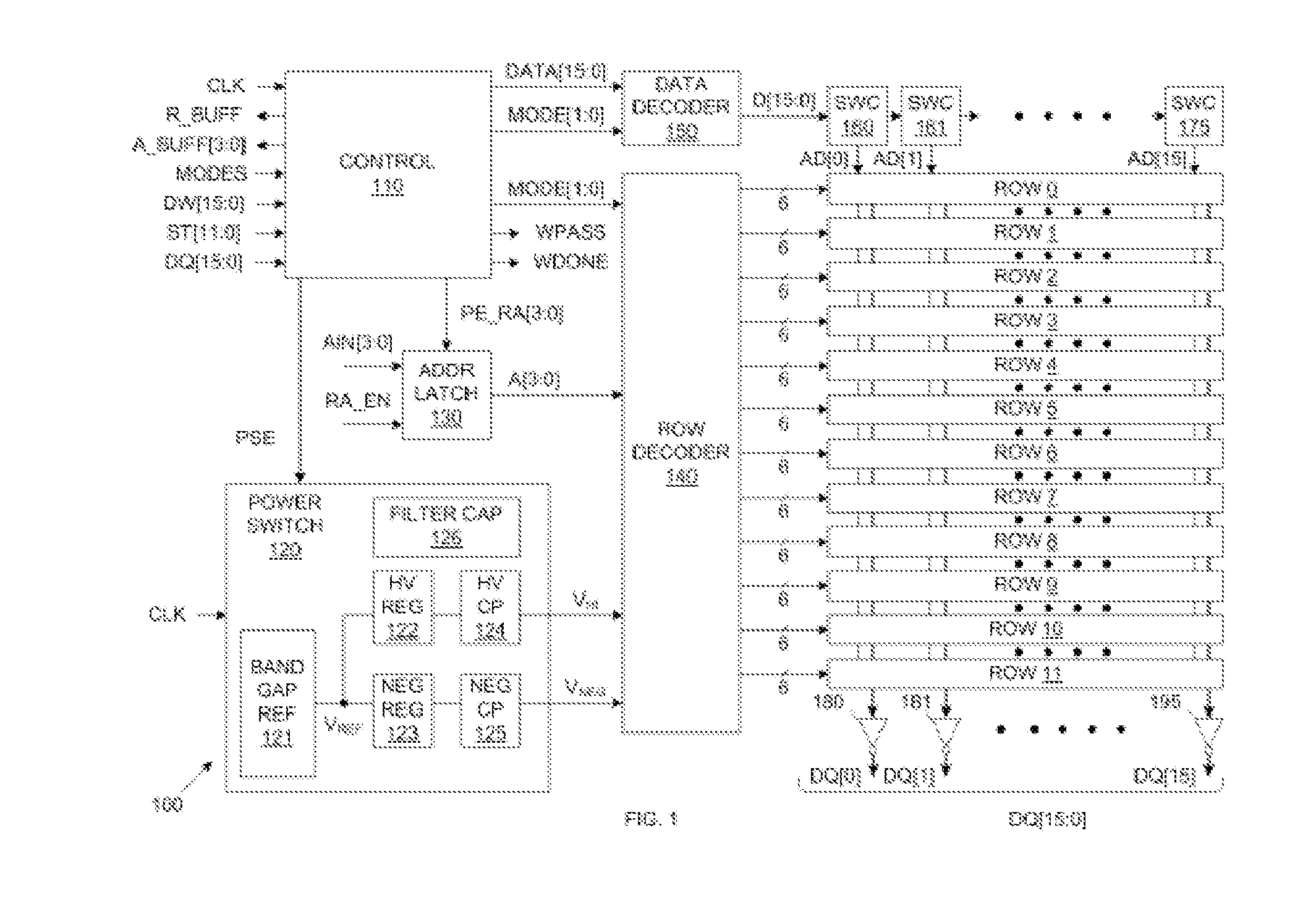

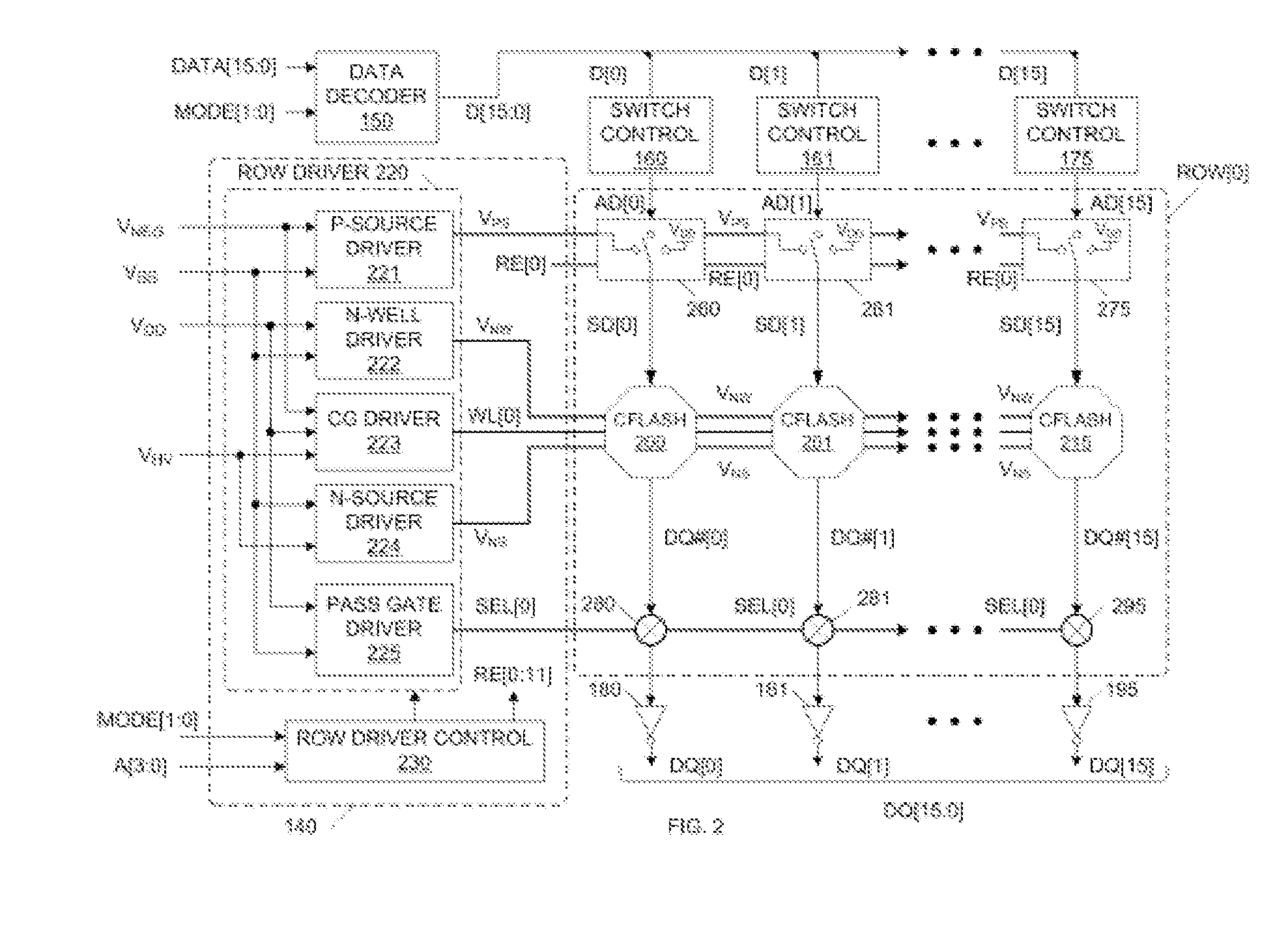

Ultra Low Power Non-Volatile Memory Module

InactiveUS20070223282A1Low powerReduce layout areaRead-only memoriesDigital storageEngineeringPower dissipation minimization

An improved ultra-low power NVM module, which exhibits low power consumption and reduced layout area. An array of compact flash memory cells are programmed and erased in response to positive and negative boosted voltages. However, the compact flash memory cells are read using conventional supply voltages, thereby minimizing power consumption during a read operation. The ultra-low power NVM module of the present invention can be fabricated using conventional VLSI process steps. The ultra-low power NVM module of the present invention also allows simple operation in all modes (i.e., program, erase, read and standby).

Owner:RPX CORP

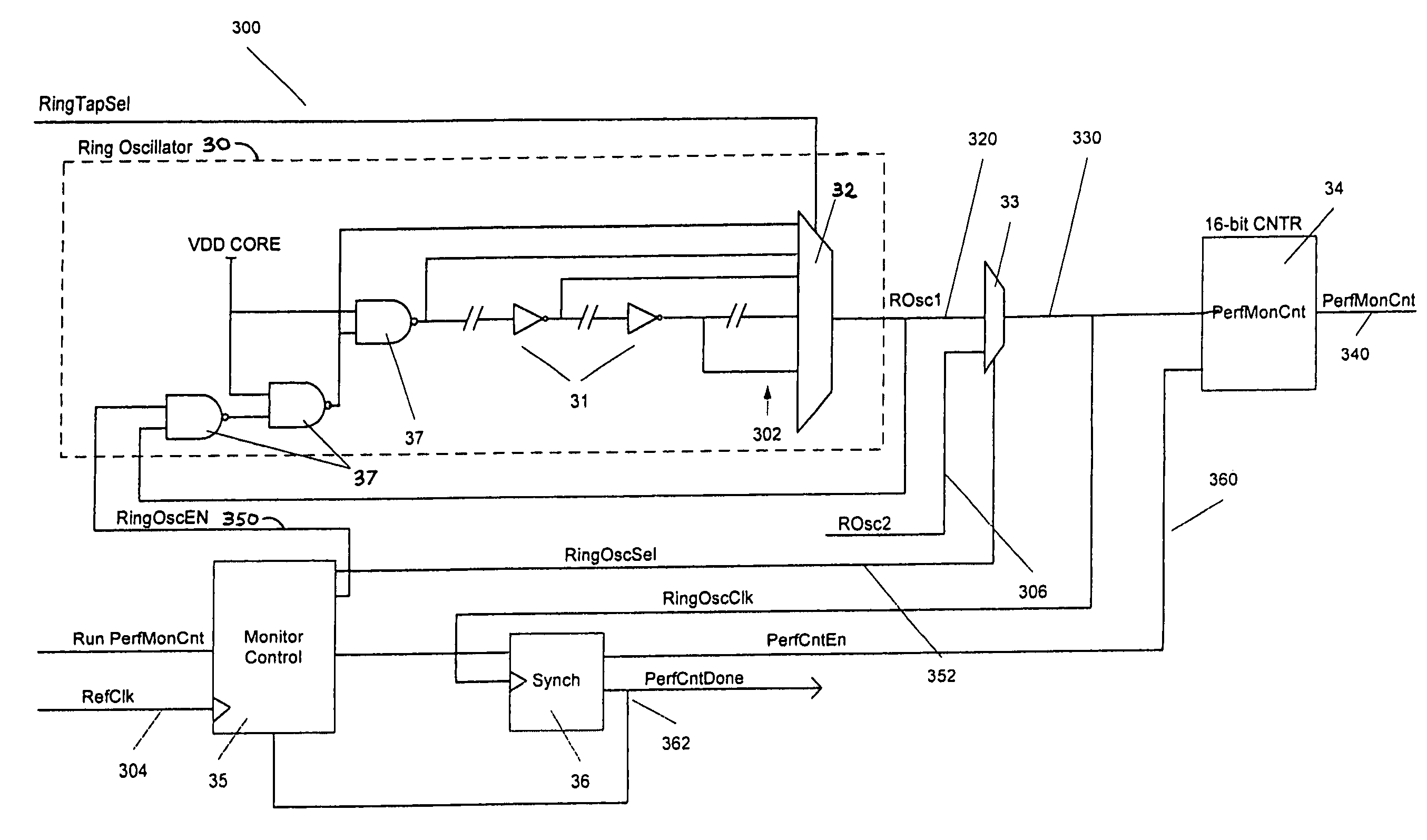

Dynamic voltage scaling

ActiveUS7739531B1Minimize power consumptionPacked tightlyEnergy efficient ICTVolume/mass flow measurementEngineeringDynamic voltage scaling

An apparatus and method for dynamically controlling the maximum frequency of operation of the IC is provided. The invention optimizes power consumption in a device by measuring a current maximum frequency of operation and adjusting IC operating voltage to provide a desired maximum operating frequency. The invention provides an apparatus and method for controlling multiple voltages in an IC to independently adjust maximum operating frequencies for a plurality of separate portions of the IC. The invention may equally be applied to a group of ICs. The invention further provides a method for calibrating an IC. Thus, the apparatus facilitates the operation of an IC at a minimum voltage for a selected maximum frequency, thereby minimizing power consumption overall a wide range of operating frequencies.

Owner:NVIDIA CORP

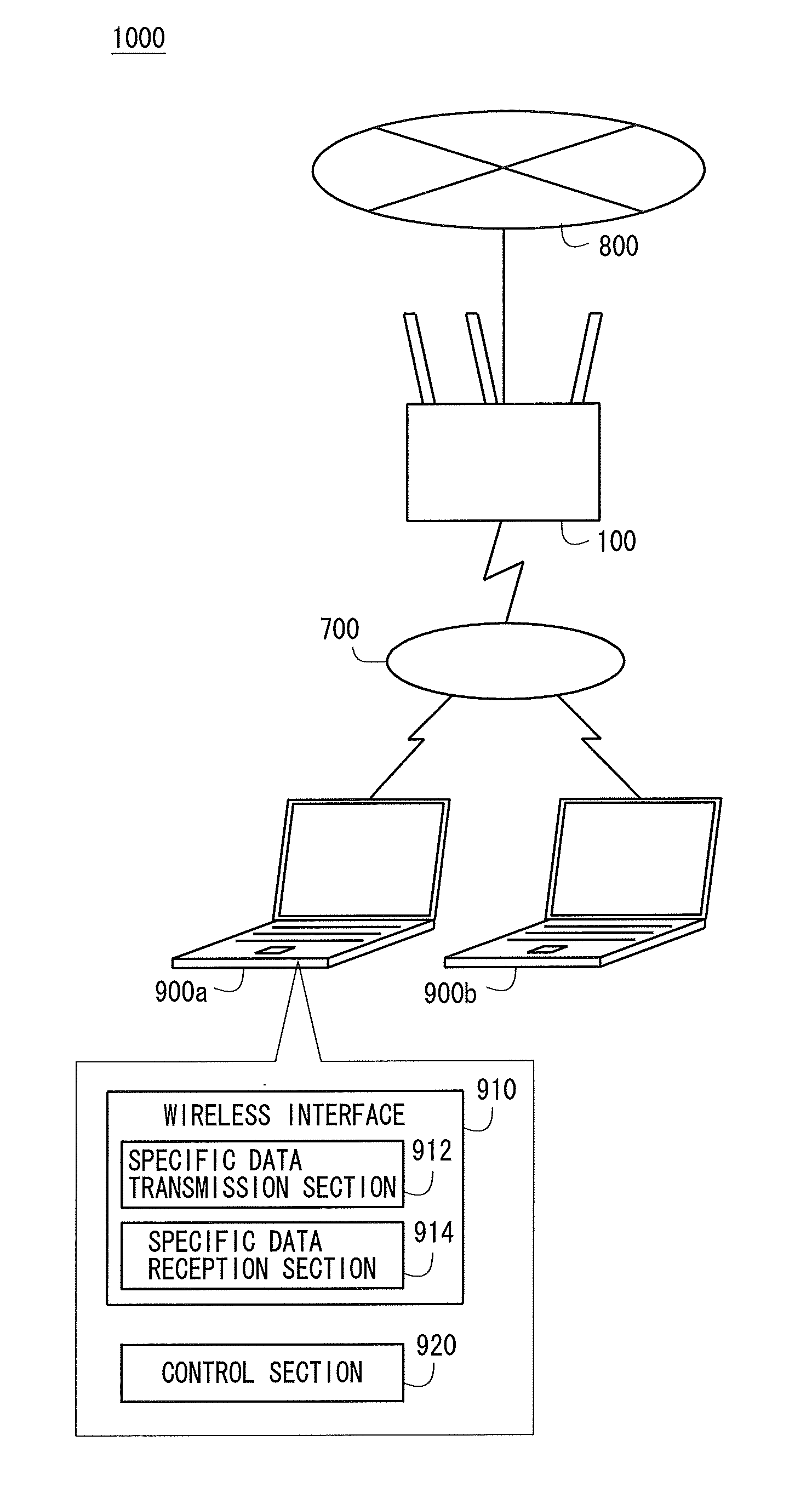

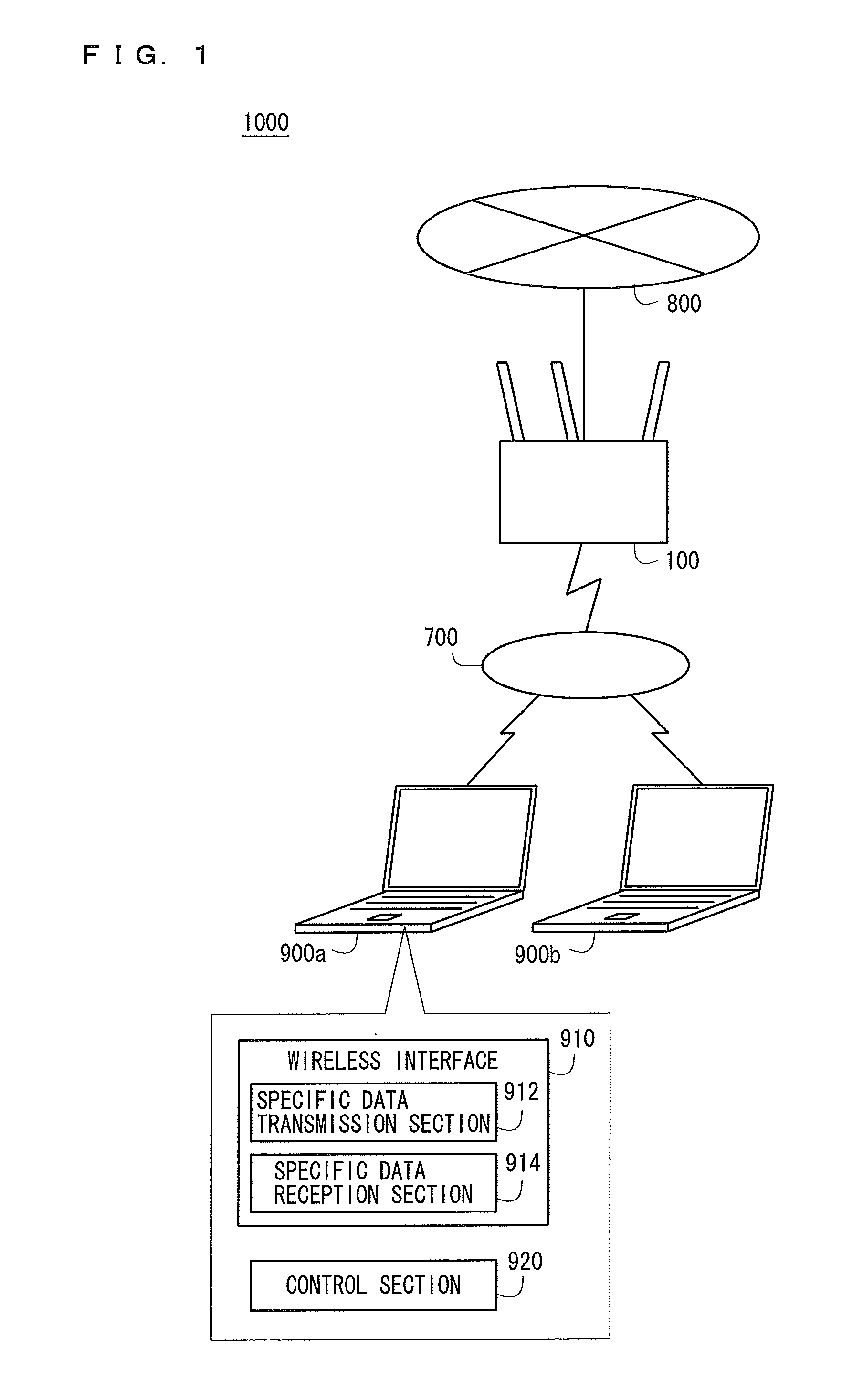

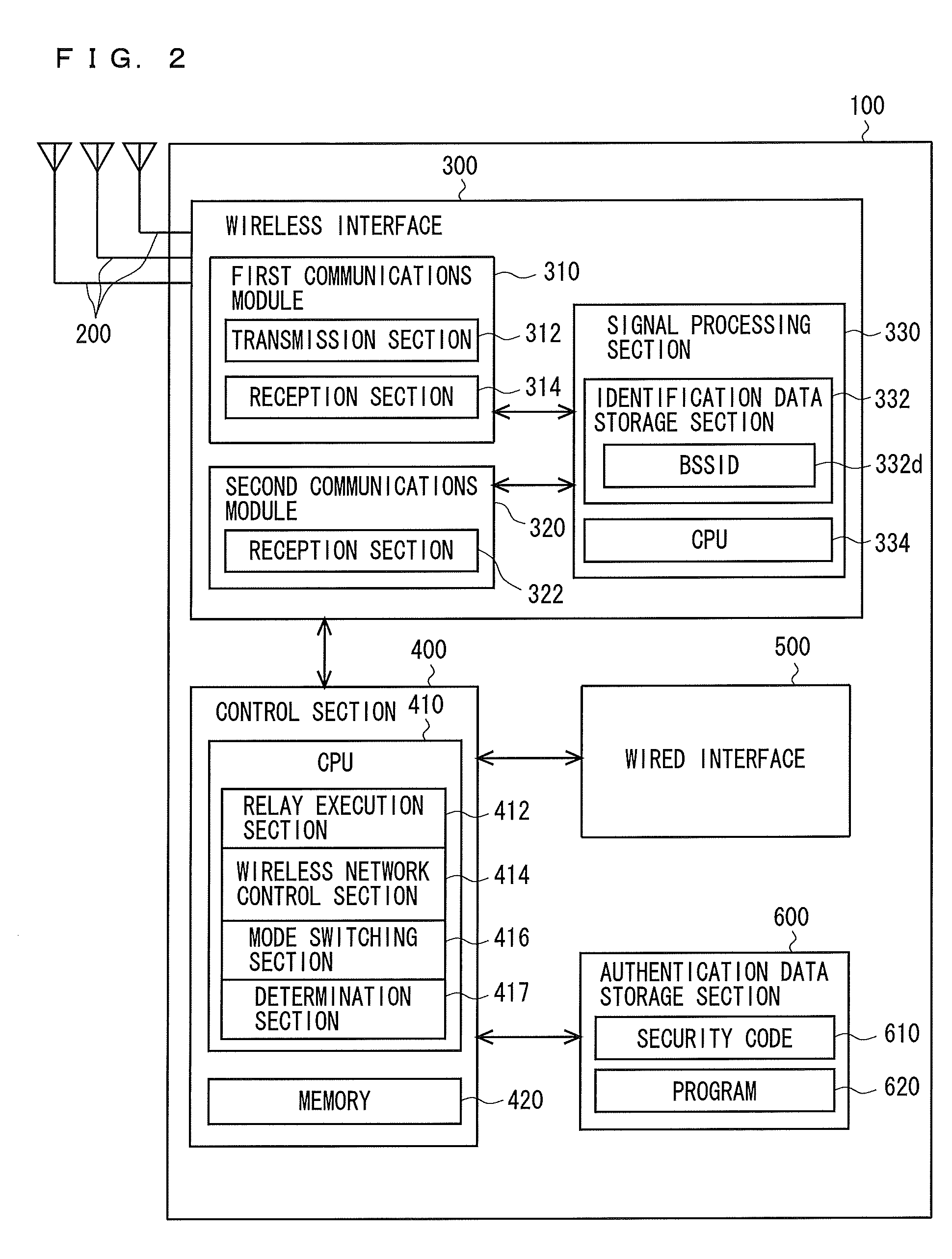

Communications device for performing wireless communications, wireless communications system, wireless communications method, and storage medium

InactiveUS20120026996A1Improve usabilityPower managementEnergy efficient ICTCommunications systemOperation mode

A communications device for performing wireless communications includes: a data receiving section for receiving data by wireless communications; a data transmitting section for transmitting data by wireless communications; a mode switching section for switching an operation mode of the communications device between a first mode in which power is supplied to the data transmitting section, and a second mode in which power consumption in at least the data transmitting section is minimized over that in the first mode; and a determination section for determining whether the data receiving section has received designated data. The mode switching section switches the operation mode of the communications device from the second mode to the first mode if, in a state in which the communications device is in the second mode, the determination section has determined that the data receiving section has received the designated data.

Owner:BUFFALO CORP LTD

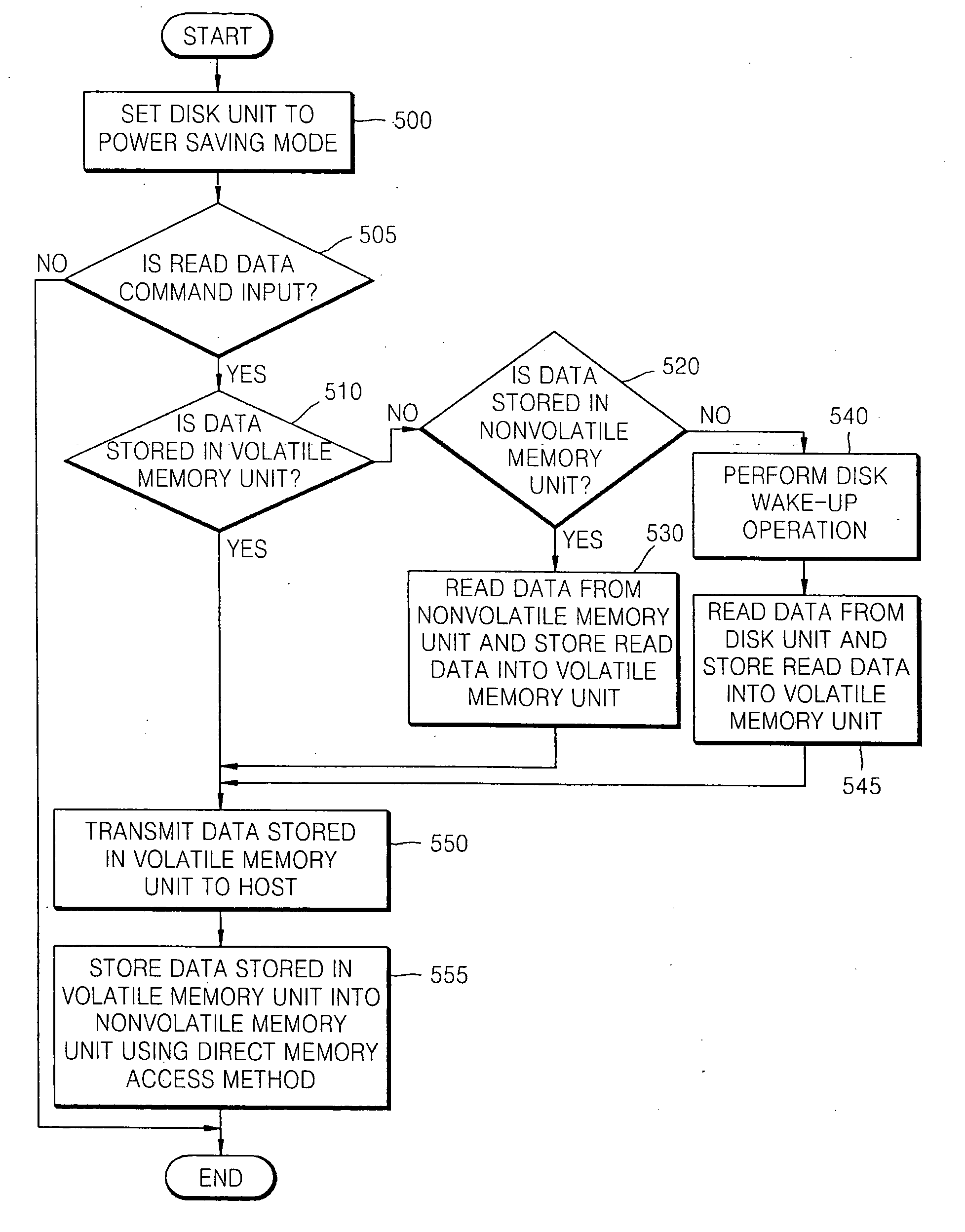

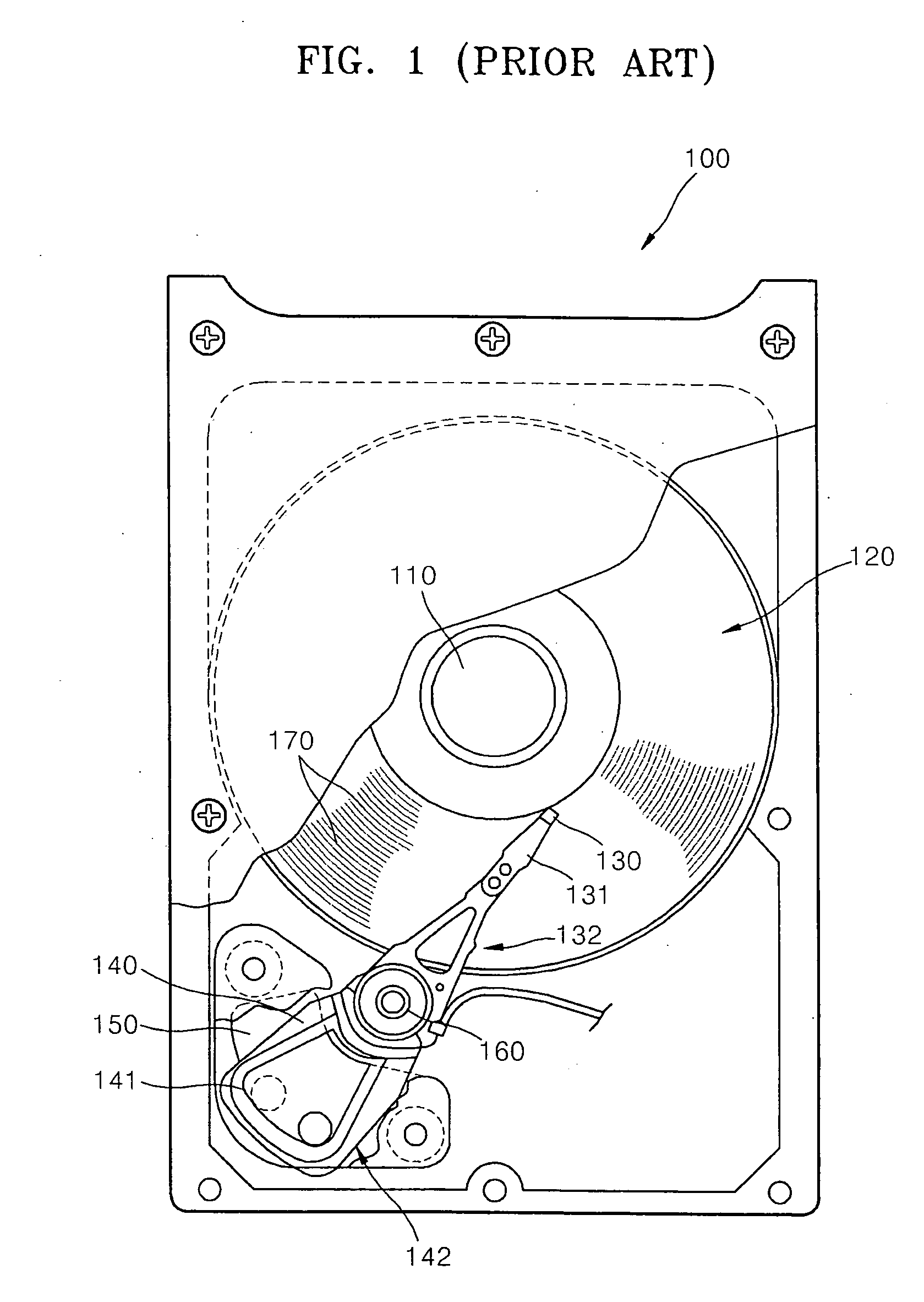

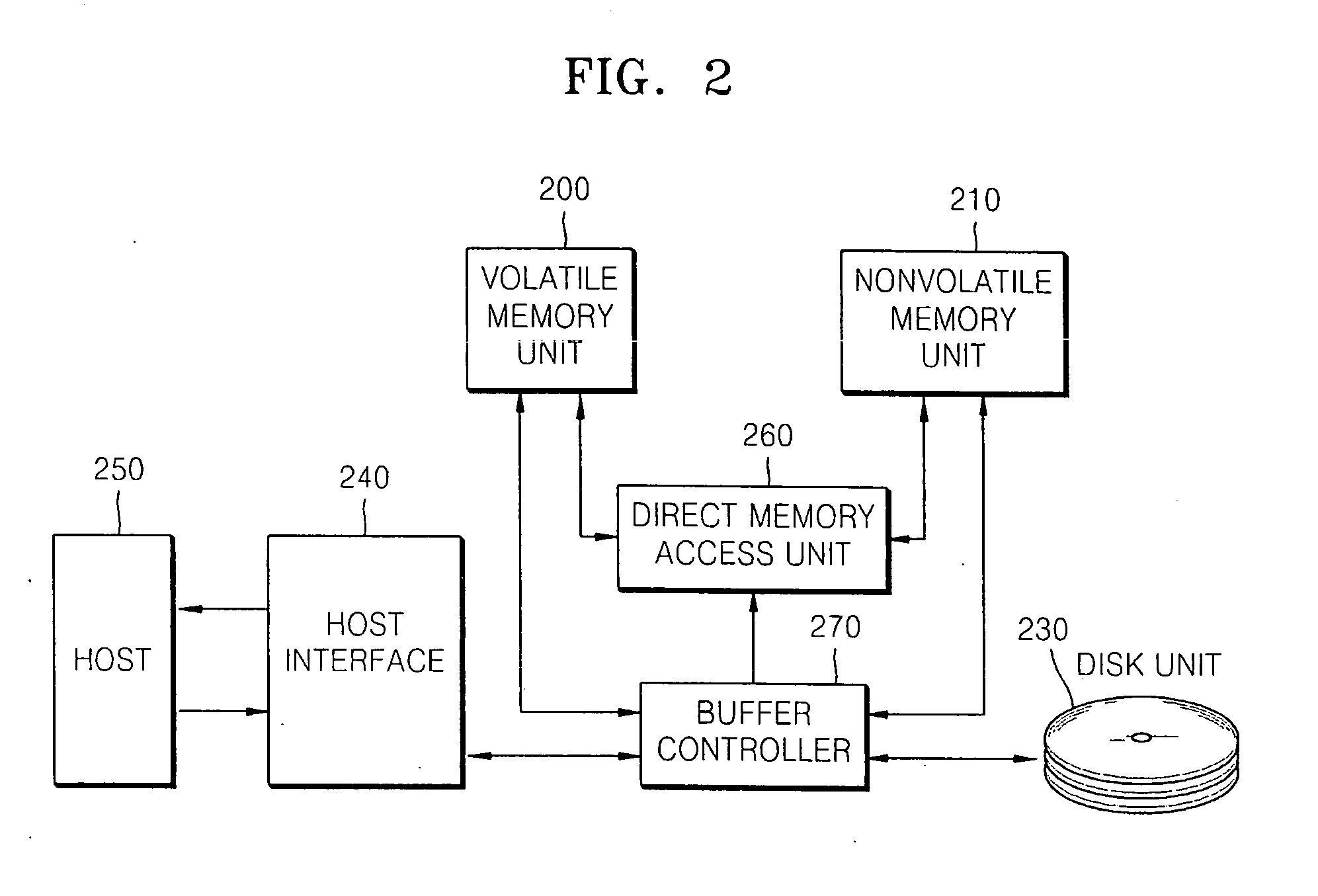

Hybrid disk drive and method of controlling data therein

ActiveUS20070174546A1Minimize power consumptionOptimized for speedEnergy efficient ICTRecord information storageData storingData transmission

A hybrid disk drive is utilized to achieve speed optimization and minimization of power consumption by installing a flash memory device in the hybrid disk drive and efficiently controlling data flow between the flash memory device and the disk drive. The hybrid disk drive includes a, volatile memory unit, a nonvolatile memory unit, a disk unit, a host interface and a buffer controller disposed between the volatile memory unit, the nonvolatile memory unit, the host interface and the disk unit. The disk unit stores data by magnetizing the surface of the disk. The host interface receives a read data command from the host and transmits the data stored in the volatile memory unit to the host. The buffer controller is configured to read the data from the nonvolatile memory unit if the data is not stored in the volatile memory unit when the read data command is received from the host interface. The buffer controller also controls the storing of the read data in the volatile memory unit if the data is stored in the nonvolatile memory unit. Alternatively, if the data is not stored in the nonvolatile memory unit, the controller reads the data from the disk unit and stories it in the volatile memory unit.

Owner:SAMSUNG ELECTRONICS CO LTD

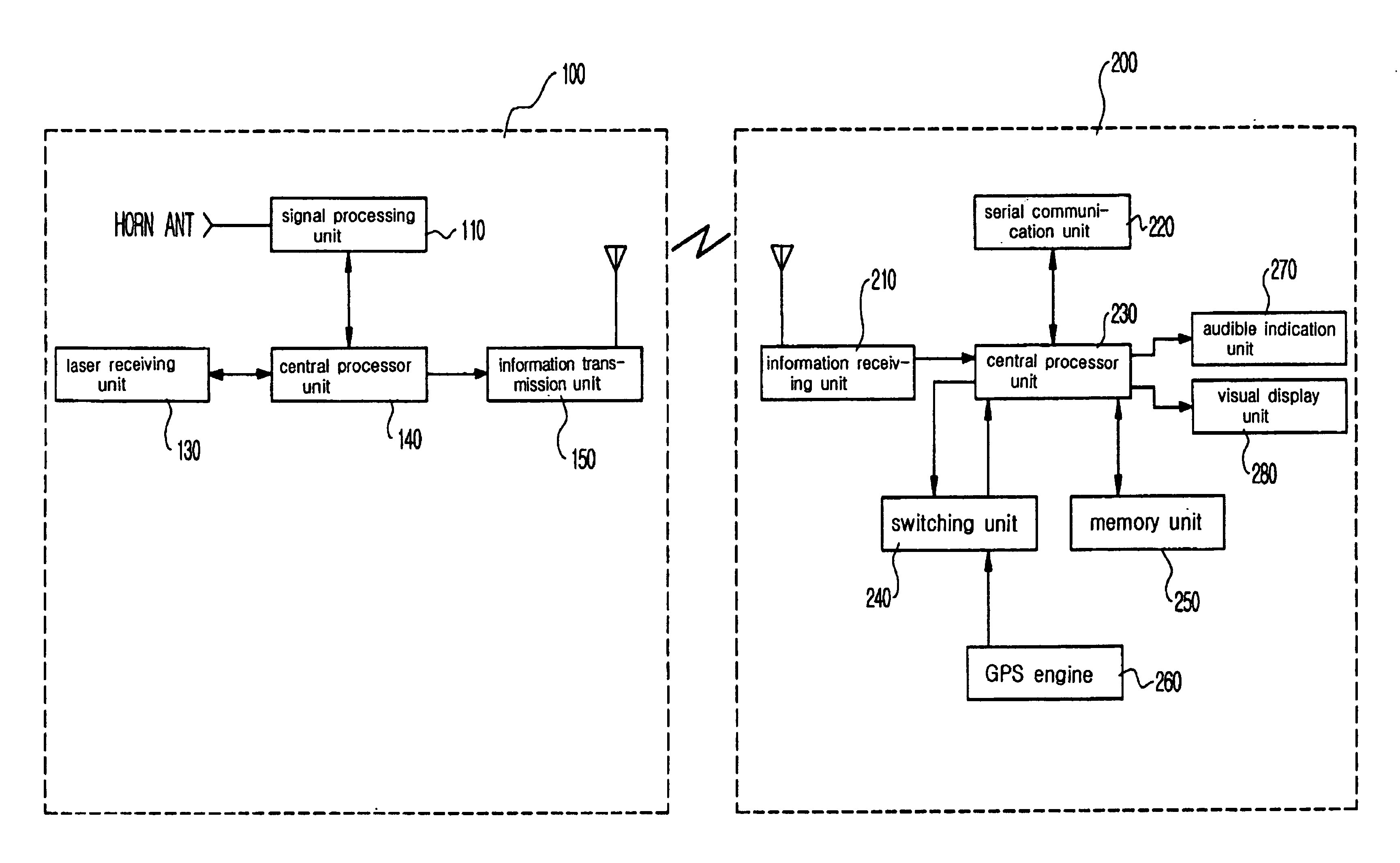

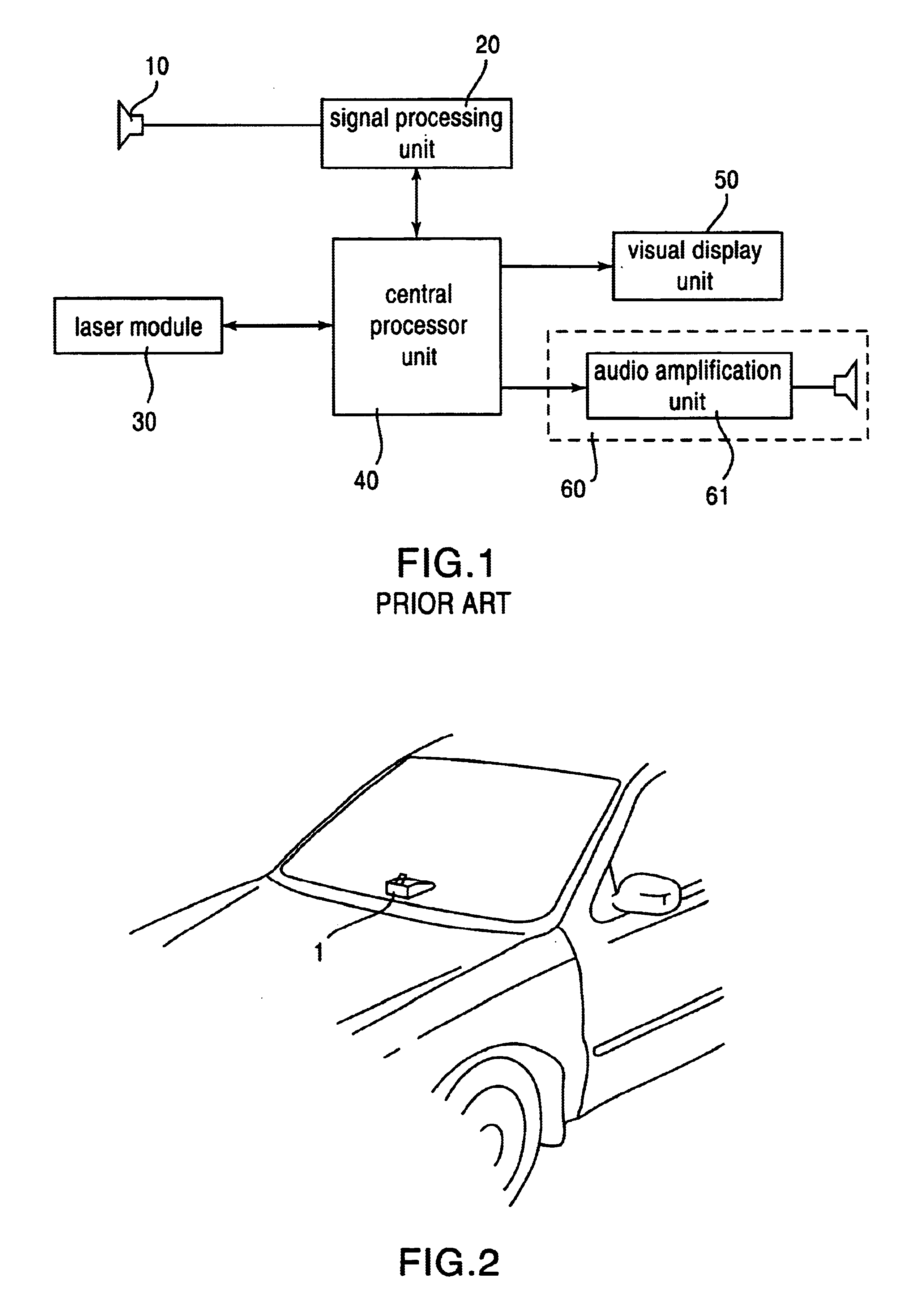

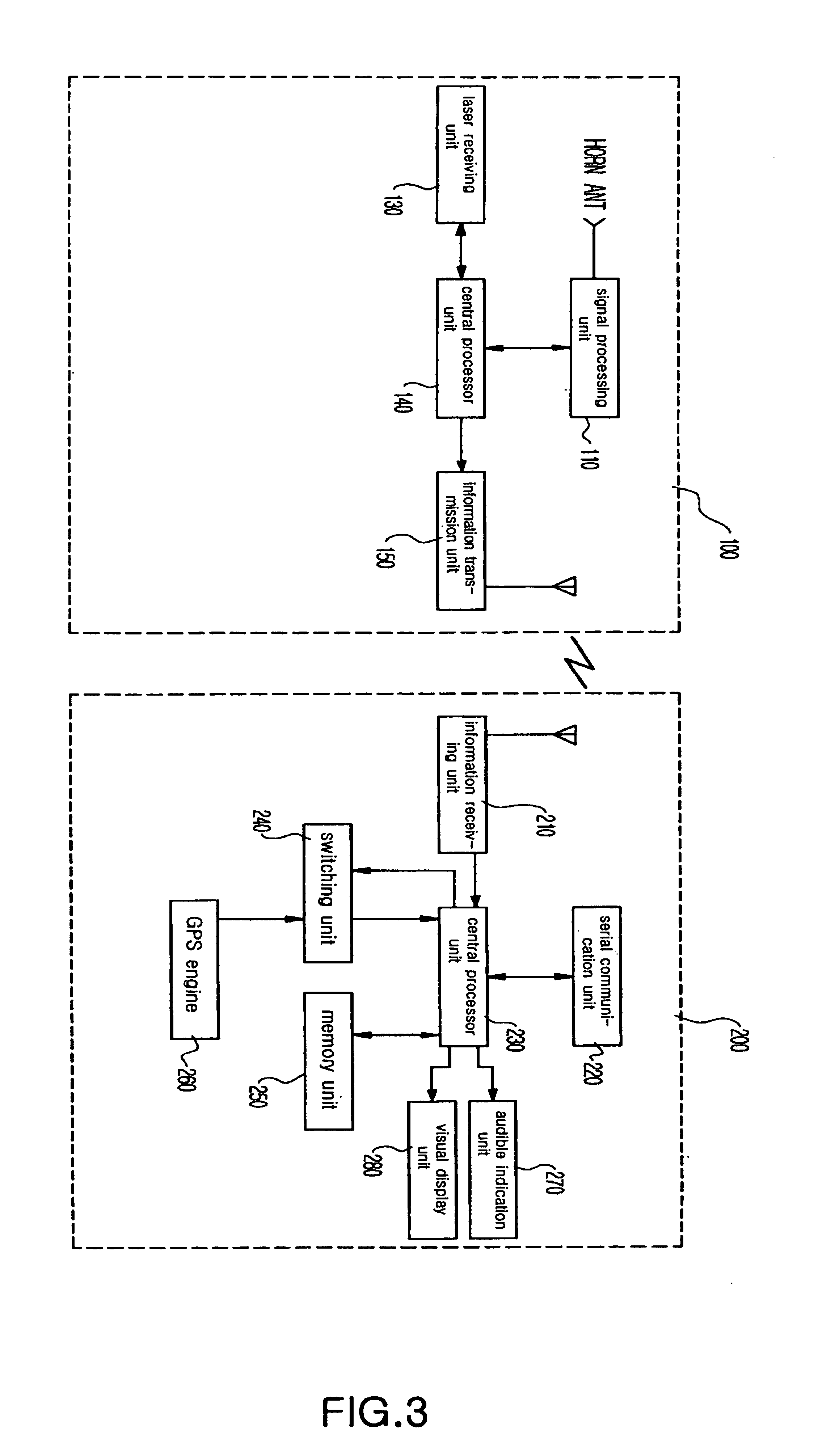

Combined radar and laser detector having GPS receiver and using wireless communication

InactiveUS6943723B2Operation be restrictRoad vehicles traffic controlPosition fixationMobile vehiclePhase detector

The present invention relates generally to a combined radar and laser detector that enables a driver to drive safely and, more particularly, to a combined radar and laser detector, in which a signal receiving module for receiving various kinds of signals including traffic information and an information display module for informing a driver of the signals are separated, the signal receiving module and information display module are constructed to communicate with each other using wireless communication, and the information display module is integrated with a Global Positioning System (GPS) receiver detecting GPS data related to the location and speed of a moving vehicle, so that the combined radar and laser detector can not only provide accurate traffic information to the driver, but also allow the installation thereof to be easy, the miniaturization thereof to be achieved, and power consumption to be minimized.

Owner:CHANNEL TECH

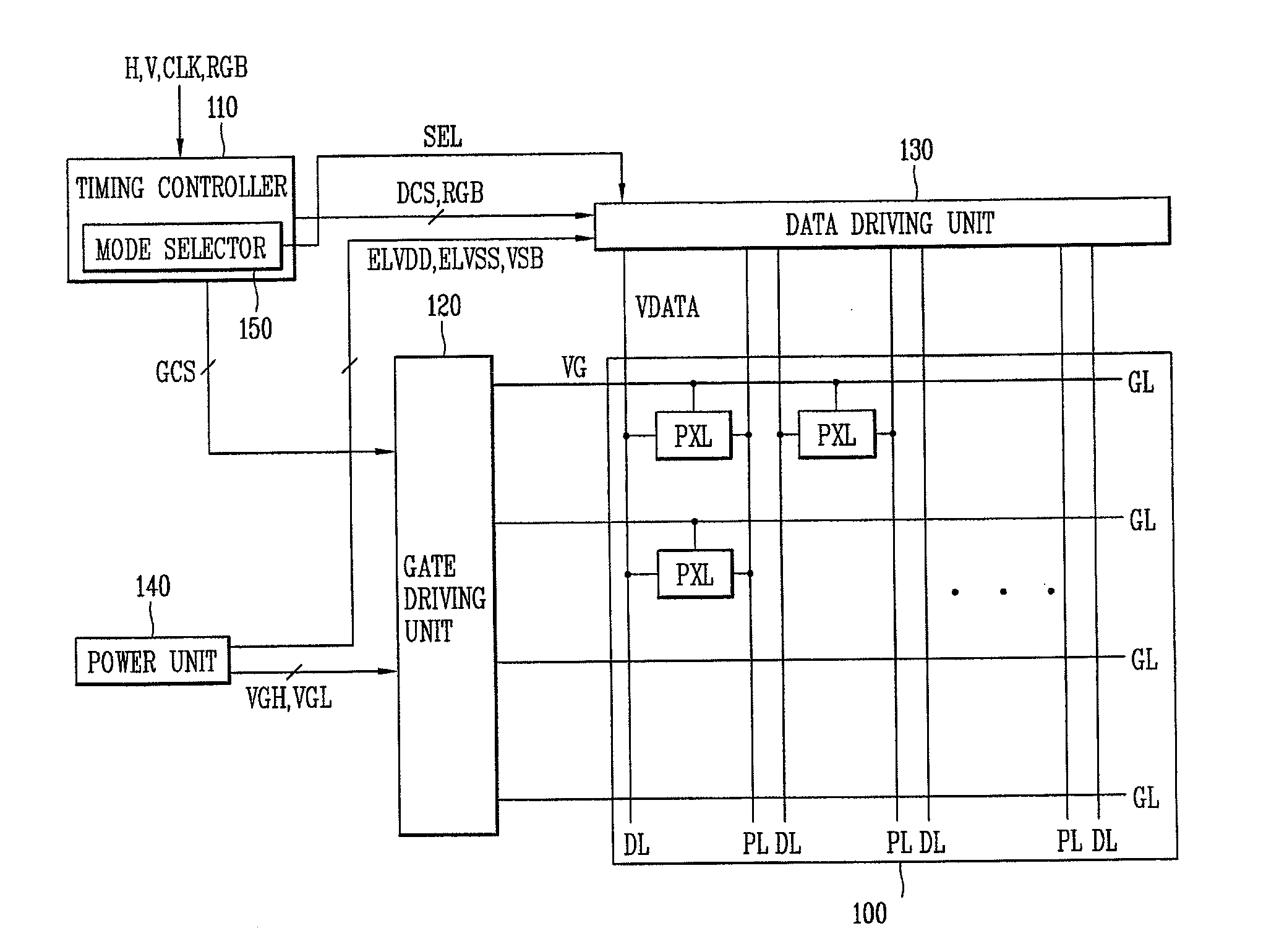

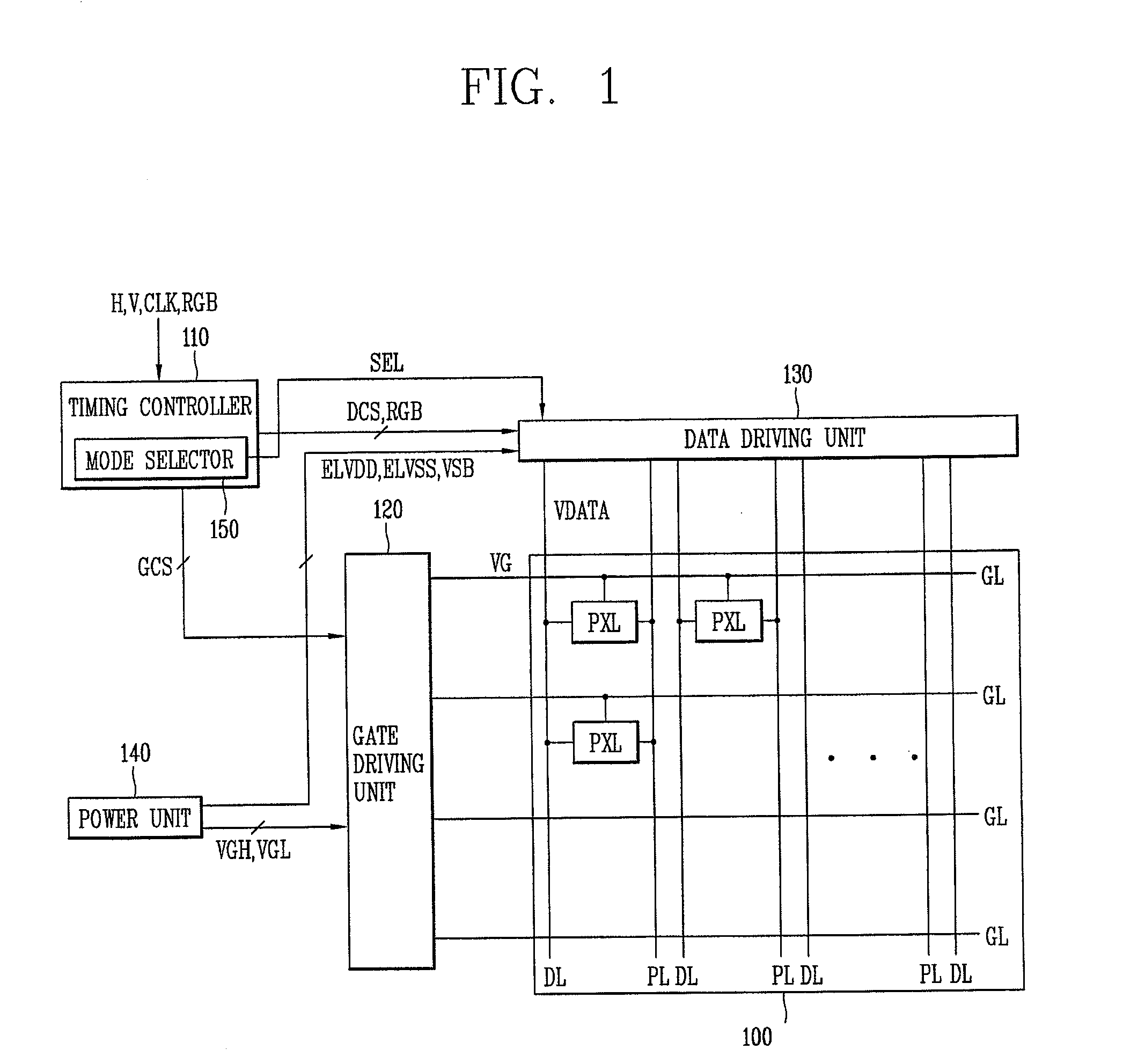

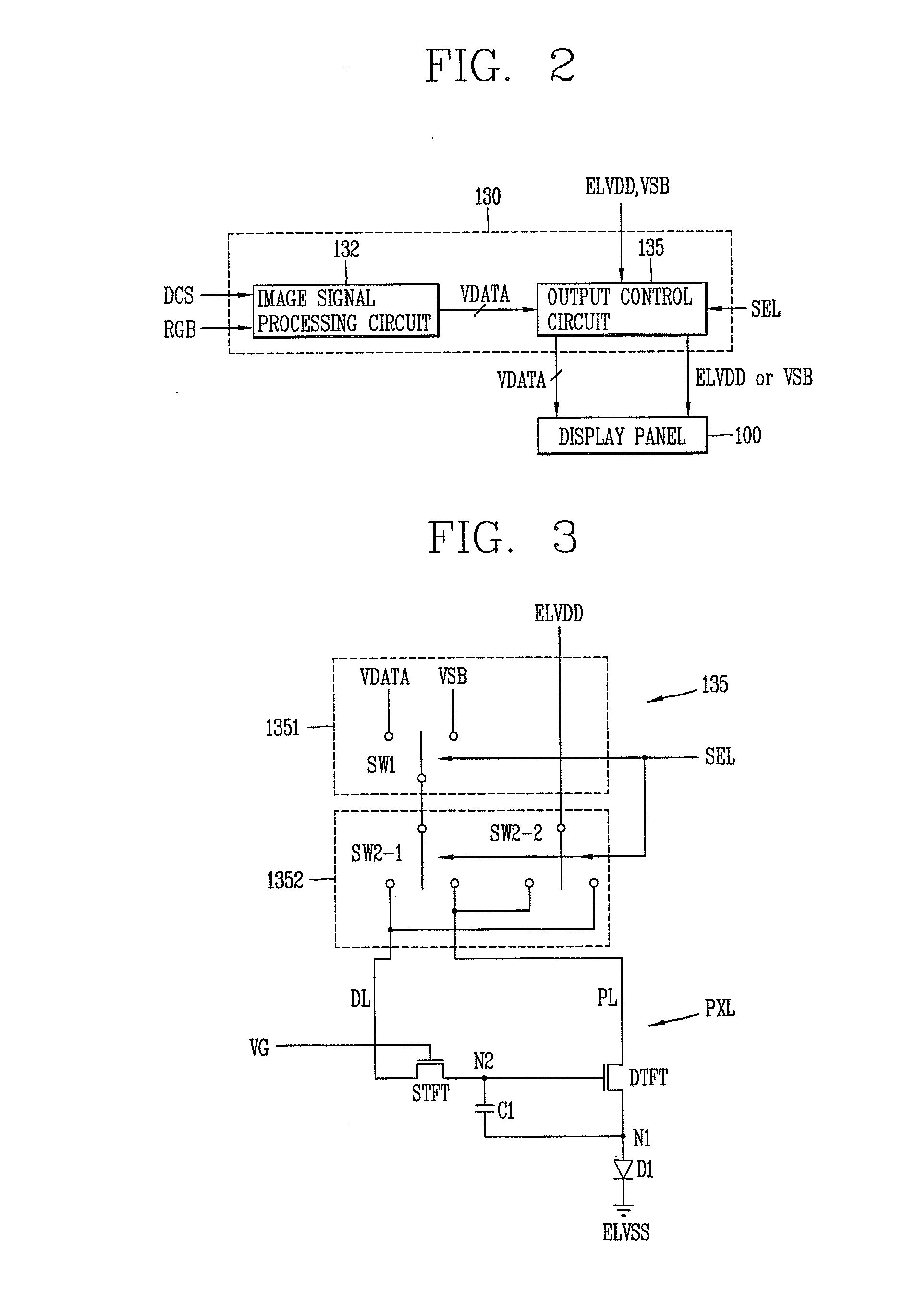

Organic light-emitting diode display, circuit and method for driving thereof

ActiveUS20130293600A1Minimize power consumptionDigital data processing detailsCathode-ray tube indicatorsNormal modeDisplay device

According to the present invention, there is discussed an organic light-emitting diode display device. More particularly, the present invention relates to an organic light-emitting diode display device for minimizing power consumption in a standby mode in which no images are displayed but not in a normal mode in which typical images are displayed, and a driving circuit and method thereof. An organic light-emitting diode according to an embodiment of the present invention may control a drain-source voltage (VDS) of the drive transistor provided in the pixel, thereby having an effect of capable of minimizing power consumption when in a standby mode.

Owner:LG DISPLAY CO LTD

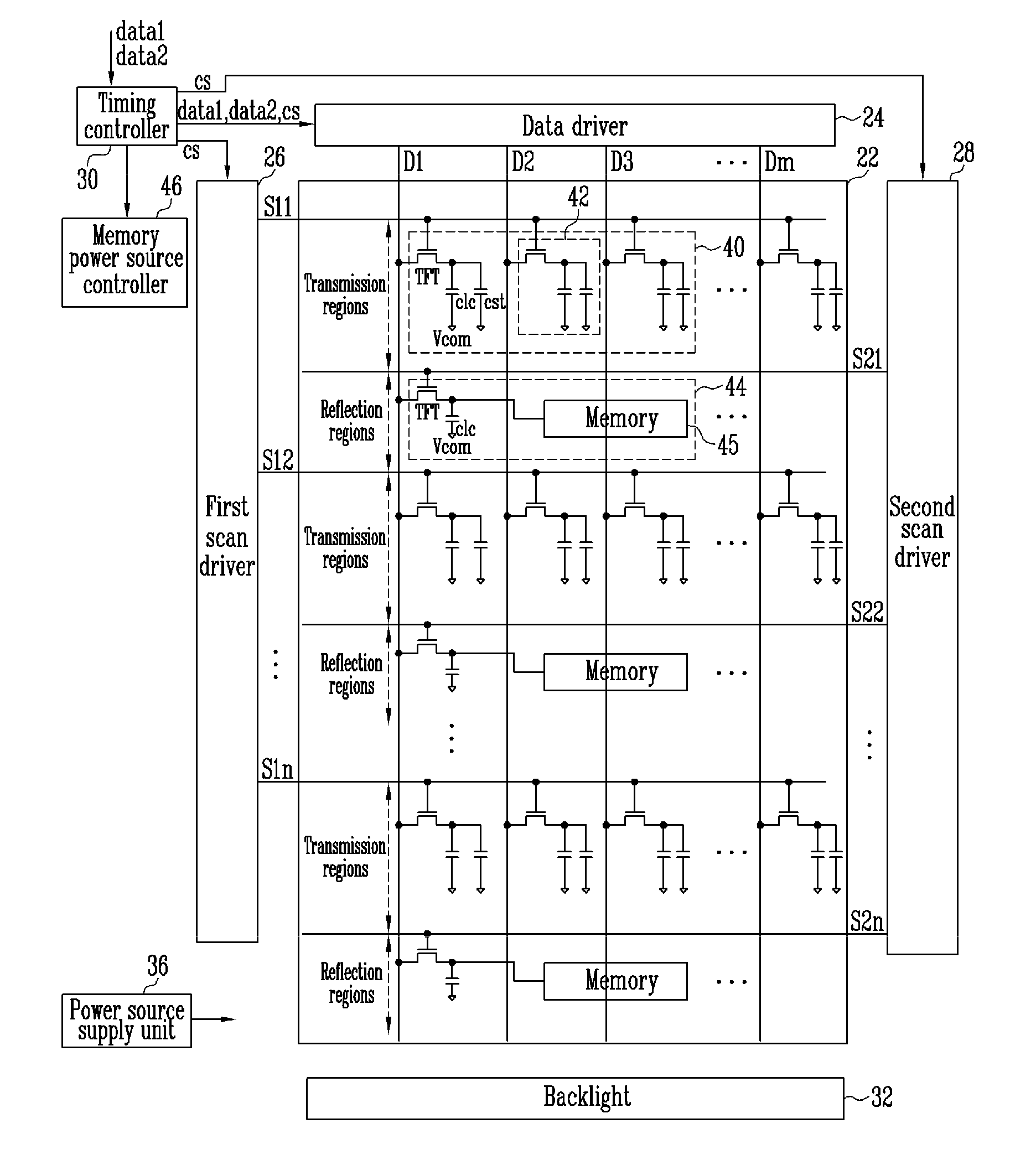

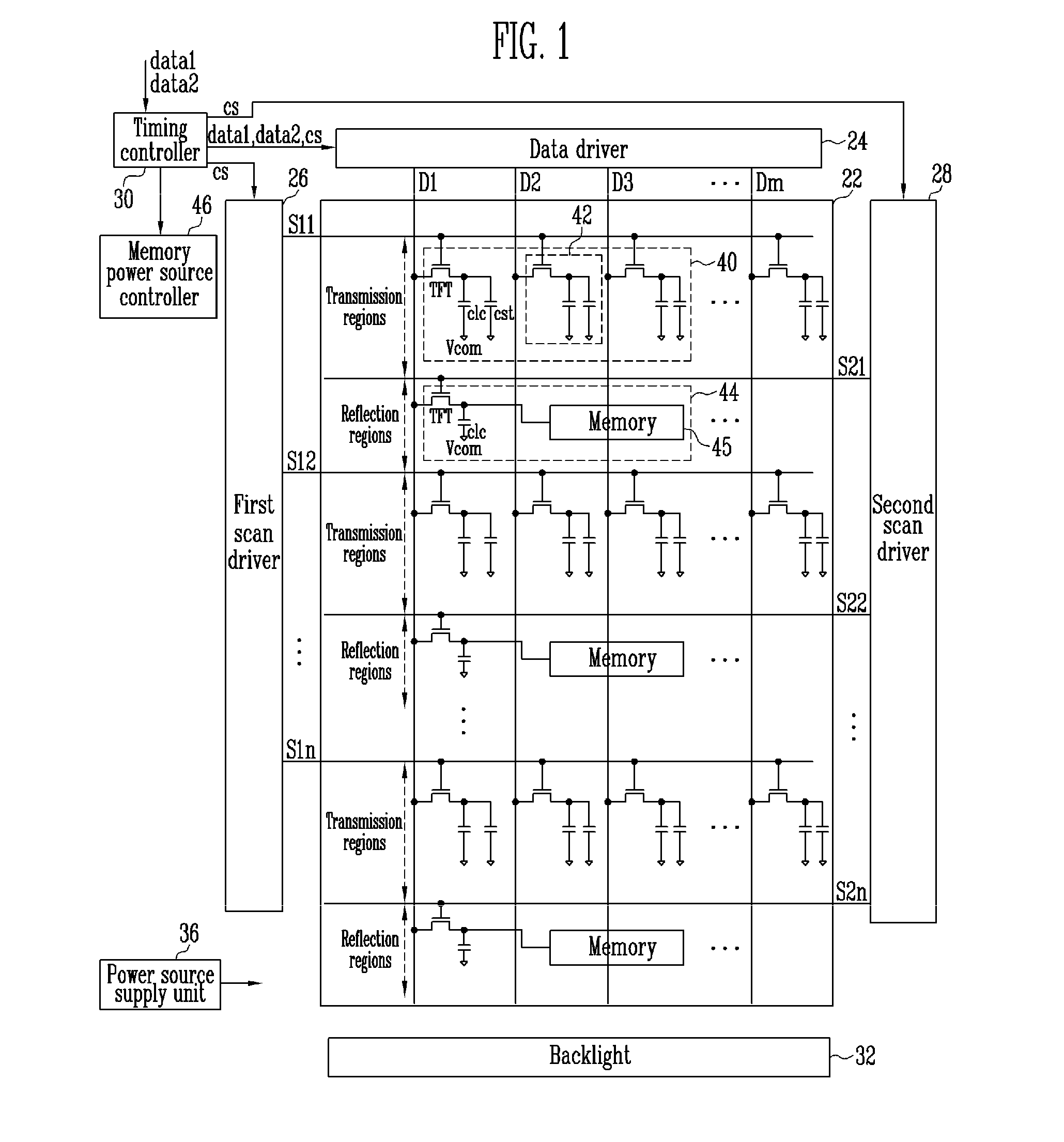

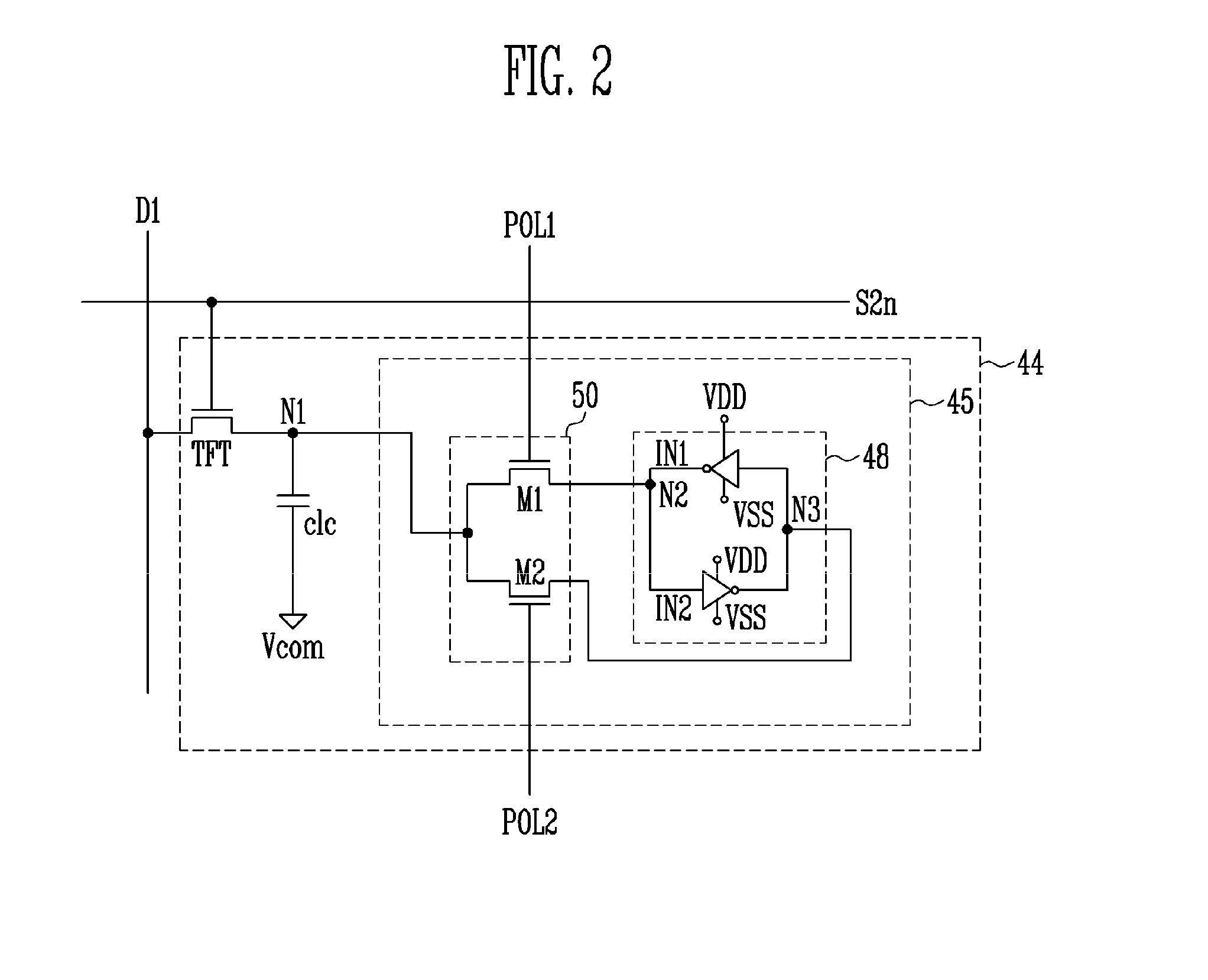

Liquid crystal display and method of driving the same

InactiveUS20110193852A1Minimize power consumptionReduce power consumptionCathode-ray tube indicatorsNon-linear opticsLiquid-crystal displayEngineering

There is provided a liquid crystal display for minimizing power consumption. The liquid crystal display includes transmission regions formed in a liquid crystal panel in units of horizontal lines, reflection regions positioned between the transmission regions, first sub pixels formed in the transmission regions, and second sub pixels formed in the reflection regions. A total number of the second sub pixels is smaller than a total number of the first sub pixels.

Owner:SAMSUNG DISPLAY CO LTD

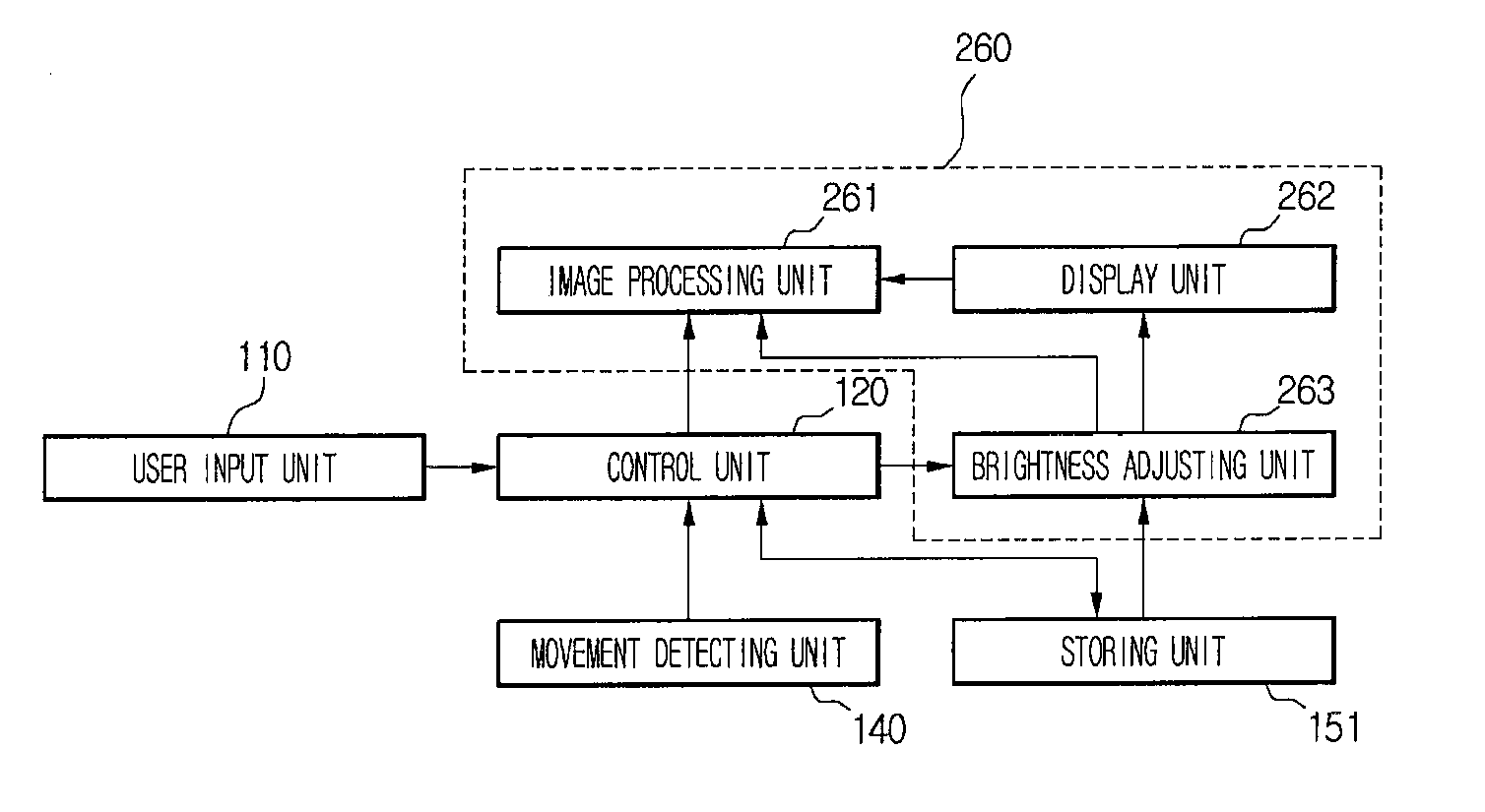

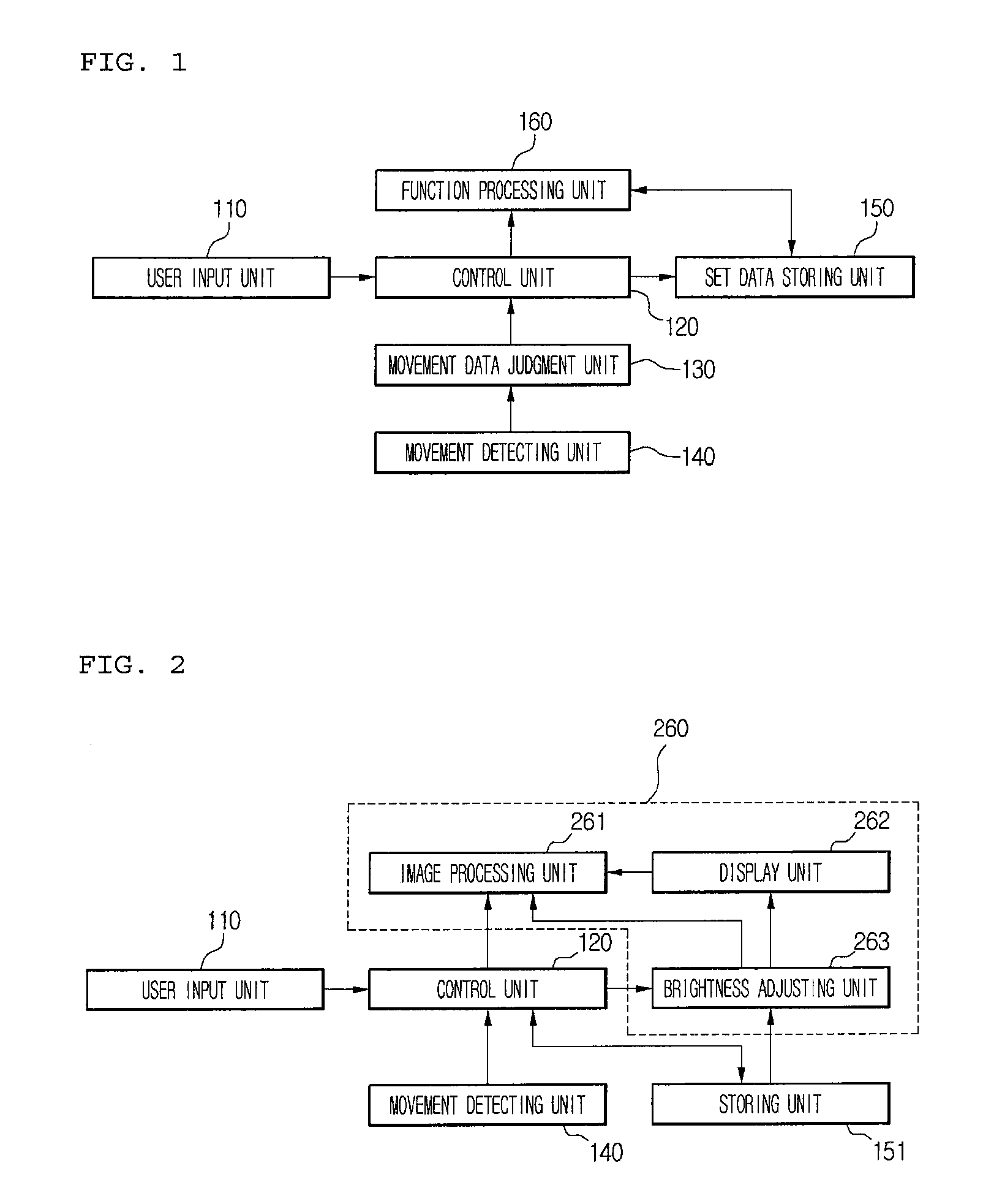

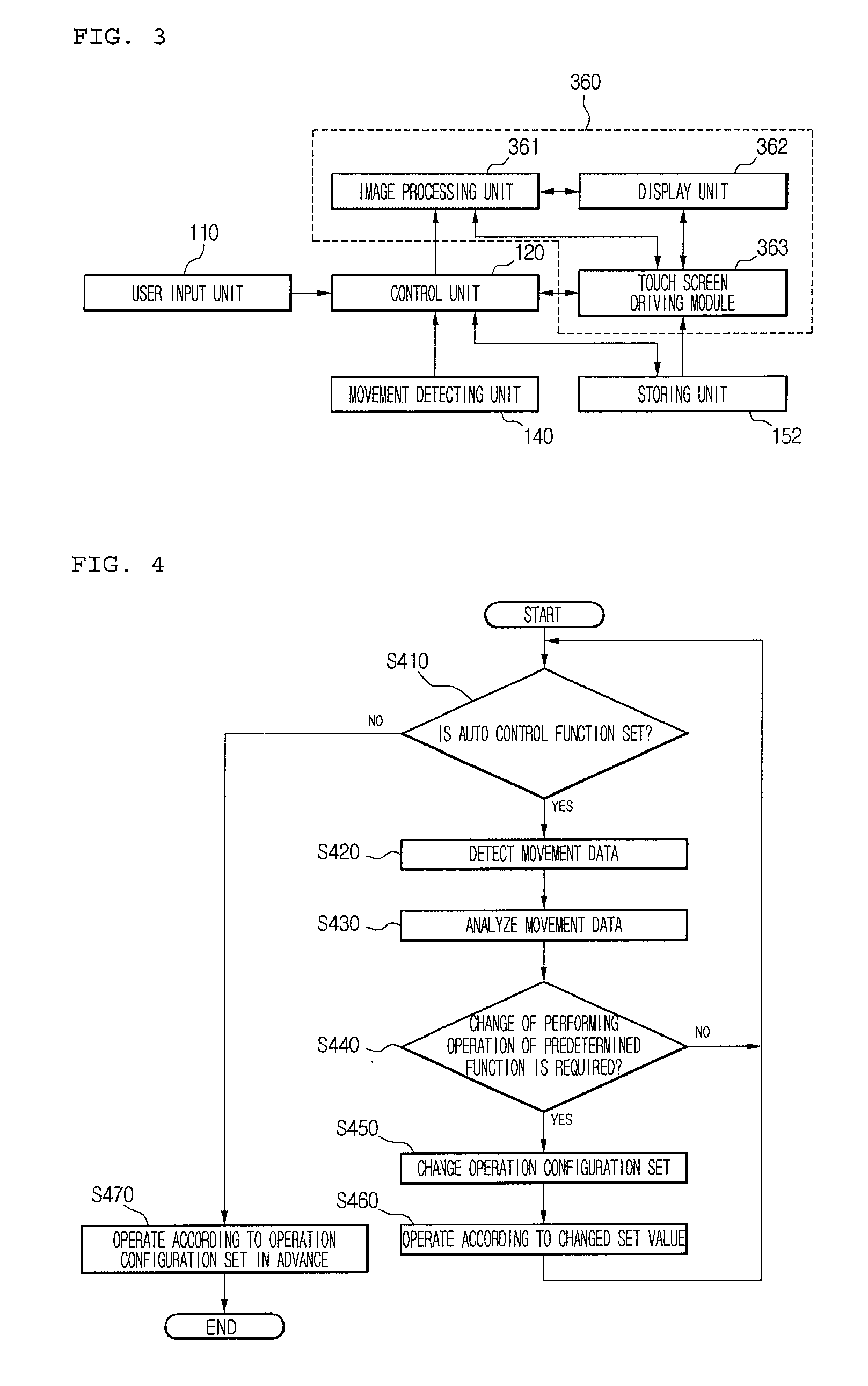

Controlling operation of information processing device using movement data

InactiveUS20070288779A1Reduce display brightnessMinimize power consumptionEnergy efficient ICTVolume/mass flow measurementInformation processingData control

An apparatus and a method for controlling an operation of an information processing device using movement data of the information processing device or a peripheral device are provided. An operation configuration variable set value for performing a predetermined function of the information processing device is changed according to movement data of the information processing device or the peripheral device detected by a movement detecting unit. After that, a predetermined function provided by the information processing device is automatically enabled or disabled, so that power consumption of a battery is minimized and user convenience in using the information processing device is enhanced.

Owner:LG ELECTRONICS INC

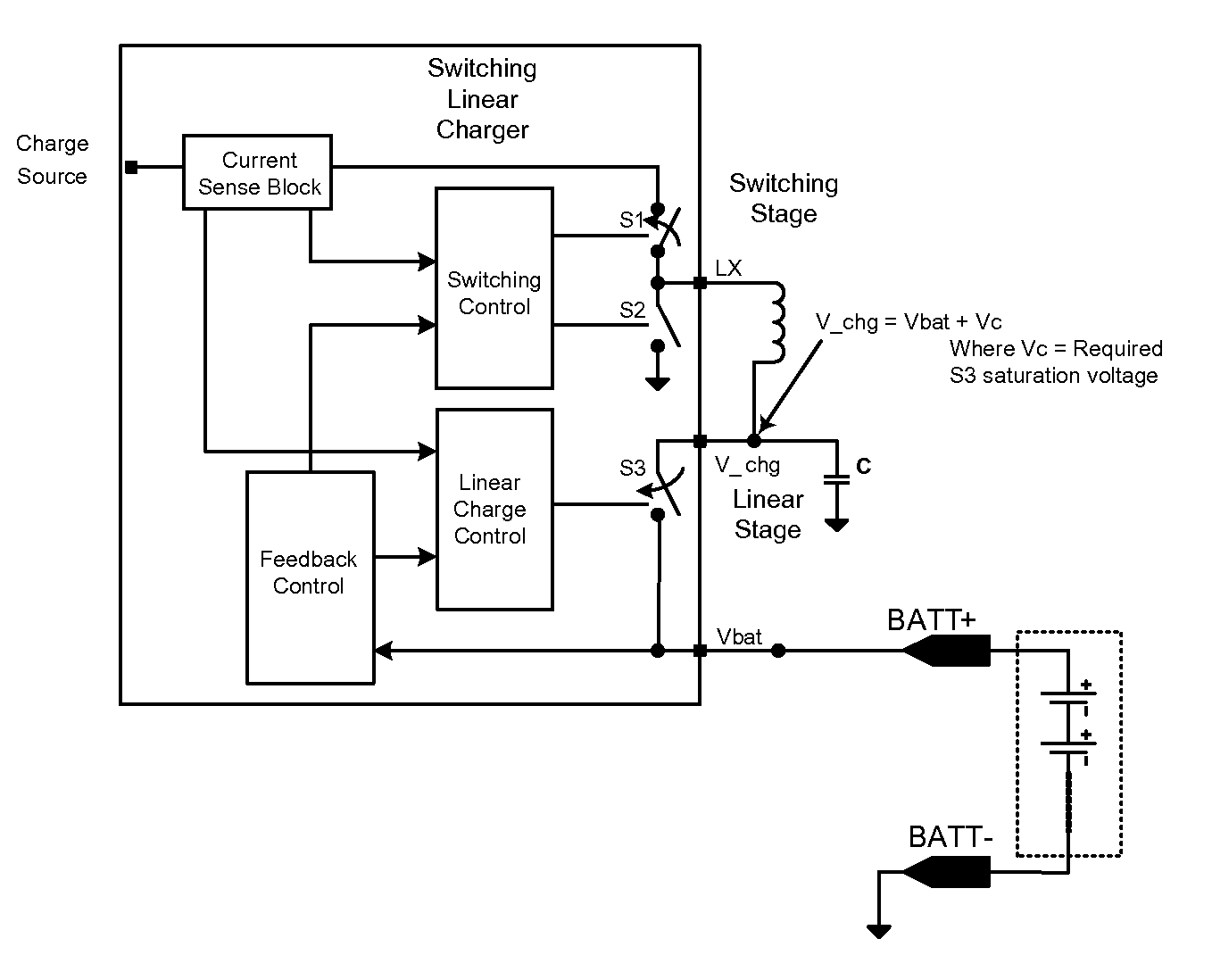

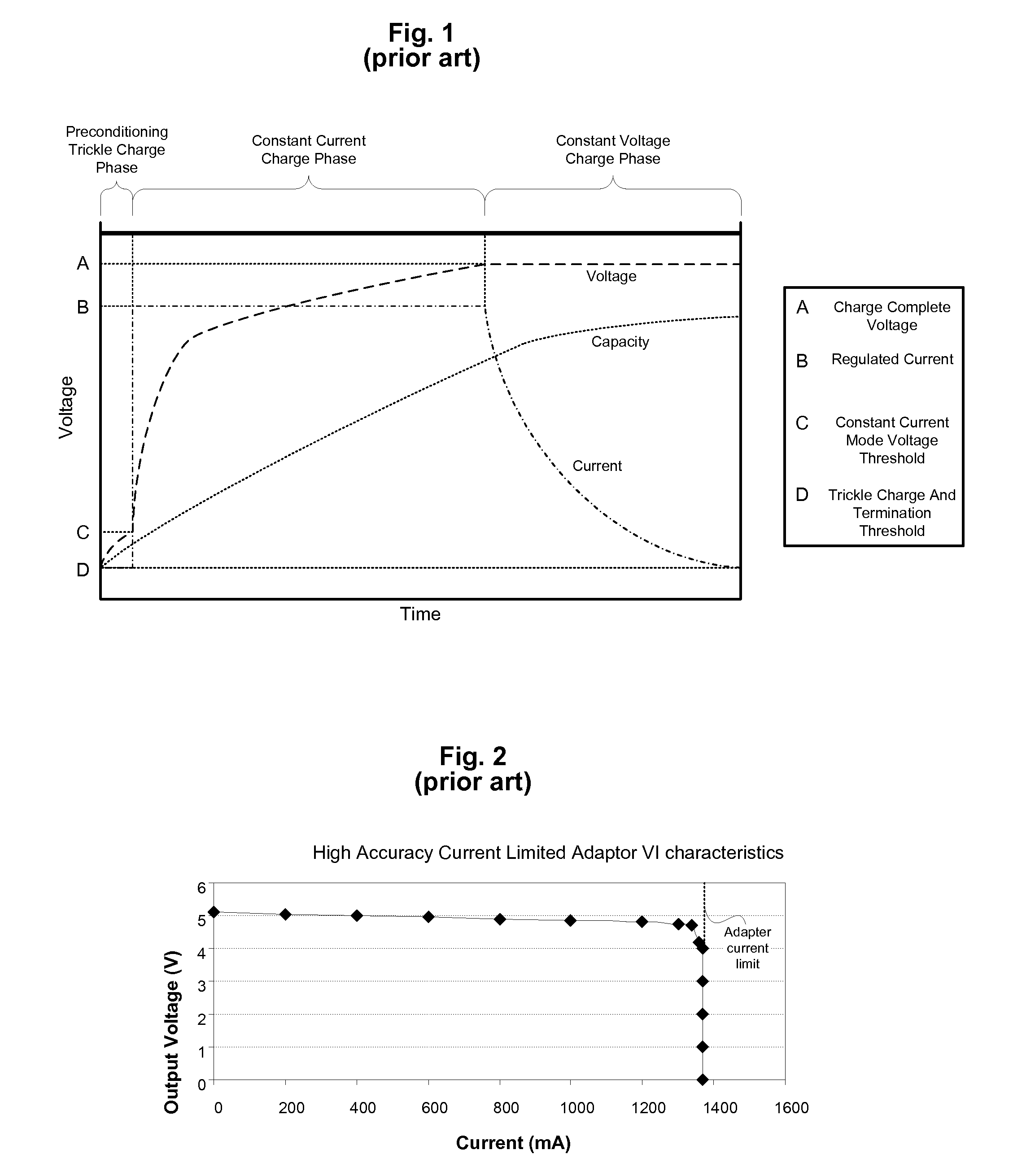

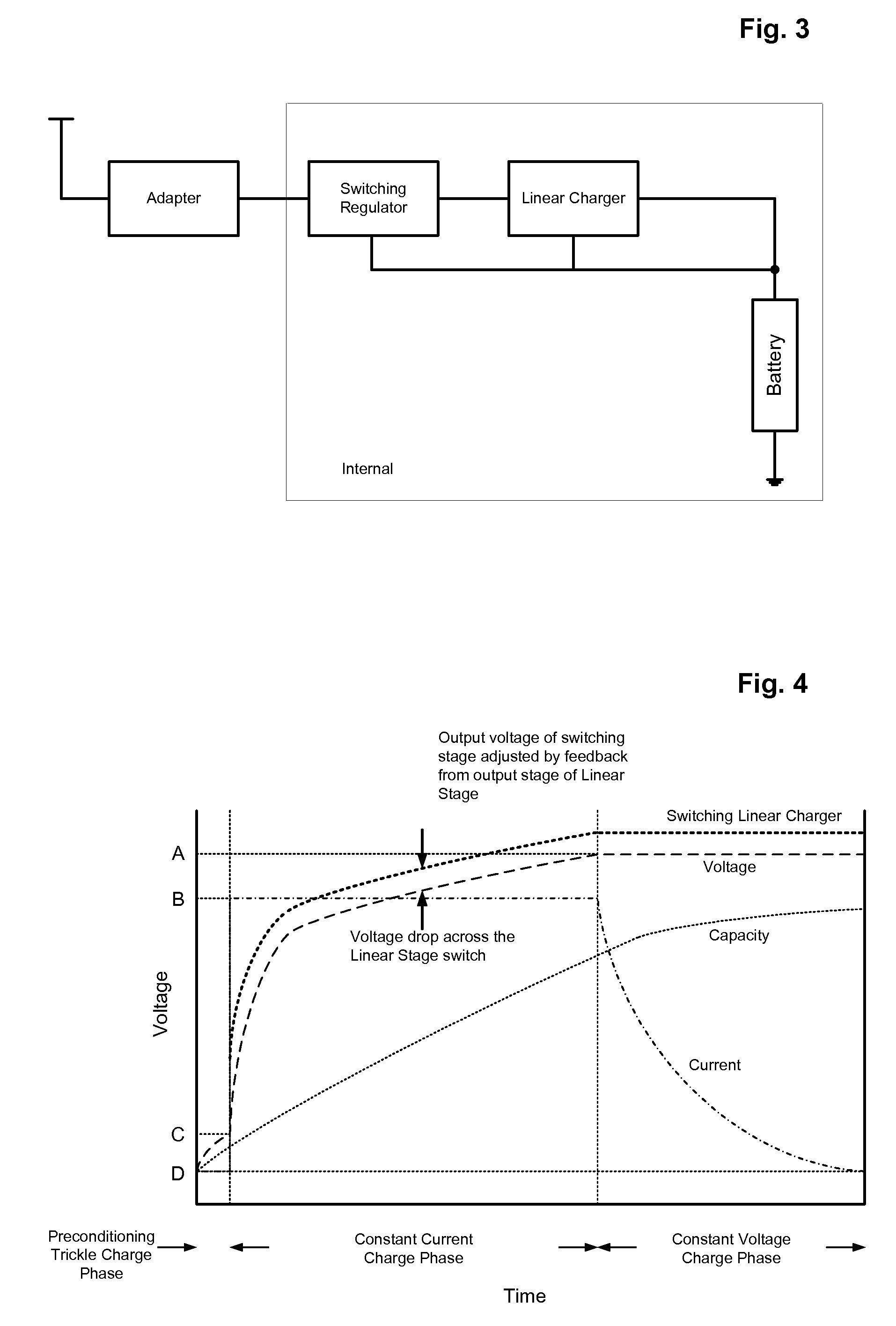

High Efficiency Switching Linear Battery Charger with Low Power Dissipation

InactiveUS20100231172A1Minimize powerHigh voltageBatteries circuit arrangementsElectric powerVoltage regulator moduleElectrical battery

A battery charger for a portable electronic device includes a linear charger to generate a substantially constant current for charging the battery and a switching voltage regulator to convert power supplied by an external adapter to a supply voltage for the linear charger. A feedback circuit controls operation of the switching voltage regulator so that the voltage supplied to the linear charger is substantially equal to the combination of the battery voltage and the drain-to-source voltage of the linear charger. In this way, power dissipation by the linear charger is minimized without requiring the use of a high accuracy current limited adapter.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

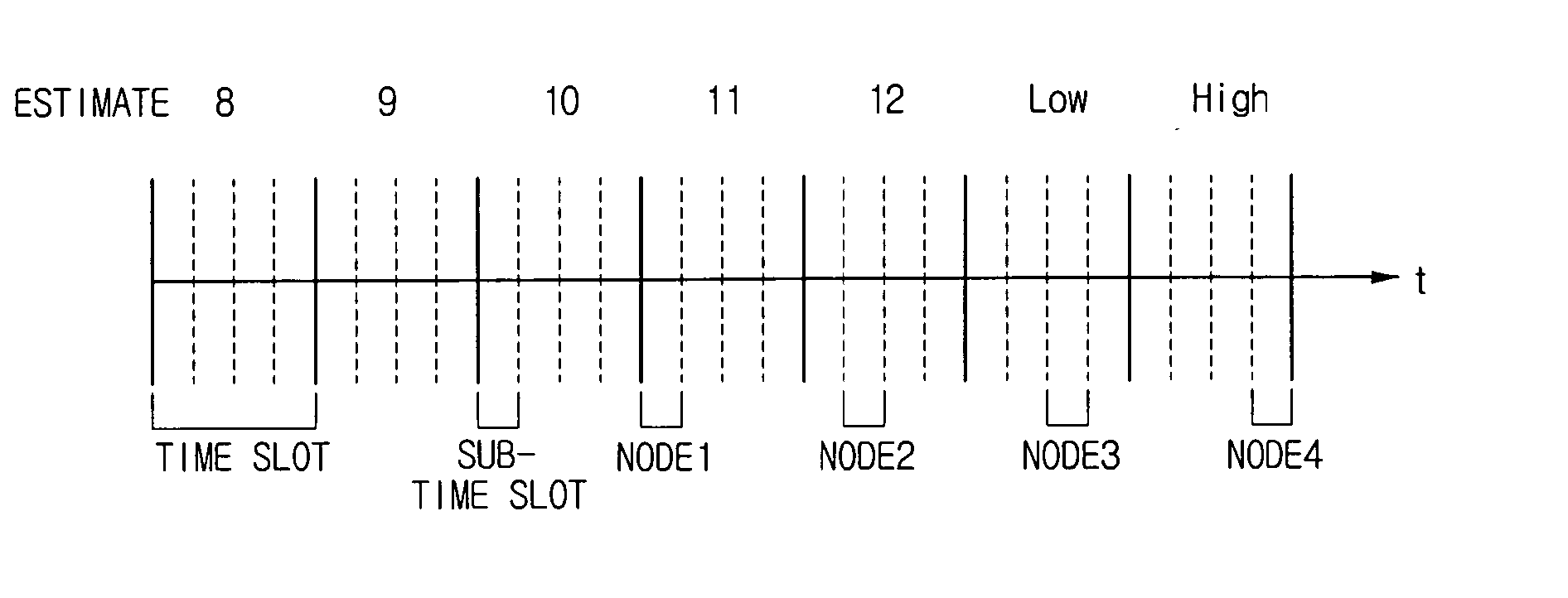

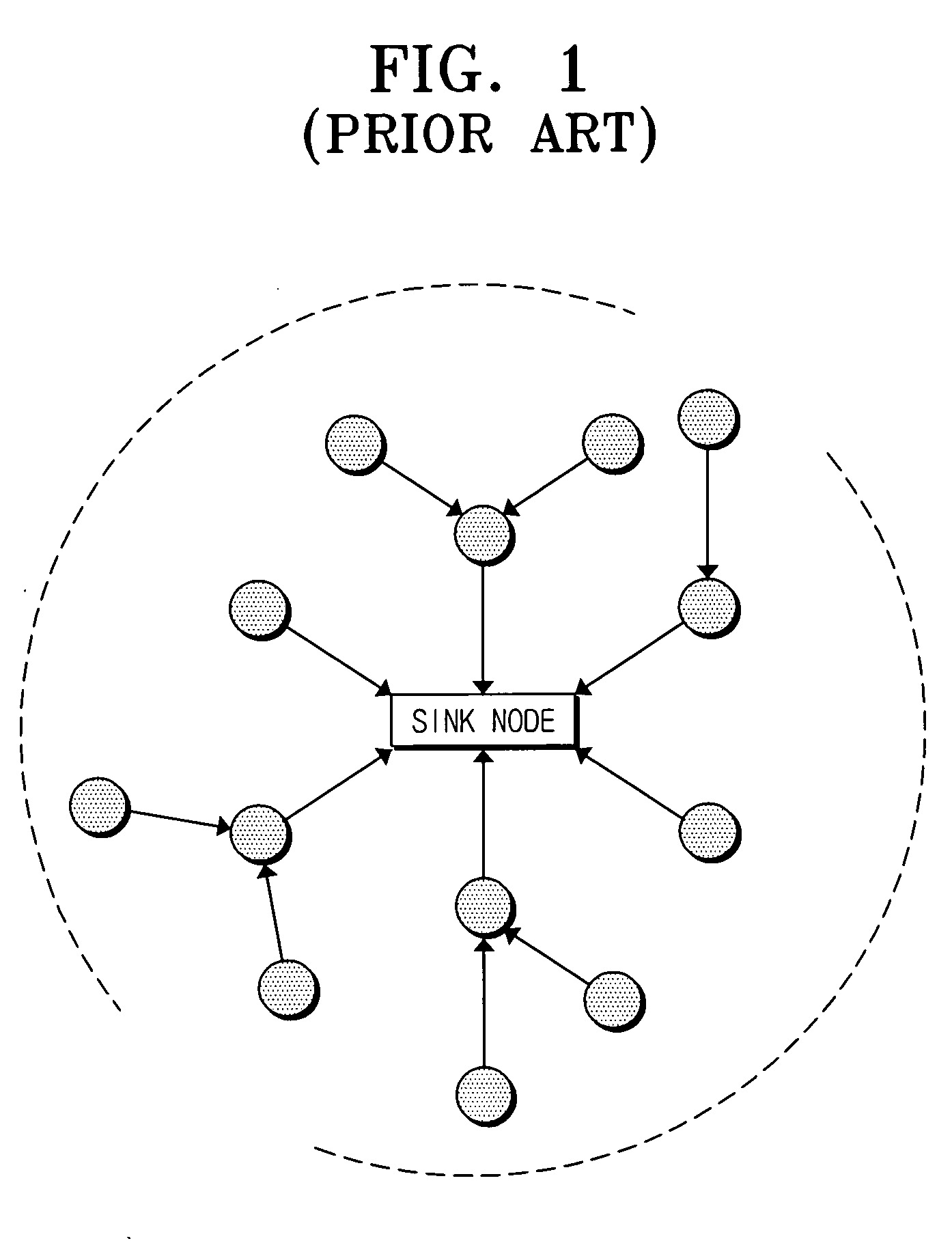

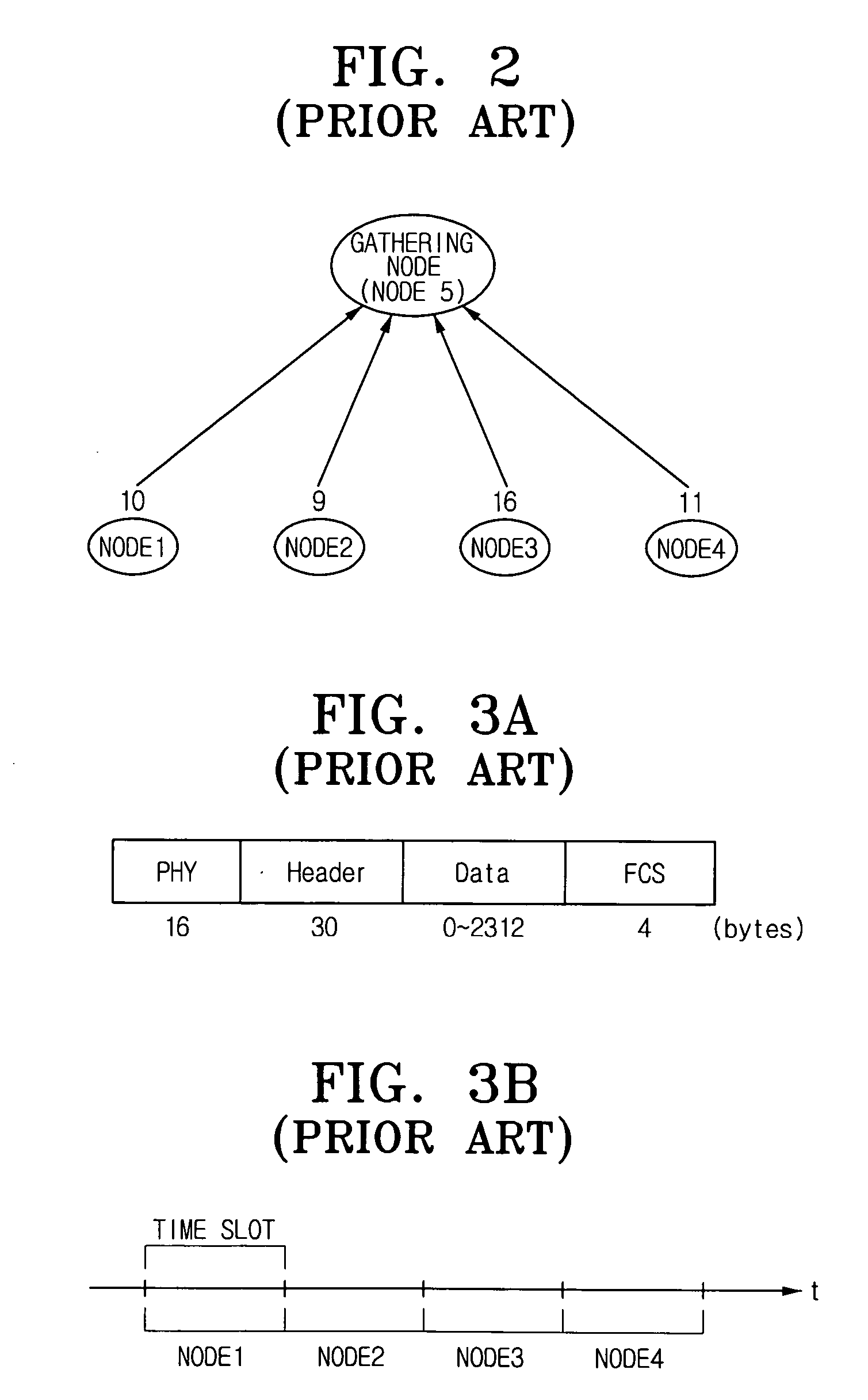

Sensor network for transmitting data and data transmitting method thereof

InactiveUS20060114940A1Avoid collisionAvoid dataPower managementMeasurement devicesInformation transmissionSensor node

Disclosed are a sensor network for transmitting data and a data transmitting method thereof. The sensor network includes one or more sensor nodes for collecting target data and transmitting the collected target data at an allocated sub-time slot among sub-time slots constituting each time slot corresponding to the collected target data, and a gathering node for allocating for the sensor nodes a sub-time slot for each of the time slots, and receiving the collected target data transmitted by the sensor nodes. Data transmission by bits reduces power consumption and does not require additional information transmission to prevent data collision. Therefore, power consumption is minimized and a plurality of sensor nodes possibly transmit data at one time, accordingly shortening transmission time.

Owner:SAMSUNG ELECTRONICS CO LTD

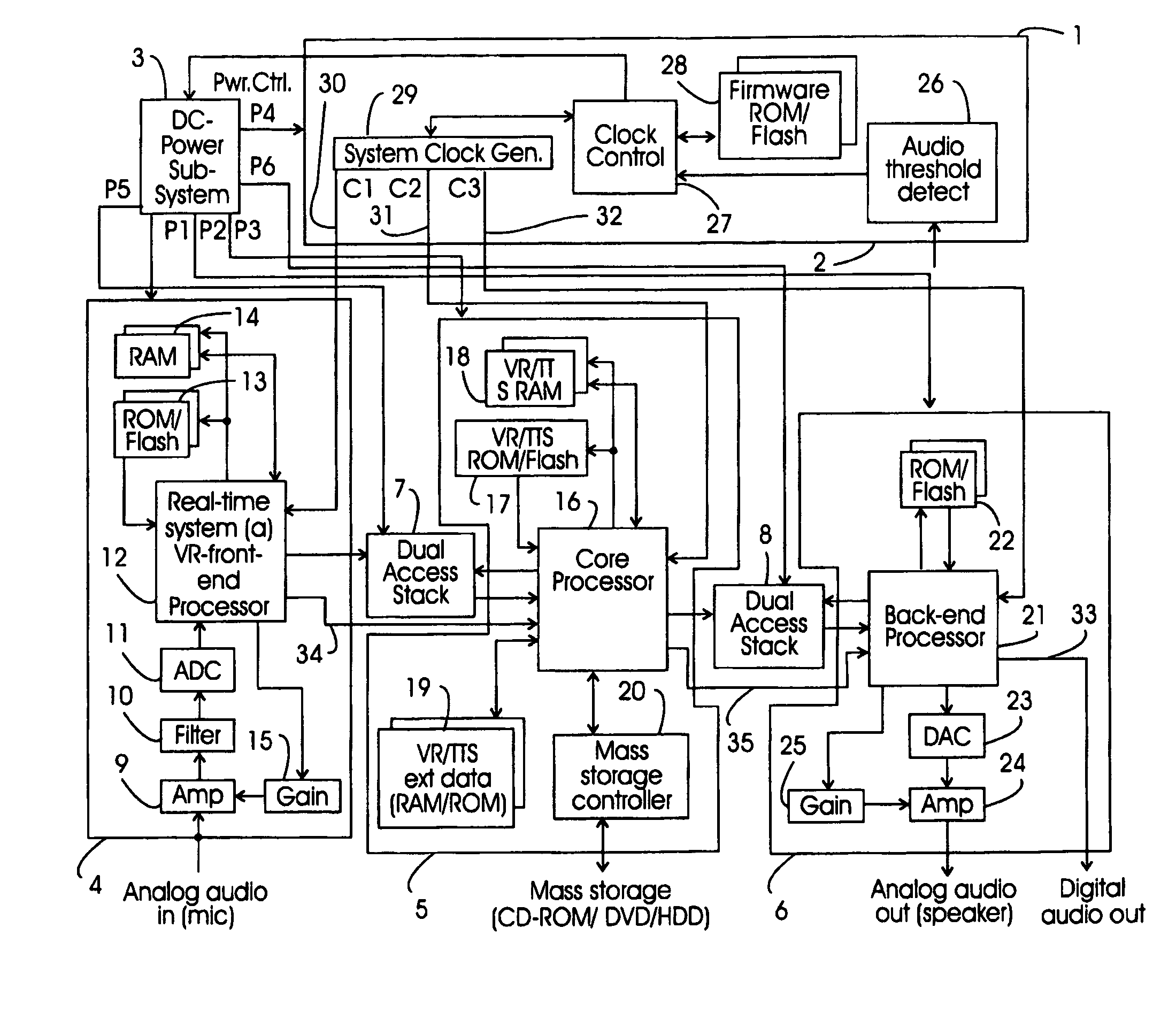

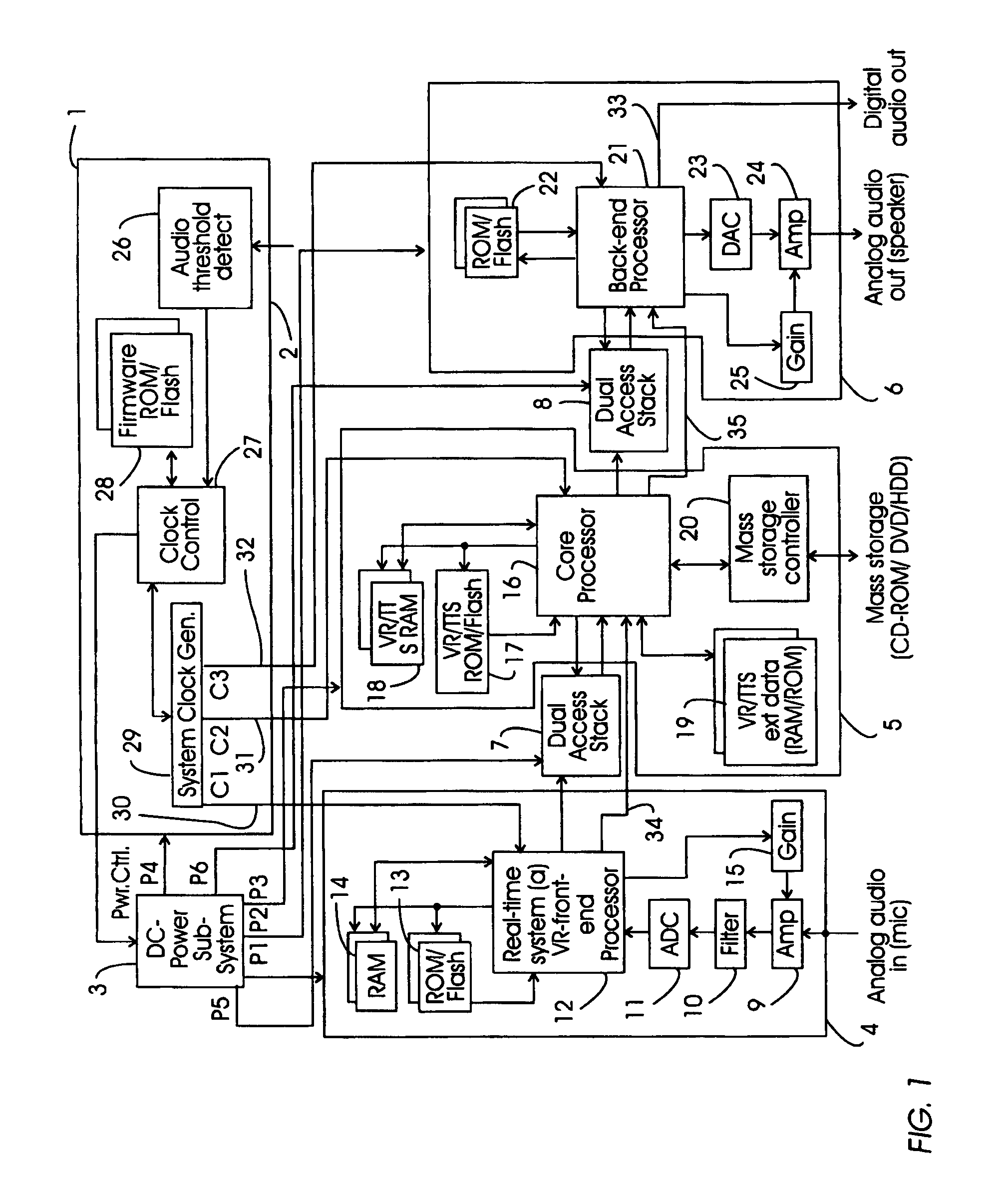

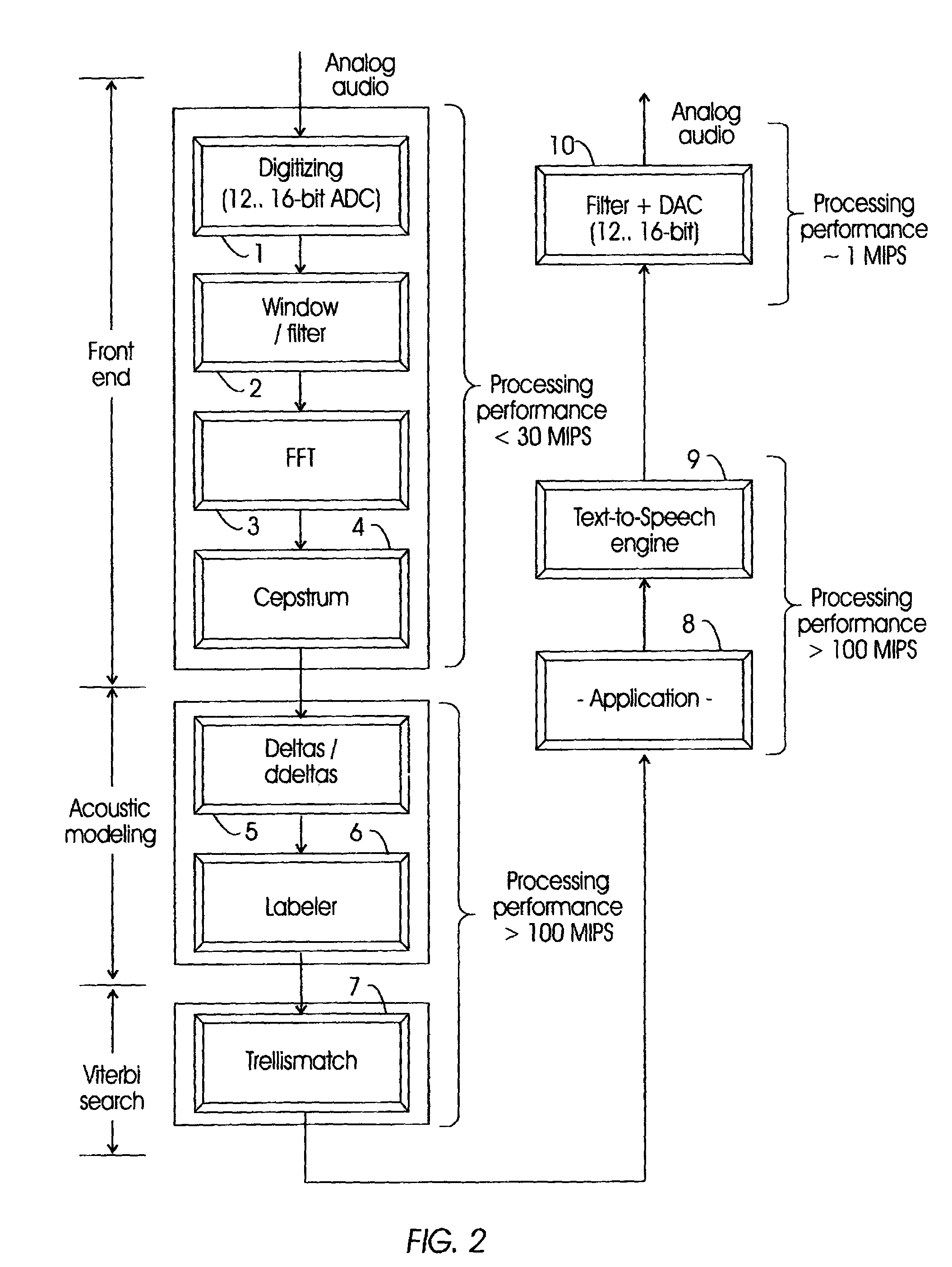

Minimizing resource consumption for speech recognition processing with dual access buffering

ActiveUS7349844B2Improve speech recognition performanceAvoiding processing demandSpeech recognitionMemory systemsResource consumptionSpeech identification

In a processor system for audio processing, such as voice recognition and text-to-speech, a dedicated front-end processor, a core processor and a dedicated back-end processor are provided which are coupled by dual access stack. When an analog audio signal is inputted core processor is invoked only when a certain amount of data is present in the dual access stack. Likewise the back-end processor is invoked only when a certain amount of data is present in the dual access stack. This way the overall processing power required by the processing task is minimized as well as the power consumption of the processor system.

Owner:NUANCE COMM INC

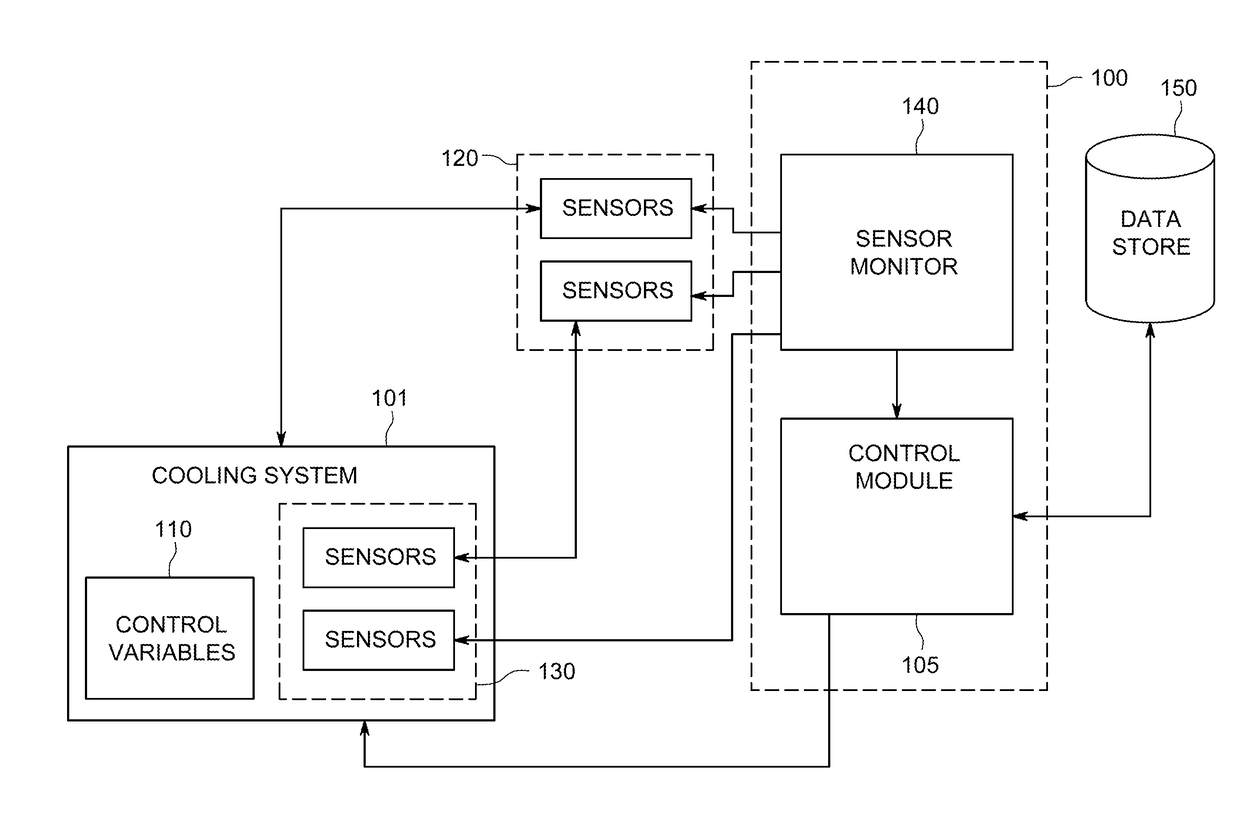

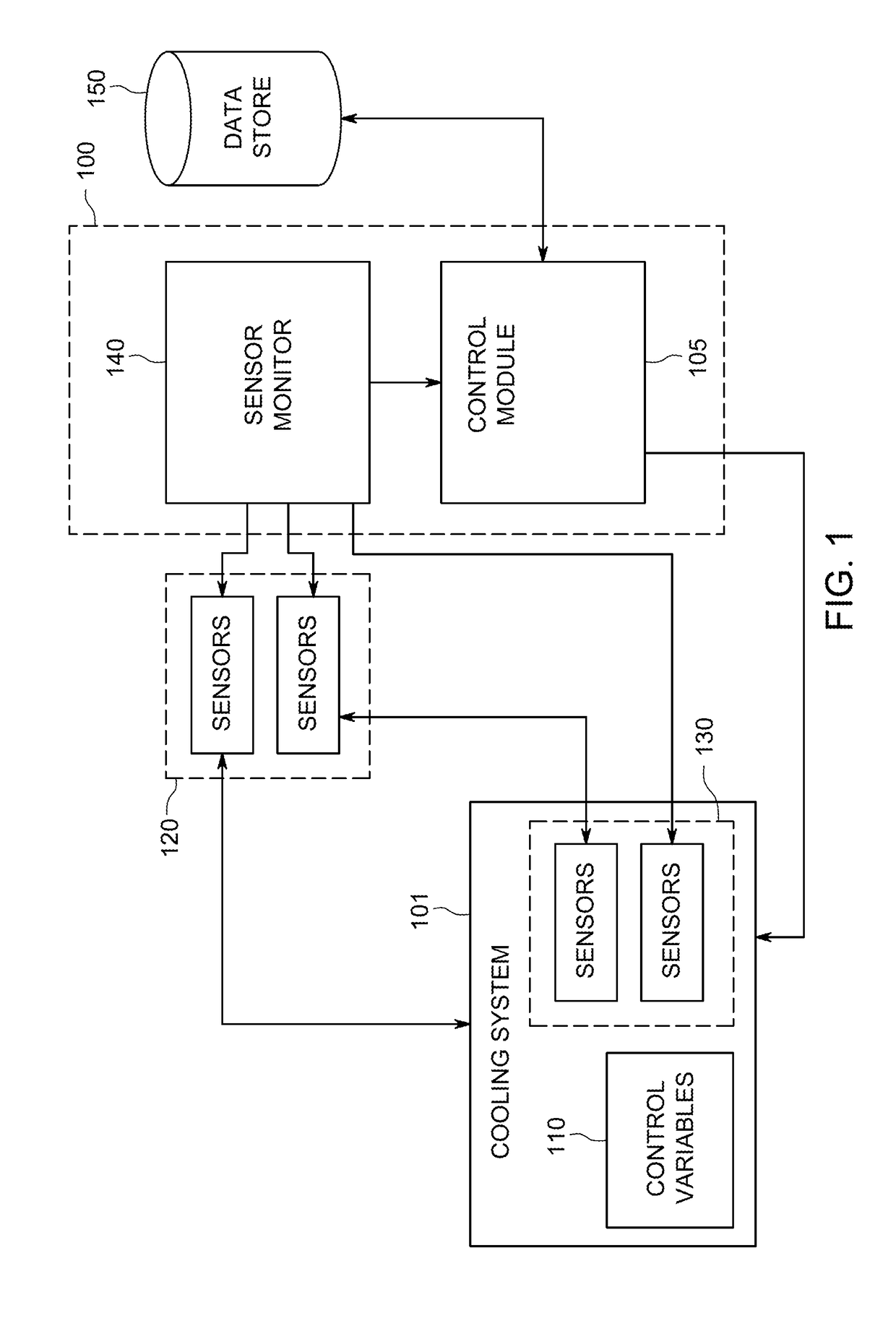

Method and apparatus for optimizing control variables to minimize power consumption of cooling systems

ActiveUS20170234559A1Minimize power consumptionProgramme controlMechanical apparatusProcess engineeringPower dissipation minimization

The present invention is directed to an apparatus for minimizing power consumption in a cooling system. In one embodiment, the apparatus comprises one or more processors, one or more sensors associated with one or more regulated environments and one or more chillers that regulate temperature of the one or more regulated environments and a storage device, coupled to the one or more processors, storing instructions that when executed by the one or more processors performs a method. The method comprises gathering readings from the one or more sensors, determining a cost and power consumption associated with setting values for a plurality of control variables associated with the one or more chiller plants, selecting values for the control variables with a minimum cost as optimized control variable values and applying the optimized control variable values to the plurality of control variables to minimize power consumption of the cooling system.

Owner:VIGILENT CORP