Method and system for accelerating storage component netlist simulation and medium

A technology for storage components and storage subsystems, applied in software testing/debugging, instrumentation, electrical digital data processing, etc., can solve problems such as difficulties in observing internal node waveforms, achieve shortened simulation verification cycle, long compilation time, and speed up Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The method, system and medium for accelerating netlist simulation of storage components of the present invention will be further described in detail below by taking the DDR4 storage subsystem as an example. Undoubtedly, the method, system and medium for accelerating storage component netlist simulation of the present invention are not limited to DDR4 storage subsystems, and can also be used for older storage subsystems such as DDR3 storage subsystems, DDR5 storage subsystems, and The updated storage subsystem will not be repeated here.

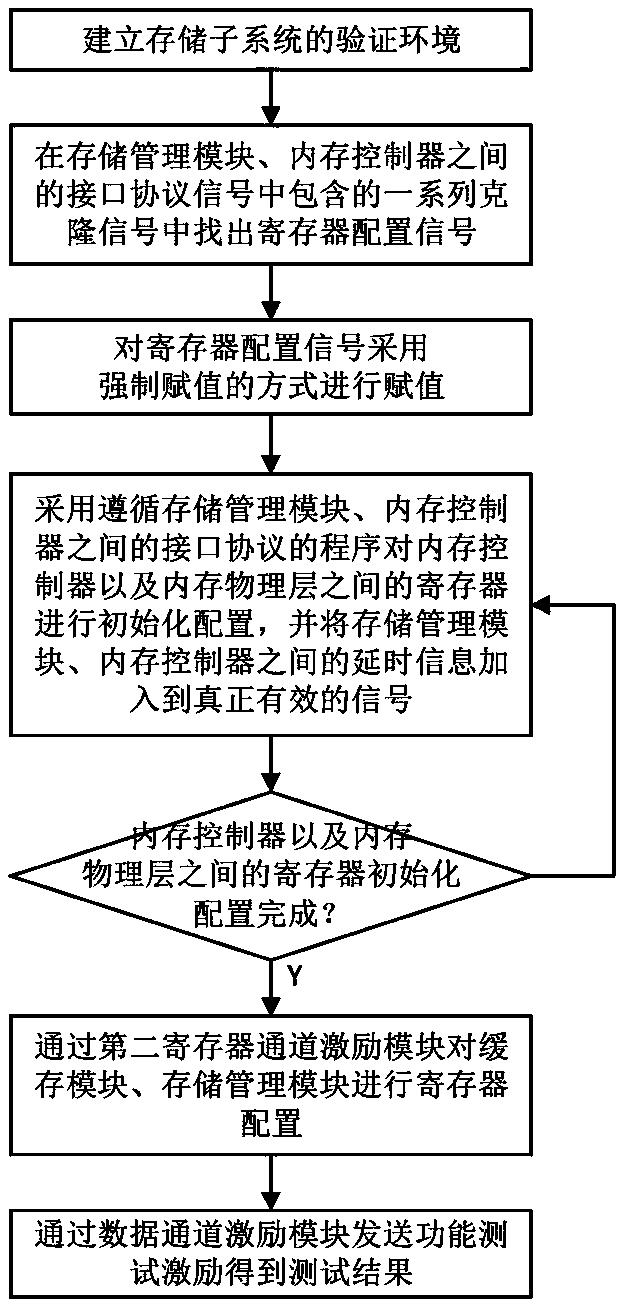

[0032] Such as figure 1 As shown, the implementation steps of the method for accelerating storage component netlist simulation in this embodiment include:

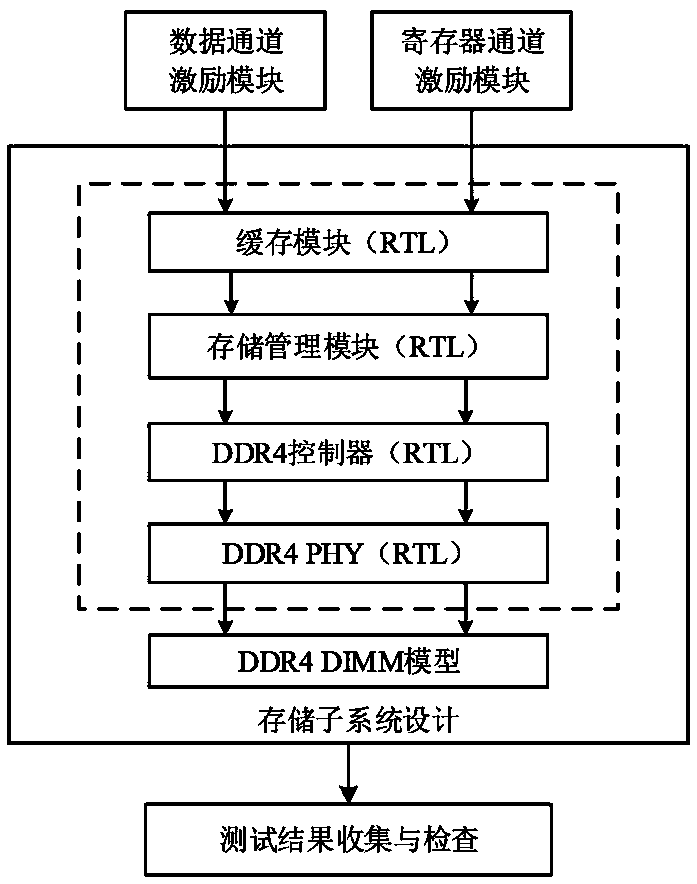

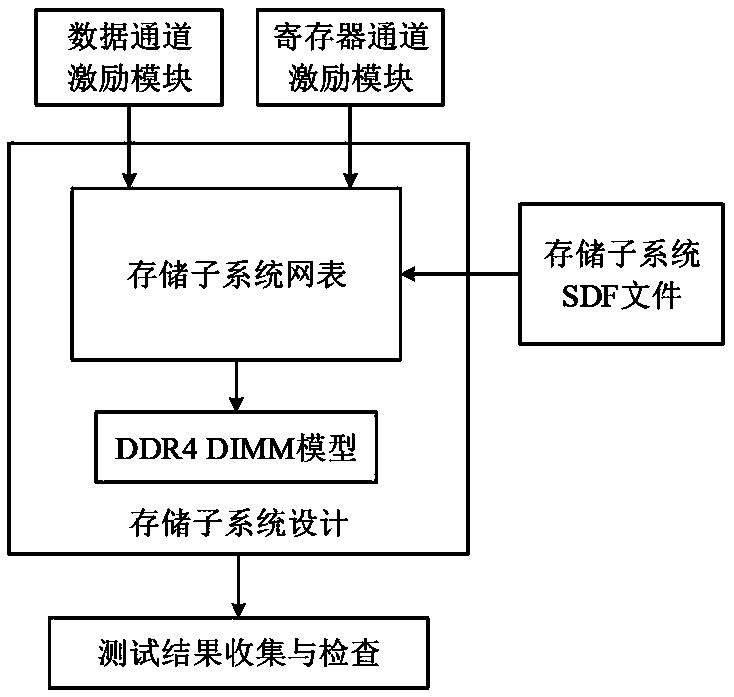

[0033] 1) Establish a verification environment for the storage subsystem, such as image 3 with Figure 4 As shown, the verification environment of the storage subsystem includes the data channel stimulus module, the first register channel stimulus module (represented as register...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More