Time sequence budgeting method capable of considering distance and clock

A timing and clock technology, applied in the field of hierarchical physical design, can solve problems such as affecting the design cycle and hindering the progress of the physical design of sub-modules

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

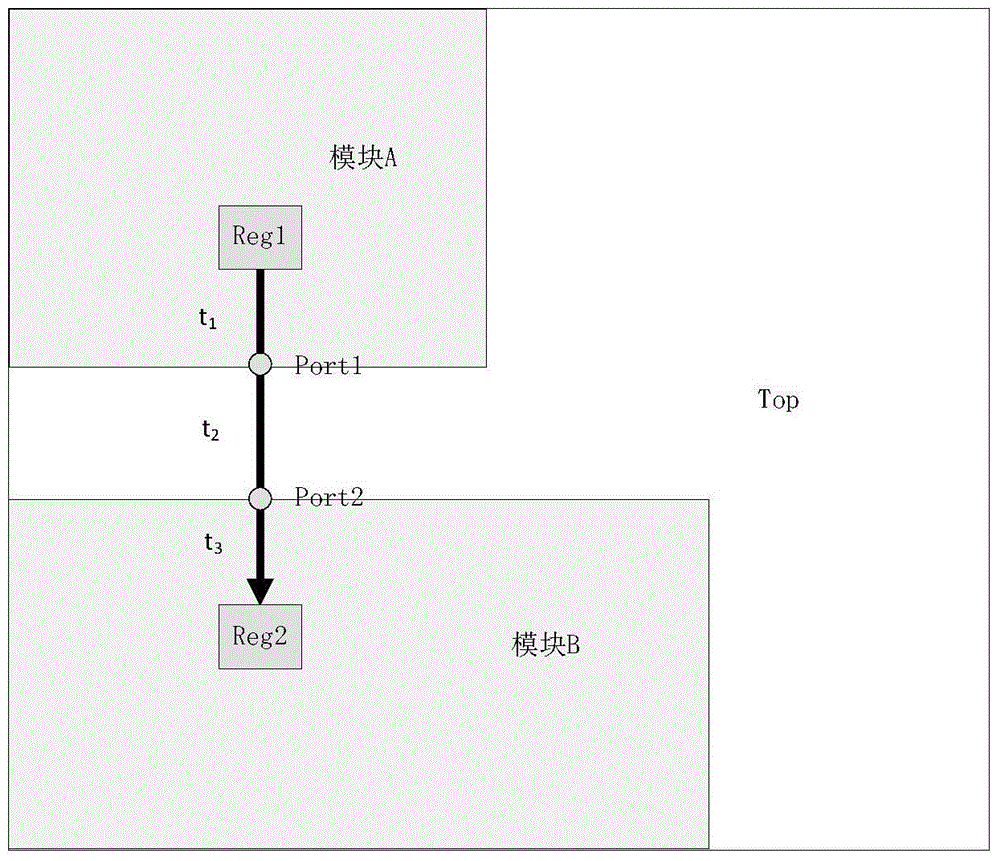

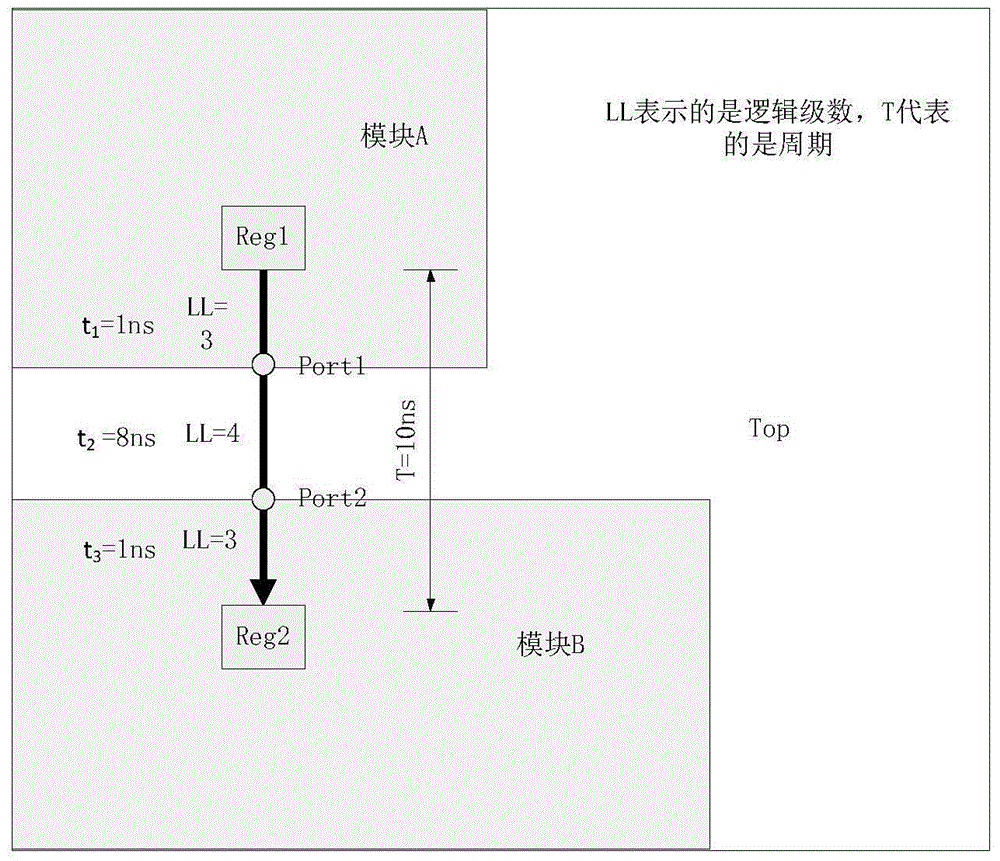

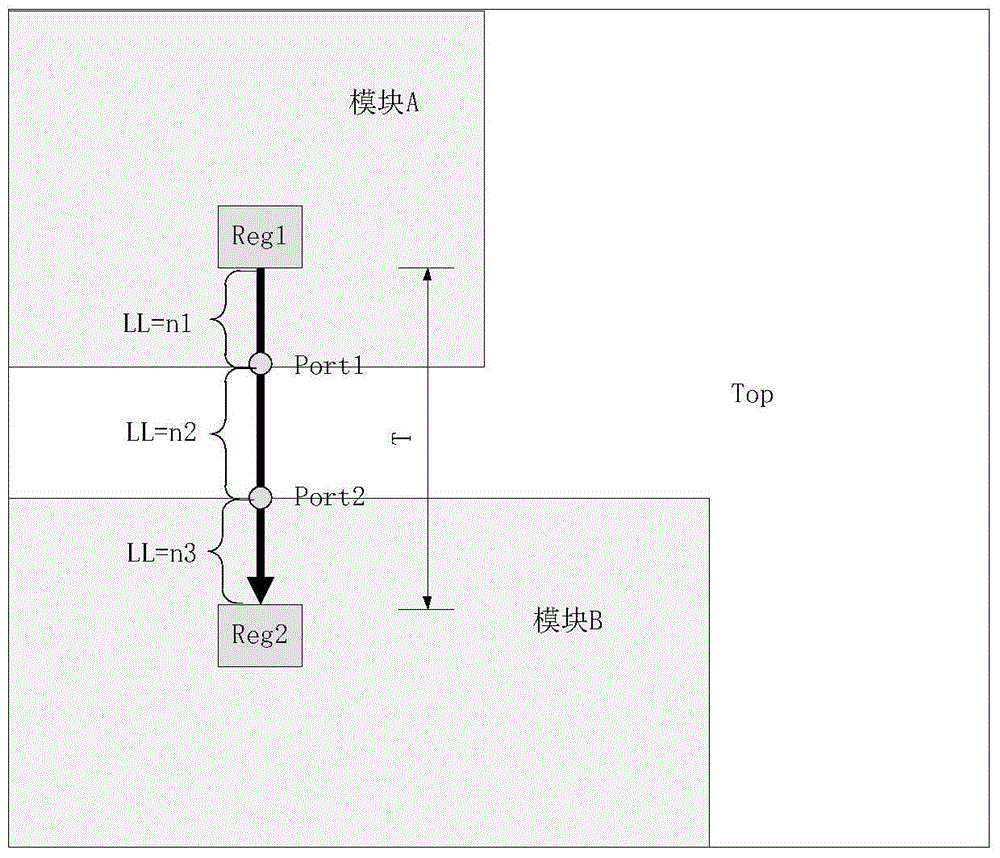

[0097] Hereinafter, the present invention will be further described in detail with reference to specific embodiments and the drawings of the specification.

[0098] Reference Figure 7 , Is a flowchart of the timing budget method considering distance and clock of the present invention. The present invention includes the following steps:

[0099] The first step is to determine the process node and the metal layer used. For a given process and metal layer, using a repeater insertion method can make the interconnection delay linearly related to the length of the interconnection line. The interconnection delay per unit length α can be obtained by the following calculation method.

[0100] 1.1 Obtain the process node and the total number of metal layers M max .

[0101] 1.2 Select section And The layer metal serves as the horizontal and vertical wiring metal layer. among them For right Rounding, For right The rounding.

[0102] 1.3 Get the first And The parasitic resistance r pe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More