Time sequence optimization method based on dummy

An optimization method and timing technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve the problems of complex implementation, inability to guarantee consistency and observability, accuracy and low repair efficiency, and achieve the cost of implementation Low cost, reduced design complexity, and a wide range of configurations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

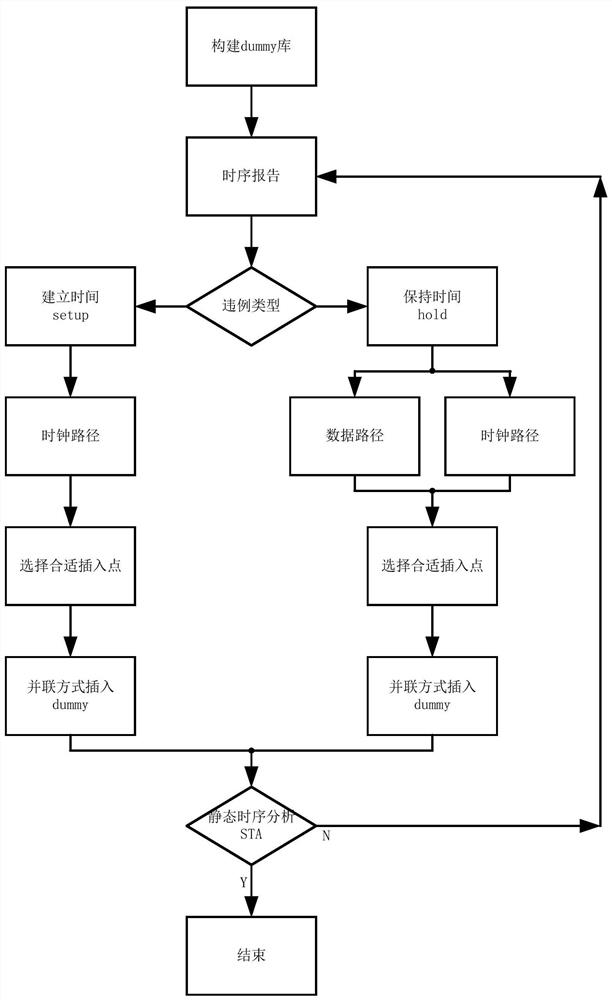

[0039] Such as figure 1 Shown, a kind of timing optimization method based on dummy of the present invention, its step comprises:

[0040] Step S1: Build the dummy library;

[0041] Step S2: Analyze the physical design sequence and prepare data for formulating a suitable repair strategy;

[0042] Step S3: process the data in step S2, classify timing violations, and divide them into data path (data path) and clock path (clock path) according to different repair paths; wherein, the data path data path can be used to repair hold time (hold ) violations, the clock path clock path can be used to fix setup and hold violations.

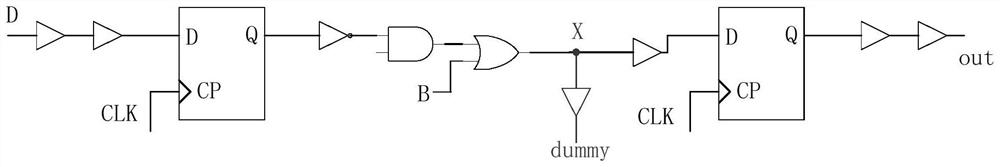

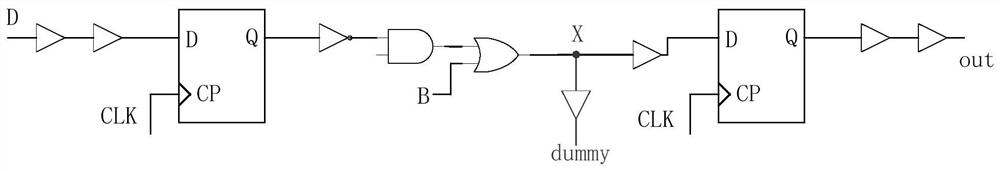

[0043] Step S4: Repair the data path (data path), that is, insert the dummy in parallel, and realize the repair of the illegal path through the dummy with an equivalent Delay;

[0044] Step S5: Repair the clock p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More