Automatic physical unit insertion method based on original layout planning

A physical unit and layout planning technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve the problem of consuming design and wiring resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0050] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

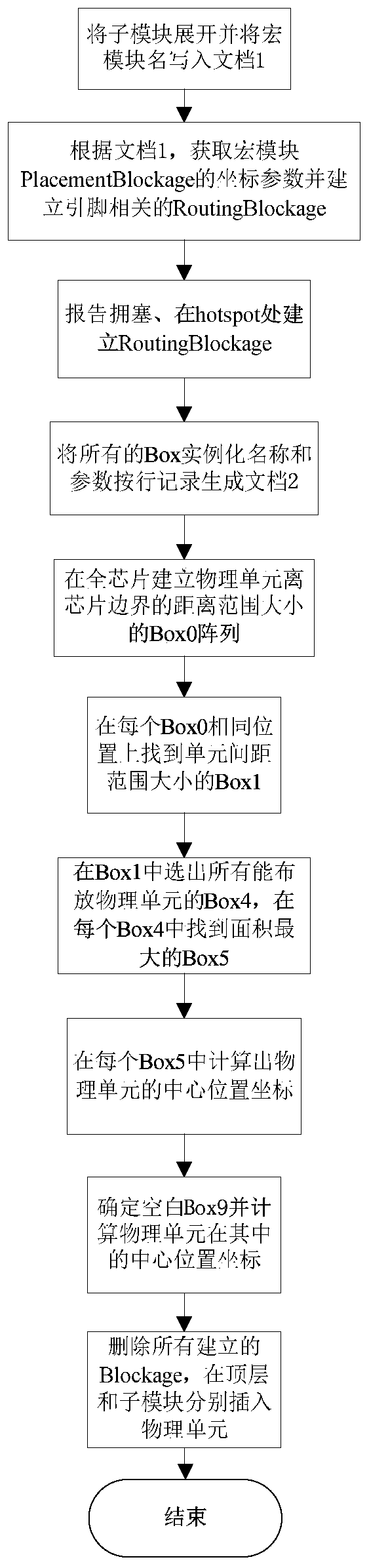

[0051] Such as figure 1 As shown, the automatic physical unit insertion method based on the original layout planning of the present invention includes:

[0052] Step S1: After designing the layout, expand all sub-modules at the top level, and record each sub-module and the instantiation name of the hard macro module that needs to be fixed at the top level to Document 1;

[0053] Step S2: Read the document 1 to obtain the information on the layout barrier layer of each hard macromodule;

[0054] Step S3: Report the full-chip congestion situation, record the coordinates and Box parameters of all hotspots, generate a wiring blocking rectangular Box of equal size, and name it according to certain rules;

[0055] Step S4: generate document 2 by recording the instantiation names, position coordinates and Box parameters of all the above Bo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More