Method and device for testing single event upset in in-field programmable logic gate array

A single-event flipping and programming logic technology, which is applied in the field of single-event flipping detection, can solve the problems affecting the normal operation of FPGA devices, the high price of FPGA devices, and the improvement, and achieve the effects of simple structure, low cost, and cost reduction.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The present invention will be further described in detail below in conjunction with specific embodiments and accompanying drawings.

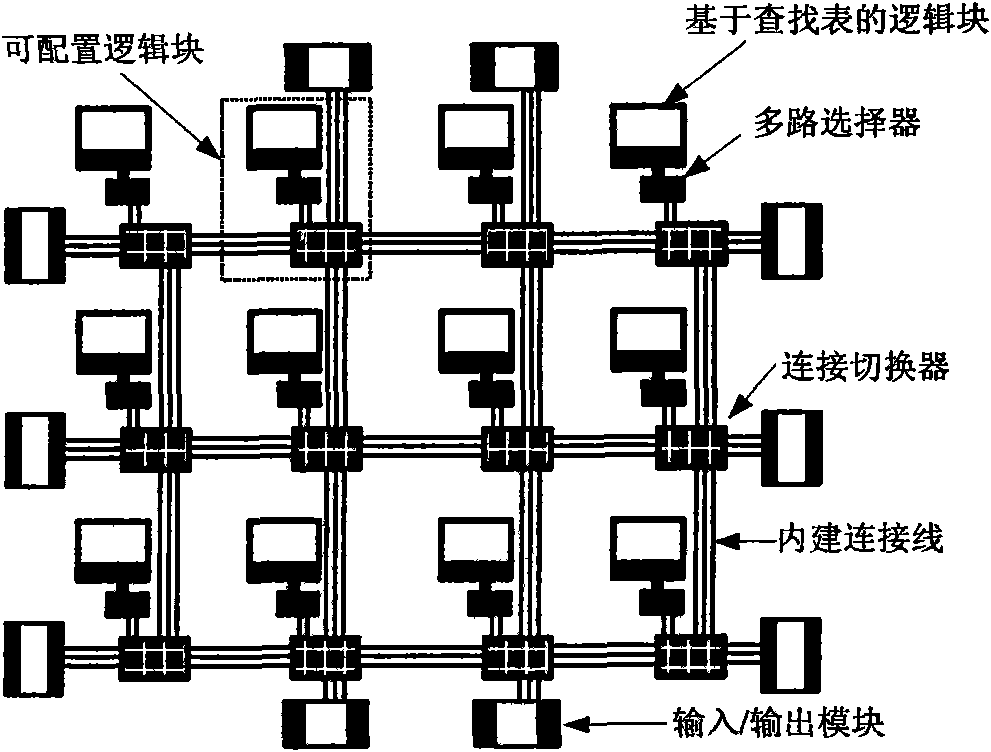

[0030] Such as figure 1 As shown, inside a typical SRAM FPGA is an array composed of a configurable logic block (CLB, Configurable LogicBlock) and a switch matrix (SwitchMatrix) interlaced layout. Wherein, the CLB based on a lookup table (LUT, LookUp Table) can realize any combination of multiple input / multiple output or sequential logic circuit. The programmable interconnection point determines the connection relationship of the internal connection lines of the switch matrix, and multiple CLBs are connected together through an input / output multiplexer (IO Mux) to form a circuit required by the user. In the SRAM FPGA, the programmable bits used to configure the circuit components form a configuration bit stream, which is stored in an SRAM memory in units of configuration frames. The SRAM memory that stores the configuration bit stream i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More