Patents

Literature

109 results about "Trapping region" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In applied mathematics, a trapping region of a dynamical system is a region such that every trajectory that starts within the trapping region will move to the region's interior and remain there as the system evolves.

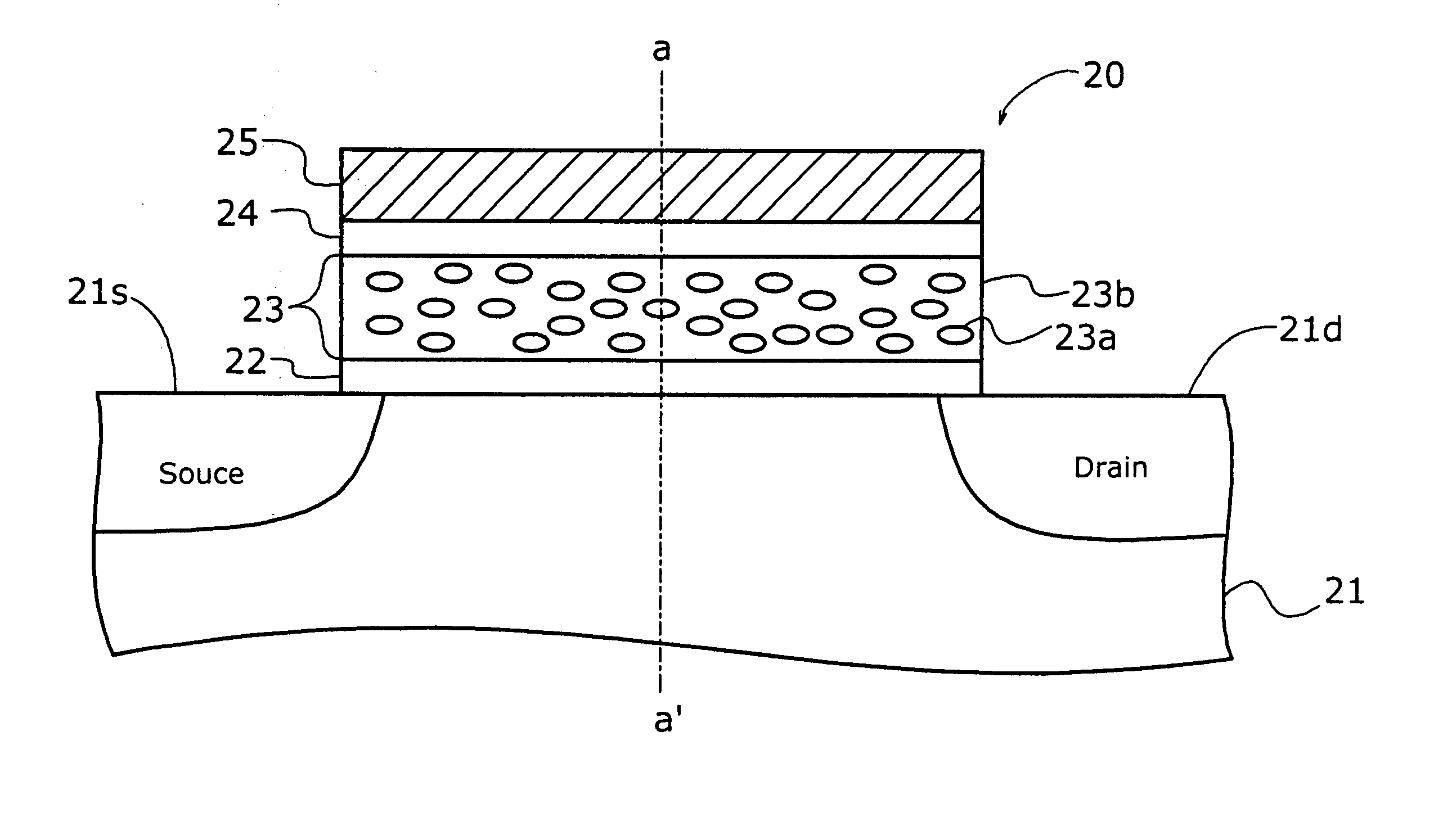

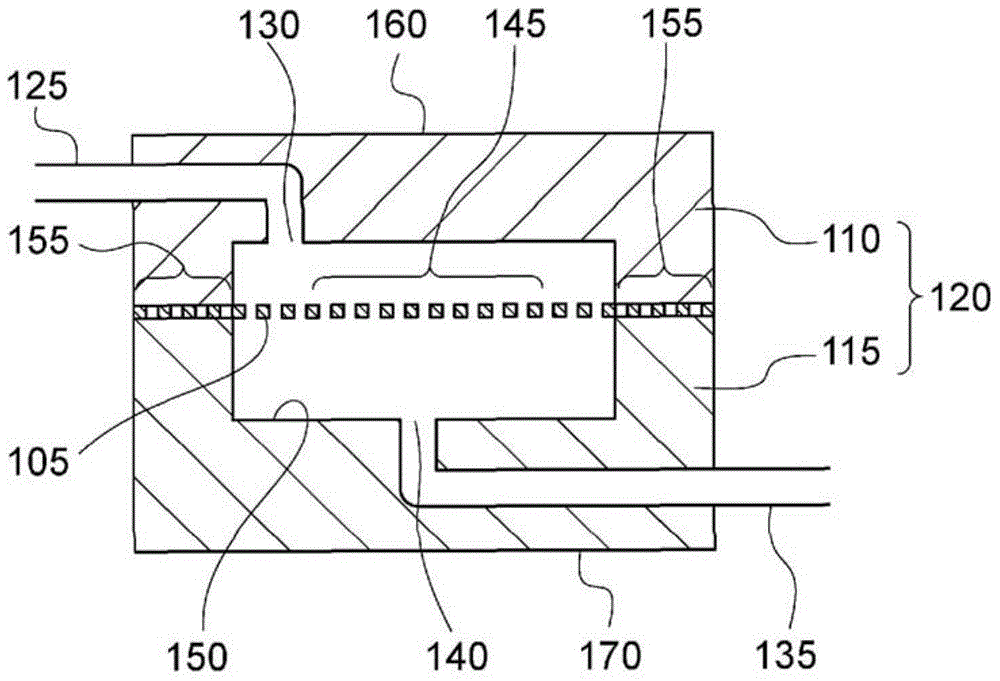

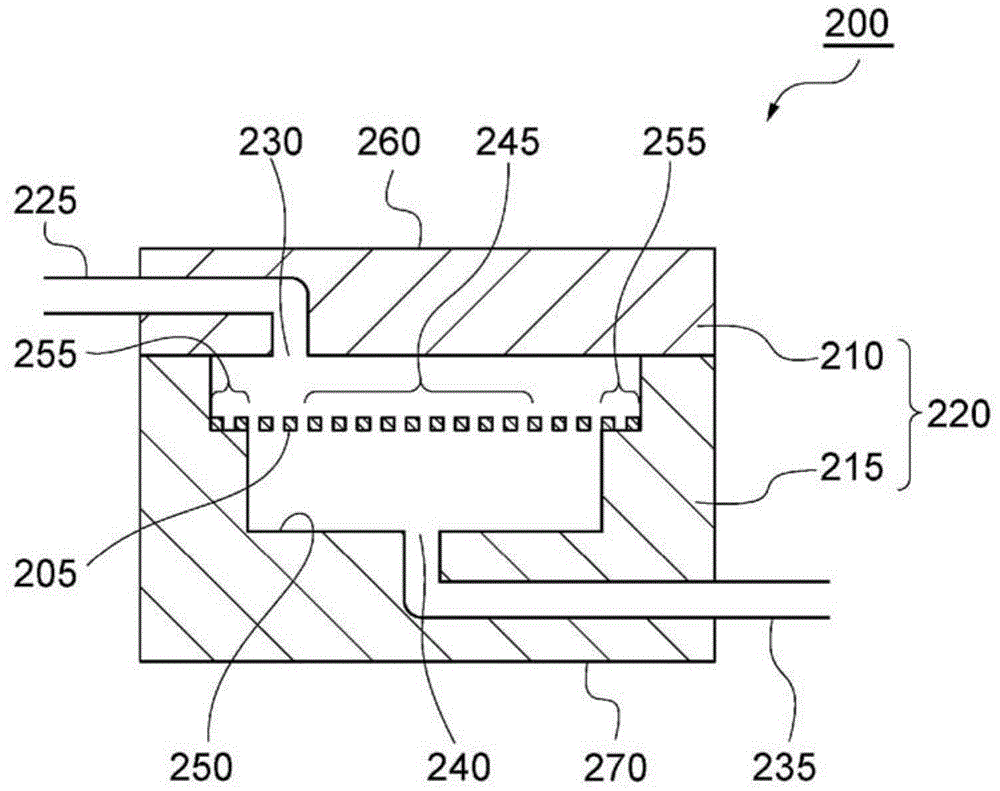

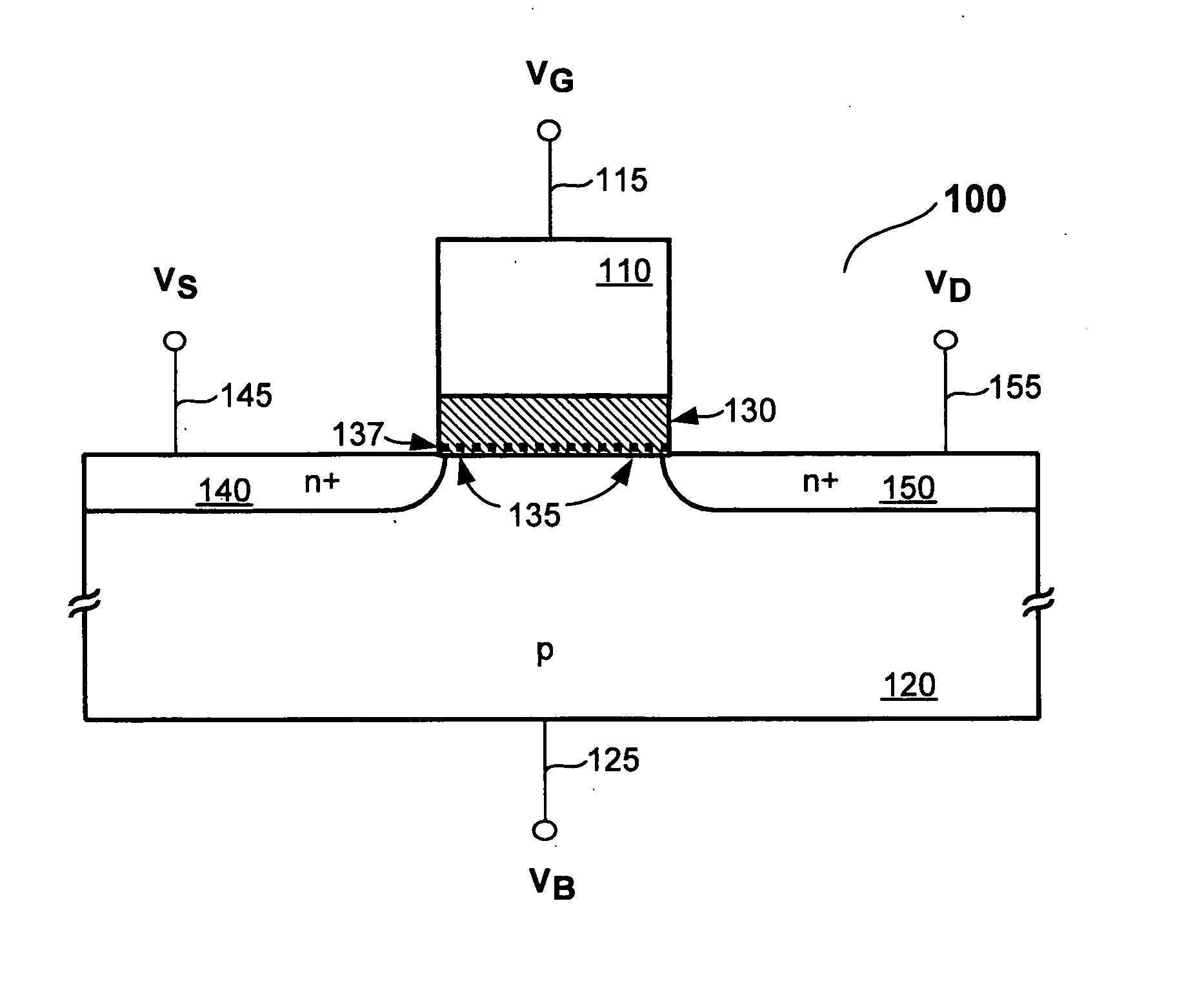

Multi-bit-per-cell nvm structures and architecture

InactiveUS20070164352A1High sensitivityReduce sensitivitySolid-state devicesRead-only memoriesGate dielectricEngineering

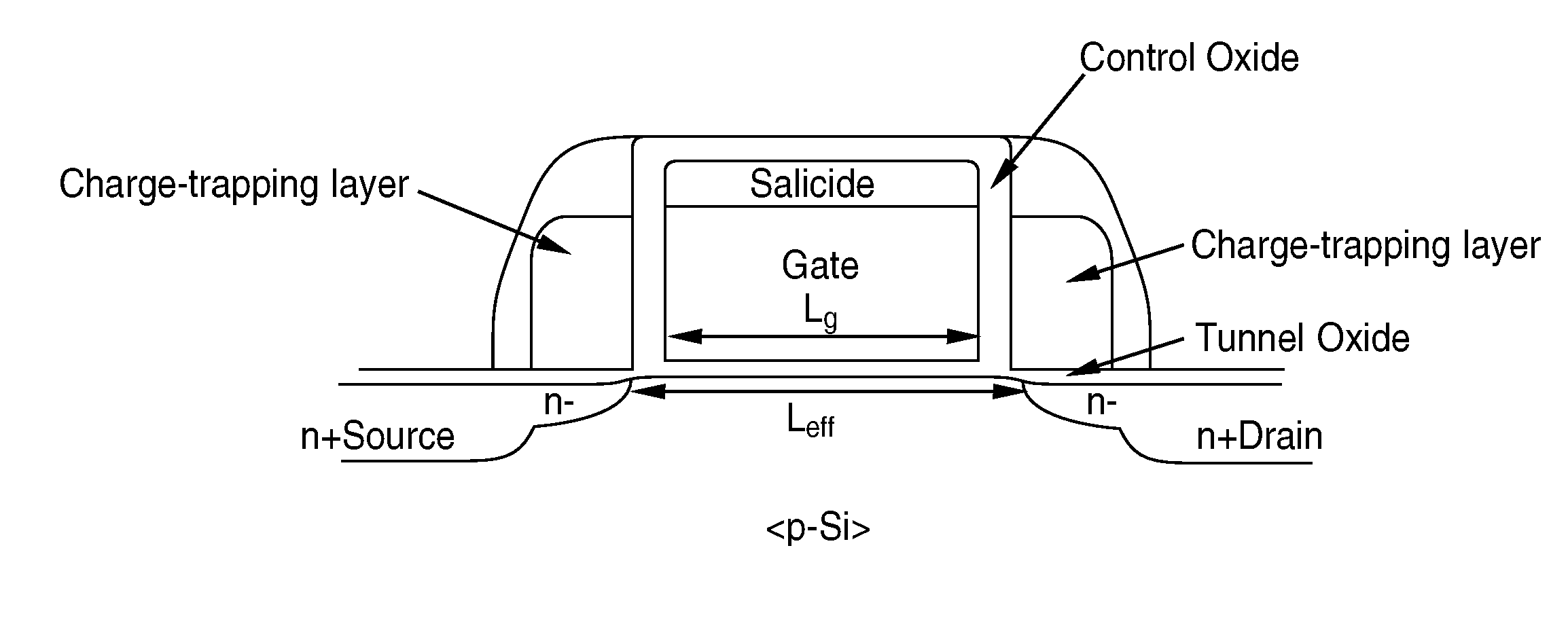

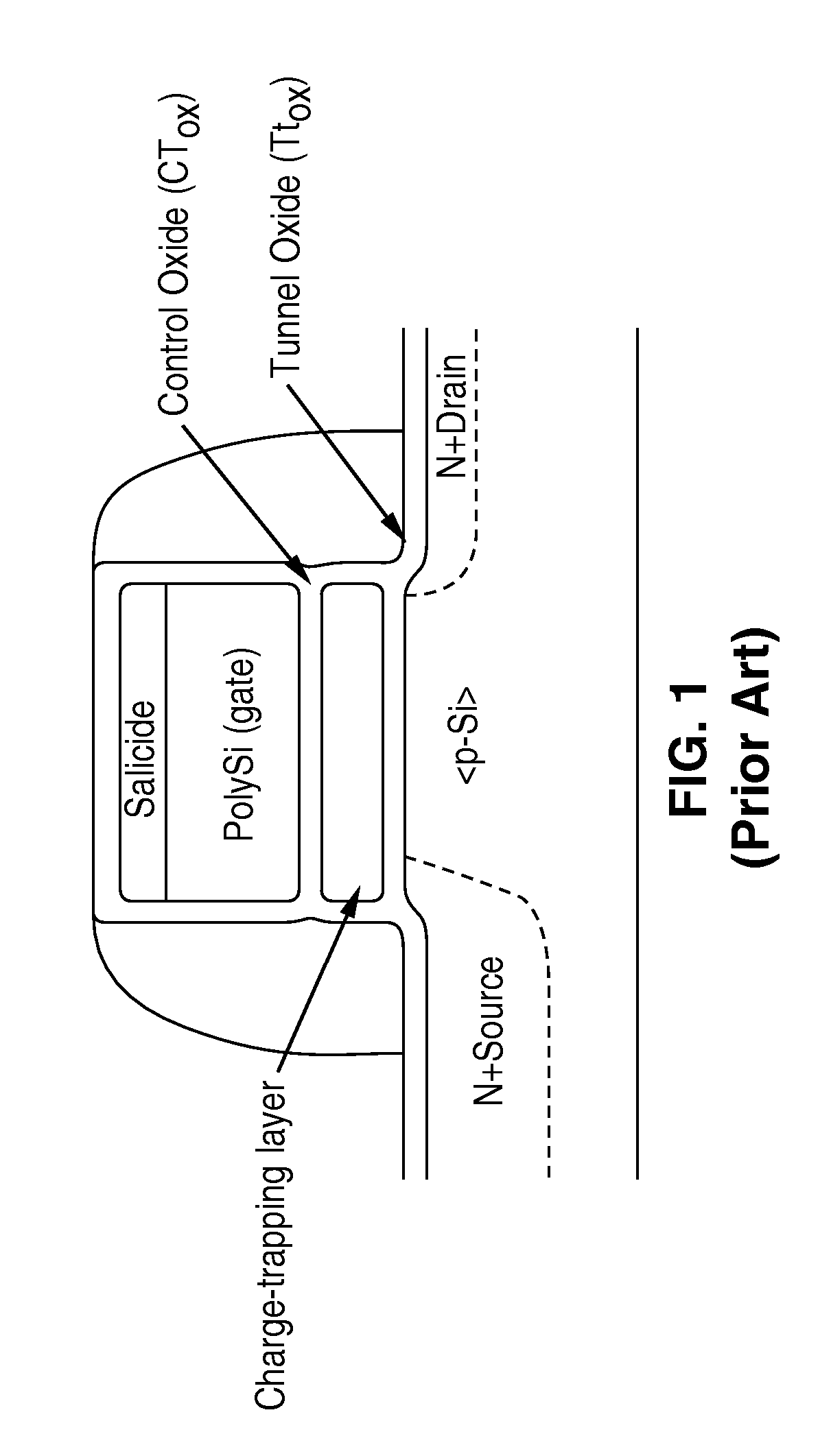

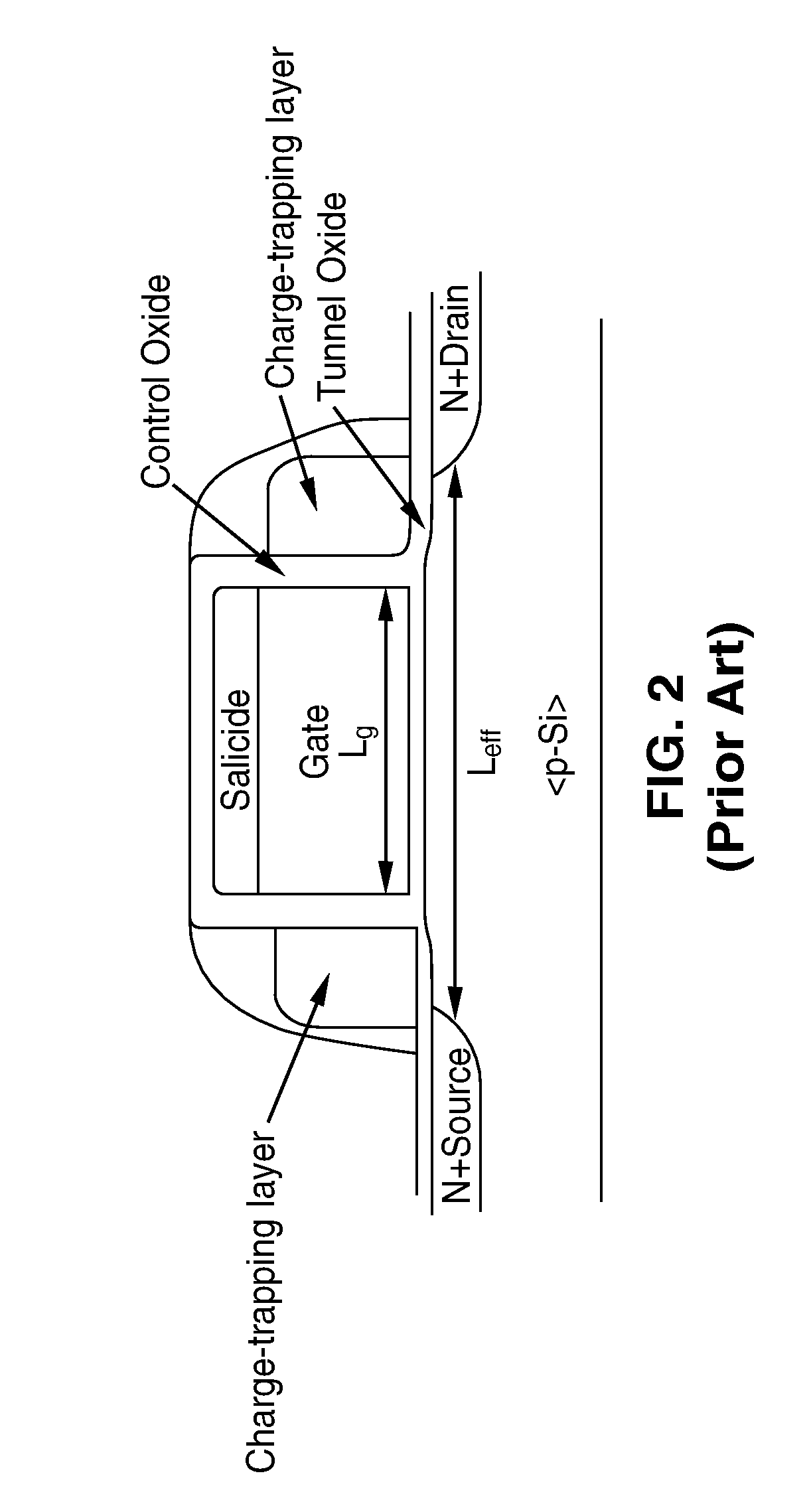

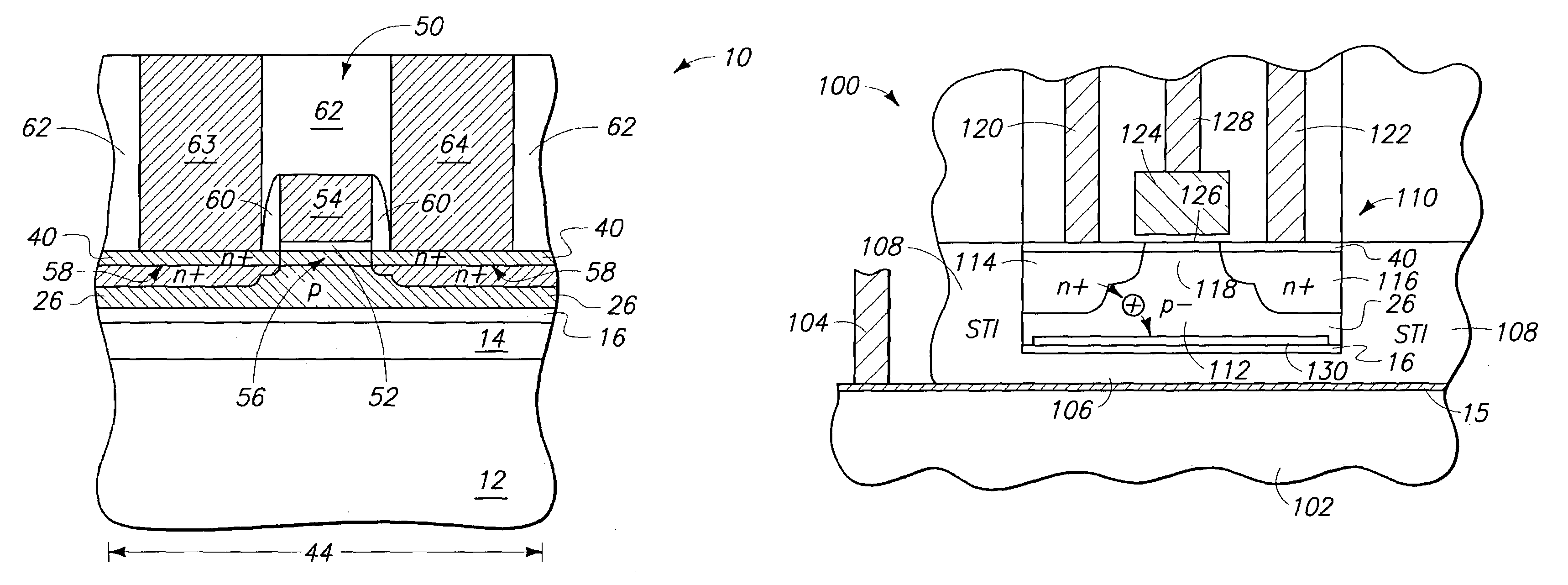

A transistor structure, such as a Double-gated FET (DG FET), that has been modified to include a charge-trapping region used to store either 2- or 4-bits of information. The charge-trapping region can, for example, be embedded in the gate dielectric stack underneath each gate electrode, or placed on the sidewalls of each gate electrode.

Owner:RGT UNIV OF CALIFORNIA

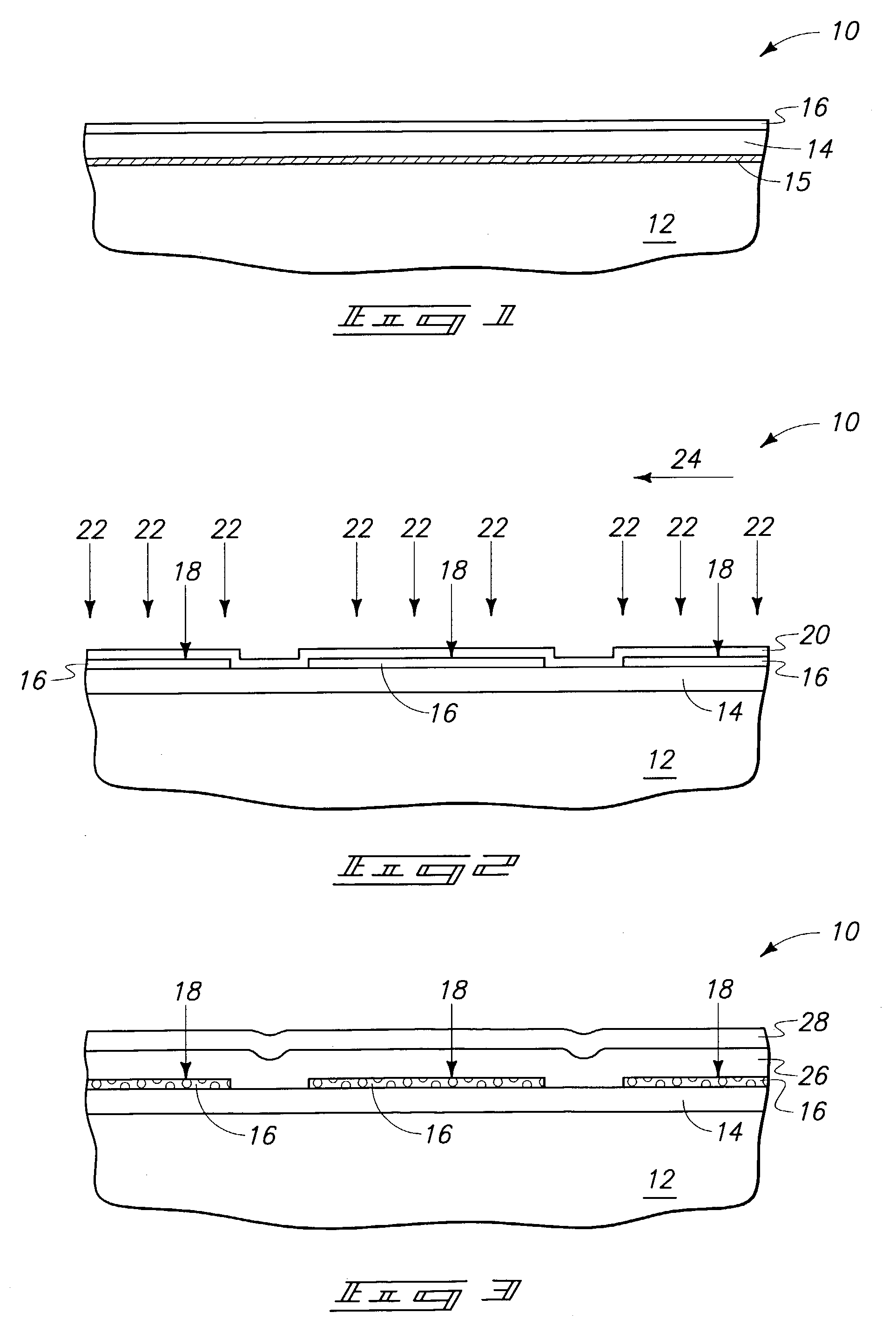

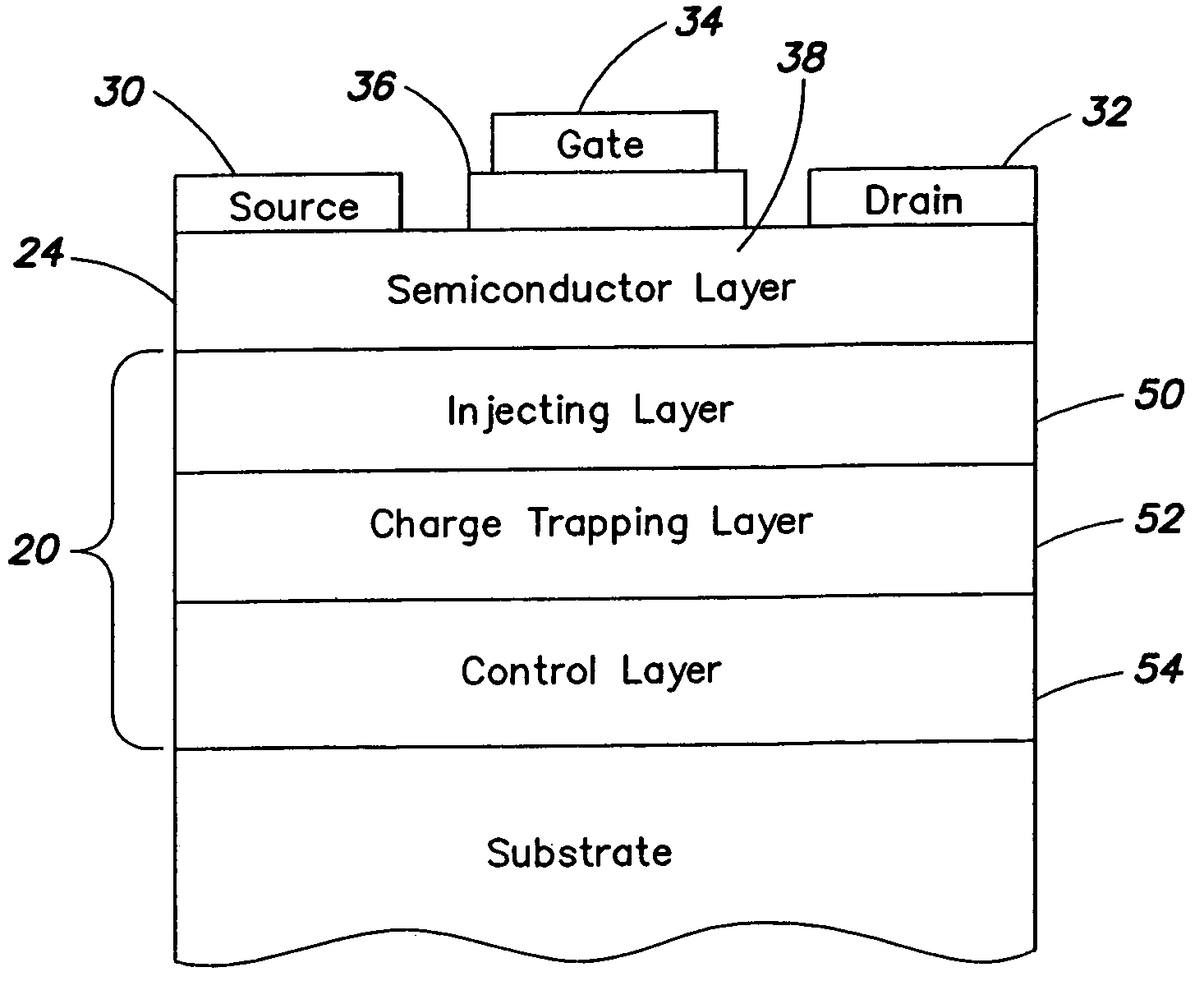

Transistor constructions and electronic devices

The invention includes a non-volatile memory cell comprising a field effect transistor construction having a body region within a crystalline material. The body region includes a charge trapping region. The memory cell can be TFT-SOI based, and can be supported by a substrate selected from a diverse assortment of materials. The top portion of the substrate can be a conductive layer separated from the memory device by the SOI-oxide insulator film. The charge trapping region can be, for example, silicon enriched silicon nitride or silicon enriched silicon oxide. The crystalline material can include silicon and germanium. The transistor comprises first and second diffusion regions within the body region, and also comprises a channel region between the first and second diffusion regions. The entirety of the body region within the crystalline material can be within a single crystal of the material.

Owner:MICRON TECH INC

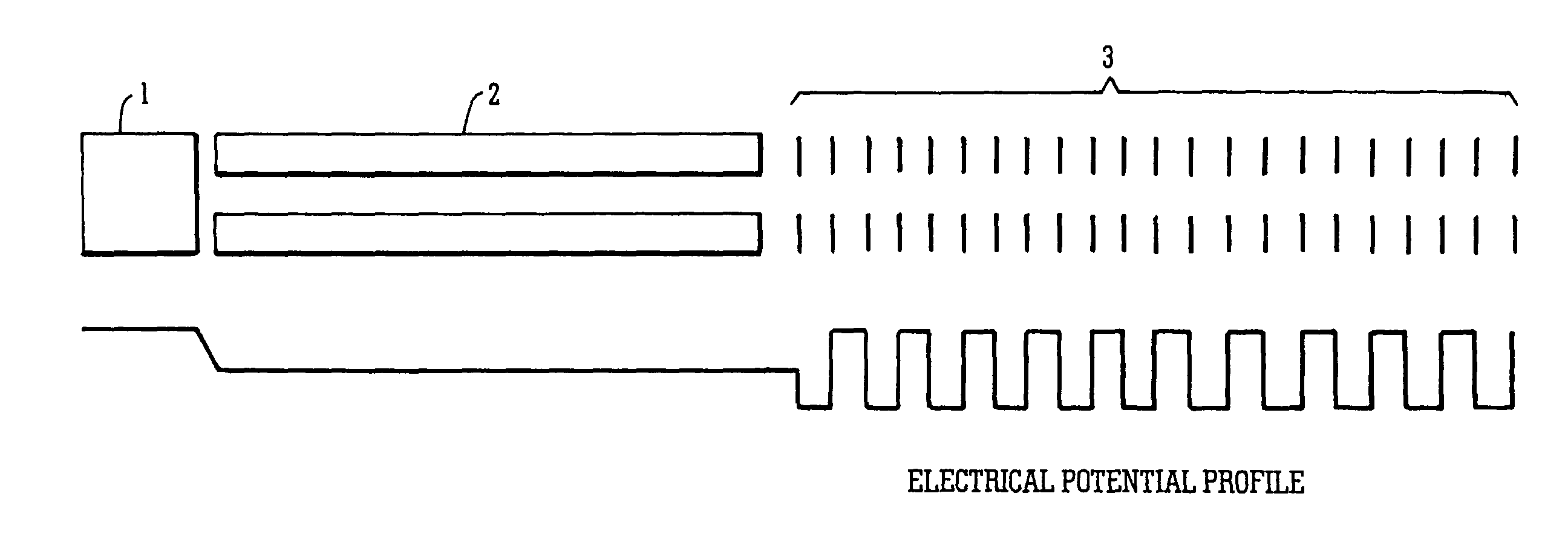

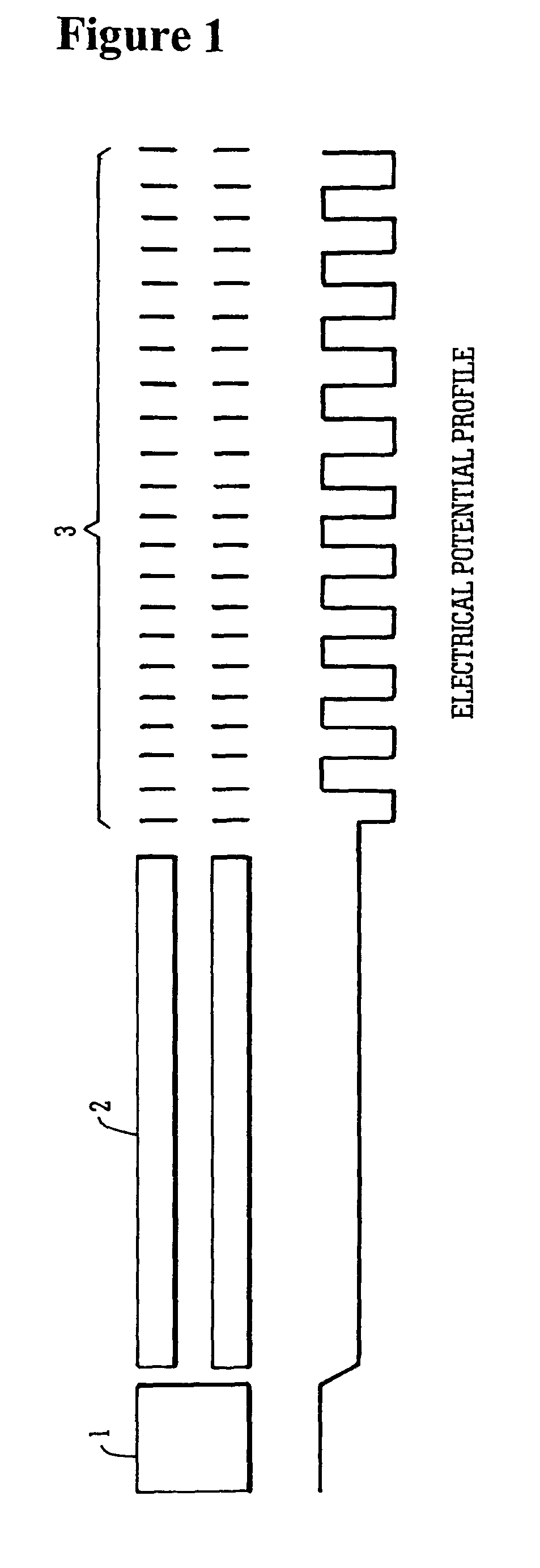

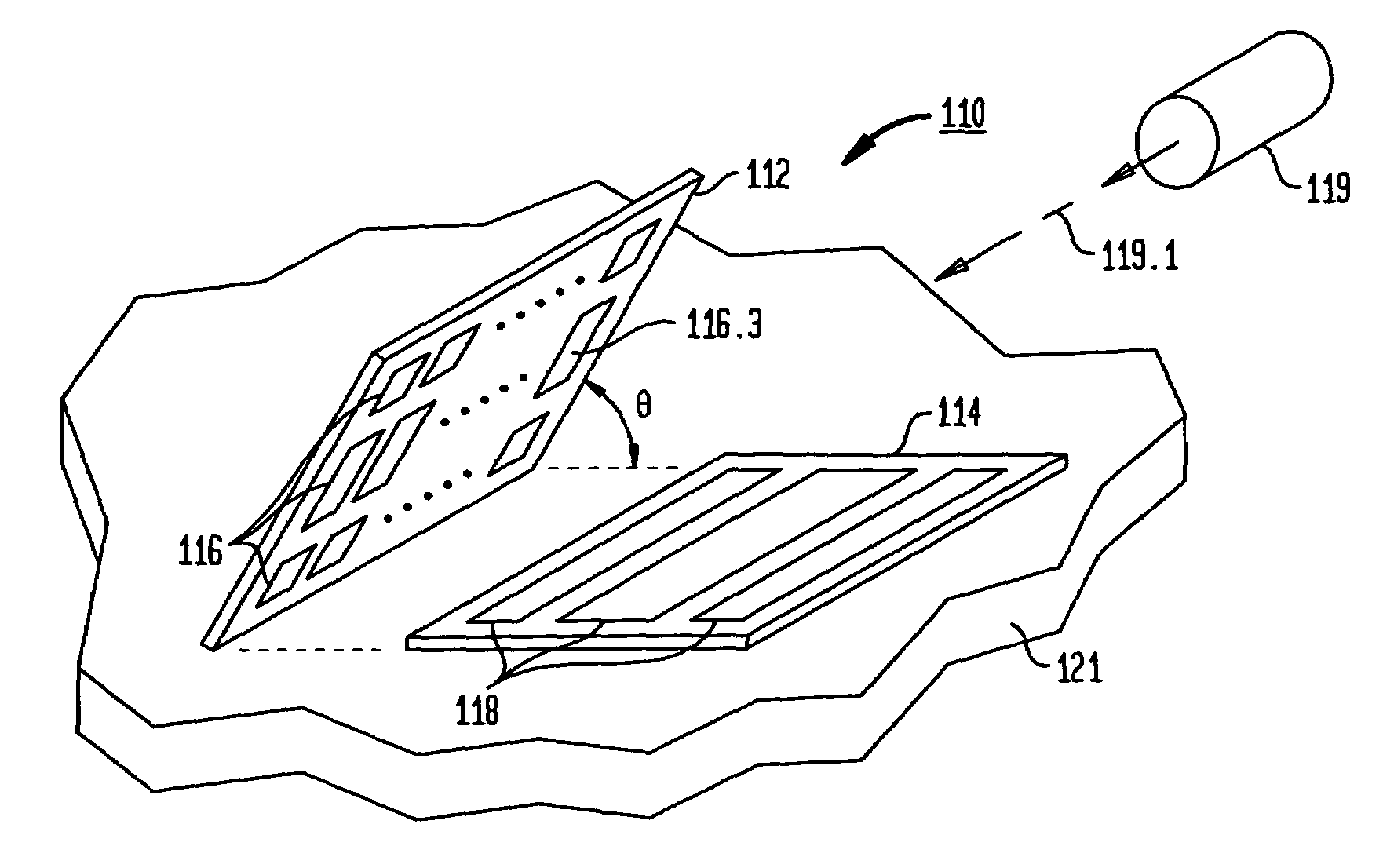

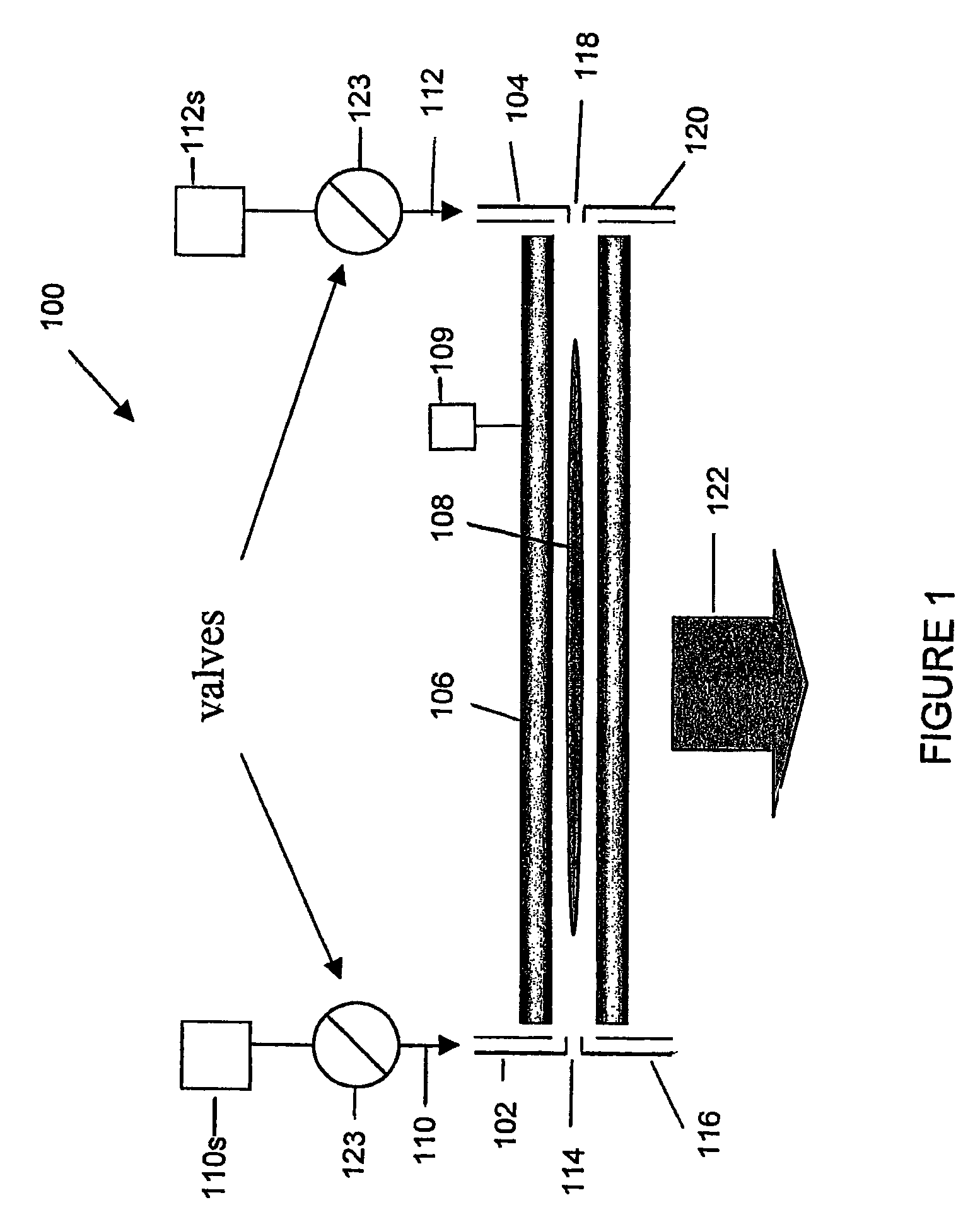

Mass spectrometer

ActiveUS7071467B2Eliminate the effects ofHigh duty cycleStability-of-path spectrometersTime-of-flight spectrometersIon trap mass spectrometryTrapping region

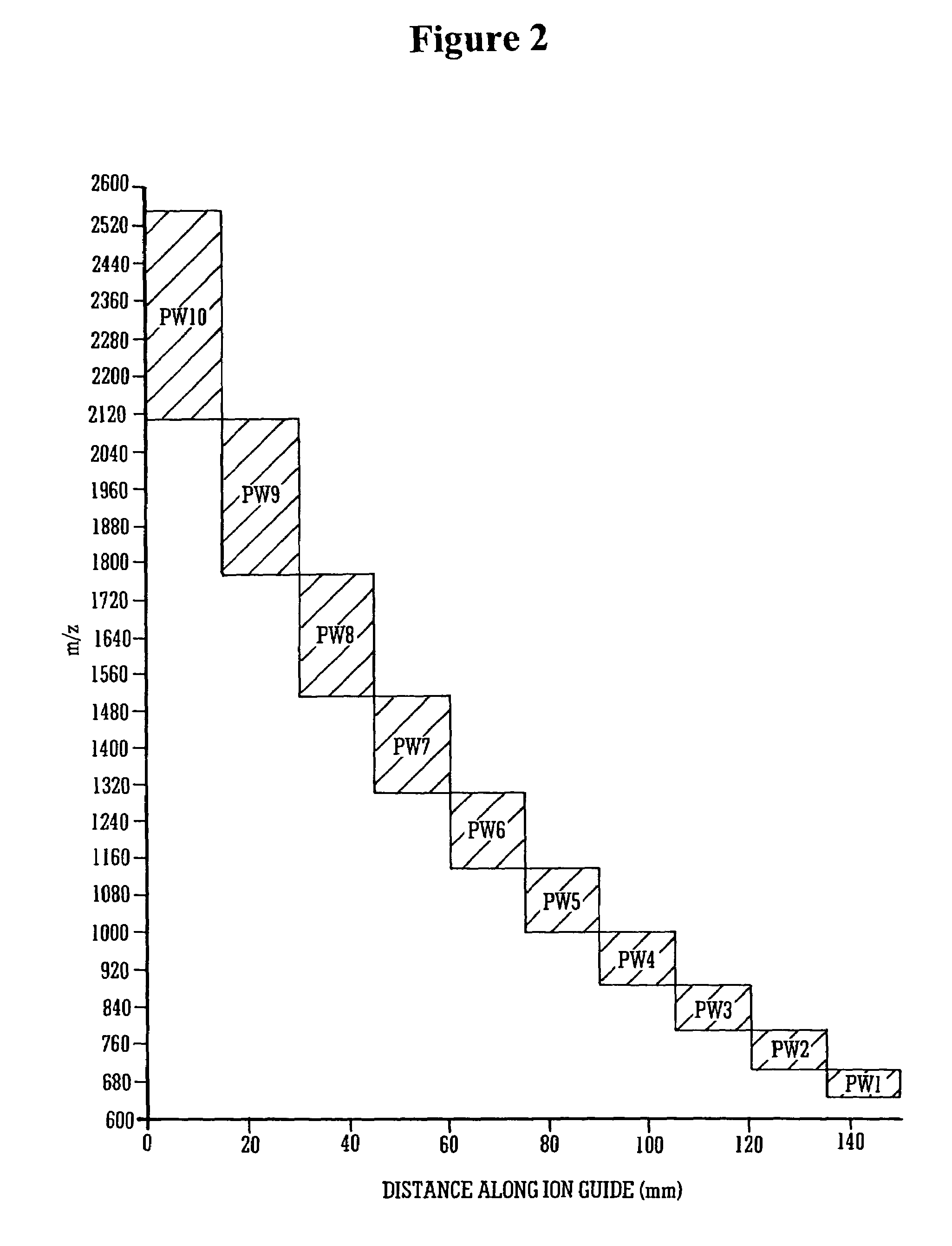

A mass spectrometer is disclosed comprising an ion trap wherein ions which have been temporally separated according to their mass to charge ratio or ion mobility enter the ion trap. Once at least some of the ions have entered the ion trap, a plurality of ion trapping regions are created along the length of the ion trap in order to fractionate the ions. Alternatively, the ions may be received within one or more axial trapping regions which are translated along the ion trap with a velocity which is progressively reduced to zero.

Owner:MICROMASS UK LTD

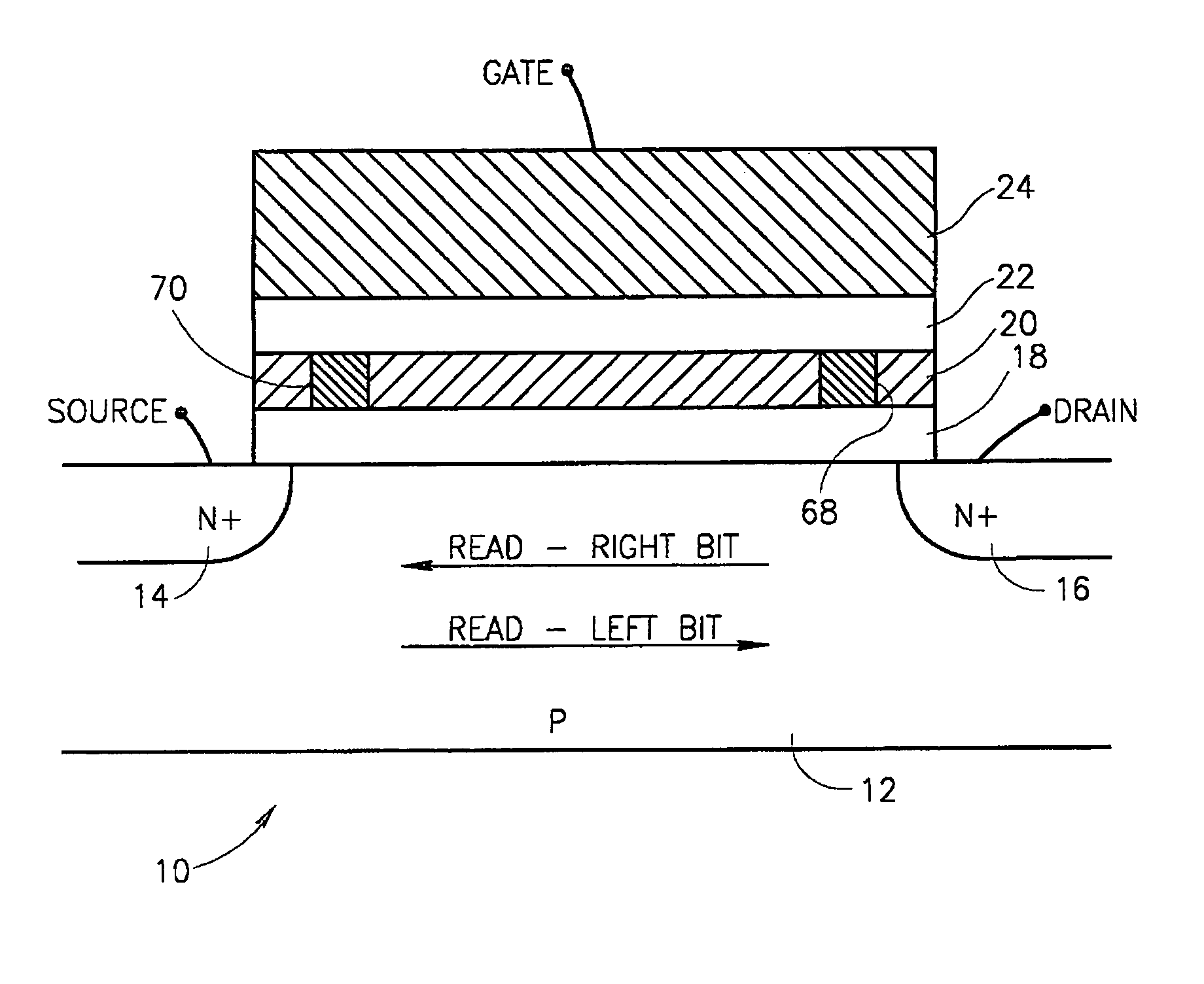

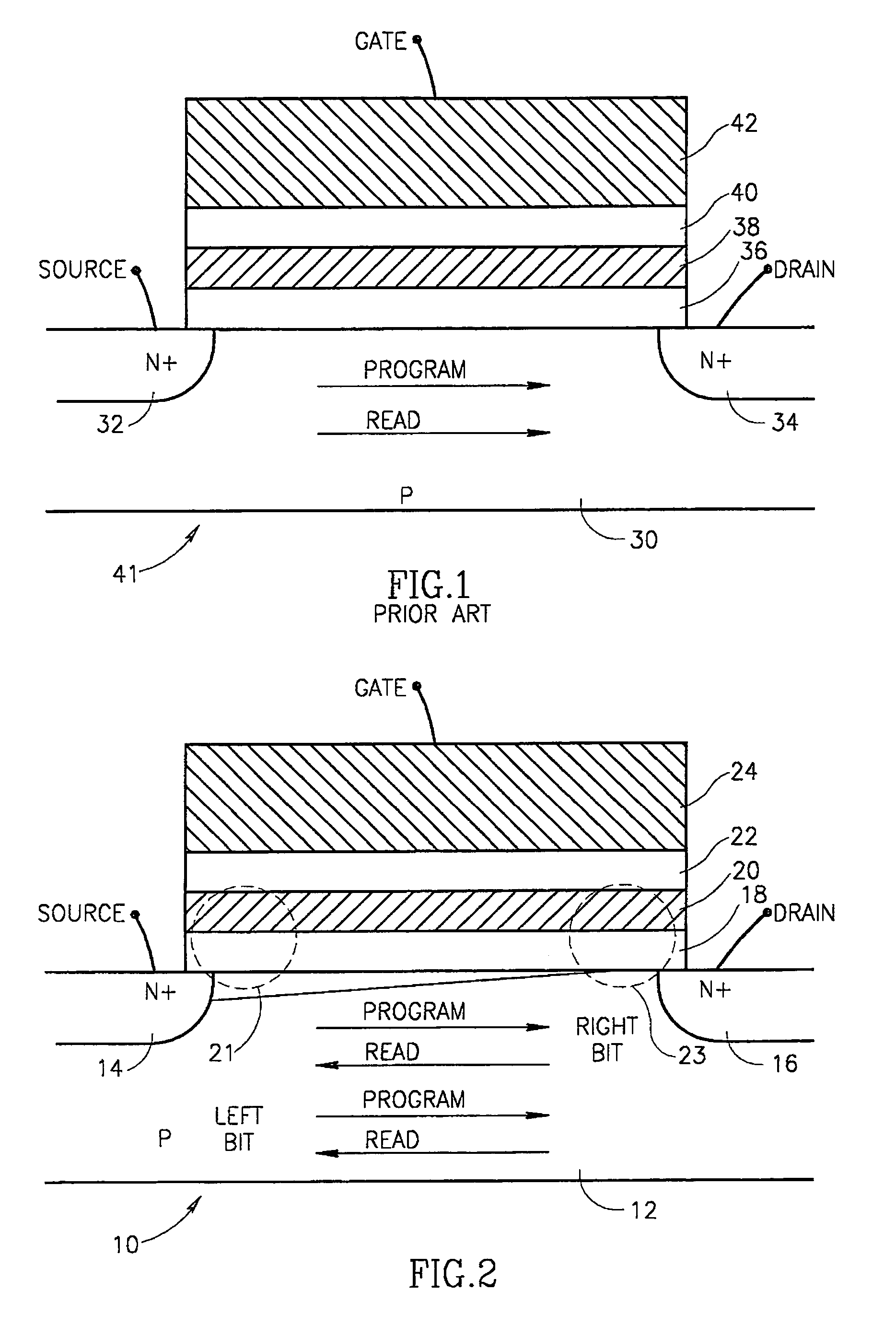

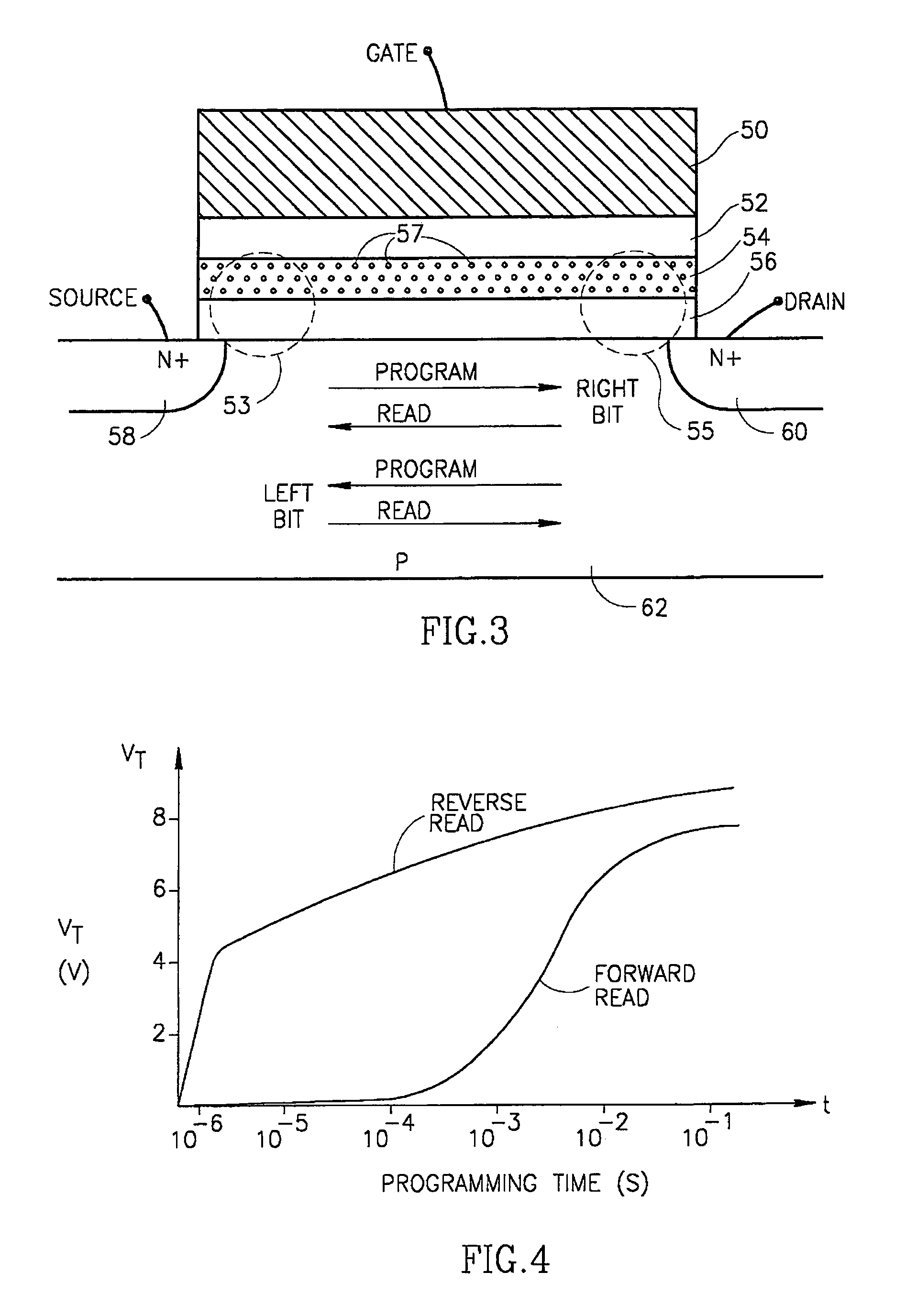

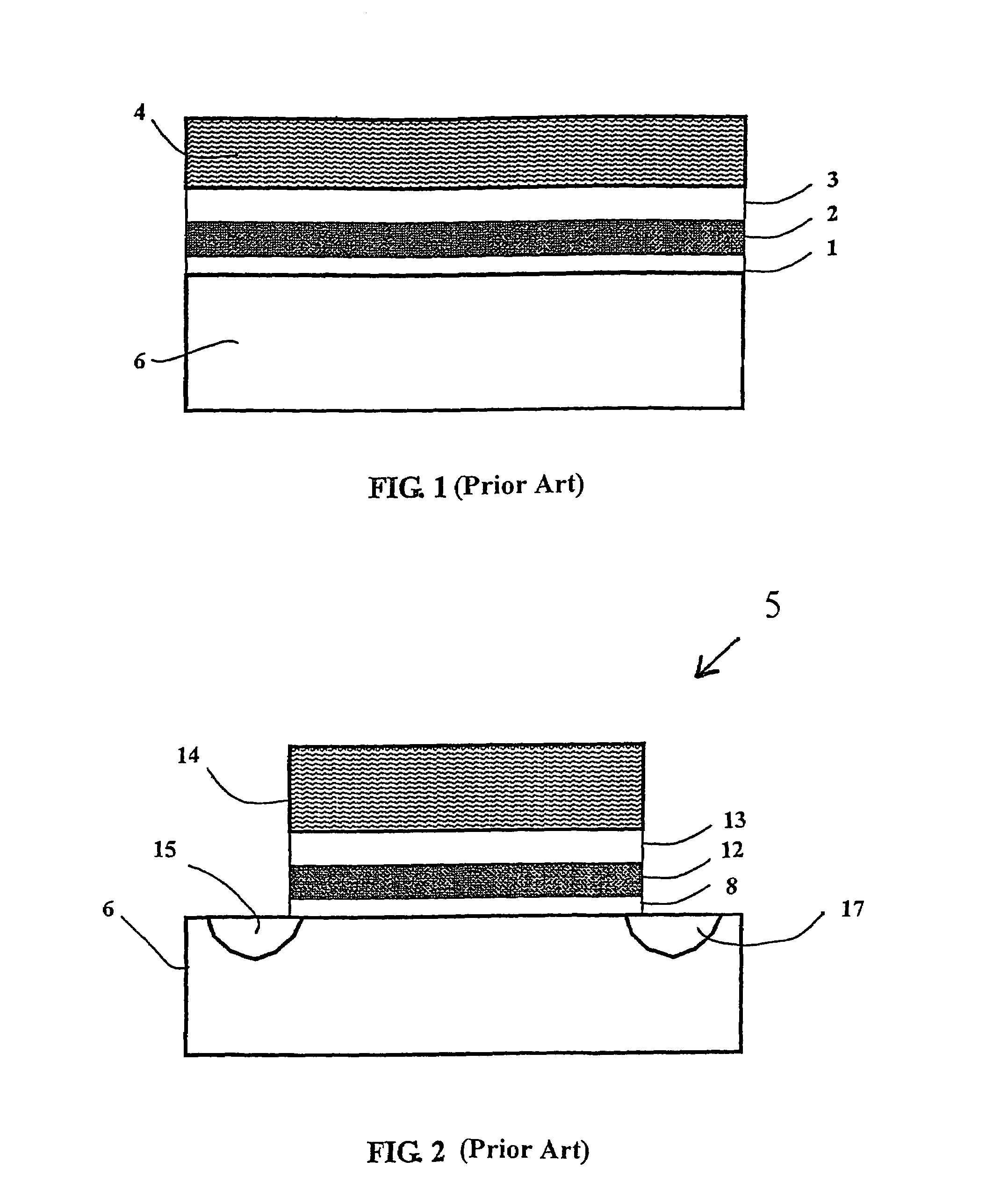

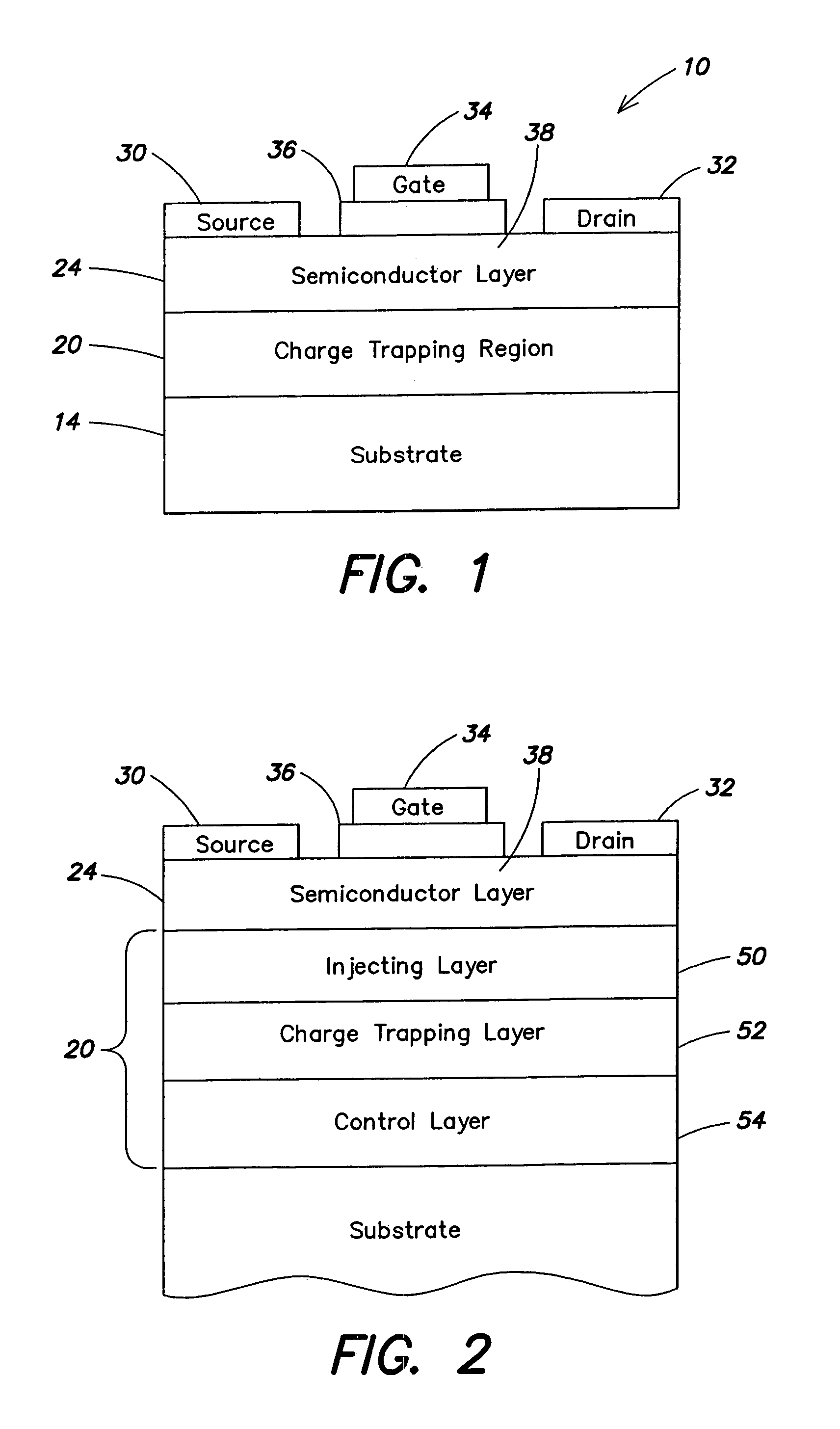

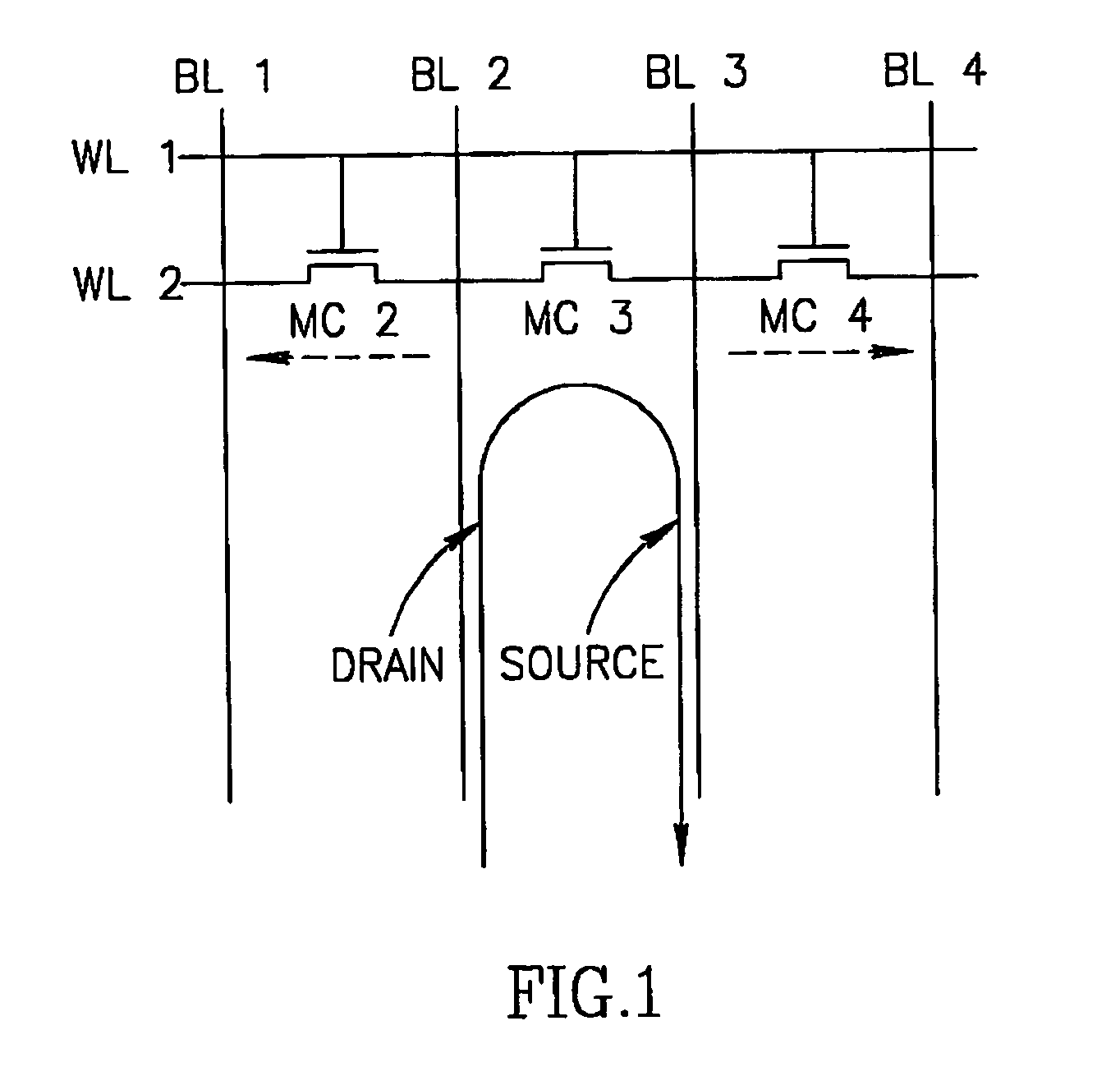

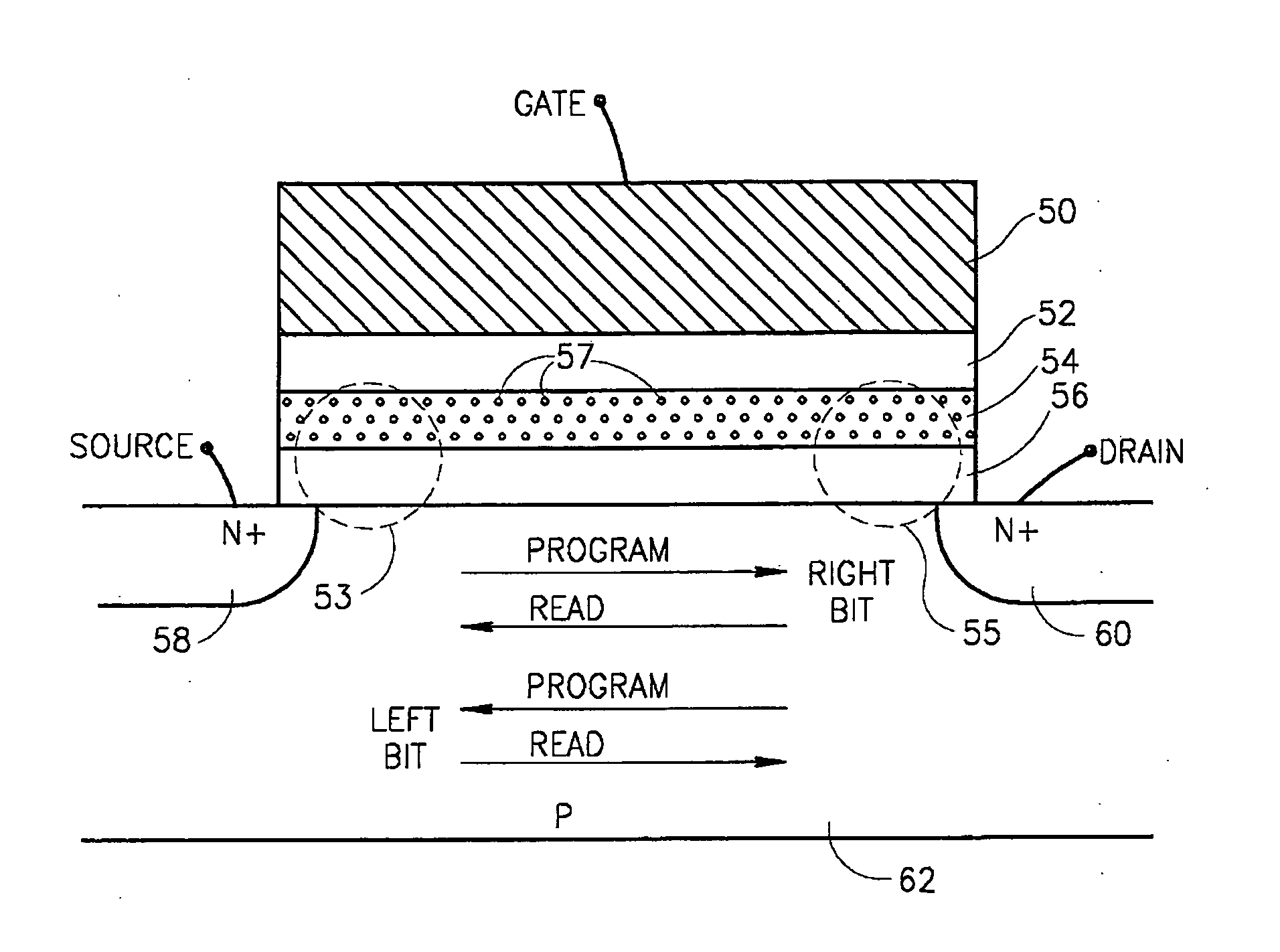

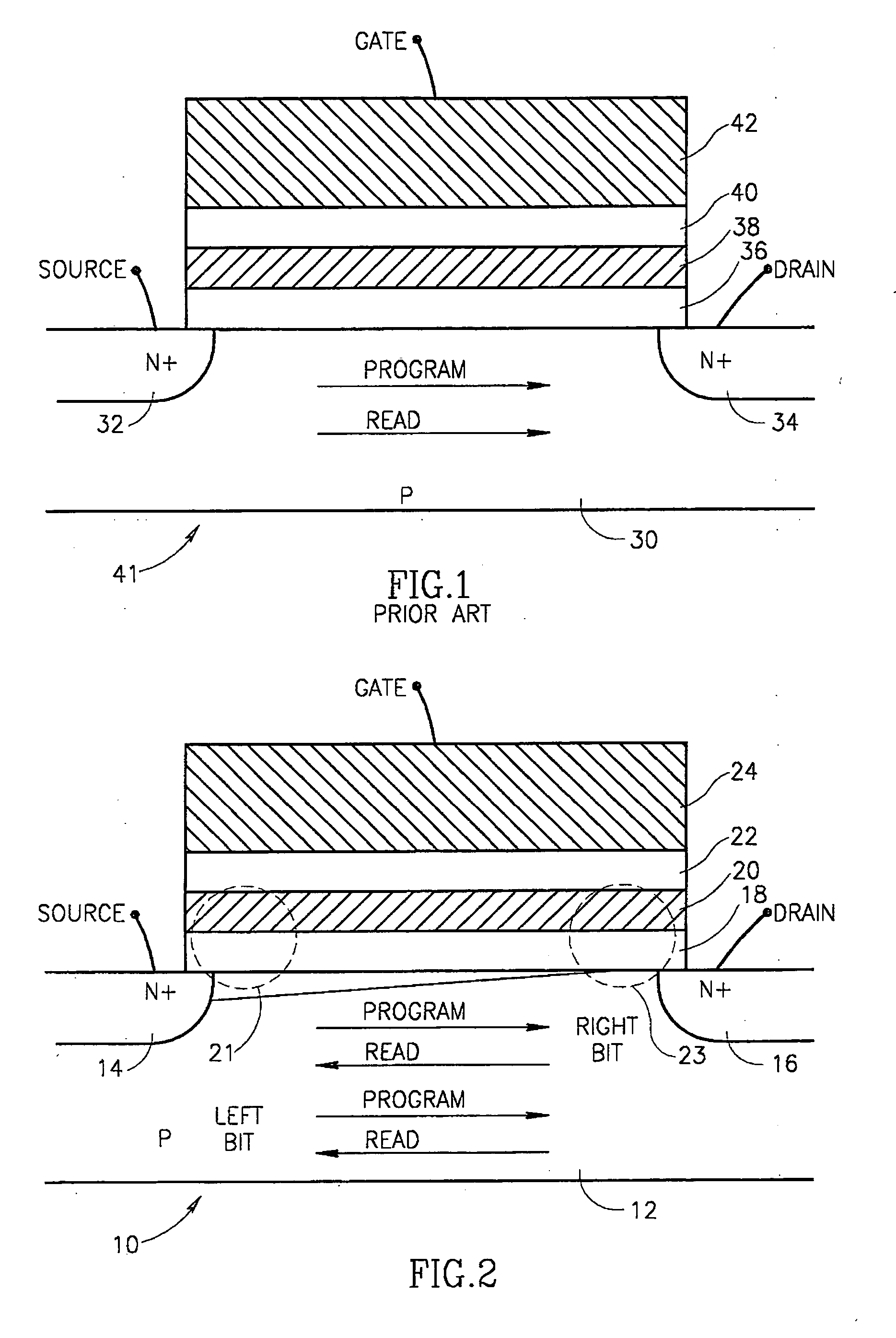

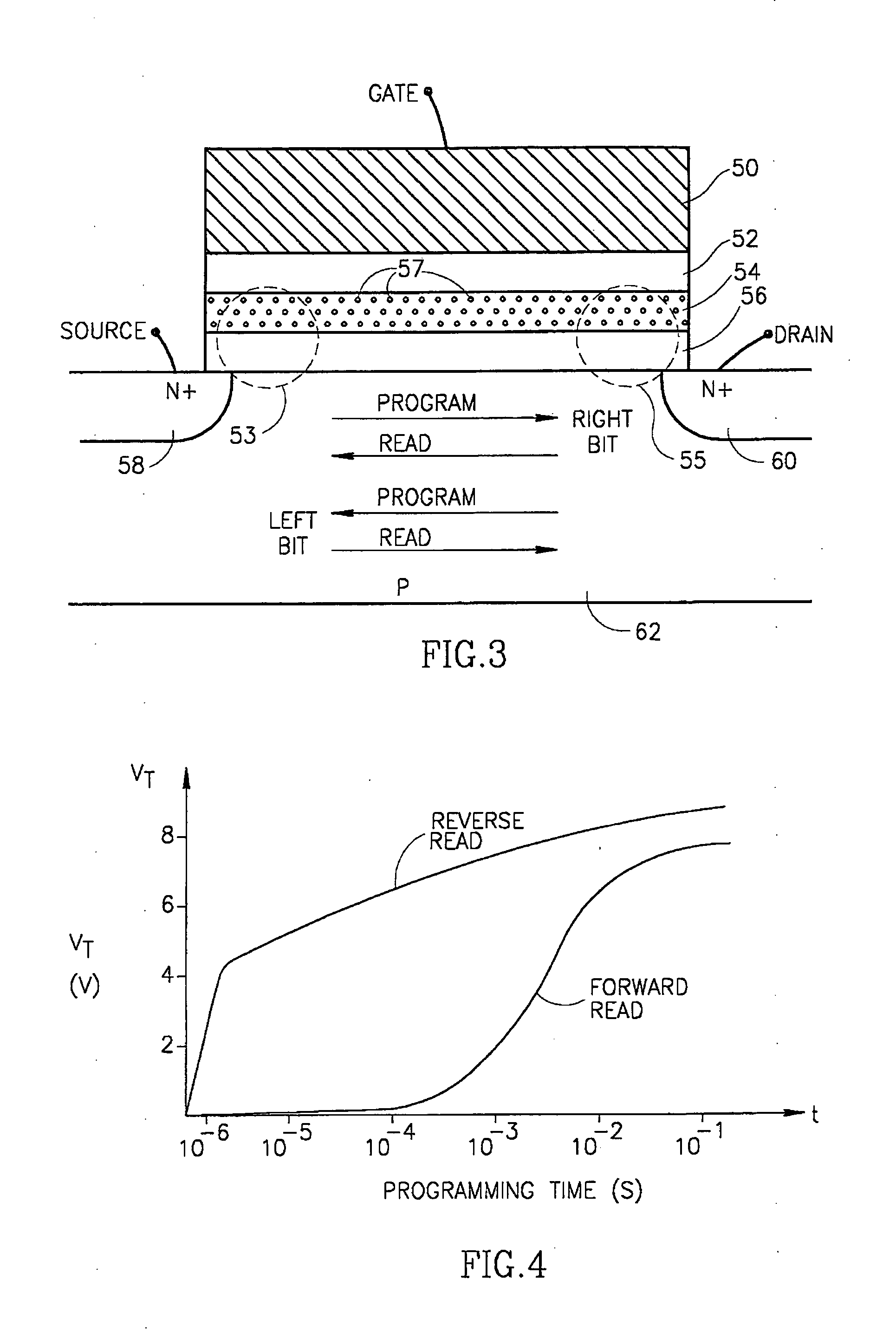

Two bit non-volatile electrically erasable and programmable semiconductor memory cell utilizing asymmetrical charge trapping

InactiveUS7116577B2Little effectShorten speedTransistorSolid-state devicesDielectricProgrammable read-only memory

A non-volatile electrically erasable programmable read only memory (EEPROM) capable of storing two bit of information having a nonconducting charge trapping dielectric, such as silicon nitride, sandwiched between two silicon dioxide layers acting as electrical insulators is disclosed. A left and a right bit are stored in physically different areas of the charge trapping layer, near left and right regions of the memory cell, respectively. Two bits are able to be programmed and read due to a combination of relatively low gate voltages with reading in the reverse direction. This greatly reduces the potential across the trapped charge region. This permits much shorter programming times by amplifying the effect of the charge trapped in the localized trapping region associated with each of the bits. In addition, both bits of the memory cell can be individually erased by applying suitable erase voltages to the gate and either left or right regions so as to cause electrons to be removed from the corresponding charge trapping region of the nitride layer.

Owner:SAIFUN SEMICON

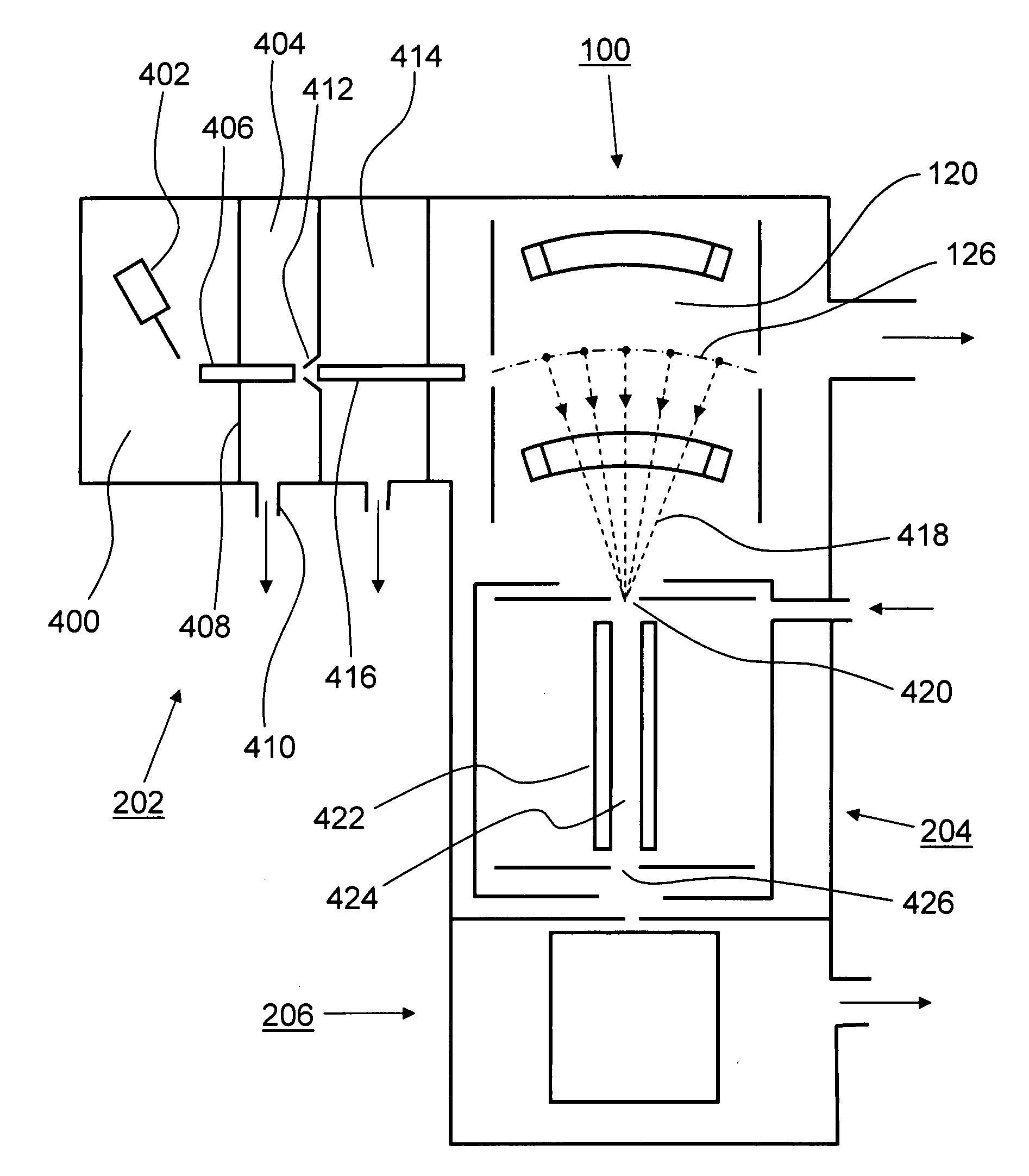

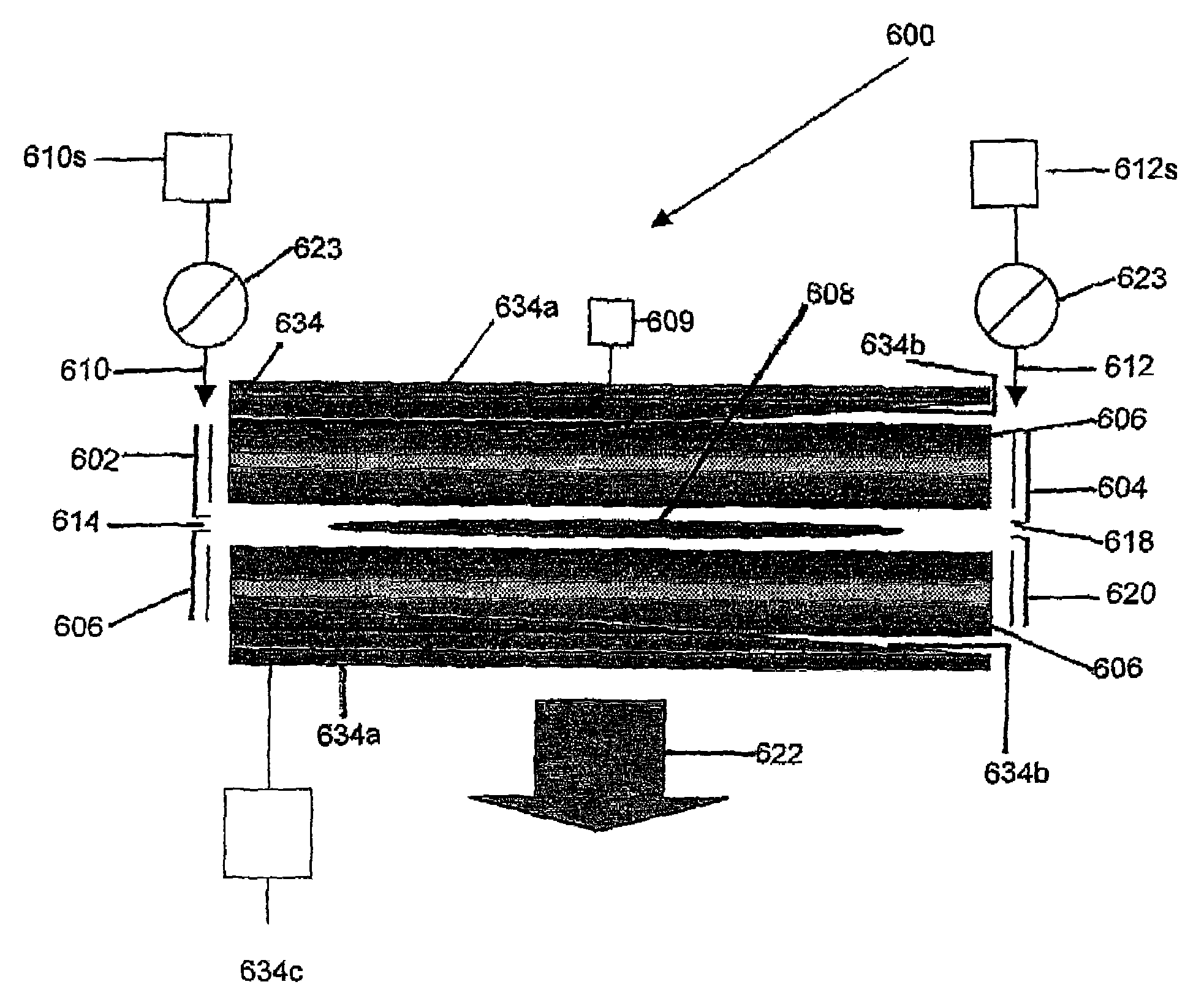

Tandem mass spectrometer

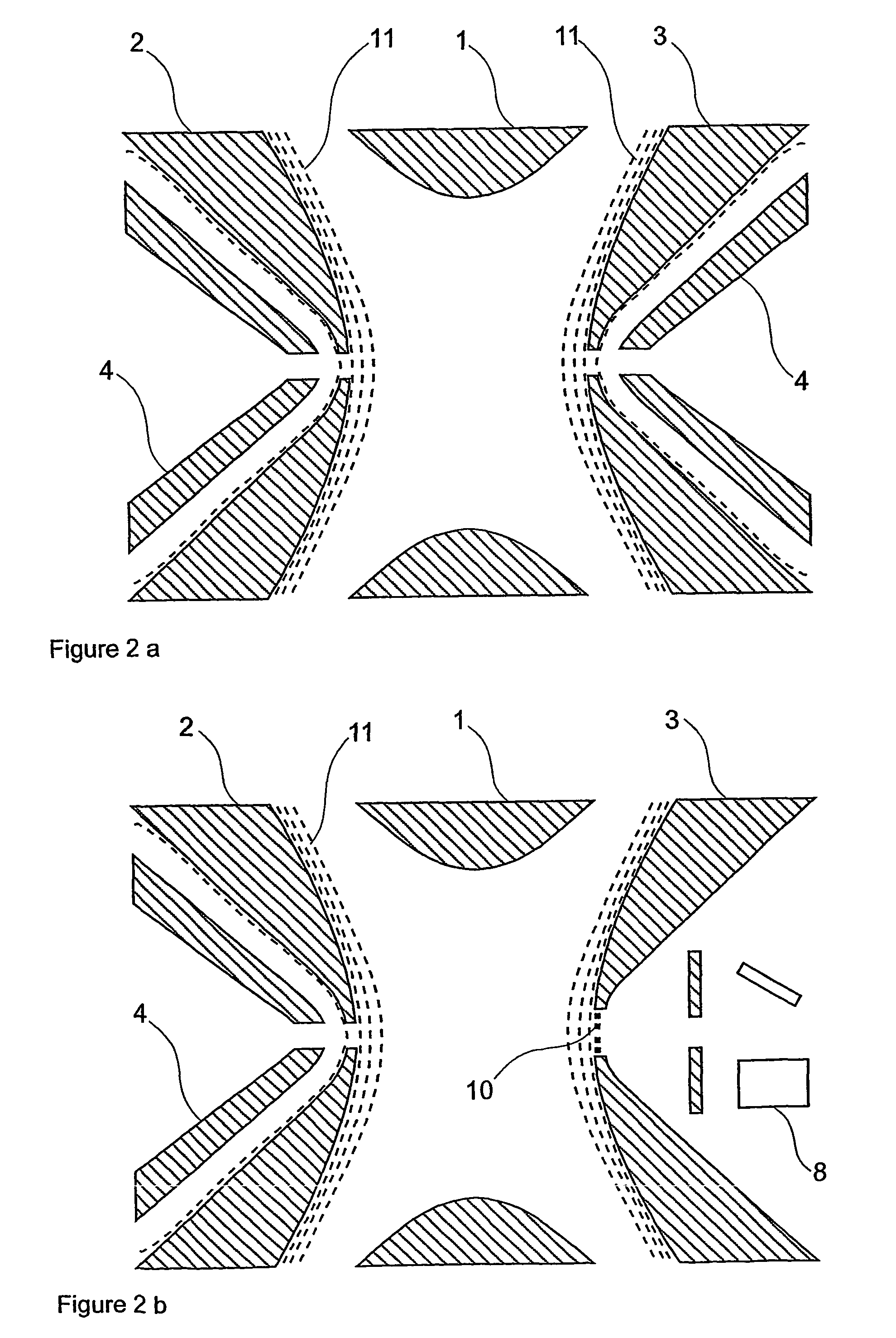

A tandem mass spectrometer includes a two-dimensional ion trap that has an elongated ion-trapping region extending along a continuously curving path between first and second opposite ends thereof. The elongated trapping region has a central axis that is defined substantially parallel to the curved path and that extends between the first and second opposite ends. The two-dimensional ion trap is configured for receiving ions through the first end and for mass selectively ejecting the ions along a direction that is orthogonal to the central axis, such that the ejected ions are directed generally toward a common point. The tandem mass spectrometer also includes a collision cell having an ion inlet that is disposed about the common point for receiving the ions that are ejected therefrom and for causing at least a portion of the ions to undergo collisions and form product ions by fragmentation. A mass analyzer in communication with the collision cell receives the product ions from the collision cell and obtains product ion mass spectra with a rapid scan rate. In this way, a plurality of product ion spectra may be obtained for a large number of precursor ions in a sample without the need for data-dependent operation.

Owner:THERMO FINNIGAN

Non-volatile memory cell having a silicon-oxide nitride-oxide-silicon gate structure

A non-volatile memory cell able to be written in a first direction and read in a second direction is described. The memory cell includes one or two charge trapping regions located near either the source or the drain, or both the source and the drain. During a programming operation, electrons can be injected into the charge trapping region by hot electron injection. During an erasing operation, holes can be injected into the charge trapping region. Embodiments of the invention include a charge trapping region that is overlapped by the control gate only to an extent where the electrons that were injected during a programming operation can be erased later by injecting holes in the charge trapping region.

Owner:SAMSUNG ELECTRONICS CO LTD

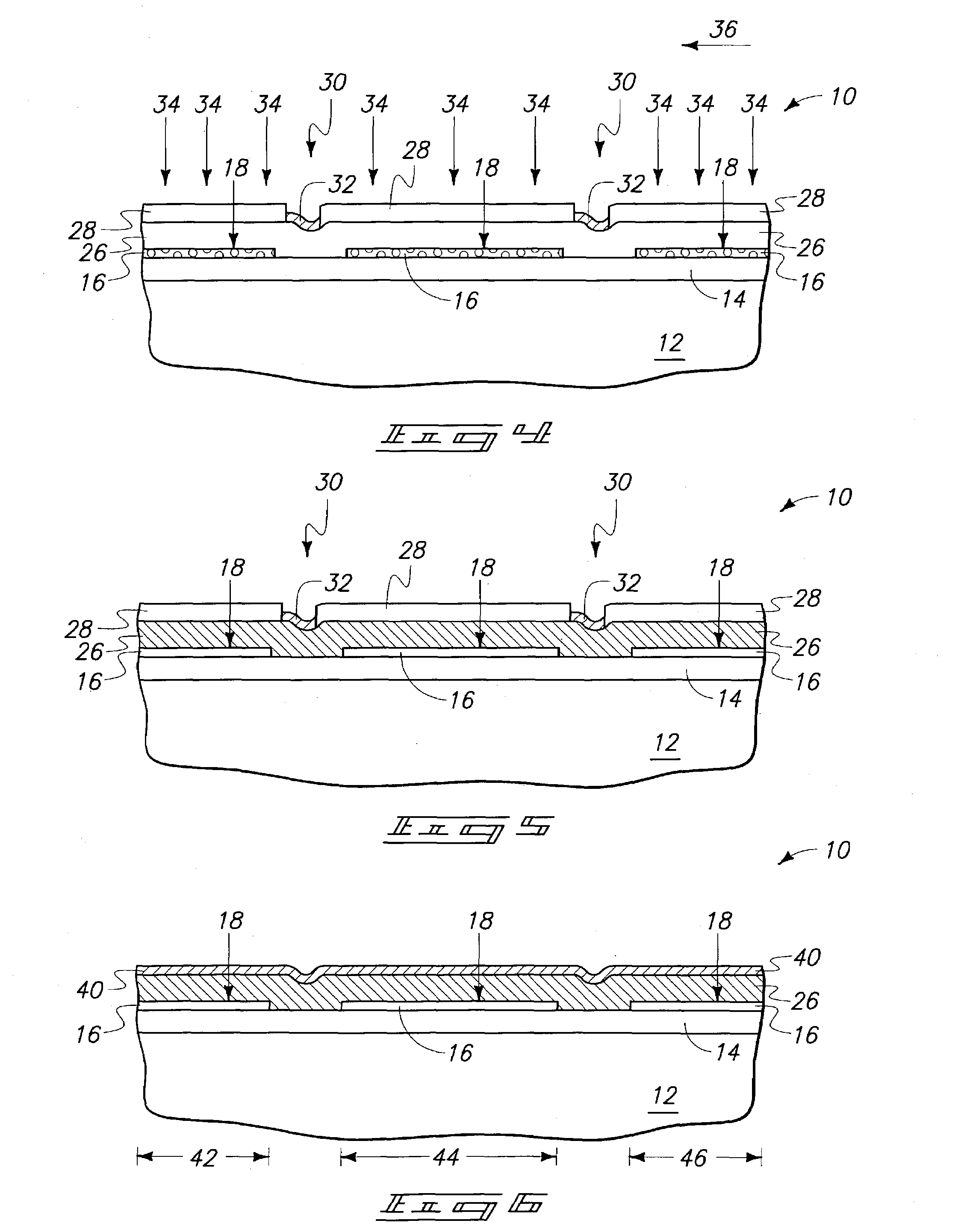

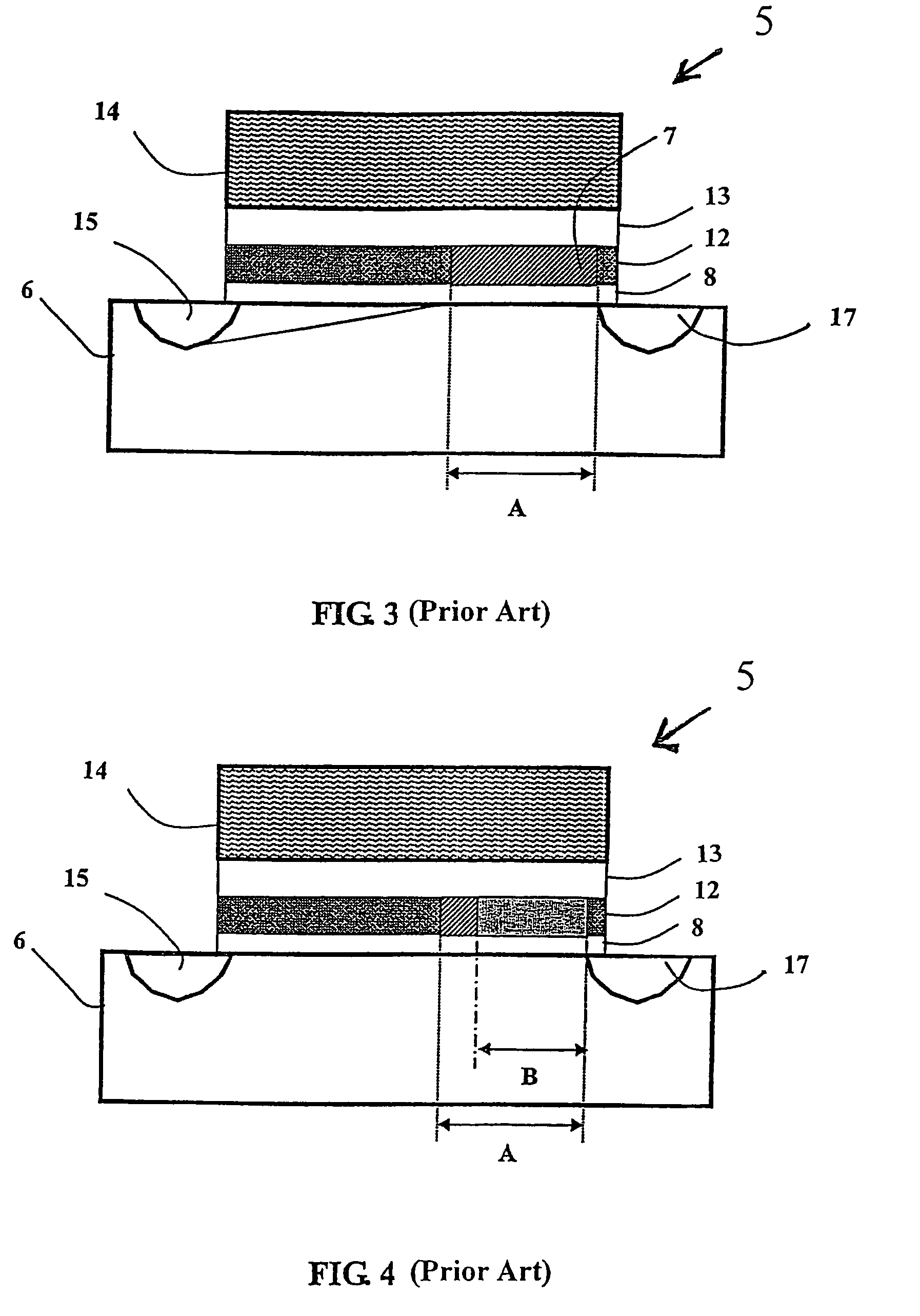

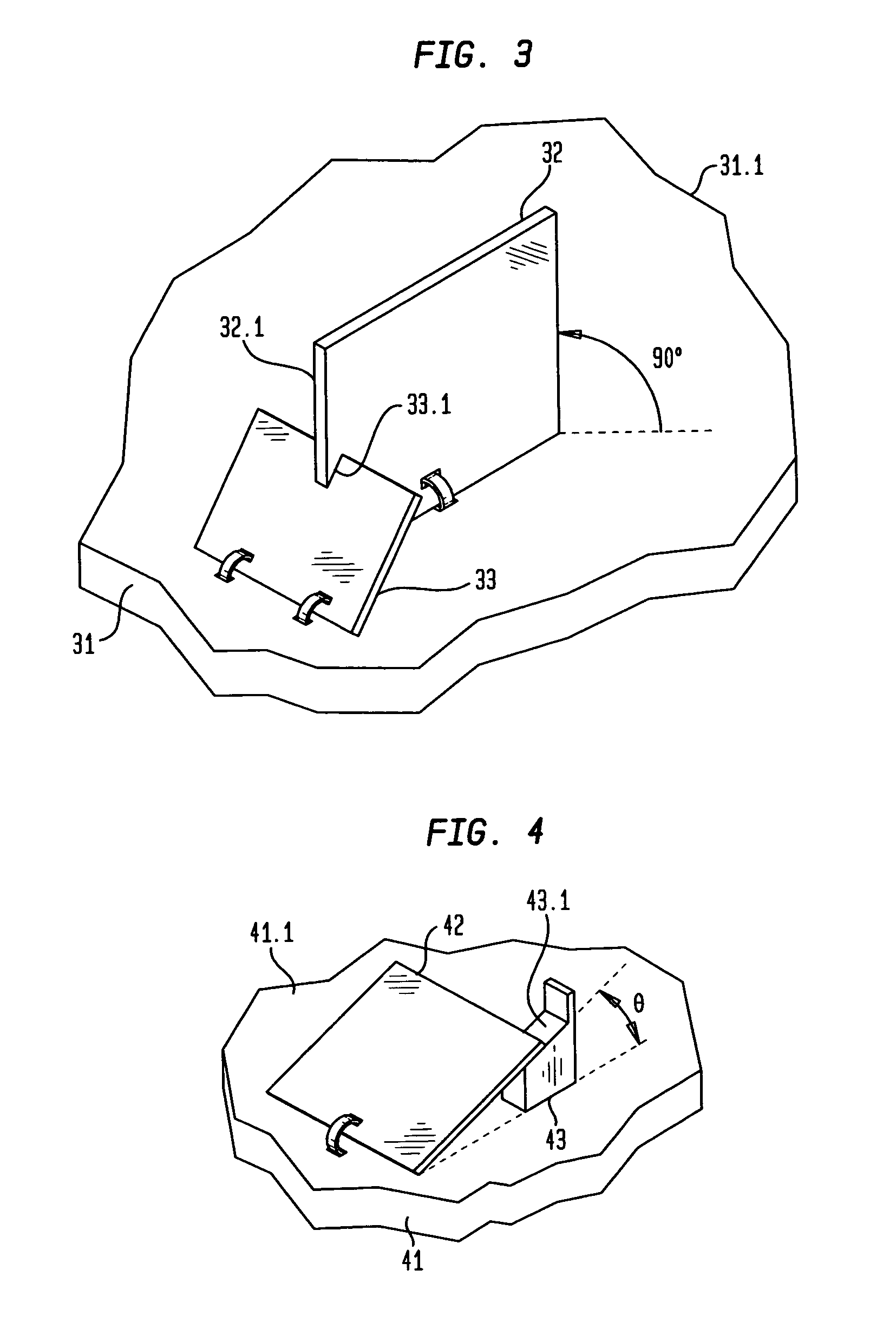

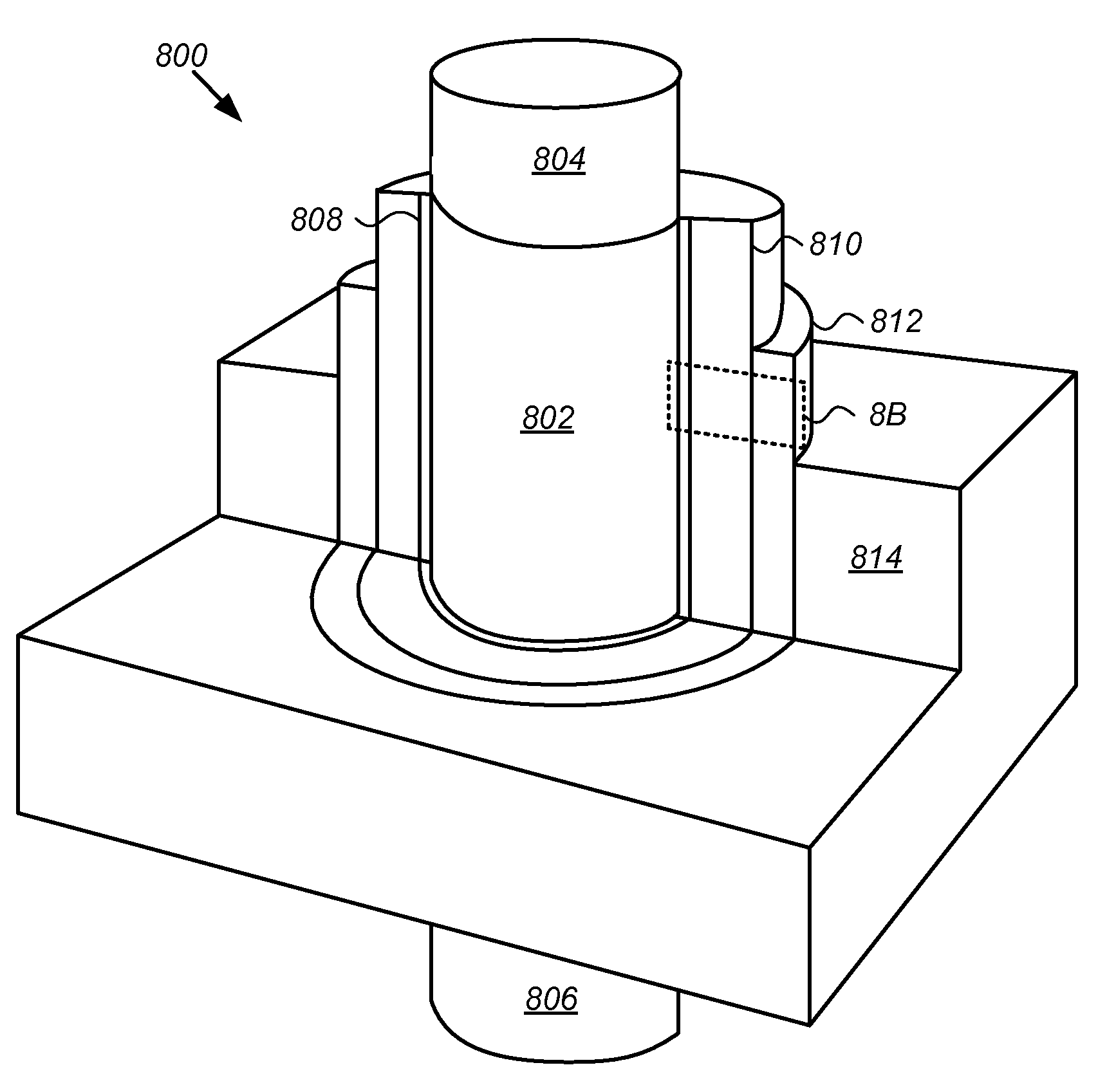

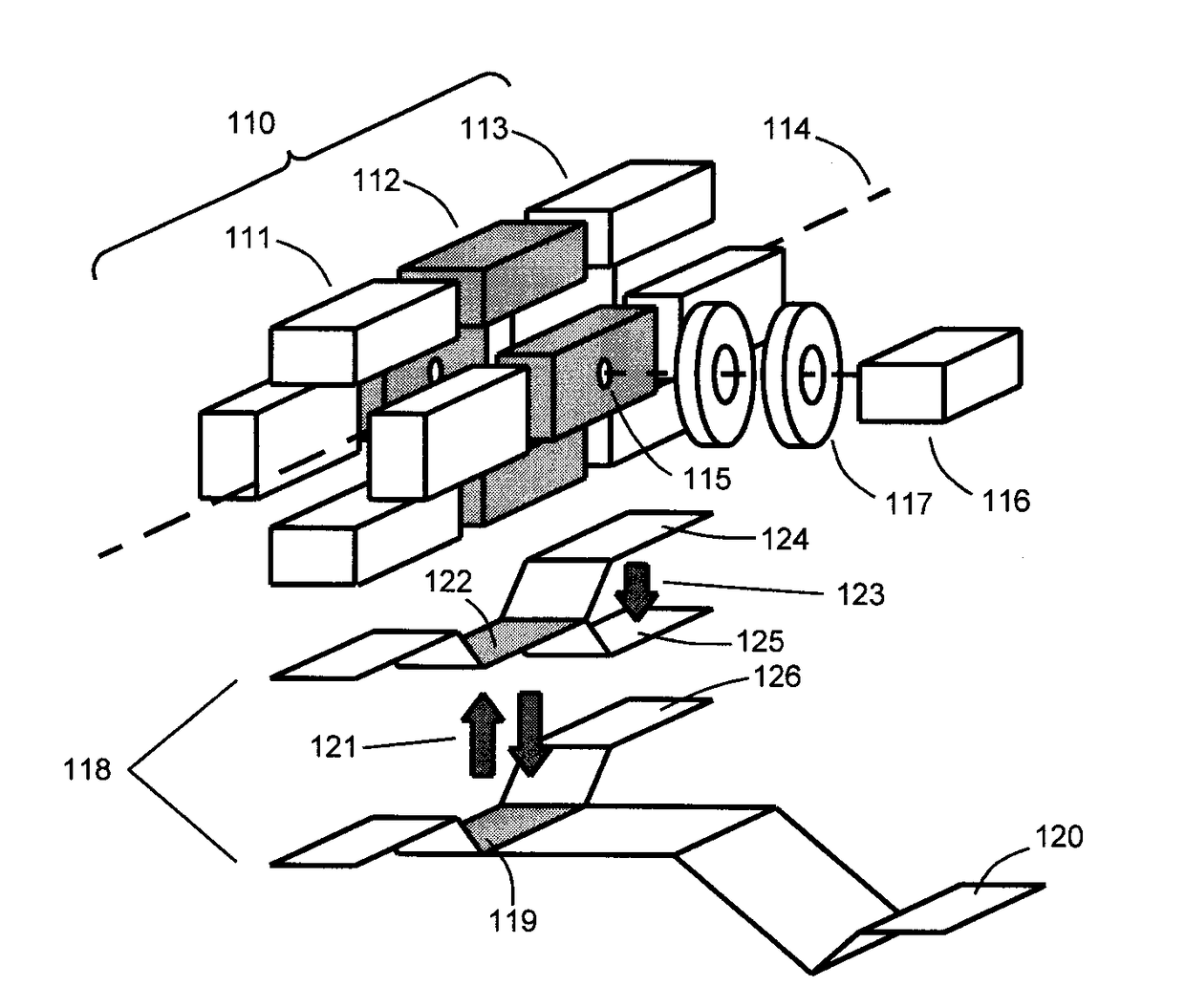

Wafer supported, out-of-plane ion trap devices

ActiveUS7012250B1Stability-of-path spectrometersIsotope separationShift registerElectrical conductor

An ion trap device comprises a wafer that supports at least one plate forming an ion trapping region therebetween. The plate has an electrically insulating surface and a multiplicity of electrodes disposed on the insulating surface. The electrodes form at least one ion trap in the trapping region when suitable voltages are applied to the electrodes via conductors coupled to the wafer. The device has a multiplicity of ports for introducing ions into the trapping region and for extracting ions from that region. In embodiments that include a multiplicity of such plates, a first one of the plates is oriented at a non-zero angle to the major surface of the wafer and is rotateably mounted on that surface. In one embodiment, at least two of the plates form an elongated micro-channel having an axis of ion propagation, and the electrodes on at least one of the two plates are segmented along the direction of the axis, thereby forming a multiplicity of ion traps along the axis. A controller applies suitable voltage (e.g., sequentially) to the segmented electrodes, thereby shifting ions from one trap to another. Preferably, the electrodes on the two plates are segmented. Applications to mass spectrometers and shift registers are described.

Owner:LUCENT TECH INC

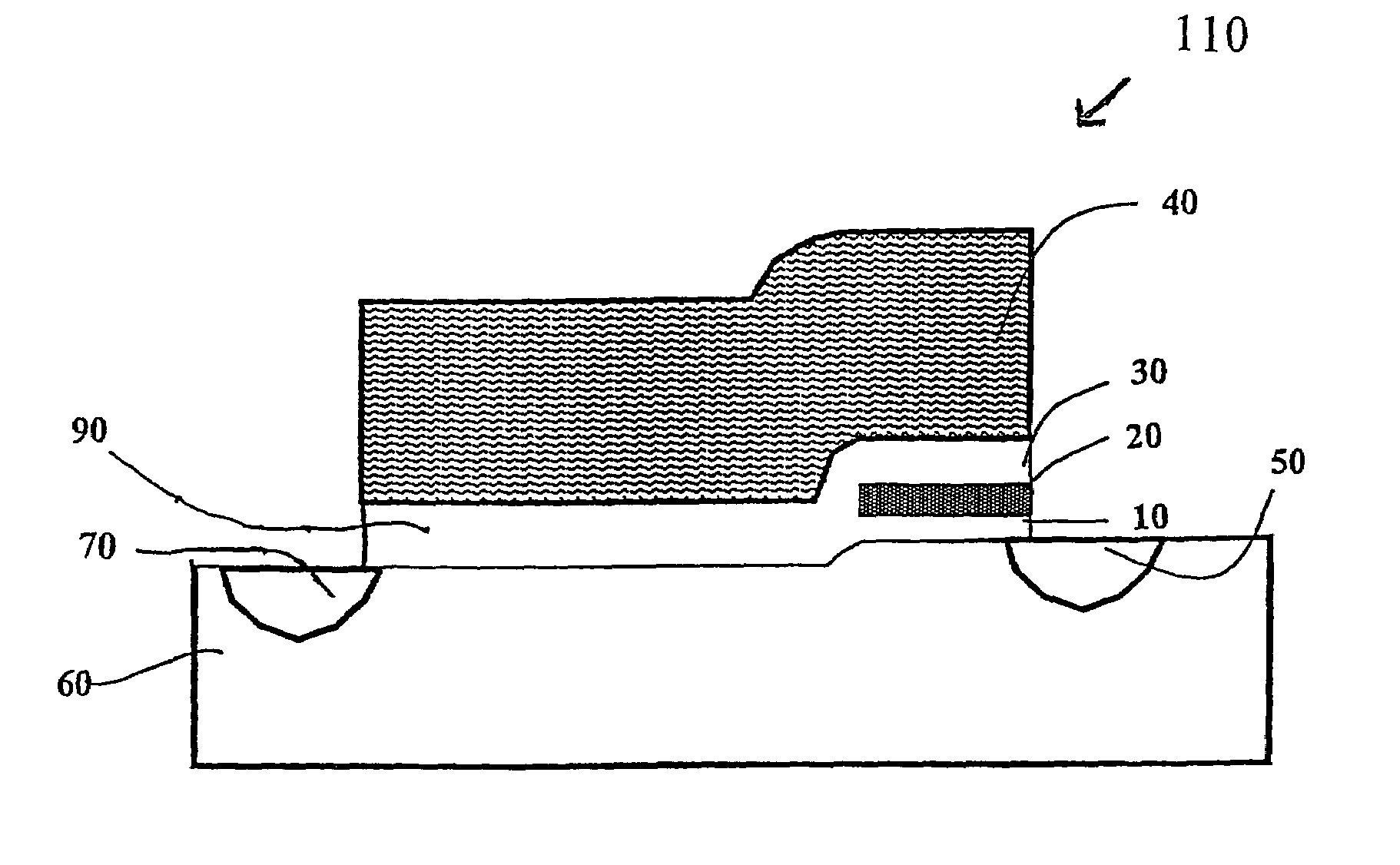

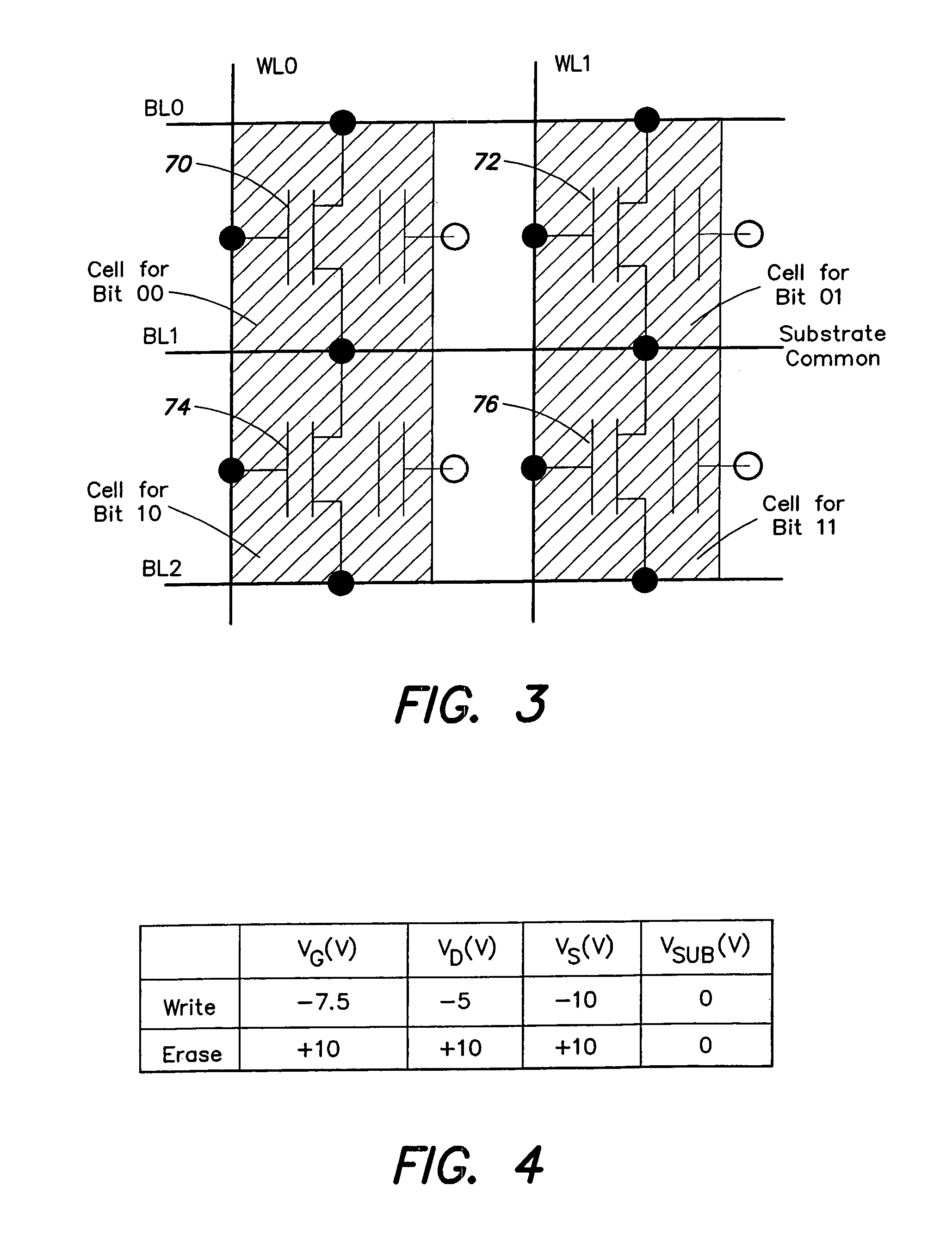

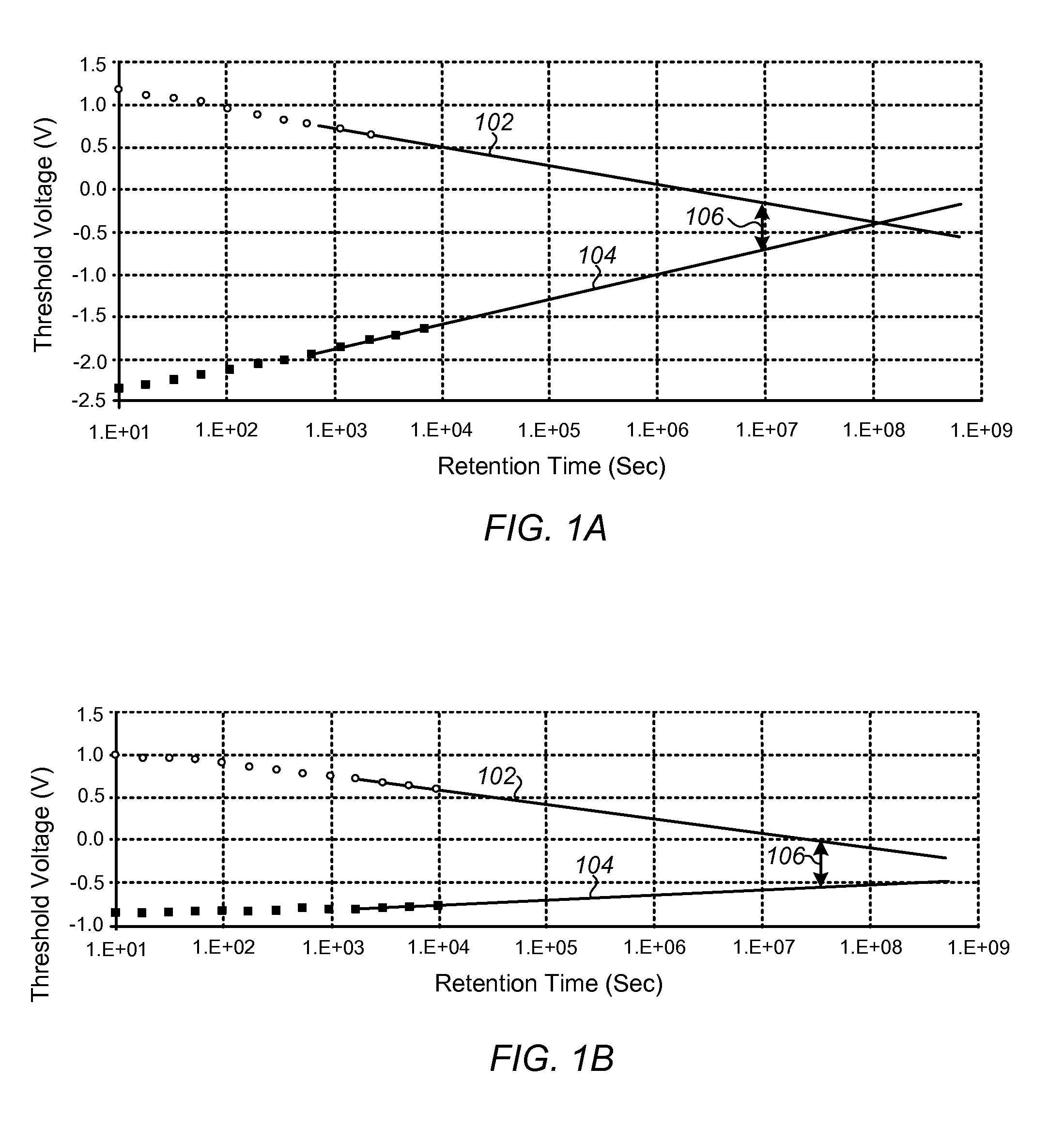

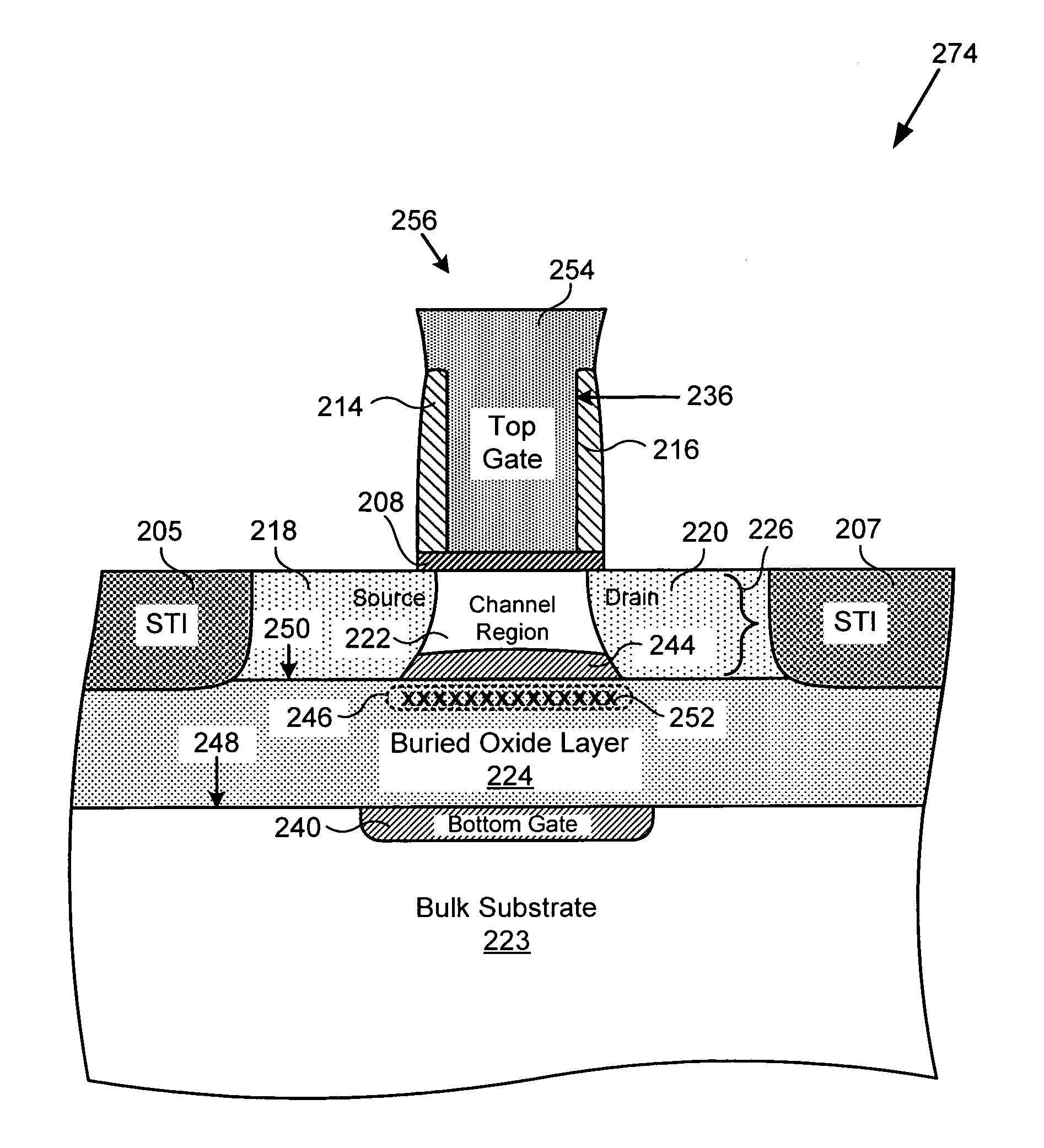

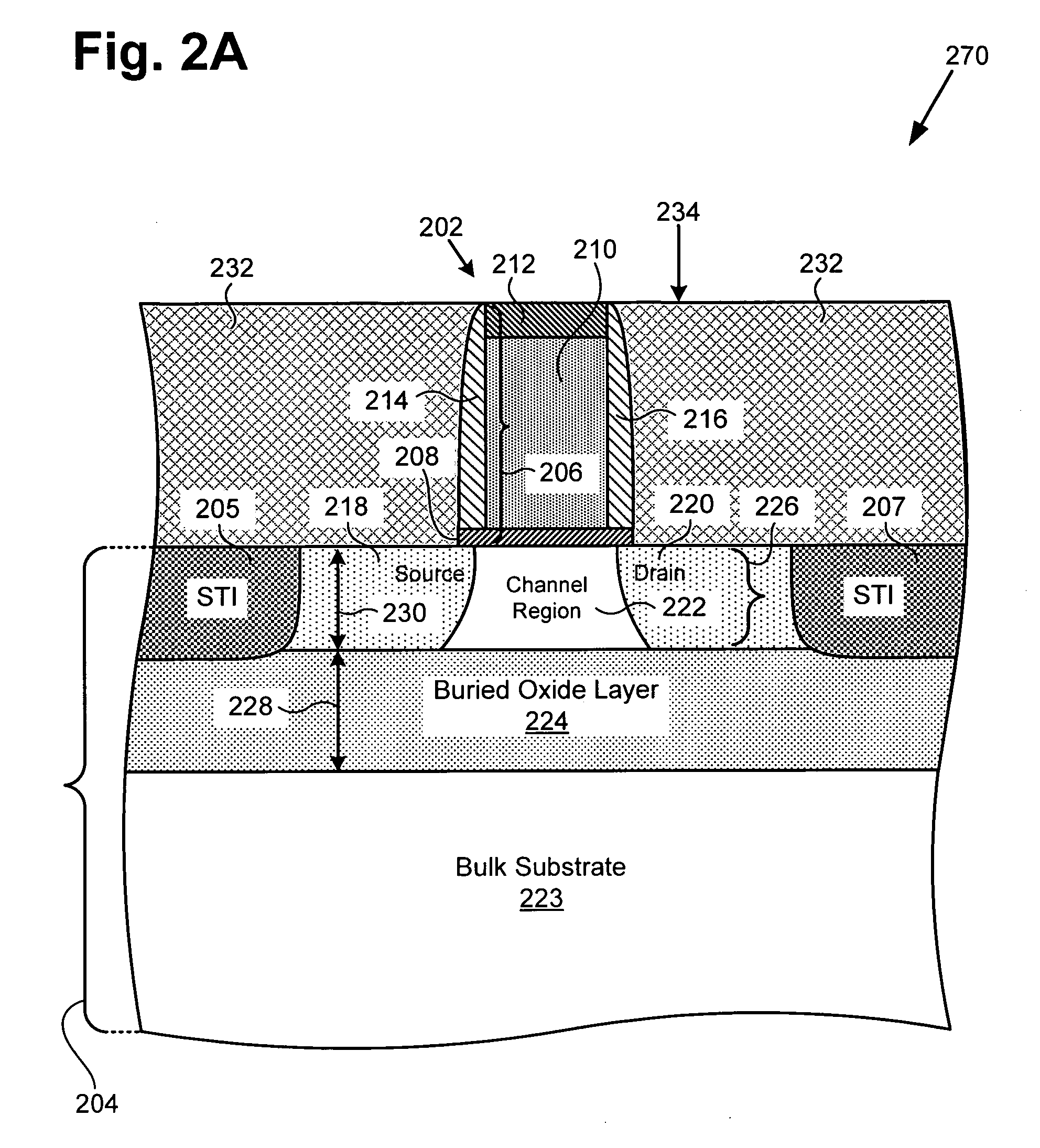

Scalable nano-transistor and memory using back-side trapping

According to an aspect of the invention, a device structure is provided where charging and discharging occur in a trapping region formed by a stack of films that is placed on the back of a thin silicon channel. Uncoupling the charging mechanisms that lead to the memory function from the front gate transistor operation allows efficient scaling of the front gate. But significantly more important is a unique character of these devices: these structures can be operated both as a transistor and as a memory. The thin active silicon channel and the thin front oxide provide the capability of scaling the structure to tens of nanometers, and the dual function of the device is obtained by using two voltage ranges that are clearly distinct. At small voltages the structure operates as a normal transistor, and at higher voltages the structure operates as a memory device.

Owner:CORNELL RES FOUNDATION INC

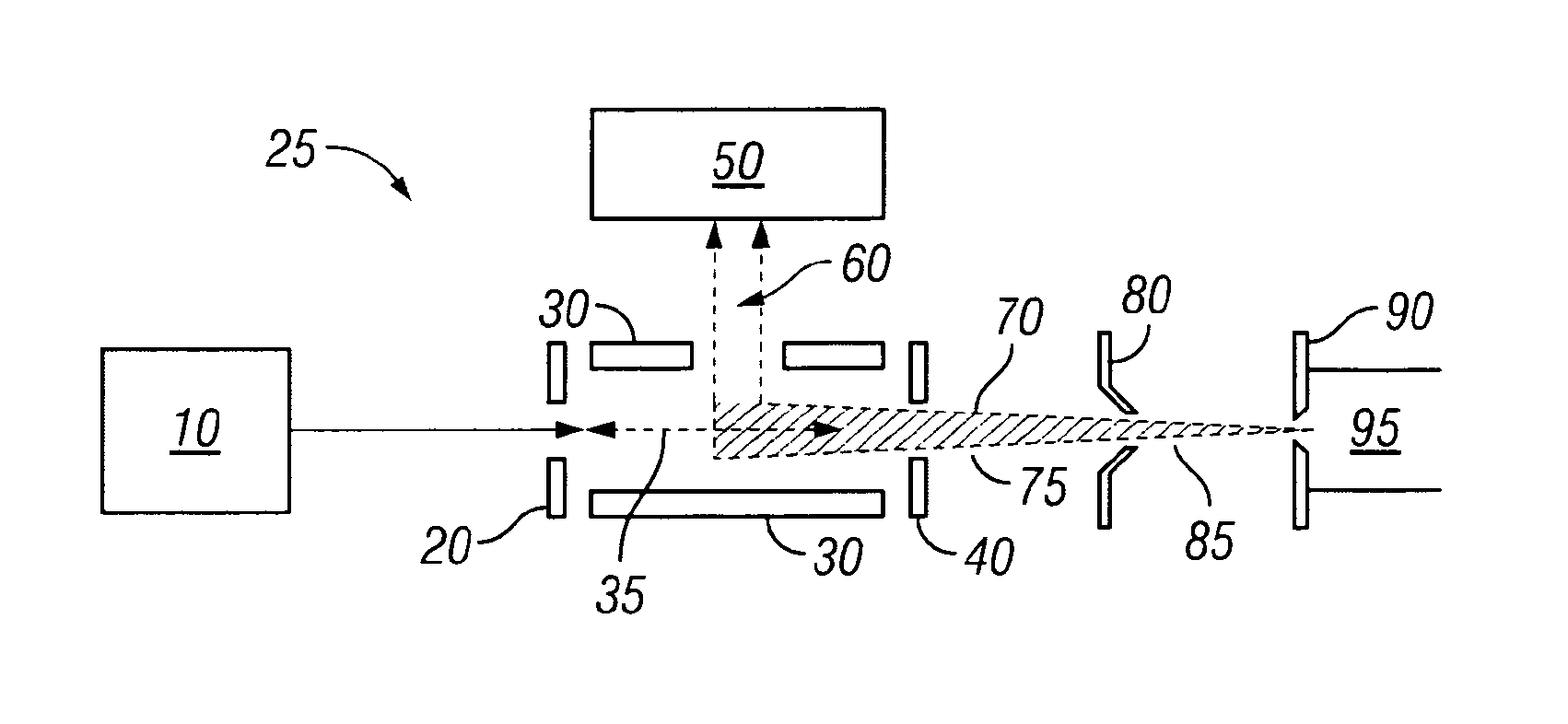

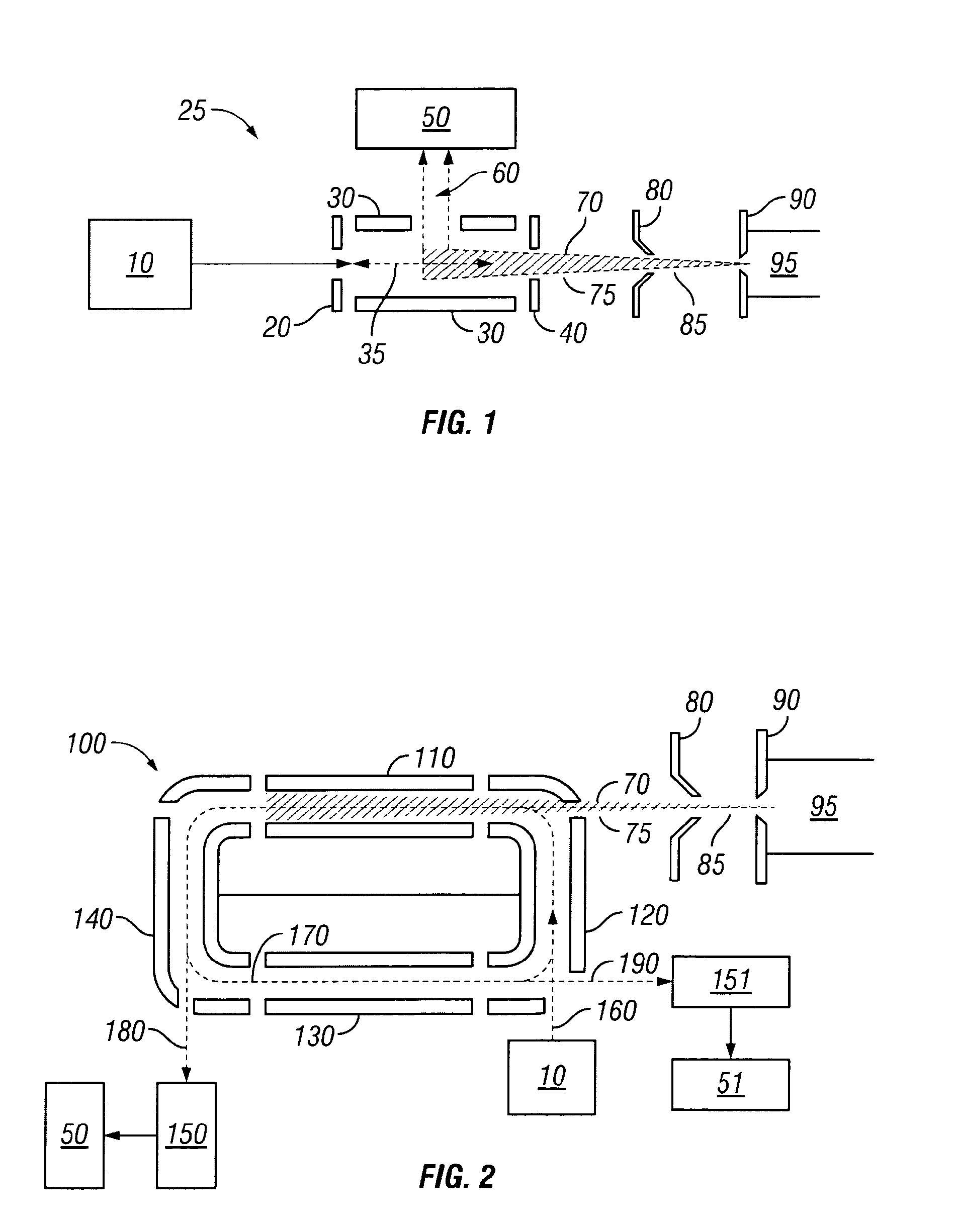

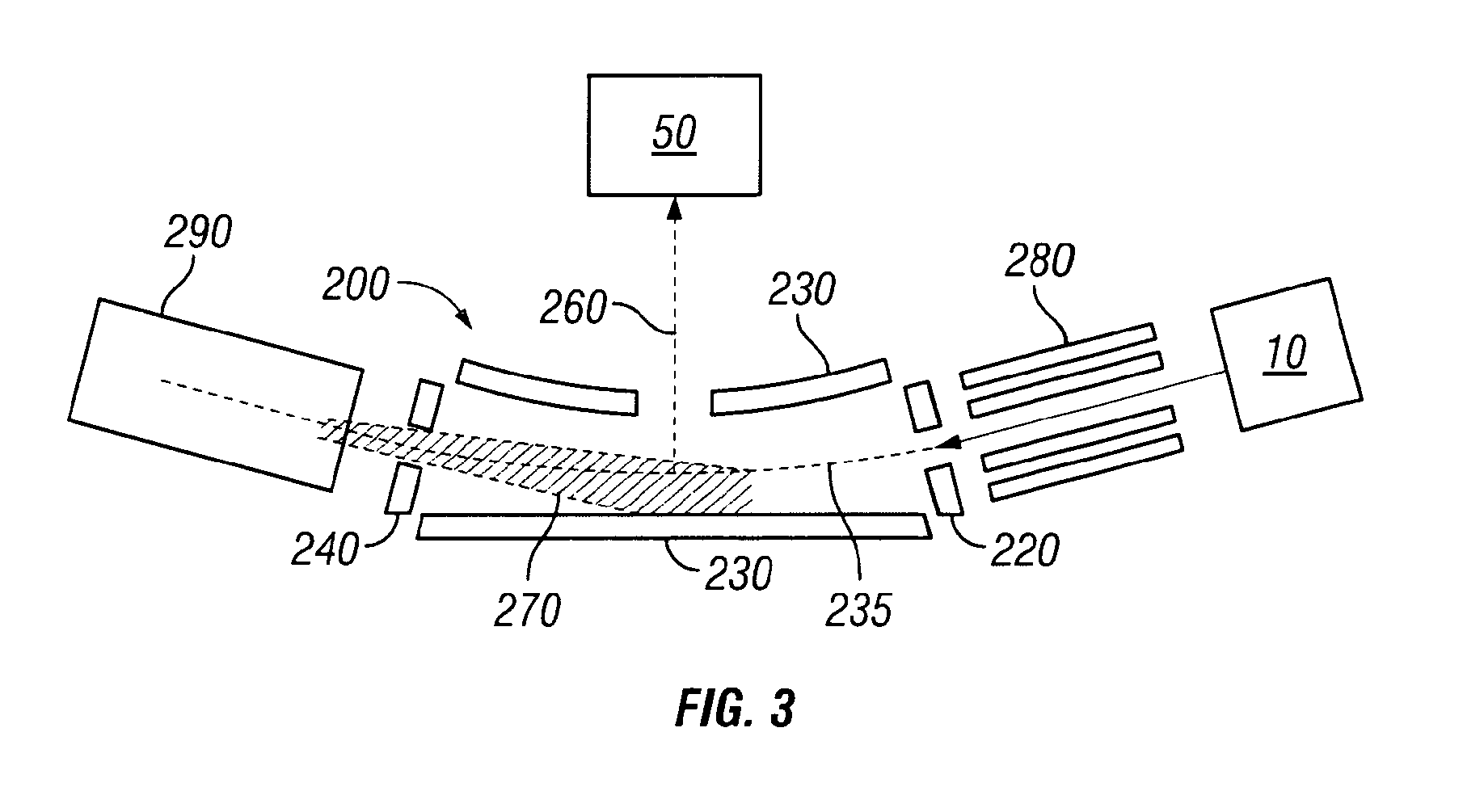

Optical trap using a focused hollow-beam for trapping and holding both absorbing and non-absorbing airborne particles

ActiveUS20160260513A1MicroscopesNeutron particle radiation pressure manipulationLight beamComputational physics

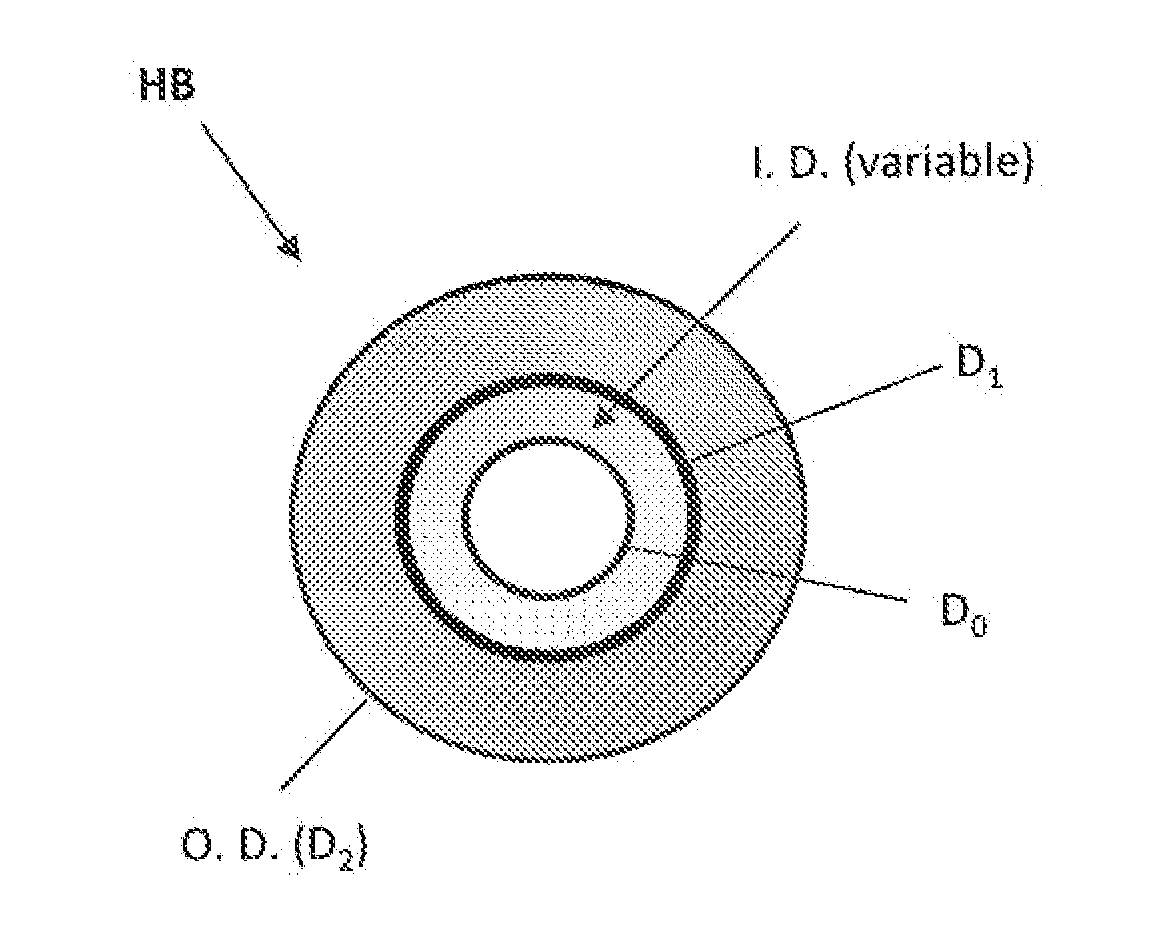

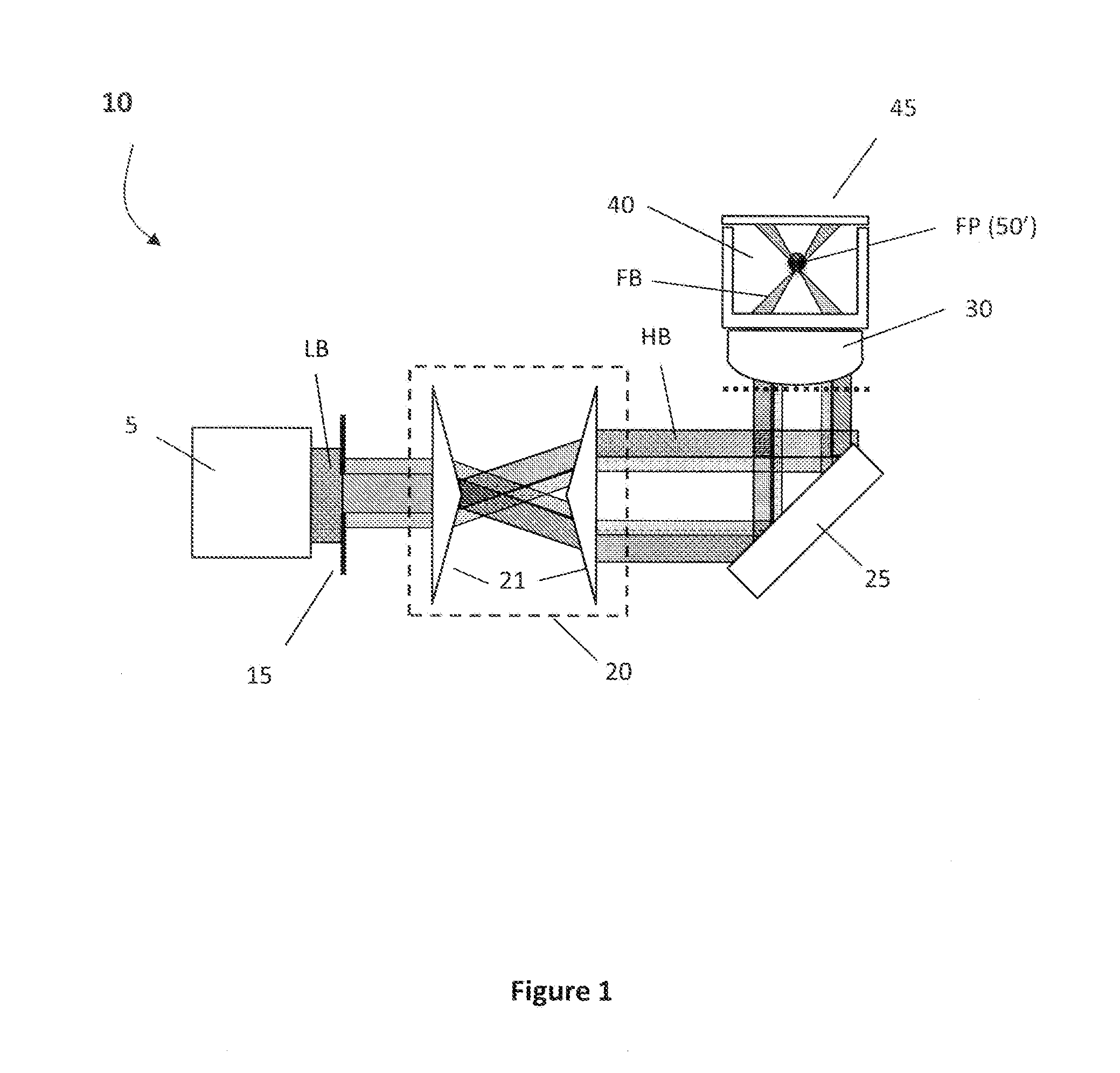

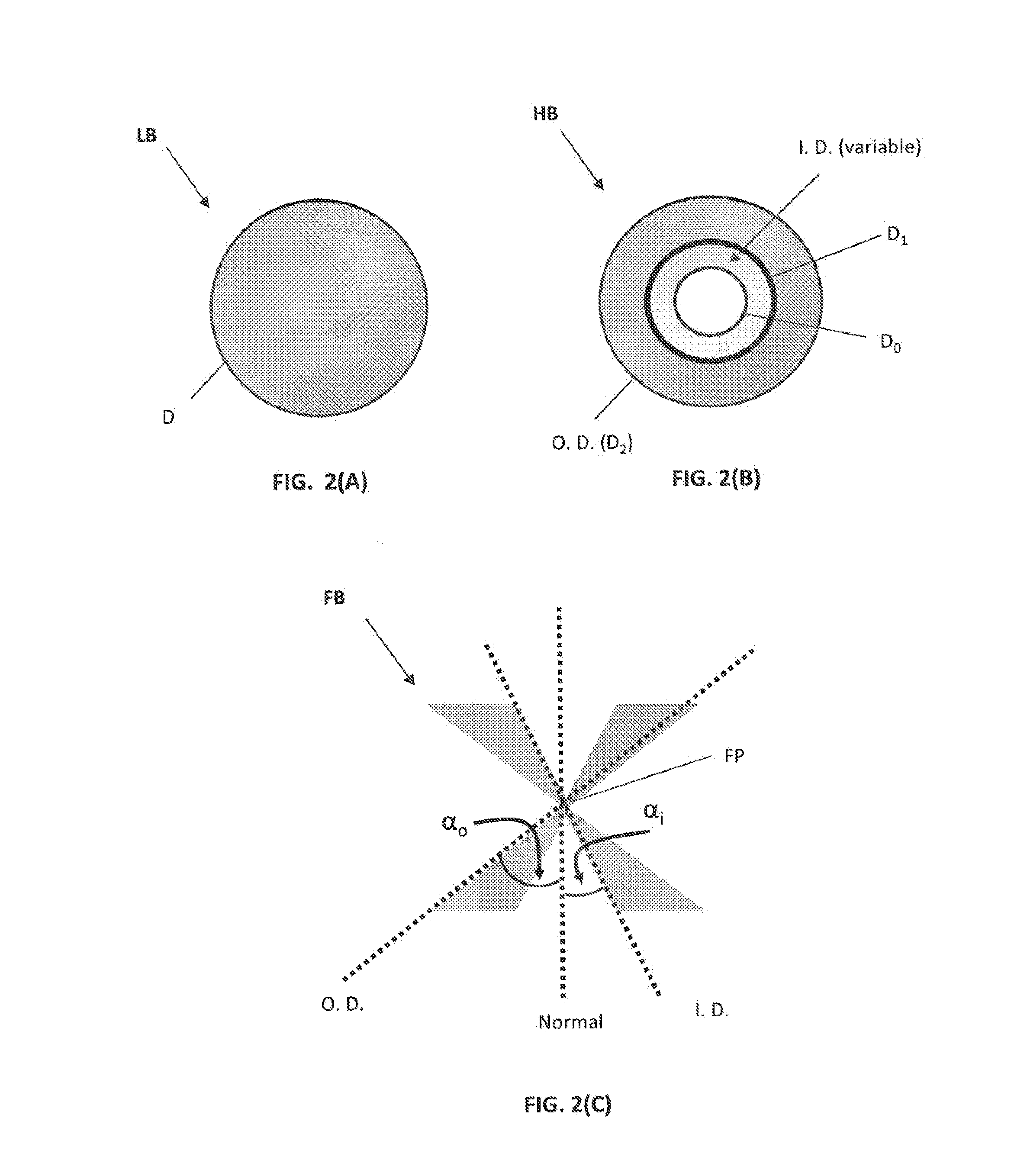

Embodiments of the present invention are directed to systems and methods for trapping and holding airborne particles. In the various embodiments, an optical trap is provided which uses a focused hollow-beam for trapping and holding both absorbing and non-absorbing airborne particles. The optical trap comprises: a trapping region where a particle can be present to be trapped; a light source for generating a coherent beam of light; optics for forming a hollow beam having a ring geometry from the coherent beam of light; and a focusing element for focusing the hollow beam to a point in the trapping region. In this arrangement, the particle is trapped at or near the focal point of the focused hollow beam.

Owner:US SEC THE ARMY THE

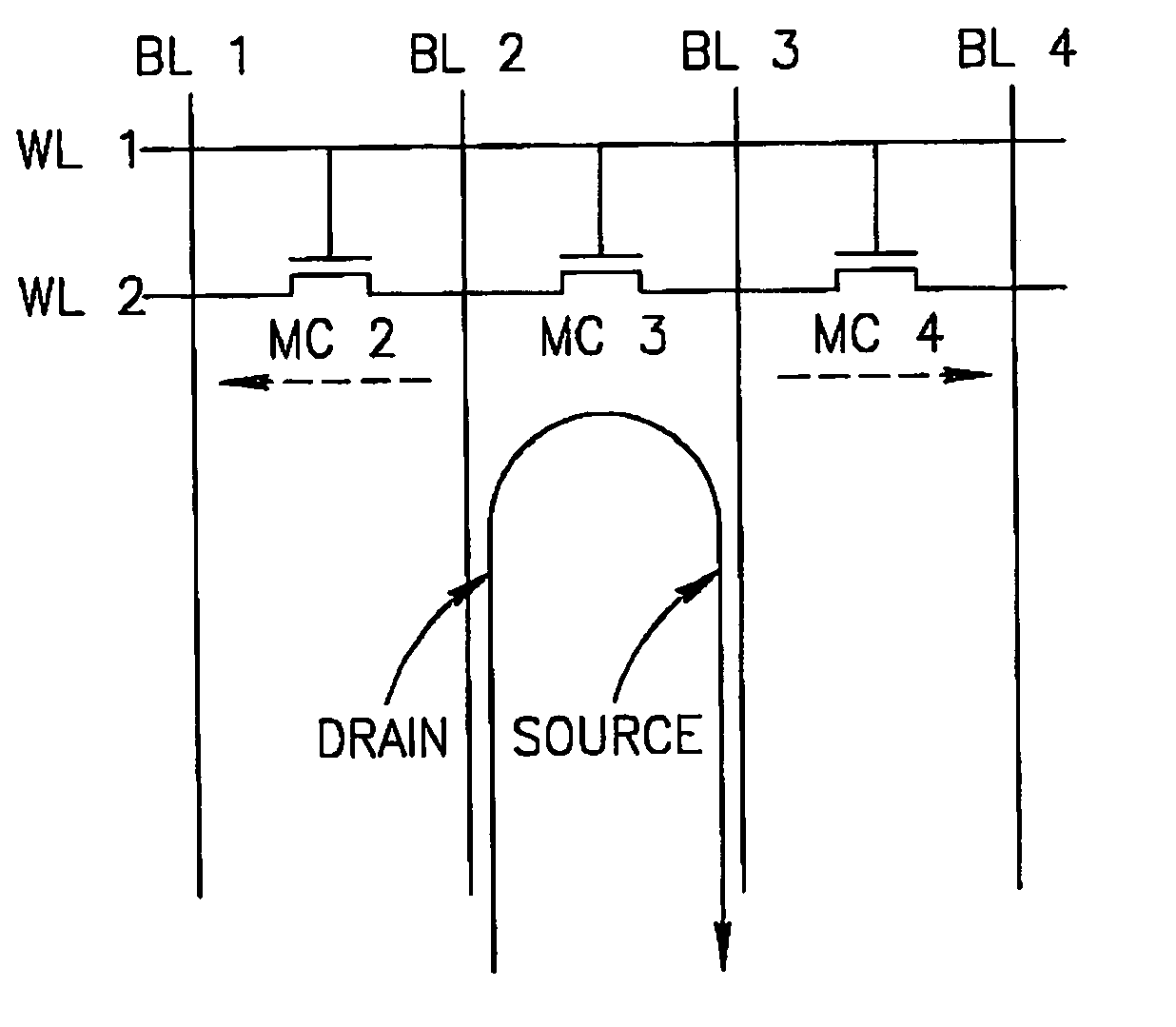

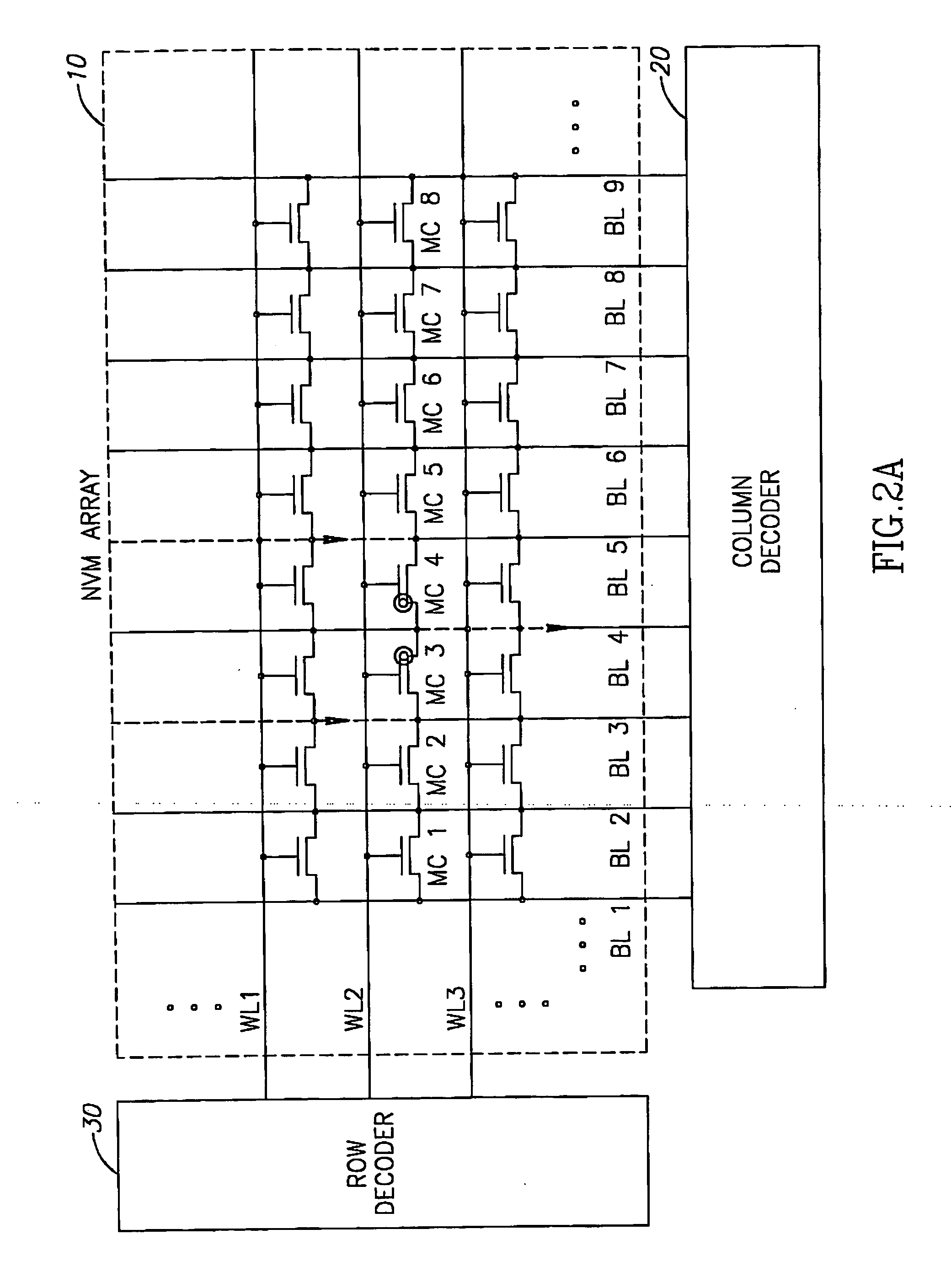

Method for reading a memory array with neighbor effect cancellation

There is provided in accordance with embodiments of the present invention a method of reducing the neighbor effect in reading data in a non-volatile memory array by sensing adjacent memory cells in a virtual ground array of memory cells comprising sensing substantially simultaneously a state of adjacent memory cells, wherein a bit stored in a charge trapping region of each cell of the adjacent memory cells is in an identical state.

Owner:SAIFUN SEMICON

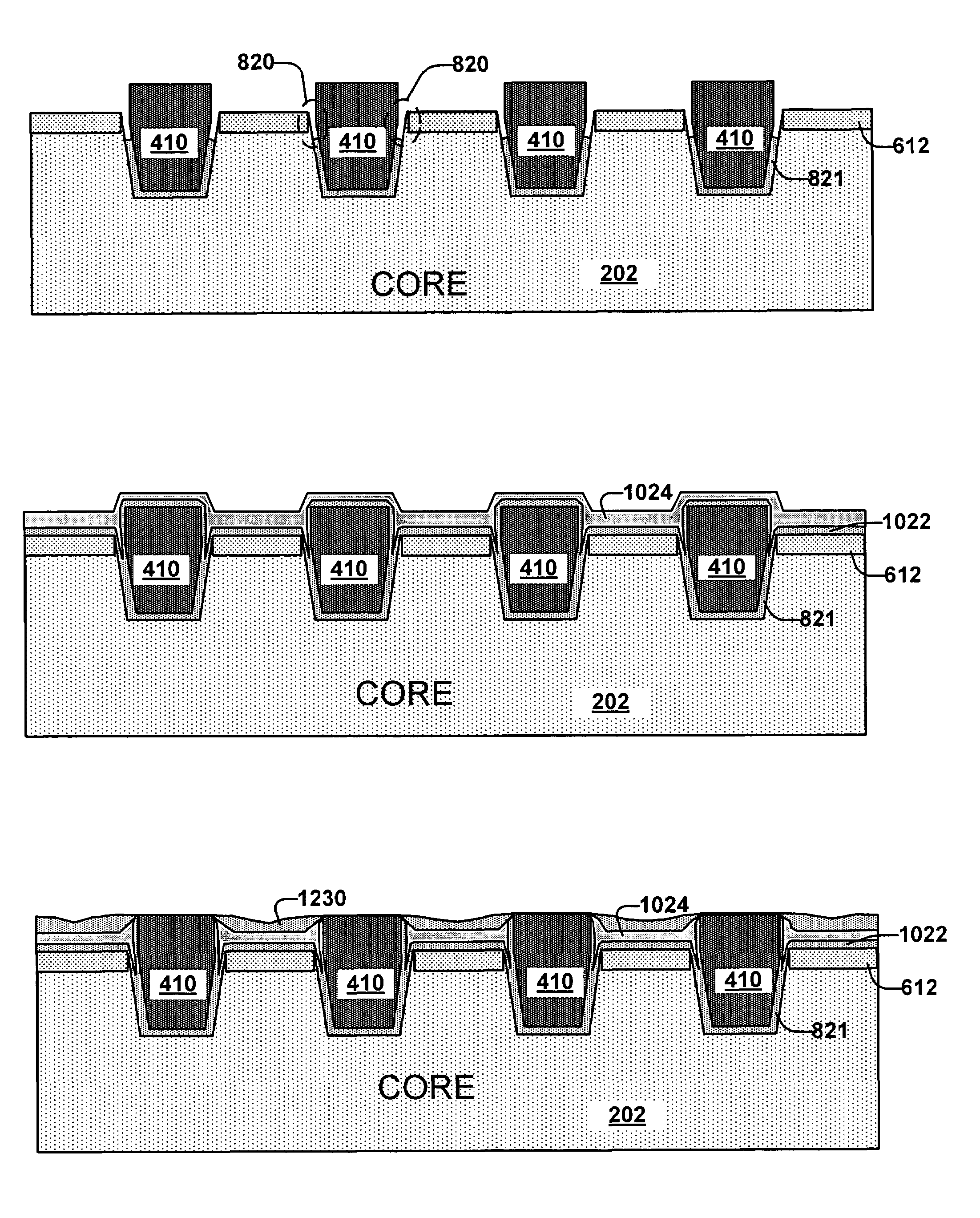

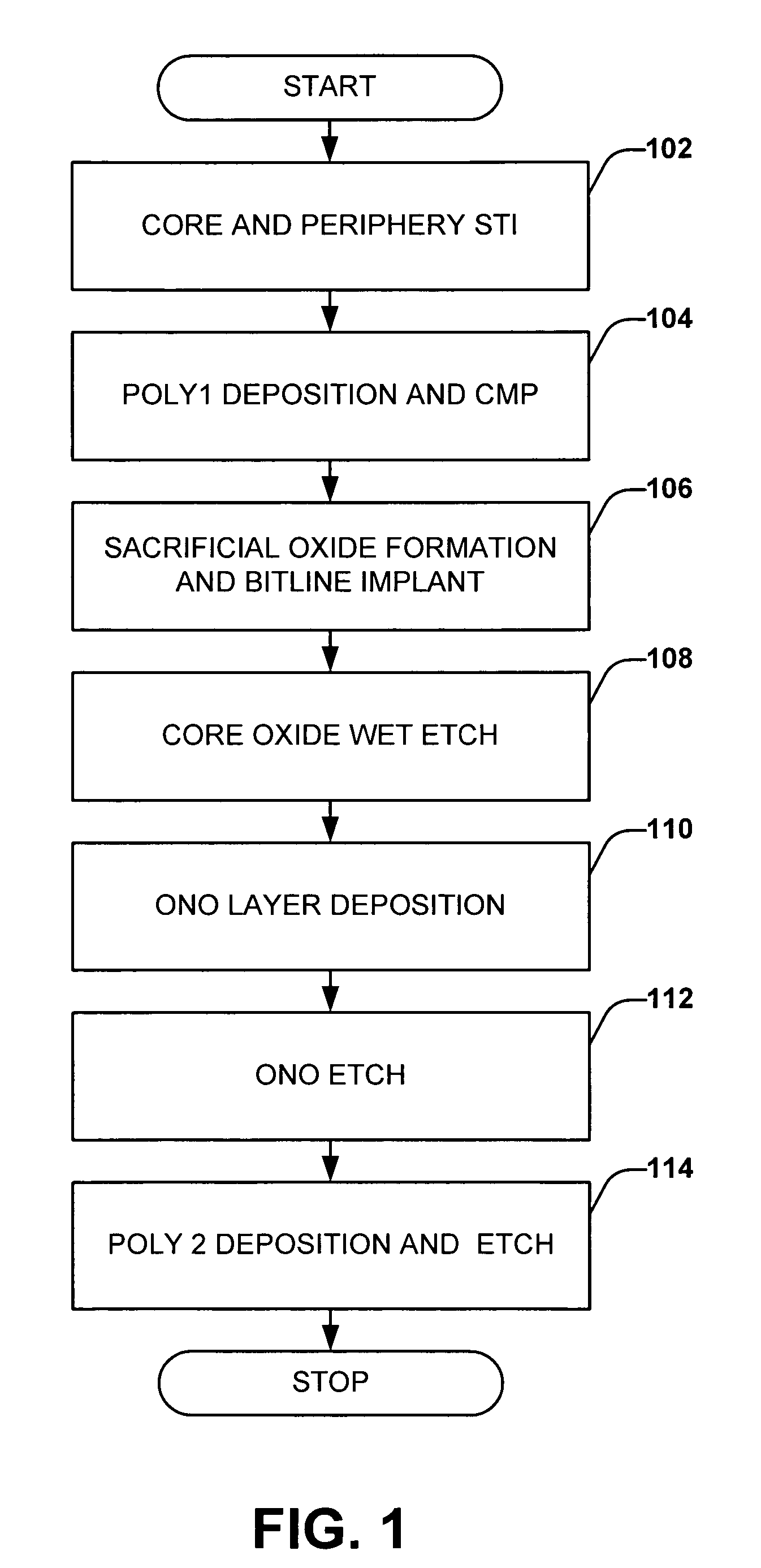

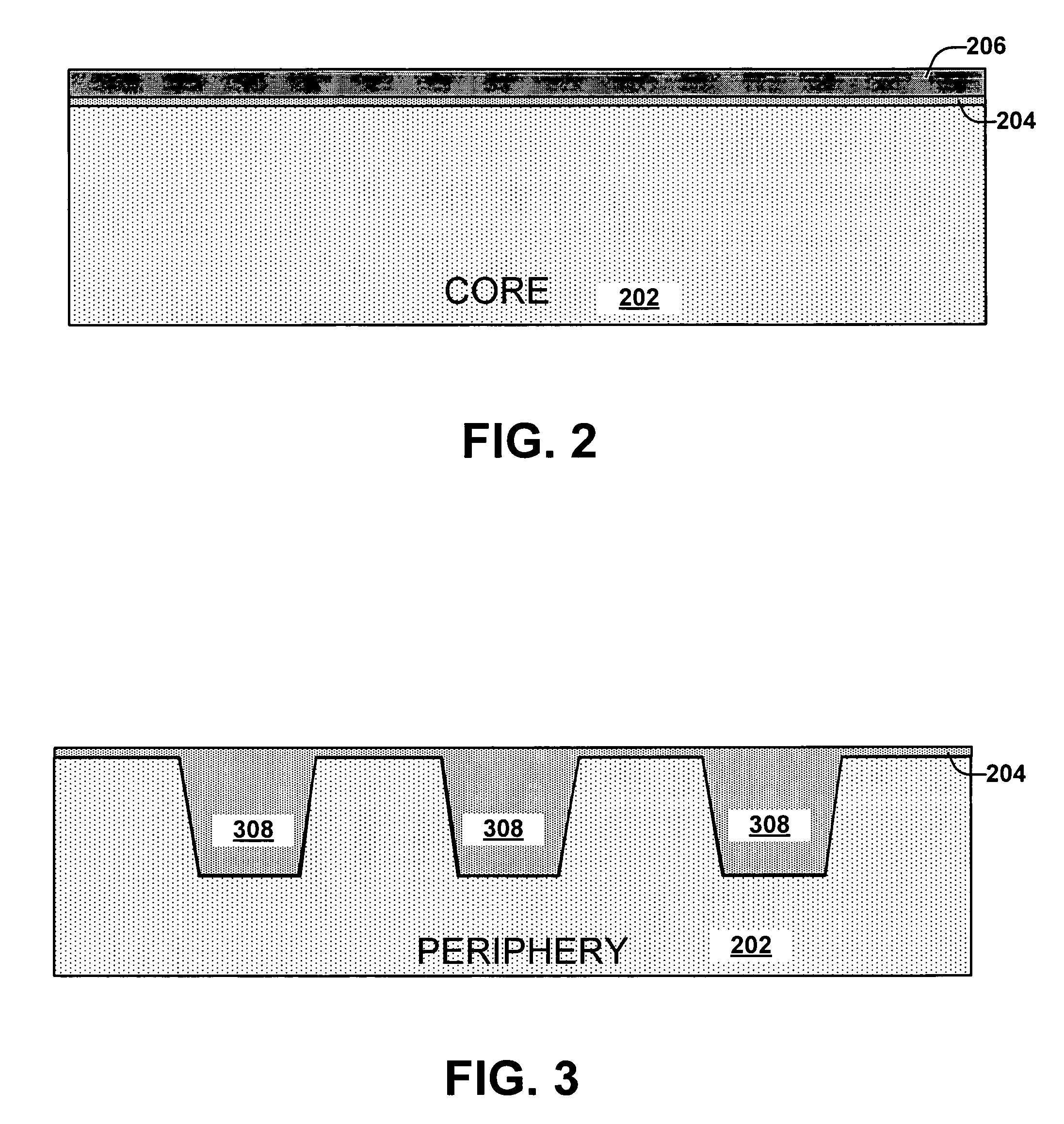

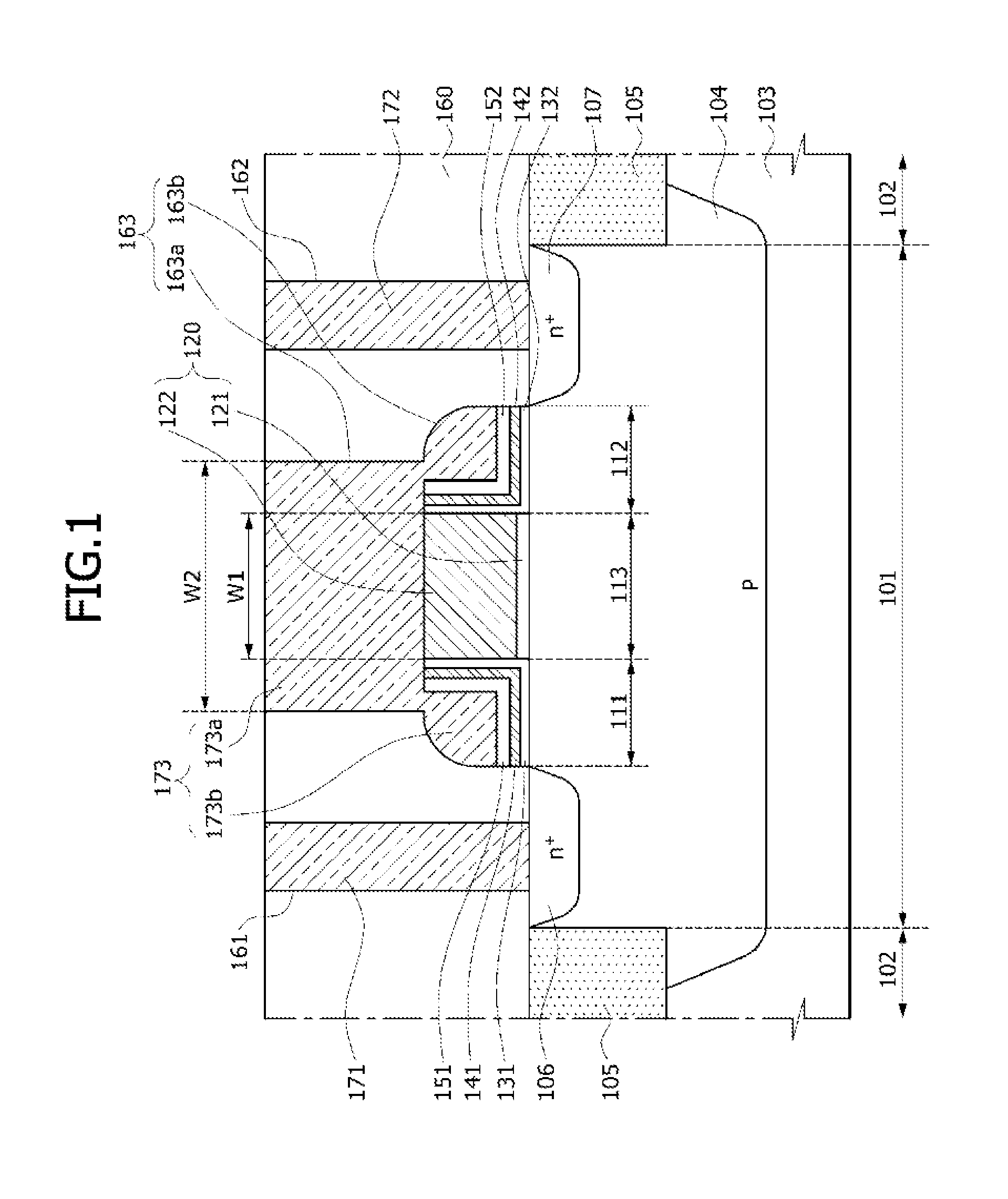

Recessed channel with separated ONO memory device

ActiveUS7067377B1Suppression of short channel effectsSacrificing memory cell packing densitySolid-state devicesSemiconductor/solid-state device manufacturingShortest distanceEngineering

Systems and methods of fabricating a U-shaped memory device with a recessed channel and a segmented / separated ONO layer are provided. Multibit operation is facilitated by a separated ONO layer, which includes a charge trapping region on sidewalls of polysilicon gate structures adjacent to source / drain regions. Programming and erasing of the memory cells is facilitated by the relatively short distance between acting source regions and the gate. Additionally, short channel effects are mitigated by a relatively long U-shaped channel region that travels around the recessed polysilicon gate thereby adding a depth dimension to the channel length.

Owner:MONTEREY RES LLC

Two bit non-volatile electrically erasable and programmable semiconductor memory cell utilizing asymmetrical charge trapping

InactiveUS20050111257A1Little effectShorten speedTransistorSolid-state devicesProgrammable read-only memoryNon symmetric

A non-volatile electrically erasable programmable read only memory (EEPROM) capable of storing two bit of information having a nonconducting charge trapping dielectric, such as silicon nitride, sandwiched between two silicon dioxide layers acting as electrical insulators is disclosed. The invention includes a method of programming, reading and erasing the two bit EEPROM device. The nonconducting dielectric layer functions as an electrical charge trapping medium. A conducting gate layer is placed over the upper silicon dioxide layer. A left and a right bit are stored in physically different areas of the charge trapping layer, near left and right regions of the memory cell, respectively. Each bit of the memory device is programmed in the conventional manner, using hot electron programming, by applying programming voltages to the gate and to either the left or the right region while the other region is grounded. Hot electrons are accelerated sufficiently to be injected into the region of the trapping dielectric layer near where the programming voltages were applied to. The device, however, is read in the opposite direction from which it was written, meaning voltages are applied to the gate and to either the right or the left region while the other region is grounded. Two bits are able to be programmed and read due to a combination of relatively low gate voltages with reading in the reverse direction. This greatly reduces the potential across the trapped charge region. This permits much shorter programming times by amplifying the effect of the charge trapped in the localized trapping region associated with each of the bits. In addition, both bits of the memory cell can be individually erased by applying suitable erase voltages to the gate and either left or right regions so as to cause electrons to be removed from the corresponding charge trapping region of the nitride layer.

Owner:SAIFUN SEMICON

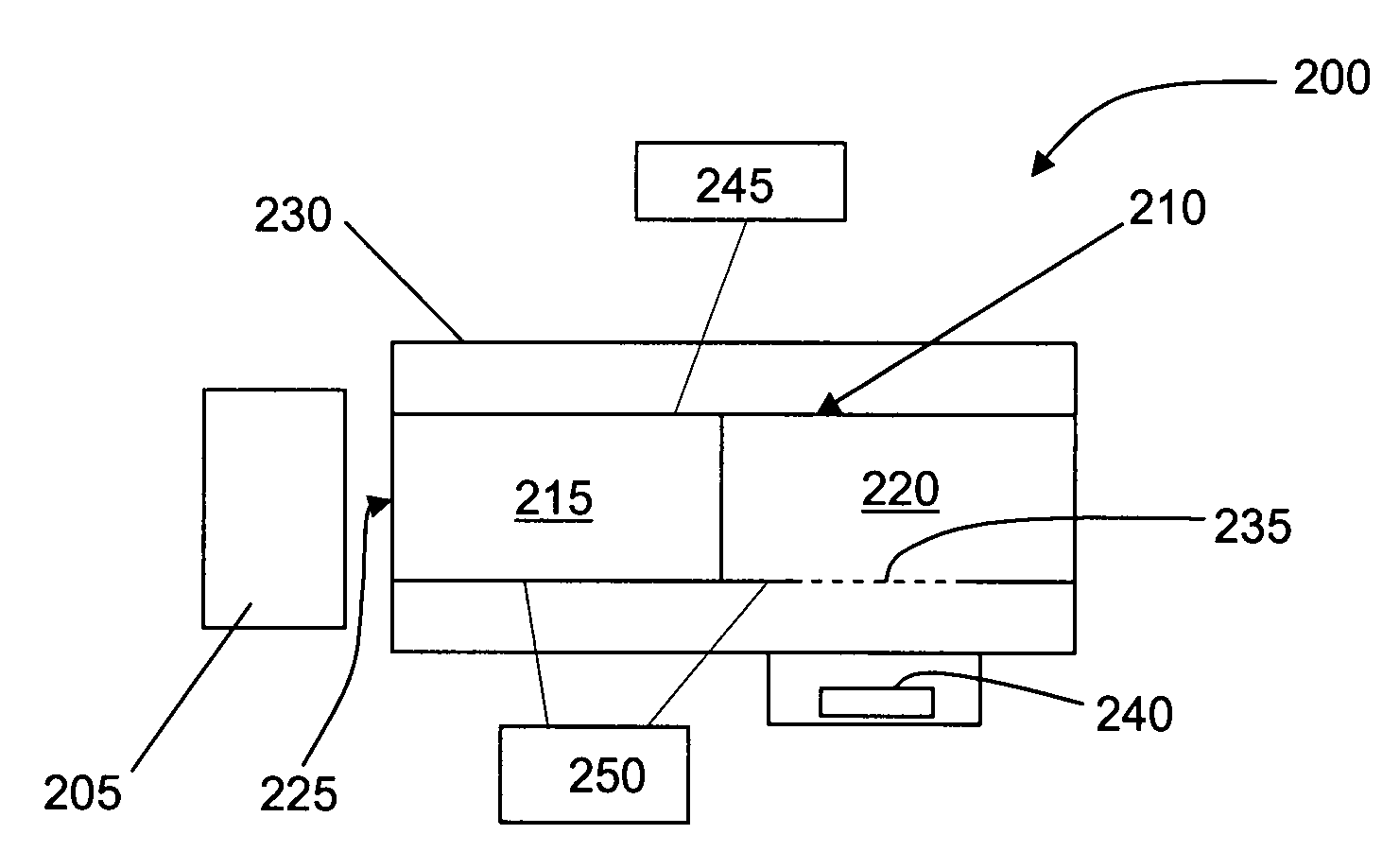

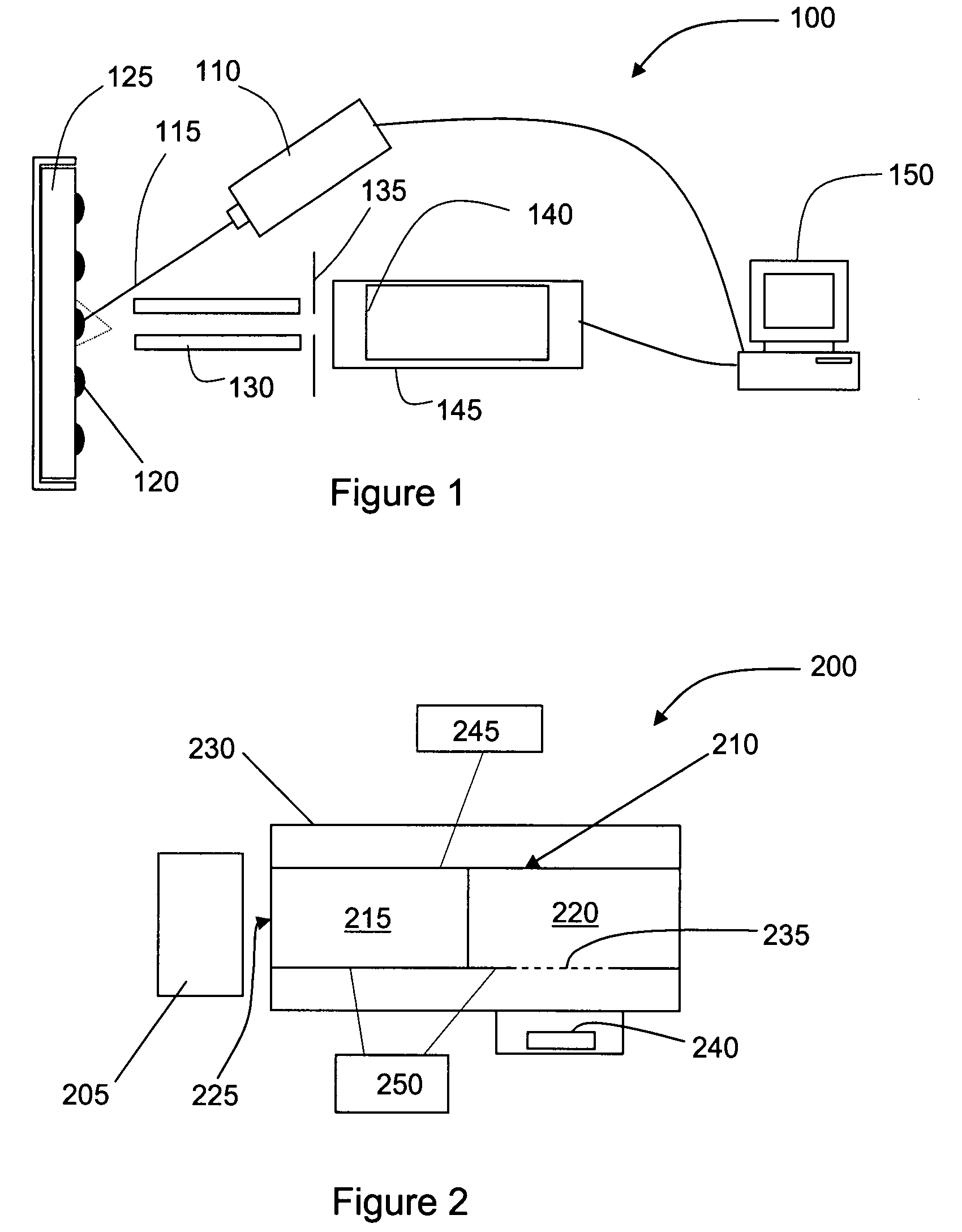

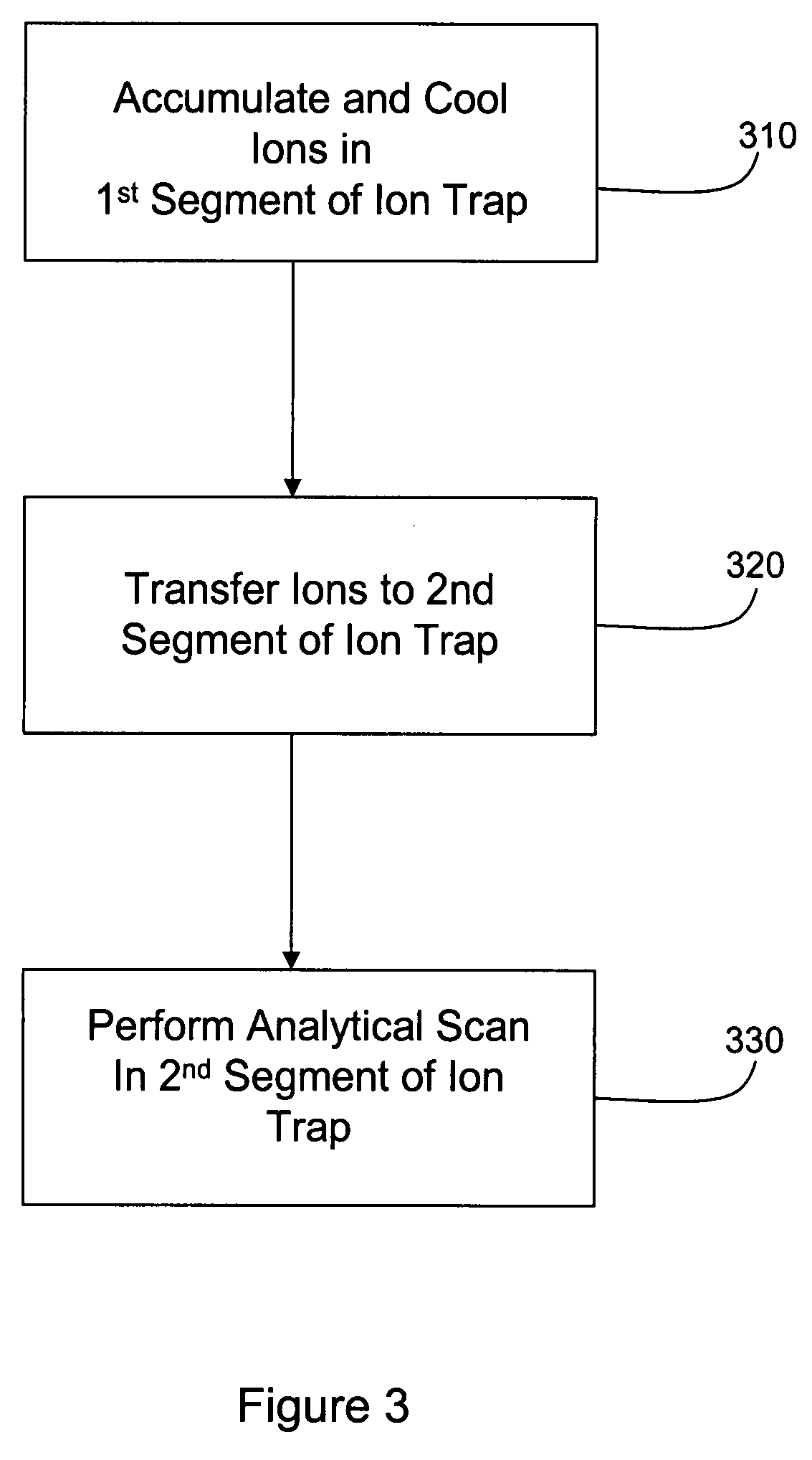

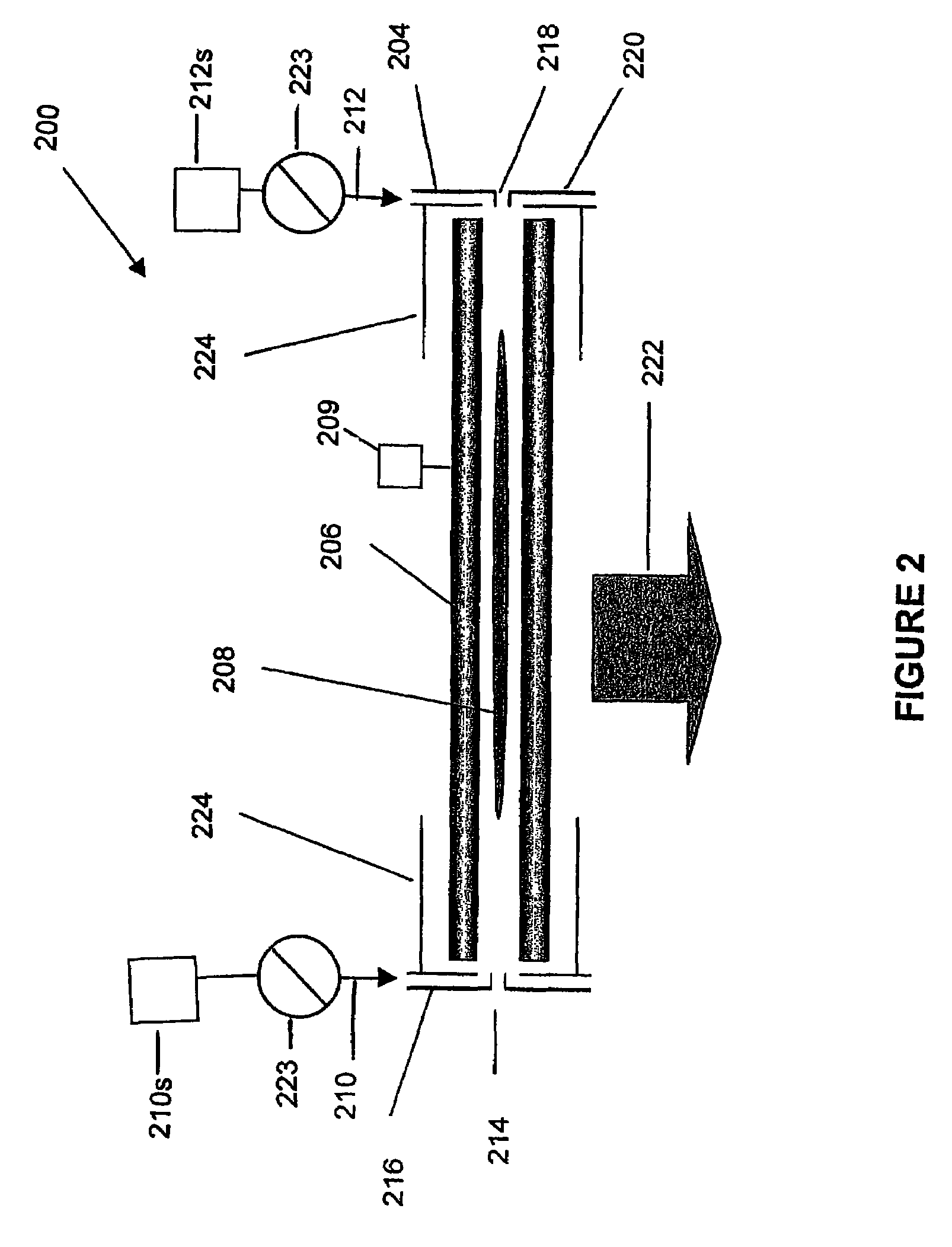

Segmented ion trap mass spectrometry

InactiveUS20080210860A1Remove foulingPoor resolutionStability-of-path spectrometersIsotope separationIon trap mass spectrometrySufficient time

An ion trap is provided with at least two discrete trapping regions or segments. Both segments are located in a vacuum chamber of a mass spectrometer system. An entrance of the ion trap is disposed downstream to a laser based ionization source to receive the ions with a wide range of kinetic energies that have been generated by the laser-based ionization source. Once sufficient ions have been accumulated in the first segment and sufficient time has passed to cool the ions, they are transferred to the second segment and ultimately ejected through an aperture or slot to a detector arrangement to produce a mass spectrum.

Owner:THERMO FINNIGAN

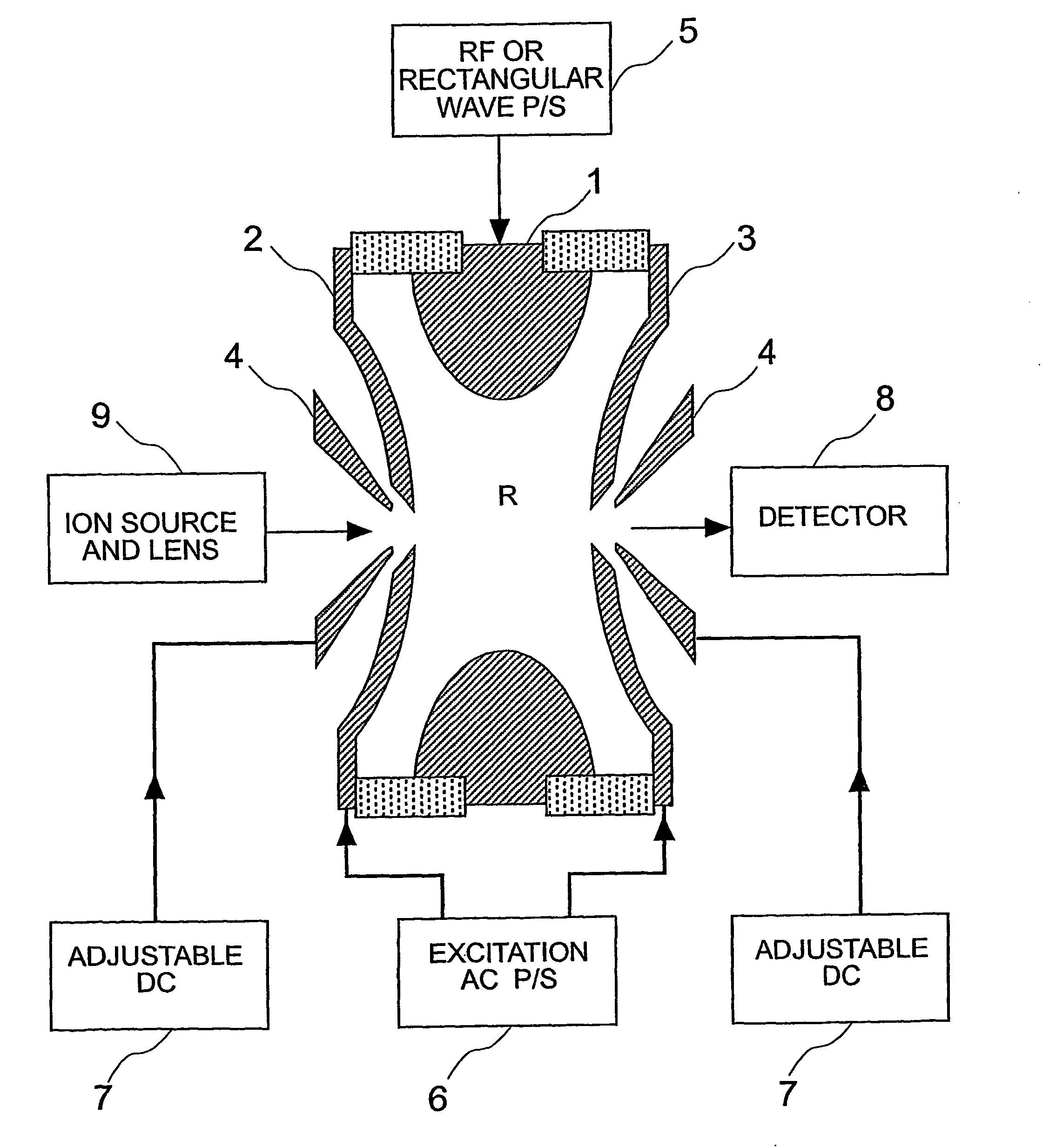

Quadrupole ion trap device and methods of operating a quadrupole ion trap device

ActiveUS7285773B2Improve efficiencyHigh resolutionStability-of-path spectrometersElectron/ion optical arrangementsImage resolutionTrapping region

A quadrupole ion trap device has a field adjusting electrode located outside the trapping region adjacent the aperture in the entrance end cap electrode, and optionally adjacent the aperture in the exit end cap electrode. The field adjusting electrode(s) controls field distortion in the vicinity of the apertures. By appropriately setting the voltages on the field adjusting electrodes the efficiency and resolution of operational processes such as ion introduction, precursor ion isolation and mass scanning can be improved.

Owner:SHIMADZU RES LAB EURO

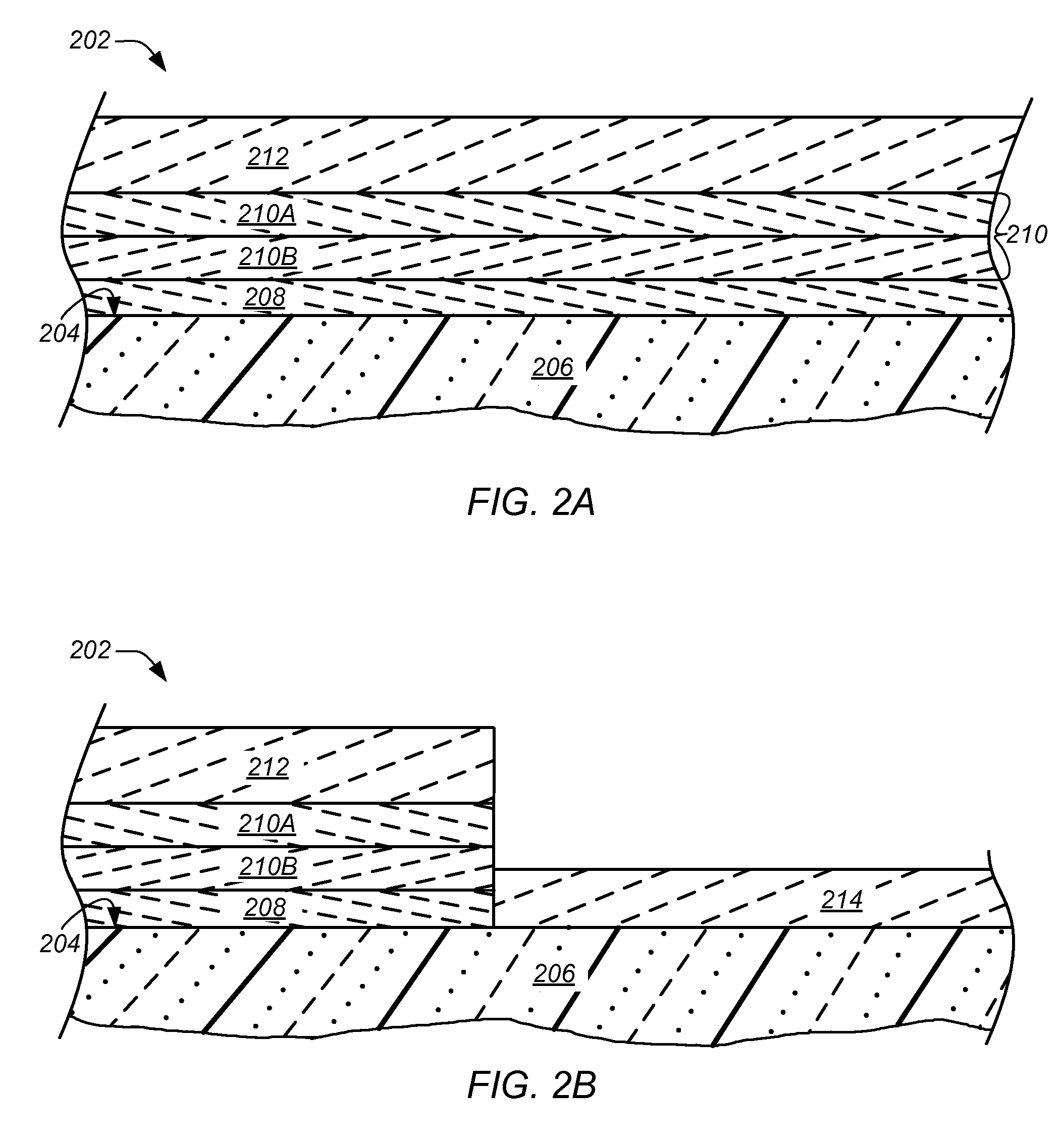

Memory transistor with multiple charge storing layers and a high work function gate electrode

A semiconductor devices including non-volatile memories and methods of fabricating the same to improve performance thereof are provided. Generally, the device includes a memory transistor comprising a polysilicon channel region electrically connecting a source region and a drain region formed in a substrate, an oxide-nitride-nitride-oxide (ONNO) stack disposed above the channel region, and a high work function gate electrode formed over a surface of the ONNO stack. In one embodiment the ONNO stack includes a multi-layer charge-trapping region including an oxygen-rich first nitride layer and an oxygen-lean second nitride layer disposed above the first nitride layer. Other embodiments are also disclosed.

Owner:LONGITUDE FLASH MEMORY SOLUTIONS LTD

Ion trap for cooling ions

ActiveUS8642948B2Degree of flexibilityReduce divergenceMaterial analysis by electric/magnetic meansIsotope separationIon trap mass spectrometryGas passing

A method of changing the kinetic energy of ions is provided, comprising: trapping ions in a trapping region of an ion trap; and directing a beam of gas through the trapping region, so as to change the kinetic energy of the trapped ions thereby. Also provided is a method of separating ions, the method comprising: causing ions to enter a trapping region of an ion trap along a first axis of the trapping region; directing a beam of gas along the first axis and applying an electric potential in the direction of the first axis so as to cause separation of the ions based on their ion mobility. An ion trap and a mass spectrometer for performing the methods are also provided.

Owner:THERMO FISHER SCI BREMEN

Segmented linear ion trap for enhanced ion activation and storage

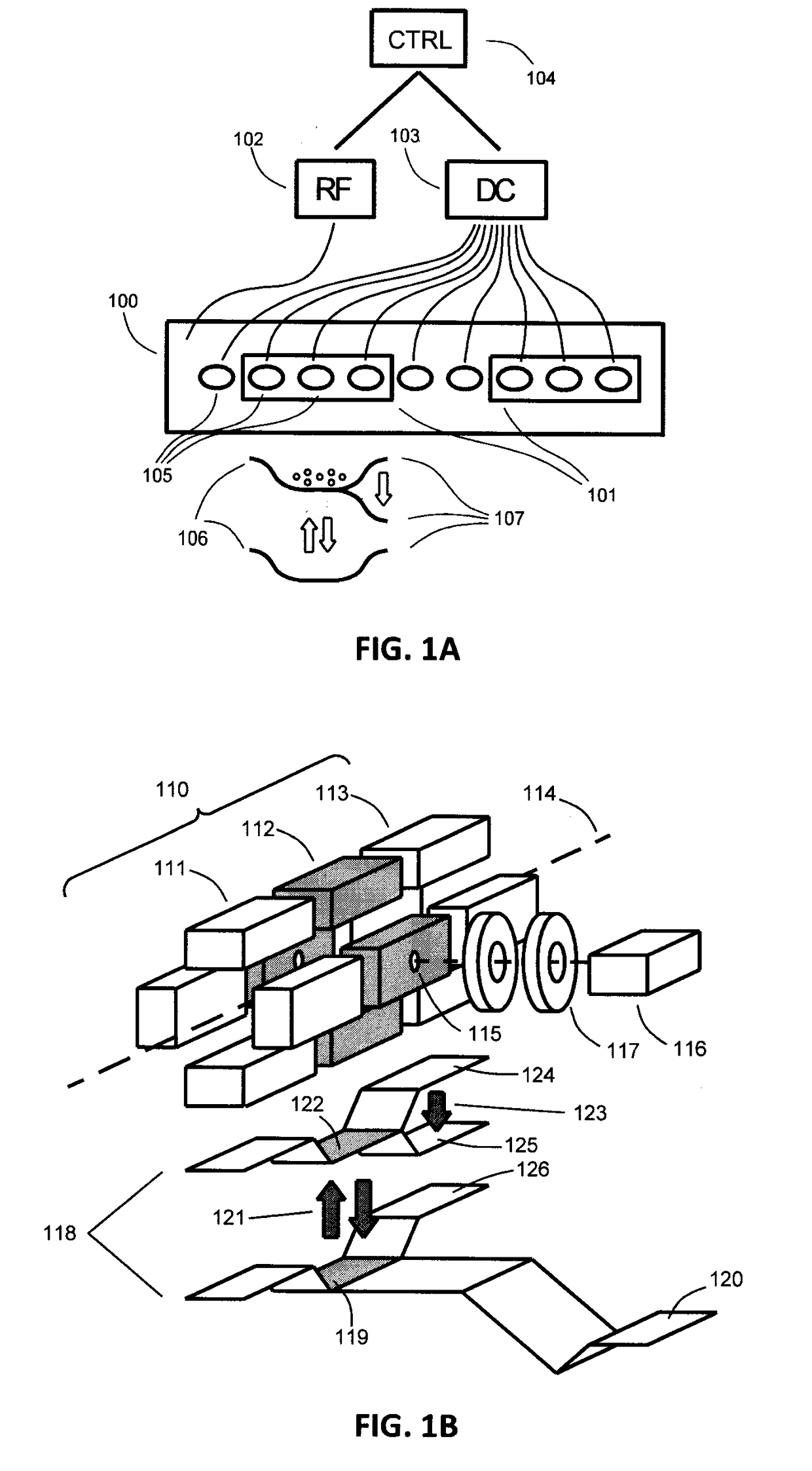

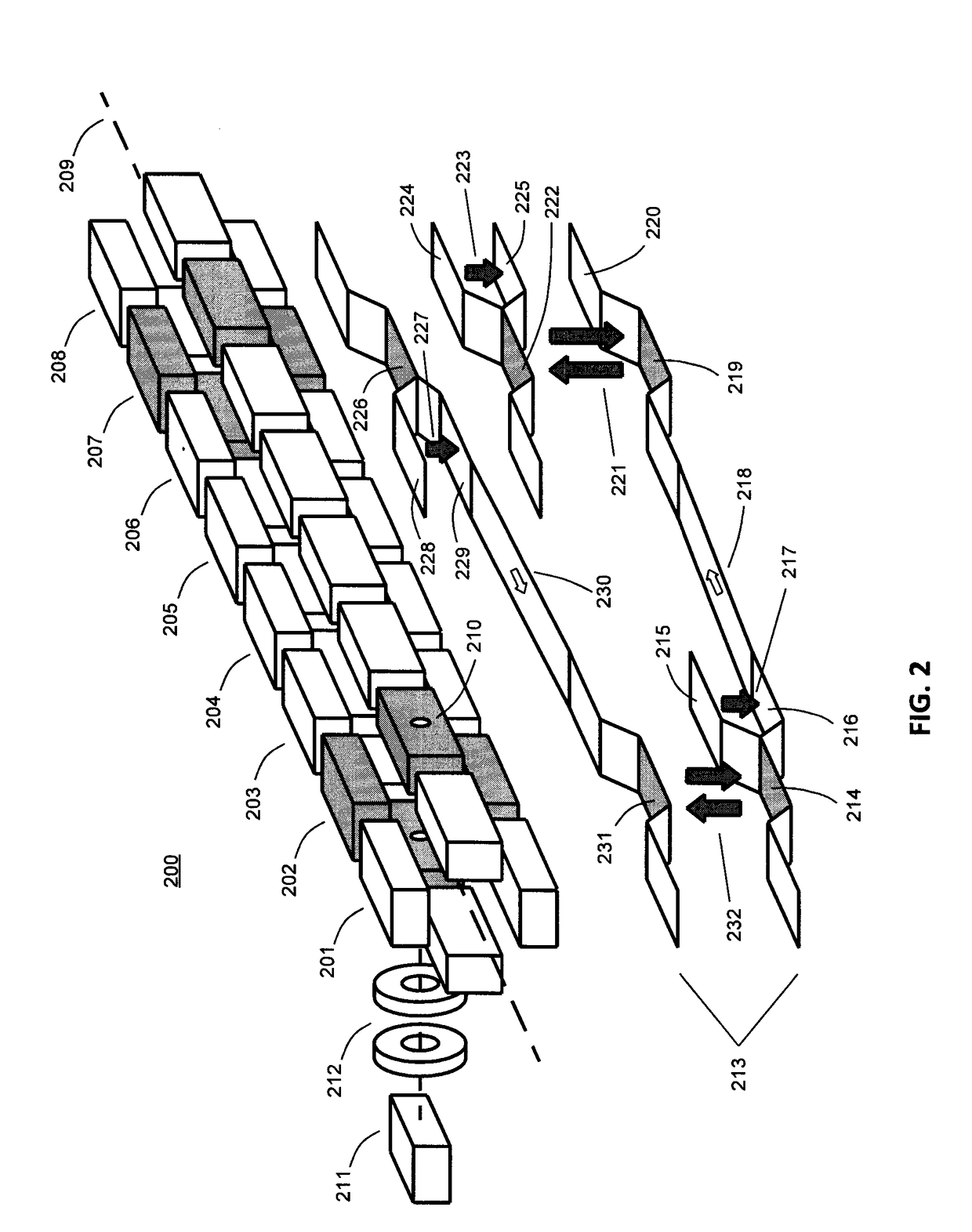

ActiveUS20170221694A1Enhance collision induced dissociationExtended durationStability-of-path spectrometersMaterial analysis by electric/magnetic meansRf fieldIon trap mass spectrometry

A linear ion trap includes at least two discrete trapping regions for processing ions, a RF electrical potential generator, a multi-output DC electrical potential generator, and a control unit. The RF electrical potential generator produces two RF waveforms each applied to a pair of pole electrodes of the linear ion trap forming a RF trapping field component to trap ions radially. The multi-output DC electrical potential generator produces multiple DC field components superimposed to the RF field component and distributed across the length of the linear ion trap to control ions axially. The control unit switches the DC electrical potentials and corresponding DC field components collectively forming a first trapping region populated with ions to alter ion potential energy from a first level to a second level, and enables a first ion processing step in at least one of the first and second levels.

Owner:FASMATECH SCI & TECH

An ion trap and a method for dissociating ions in an ion trap

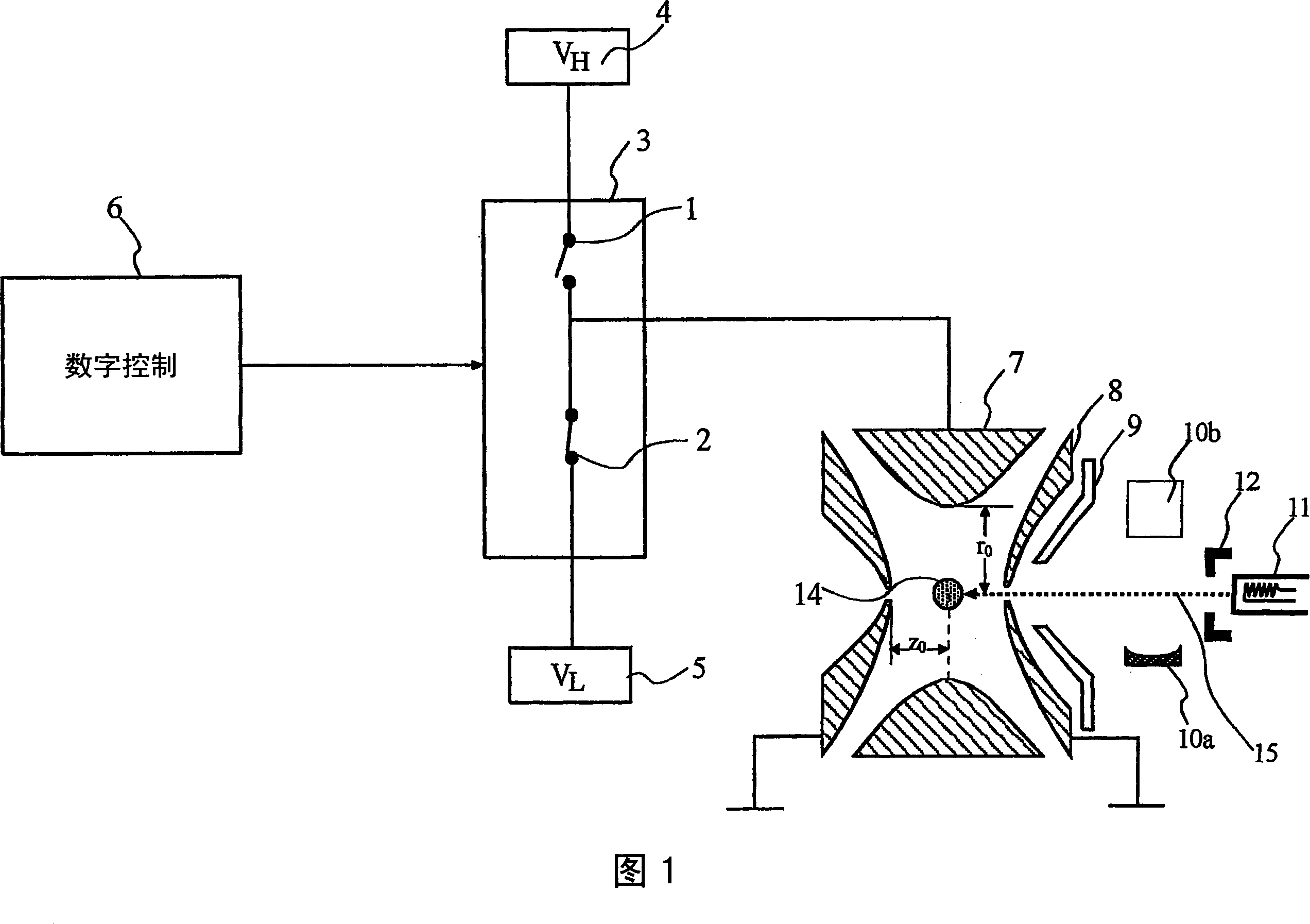

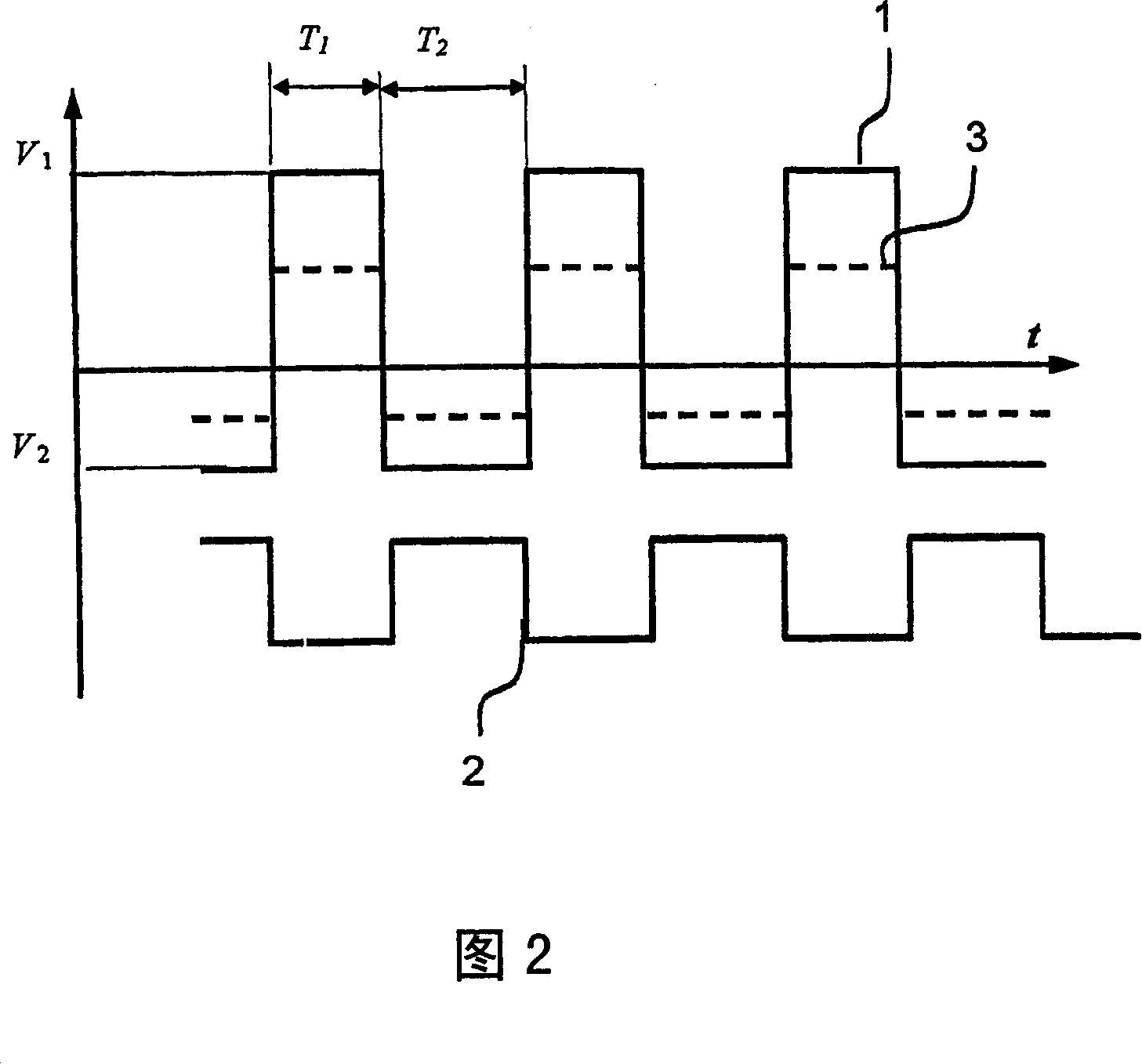

ActiveCN1922711AReduce electric field strengthRelieve pressureStability-of-path spectrometersTime-of-flight spectrometersIon trap mass spectrometryElectron injection

A quadrupole ion trap includes a switch (3) for switching a trapping voltage between discrete voltage levels VH, VL. This creates a digital trapping field for trapping precursor ions and product ions in a trapping region of the ion trap. A gating voltage is applied to a gate electrode (12) to control injection of source electrons into the ion trap. Application of the gating voltage is synchronised with the switching so that electrons are injected into the trapping region while the trapping voltage is at a selected one of the voltage levels and can reach the trapping region with a kinetic energy suitable for electron capture dissociation to take place.

Owner:岛津欧州研究所

Micro-channel device

A micro-channel device has a micro-channel for flowing liquid therethrough and includes a first aperture held in communication with the micro-channel for the purpose of injecting liquid, a second aperture held in communication with the micro-channel for the purpose of discharging liquid and a bubble trapping region constituting a part of the micro-channel. The height of the bubble trapping region is greater than the height of the micro-channel at the position of liquid inflow into the micro-channel located downstream relative to the bubble trapping region.

Owner:CANON KK

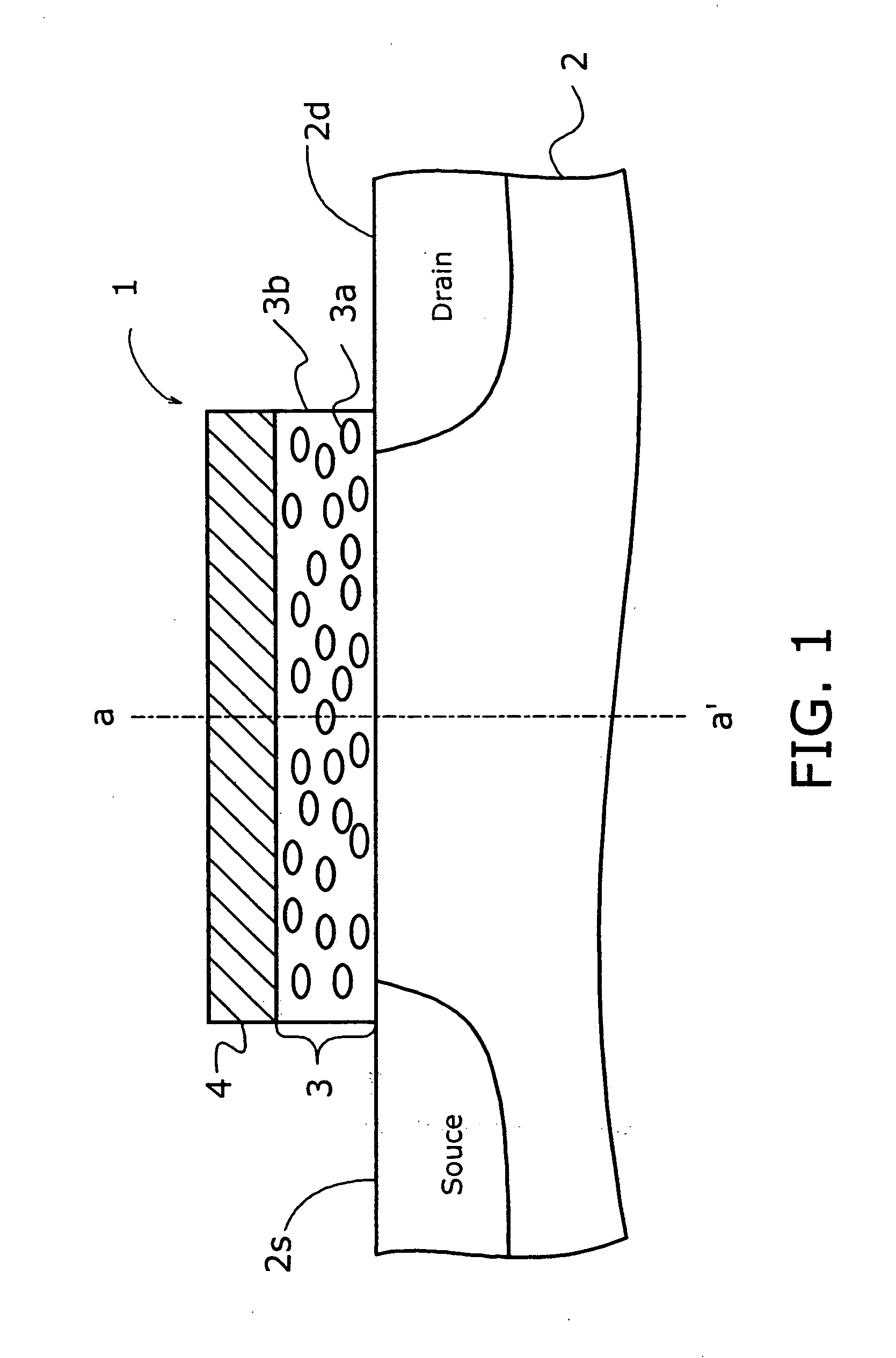

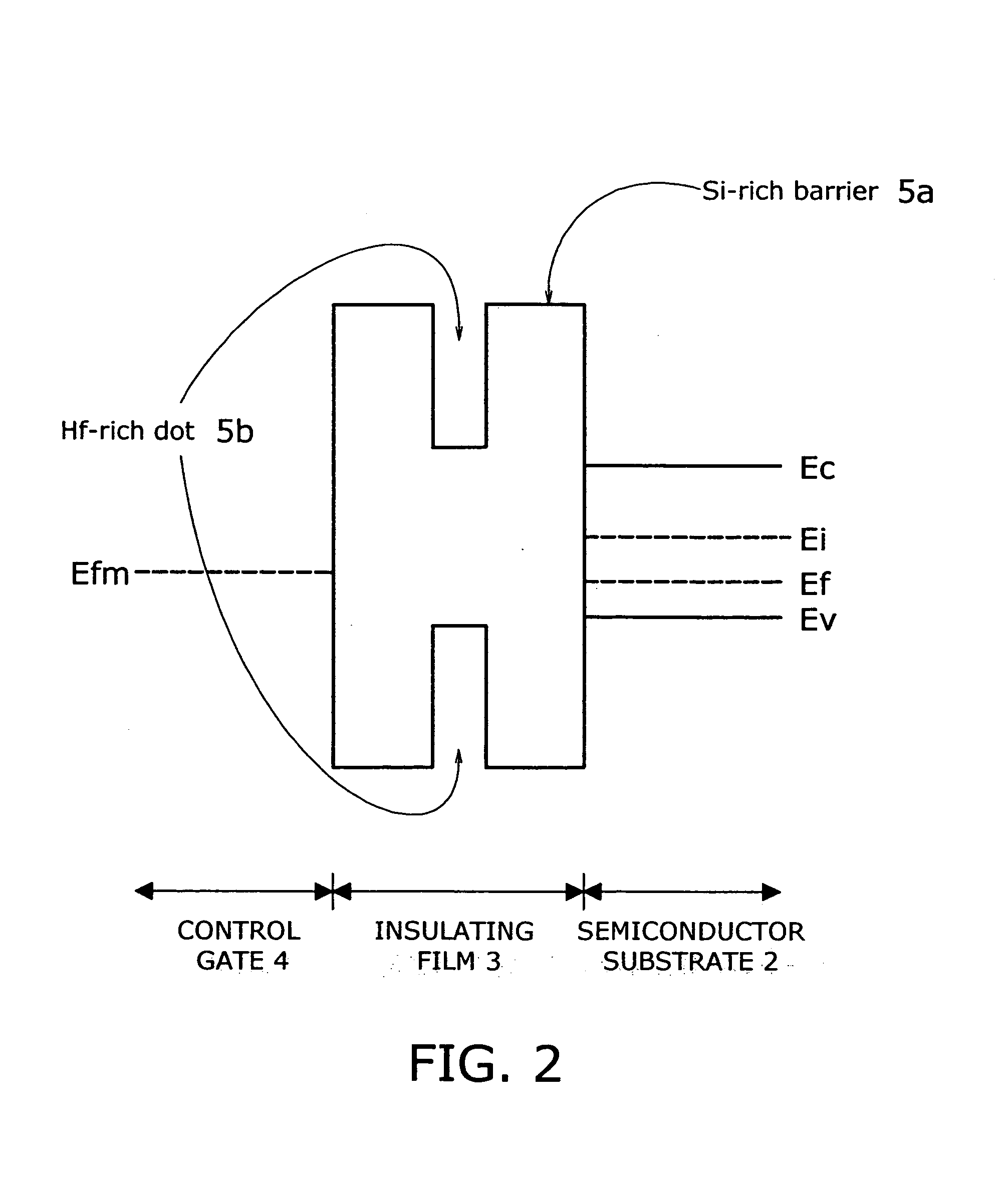

Semiconductor memory device and manufacturing method thereof

ActiveUS20050037574A1Reliable retentionReliably retains electrons trapped in its charge-trapping regionsTransistorSolid-state devicesDielectricTrapping region

A semiconductor memory device which more reliably retains electrons trapped in its charge-trapping regions. A high-dielectric gate insulating film is grown on a semiconductor substrate. This gate insulating film is composed of first and second oxides, where the second oxide has a smaller bandgap than that of the first oxide and is scattered in dot-like form, surrounded by the first oxide. The memory cell is programmed by injecting electrons into a local potential minimum that is produced due to the bandgap difference between the phase-separated first and second oxides.

Owner:FUJITSU LTD

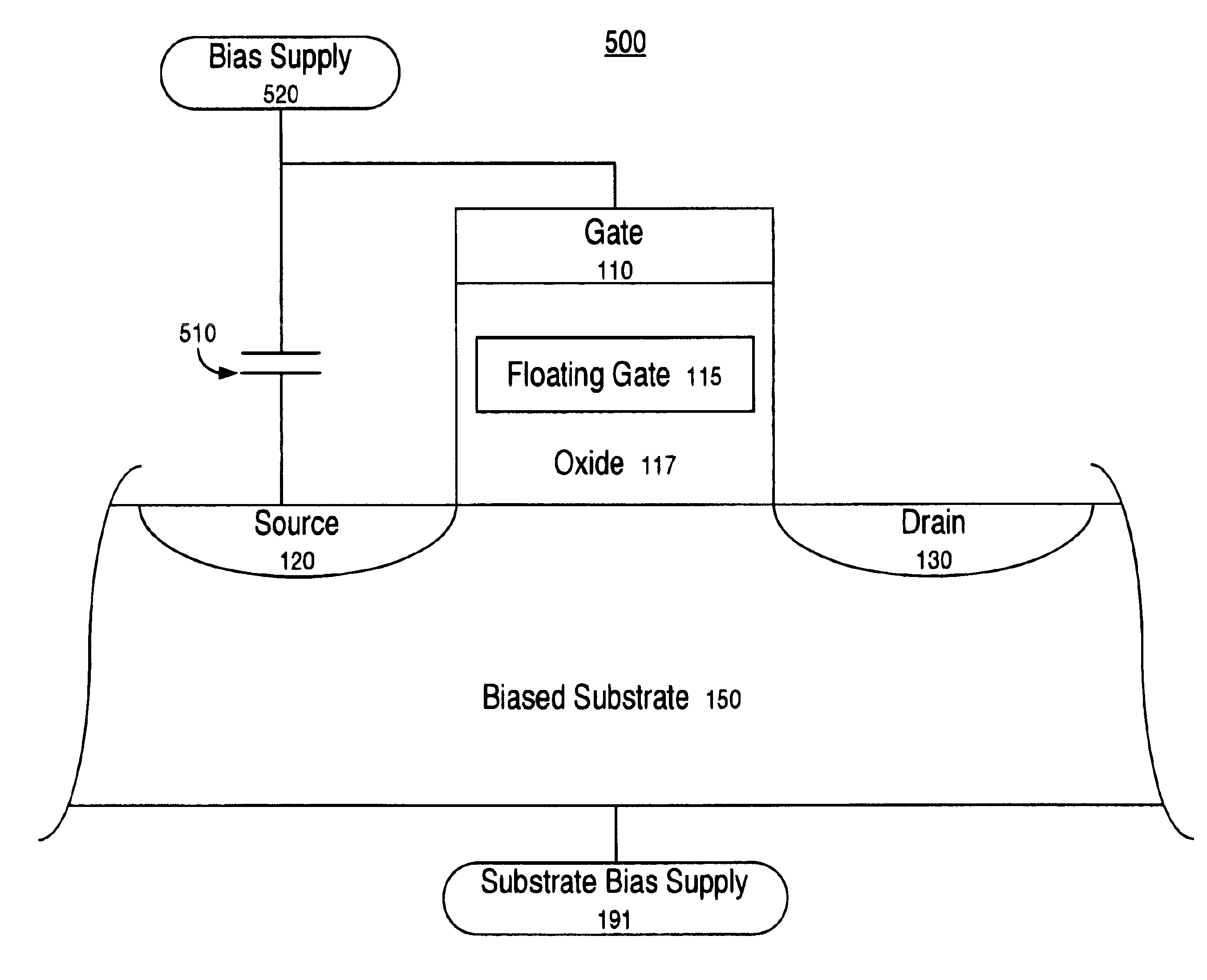

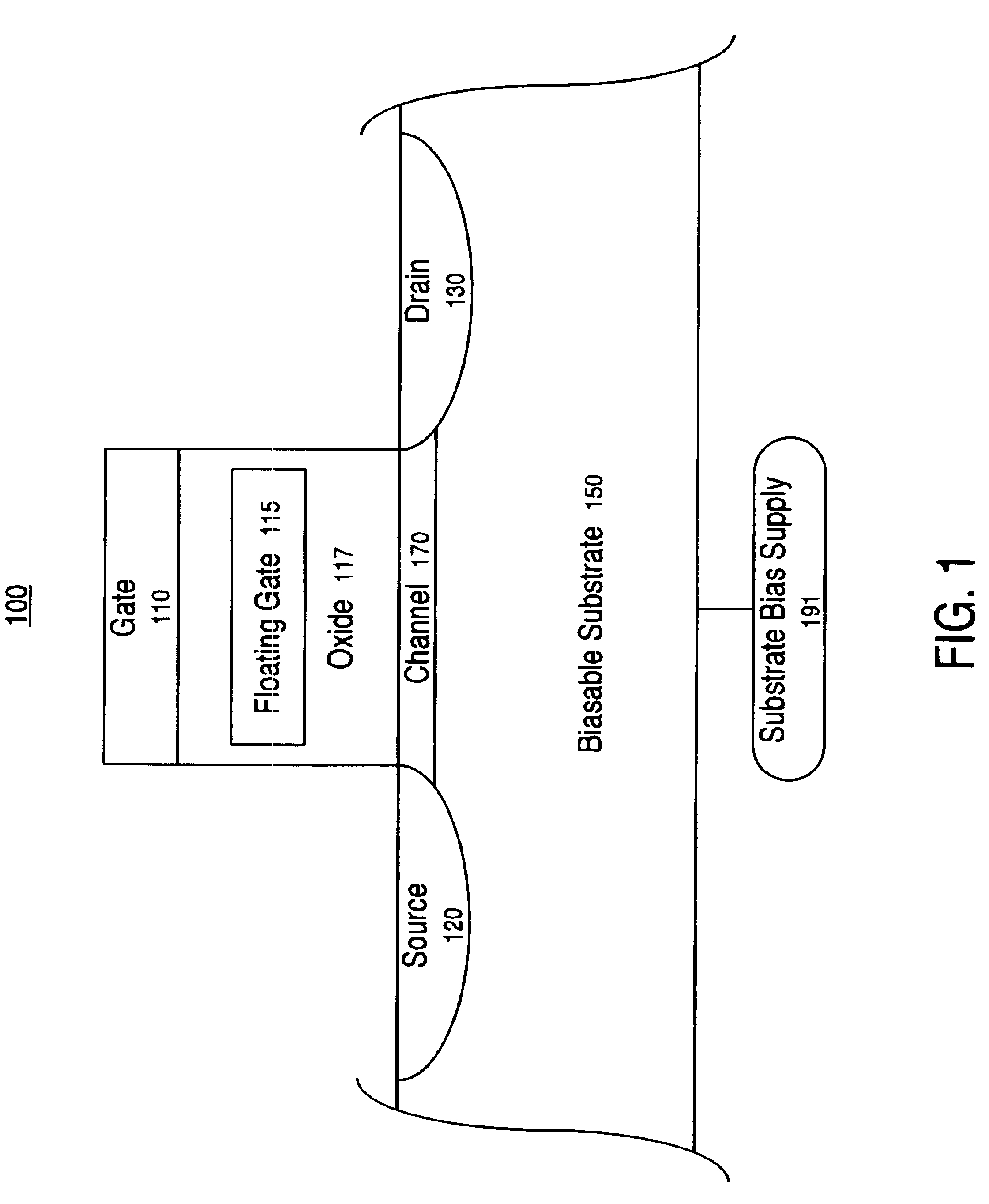

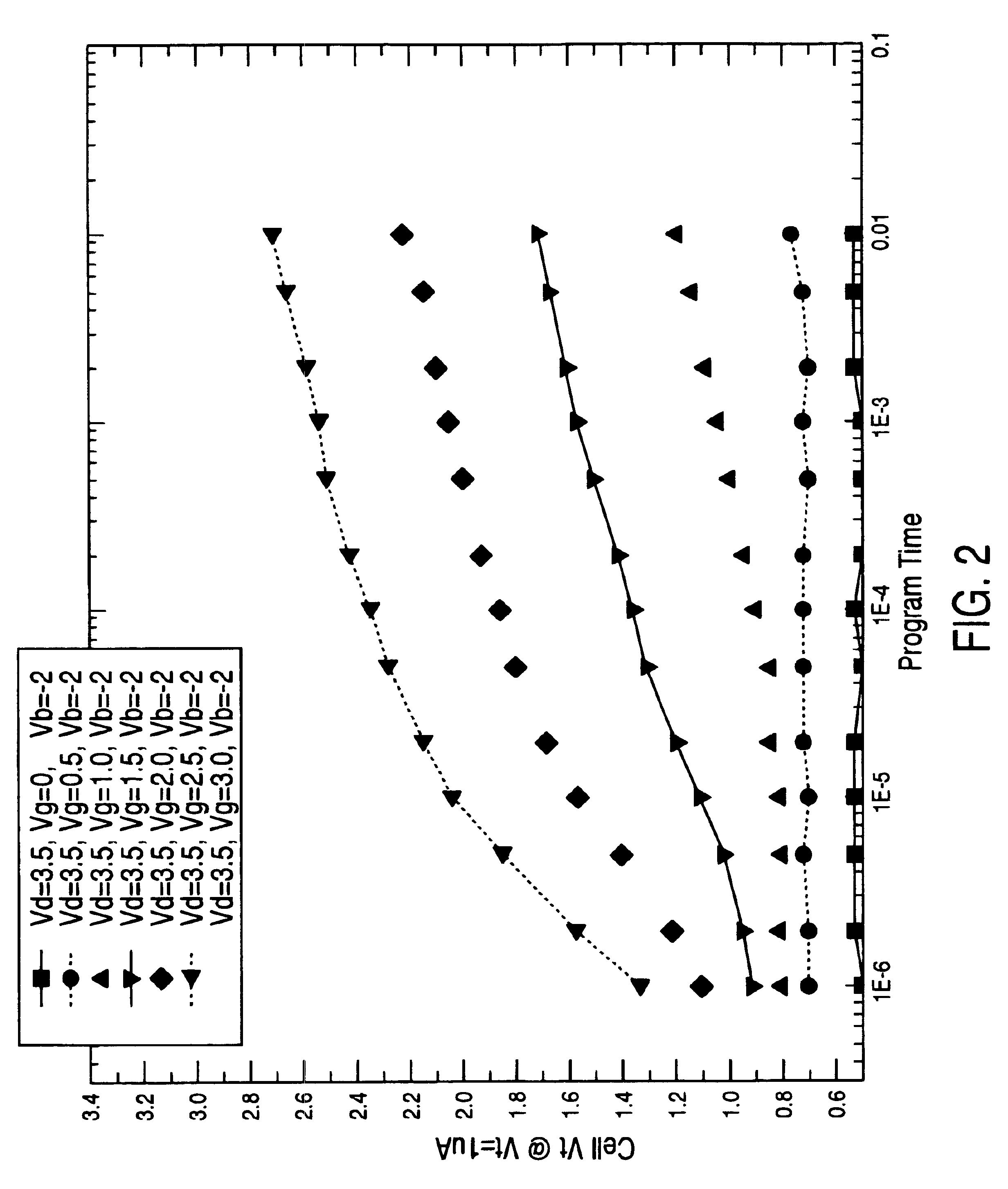

Flash memory cell programming method and system

InactiveUS6894925B1Quickly and efficiently operateIncrease the electric field strengthTransistorRead-only memoriesElectricityElectrical field strength

A flash memory cell programming system and method that facilitate efficient and quick operation of a flash memory cell by providing a biasable well (e.g., substrate) is presented. The biasable well flash memory cell enables increases in electrical field strengths in a manner that eases resistance to charge penetration of a dielectric barrier (e.g., oxide) around a charge trapping region (e.g., a floating gate). The present biasable well system and method also create a self convergence point that increase control during programming operations and reduces the chances of excessive correction for over erased memory cells. The biasing can assist hard programming to store information and / or soft programming to correct the effects of over-erasing. The biasing can also reduce stress on a drain voltage pump, reduce leakage current and reduce programming durations. Some implementations also include a biasable control gate component, biasable source component and biasable drain component.

Owner:INFINEON TECH LLC

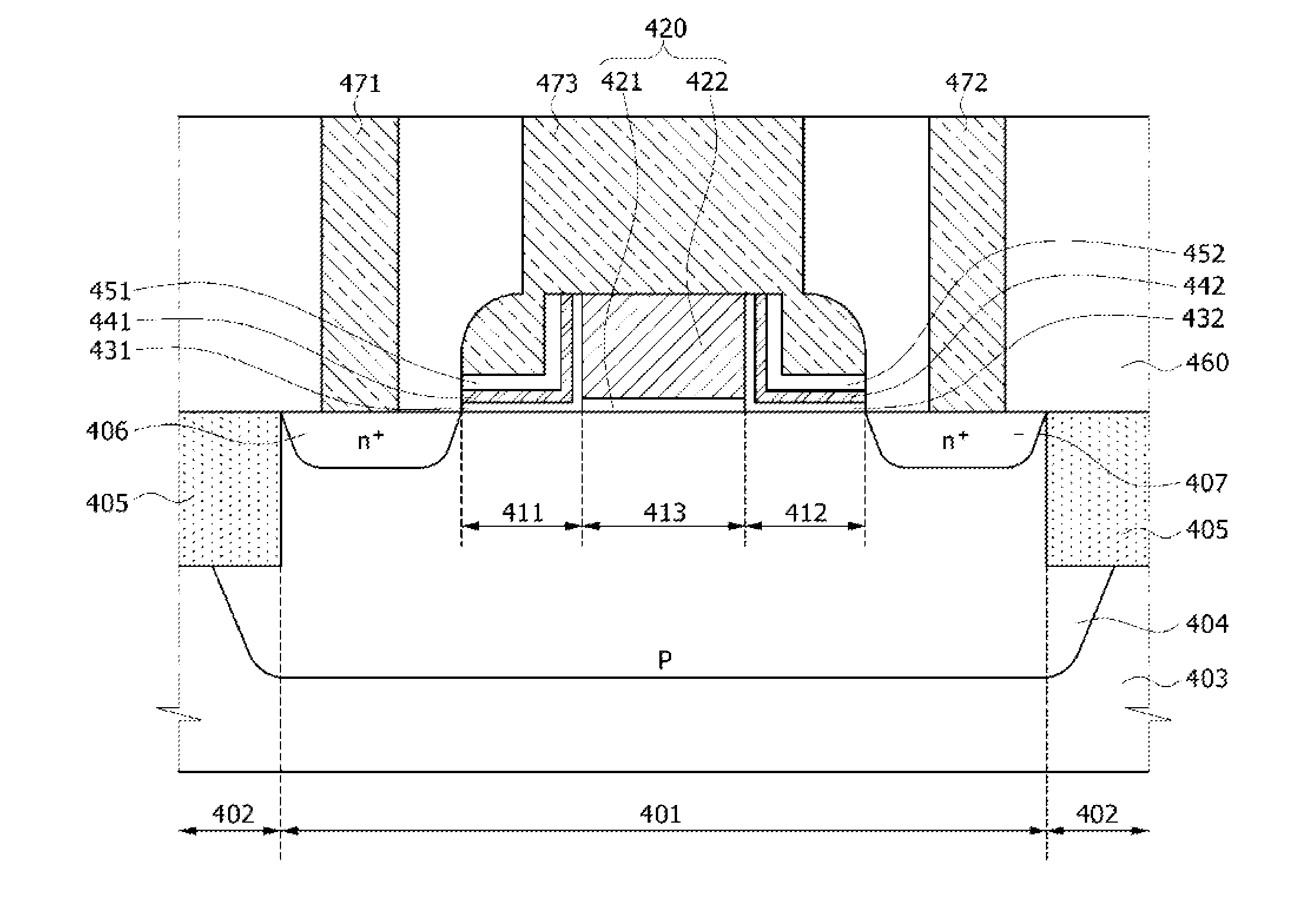

Charge trapping nonvolatile memory devices, methods of fabricating the same, and methods of operating the same

A charge trapping nonvolatile memory device includes a source region and a drain region disposed in an upper portion of a substrate and spaced apart from each other by a first trapping region, a channel region, and a second trapping region. A gate stack structure is disposed over the channel region. A first stack including a tunnel insulation layer, a first charge trap layer, and a first blocking insulation layer are disposed over the first trapping region. A second stack including a tunnel insulation layer, a second charge trap layer, and a second blocking insulation layer are disposed over the second trapping region. An interlayer insulation layer is disposed over the substrate and covers the gate stack structure. A first contact plug and a second contact plug penetrate the interlayer insulation layer and respectively contact the source region and the drain region. A third contact plug penetrates the interlayer insulation layer, contacts the gate stack structure, and overlaps with the first and the second charge trap layers.

Owner:SK HYNIX INC

Cell trapping device

InactiveUS20150004687A1Bioreactor/fermenter combinationsBiological substance pretreatmentsIn planeCancer cell

A cell trapping device includes a housing that includes an inlet opening connected to an inlet line through which a cell dispersion liquid is introduced and an outlet opening connected to an outlet line through which the cell dispersion liquid is discharged; and a filter which is positioned within the housing and includes a trapping region for trapping cancer cells contained in the cell dispersion liquid. The filter is bonded to the housing, at least a part of the trapping region is formed of an observation region for observing the trapping region from the outside, the inlet line and the inlet opening are arranged at outer positions than the observation region when viewed from a normal line direction of the filter, and the inlet line is extended along an in-plane direction of the filter.

Owner:HITACHI CHEM CO LTD +1

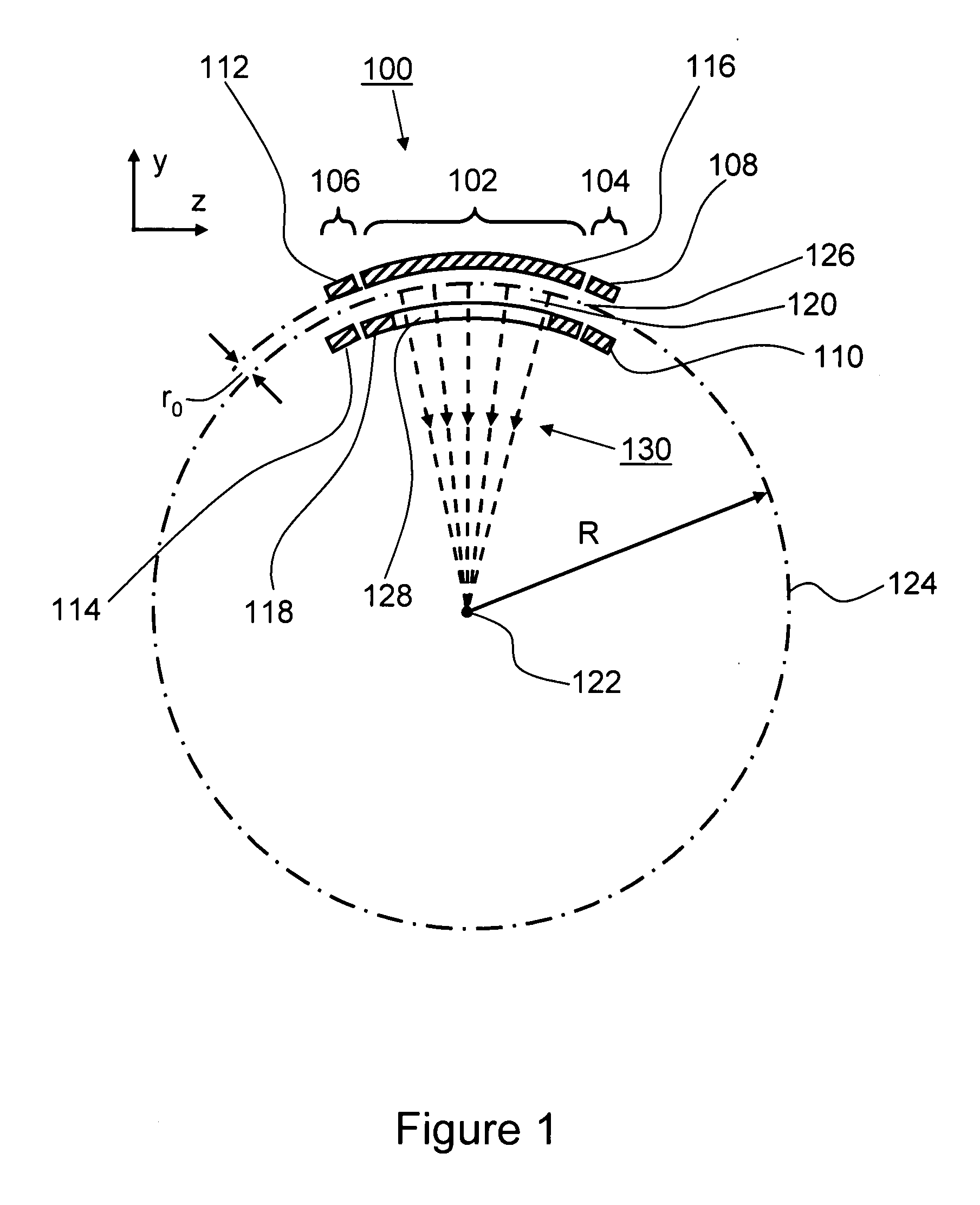

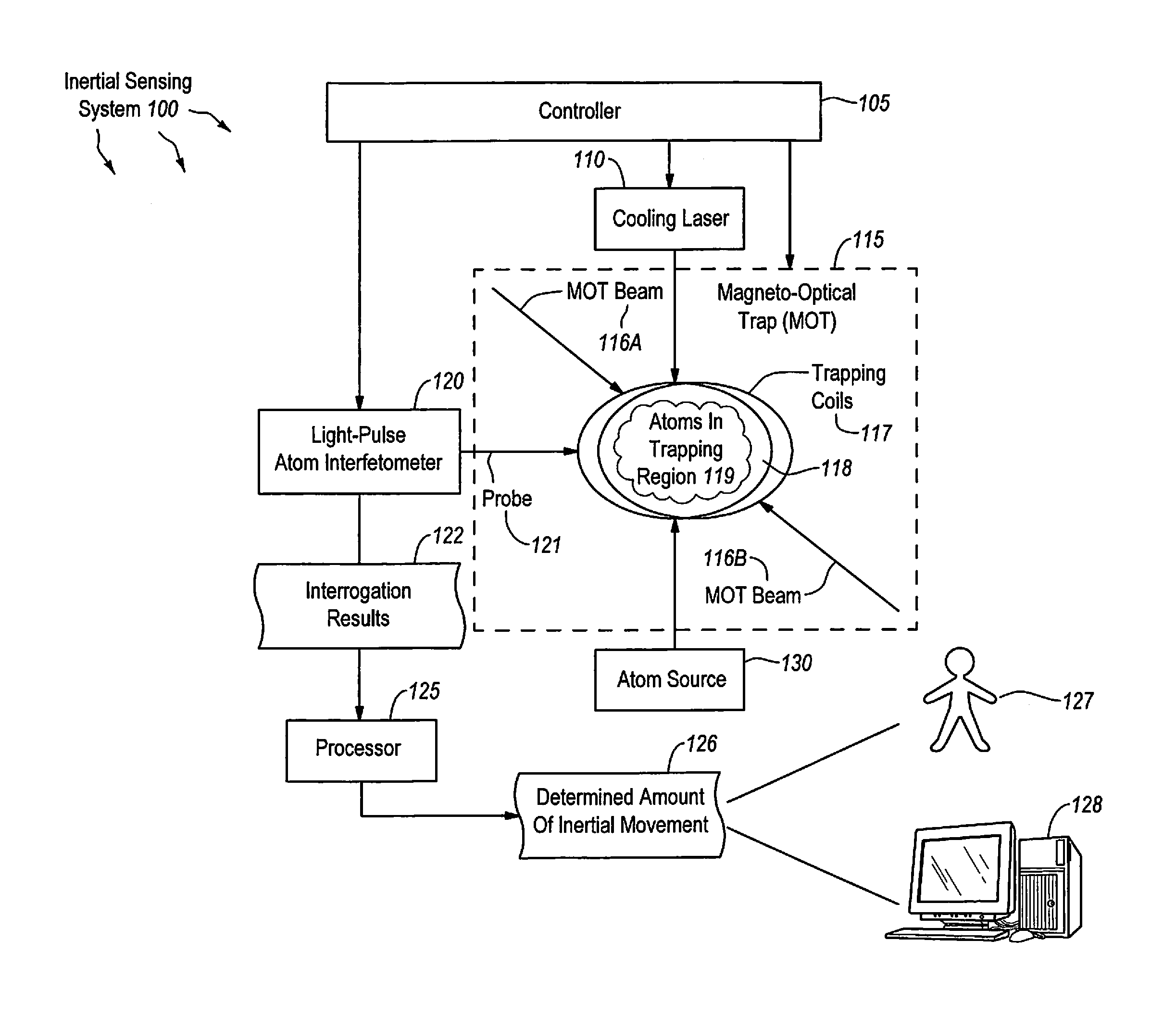

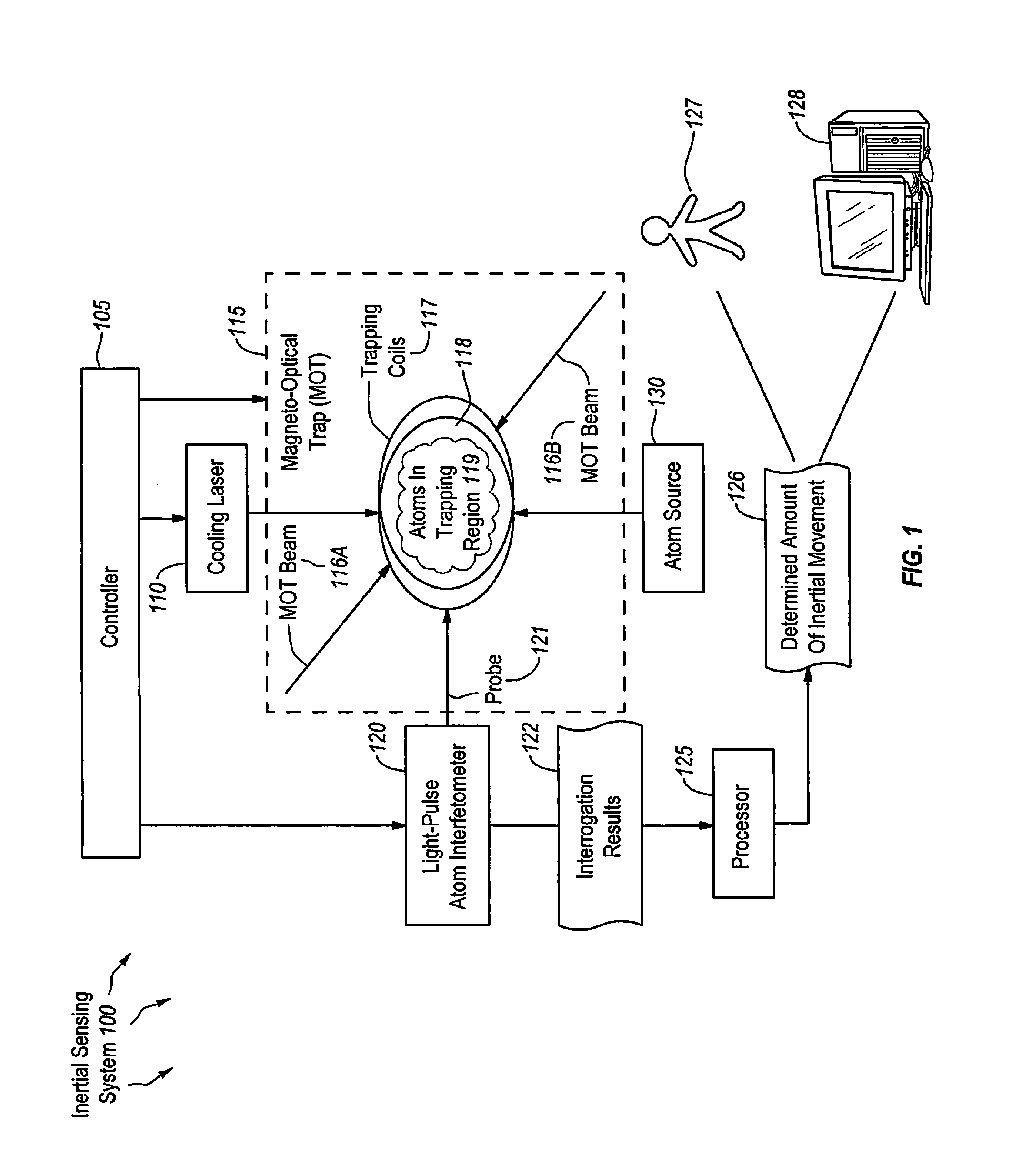

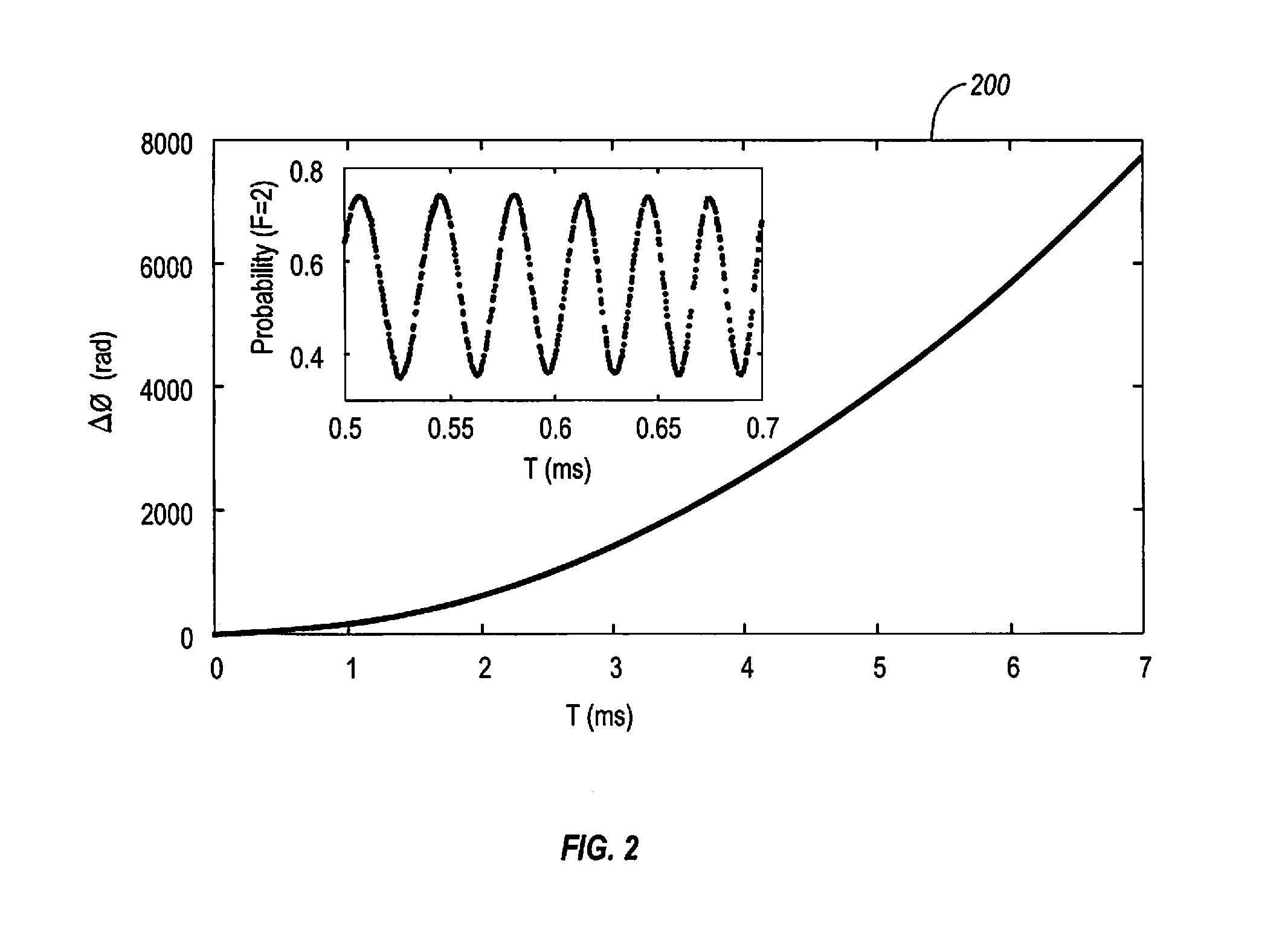

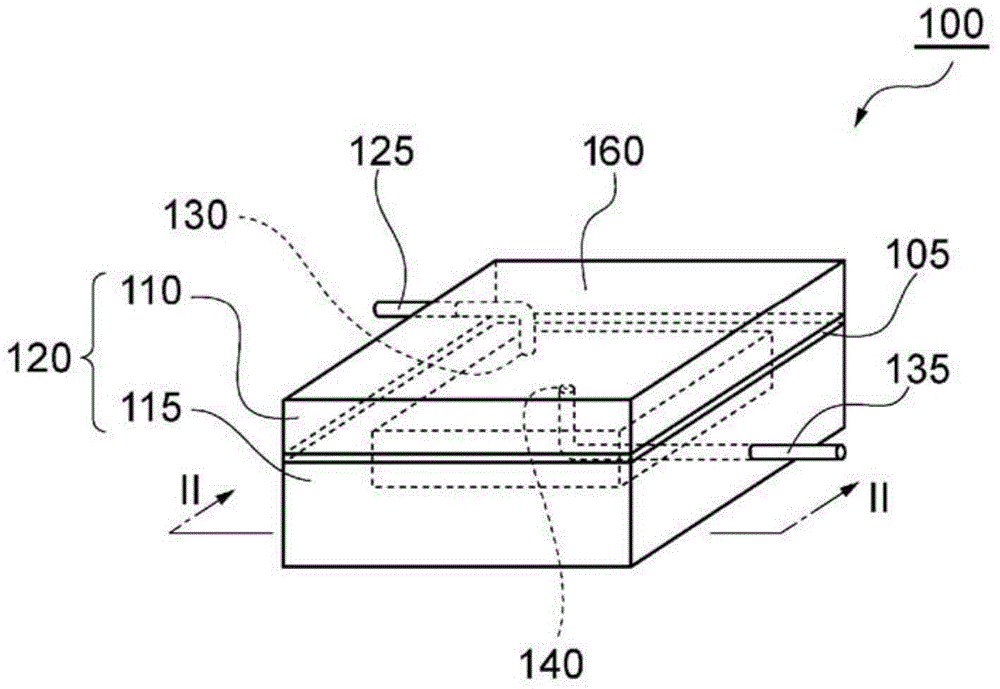

High data-rate atom interferometers through high recapture efficiency

An inertial sensing system includes a magneto-optical trap (MOT) that traps atoms within a specified trapping region. The system also includes a cooling laser that cools the trapped atoms so that the atoms remain within the specified region for a specified amount of time. The system further includes a light-pulse atom interferometer (LPAI) that performs an interferometric interrogation of the atoms to determine phase changes in the atoms. The system includes a controller that controls the timing of MOT and cooling laser operations, and controls the timing of interferometric operations to substantially recapture the atoms in the specified trapping region. The system includes a processor that determines the amount inertial movement of the inertial sensing system based on the determined phase changes in the atoms. Also, a method of inertial sensing using this inertial sensing system includes recapture of atoms within the MOT following interferometric interrogation by the LPAI.

Owner:NAT TECH & ENG SOLUTIONS OF SANDIA LLC

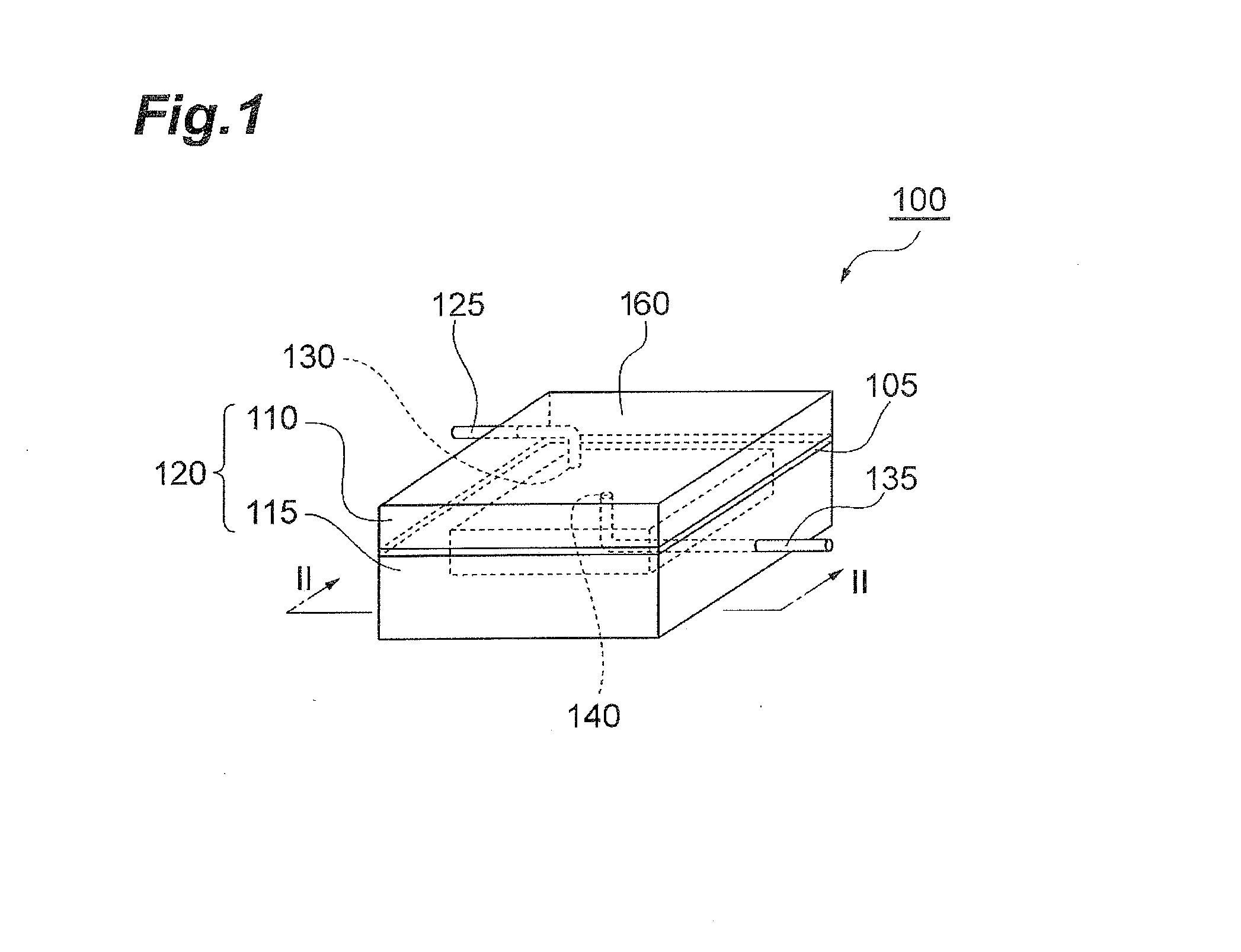

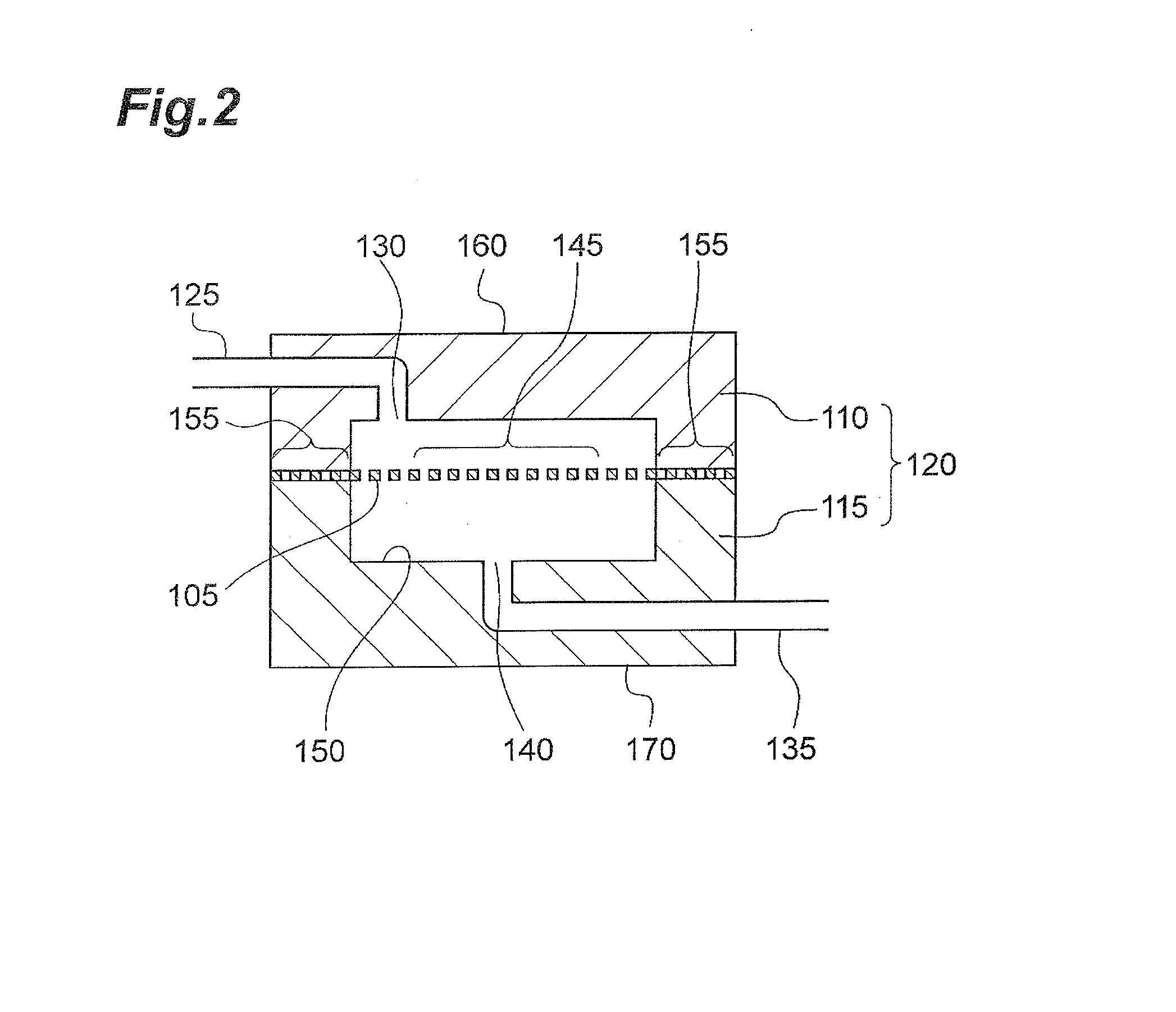

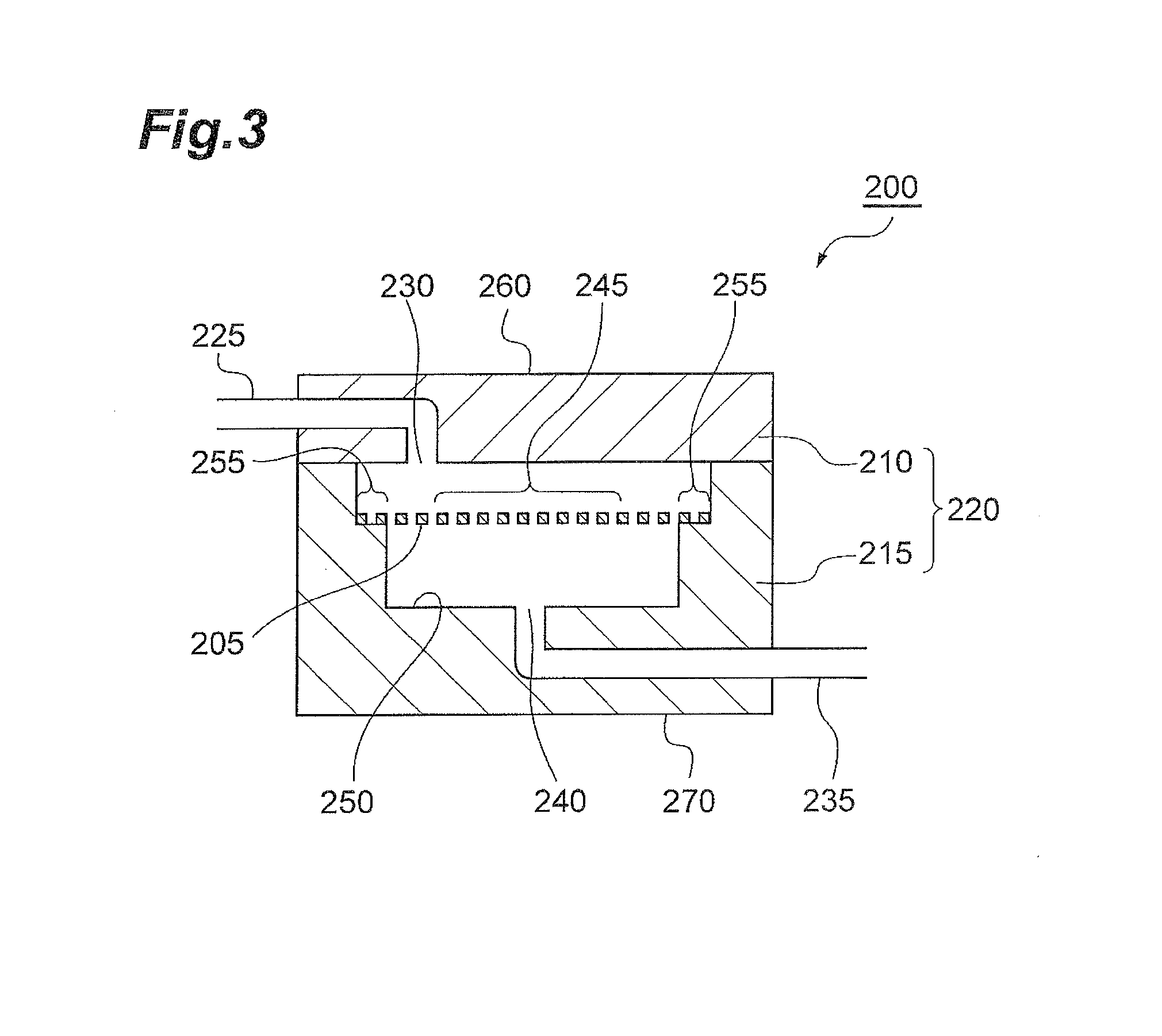

Cell Trapping Device

InactiveCN104039948ABioreactor/fermenter combinationsBiological substance pretreatmentsIn planeCancer cell

Provided is a cell trapping device with which a cell trapped on a filter can be observed without having to disassemble the device. The present invention comprises: a housing (120) that includes an inlet (130) to which an inlet pipe (125) is connected for the inflow of a cell dispersion liquid, and an outlet (140) to which an outlet pipe (135) is connected for the outflow of the cell dispersion liquidand a filter (105) that is disposed in the housing (120) and comprising a trapping region to trap a cancer cell in the cell dispersion liquid. The filter (105) is coupled with the housing (120). At least a portion of the trapping region serves as an observation region for the observation of the trapping region from outside. The inlet pipe (125) and the inlet (130) are disposed at a position further outward than the observation region when viewed in a normal direction of the filter (105). The inlet pipe (125) extends in an in-plane direction of the filter (105).

Owner:RESONAC CORPORATION +1

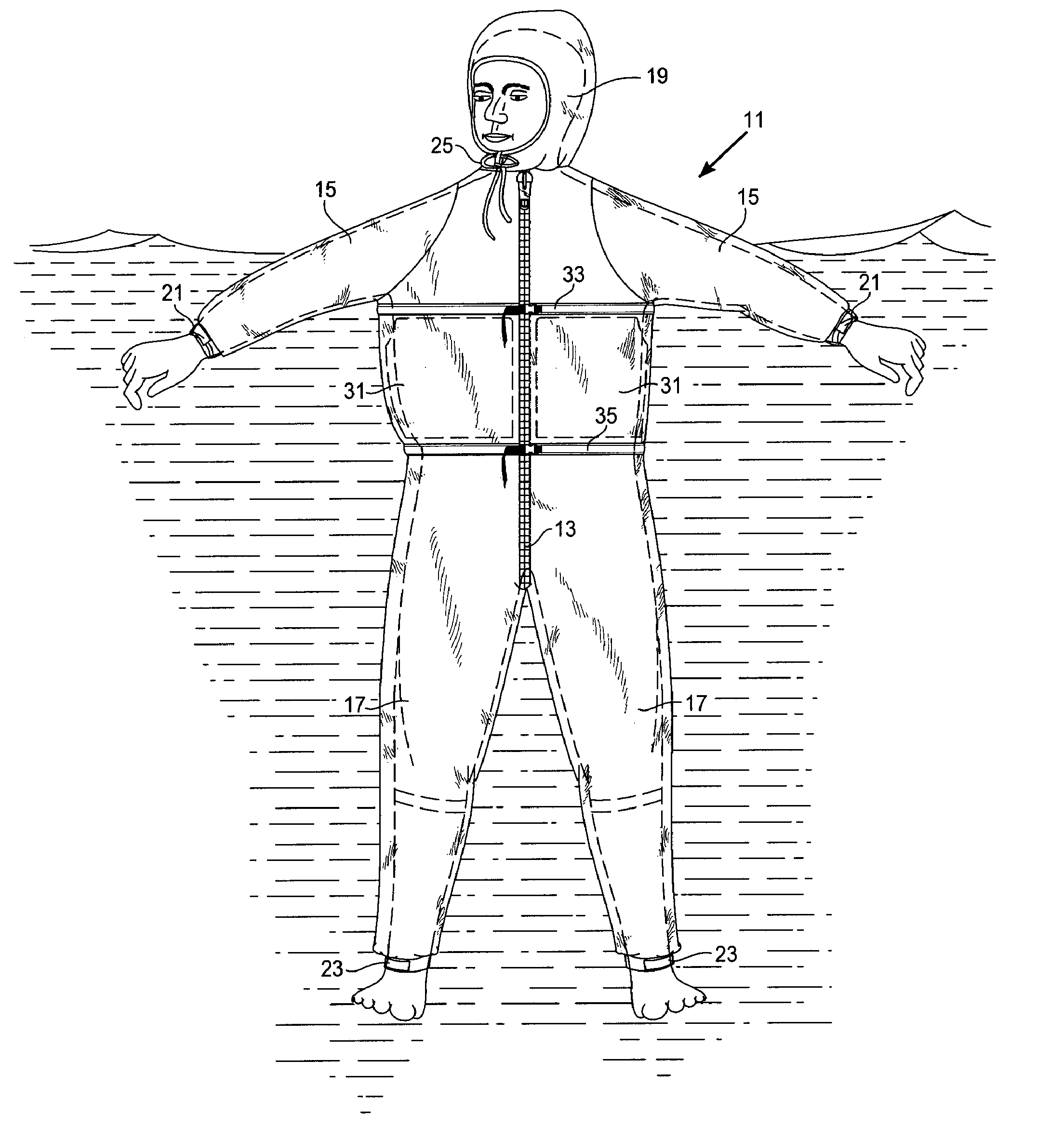

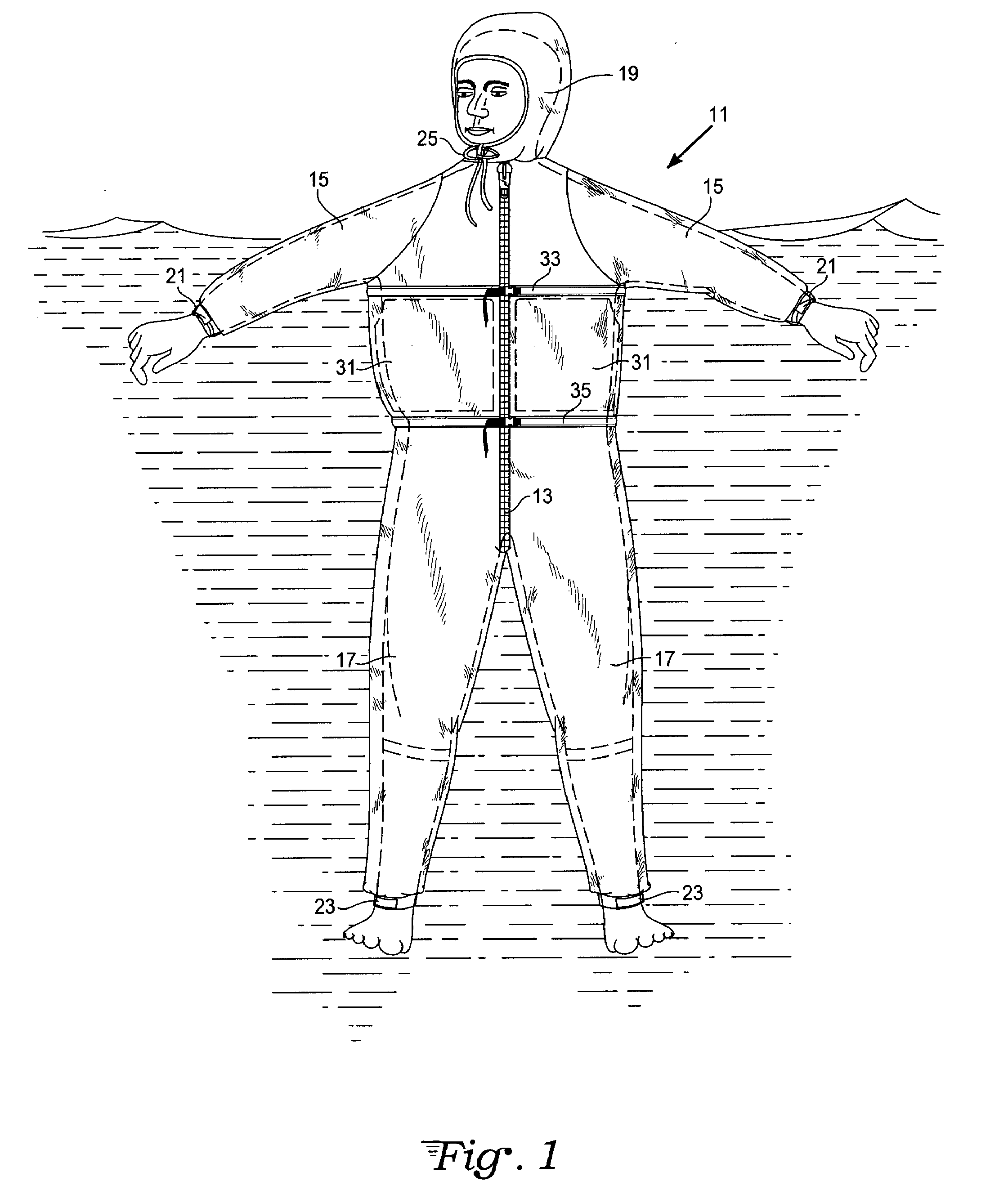

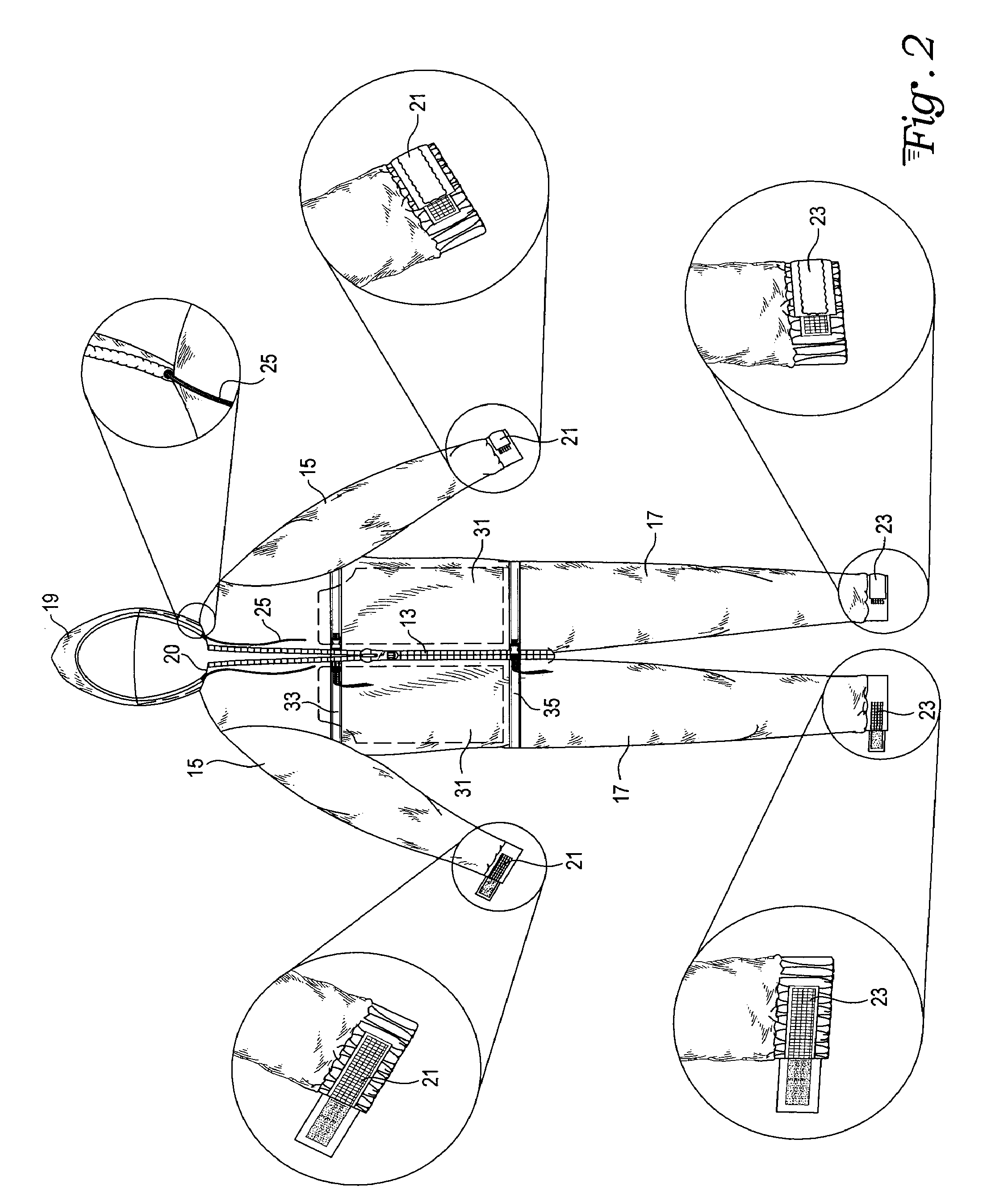

Thermally protective survival garment

InactiveUS20080301861A1Restricting water circulationConvenient thermal protectionChemical protectionHeat protectionEngineeringWater circulation

A thermally protective coveralls style suit having a plurality of separate water trapping regions between the suit and a user. The suit has a front slide fastener from crotch to neck with water entry retarding arm closures at the wrists and leg closures at ankles or thighs forming water trapping regions, leaving hands and feet free for swimming. Upper and lower chest straps cooperate forming water trapping regions by blocking pocket or water exchange between upper and lower torso regions. Permissive water entry at wrists, ankles or thighs, and neck or face, without circulation or exchange to surrounding water, allows separate pockets or thin film layers of water in the upper, lower, and central torso regions to insulate the body somewhat like a wetsuit where a single film provides insulation. An optional hood is provided to form another pocket or thin film layer without water circulation. Floatation pads assist buoyancy. A jacket embodiment is truncated at the lower chest strap.

Owner:MEISTRELL ROBERT F +1

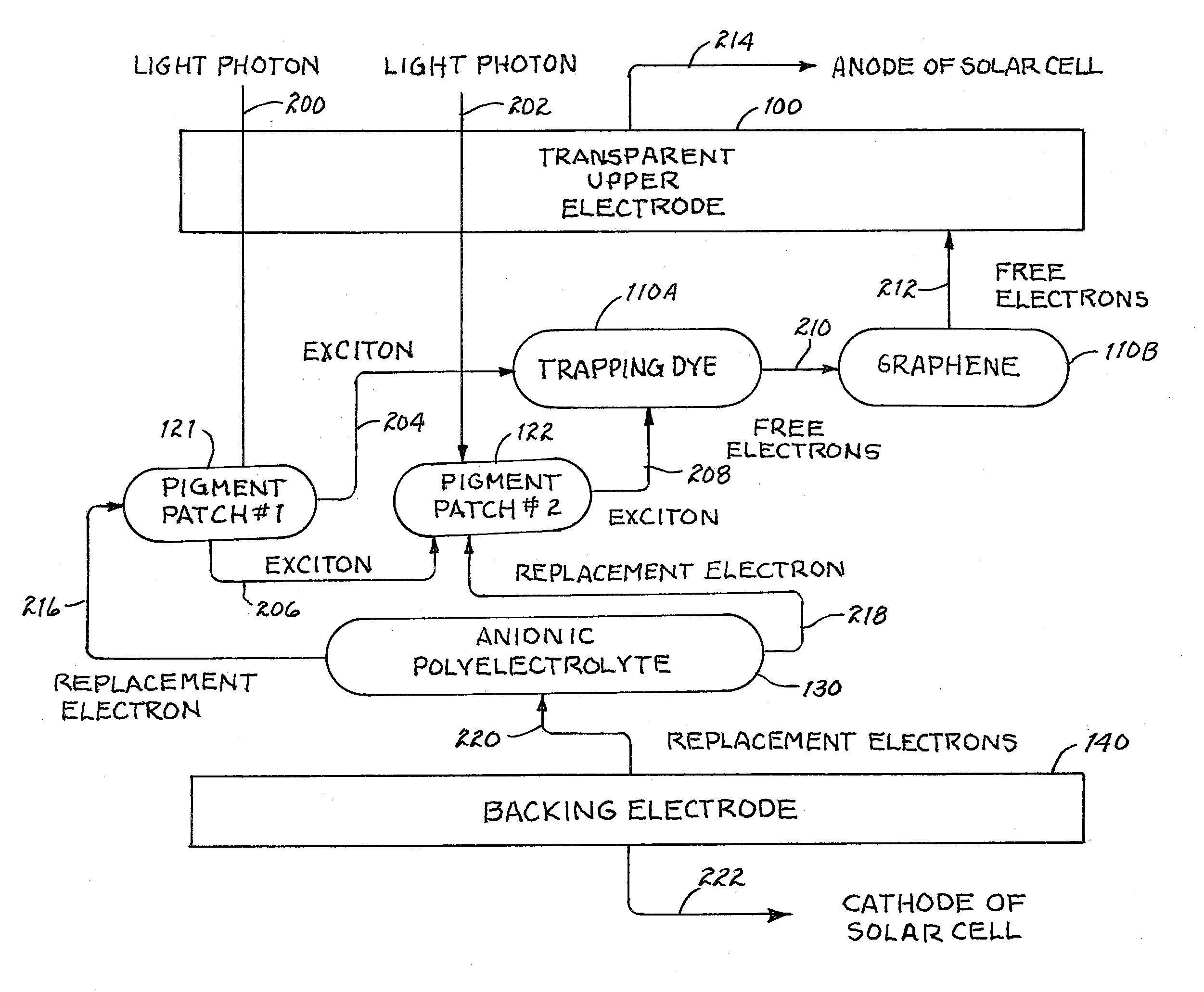

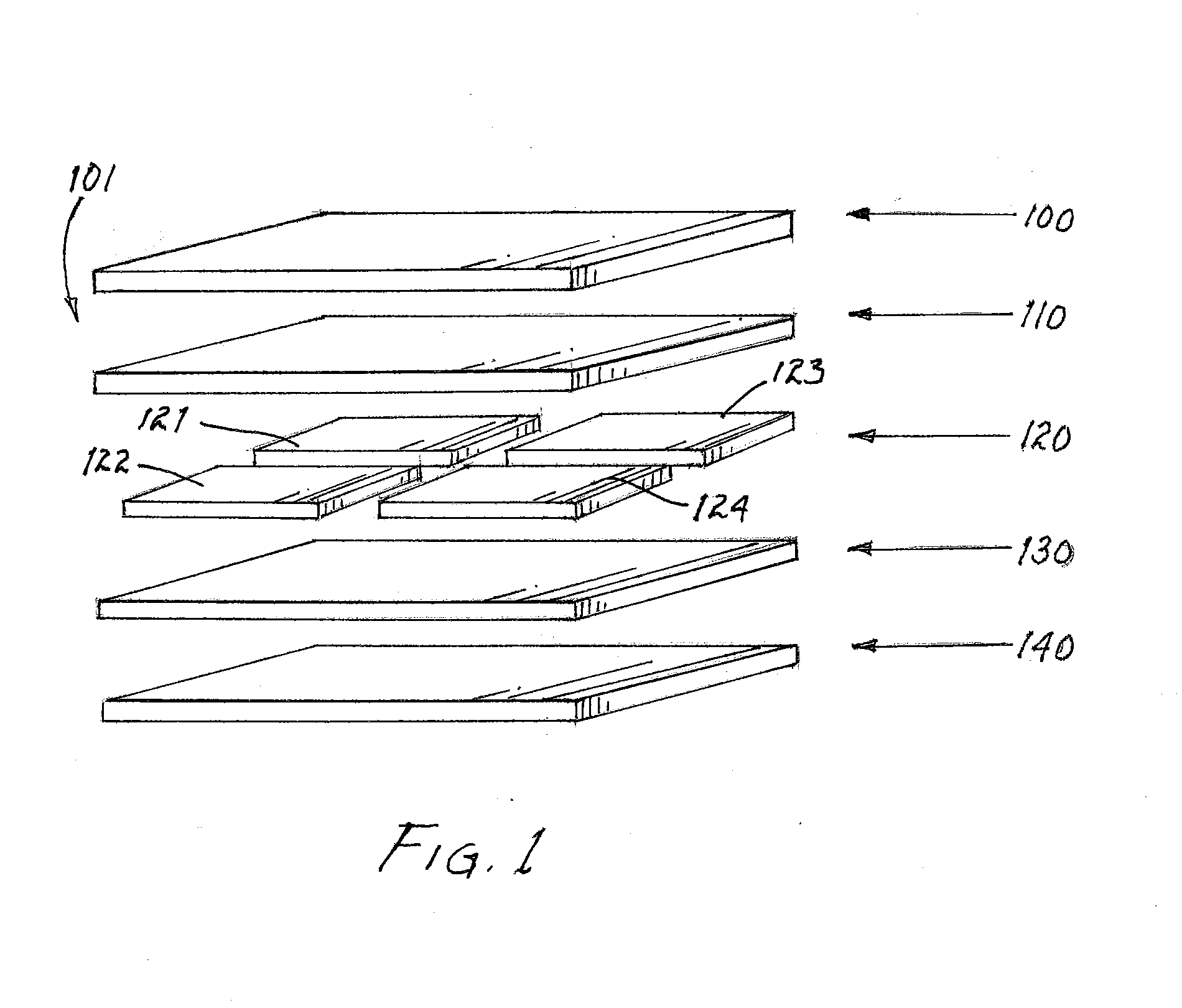

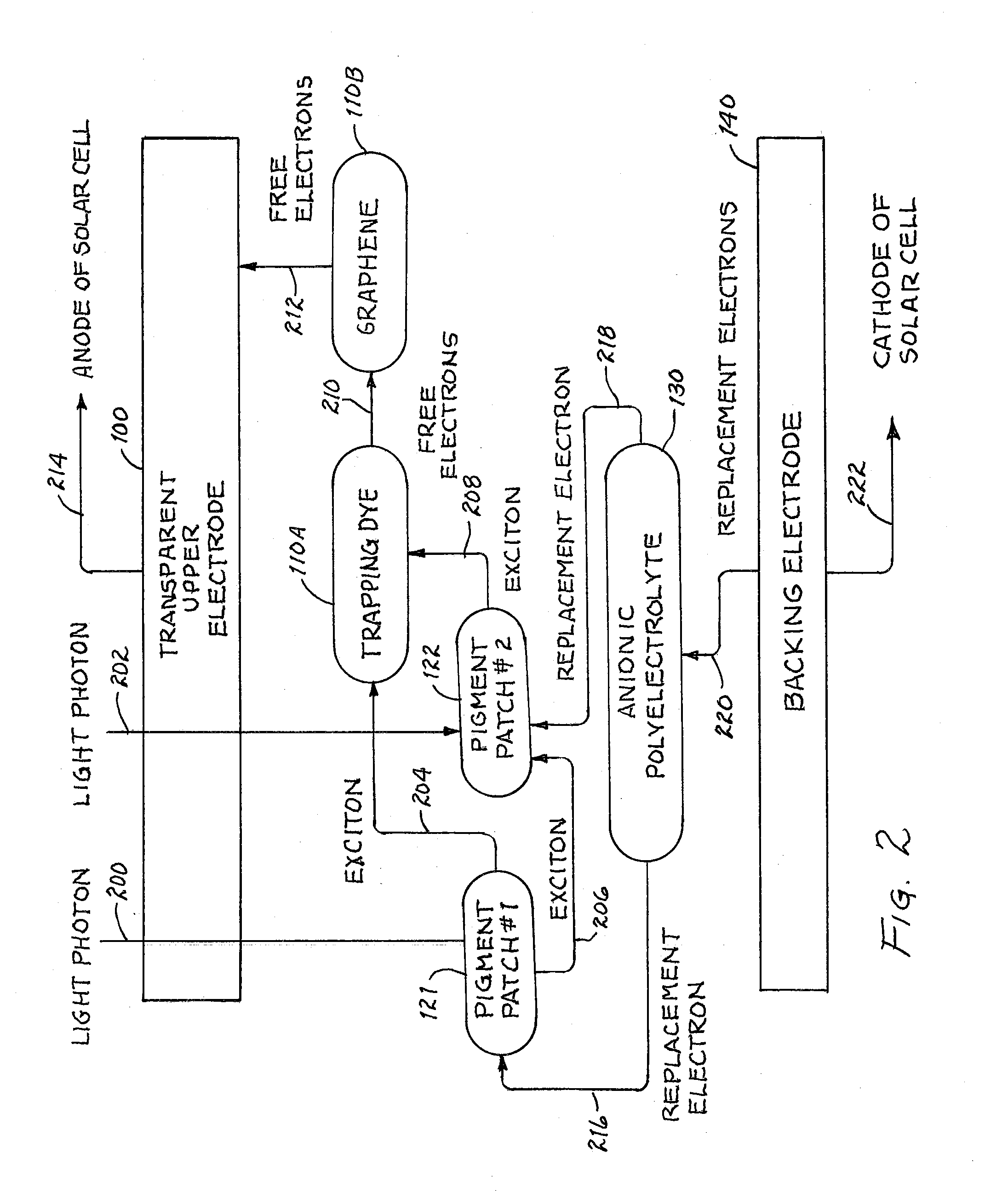

Graphene-based solar cell

InactiveUS20120097238A1Fast conductionFacilitates electron transferMaterial nanotechnologyElectrolytic capacitorsPolyelectrolyteTrapping region

A solar cell includes a transparent upper electrode for conducting electrons and for allowing incoming photons of light to pass therethrough. An exciton trapping region is disposed proximate the upper electrode, and includes graphene and an exciton trapping dye. The trapping dye traps captured excitons, and the graphene rapidly conducts freed electrons therefrom to the upper electrode. A pigment layer, in close proximity to the exciton trapping region, includes one or more pigment dyes that absorb light photons and emit excitons for transmission to the trapping dye. Excitons emitted by a first pigment dye can further trigger emission of excitons by a second pigment dye. A backing electrode is electrically coupled to the pigment layer via an anionic polyelectrolyte for transporting electrons to the pigment layer to replenish electrons conducted by the transparent upper electrode.

Owner:ISAACS SODEYE AKINBODE I

Method and apparatus for providing ion barriers at the entrance and exit ends of a mass spectrometer

InactiveUS7495213B2Time-of-flight spectrometersPositive/negative analyte ion analysis/introduction/generationIon trap mass spectrometryPhysical chemistry

There is provided a linear ion trap having an ion guide and a method of operating same. The ion guide has a first end and a second end. The method involves a) providing a first group of ions within the ion guide; b) providing a second group of ions within the ion guide, the second group of ions being opposite in polarity to the first group of ions; c) providing an RF drive voltage to the ion guide to radially confine the first group of ions and the second group of ions in the ion guide; d) providing a gas flow of an inert gas in a first axial direction away from the first end of the ion guide and toward a middle of the ion guide to repel both the first group of ions and the second group of ions from the first end of the ion guide; and, e) providing a trapping region barrier for repelling both the first group of ions and the second group of ions away from the second end of the ion guide. The gas flow in the first axial direction and the trapping region barrier together define a main trapping region for trapping both the first group of ions and the second group of ions.

Owner:DH TECH DEVMENT PTE

Charge trapping device and method of forming the same

InactiveUS20050156158A1Seizure suppressionMaximize “source side” trappingSolid-state devicesSemiconductor/solid-state device manufacturingElectrical resistance and conductanceEngineering

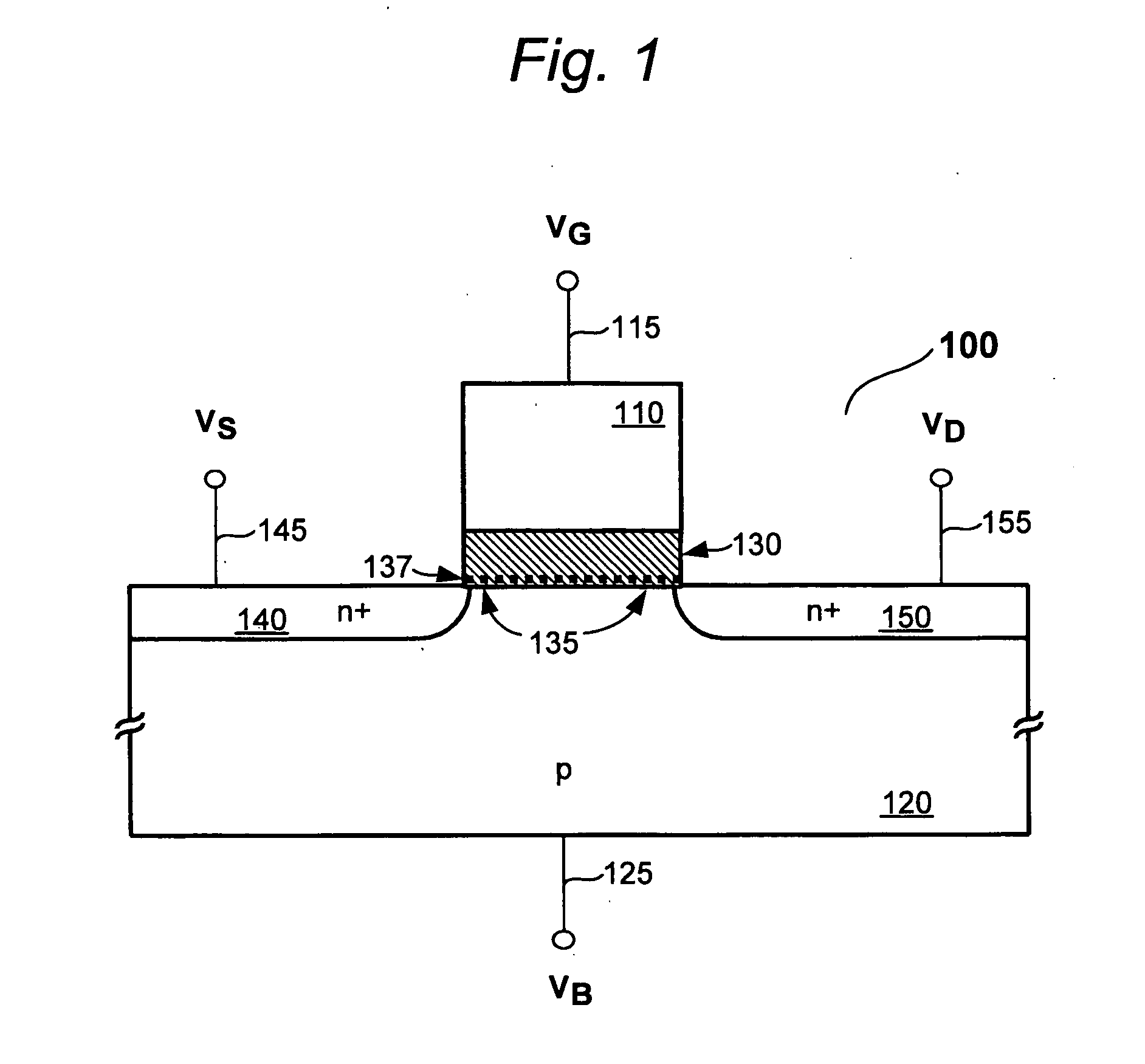

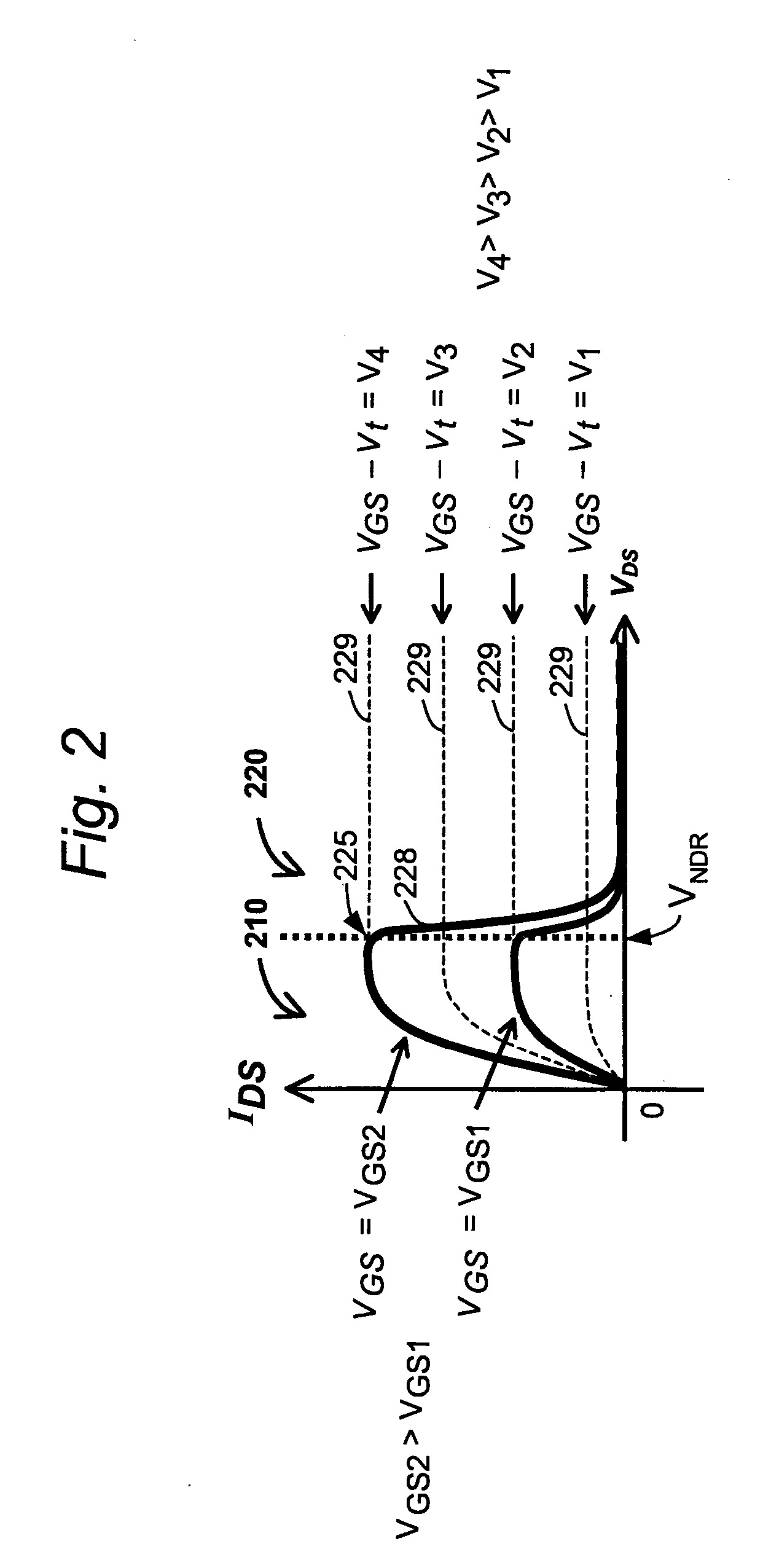

A charge trapping device, and a method of forming the same is disclosed. Charge traps are optimally distributed through a trapping region based on controlling various conventional processing operations, such as an implant, an anneal, an insulator film deposition, and the like. In some embodiments, FETs can be configured to include a negative differential resistance (NDR) characteristic when they utilize a particular charge trap energy and distribution.

Owner:SYNOPSYS INC

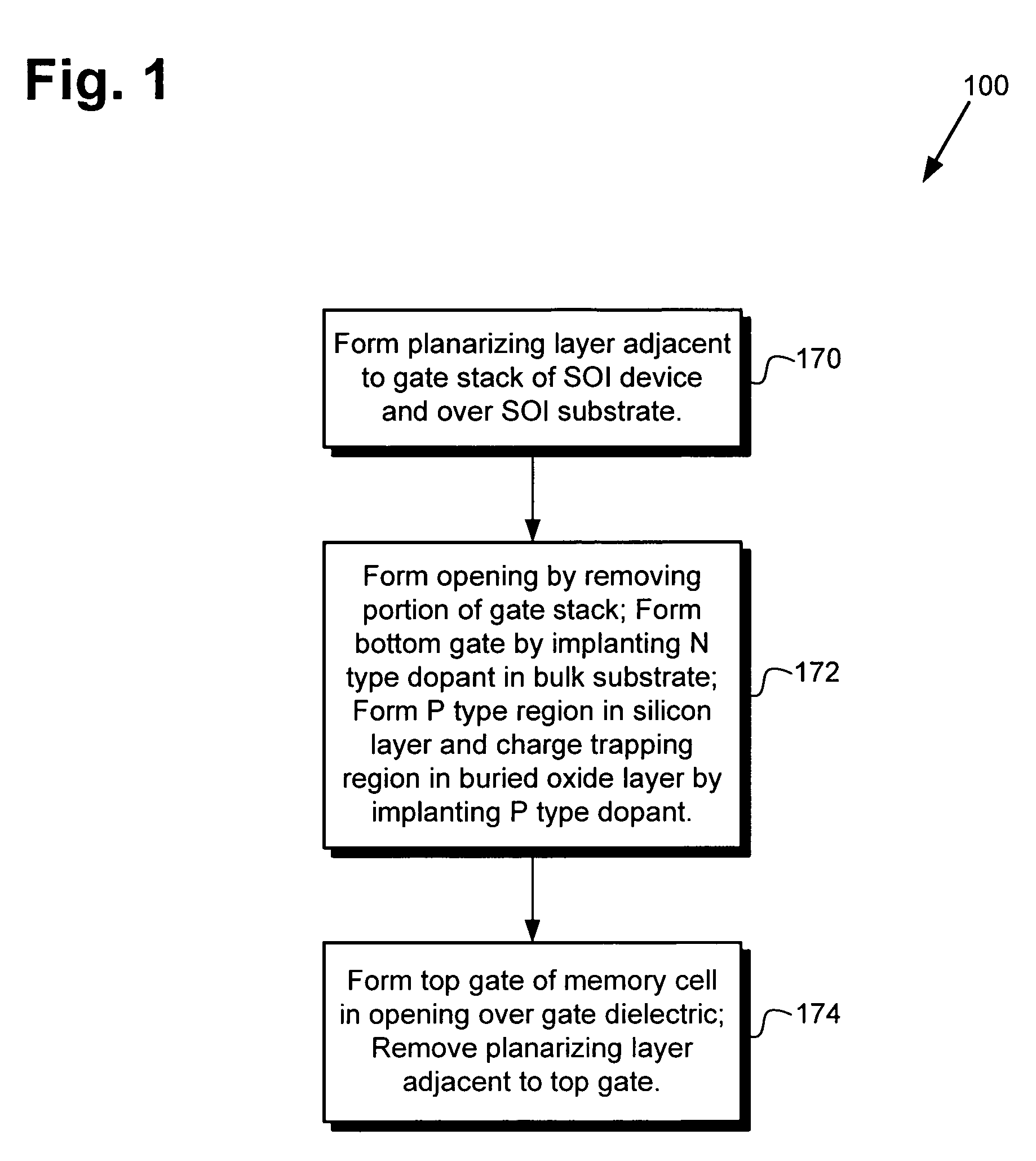

Method for forming a one-transistor memory cell and related structure

Owner:GLOBALFOUNDRIES U S INC