Patents

Literature

113 results about "Dc field" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

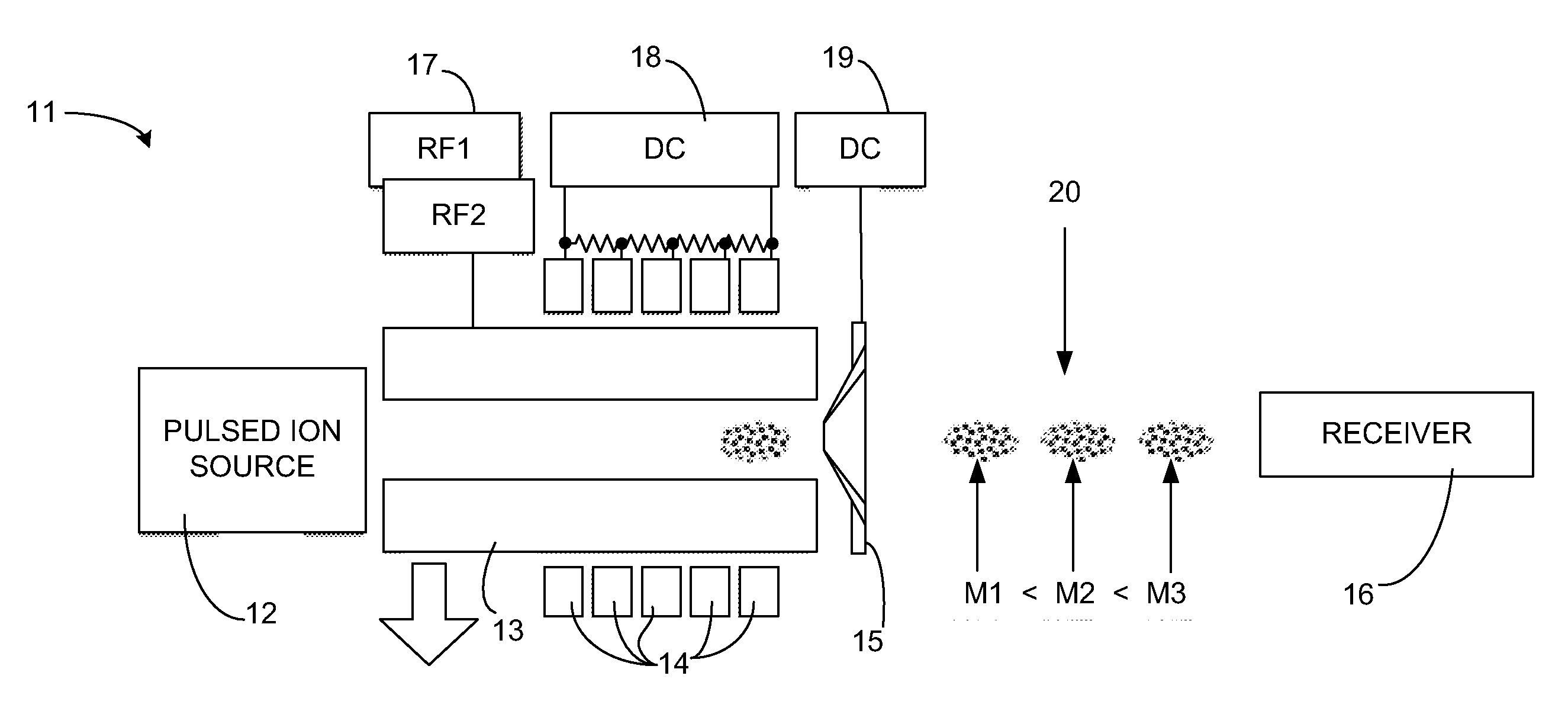

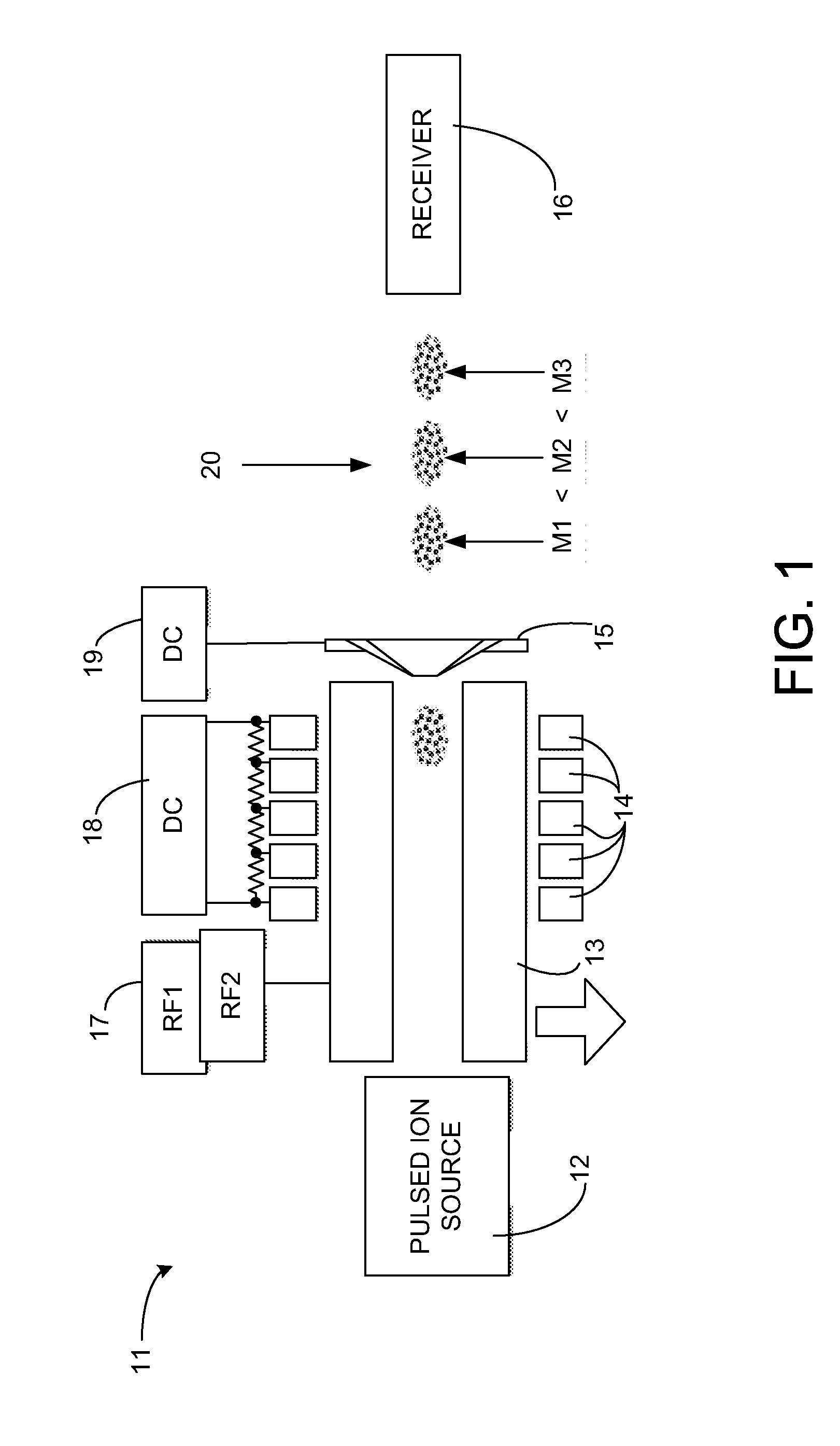

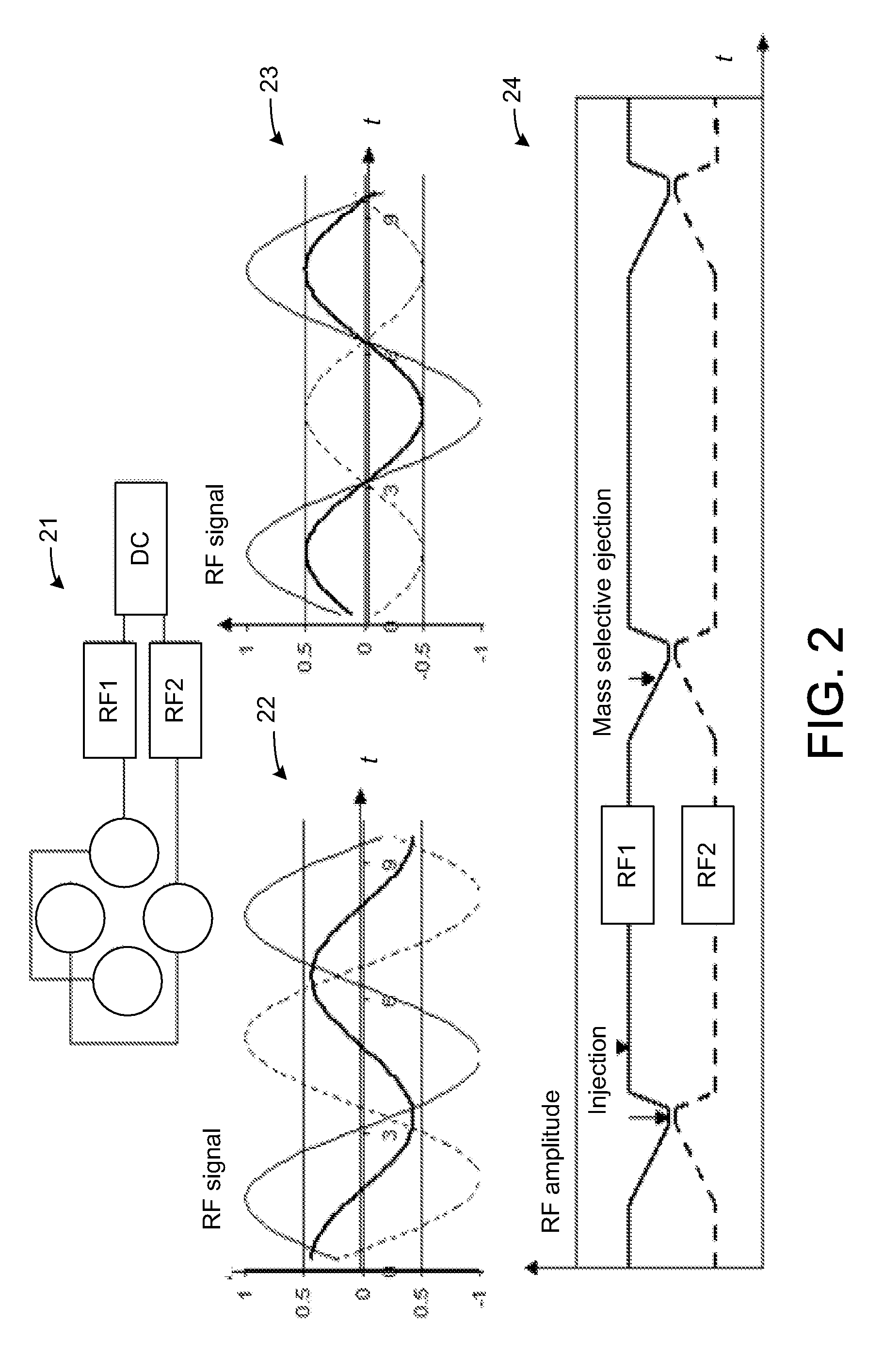

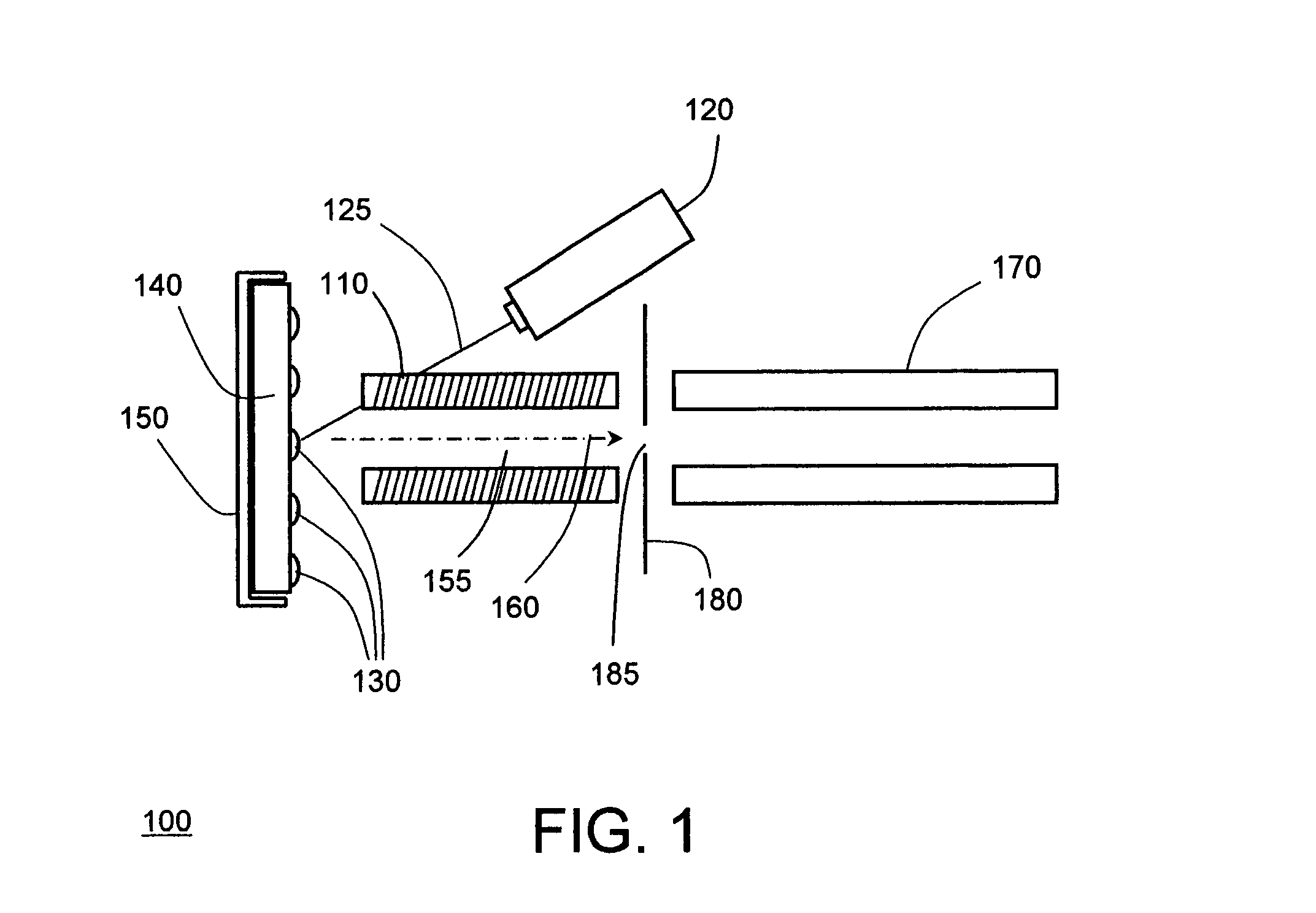

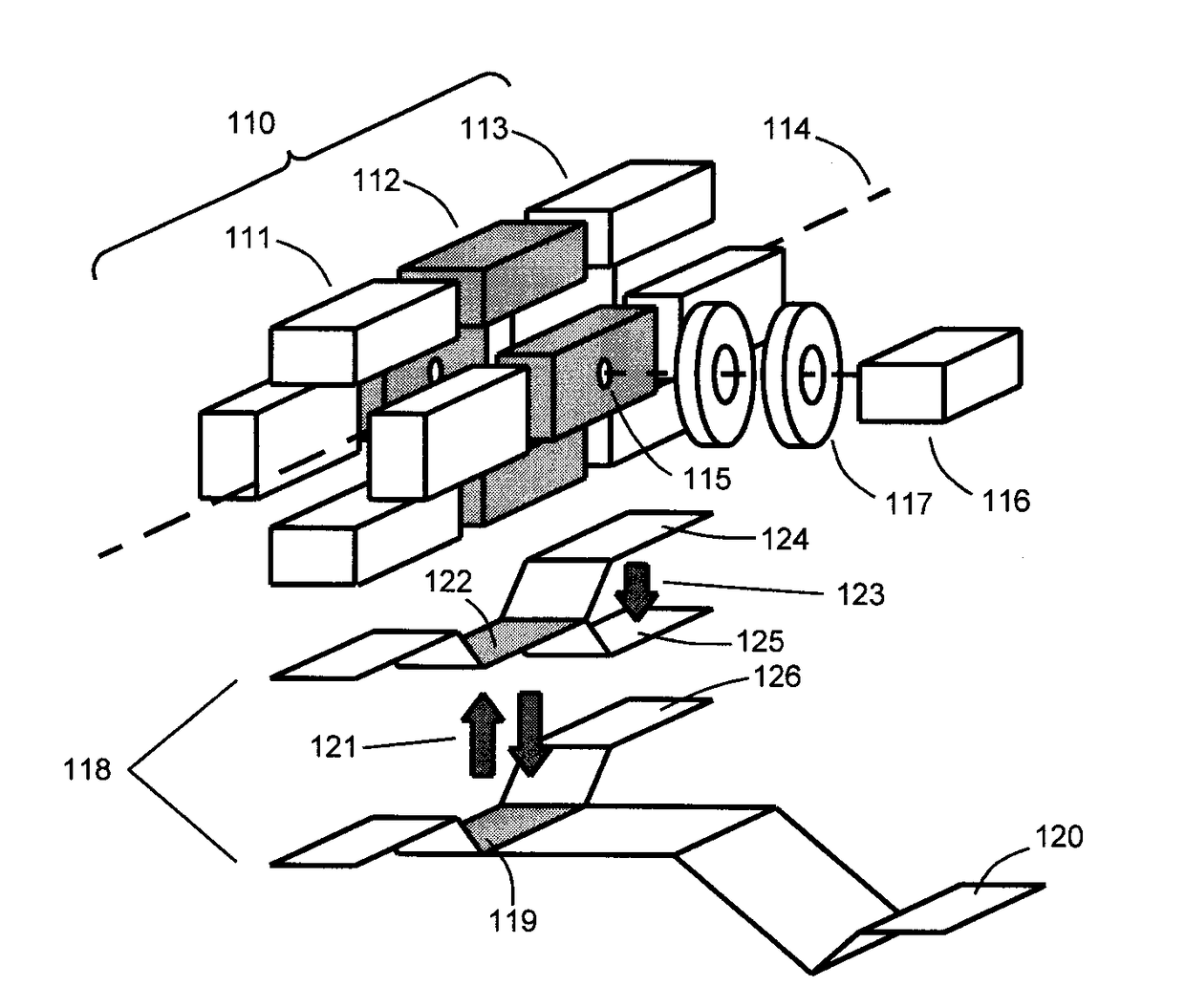

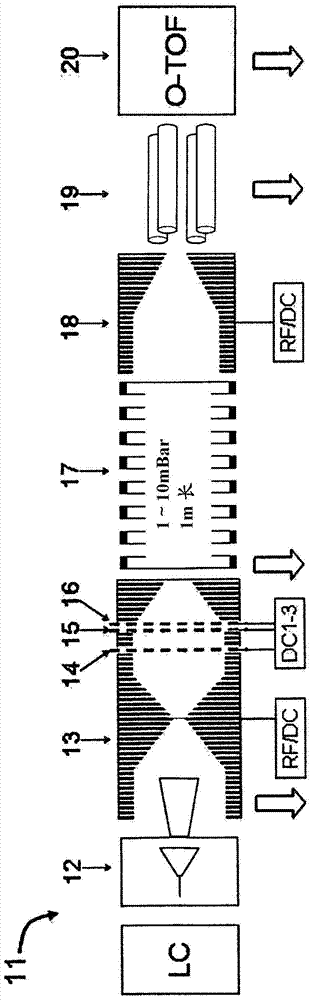

Linear ion trap with an imbalanced radio frequency field

ActiveUS20070158545A1Improving duty cycle of o-TOFQuick scanIsotope separationSpectrometer combinationsIon trap mass spectrometryIon beam

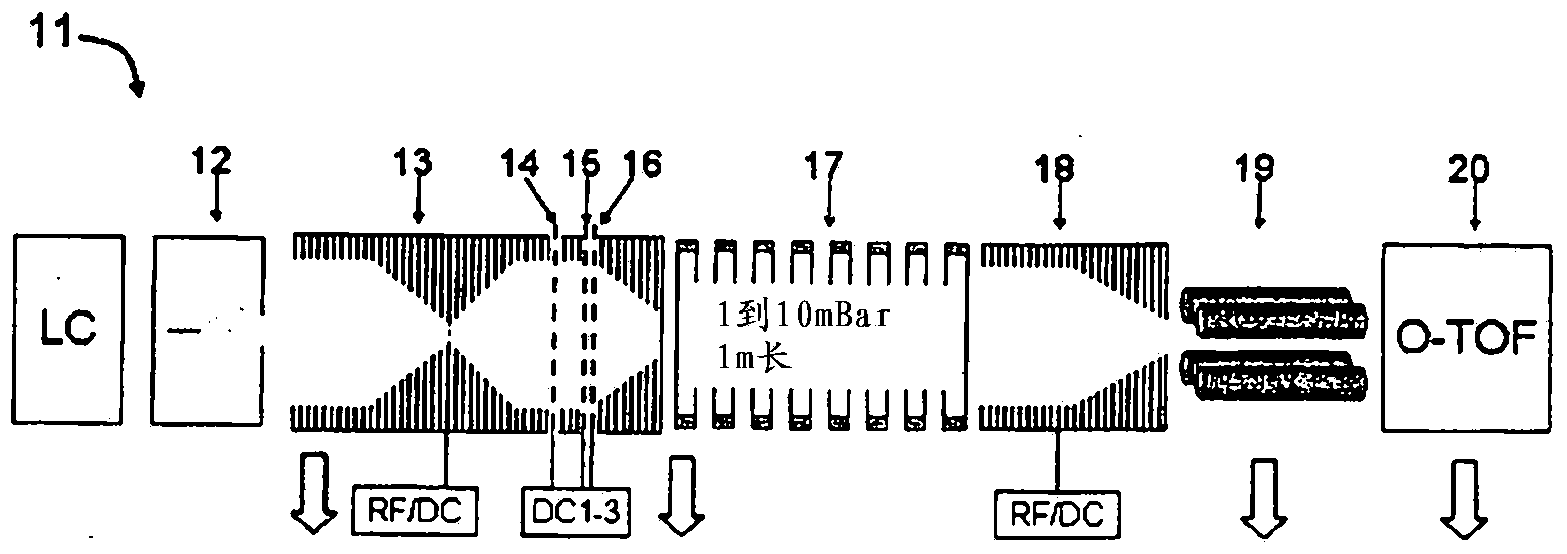

An imbalanced radio frequency (RF) field creates a retarding barrier near the exit aperture of a multipole ion guide, in combination with the extracting DC field such that the barrier provides an m / z dependent cut of ion sampling. Contrary to the prior art, the mass dependent sampling provides a well-conditioned ion beam suitable for other mass spectrometric devices. The mass selective sampling is suggested for improving duty cycle of o-TOF MS, for injecting ions into a multi-reflecting TOF MS in a zoom mode, for parallel MS-MS analysis in a trap-TOF MS, as well as for moderate mass filtering in fragmentation cells and ion reactors. With the aid of resonant excitation, the mass selective ion sampling is suggested for mass analysis.

Owner:LECO CORPORATION

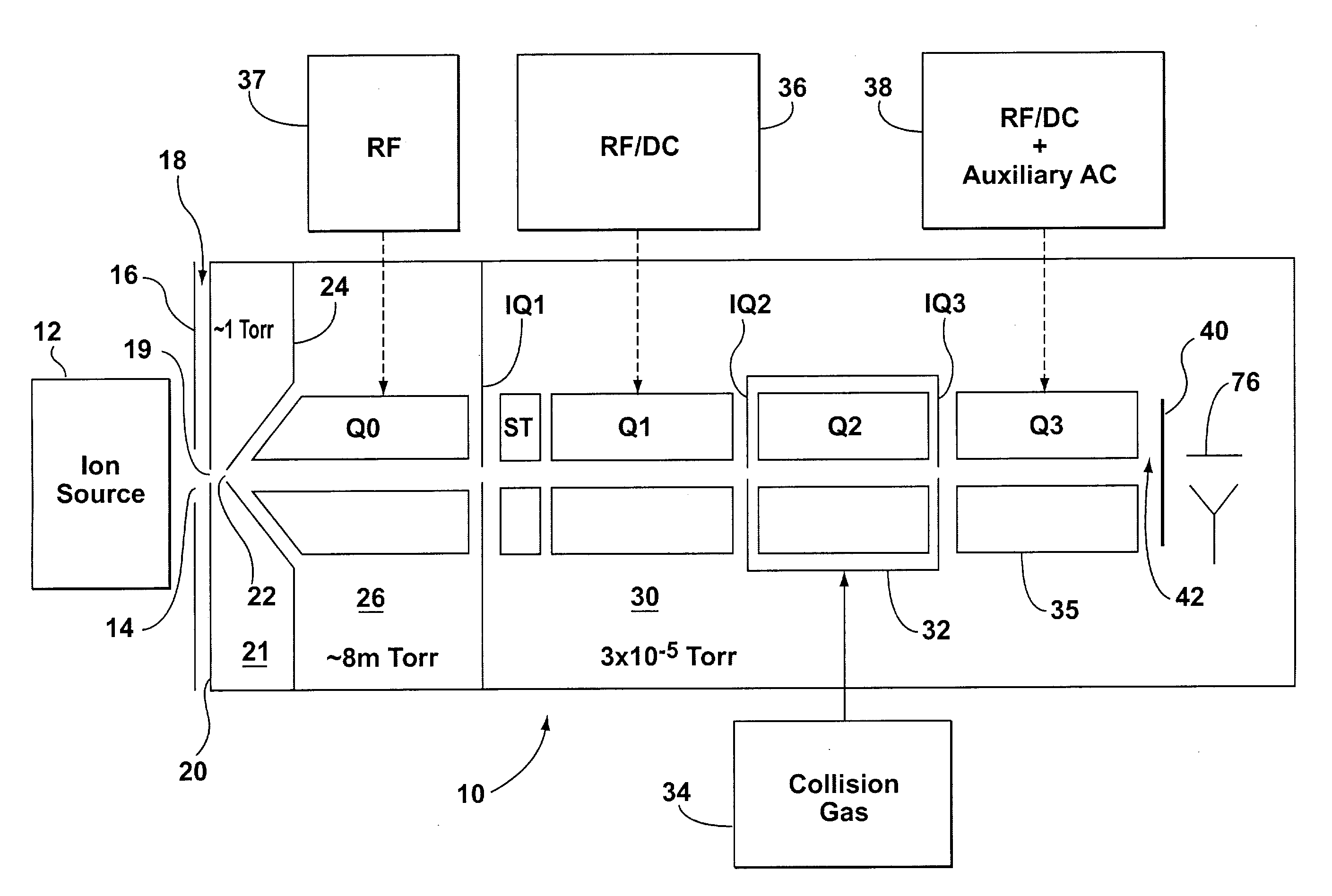

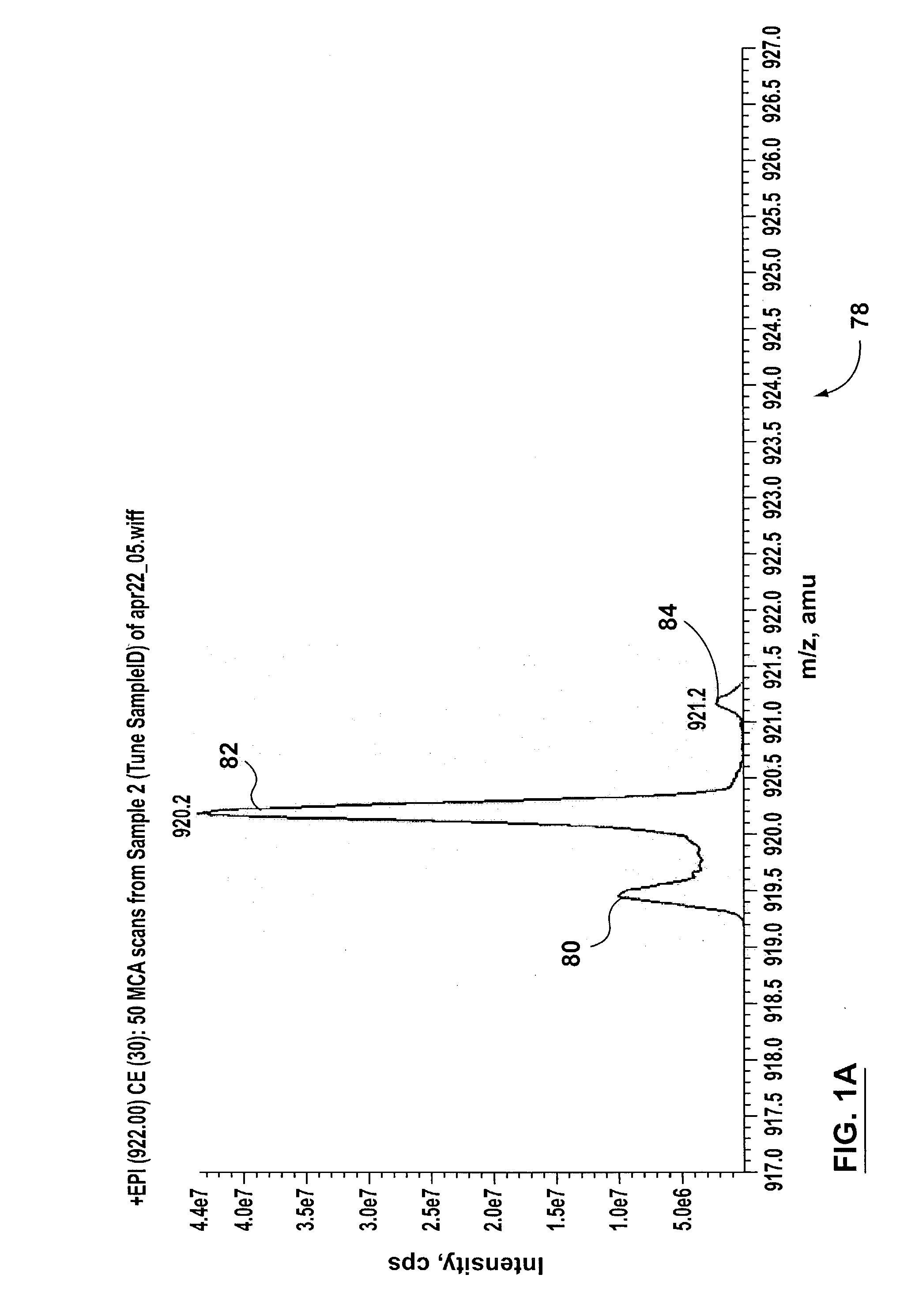

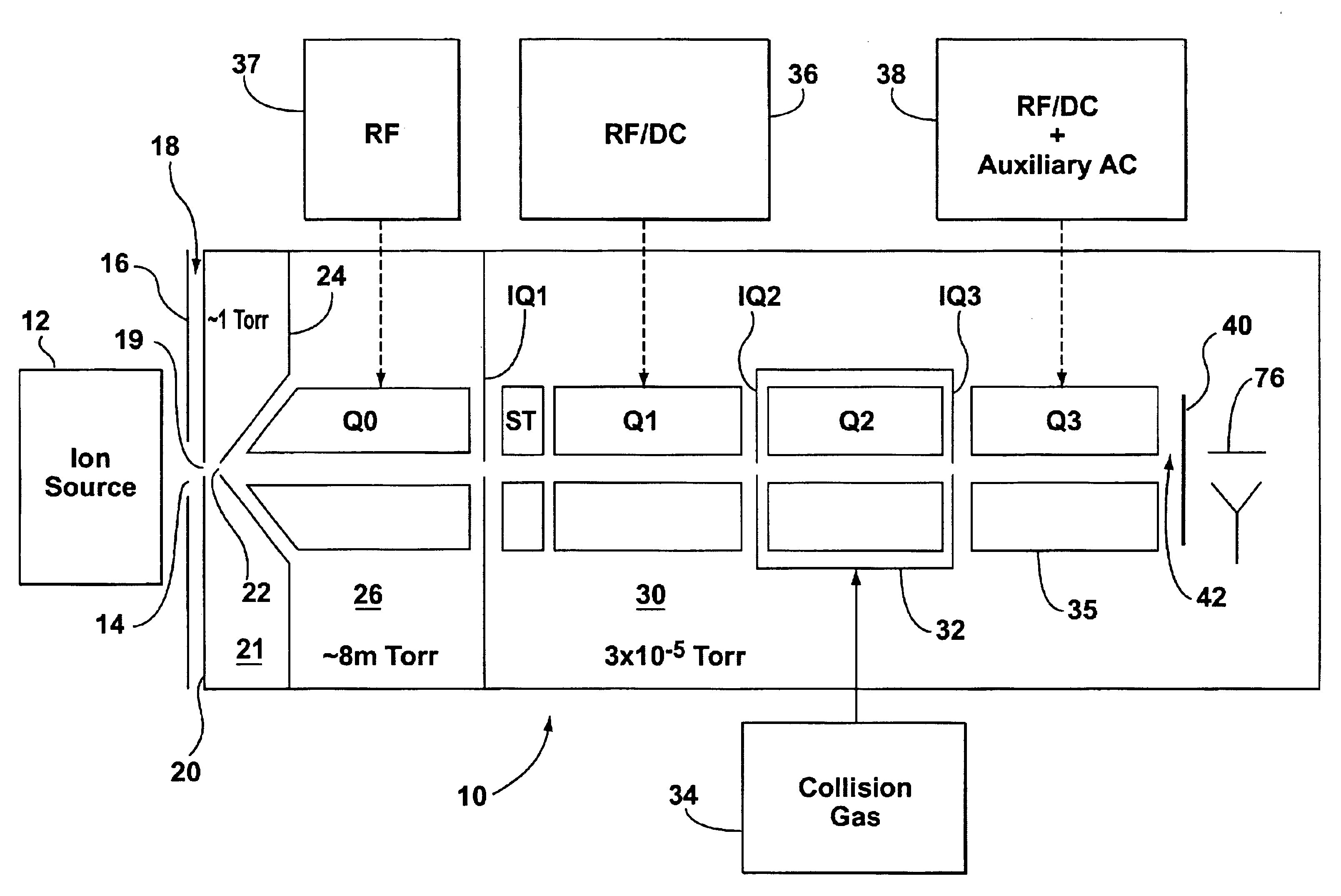

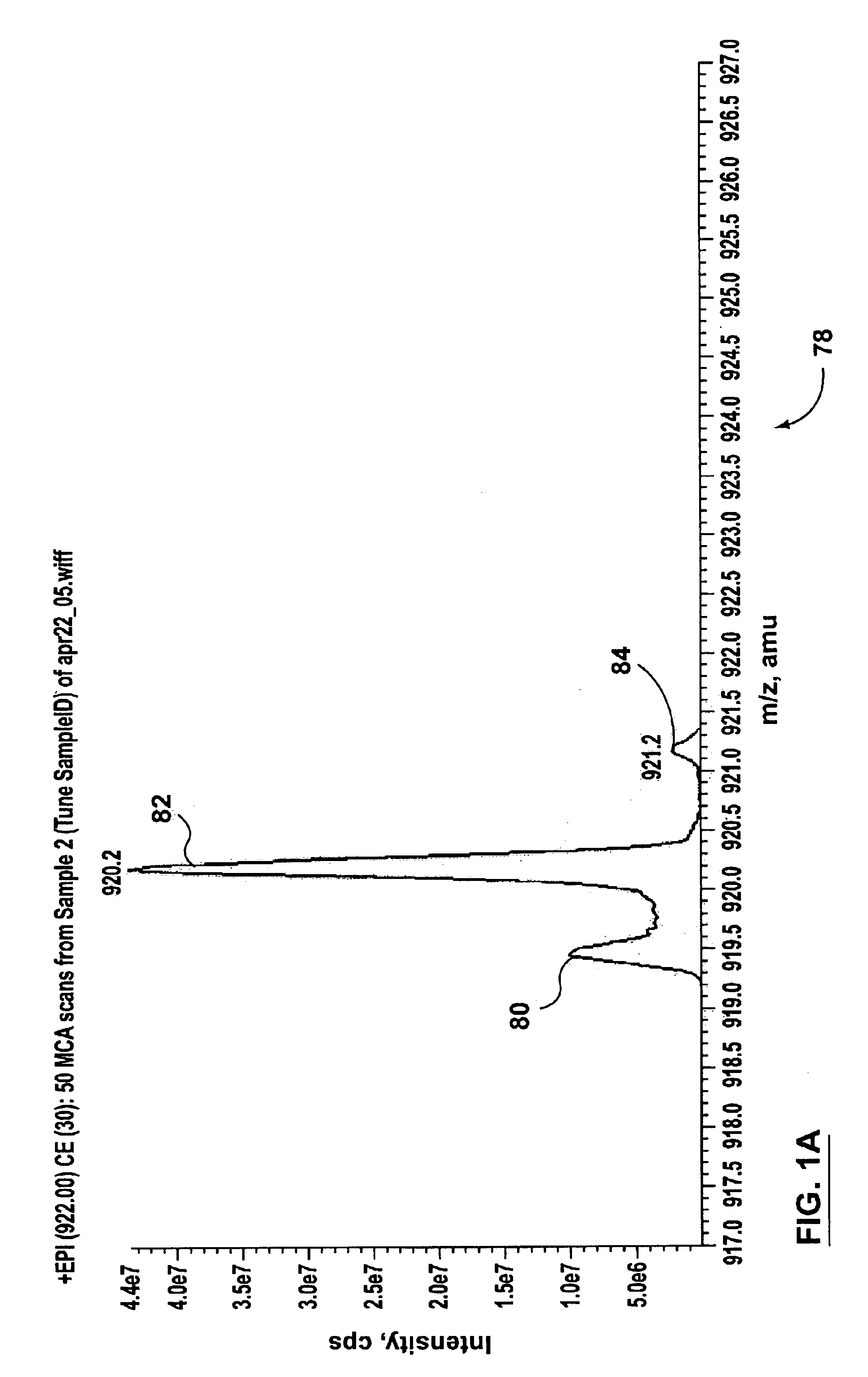

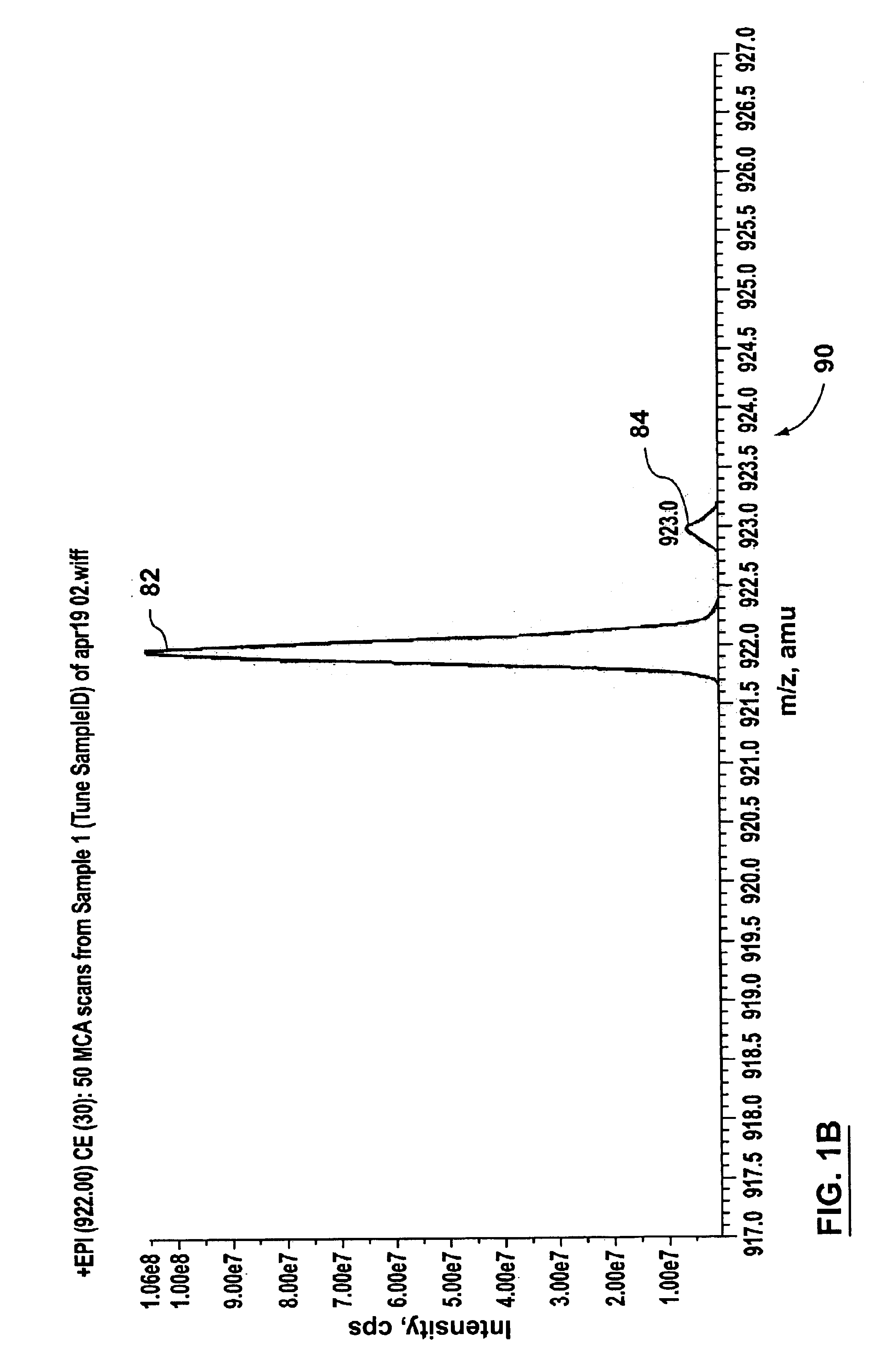

Methods and apparatus for reducing artifacts in mass spectrometers

InactiveUS20040011956A1Excellent characteristicsImprove propertiesStability-of-path spectrometersMaterial analysis by electric/magnetic meansVoltage gradientMass analysis

The invention solves the problem of artifact ghost peaks which can sometimes arise in mass spectrometers that employ a quadrupole rod set for both trapping and mass analyzing the trapped ions. The problem arises as a result of randomly distributed voltage gradients along the length of the rods. Three solutions are presented. The first approach involves improving the conduction characteristics of the rod sets. The second approach involves the application of at least one continuous axial DC field to the trapping quadrupole rod set in order to urge ions towards a pre-determined region of the trap, thereby avoiding voltage gradients. The third approach involves the application of one or more discrete axial fields to create one or more potential barriers along the axial dimension of the trap (in addition to the barriers used to initially trap the ions). These barriers prevent ions of differing voltage gradients from equilibrating with one another.

Owner:MDS CO LTD +2

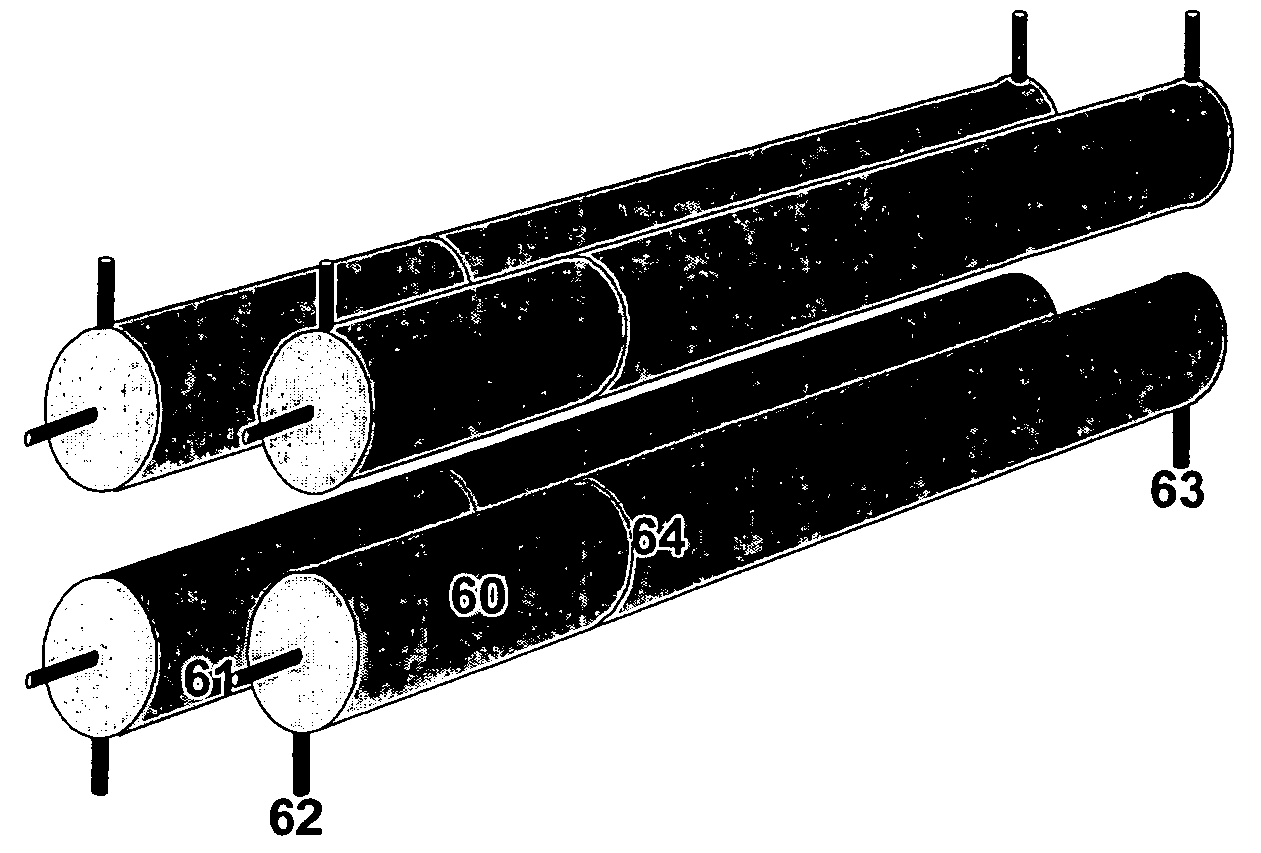

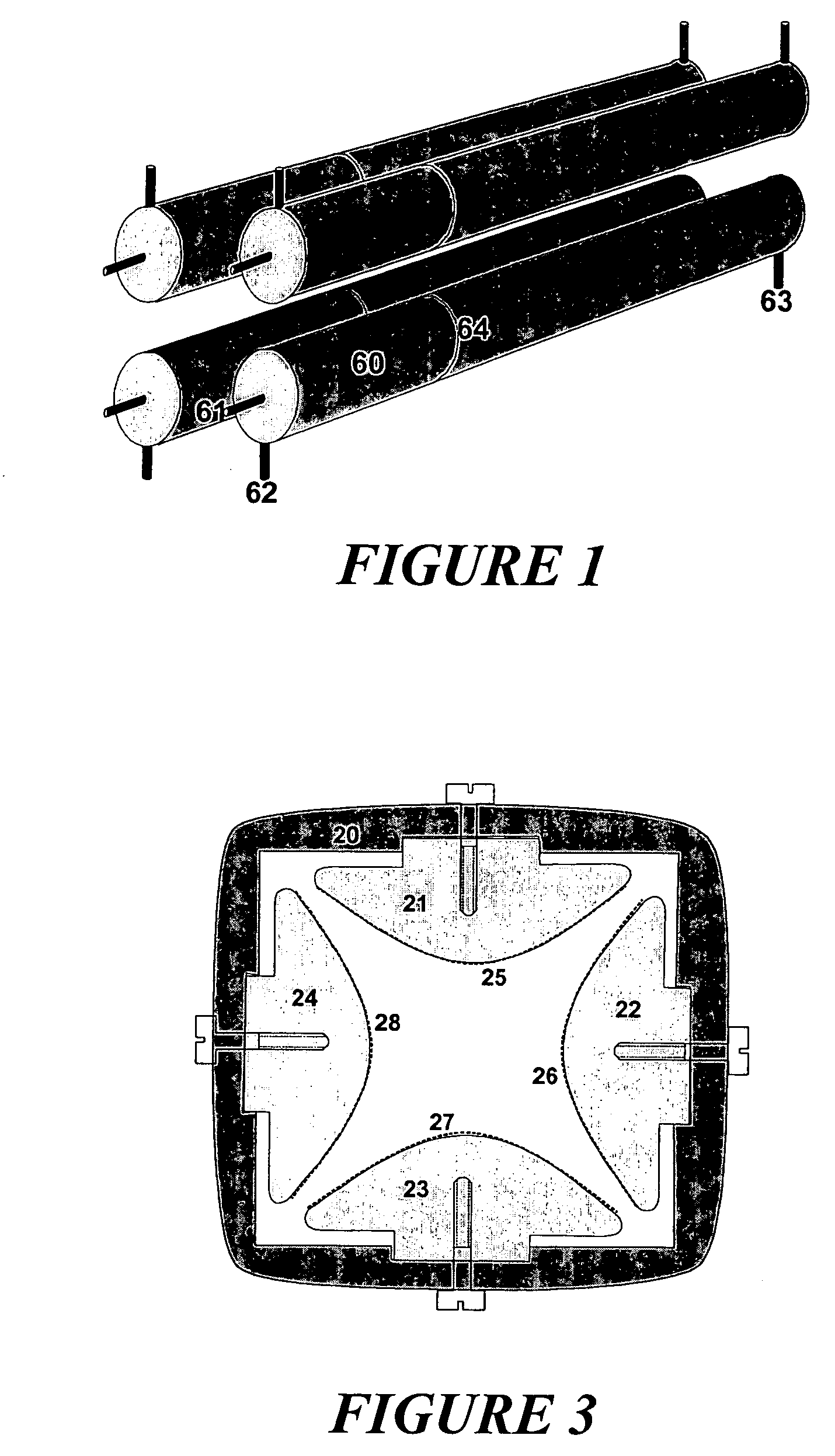

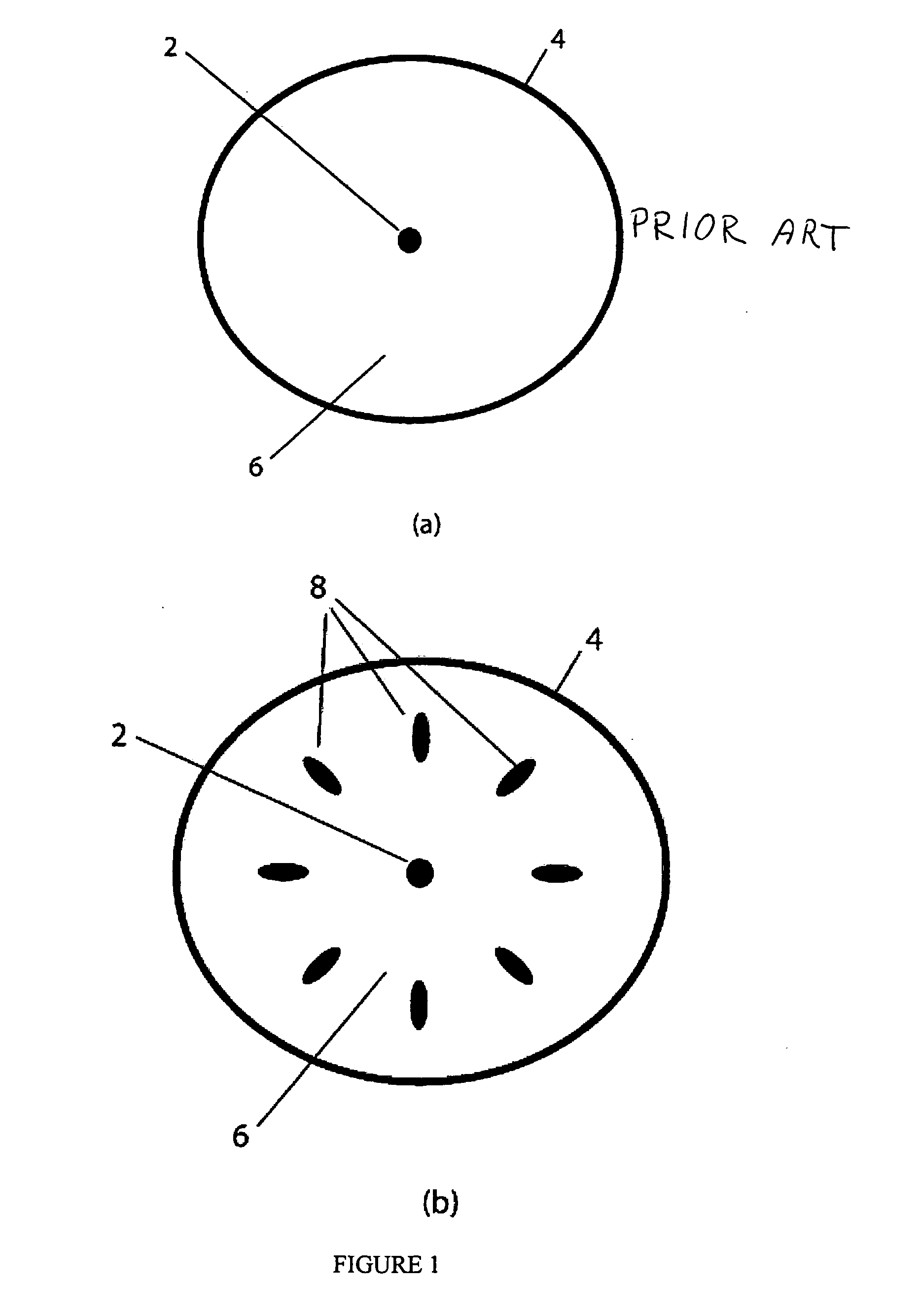

Generation of combination of RF and axial DC electric fields in an RF-only multipole

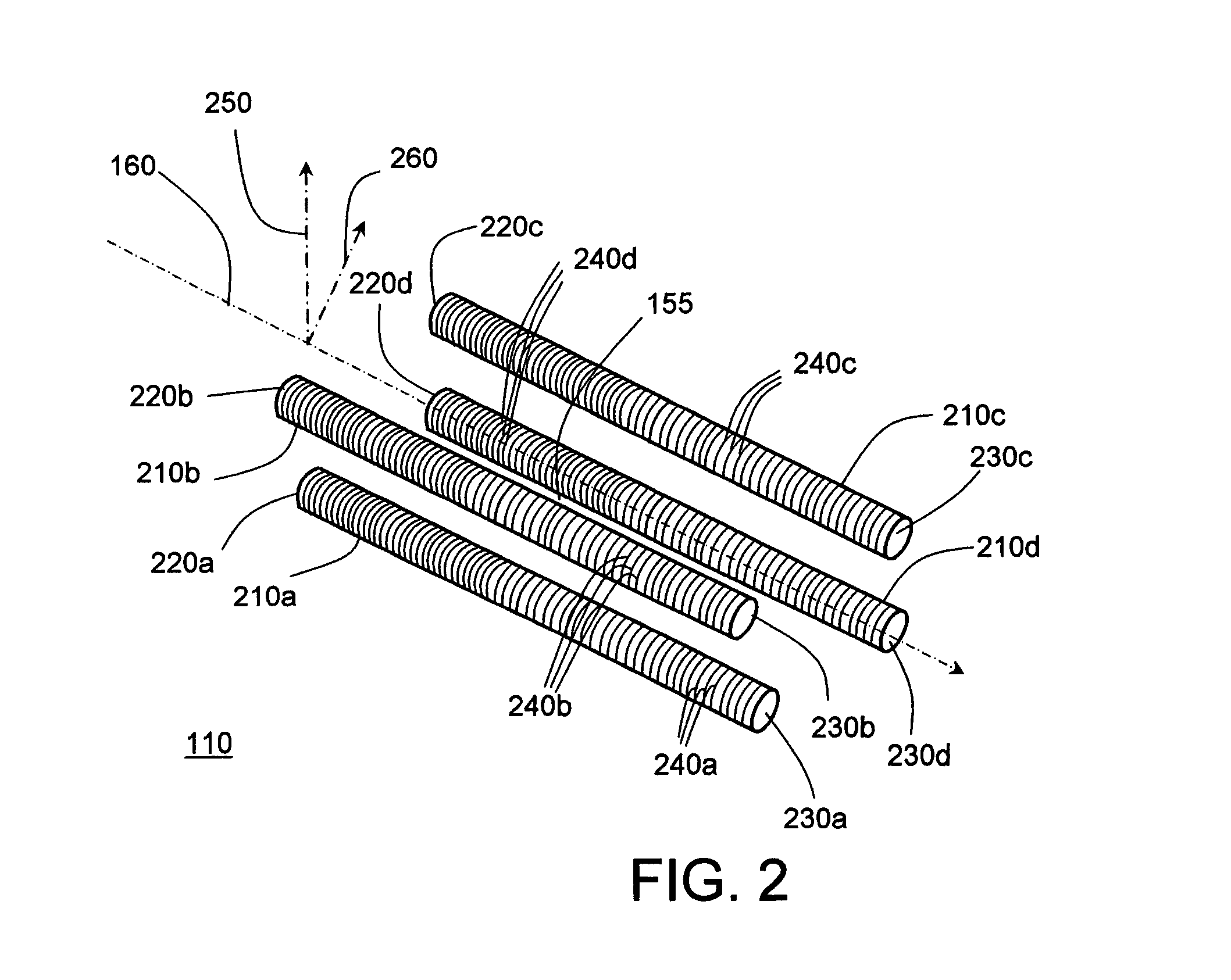

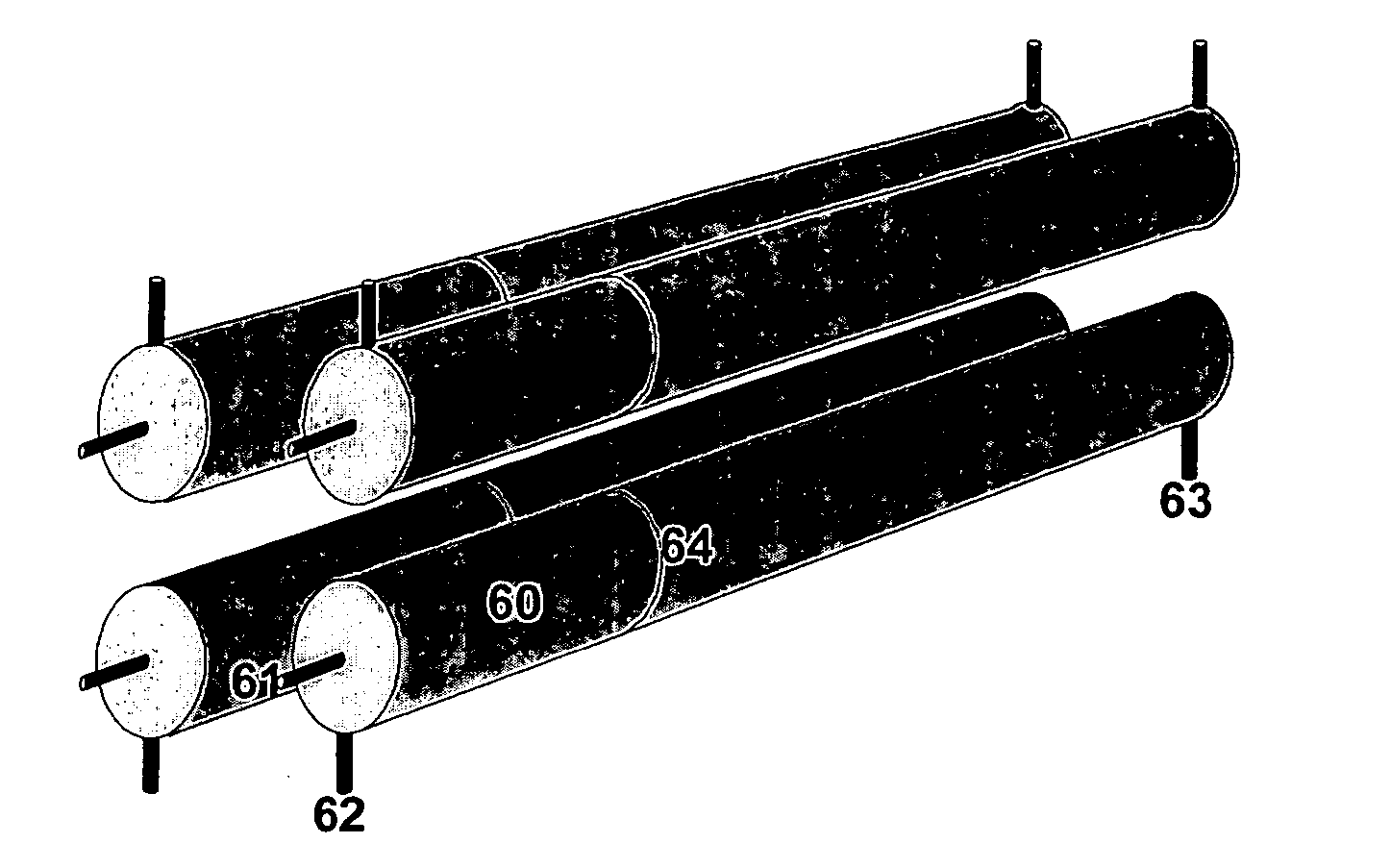

InactiveUS7067802B1Reduce usageParticle separator tubesIsotope separationRf fieldElectrical resistance and conductance

An RF-only multipole includes a spiral resistive path formed around each multipole rod body. RF voltages are applied to the rod body and resistive path, and DC voltages are applied to the resistive path, to create a radially confining RF field and an axial DC field that assists in propelling ions through the multipole interior along the longitudinal axis thereof. In one implementation, the resistive path takes the form of a wire of resistive material, such as nichrome, which is laid down in the groove defined between threads formed on the rod body. The RF-only multipole of the invention avoids the need to use auxiliary rods or similar supplemental structures to generate the axial DC field.

Owner:THERMO FINNIGAN

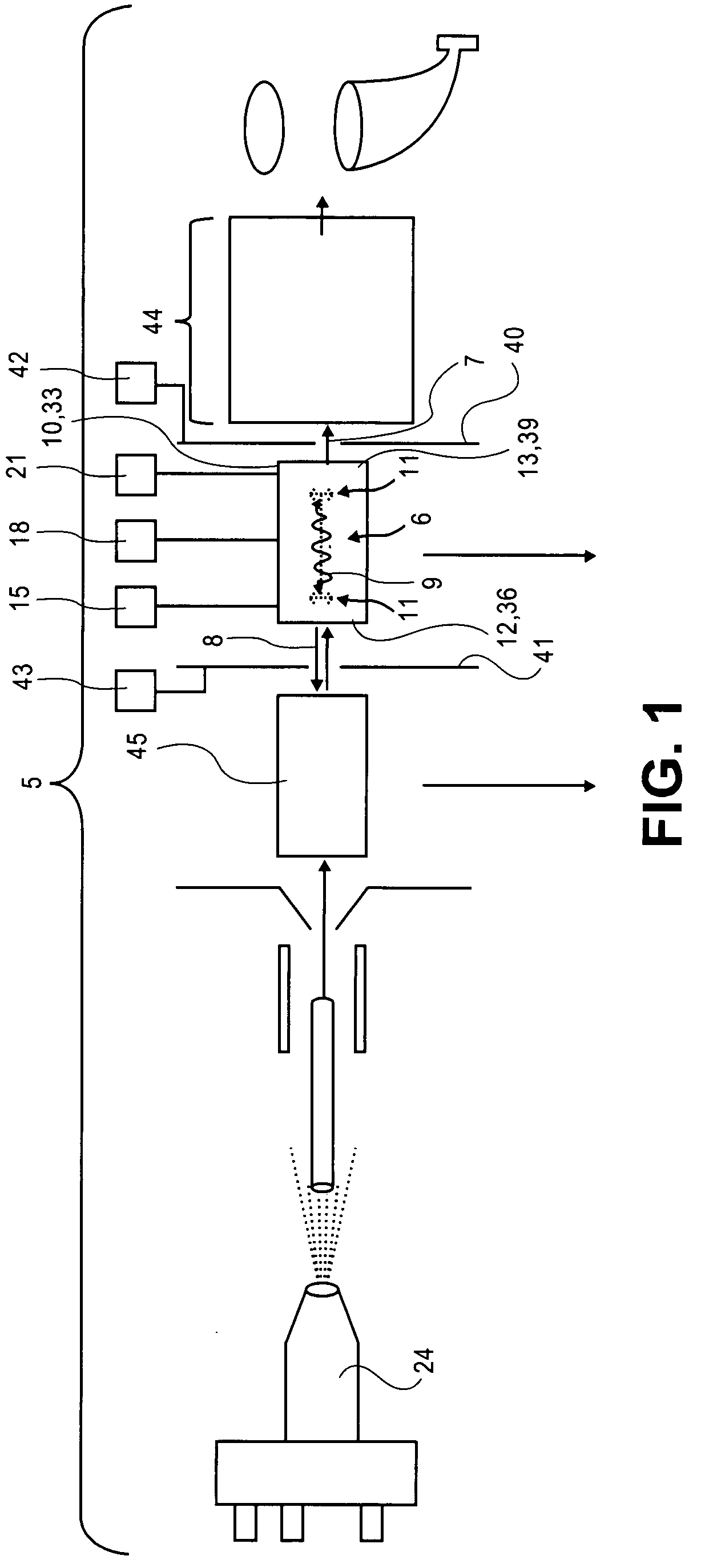

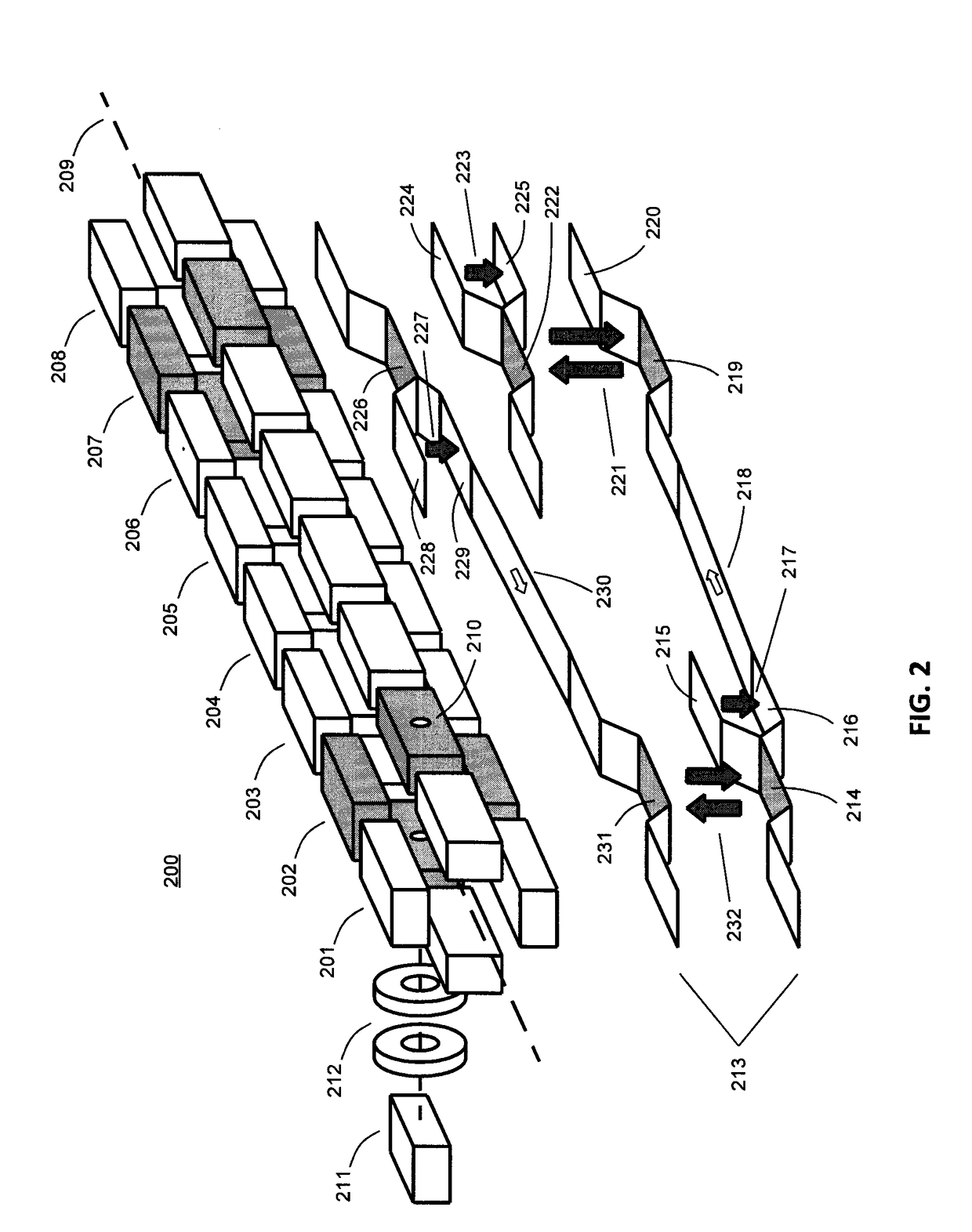

Tandem time of flight mass spectrometer and method of use

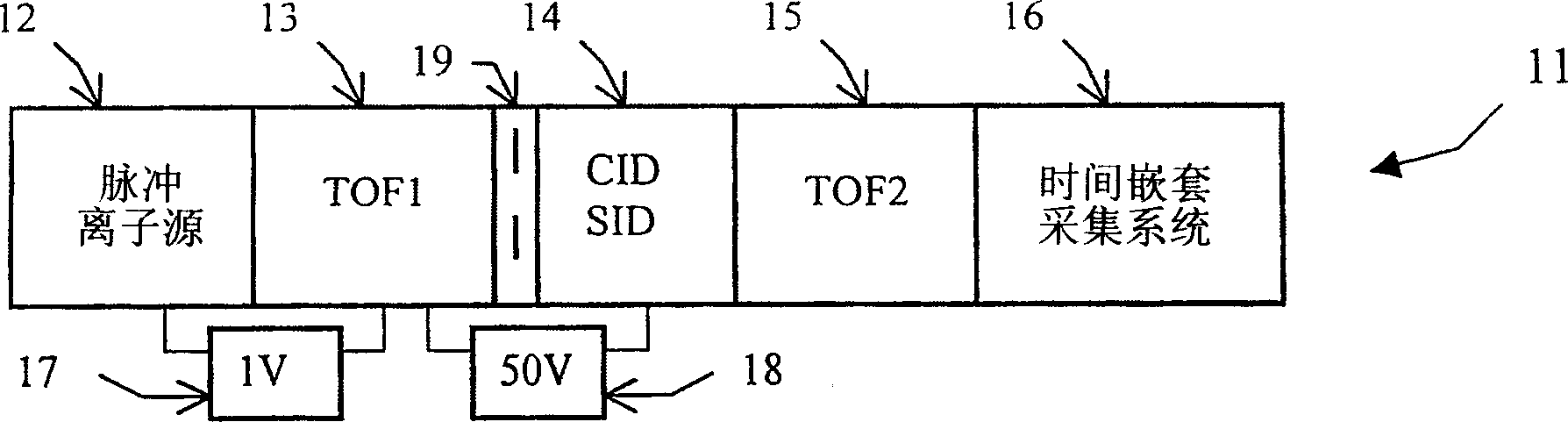

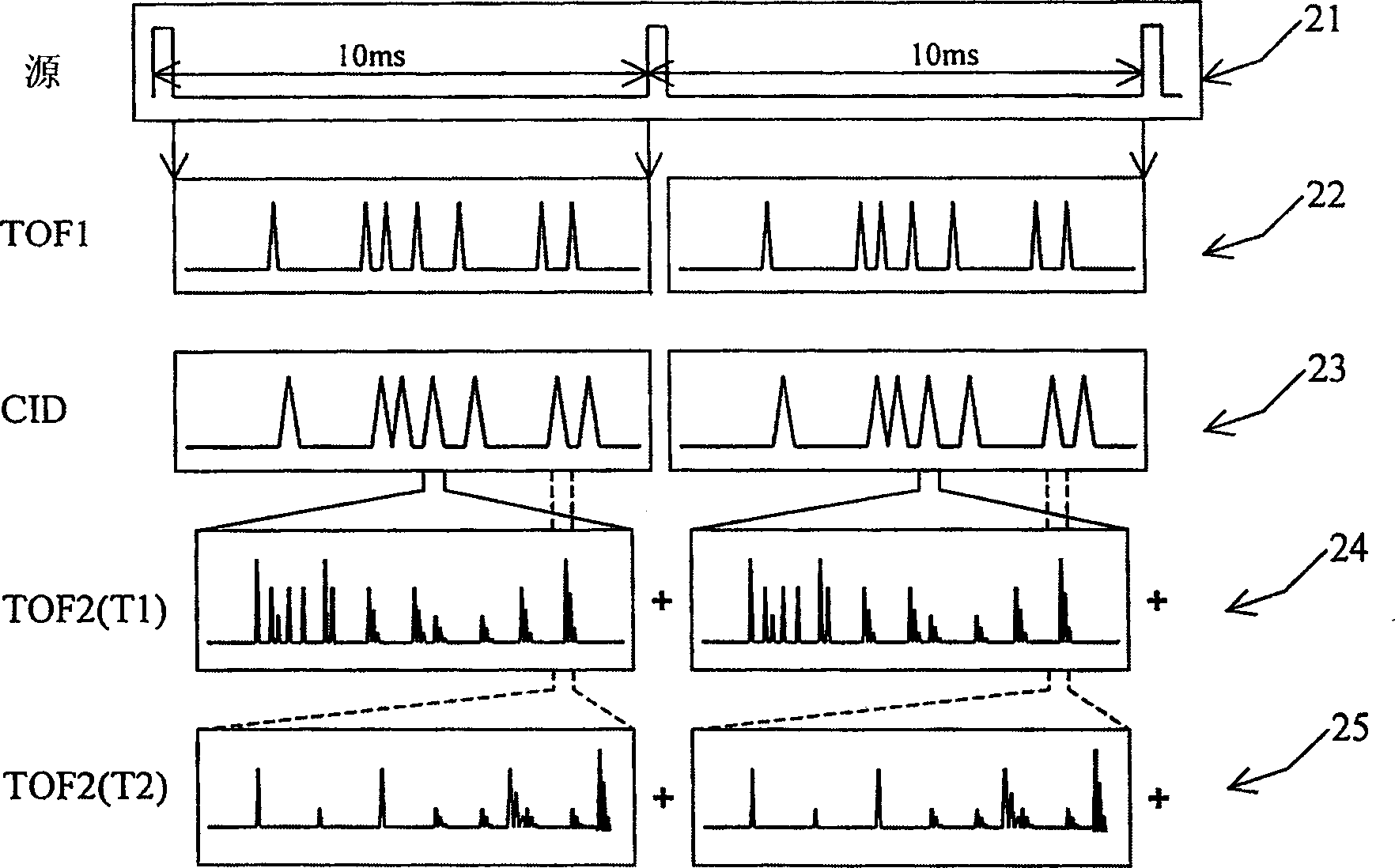

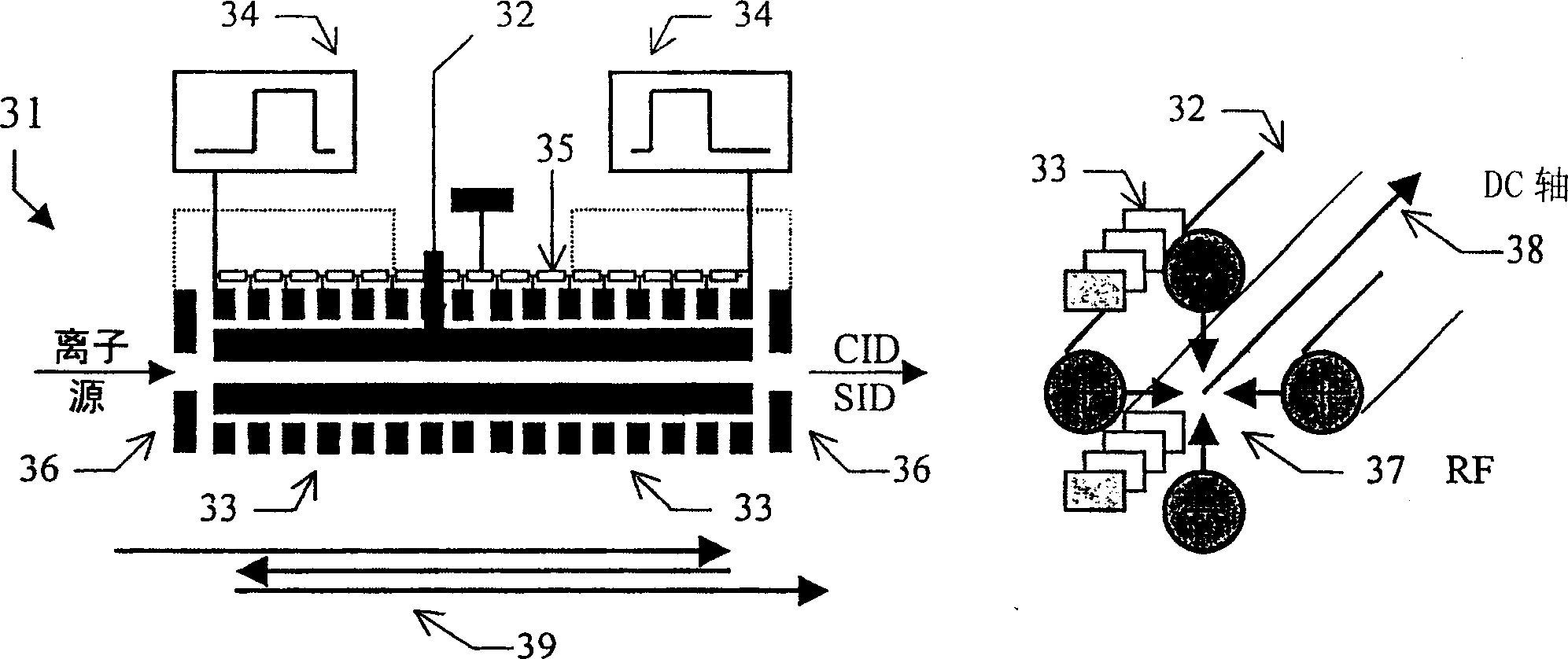

InactiveCN1689134AAcquisition speed is fastHigh sensitivityTime-of-flight spectrometersElectron/ion optical arrangementsRelative energyMass analyzer

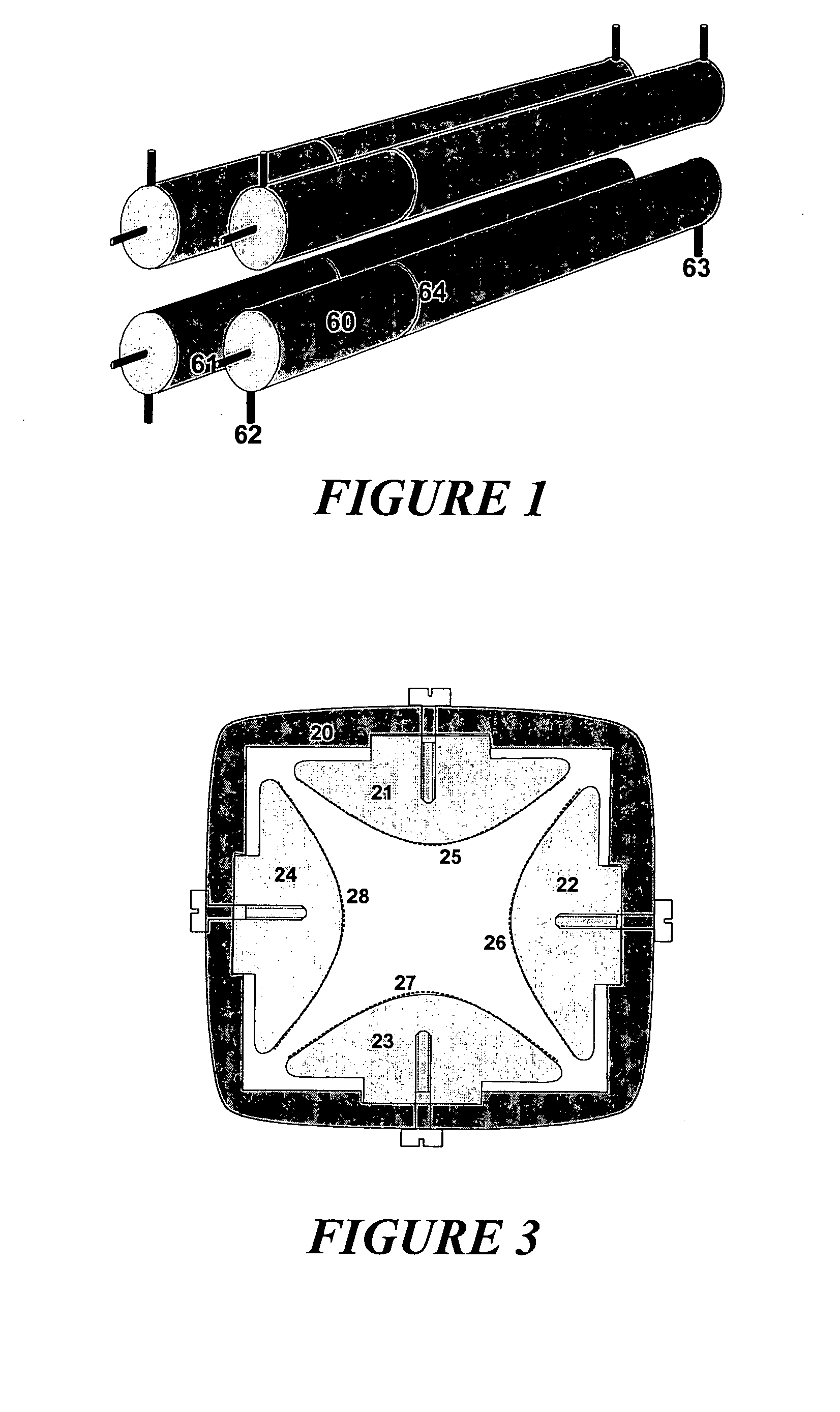

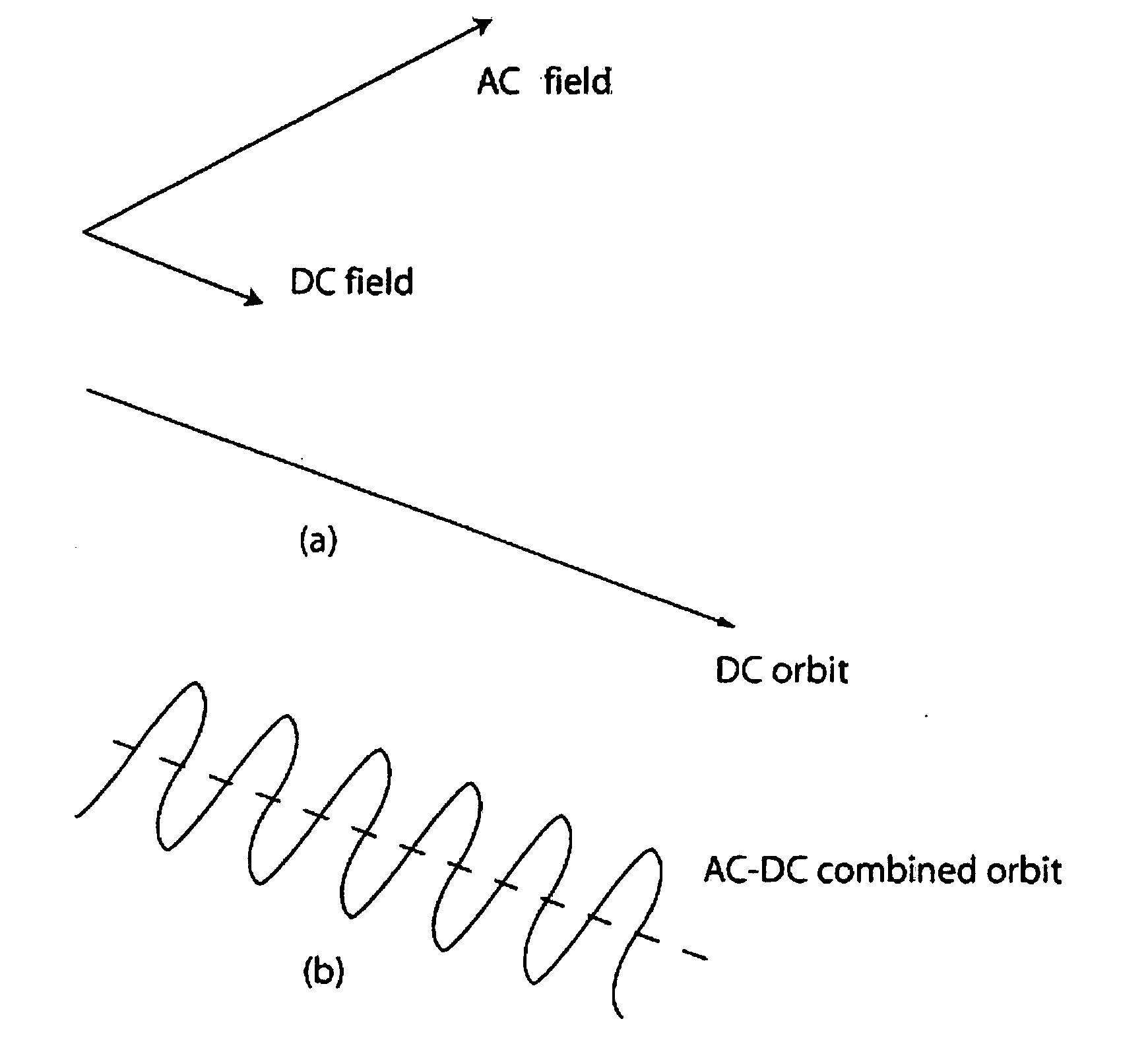

To provide comprehensive (i.e. rapid and sensitive) MS-MS analysis, the inventor employs a time-nested separation, using two time-of-flight (TOF) mass spectrometers. Parent ions are separated in a slow and long TOF1, operating at low ion energy (1 to l00eV), and fragment ions are mass analyzed in a fast and short TOF2, operating at much higher keV energy. Low energy fragmentation cell between TOF1 and TOF2 is tailored to accelerate fragmentation and dampening steps, mostly by shortening the cell and employing higher gas pressure. Since separation in TOF1 takes milliseconds and mass analysis in TOF2- microseconds, the invention provides comprehensive MS-MS analysis of multiple precursor ions per single ion pulse. Slow separation in TOF1 becomes possible with an introduction of novel TOF1 analyzers. The TOF-TOF could be implemented using a static TOF1, here described on the examples of spiratron, planar and cylindrical multi-pass separators with griddles spatial focusing ion mirrors. Higher performance is expected with the use of novel hybrid TOF 1 analyzers, combining radio frequency (RF) and quadratic DC fields. RF field retains low-energy ions within TOF 1 analyzer, while quadratic DC field improves resolution by compensate for large relative energy spread.

Owner:力可公司

Methods and apparatus for reducing artifacts in mass spectrometers

InactiveUS6909089B2Eliminate this undesirable phenomenonExcellent characteristicsStability-of-path spectrometersMaterial analysis by electric/magnetic meansVoltage gradientDc field

The invention solves the problem of artifact ghost peaks which can sometimes arise in mass spectrometers that employ a quadrupole rod set for both trapping and mass analyzing the trapped ions. The problem arises as a result of randomly distributed voltage gradients along the length of the rods. Three solutions are presented. The first approach involves improving the conduction characteristics of the rod sets. The second approach involves the application of at least one continuous axial DC field to the trapping quadrupole rod set in order to urge ions towards a pre-determined region of the trap, thereby avoiding voltage gradients. The third approach involves the application of one or more discrete axial fields to create one or more potential barriers along the axial dimension of the trap (in addition to the barriers used to initially trap the ions). These barriers prevent ions of differing voltage gradients from equilibrating with one another.

Owner:MDS CO LTD +2

RF quadrupole systems with potential gradients

ActiveUS7164125B2Prevent escapeAvoid hard collisionStability-of-path spectrometersRadiation/particle handlingTransmittanceEngineering

The invention relates to two-dimensional quadrupole systems along whose axis an axial DC field is superimposed. The invention involves coating the hyperbolic or cylindrical surfaces of quadrupole systems with thin insulating layers and metal films thereupon and generating axial potential gradients or saddle ramps using appropriate electrical supply of DC potentials and superimposed RF voltages to the metal films. Systems of this type can be used in a plurality of ways, ranging from mass filters with high transmission to fragmentation cells with extremely low ion losses.

Owner:BRUKER DALTONIK GMBH & CO KG

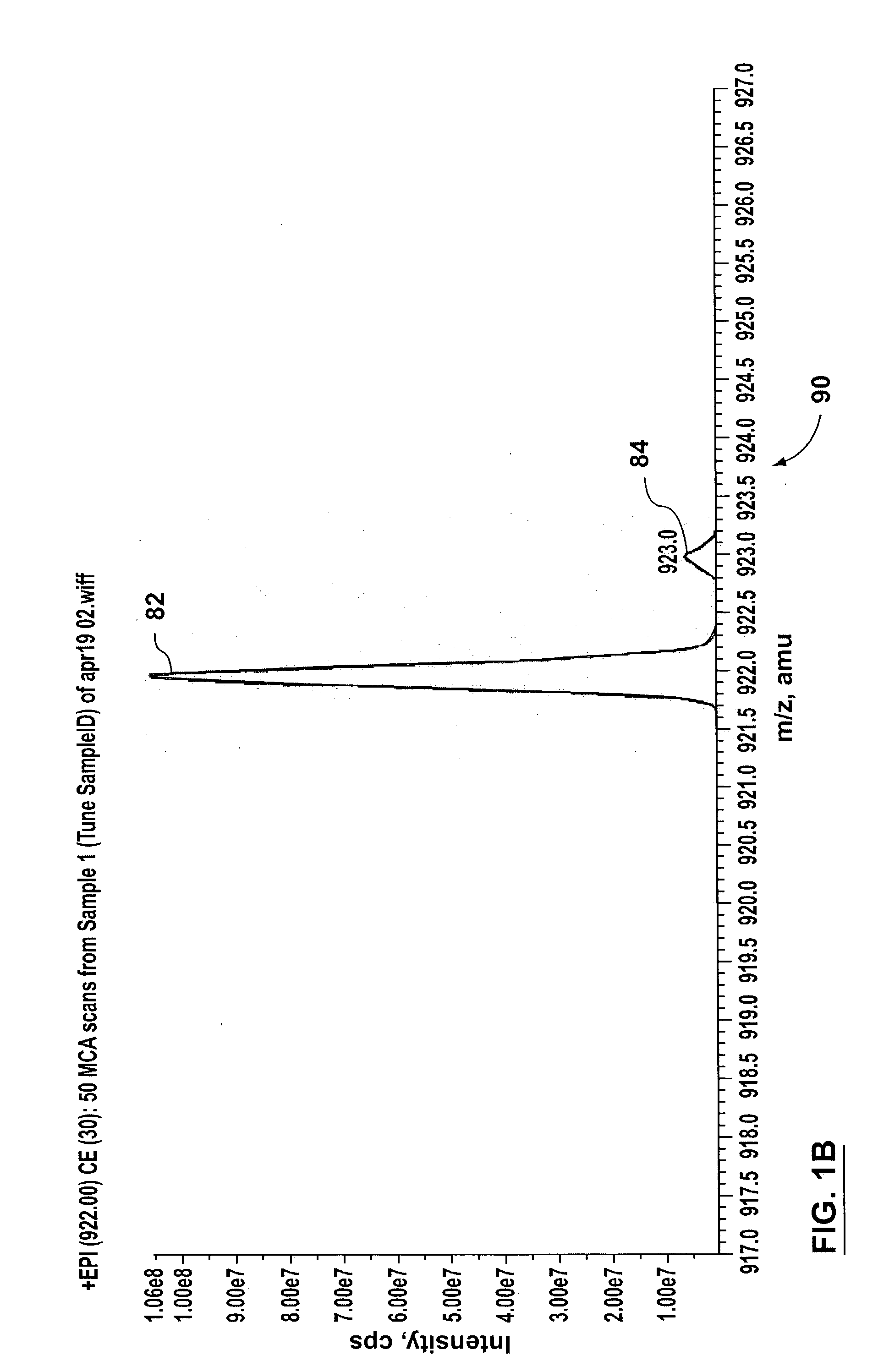

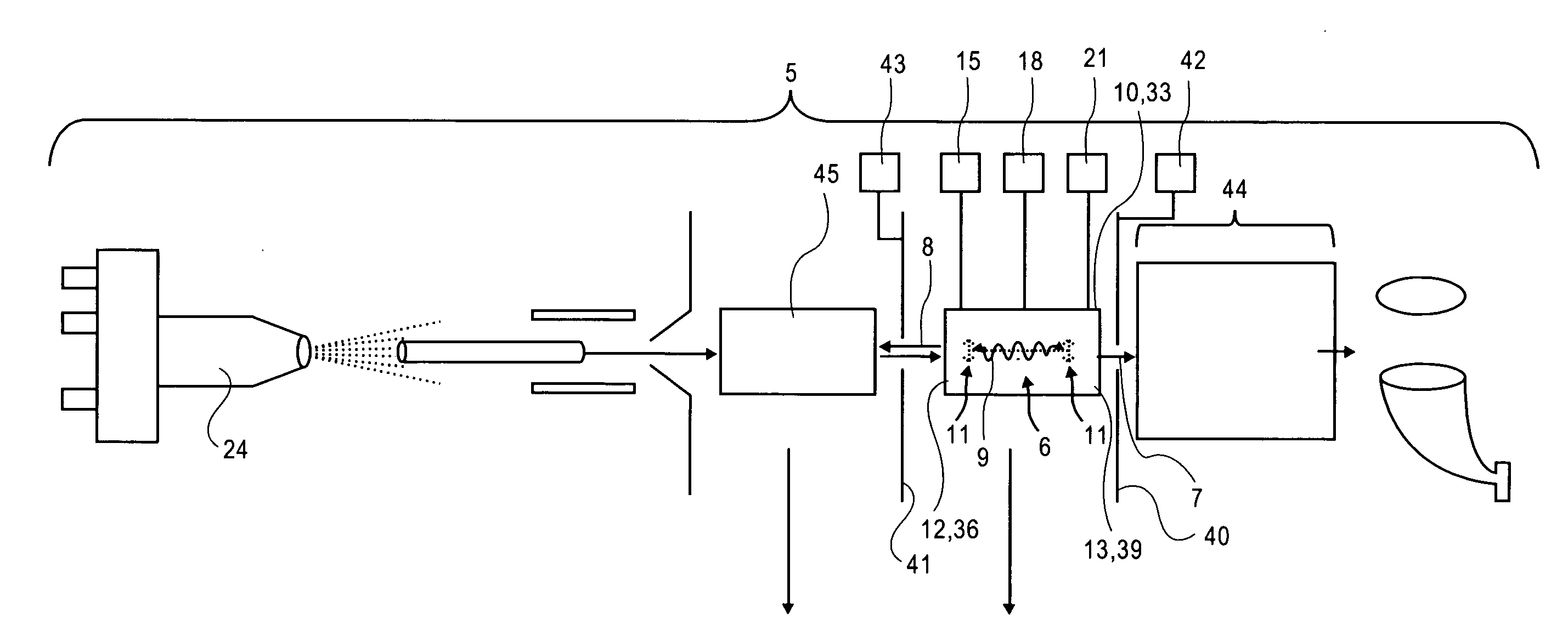

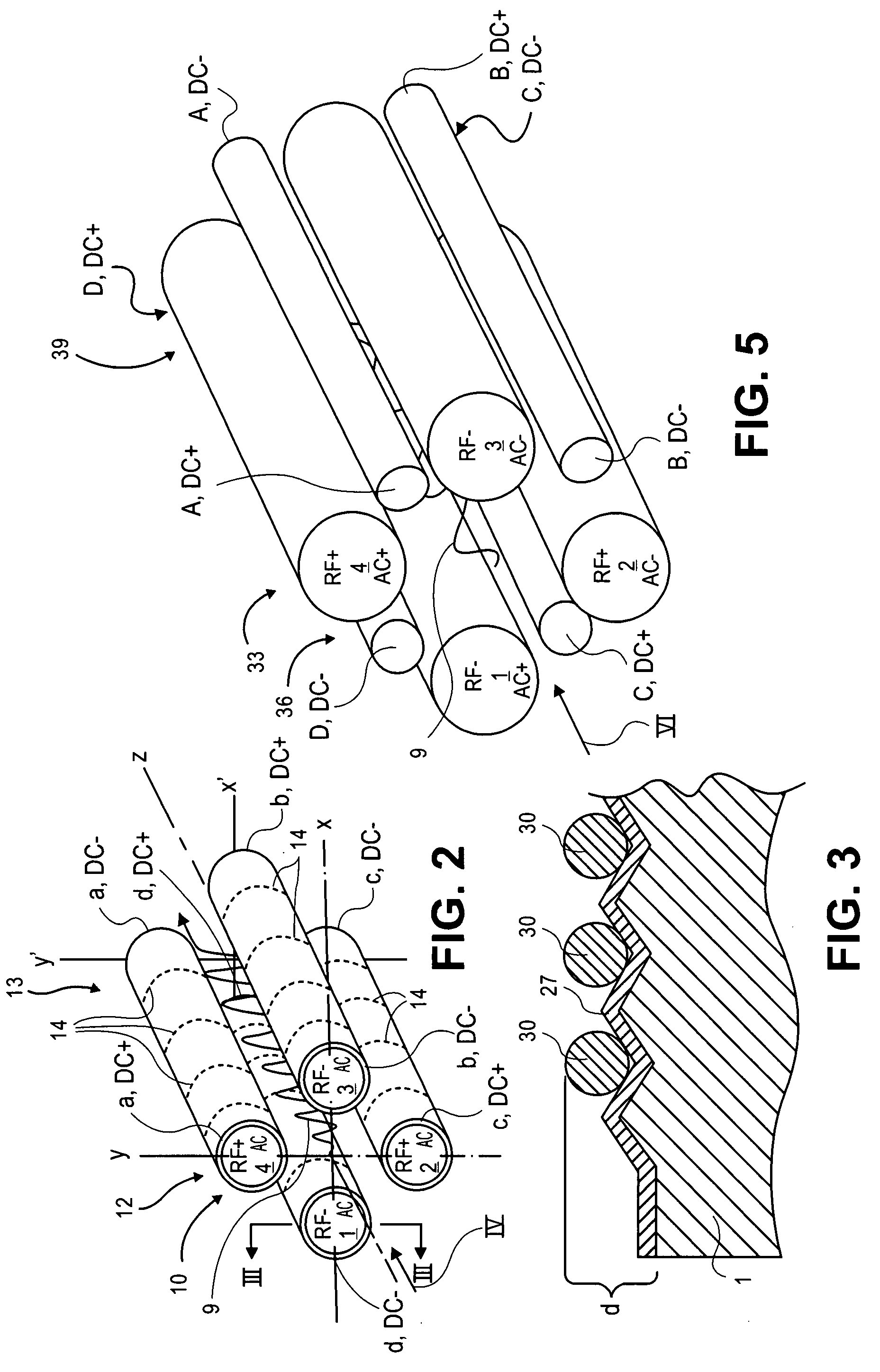

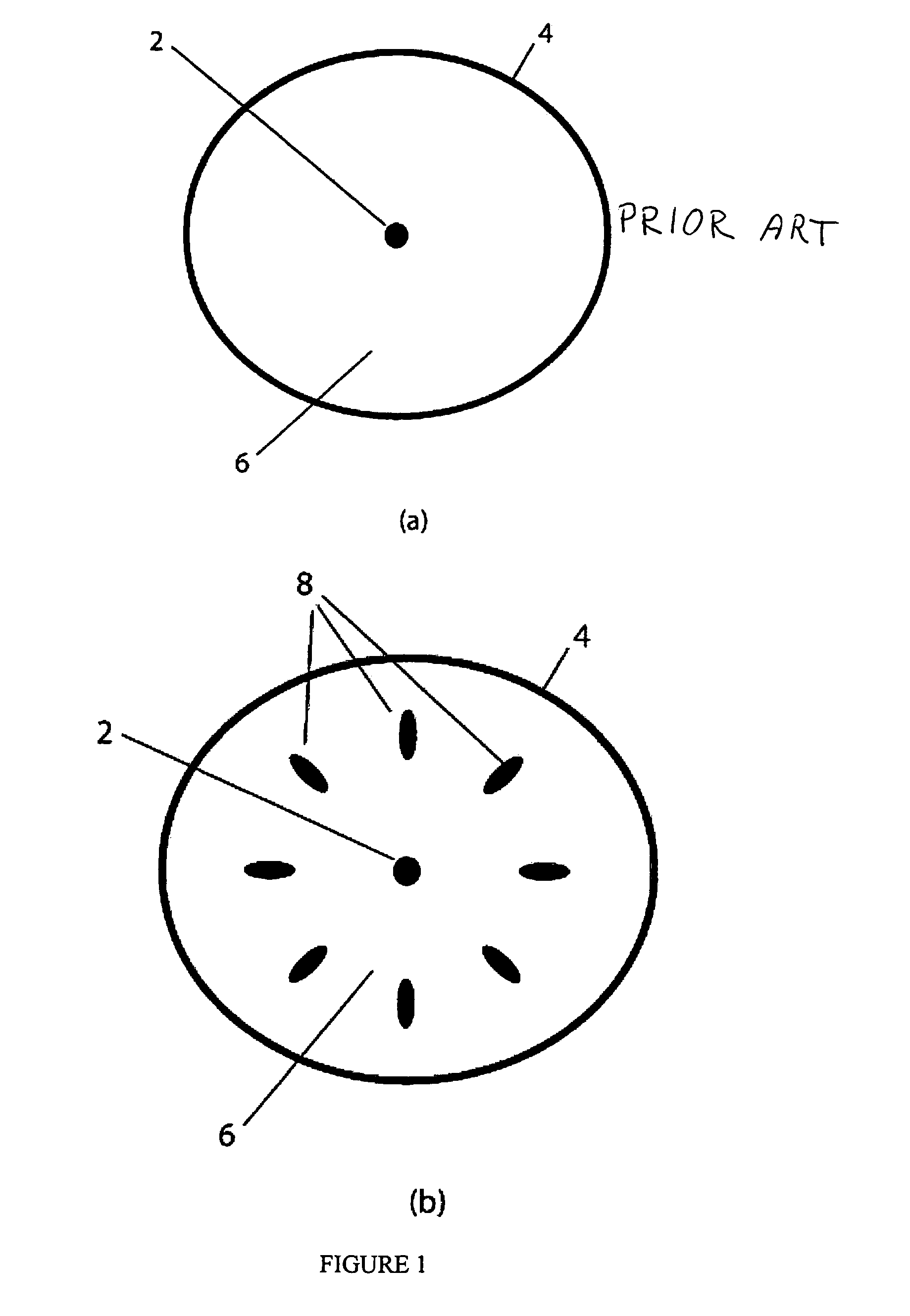

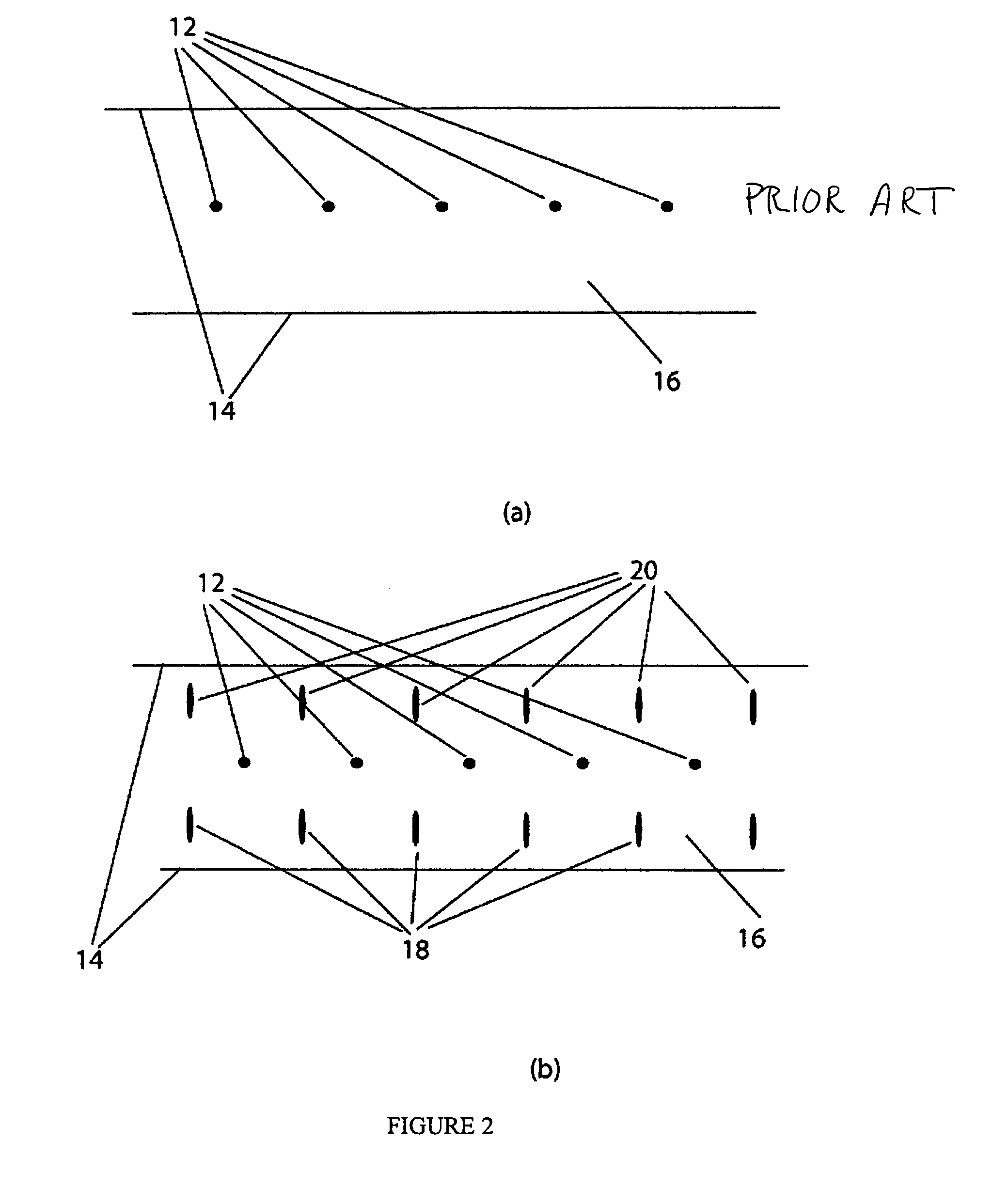

Separation and axial ejection of ions based on m/z ratio

ActiveUS20080265155A1High ion selectivityIncreased ion storage capacityParticle separator tubesIsotope separationDc fieldSpectrometer

A mass spectrometer includes a multipole having a main RF field for radially containing ions generally on a central axis. The multipole has first and second axial DC fields in opposite first and second direction along a length of the multipole. The first and second axial DC fields approach or add substantially to zero on the central axis. The multipole has an excitation voltage applied thereto for selectively exciting the ions of desired m / z ratios off the central axis. The excitation voltage thus causes excursion of the ions into a region where either the first or second axial DC field is strong. Thus, excitation of the ions and the DC fields cause ion drift toward a front end or a back end of the multipole. Further excitation moves the ions into regions of the DC fields that overcome barriers and causes axial ejection of the ions from the multipole.

Owner:THERMO FINNIGAN

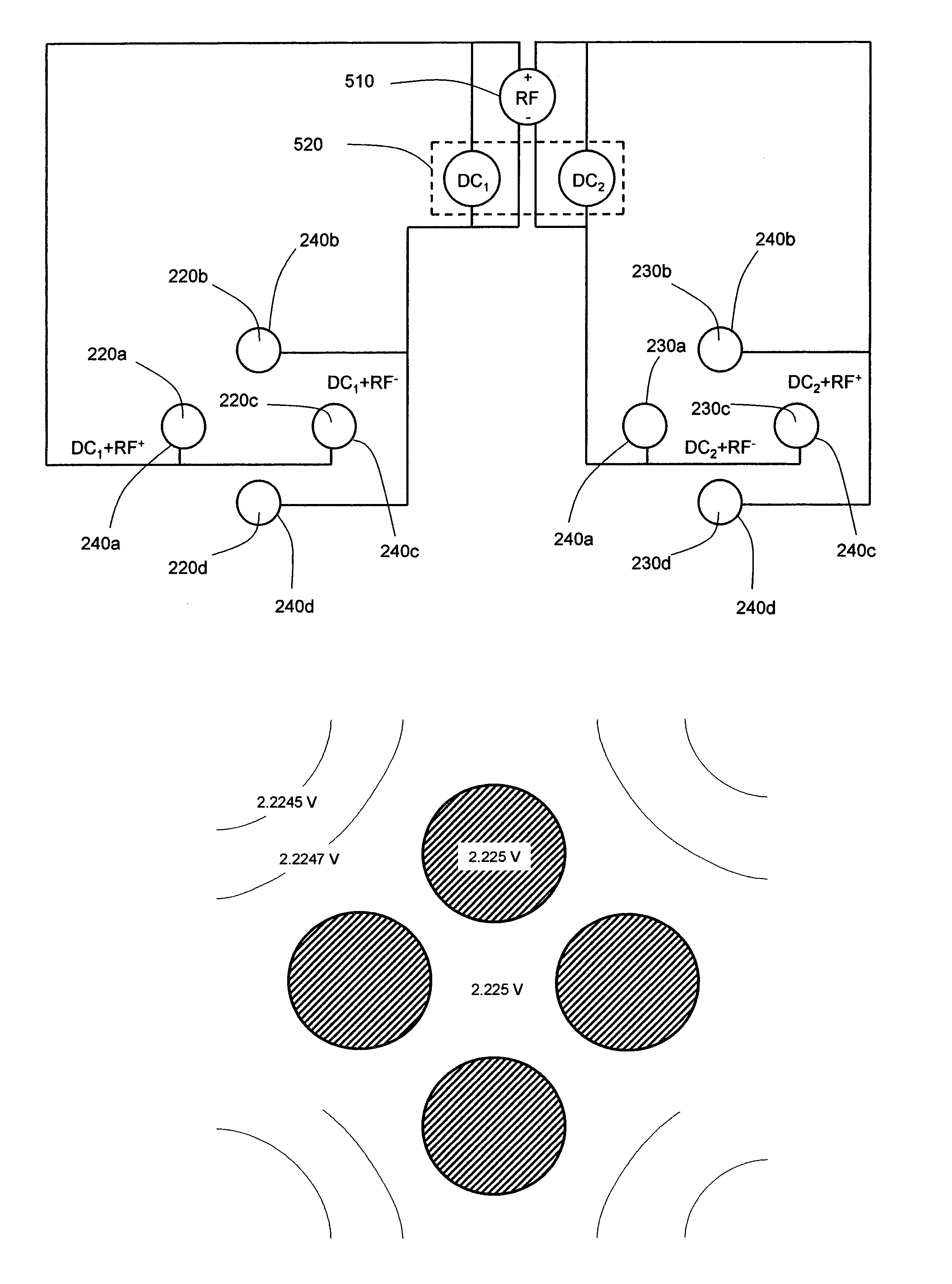

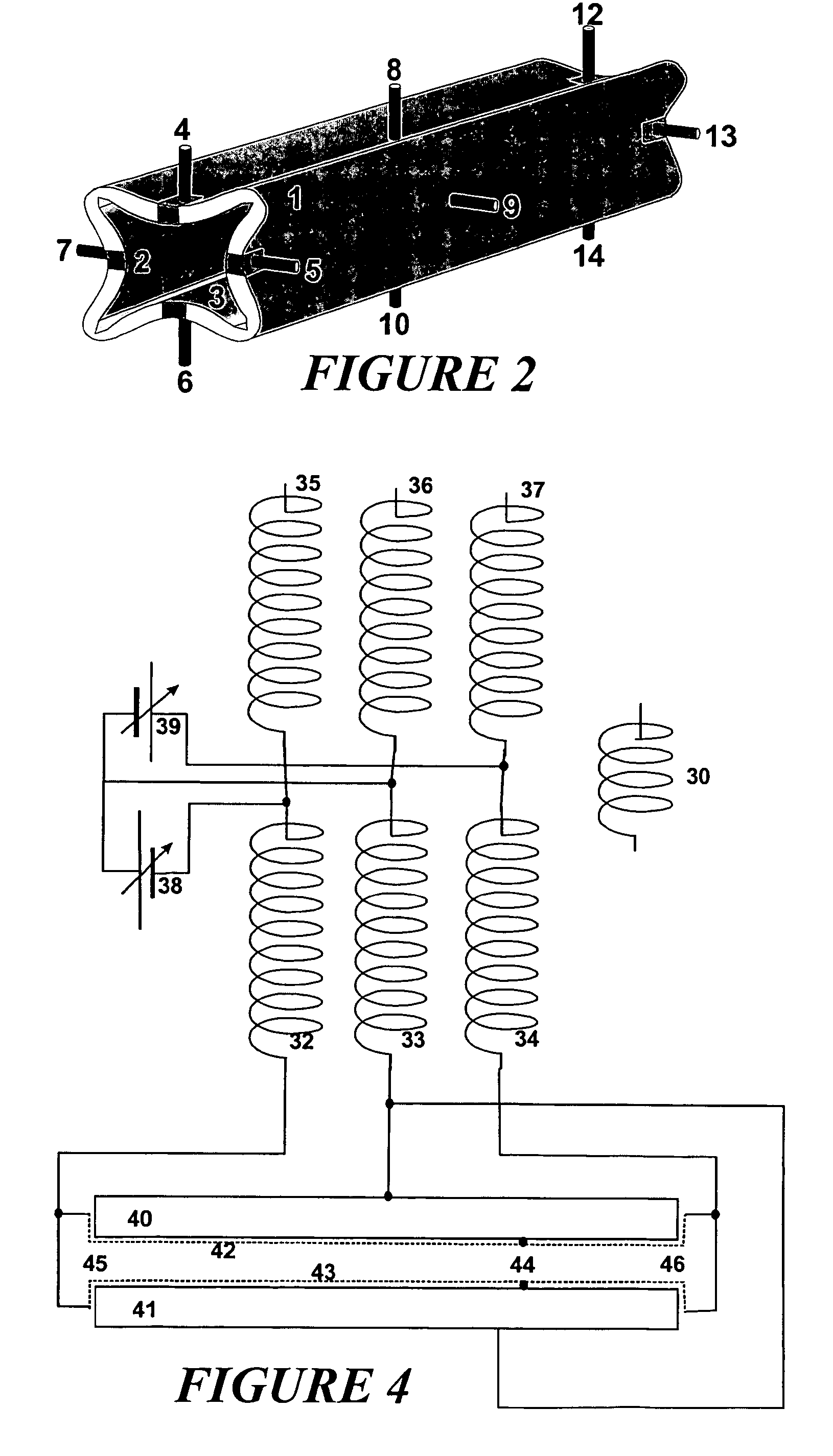

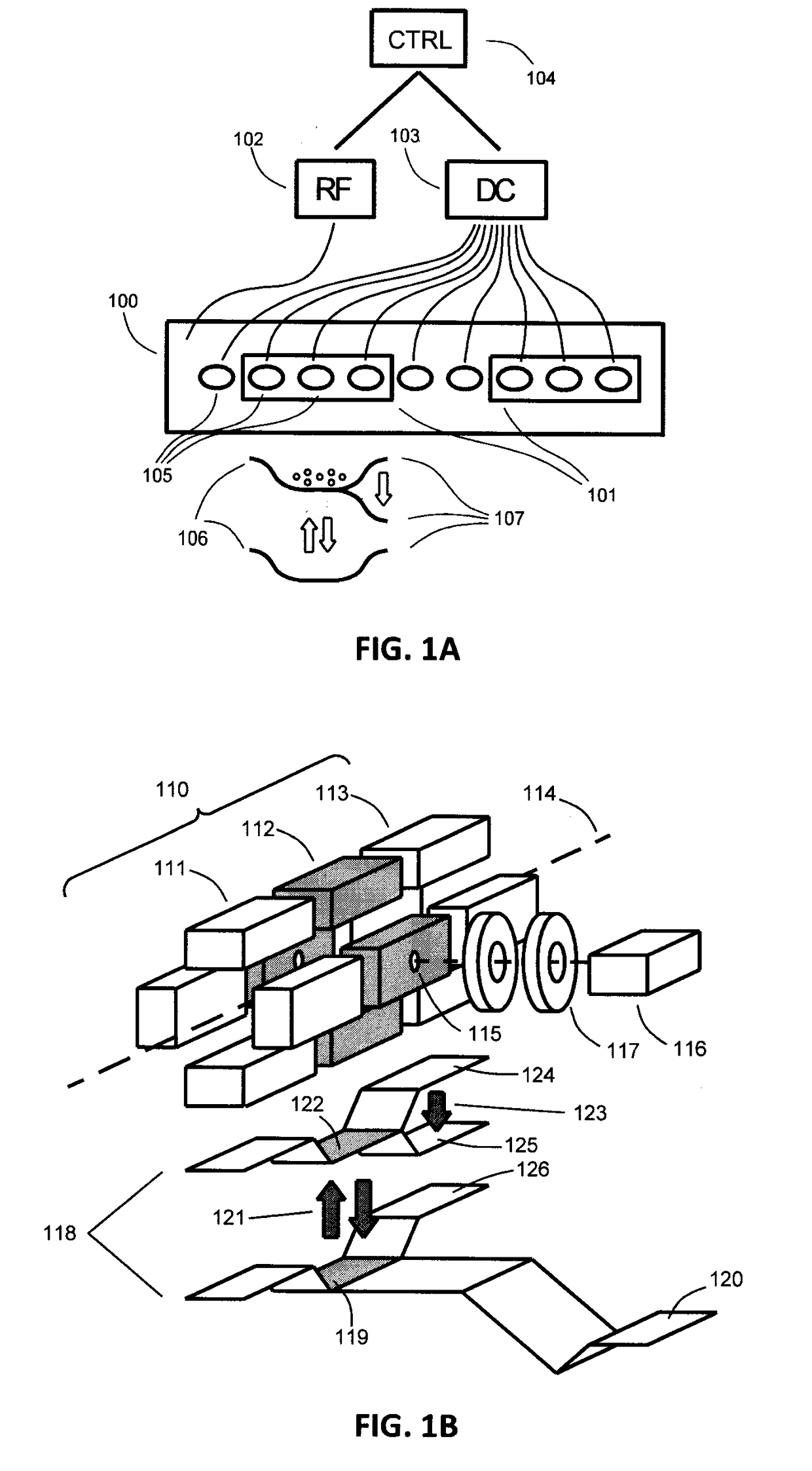

Segmented linear ion trap for enhanced ion activation and storage

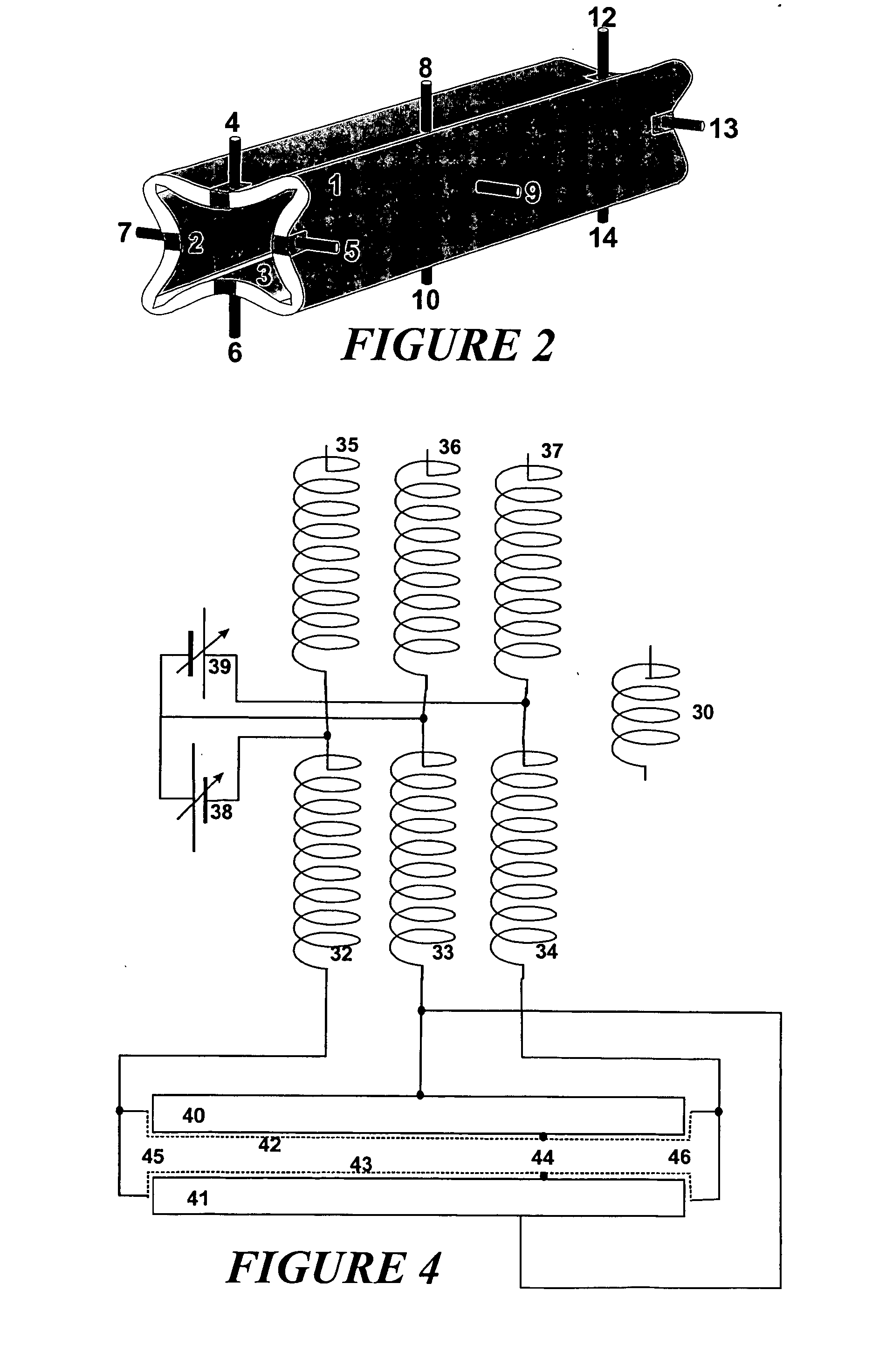

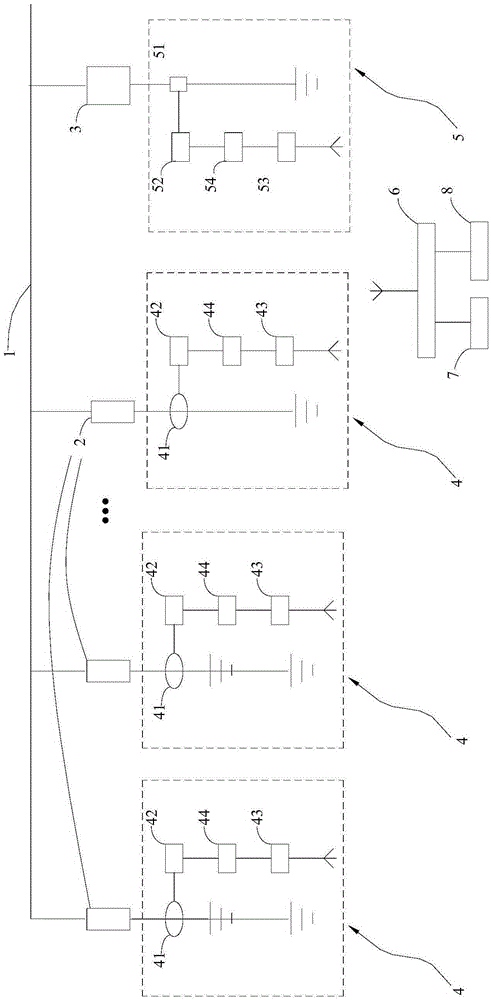

ActiveUS20170221694A1Enhance collision induced dissociationExtended durationStability-of-path spectrometersMaterial analysis by electric/magnetic meansRf fieldIon trap mass spectrometry

A linear ion trap includes at least two discrete trapping regions for processing ions, a RF electrical potential generator, a multi-output DC electrical potential generator, and a control unit. The RF electrical potential generator produces two RF waveforms each applied to a pair of pole electrodes of the linear ion trap forming a RF trapping field component to trap ions radially. The multi-output DC electrical potential generator produces multiple DC field components superimposed to the RF field component and distributed across the length of the linear ion trap to control ions axially. The control unit switches the DC electrical potentials and corresponding DC field components collectively forming a first trapping region populated with ions to alter ion potential energy from a first level to a second level, and enables a first ion processing step in at least one of the first and second levels.

Owner:FASMATECH SCI & TECH

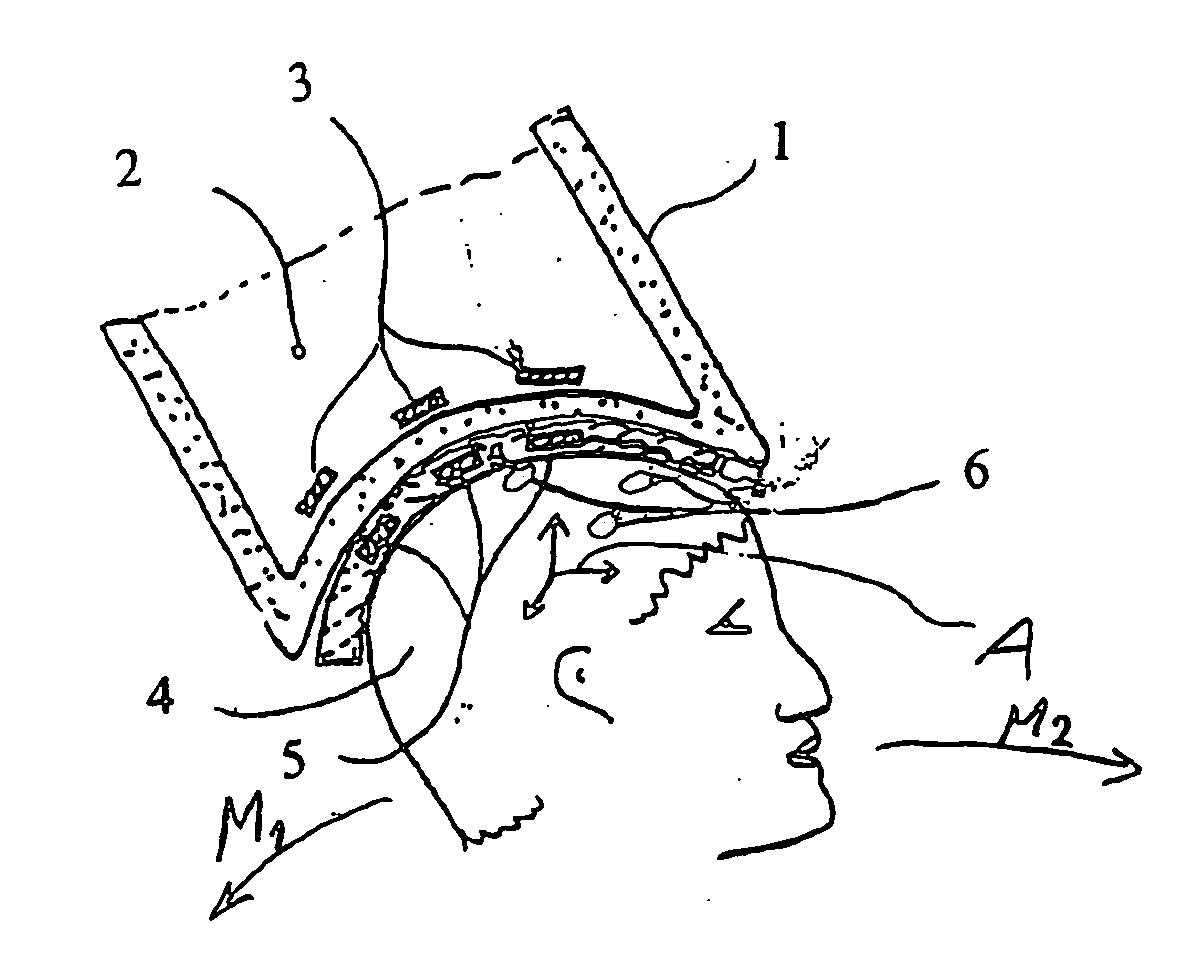

Method of electrodynamics for quick restoring soil polluted by heavy metal in situ

InactiveCN1695835AGood dissolution effectShorten migration distanceContaminated soil reclamationProcess regionSoil heavy metals

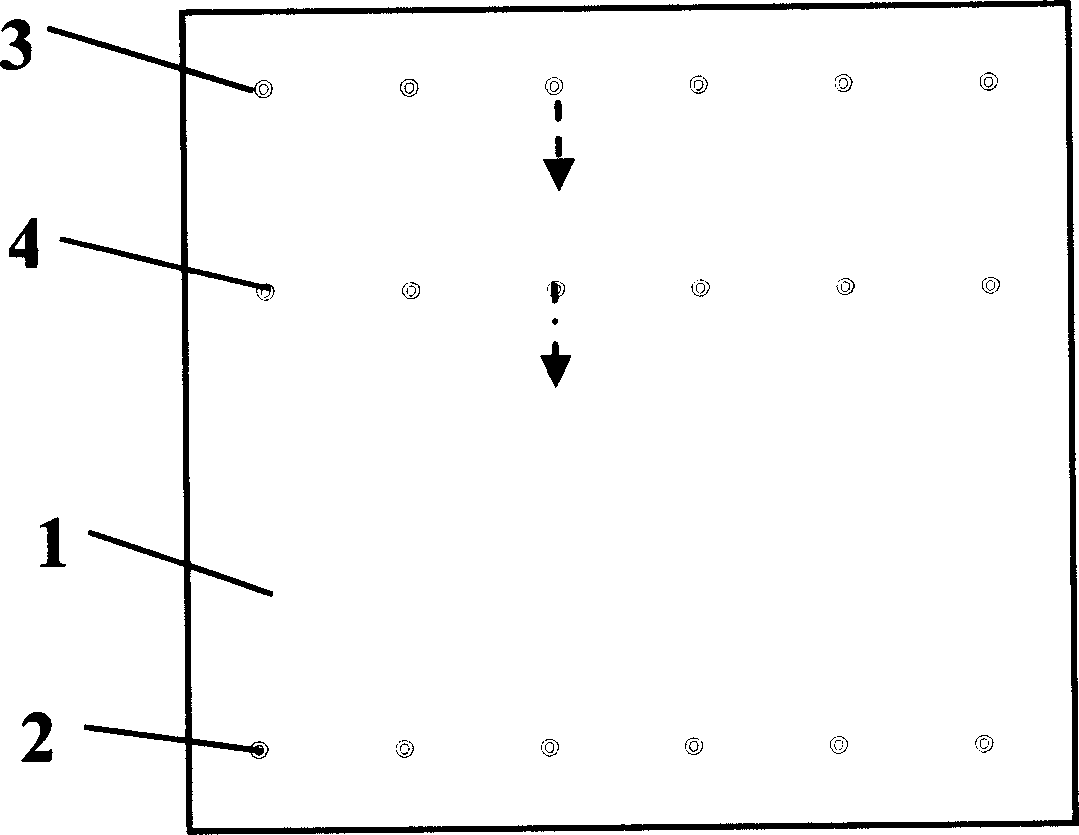

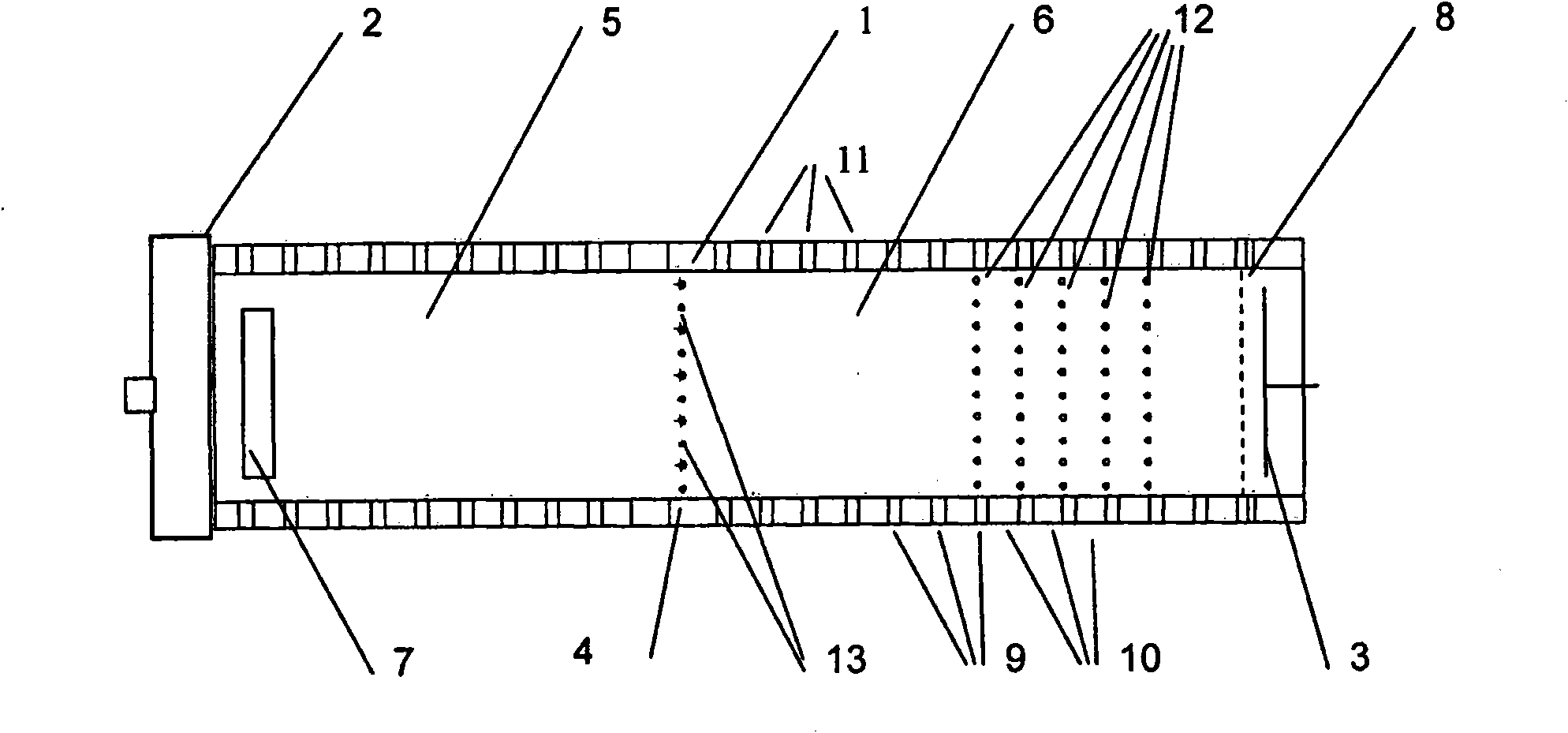

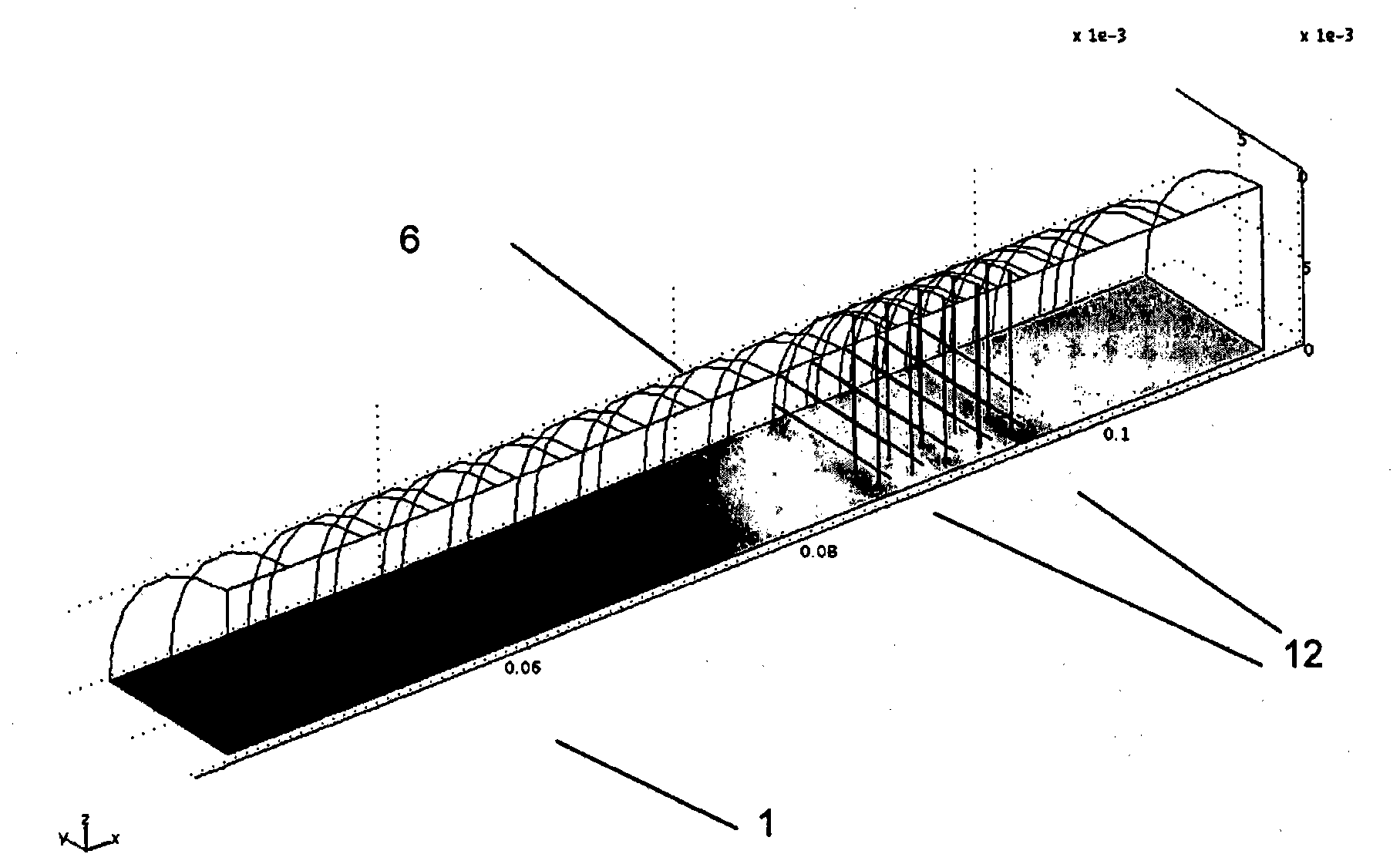

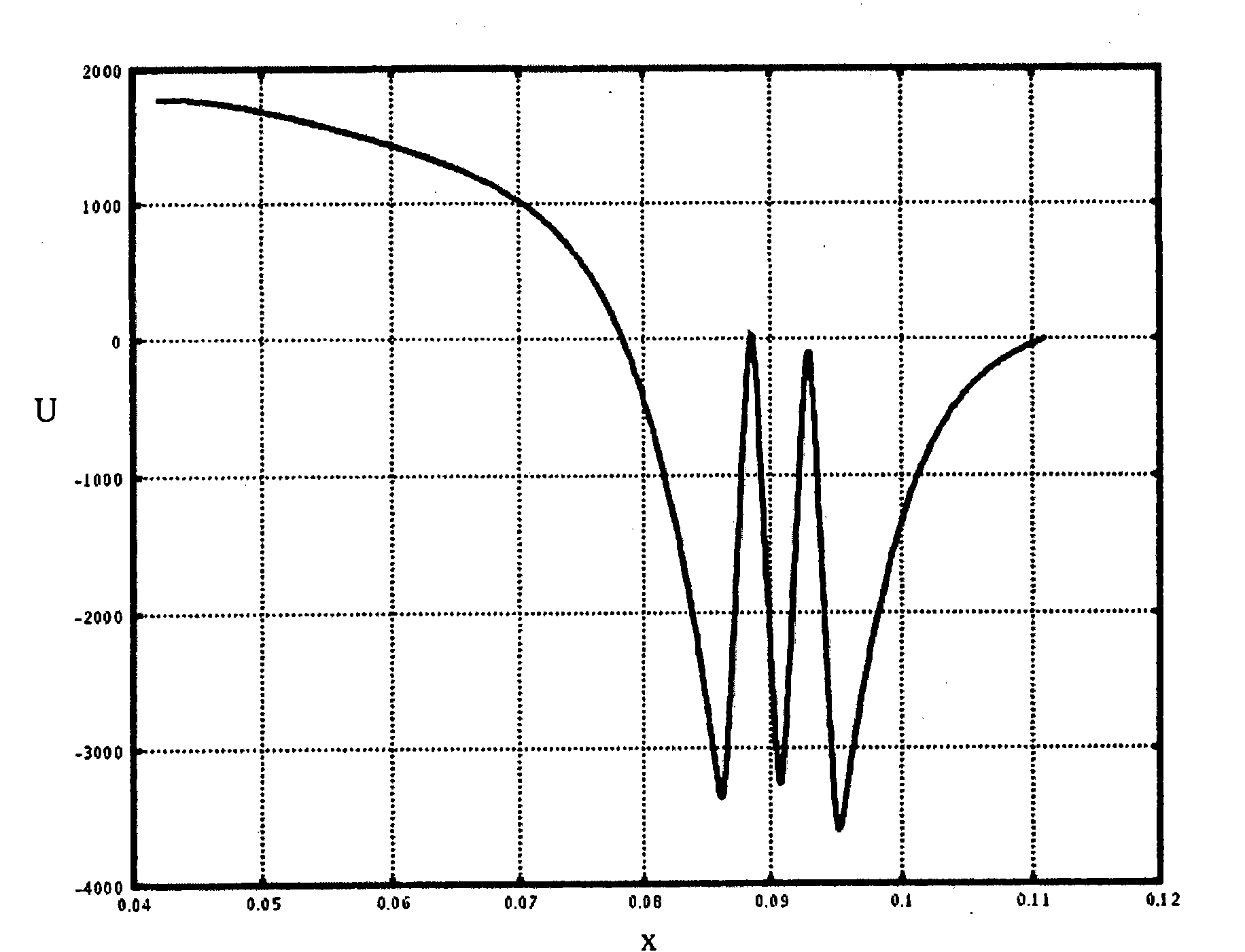

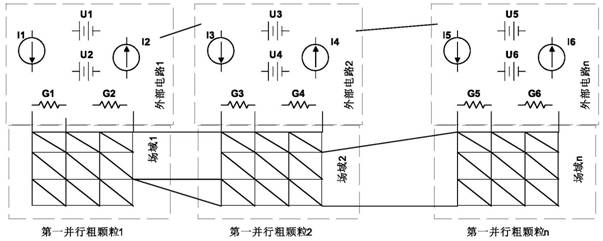

An electrodynamic method for fasthy in-situ repairing the pollated soil includes inserting a collecting electrode at one end of the region to be treated, inserting the working electrode in the region in array mode, and sequentially applying a DC field between the collecting electrode and the working electrodes changed from far end to near end for moving the pollutants, so cleaning the region.

Owner:SHANGHAI JIAO TONG UNIV

RF quadrupole systems with potential gradients

ActiveUS20050274887A1Prevent escapeAvoid hard collisionStability-of-path spectrometersRadiation/particle handlingTransmittanceEngineering

The invention relates to two-dimensional quadrupole systems along whose axis an axial DC field is superimposed. The invention involves coating the hyperbolic or cylindrical surfaces of quadrupole systems with thin insulating layers and metal films thereupon and generating axial potential gradients or saddle ramps using appropriate electrical supply of DC potentials and superimposed RF voltages to the metal films. Systems of this type can be used in a plurality of ways, ranging from mass filters with high transmission to fragmentation cells with extremely low ion losses.

Owner:BRUKER DALTONIK GMBH & CO KG

Converter station DC field neutral bus lightning arrester charged analysis device and method

InactiveCN105388374AFind faults in timeGuaranteed safe operationElectrical testingEnergy absorptionEngineering

The present invention discloses a converter station DC field neutral bus lightning arrester charged analysis device. The device comprises a neutral bus lightning arrester, a DC neutral bus, an energy absorbing checking device, and a current nonuniformity analyzer. The DC neutral bus generates an operation over-voltage signal in DC system debugging. The primary side of the neutral bus lightning arrester is electrically connected to the DC neutral bus, and after the operation over-voltage signal passes by the neutral bus lightning arrester, the grounding side of the neutral bus lightning arrester generates a discharge current signal. The high voltage end of an impact voltage divider is electrically connected to the DC neutral bus, and the measuring end of the impact voltage divider generates a converted impact voltage signal. The device comprises a plurality of current sampling modules, the input ends of the current sampling modules are electrically connected to the grounded circuit of the neutral bus lightning arrester. The input end of a voltage sampling module is electrically connected to the measuring end of the impact voltage divider. The device has the advantage that energy absorption and discharge current unevenness of the lightning arrester can be monitored in real time during debugging and operation.

Owner:EXAMING & EXPERIMENTAL CENT OF ULTRAHIGH VOLTAGE POWER TRANSMISSION COMPANY CHINA SOUTHEN POWER GRID

High performance electrostatic precipitator

ActiveUS20070234905A1Low production of ozoneImprove efficiencyParticle charging/ionising stationsExternal electric electrostatic seperatorParticulatesAc field

Electrostatic system is for optimal charging of aerosols and particulates. In order to improve their collection, the system uses a combination of DC field and AC fields produced by multiple AC electrodes. The system minimizes the size and power consumption of the device, as well as increasing the collection efficiency.

Owner:MASSACHUSETTS INST OF TECH

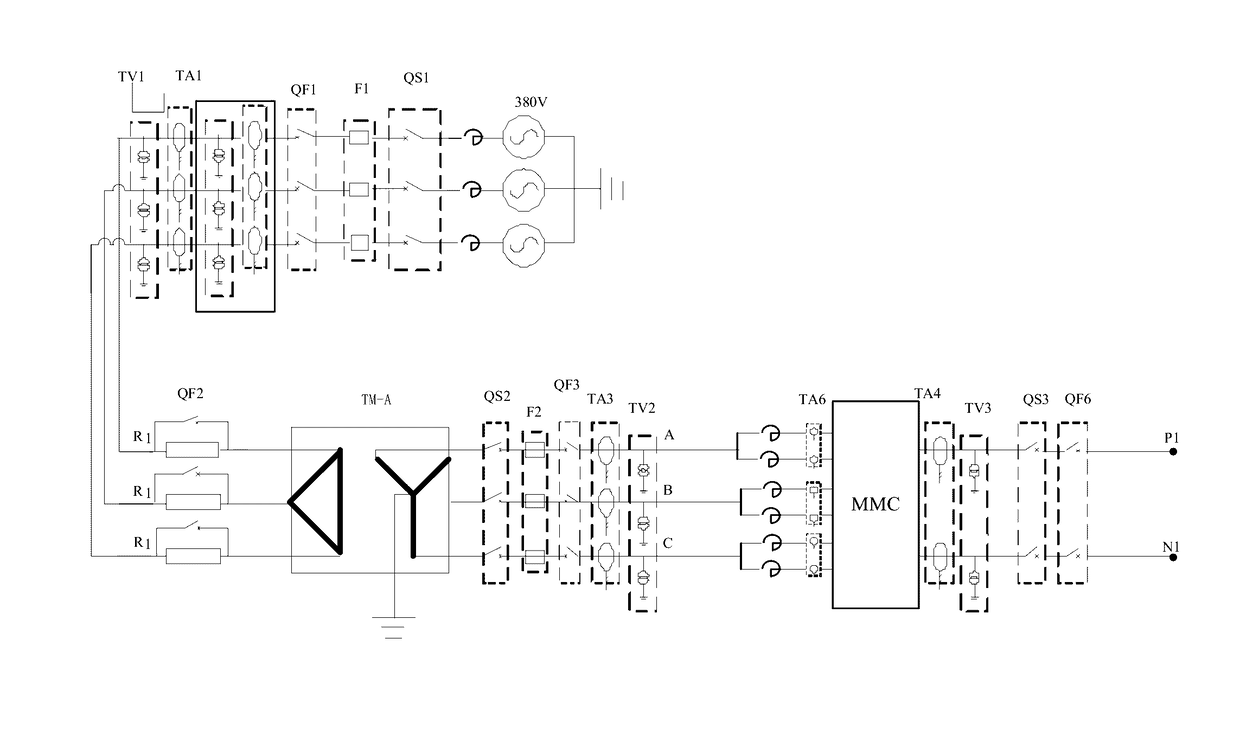

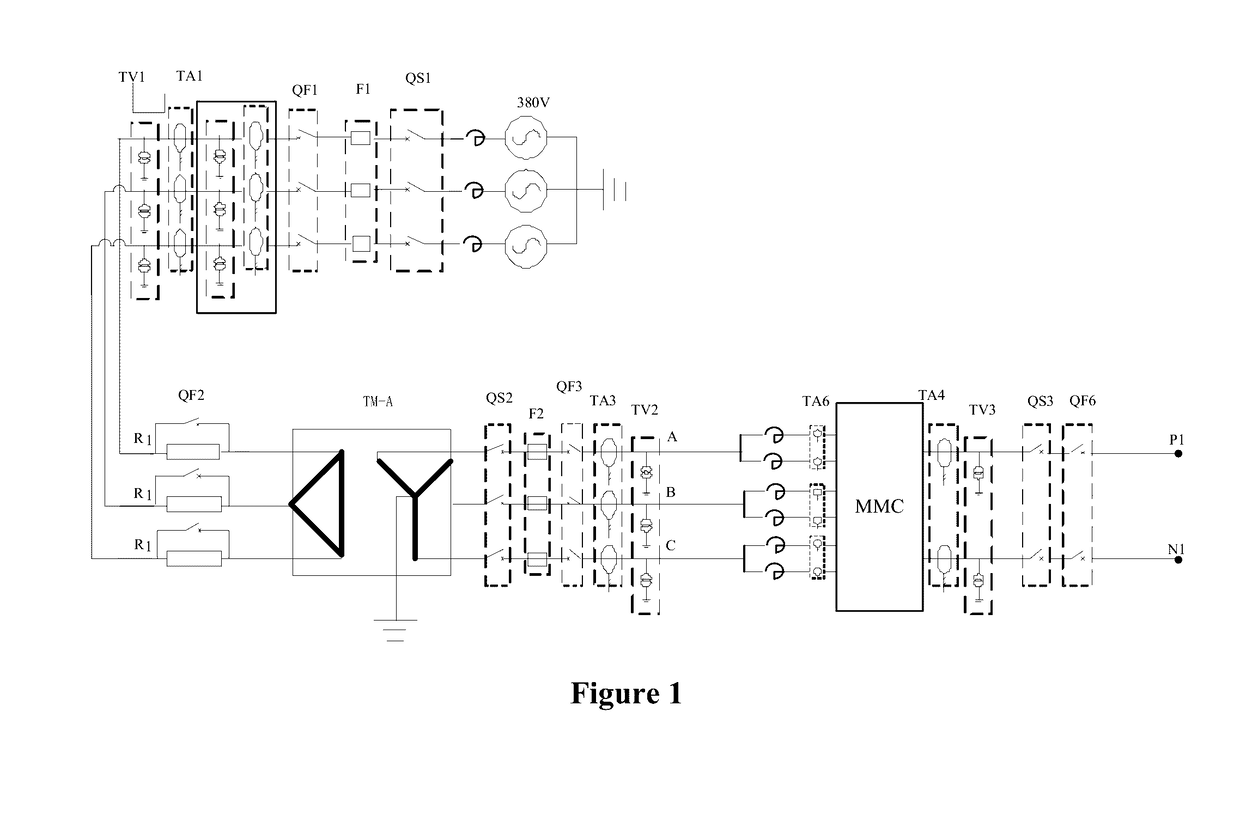

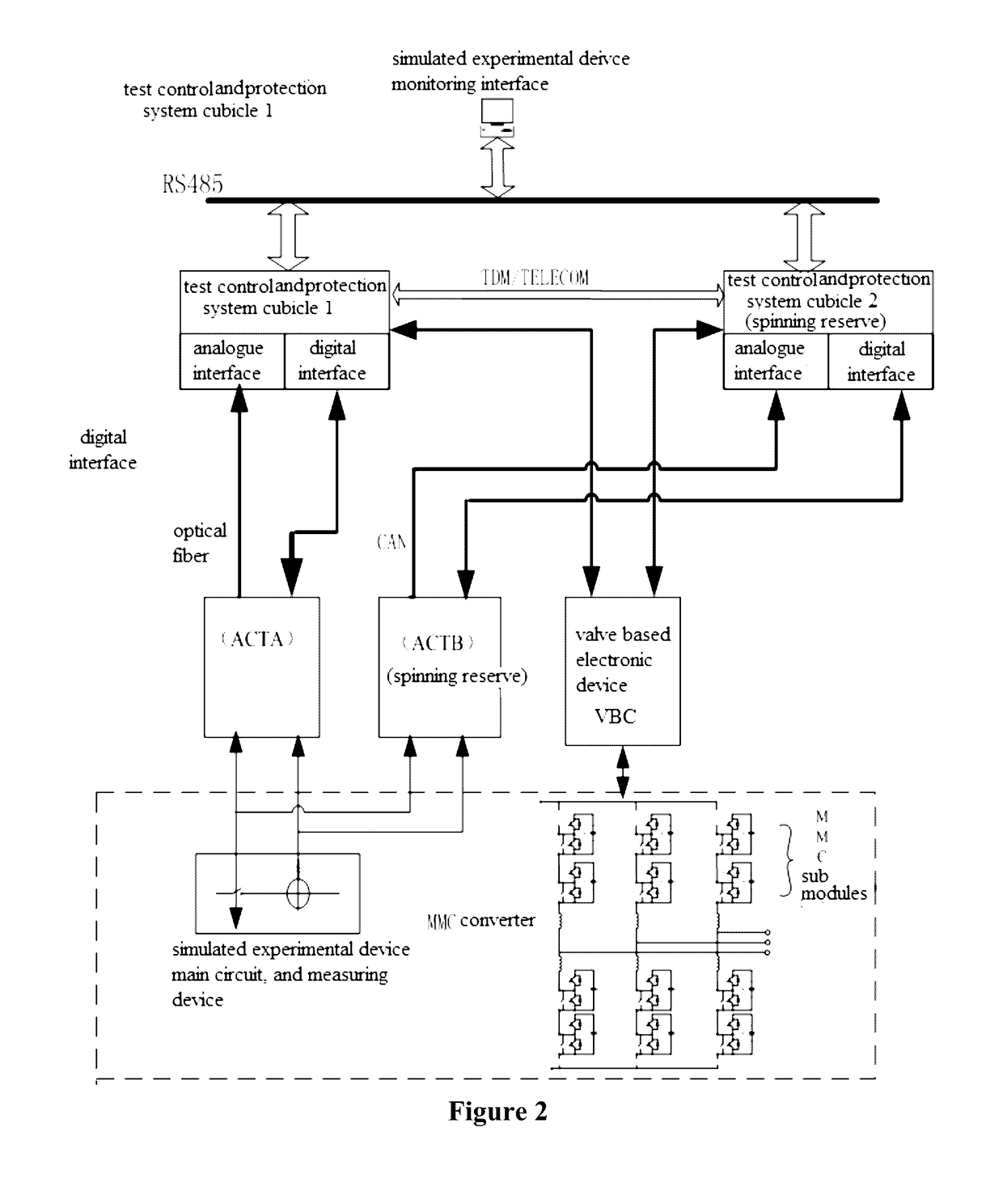

Real time dynamic physics simulation device of flexible DC transmission system

ActiveUS9659114B2Accurate understandingCompact structureElectronic circuit testingFault location by conductor typesAc fieldTransformer

The present invention relates to a real time dynamic physics simulation device of flexible DC transmission system. The device includes simulated converter transformer, simulated AC field, simulated DC field, simulated converter reactor, simulated converter, and measurement and control cabinet chassis; the simulated AC field includes the vacuum switch I, the contactor I, resistors and the vacuum switch II connected orderly; the simulated DC field includes successively connected the vacuum switch contactor III and II; the simulated AC field is connected with said measurement and control cabinet chassis; Said converter transformer is set between said resistors and said vacuum switch II; Said simulated converter reactors and said simulated converter connected are set between the vacuum switch II and the vacuum switch III. The present invention can accurately simulate different voltage level flexible DC transmission system based on modular multilevel converter (MMC-HVDC), able to accurately understand the operation characteristics of MMC-HVDC and the dynamic responds to the instruction of the control system.

Owner:STATE GRID CORP OF CHINA +1

Method and device for detection and identification of gases

ActiveCN101918827ADrift speed increased or decreasedExtended flight timeTime-of-flight spectrometersParticle spectrometer methodsElectrical field strengthChemical compound

Owner:AIRSENSE ANALYTICS

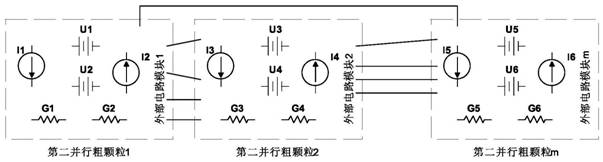

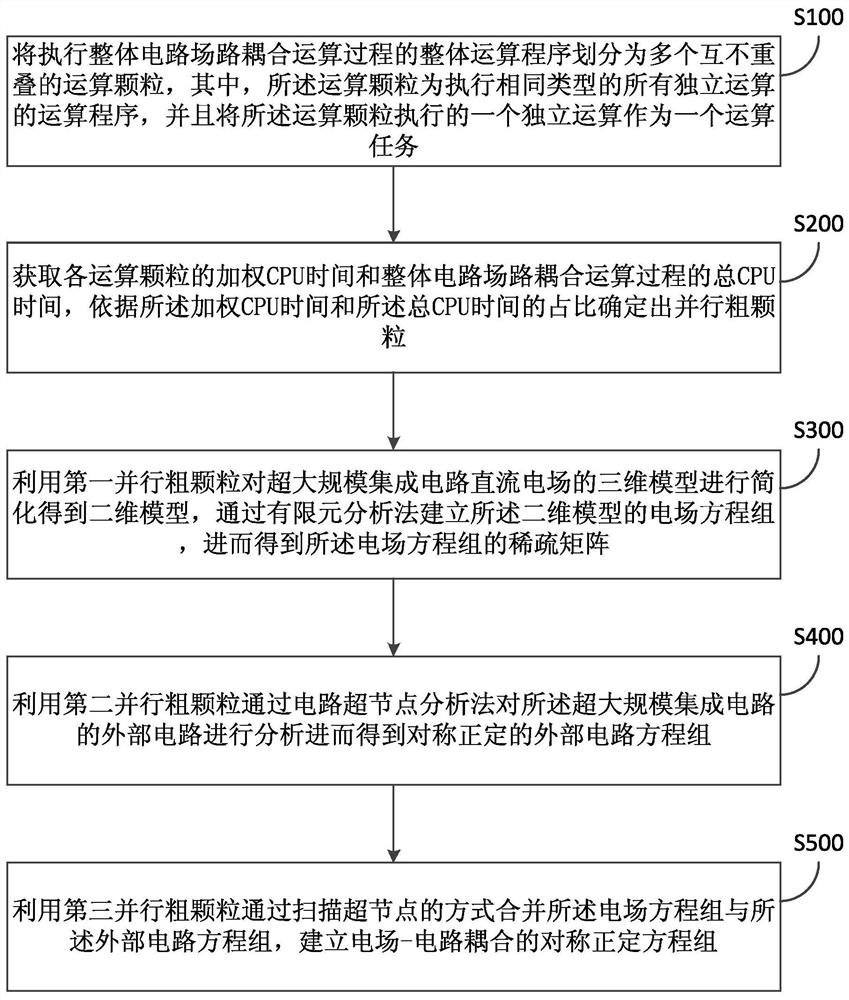

Multi-process self-adaptive allocation multilayer super-large-scale integrated circuit field circuit coupling method

InactiveCN111881641AImprove design efficiencyAvoid reading and writing bottlenecksCAD circuit designSpecial data processing applicationsTerm memoryField analysis

The invention discloses a multi-process self-adaptive allocation super-large-scale integrated circuit field-circuit coupling method, which perfectly realizes a rapid and accurate calculation target offield-circuit coupling of multi-layer super-large-scale integrated circuit direct-current field analysis by simplifying a three-dimensional problem into a two-dimensional problem and adopting a super-node technology. Field circuit coupling can be accurately and completely carried out on the multi-layer integrated circuit direct-current electric field, and the calculation speed of the multi-layerintegrated circuit and chip packaging direct-current electric field is increased. Meanwhile, coarse particle parallelism is achieved in the operation process, communication between processes and waiting time generated by synchronization are reduced to a great extent, meanwhile, due to the fact that a calculation task random dynamic allocation method is adopted, it is guaranteed that calculation models with unequal complexity are randomly and evenly distributed on all calculation nodes, and calculation efficiency is improved. And a hard disk read-write bottleneck caused by virtual memory accessdue to an overhigh peak memory is avoided.

Owner:北京智芯仿真科技有限公司

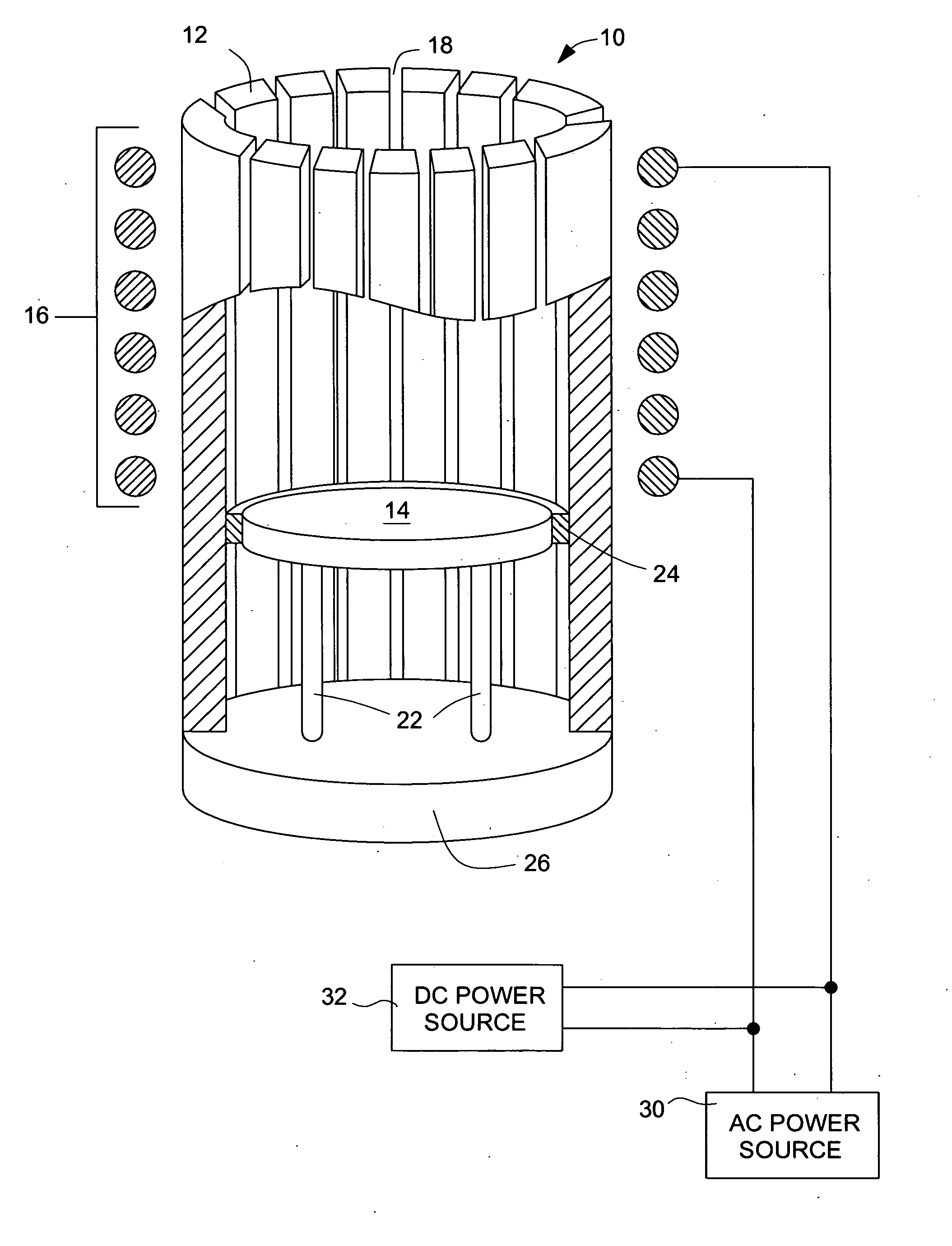

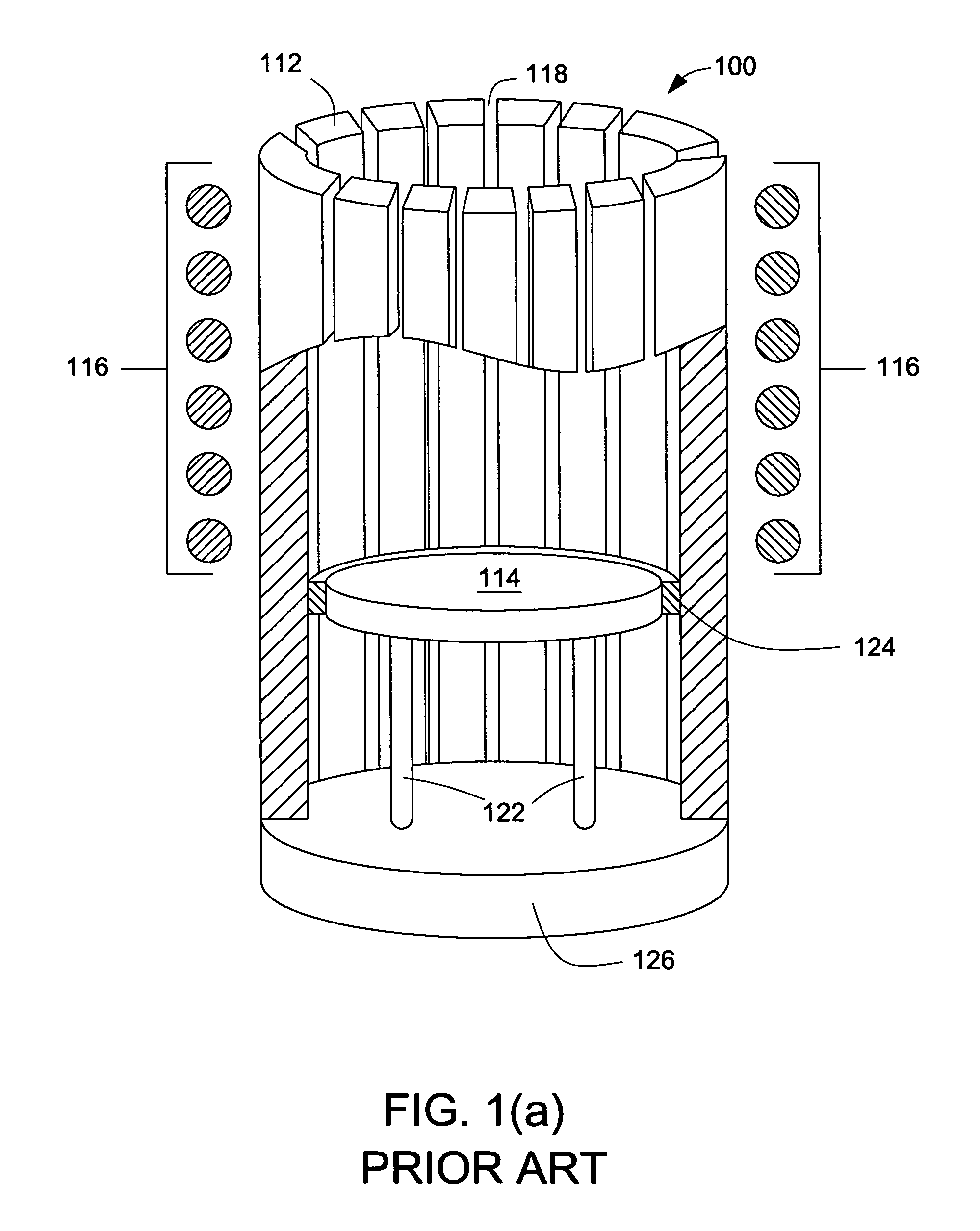

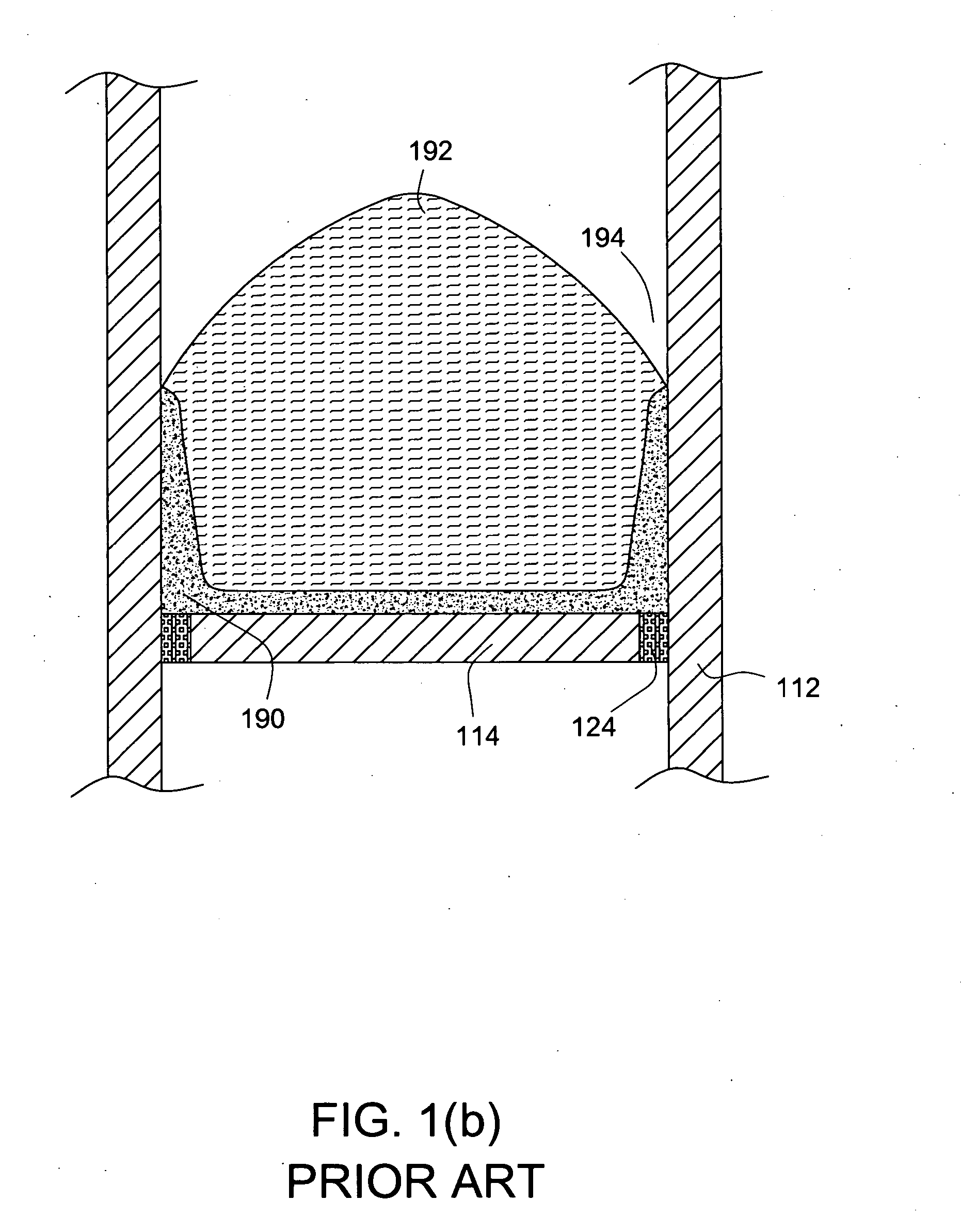

Cold crucible induction furnace with eddy current damping

Apparatus and method are provided for damping the induced fluid flow, particularly in the region of the base plate, in an electrically conductive material that is heated and melted in a cold crucible induction furnace. Damping is accomplished by establishing a dc magnetic field such that flow of the electrically conductive liquid metal in that dc magnetic field would induce eddy currents in the liquid metal which would generate forces that tend to oppose the flow. The dc magnetic field may be established by dc current flow in the ac induction coil that induces current in the material, dc current flow in a separate dc coil, or coils, constructed to prevent excessive induced losses, by discrete magnets, or a combination of any of the three prior methods. The dc magnetic field may also be established by dc current flow in one or more dc coils disposed around a magnetic pole piece located below the base of the furnace. One end of the magnetic pole piece is located adjacent to the bottom of the crucible base, so that the pole piece concentrates the dc field into the lower portion of the molten electrically conductive material.

Owner:CONSARC

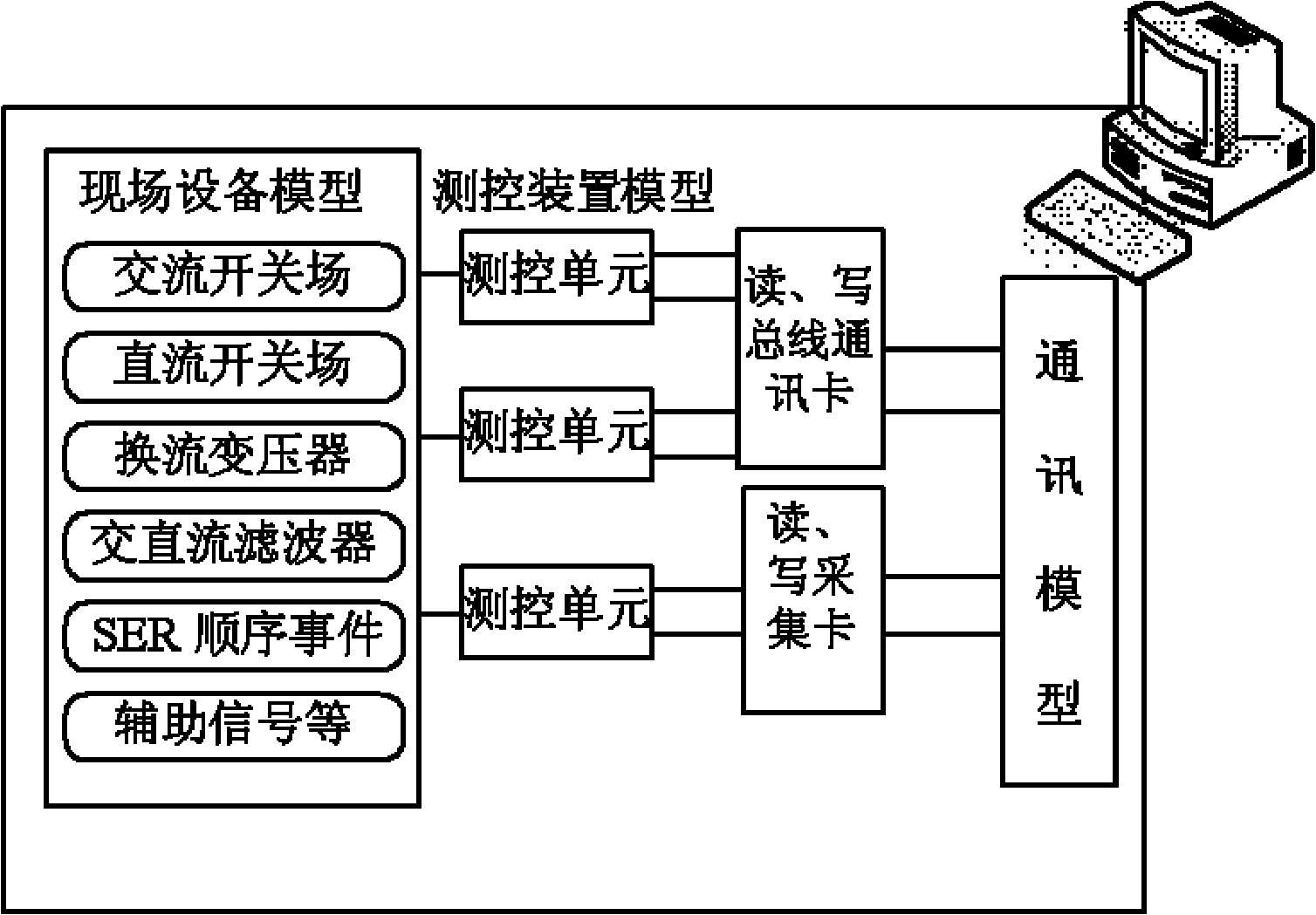

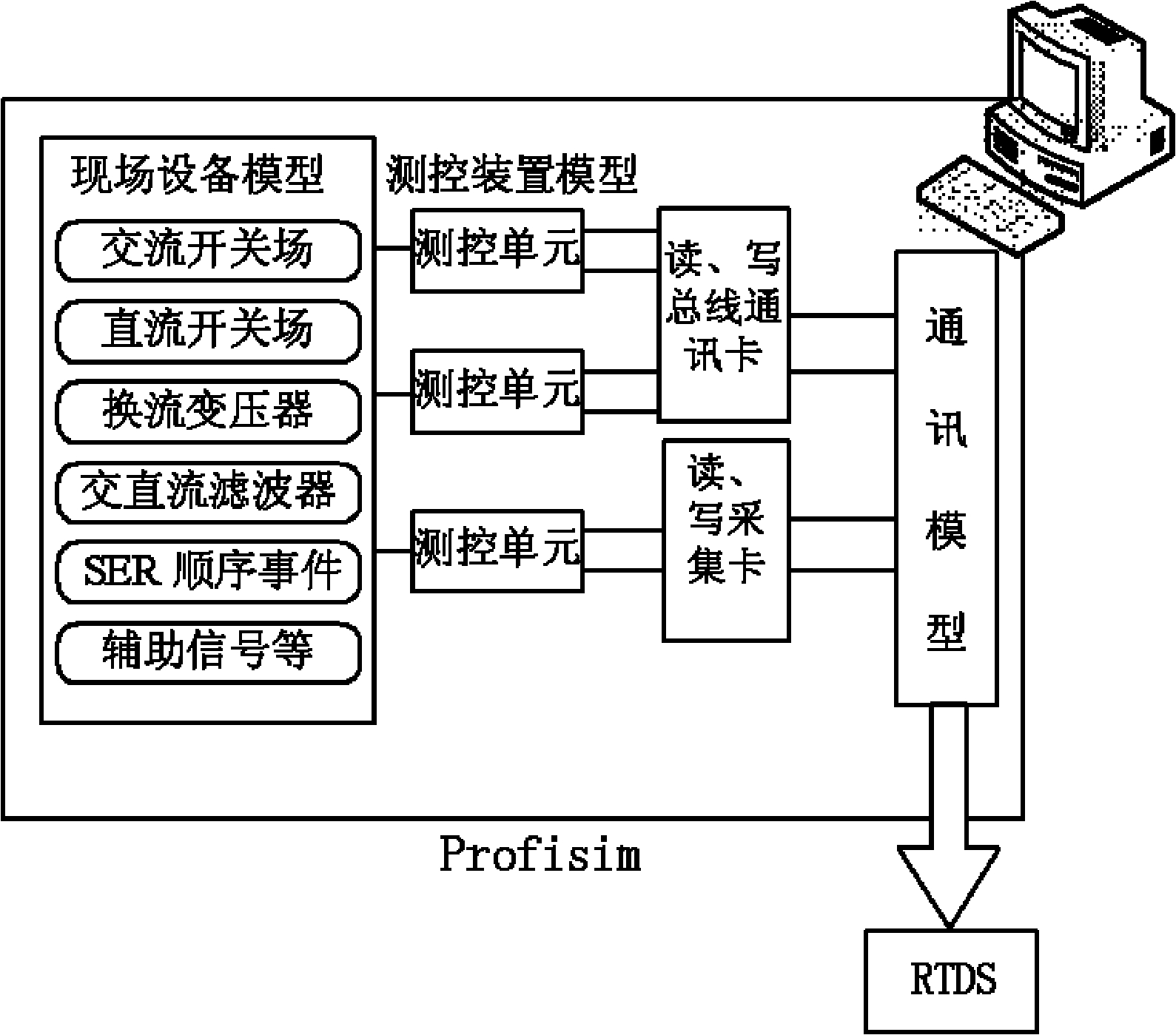

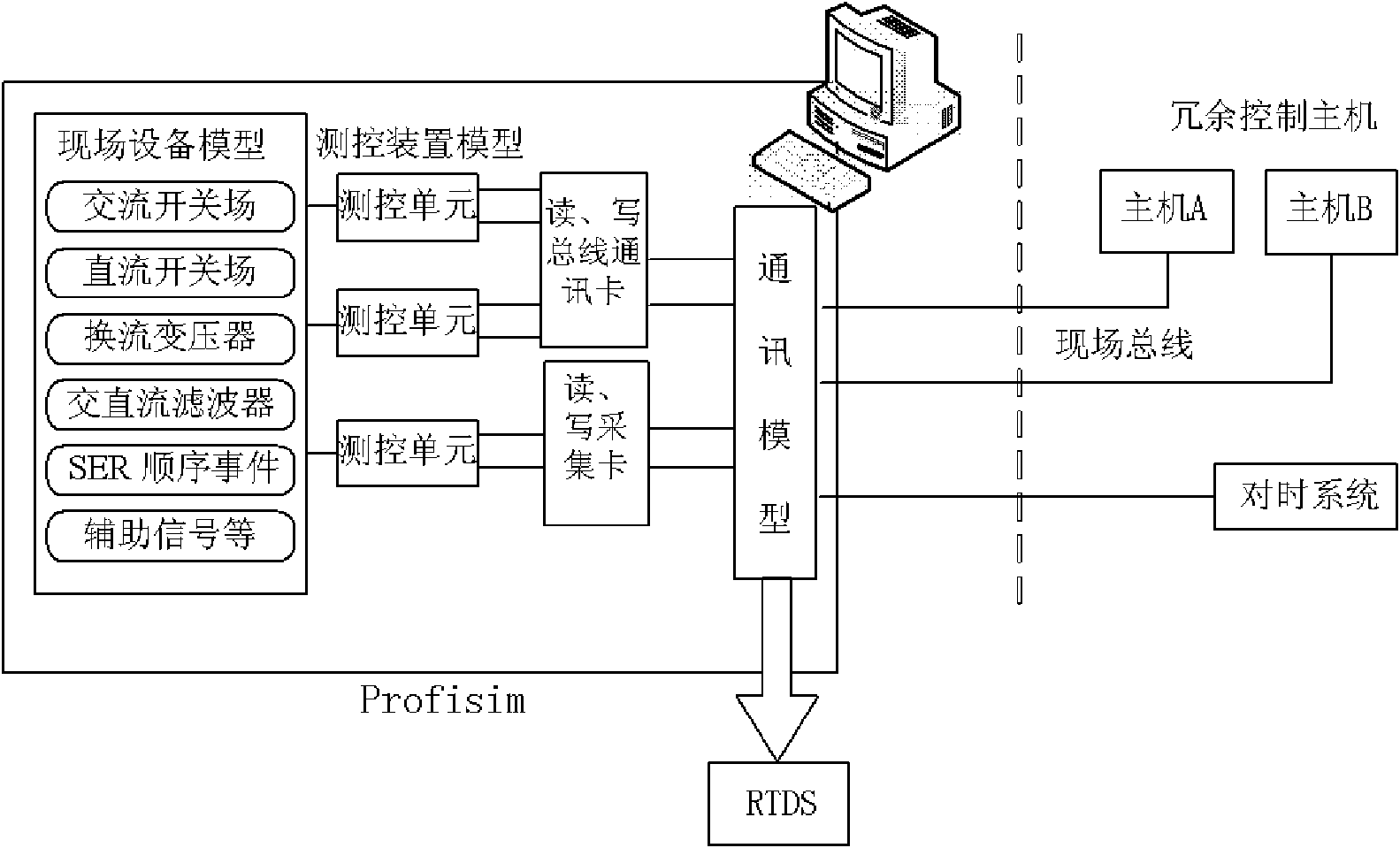

DC field layer simulation system, digital real-time emulation system and closed loop test system

ActiveCN101782774AReduce constructionWon't show up? Uncontrollable? The problemElectric testing/monitoringProgramme total factory controlReal-time simulationTransformer

The invention relates to a DC field layer simulation system, a digital real-time emulation system and a closed loop test system. The DC field layer simulation system comprises a field equipment model, a test and control device model, a communication model and a bus communication card and a collection card reading and writing module, wherein the field equipment model is used for simulating an AC / DC switch field, an AC / DC wave filter, a convertor transformer, an SER sequence event and an auxiliary signal in the field, the test and control device model can deliver operation commands, return the field equipment state and collect the analog variable, and the communication model is provided with a data collection card and a field bus communication card. The DC field layer simulation system simulates primary equipment and test and control devices in the field directly through the field equipment model and the test and control device model, reduces the building of the field physical test equipment environment, and can freely select devices to be tested in the simulation range, the problem of control incapability is avoided, the DC field layer simulation system is the system with actual and reliable test environment, and the expansion and the upgrading of the system are convenient.

Owner:XJ LIANHUA INT L ENVIRONMENTAL

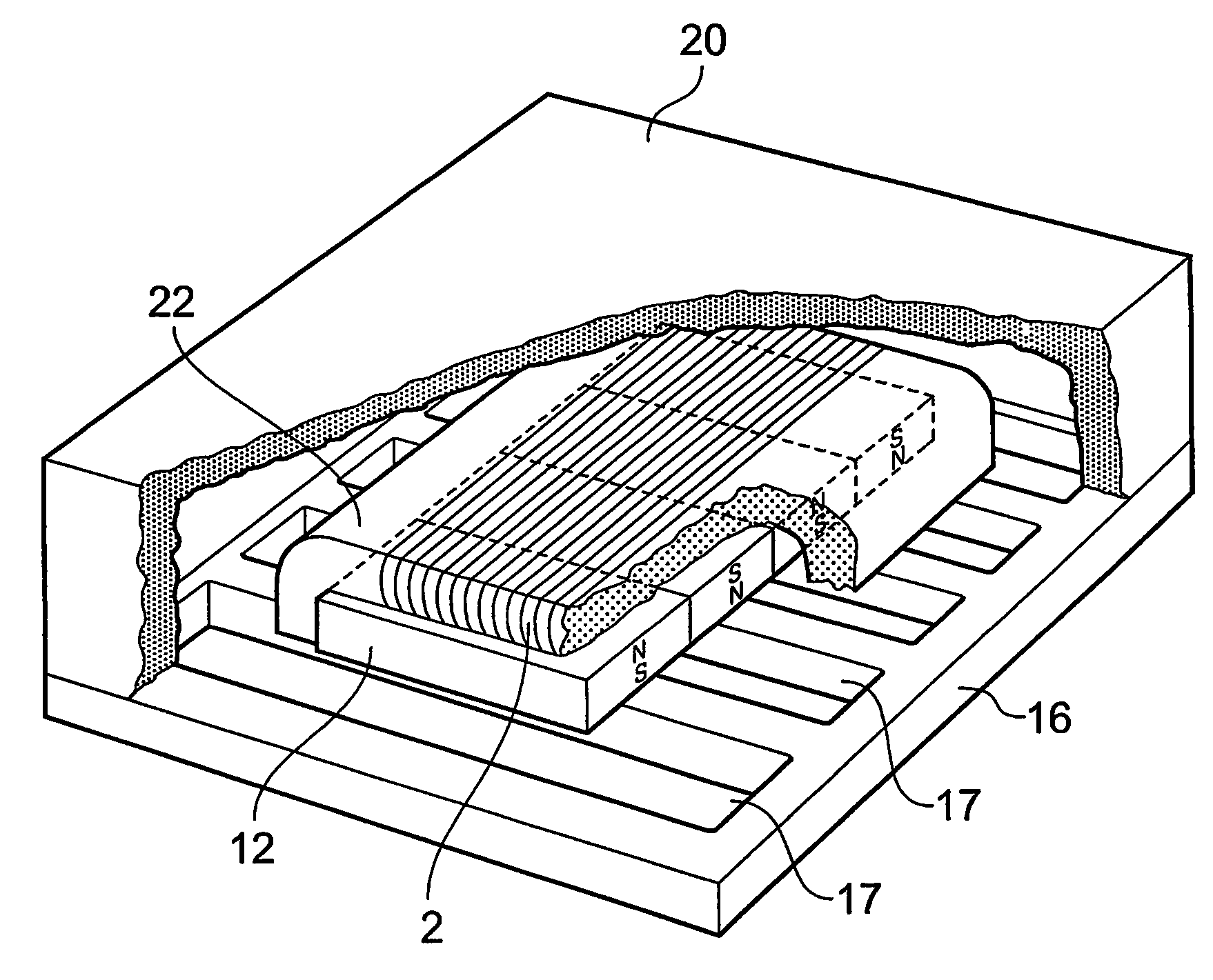

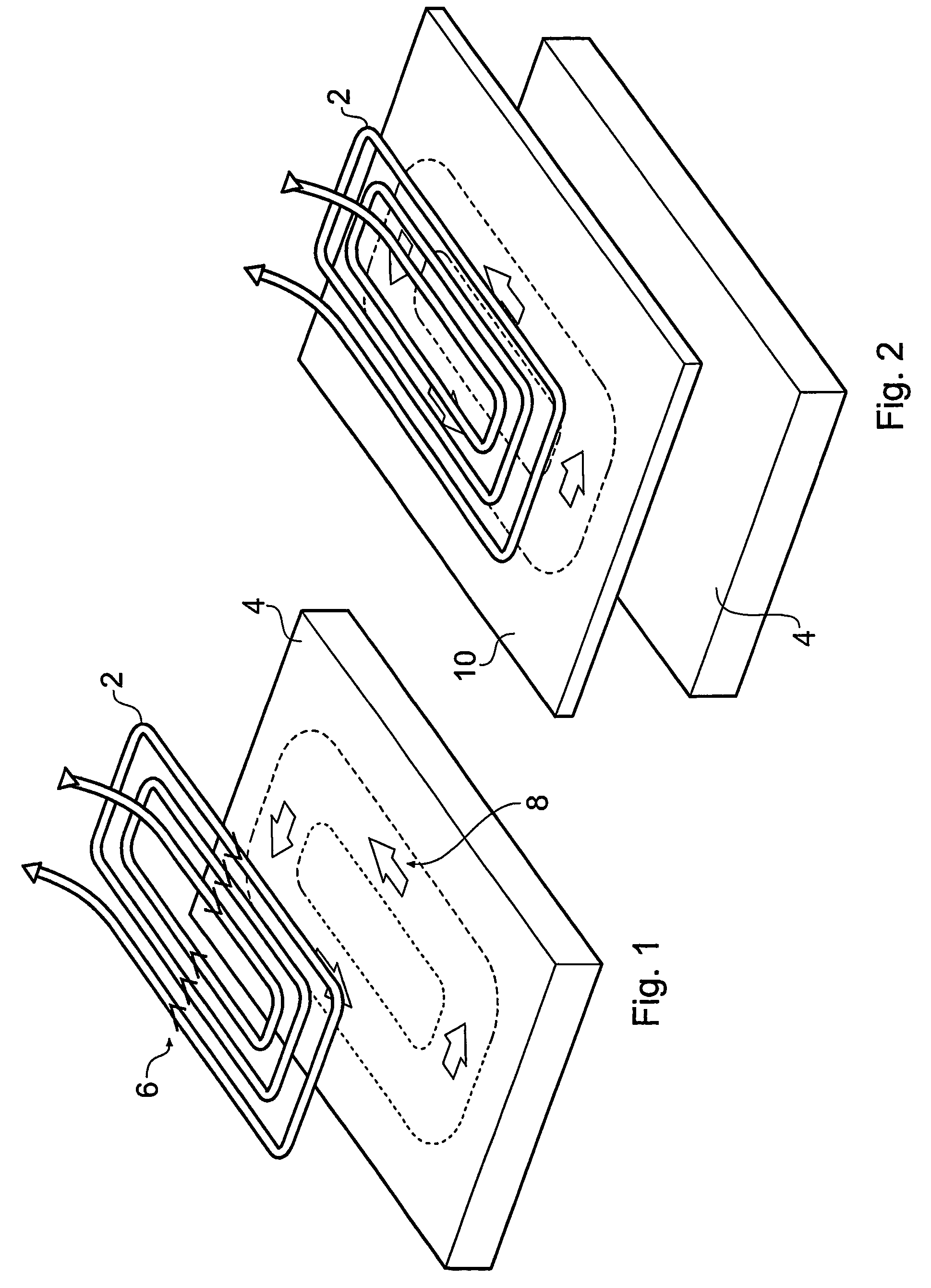

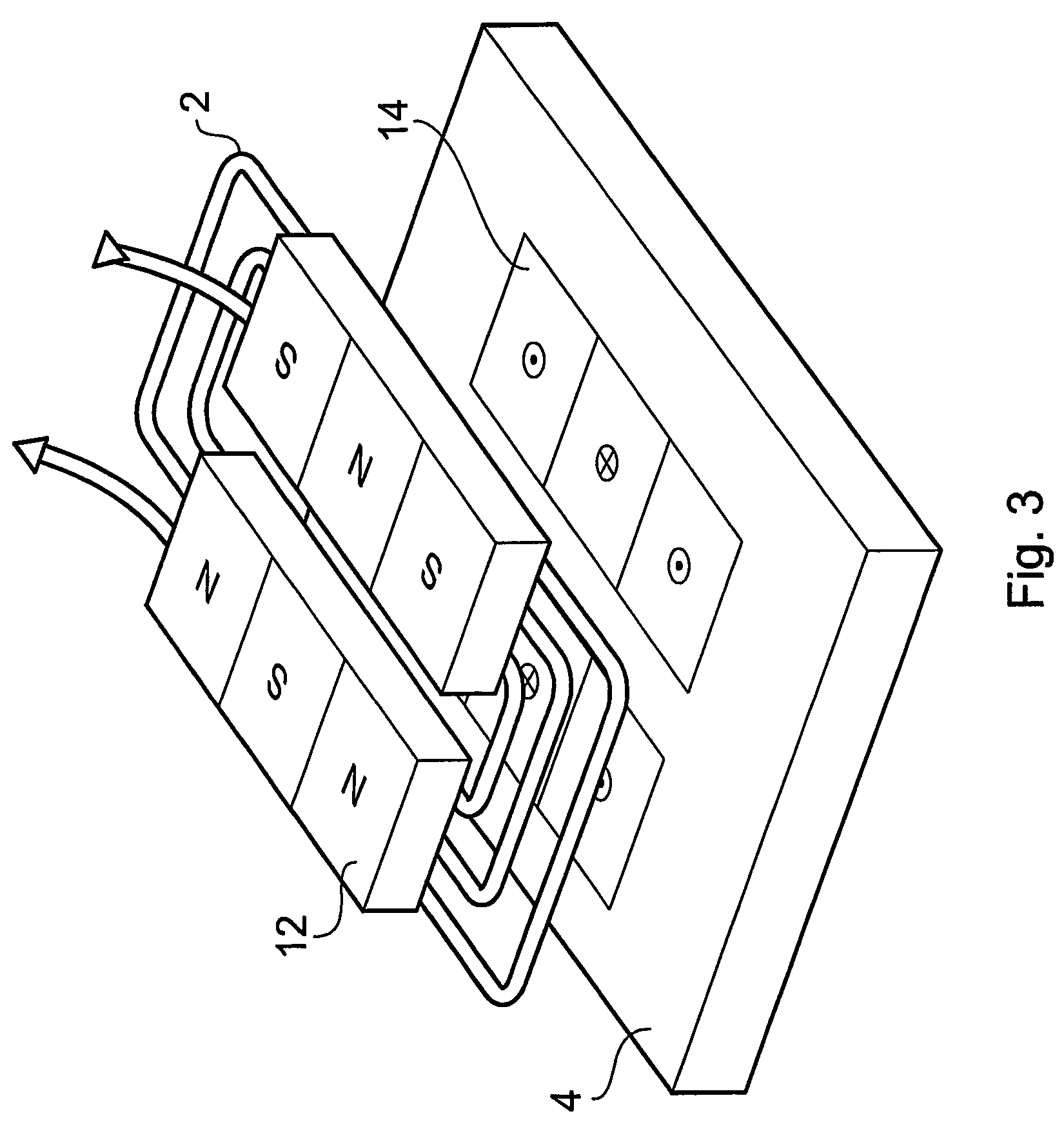

Electromagnetic acoustic transducer

ActiveUS7406873B2Wide choiceThickness wideAnalysing solids using sonic/ultrasonic/infrasonic wavesMechanical vibrations separationSonificationMaterial under test

Owner:PII LIMITED

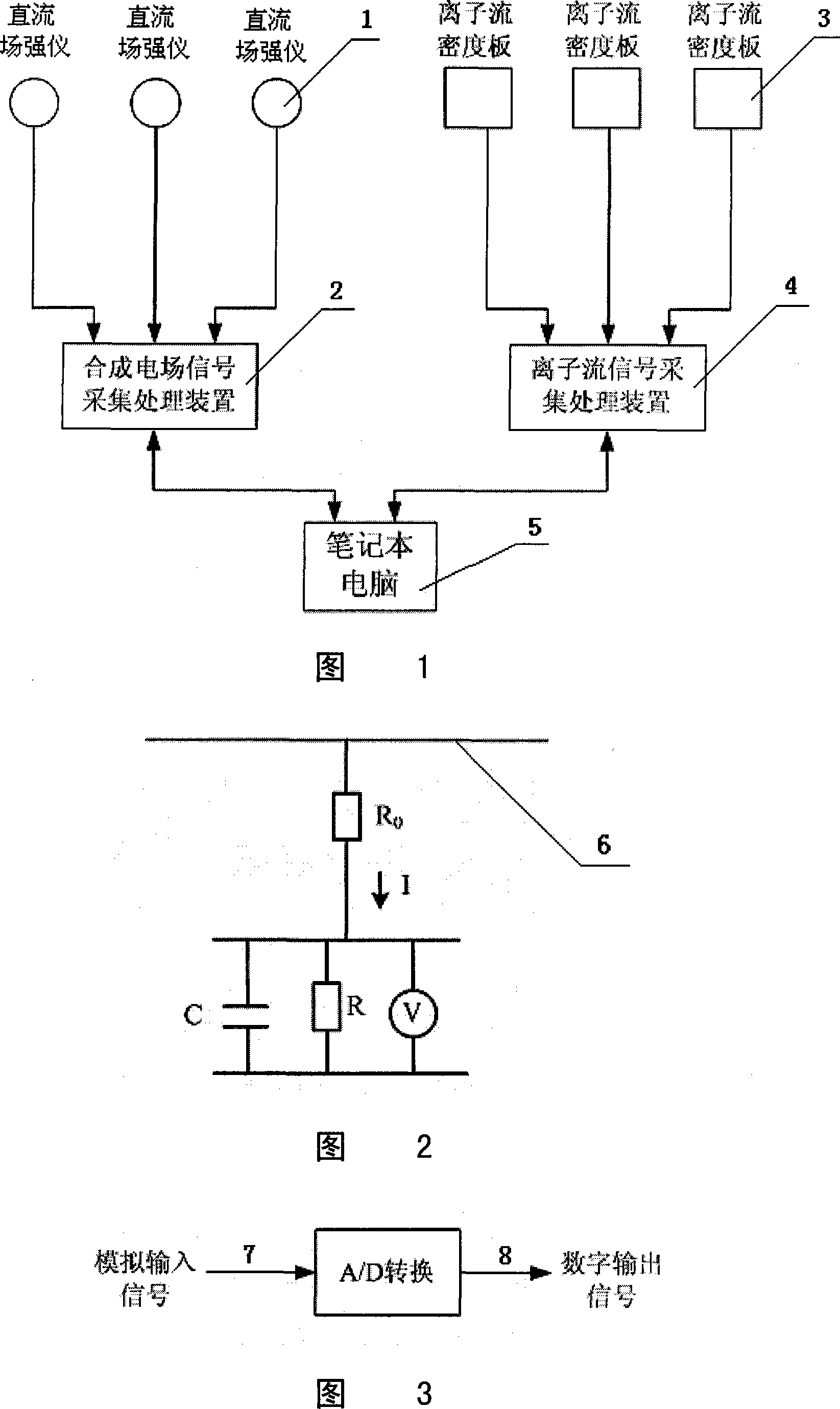

DC combination electric field and ion stream density measuring system

InactiveCN101188059AConvenient collection time settingElectric signal transmission systemsElectric discharge tubesAcquisition timeDisplay device

The invention relates to a system for measuring the DC combined electric field and the density of the ion flow. The invention is characterized in that the measuring system comprises a group of DC field intensity indicators connected with the signal collecting and processing device of the combined electric field by a signal cable, and a group of ion flow density board connected with the signal collecting and processing device of the ion flow by a signal cable. A / D converter modules are arranged in the signal collecting and processing devices of the combined electric field and the ion flow which are respectively connected with a control and signal display device in double ways by network tables. The control and signal display device is provided with dedicated software. The invention can conveniently set the channel collecting time of measuring signals, and can automatically measure the DC combined electric field and the density of the ion flow for a long time.

Owner:CHINA ELECTRIC POWER RES INST

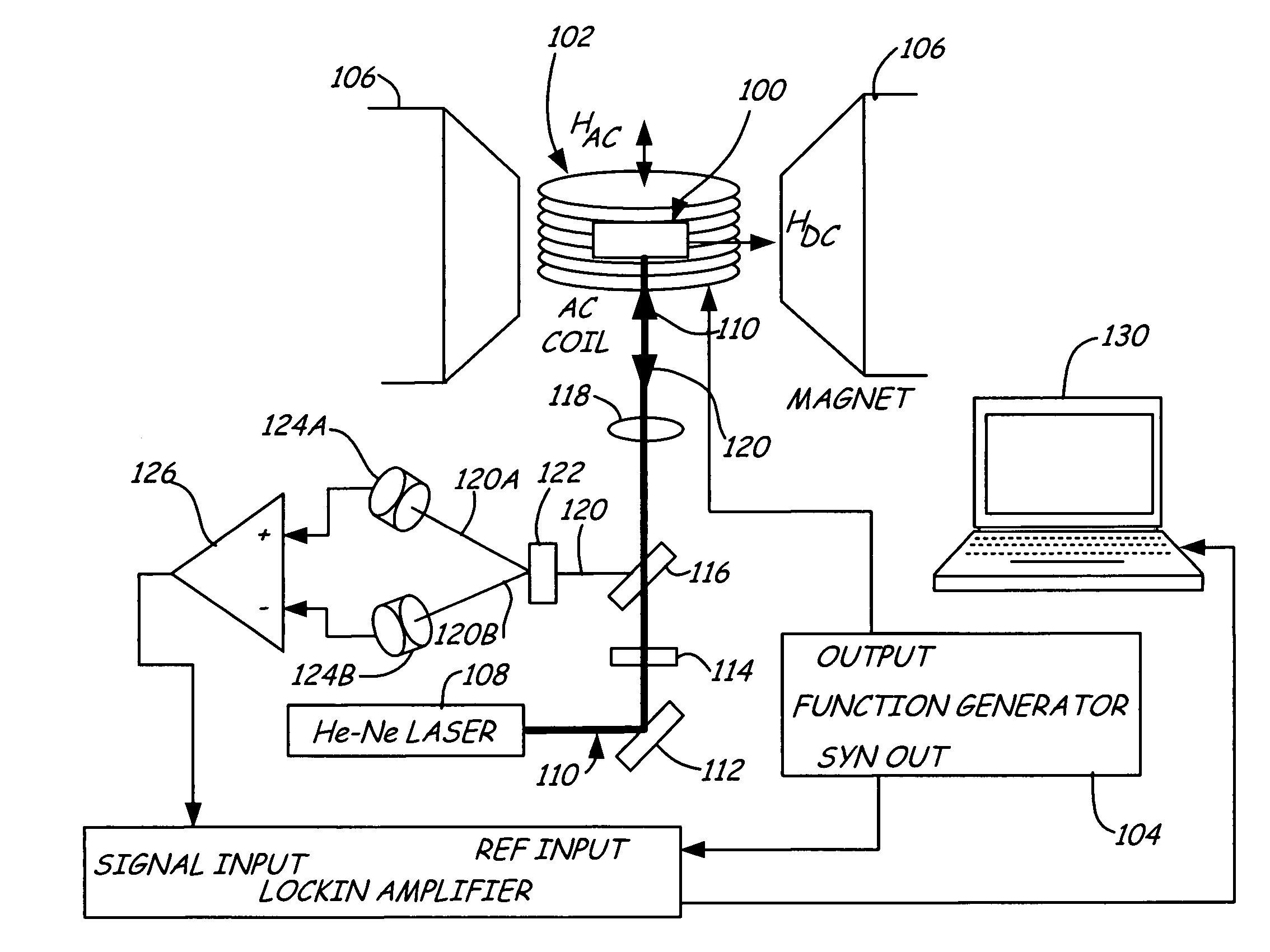

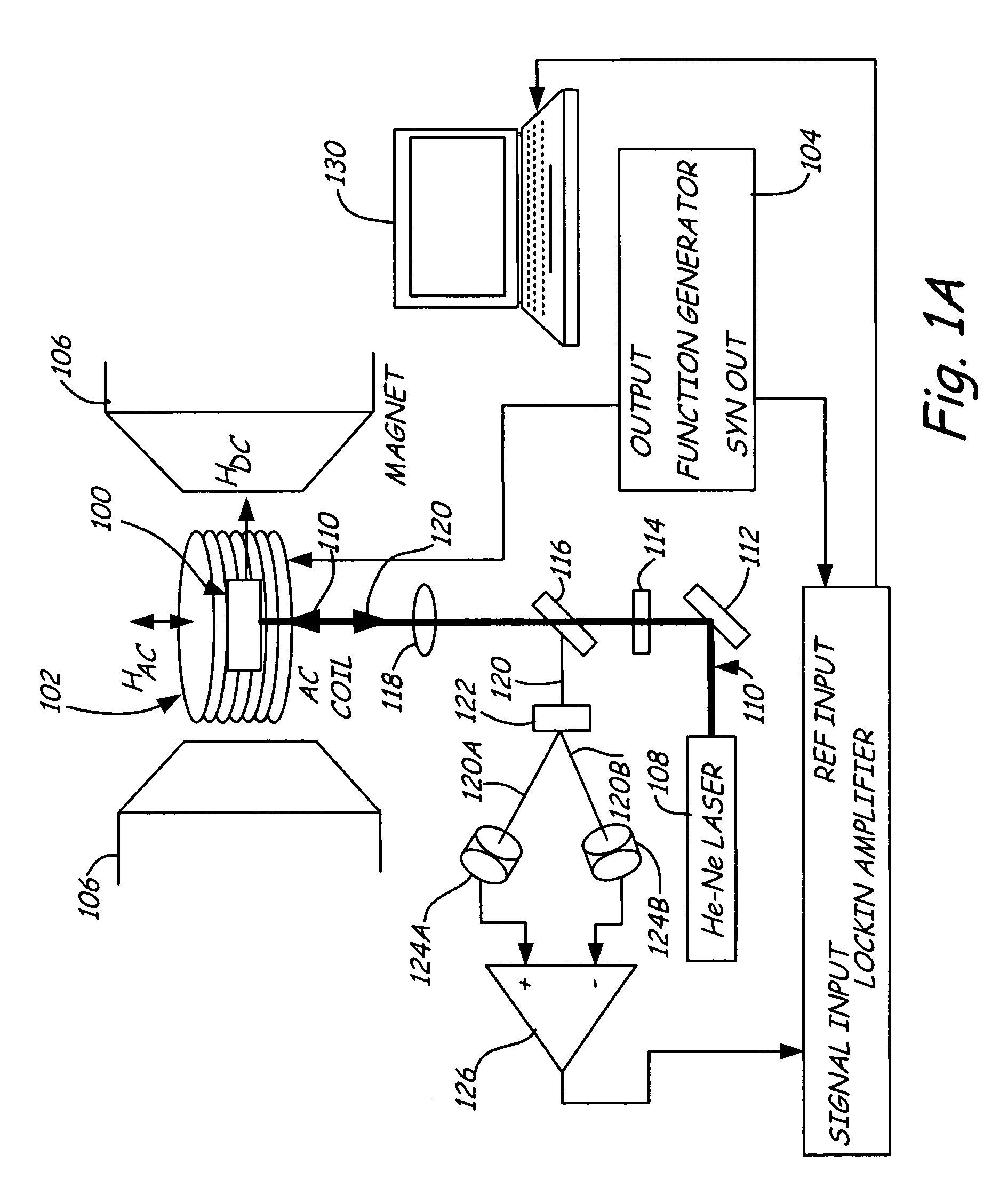

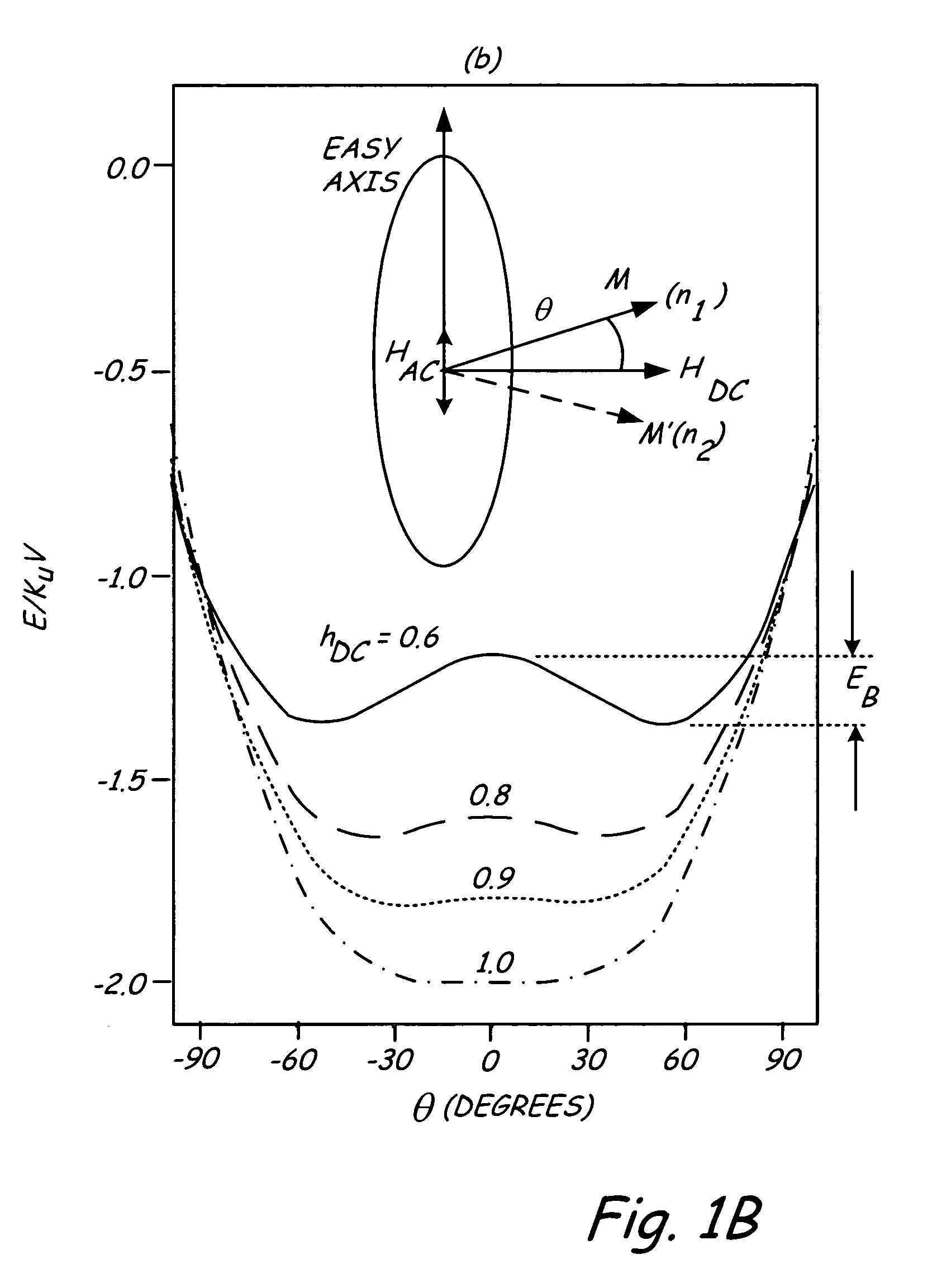

Complex transverse AC magneto-optic susceptometer for determination of volume and anisotropy field distribution in recording media

InactiveUS7166997B2Magnetic field measurement using magneto-optic devicesSusceptibility measurementsMagnetic susceptibilityDc field

A method and apparatus for determining volume and anisotropy field distribution of thin film granular material includes the use of a magneto-optic probe, a lock-in amplifier, and a computer. The magneto-optic probe utilizes the Kerr effect in order to determine the transverse AC susceptibility of the sample. The Lock-in amplifier determines the complex parameters of the susceptibility as a function of the DC field and AC frequency. Separate distribution values of anisotropy field and grain volume can then be determined mathematically from the relationship of complex susceptibility parameters to the DC field strength.

Owner:SEAGATE TECH LLC

High performance electrostatic precipitator

ActiveUS7534288B2Low production of ozoneImprove efficiencyParticle charging/ionising stationsExternal electric electrostatic seperatorParticulatesAc field

Owner:MASSACHUSETTS INST OF TECH

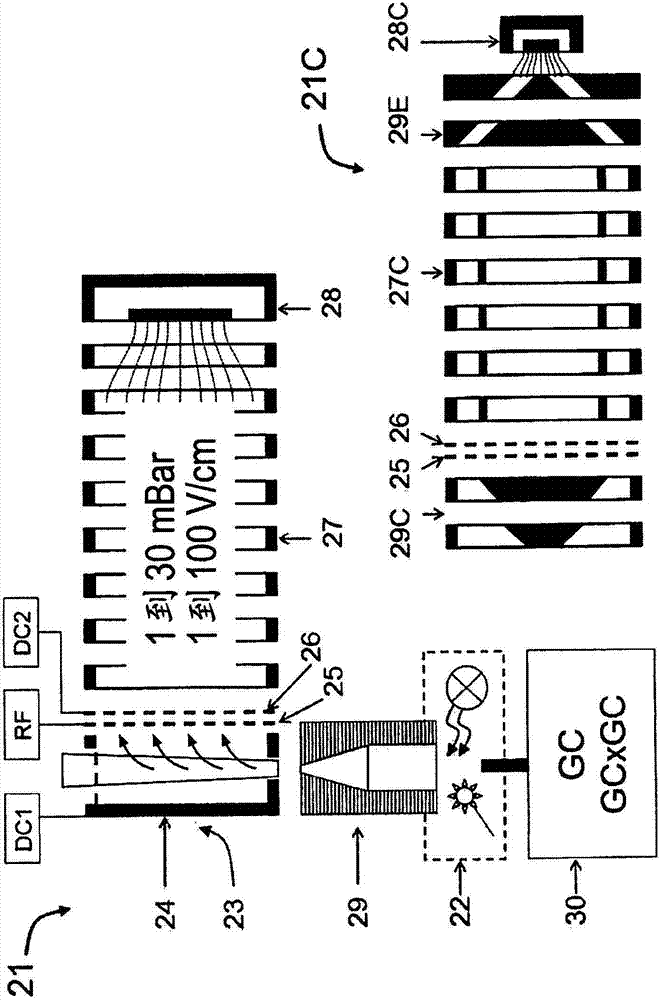

Ion mobility spectrometer with high throughput

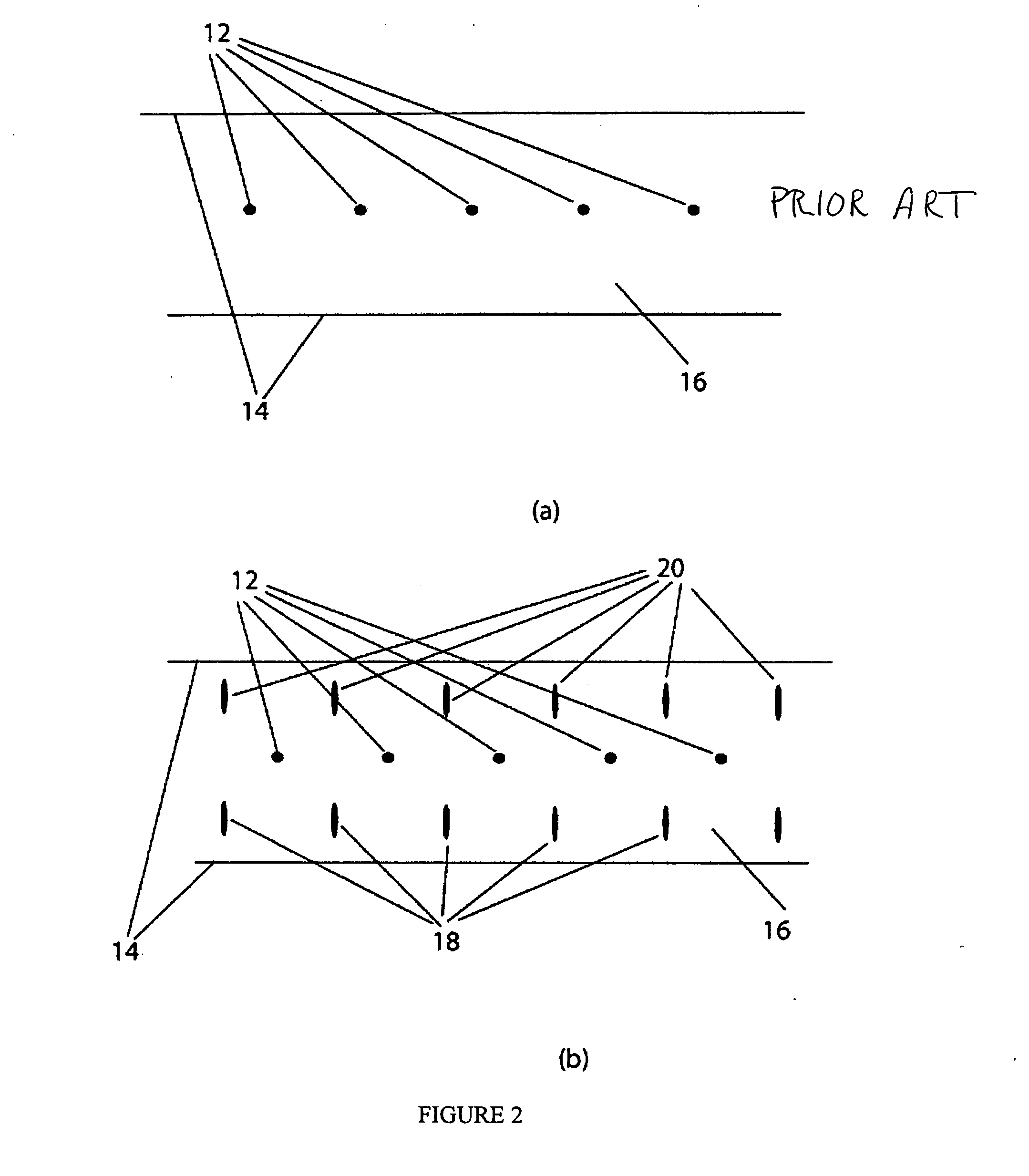

InactiveCN104508475AReduce the injection flow rateImproved signal-to-chemical-background ratioTime-of-flight spectrometersElectron/ion optical arrangementsIon-mobility spectrometryAtomic physics

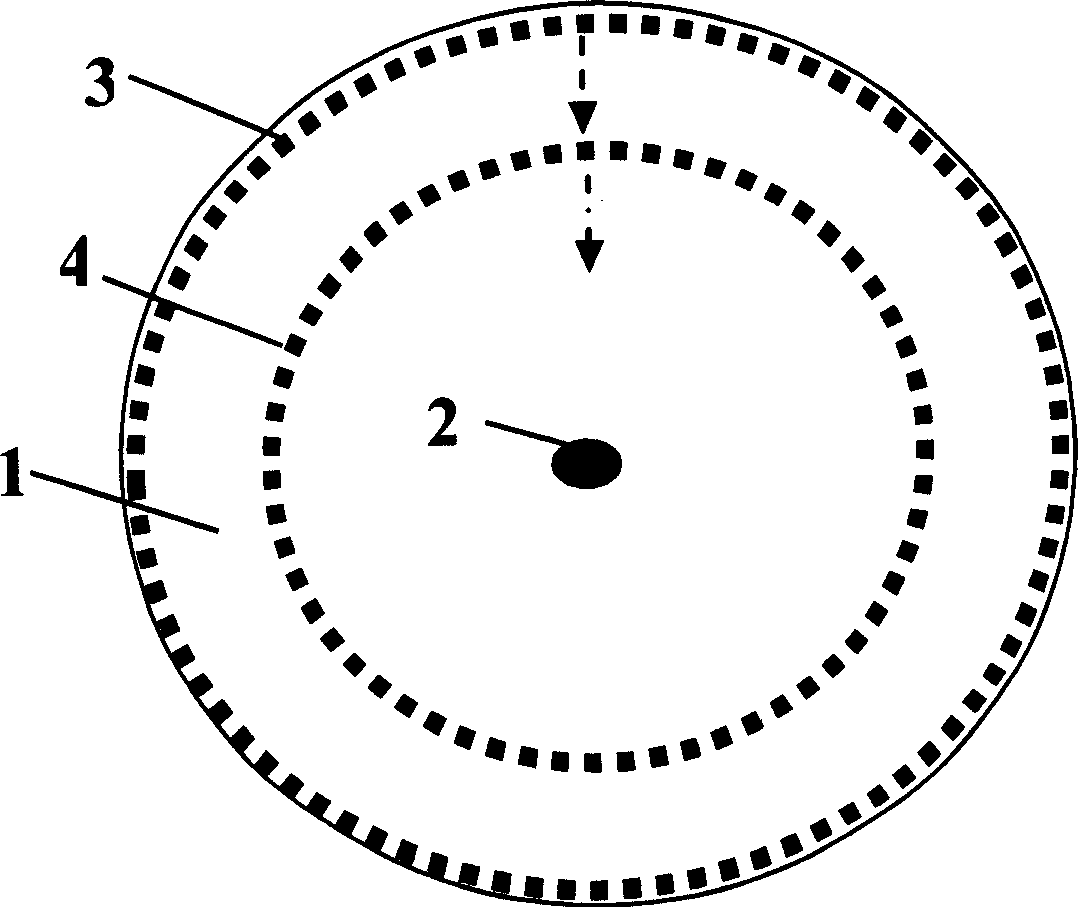

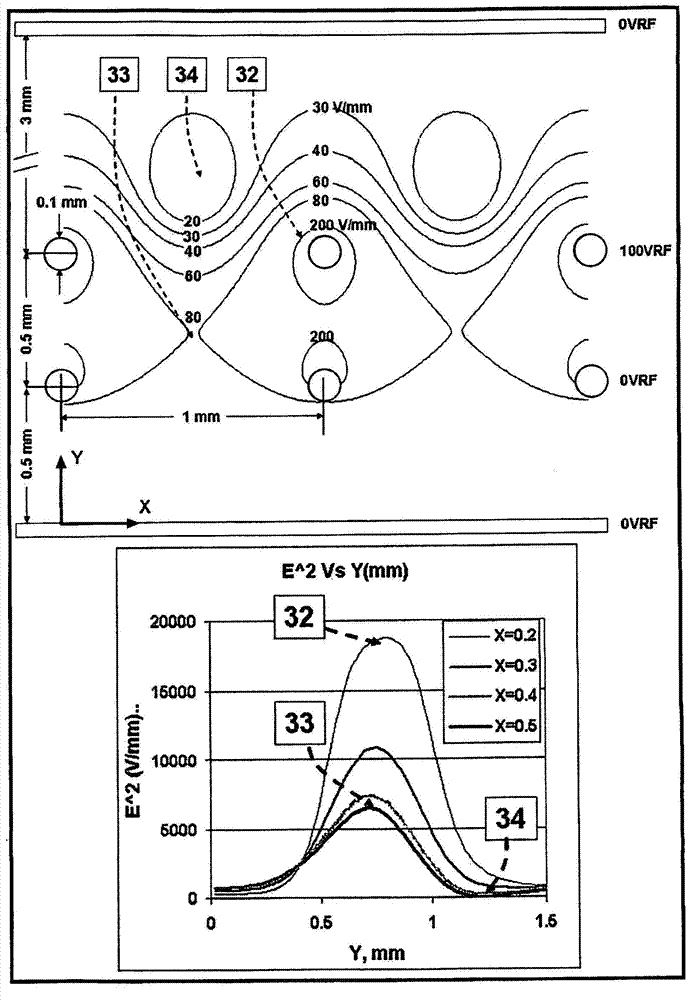

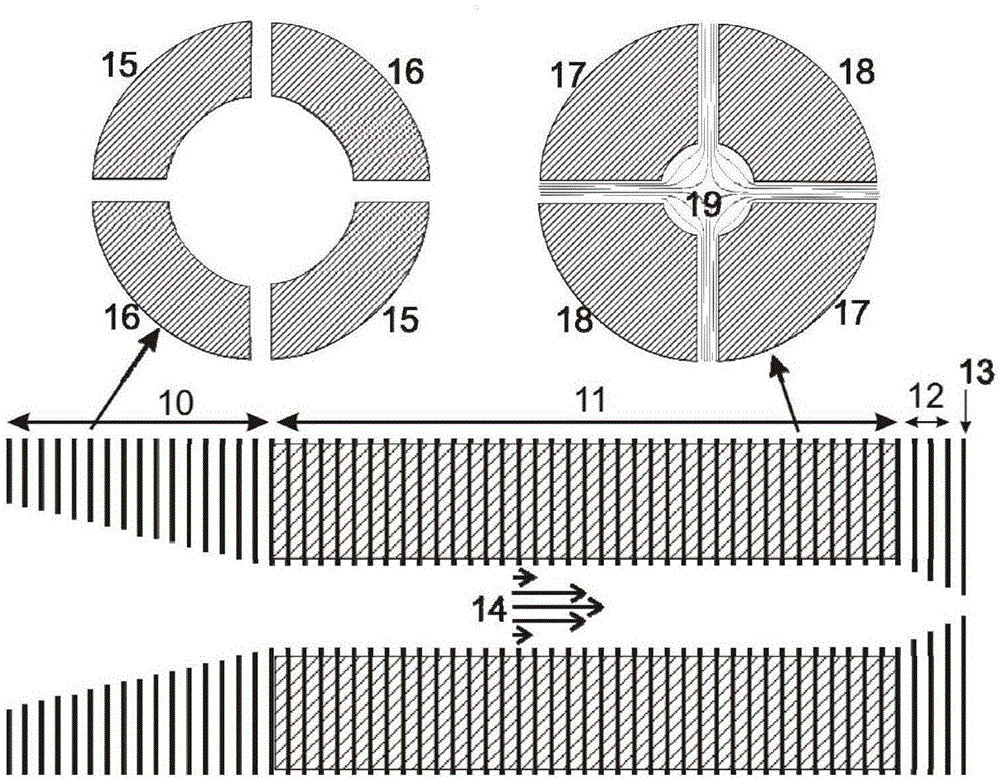

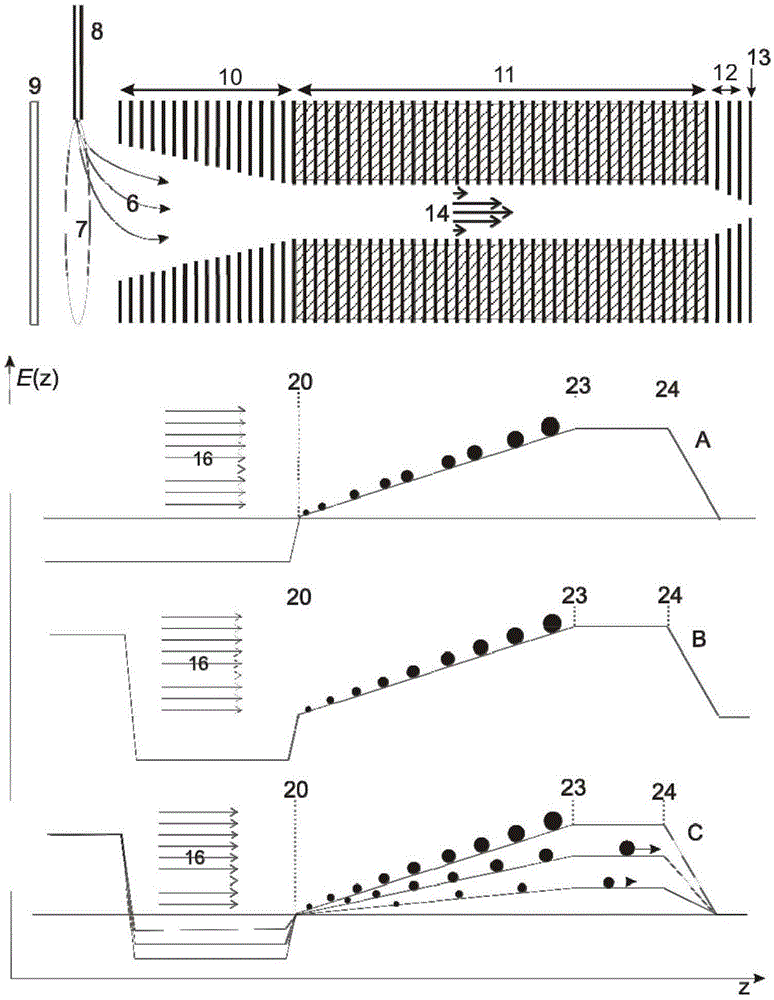

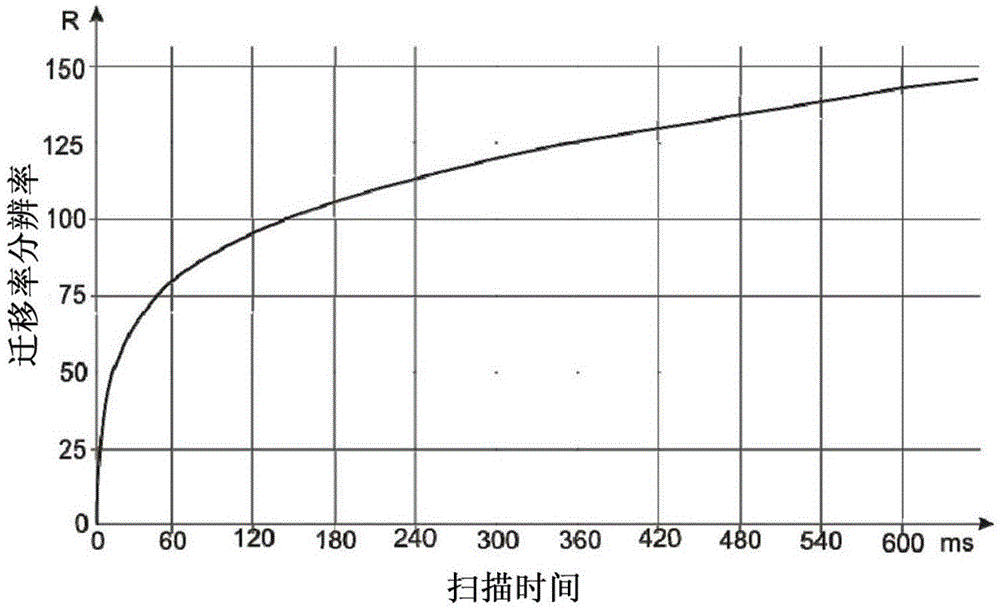

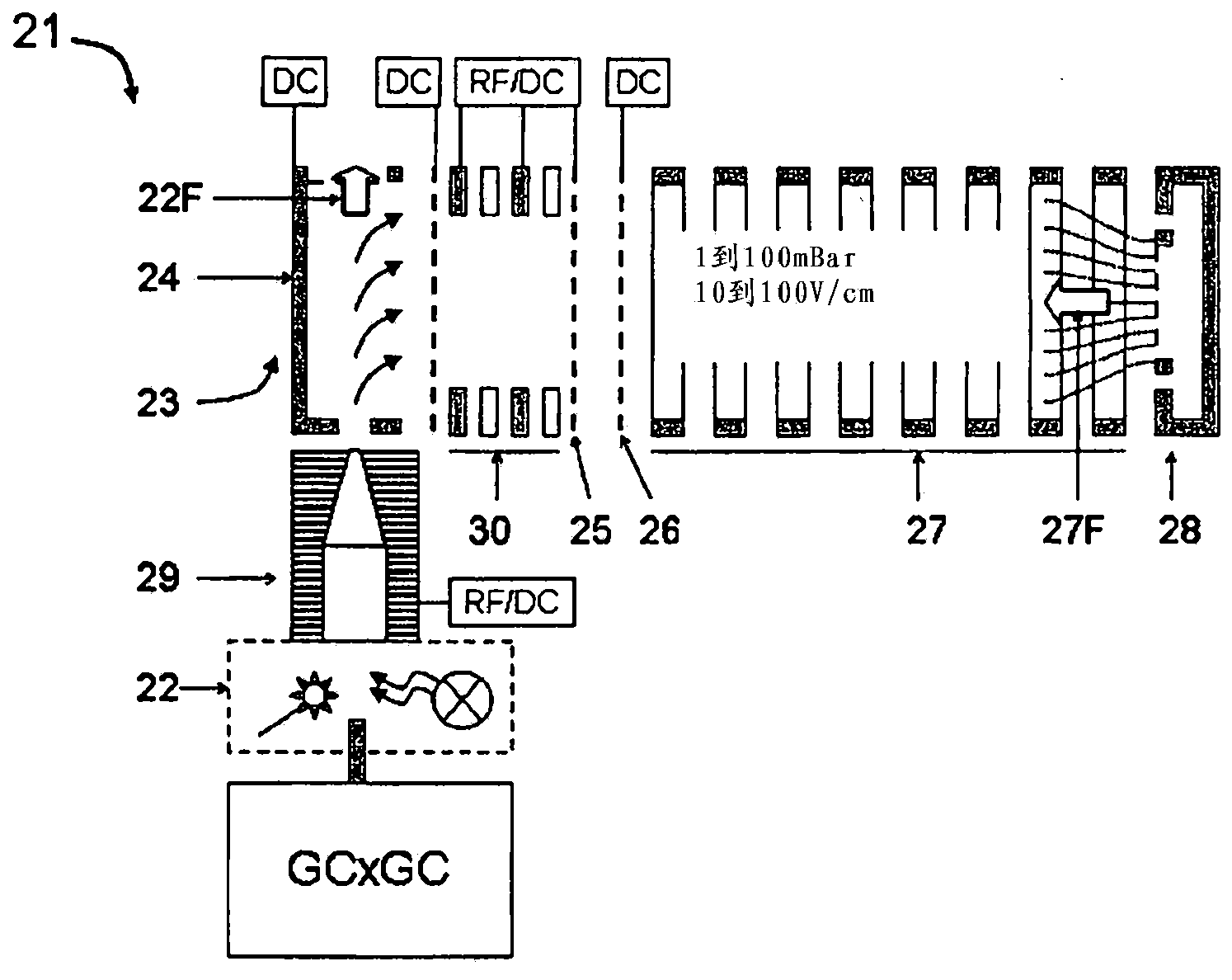

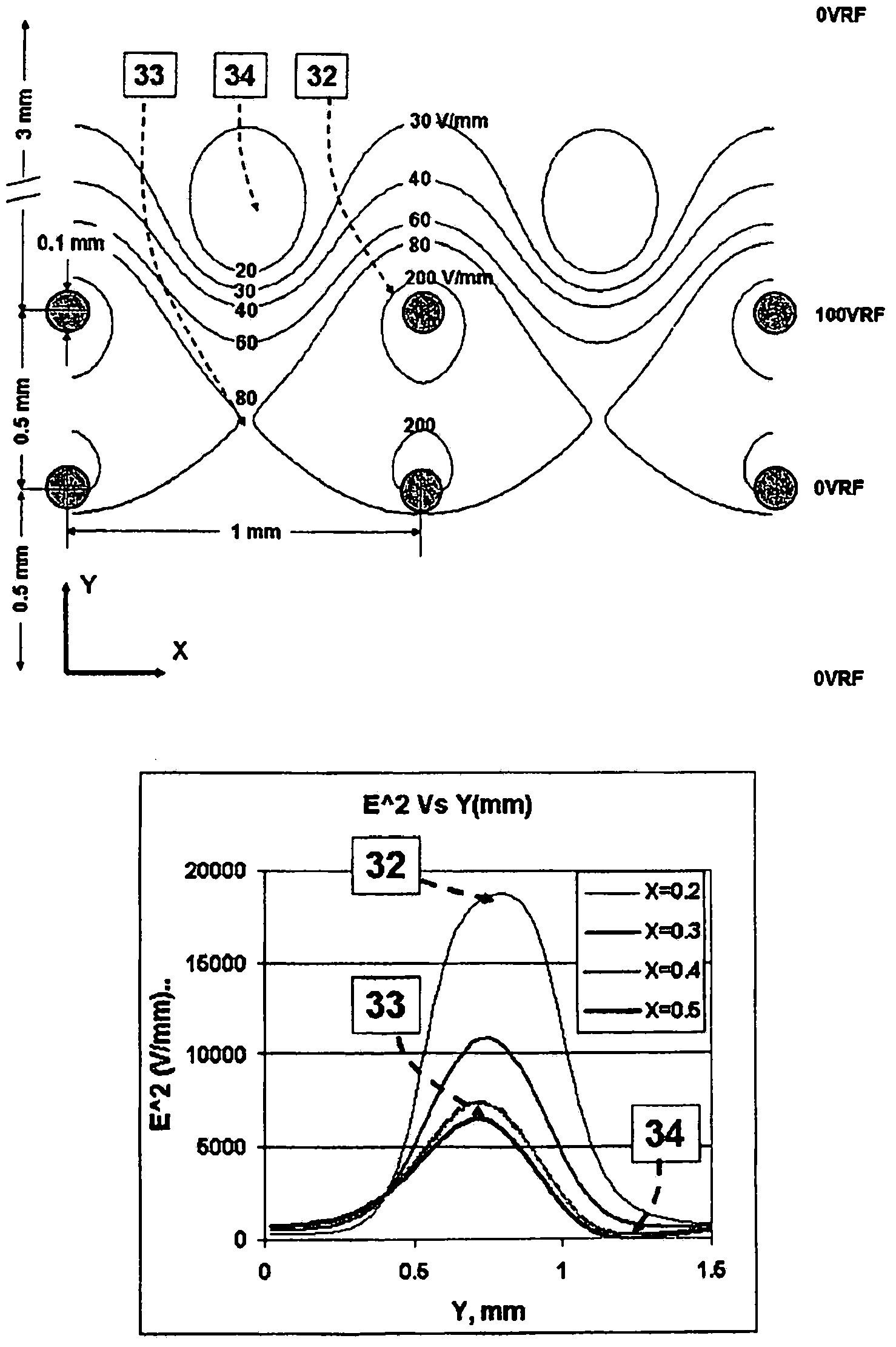

A method and apparatus are disclosed for improving ion mobility spectrometry by using a fast and spatially wide ion gate based on local RF field barrier opposed to a switching DC field. Alternatively, the speed and charge throughput of ion mobility separator are improved by arranging coaxial mobility cell followed by conical coaxial ion channel. The improvement accelerates the ion mobility analysis and improves charge throughput and dynamic range of the IMS. The invention is particularly suited for rapid dual gas chromatography, fast CE. Preferably, the accelerated and wide bore IMS is coupled to a multi-reflecting time-of-flight mass spectrometer with a fast encoded orthogonal acceleration. Speed and sensitivity of IMS with fast pulsing MR-TOF make it practical to arrange analytical methods of comprehensive and orthogonal separation in multiple analytical dimensions.

Owner:LECO CORPORATION

Polymer coated long duration optical memory device and a method for the development thereof

The invention relates to a method for the preparation of a polymer coated long duration optical memory device having applications in ferroelectric liquid crystal materials, the said method comprising the steps of forming patterns of different shapes and configurations on a glass substrate coated with indium tin oxide by lithographic methods to obtain an effective electrode area of at least 5 mm2; depositing an antireflection coating on external surfaces of glass substrates followed by coating the patterned glass substrate with a polymer selected from the polyamide group of nylon 6 / 6 and nylon 6 / 9 in the thickness range of 900 Å-1100 Å; baking the coated substrate followed by hard rubbing of the polymer coated surface; coating one of the substrates with a spacer selected from photoresist having thickness in the range of 1 mum to 3 mum; inserting a ferroelectric liquid crystal material in the space between the coated glass substrates, followed by sealing the sandwiched glass substrates at the periphery; heating and cooling the sandwiched glass substrates; fixing a polariser and an analyser on non conducting surface of each of the respective glass plates, followed by application of electric field across the sandwiched substrates for achieving the stable memory action, by applying an AC and DC field across the device to obtain an optical memory device having a long duration of memory at least one year.

Owner:COUNCIL OF SCI & IND RES

High duty cycle trapping ion mobility spectrometer

ActiveCN105869980AElectron/ion optical arrangementsMaterial analysis by electric/magnetic meansElectrical field strengthTrapping

The invention provides a trapping ion mobility analyzer and methods for operating the ion mobility analyzer. The trapping ion mobility analyzer comprises an RF field for radially confining ions along an axis, a region with an axial electric DC field and a gas flow along the axis counteracting the electric DC field in the region, wherein the region either comprises a rising edge with an increasing axial electric DC field or a falling edge with a decreasing axial electric DC field and wherein the slope of the electric field strength along the axis is not constant at a substantial portion of the edge.

Owner:브루커달토닉스게엠베하&씨오케이지

Ion mobility spectrometer

InactiveCN104067116AStability-of-path spectrometersComponent separationTime-of-flight mass spectrometryIon-mobility spectrometry

A method and apparatus are disclosed for improving ion mobility spectrometry by using a fast and spatially wide ion gate based on local RF field barrier opposed to a switching DC field. The improvement accelerates the ion mobility analysis and improves charge throughput and dynamic range of the IMS. The invention is particularly suited for rapid dual gas chromatography. In one important embodiment, the accelerated IMS is coupled to a multi- reflecting time-of-flight mass spectrometer with a fast encoded orthogonal acceleration. There are described methods of comprehensive and orthogonal separation in multiple analytical dimensions.

Owner:LECO CORPORATION

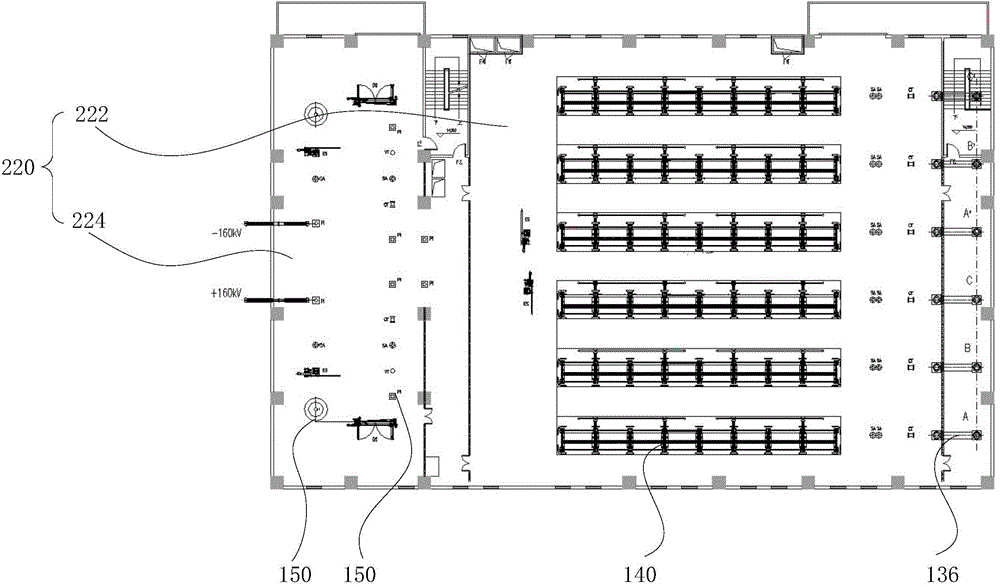

Flexible DC converter station

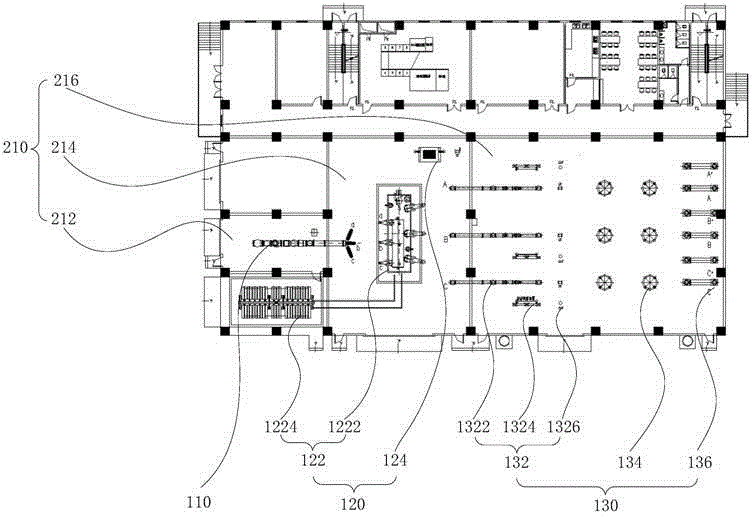

ActiveCN103956763AImprove environmental friendlinessReduce electromagnetic pollutionSubstation/switching arrangement cooling/ventilationElectric power transfer ac networkElectrical devicesEngineering

A flexible DC converter station comprises an AC / DC power distribution device and an AC / DC power distribution device chamber used for arranging the AC / DC power distribution device. The AC / DC power distribution device chamber is formed by arranging a first chamber body and a second chamber body in a stacked mode. The AC / DC power distribution device comprises an AC GIS power distribution device unit, a coupling transformer unit, a starting loop and valve reactor unit, a converter valve unit and a DC field unit. The function division of the all-indoor flexible DC converter station is definite and reasonable, operation and maintenance are convenient, space is utilized to the maximum degree, the land utilization rate is increased, and land occupation is reduced. Because all devices of the converter station are arranged indoors, on the basis of meeting the requirements for safety and reliability, the influences on the electrical devices by the external environment are effectively reduced, the reliability and the safety of the converter station of the electrical devices are improved, the manufacturing difficulty of the electrical devices is lowered, and cost is cut down.

Owner:CHINA ENERGY ENG GRP GUANGDONG ELECTRIC POWER DESIGN INST CO LTD

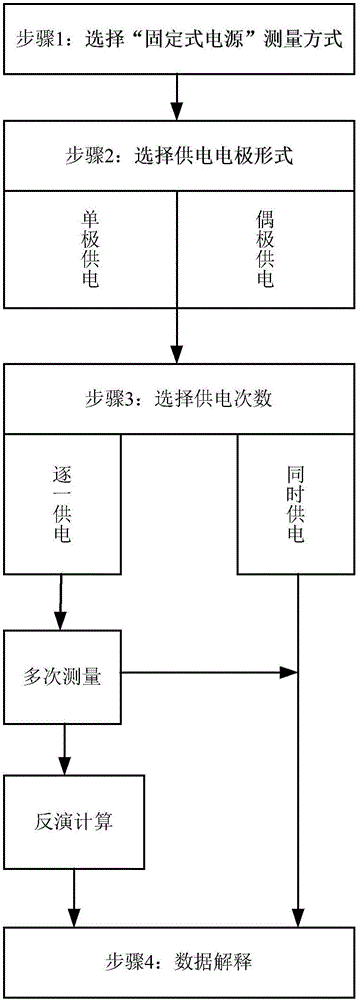

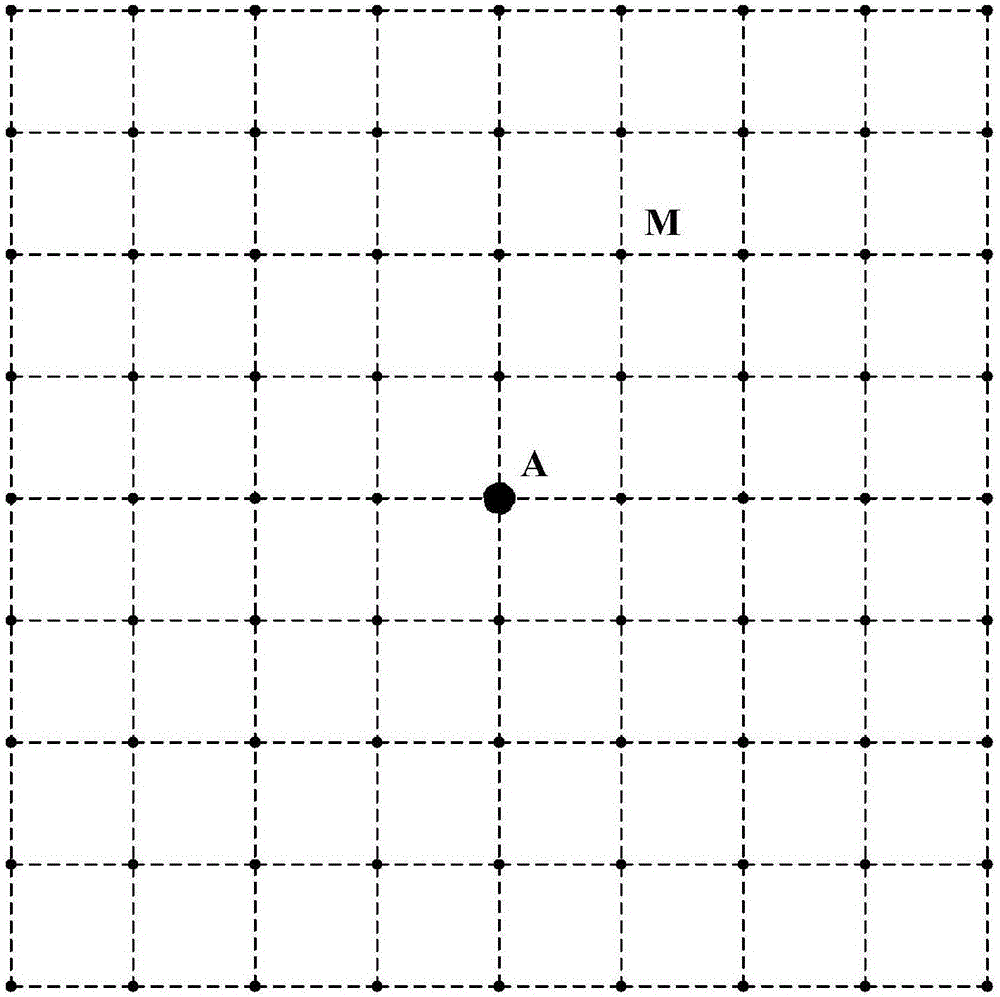

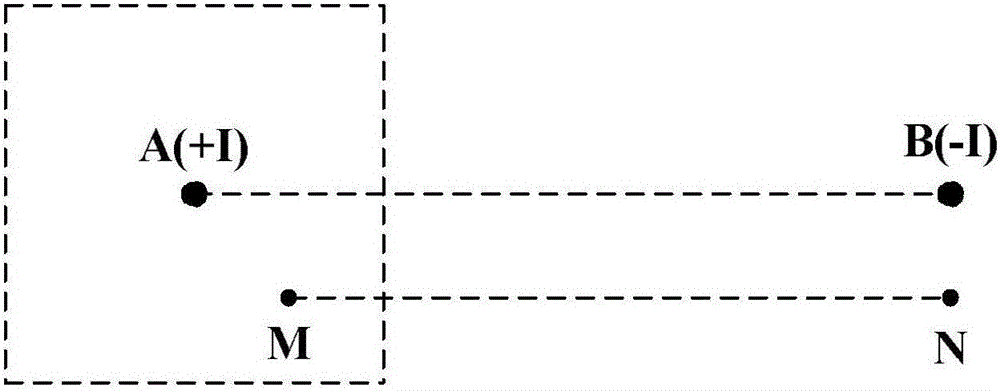

DC field fixed-type power exploration method

InactiveCN106125143AImprove the efficiency of field exploration workImprove stabilityElectric/magnetic detectionAcoustic wave reradiationMeasurement pointDc field

The invention belongs to the technical field of geophysical prospecting, and in particular relates to a direct current field fixed power source prospecting method. A. Determine the grid pattern measurement network, each network point on the measurement network is a measurement point position, place the power supply electrode at one or more measurement point positions, and place the measurement electrode at other measurement point positions except the power supply electrode. At the position of the measuring point; B. Supply power to the power supply electrode, obtain a set of measurement data through the measurement electrode, and analyze the data. The advantage is: fix the power supply electrodes at one or several arbitrary test positions, and supply power one by one or at the same time, then other electrodes are used as measurement electrodes, and all the measurement work can be completed by only measuring once or a few times, thus improving field testing. Exploration work efficiency and measurement data stability.

Owner:INST OF GEOCHEM CHINESE ACADEMY OF SCI

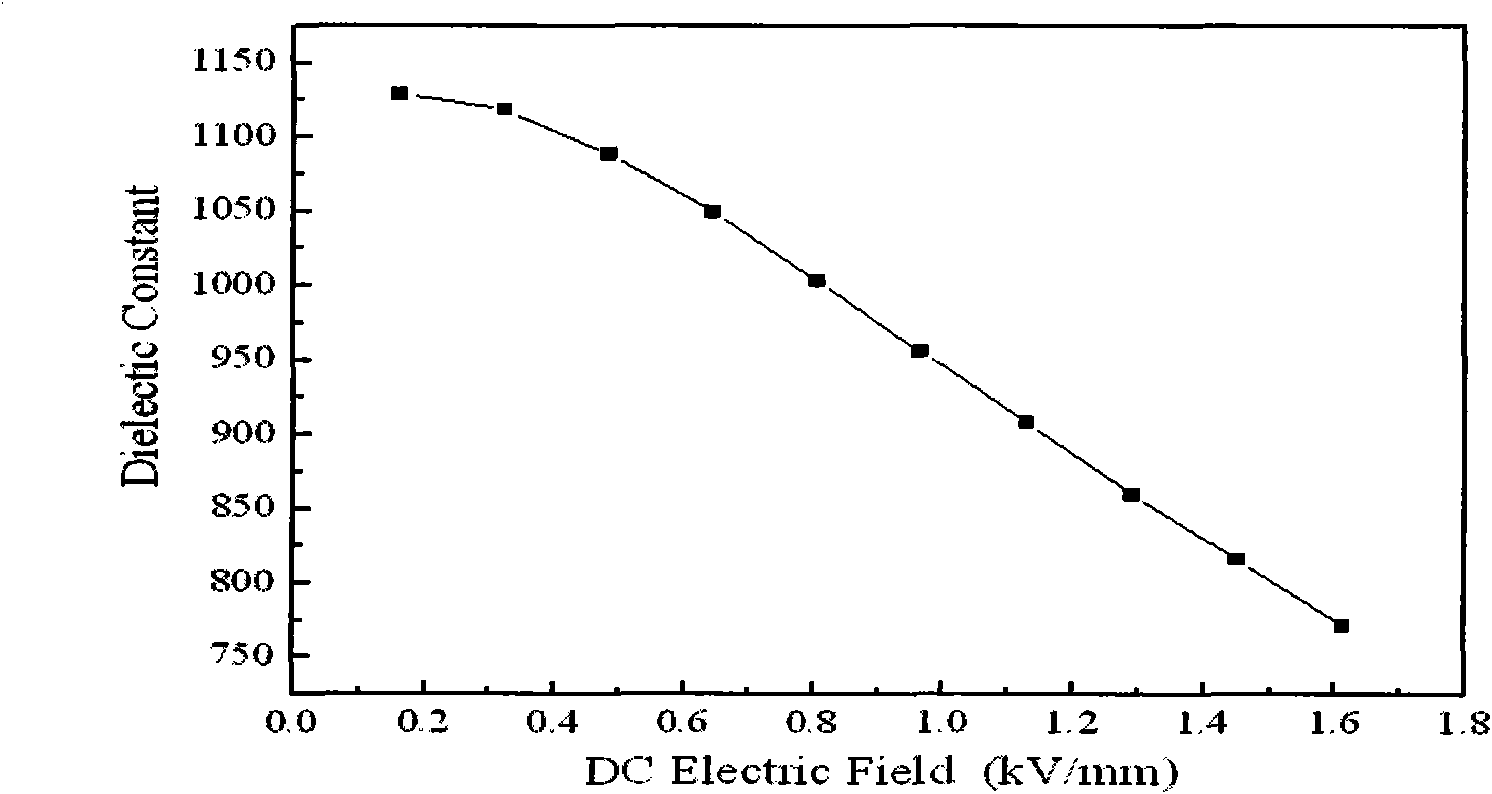

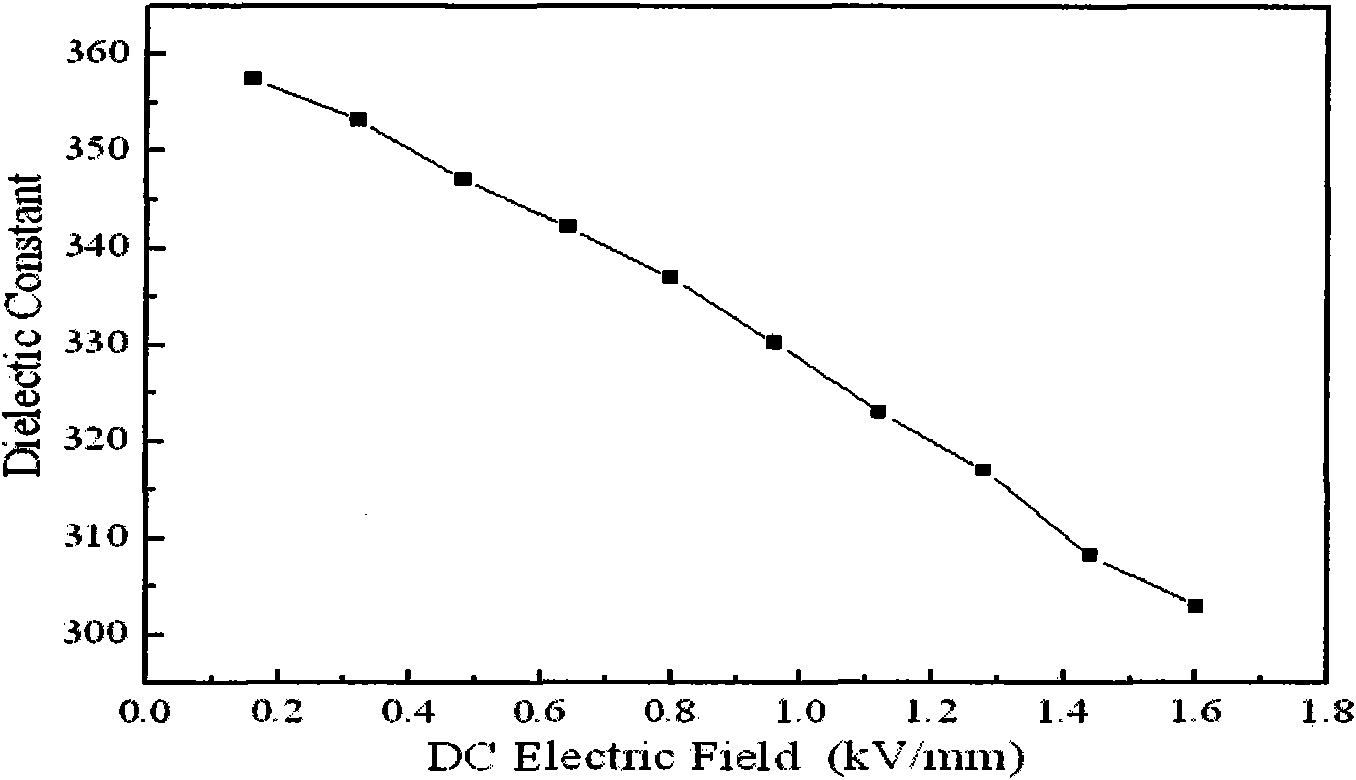

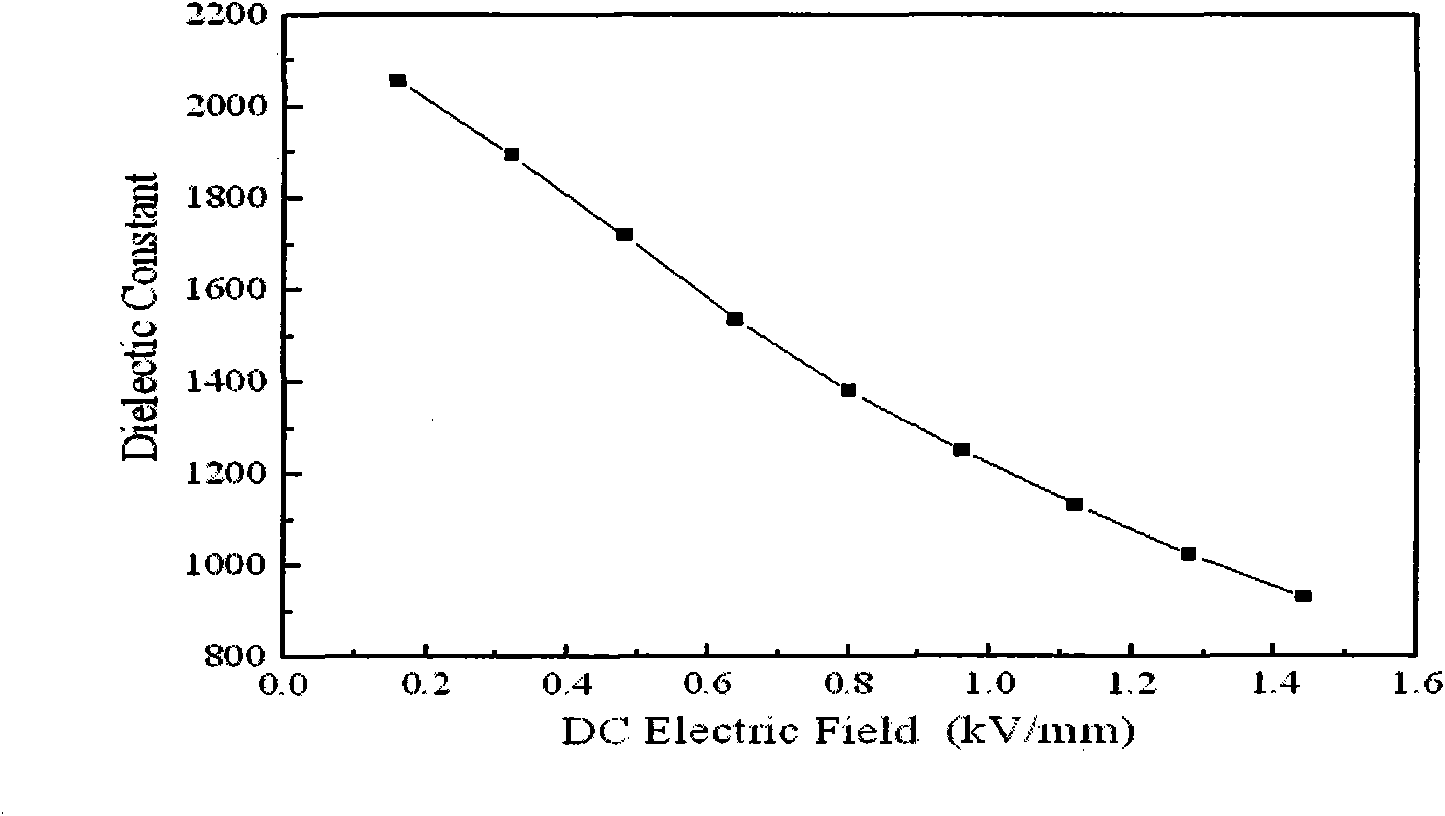

Composite barium strontium titanate ceramics and preparation method thereof

ActiveCN101844919AMeet the use requirementsHigh application potentialBarium strontium titanateDielectric loss

The invention relates to high-tunability composite barium strontium titanate ceramics. Ba0.6Sr0.4TiO3 which is prepared by analytical pure BaCO3, SrCO3 and TiO2 is taken as a matrix material, and analytical pure 0.5-5wt% of ZnO, 10-30wt % of A12O3 and 10wt% of MgO are compositely added to obtain an oxide compositely doped Ba0.6Sr0.4TiO3 powder body by ball milling, drying and presintering; and 5-10wt% of PVA is added to be granulated and formed by pressing, and a ceramic material with 18% to 42% of adjustability is obtained after sintering. The invention has lower dielectric constant and dielectric loss, realizes the substantial adjustability of dielectric constant under low DC field strength, can meet the use requirements of a phase shifter, a dynamic random access memory and other devices for adjustable materials, improves the work efficiency of such devices, and has stable and reliable preparation process.

Owner:山东煜辉电子科技有限责任公司

Method for separating multichannel signals produced by ac and DC sources from one another

ActiveUS20090069661A1Remove distortionEliminate disadvantagesDigital variable/waveform displayDiagnostic recording/measuringPower flowMeasuring instrument

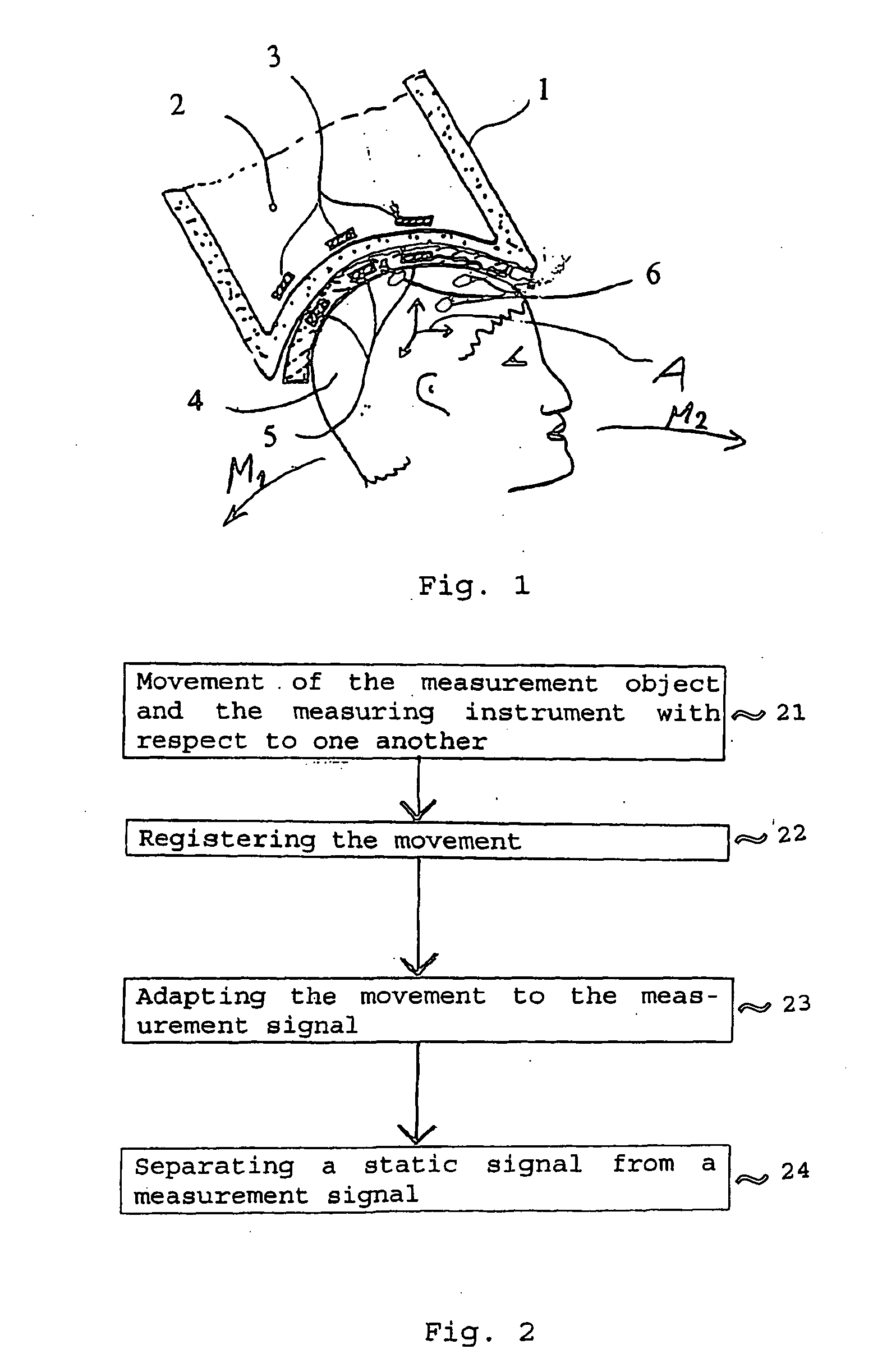

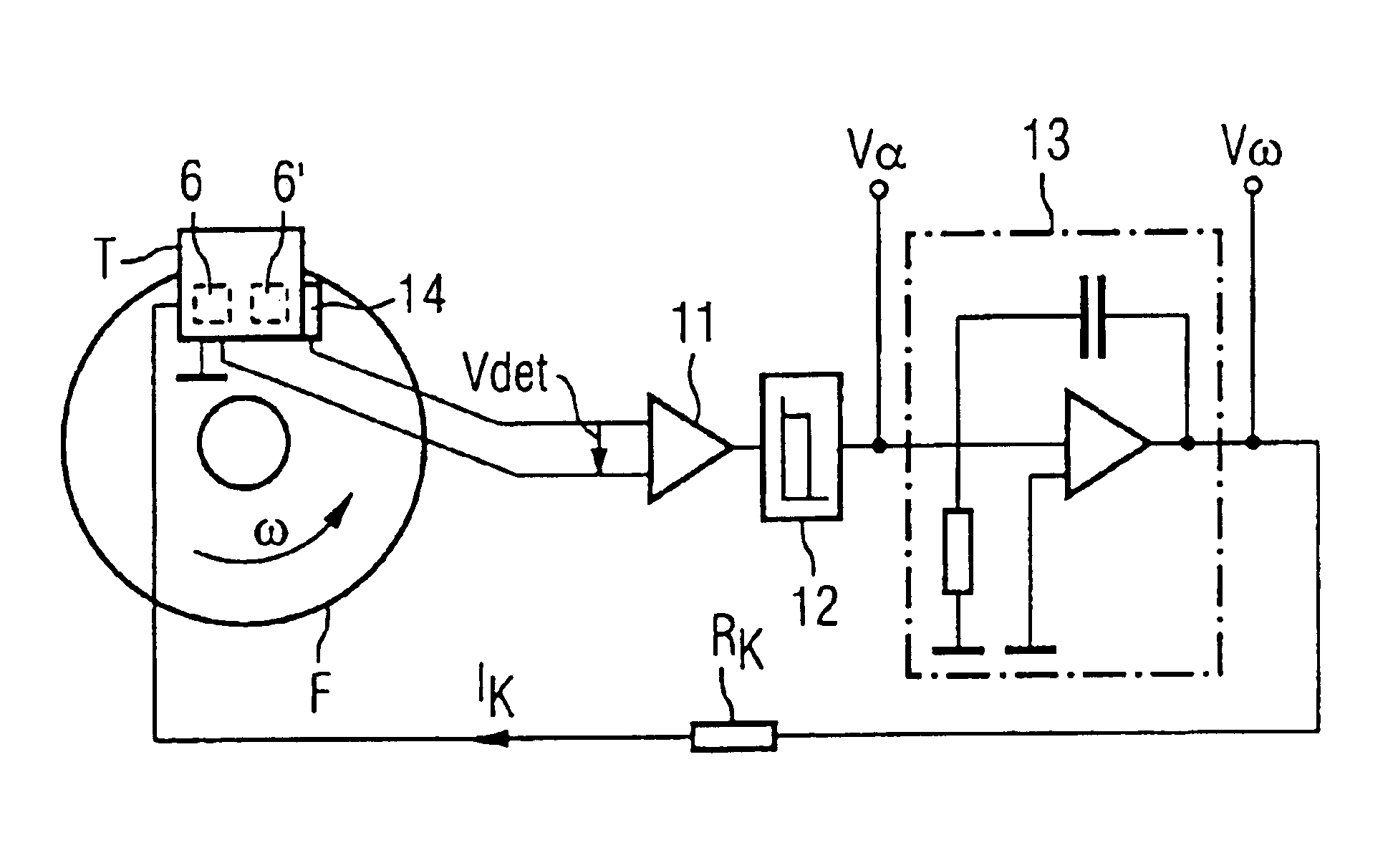

The present invention relates to a novel manner of measuring DC fields using a multi-channel MEG or MKG measuring instrument; and on the other hand, to a manner of eliminating from the measurement result the interference signals caused by the DC currents. The invention combines the monitoring system of a testee's movement and the method for motion correction of the measured signals so that the signals produced by the DC currents of a moving testee's are visible in the final measurement result as a static signal component in a conventional MEG or MKG measurement. In that case, in the measurement, it is not necessary to beforehand prepare oneself for measuring the DC fields.

Owner:MEGIN OY

Circuit arrangement for evaluating an acceleration sensor using the Ferraris principle

InactiveUS6848308B2Wide speed rangeLower ratioAcceleration measurement using interia forcesDevices using electric/magnetic meansControl signalClassical mechanics

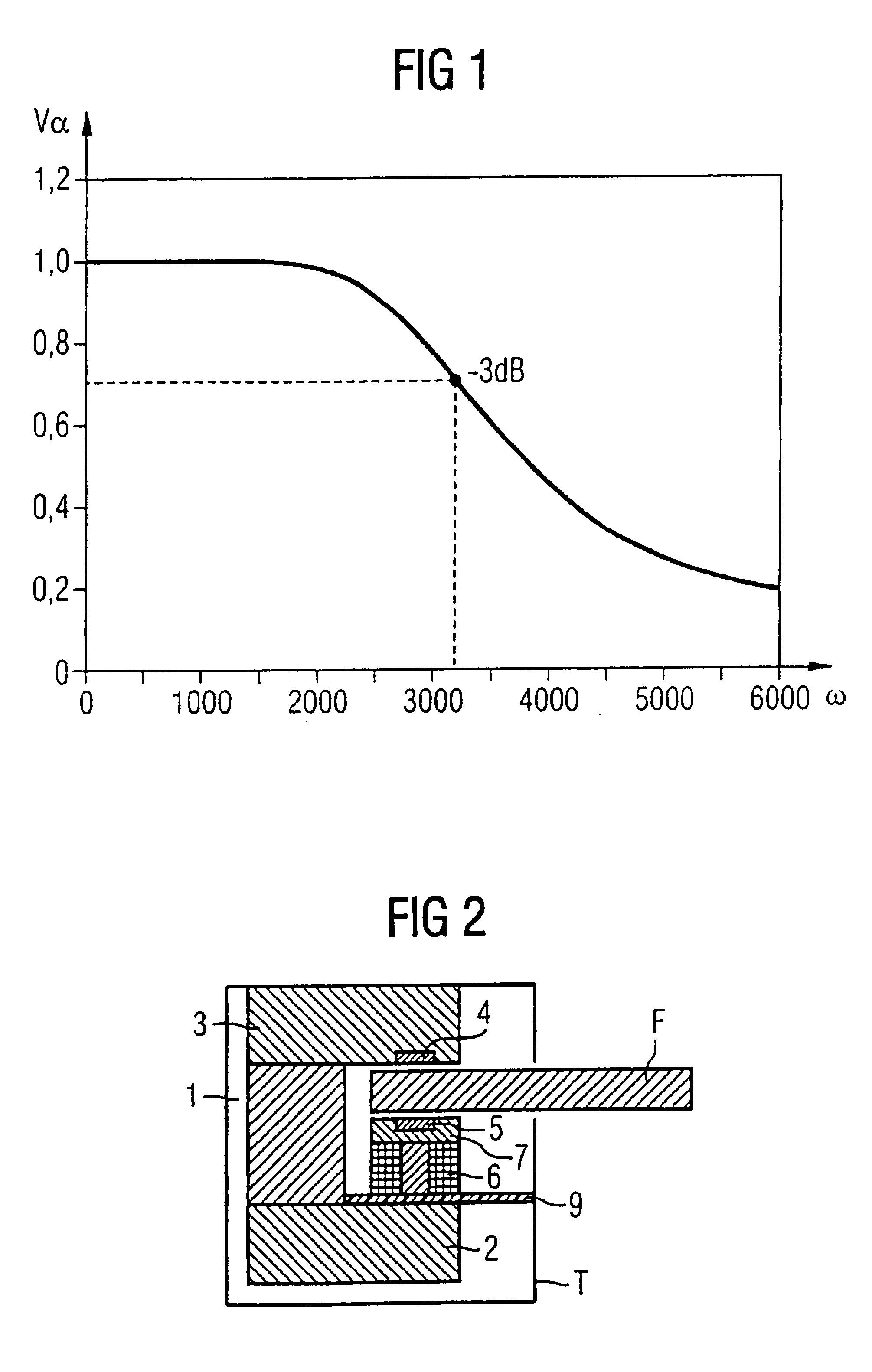

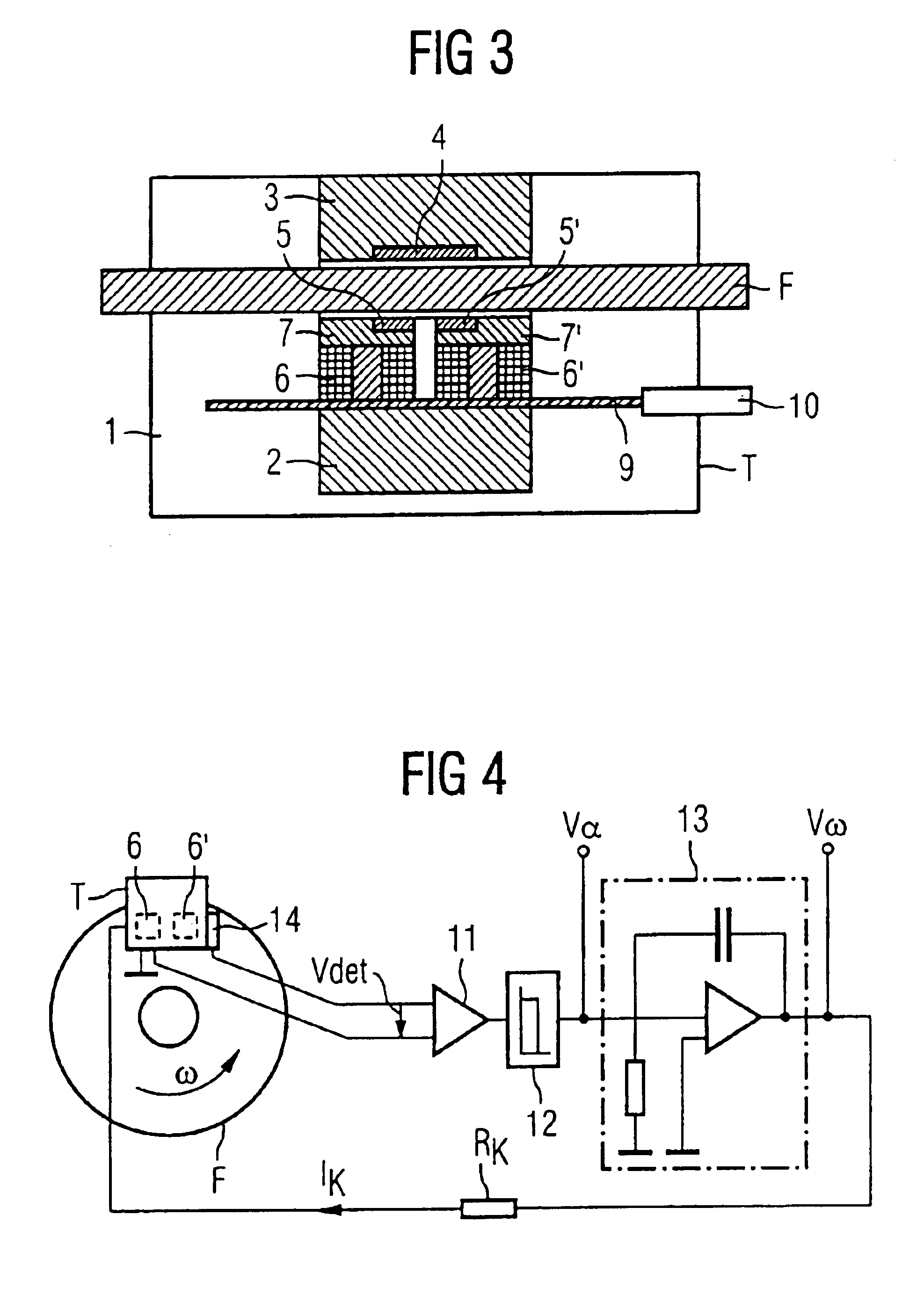

In order to compensate for a drop in sensitivity at high rotational speeds, an acceleration sensor having an inductive measuring head (T) which cooperates with a moving Ferraris disk (F) essentially over a main magnetic field and which supplies an acceleration-dependent variable (Vdet; Vα) is expanded by an additional DC magnetic field excitation circuit (13, 14, IK, RK) with a means for driving the latter with the effect that the additional DC magnetic field acts in a compensating fashion on an eddy-current DC field, starting from a relatively high rotational speed (ω) of the Ferraris disk (F). This can be performed by amplifying the main magnetic field or by reducing the eddy-current DC field. A control signal (Vω), dependent on rotational speed, which both can be generated outside the sensor via a characteristic curve, and can be derived in the form of a control loop from the sensor signal (Vα), serves as a drive.

Owner:SIEMENS AG