Patents

Literature

33results about How to "Effective mass reduction" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

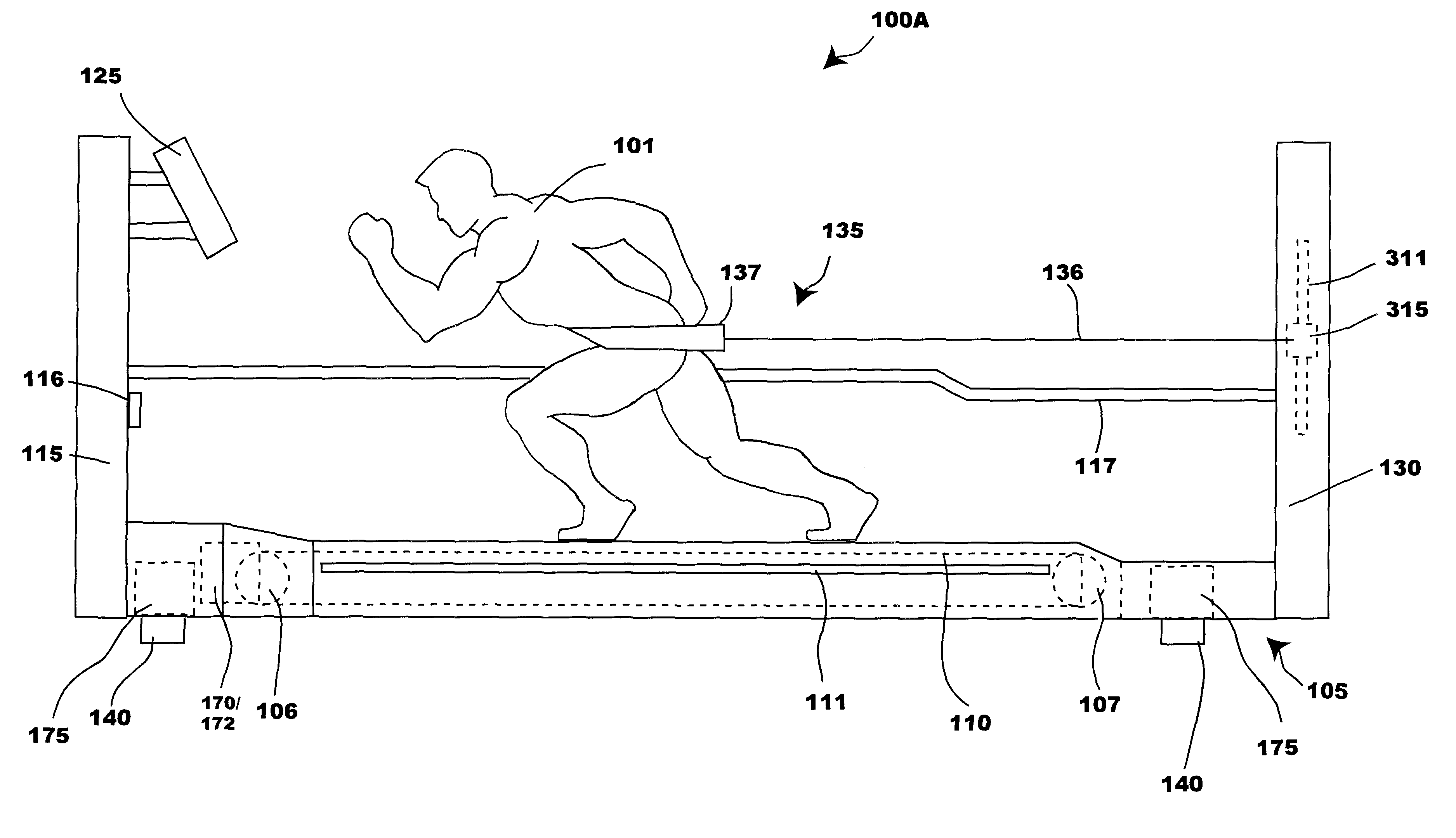

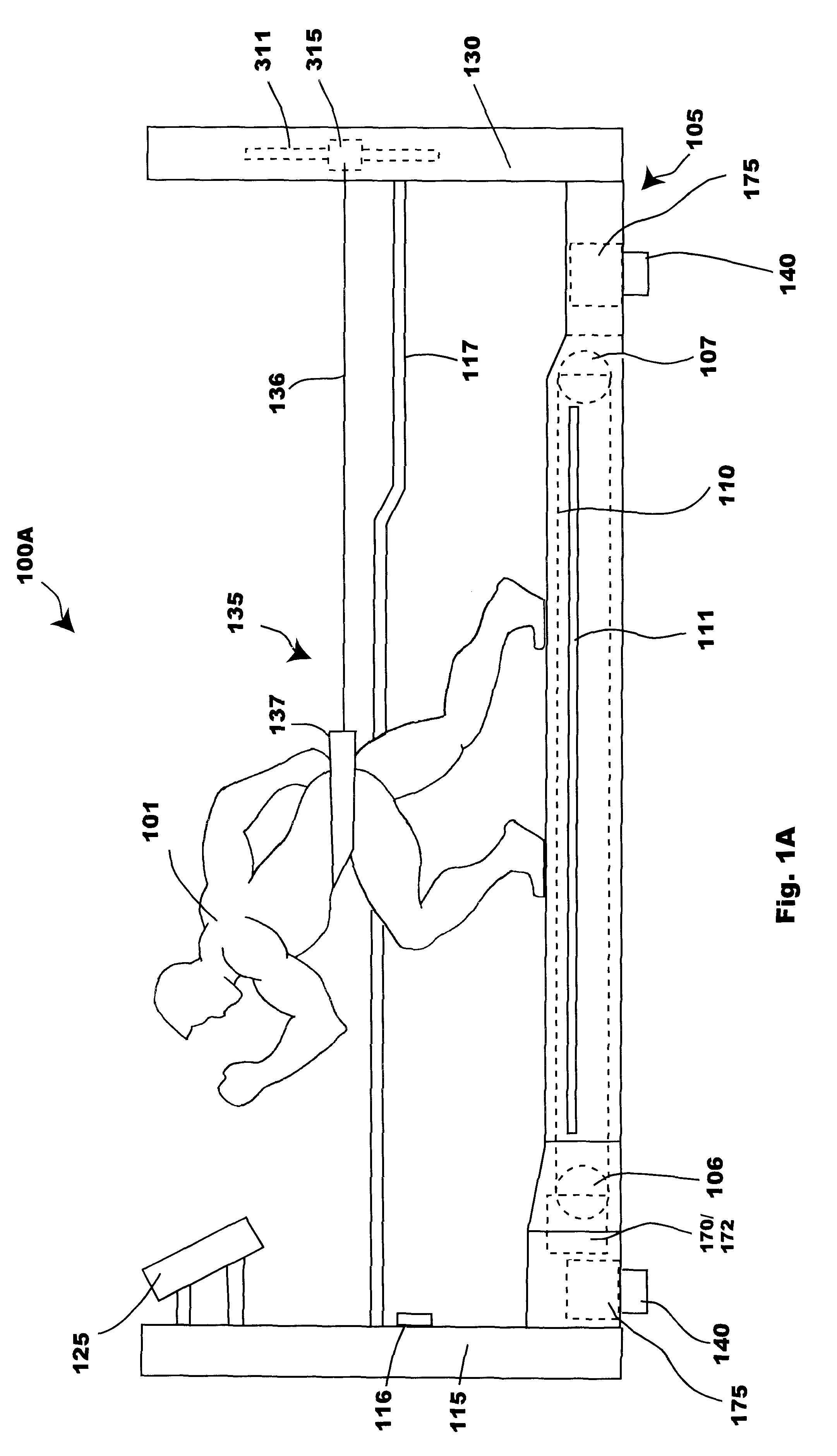

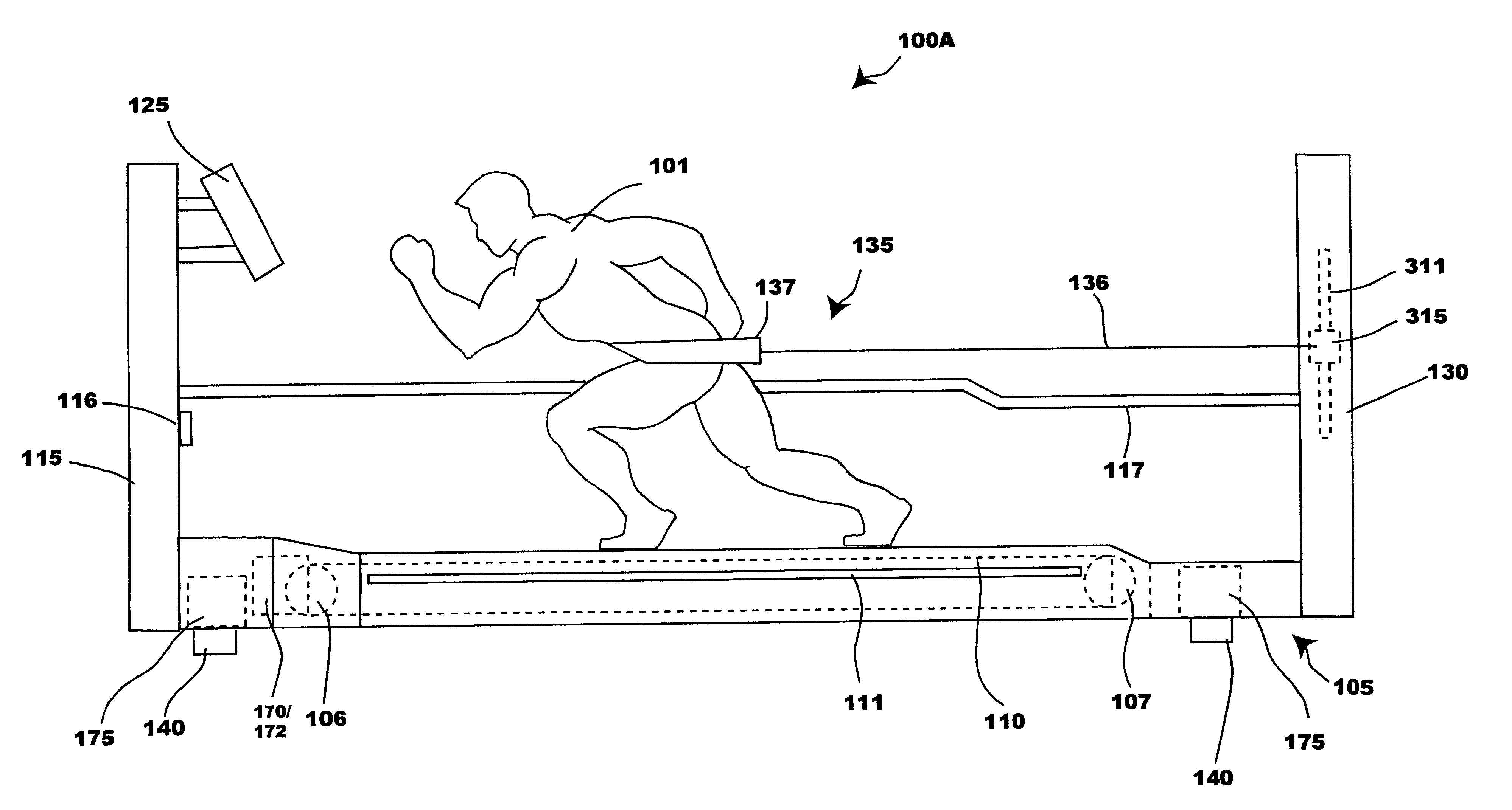

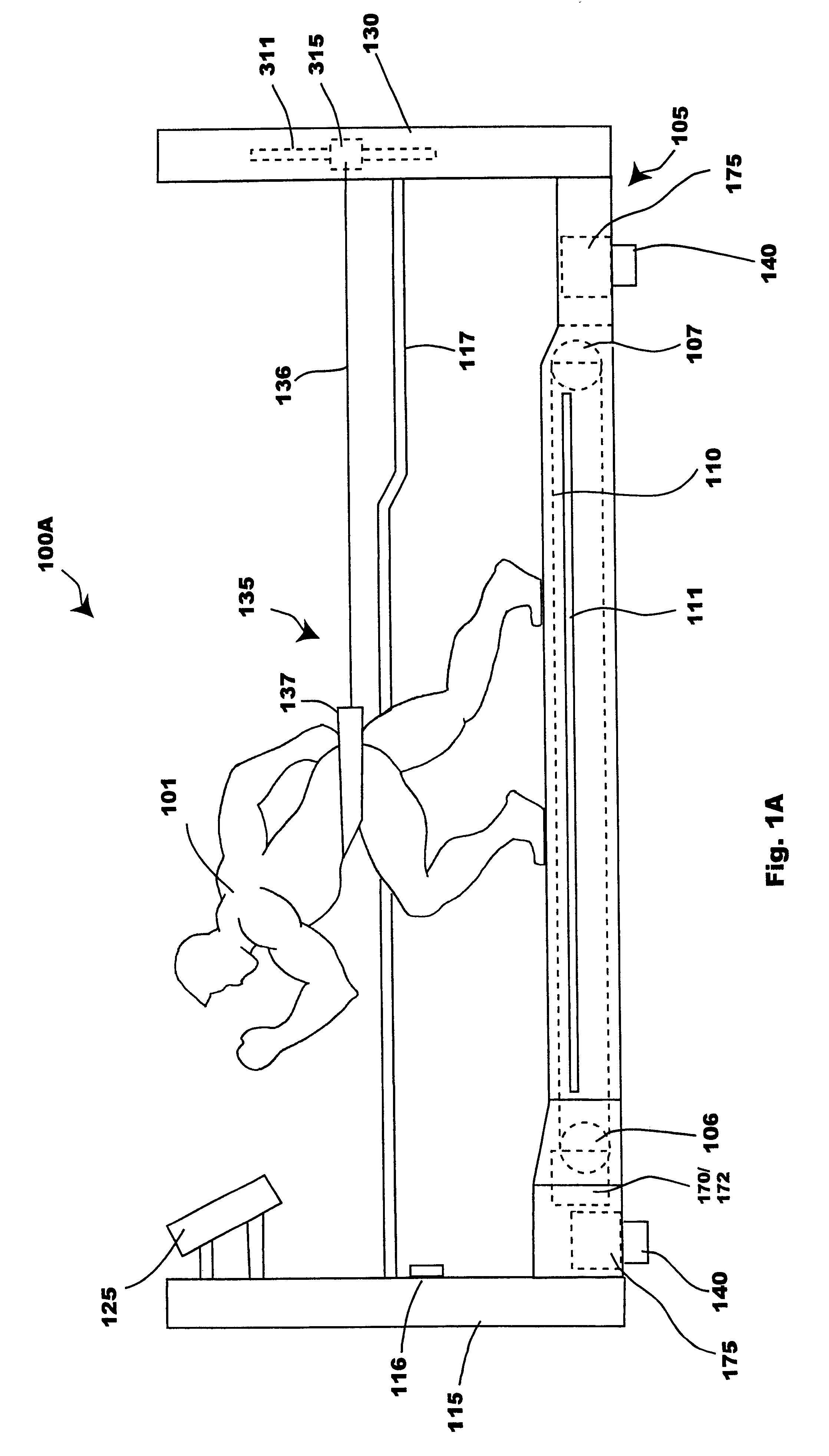

Bipedal locomotion training and performance evaluation device and method

InactiveUS6454679B1Effective mass reductionTherapy exerciseMovement coordination devicesExercise performanceForce velocity

A bipedal locomotion exercise and performance evaluation apparatus including a revolving belt, a harness for securing the position of a subject on the belt, a harness-force measuring means, and a belt volocity monitoring and controlling means. The harness may be secured on various points of a subject and includes push / pull engagement means. An overhead harness may be used to reduce effective body mass. The velocity of the belt may be controlled by a unidirectional or bidirectional motor / brake system. Velocity of the belt may also be controlled by a brake only. A digital processor may be used to control the motor and / or brake as a function of the forces applied allowing multiple operating modes. Recording of velocity and force as functions of time facilitates analysis of exercise performance. The apparatus allows exertions throughout the first quadrant of a force-velocity-duration space, and outside that first quadrant.

Owner:RADOW SCOTT BRIAN

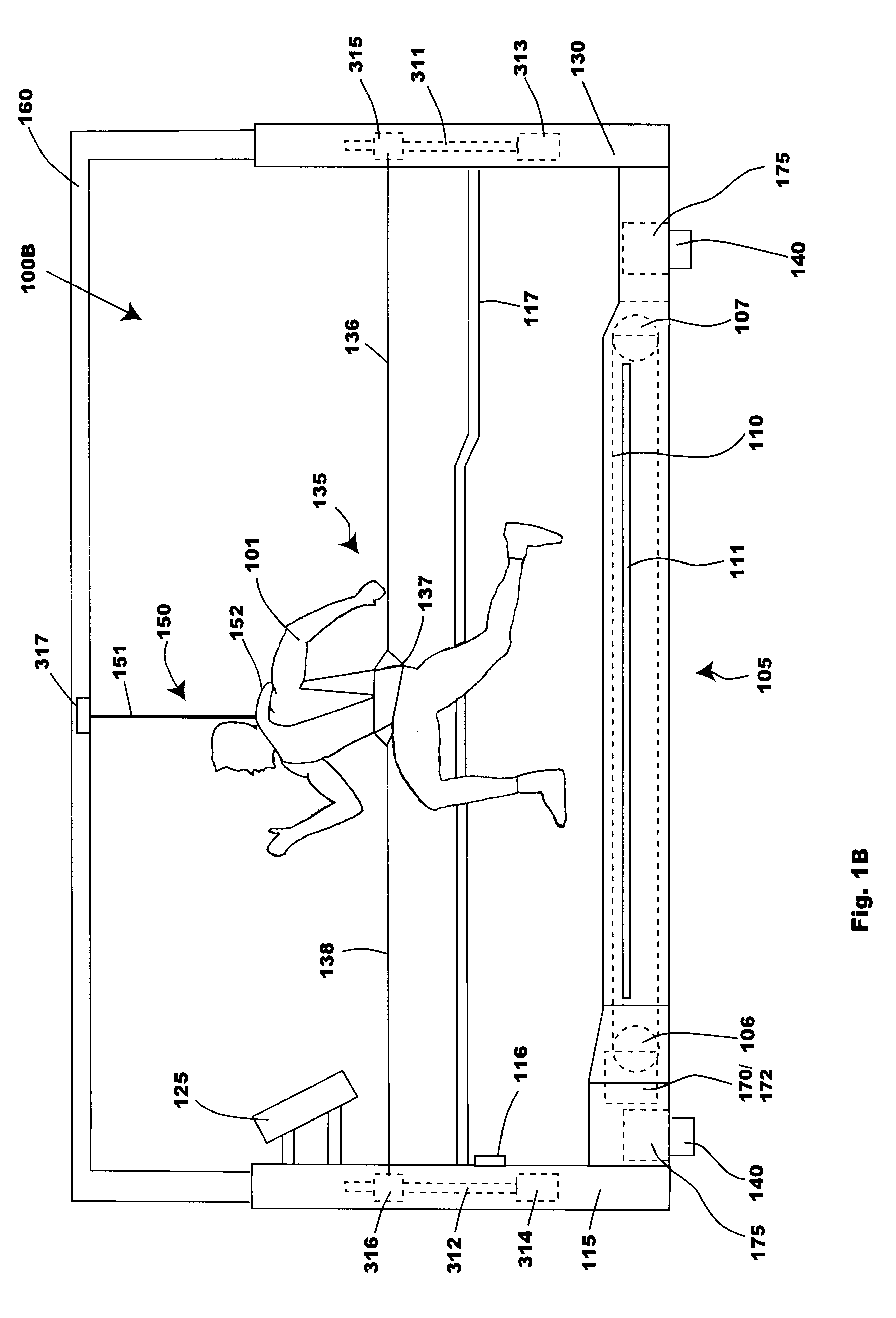

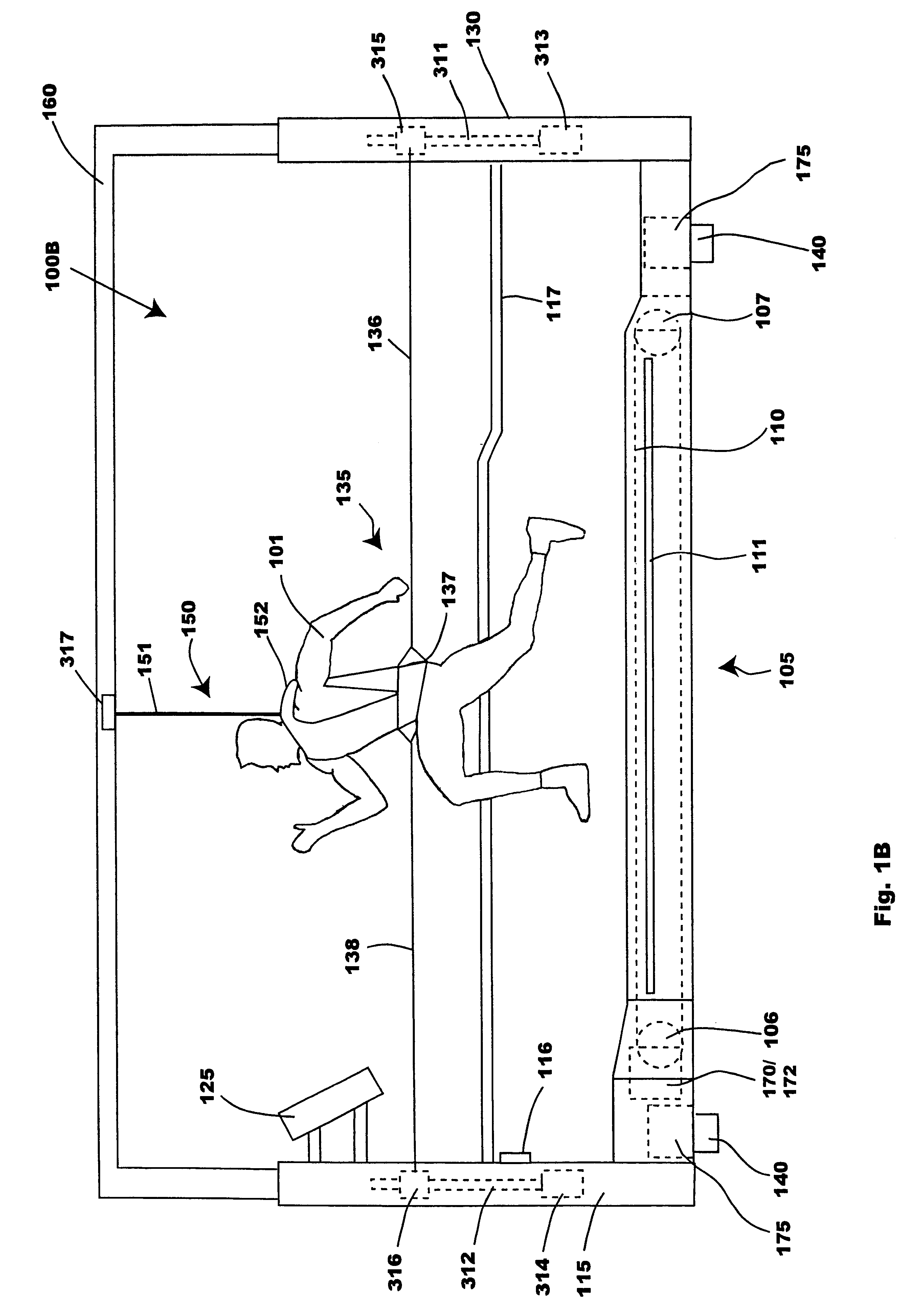

Bipedal locomotion training and performance evaluation device and method

InactiveUS6676569B1Effective mass reductionTherapy exerciseMovement coordination devicesForce velocityEngineering

An exercise and performance evaluation apparatus including a revolving belt or other engagement surface on which a subject can perform forward, backward, or sideways bipedal locomotion or other exercise movement, a means for securing the position of the subject relative to the frame of the apparatus, a means for measuring the force applied by the subject to the engagement surface, and a means for monitoring and / or controlling the velocity of the engagement surface. Securing the subject relative to the frame of the apparatus facilitates monitoring velocity as a function of time. Processing of velocity and force as a function of time allows for recording and analysis of data such as the maximal exertion force-velocity curve. Force-velocity-duration data for exertions is analyzed in terms of an intensity function. The apparatus allows exertions to be performed throughout, and outside, the first quadrant of a force-velocity-duration space.

Owner:RADOW SCOTT BRIAN

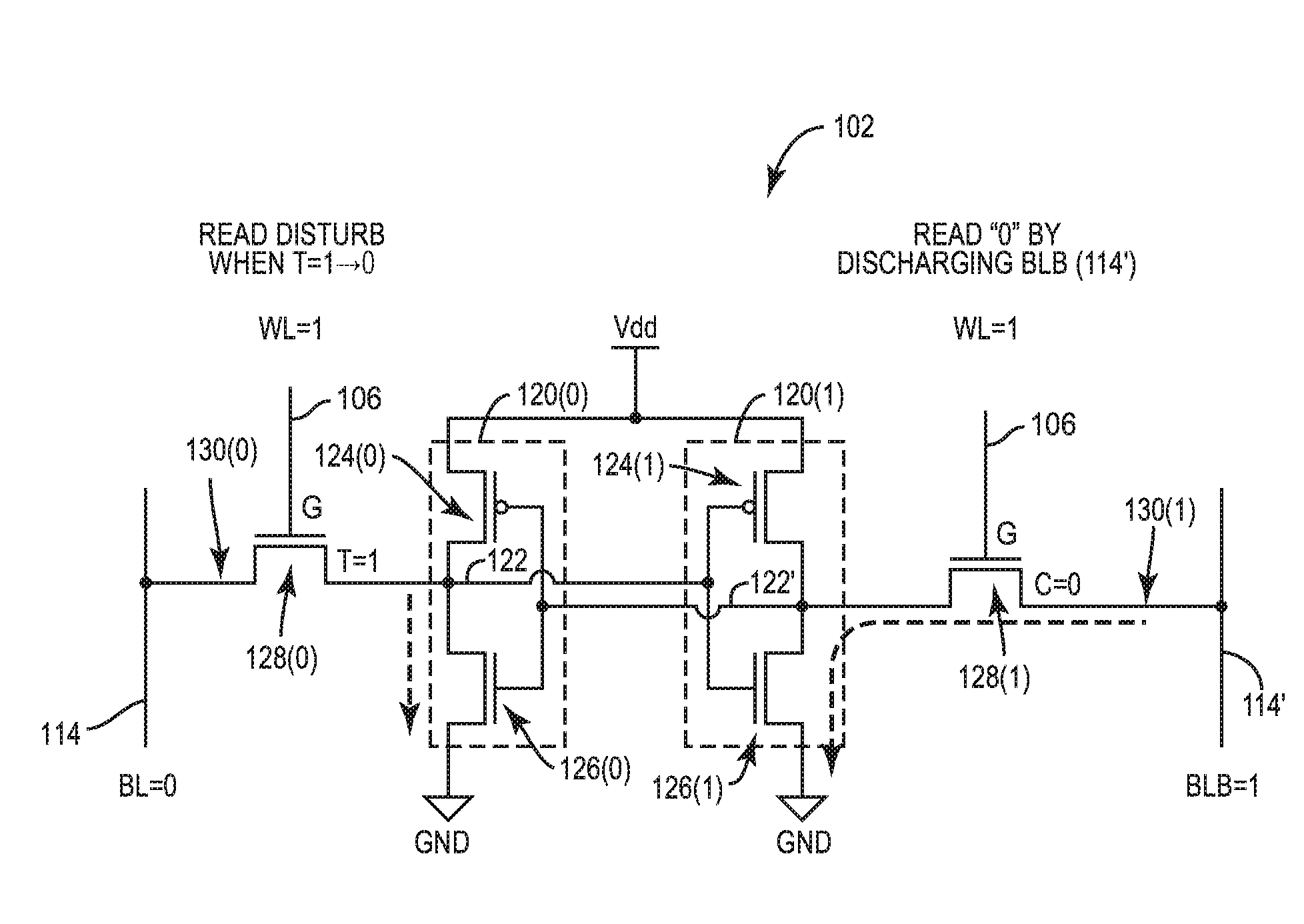

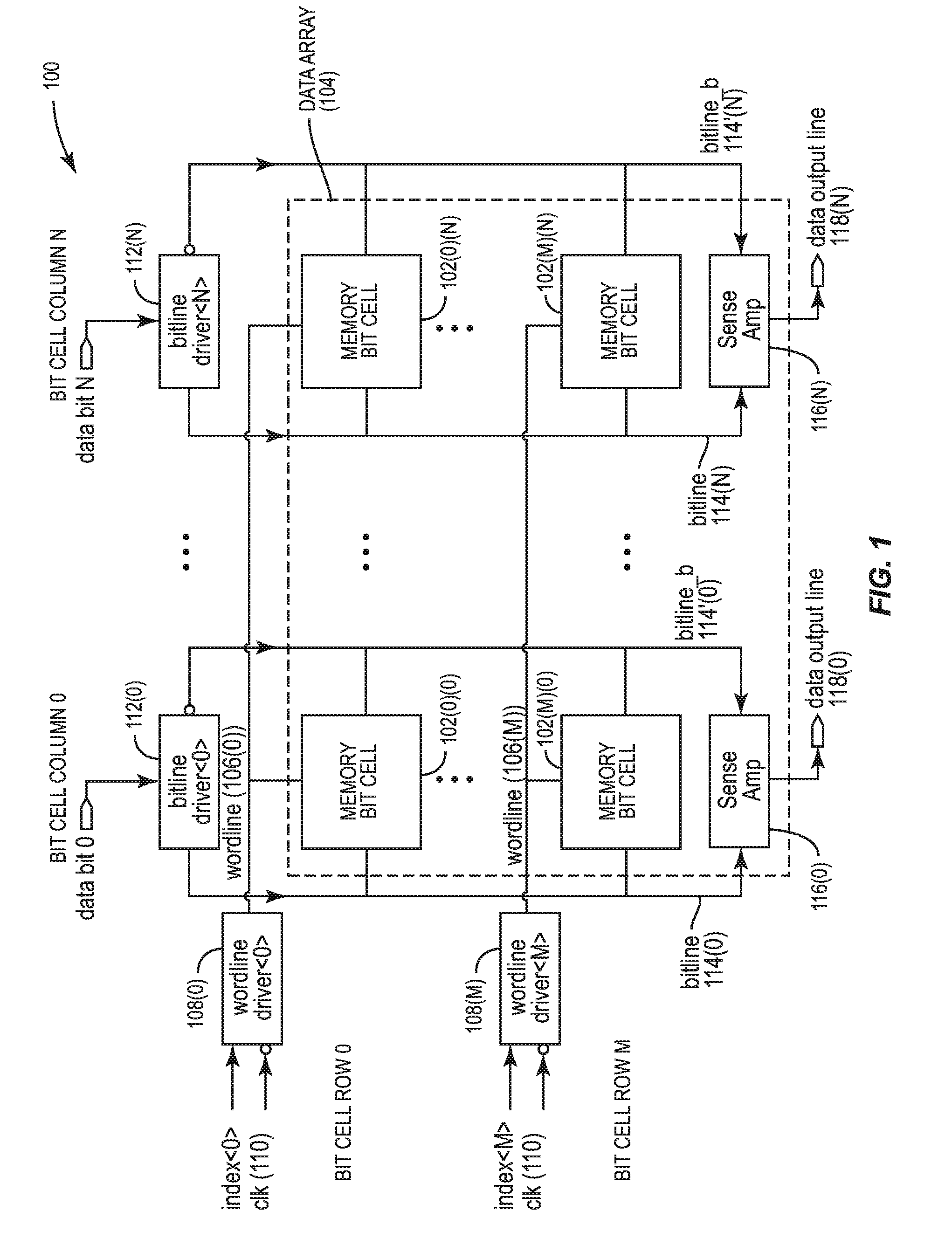

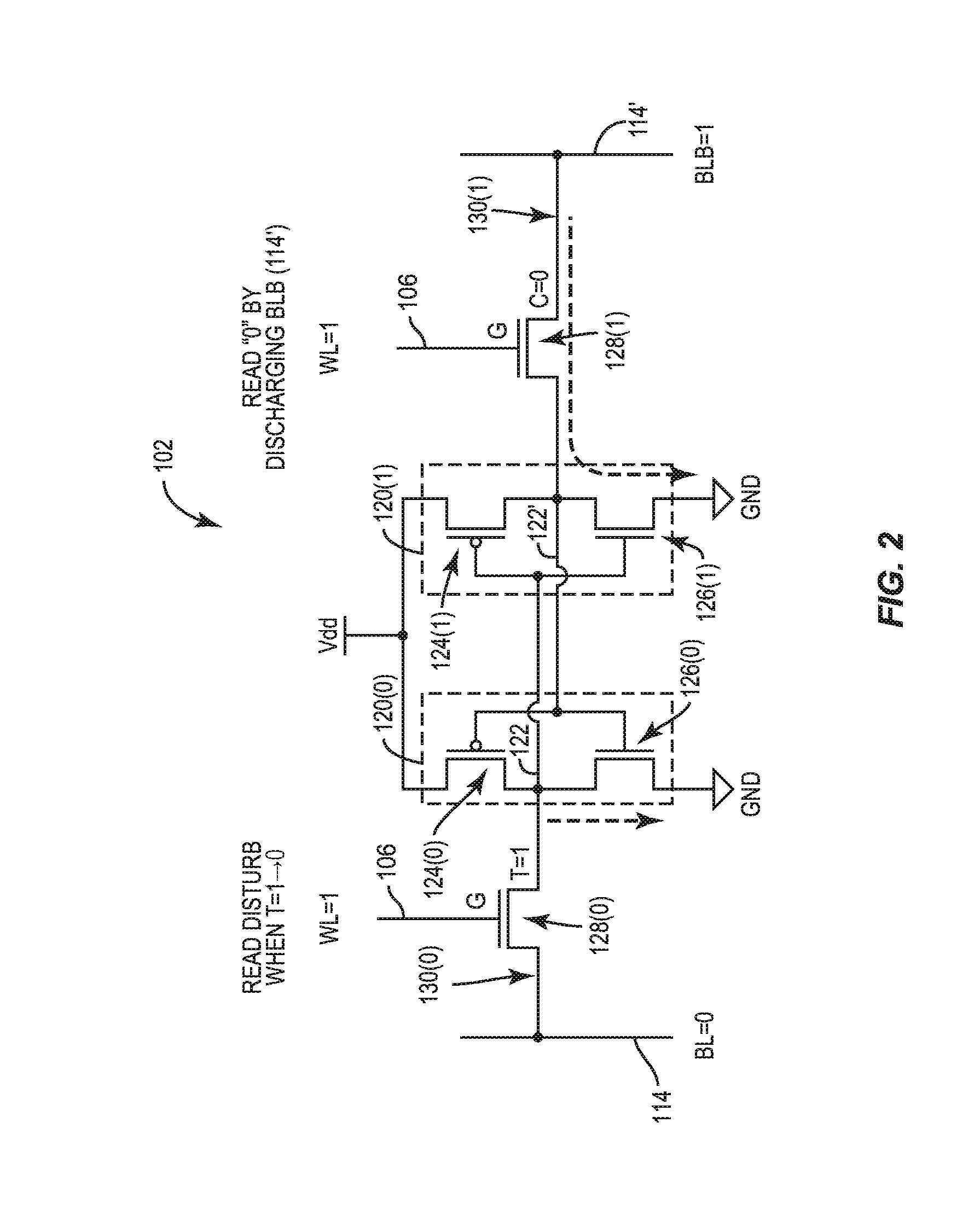

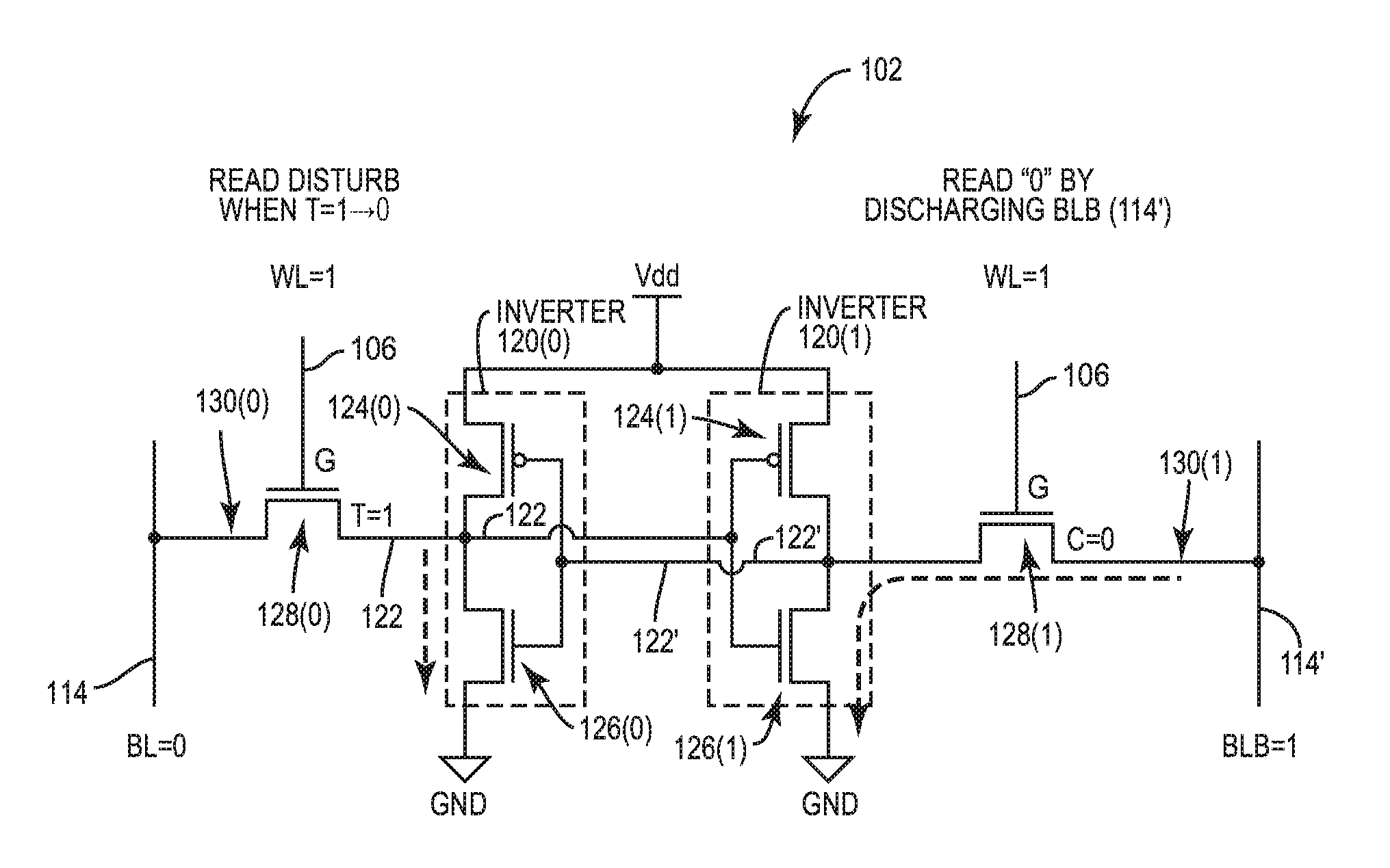

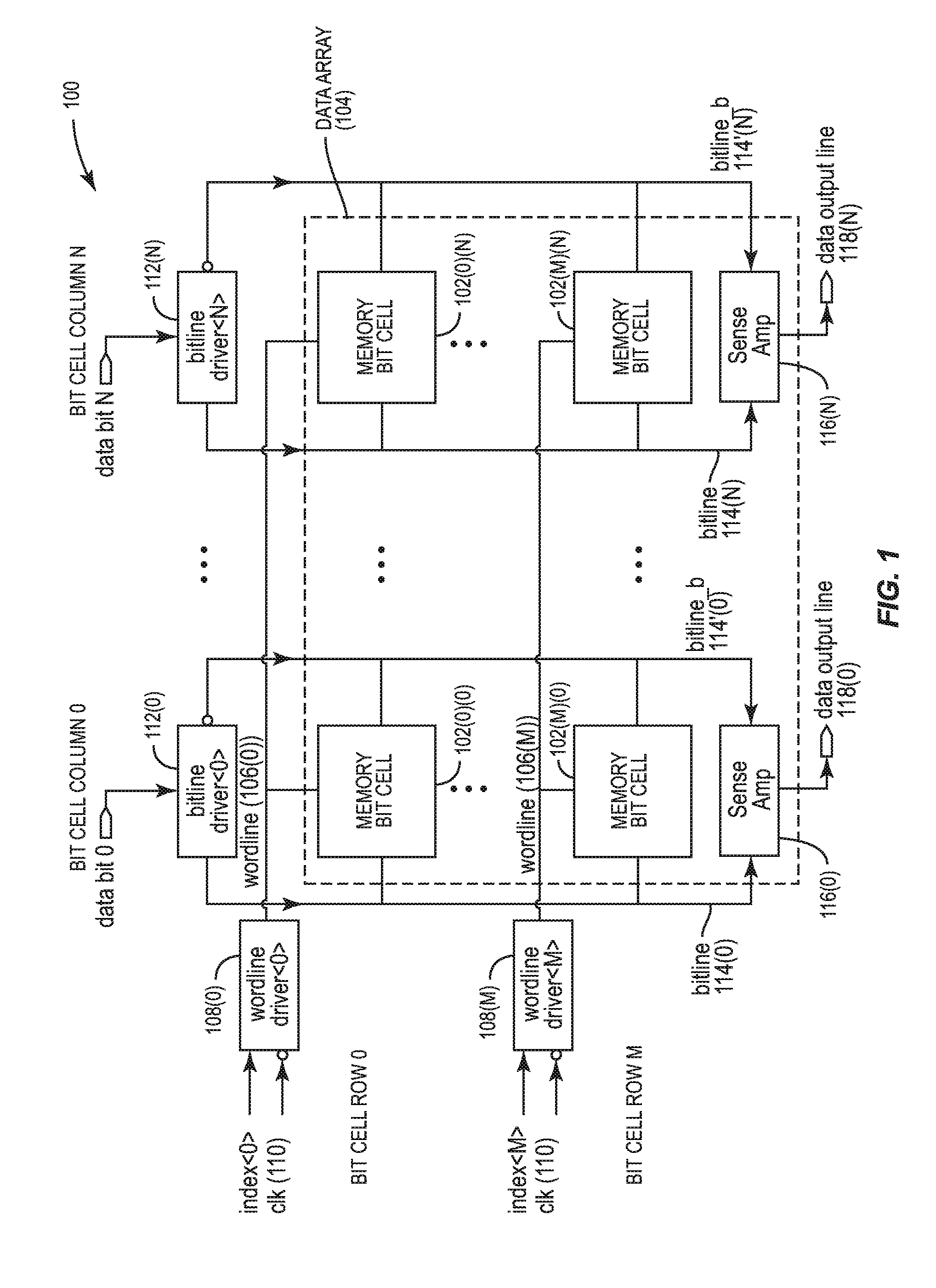

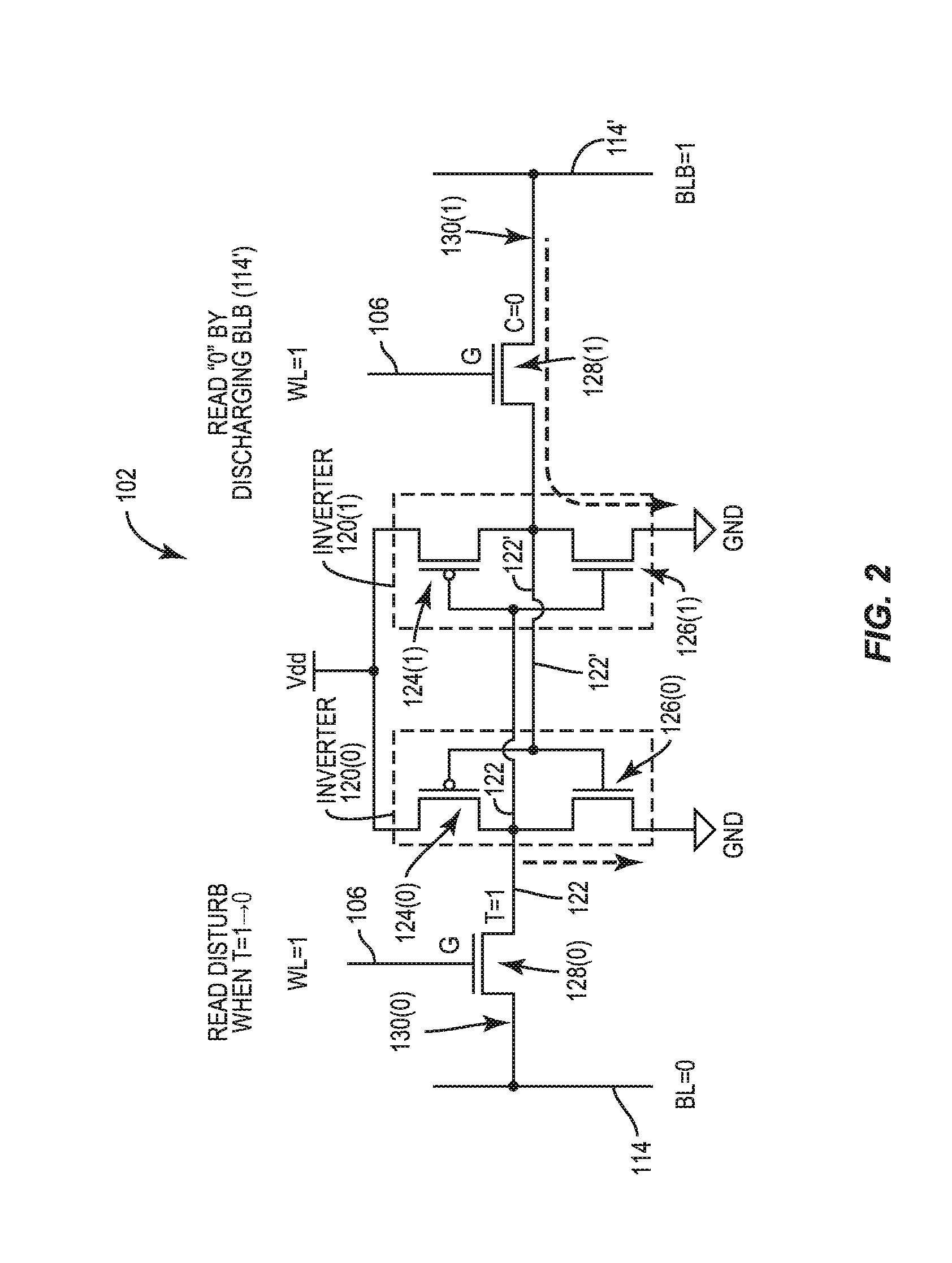

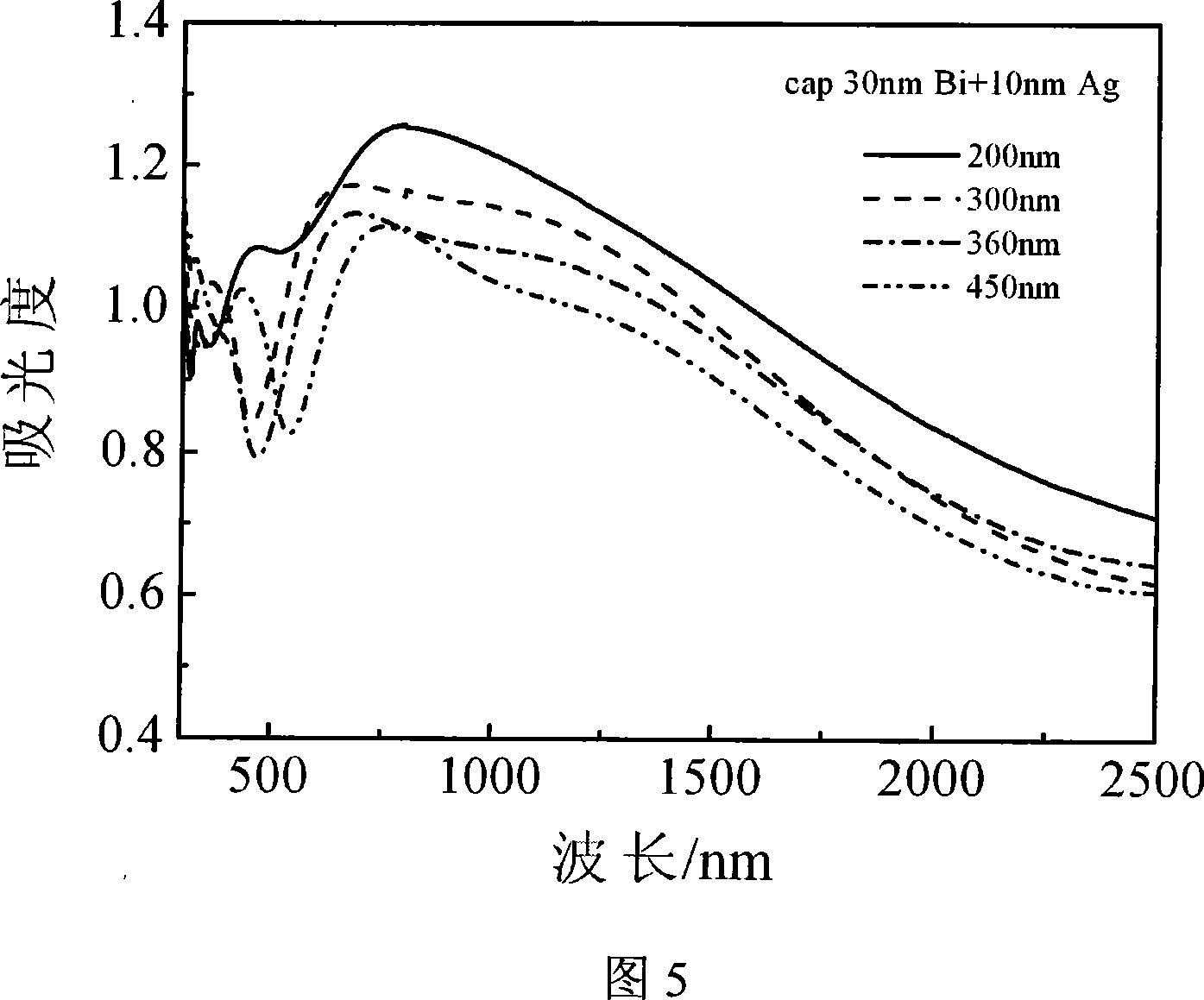

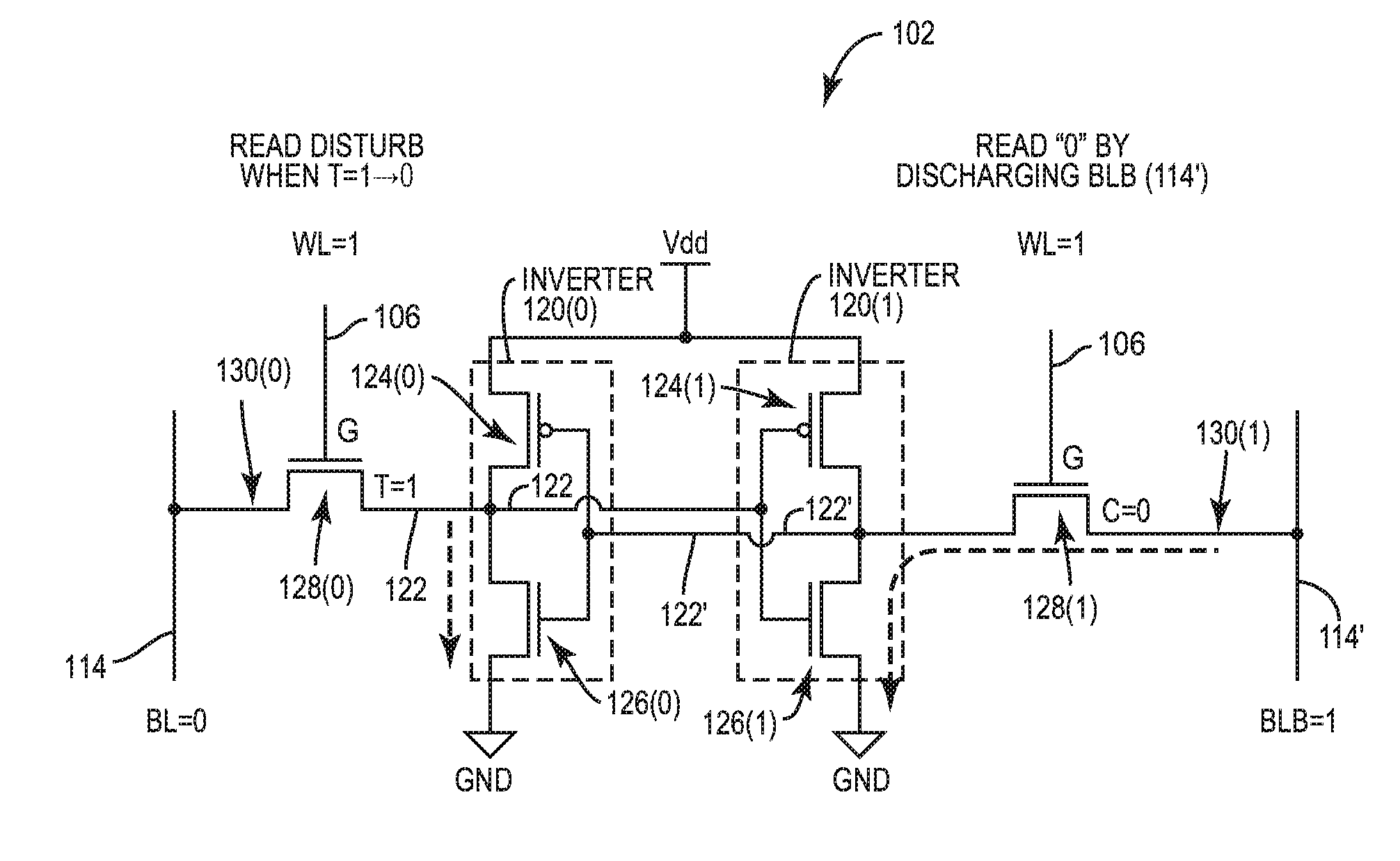

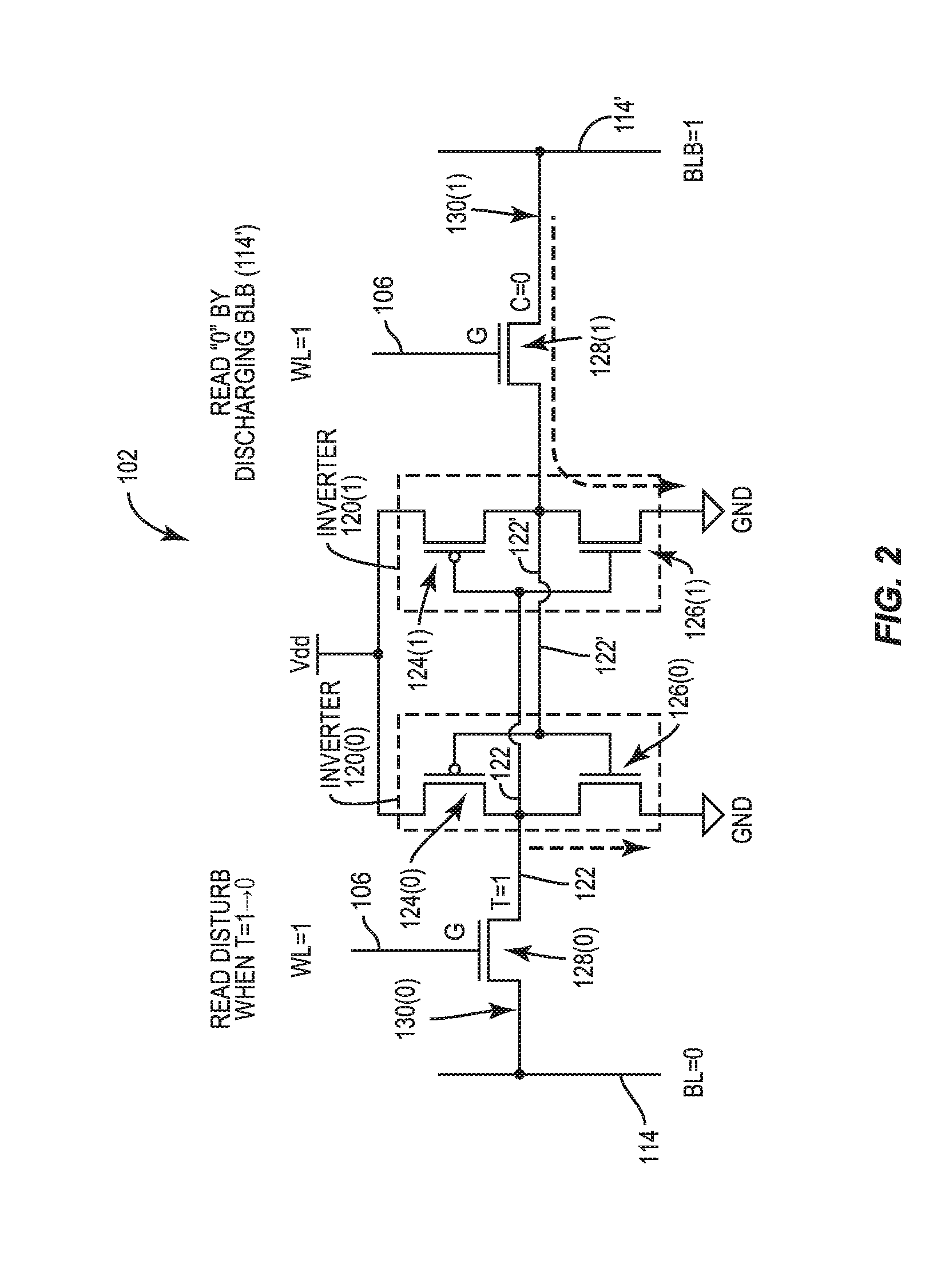

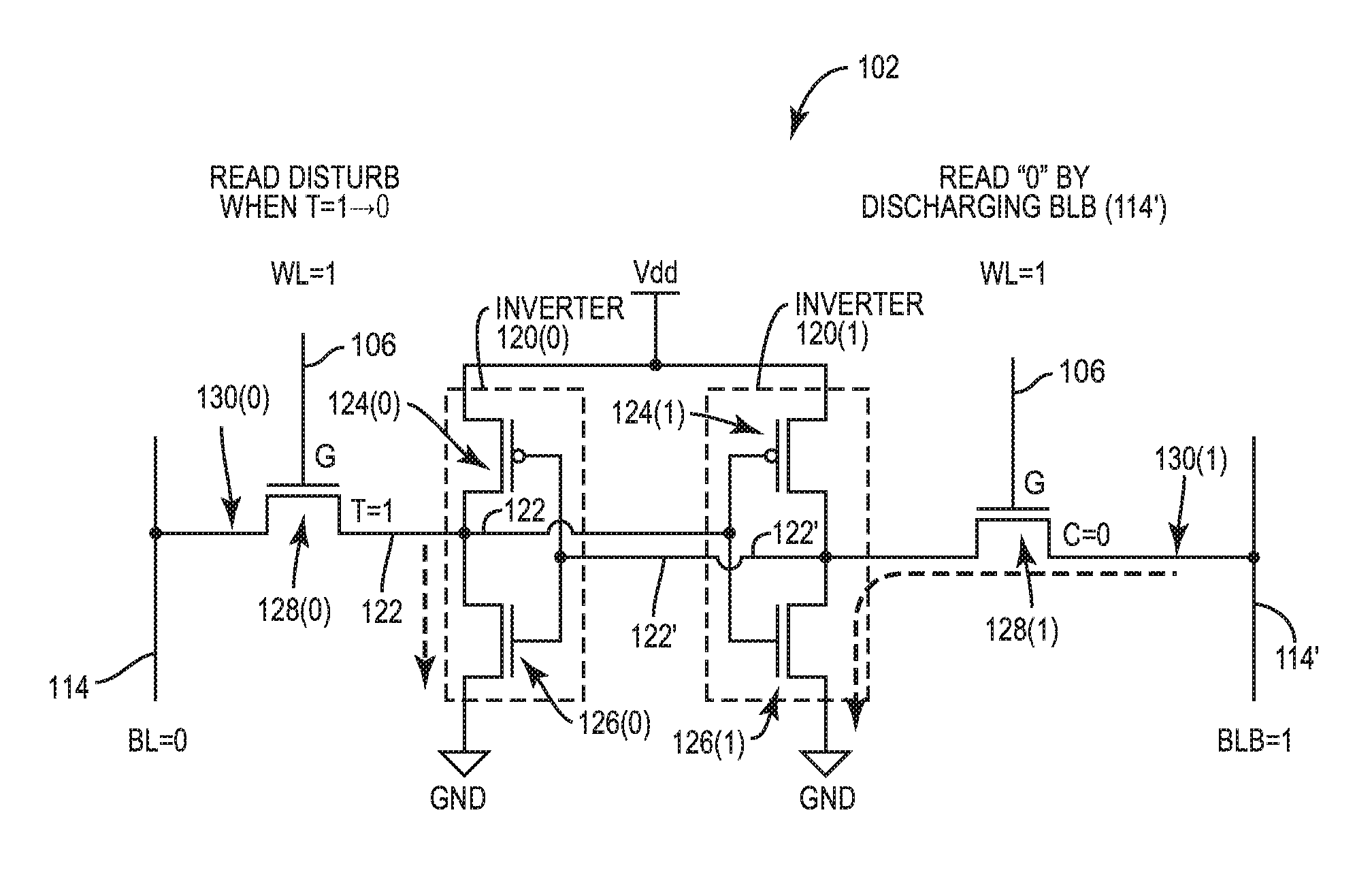

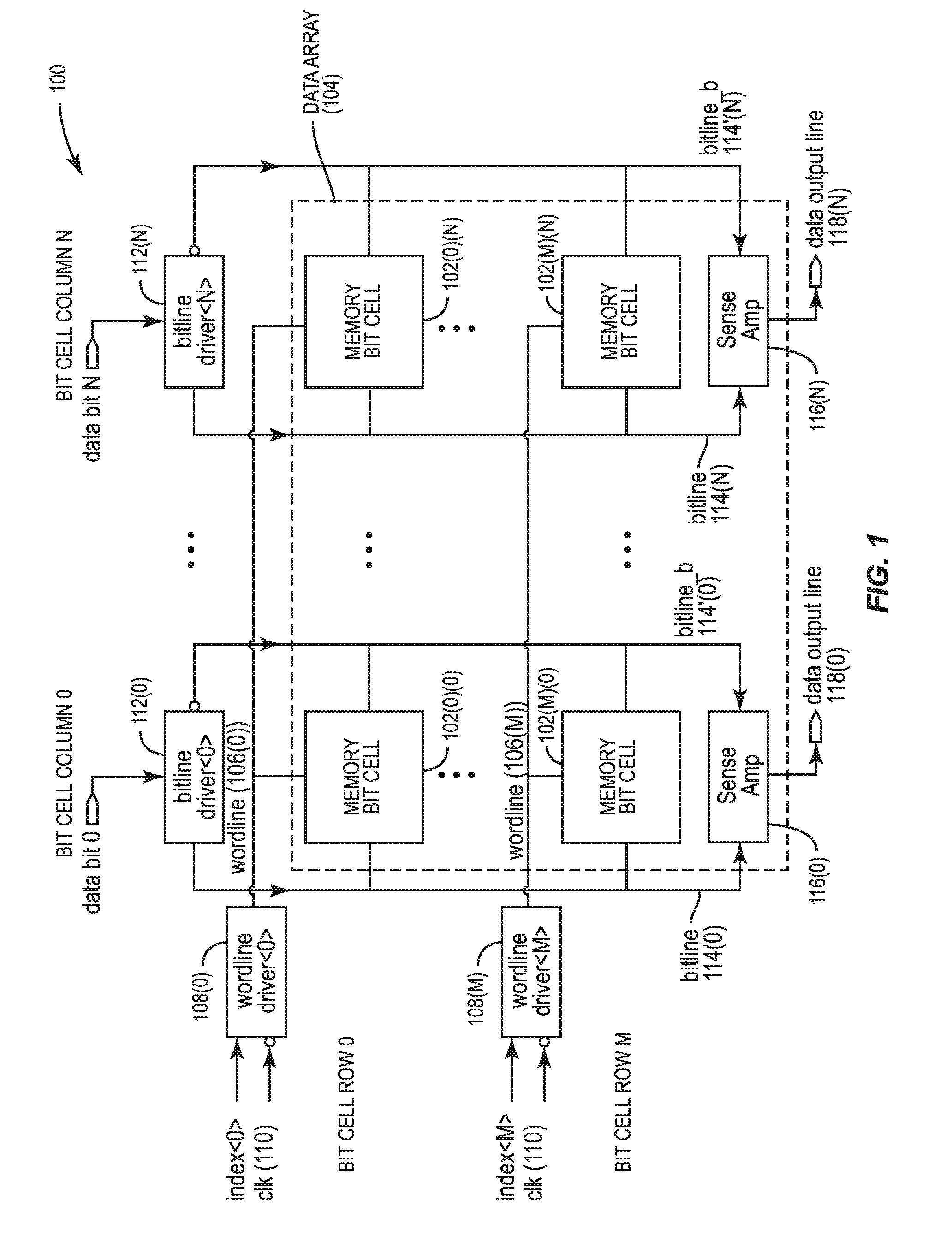

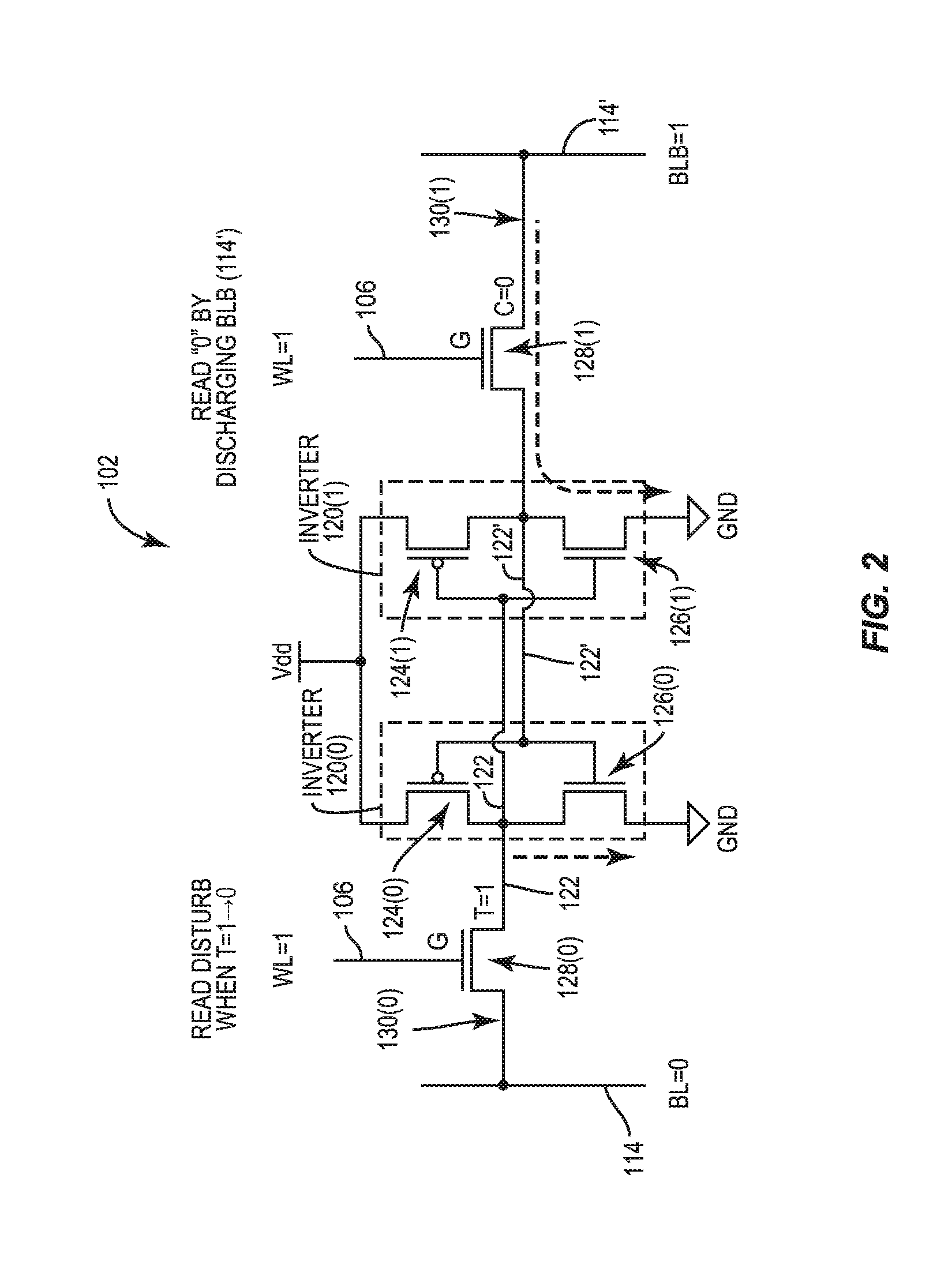

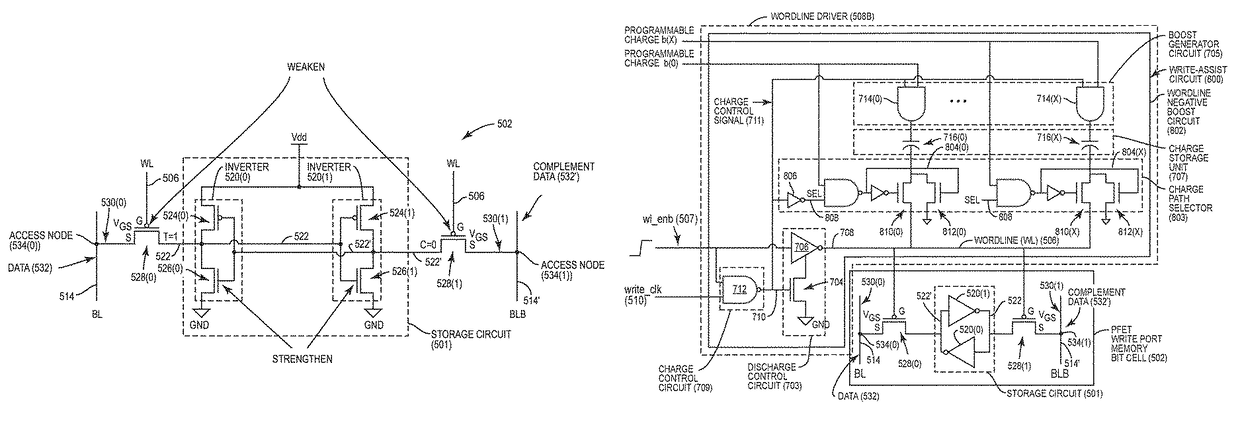

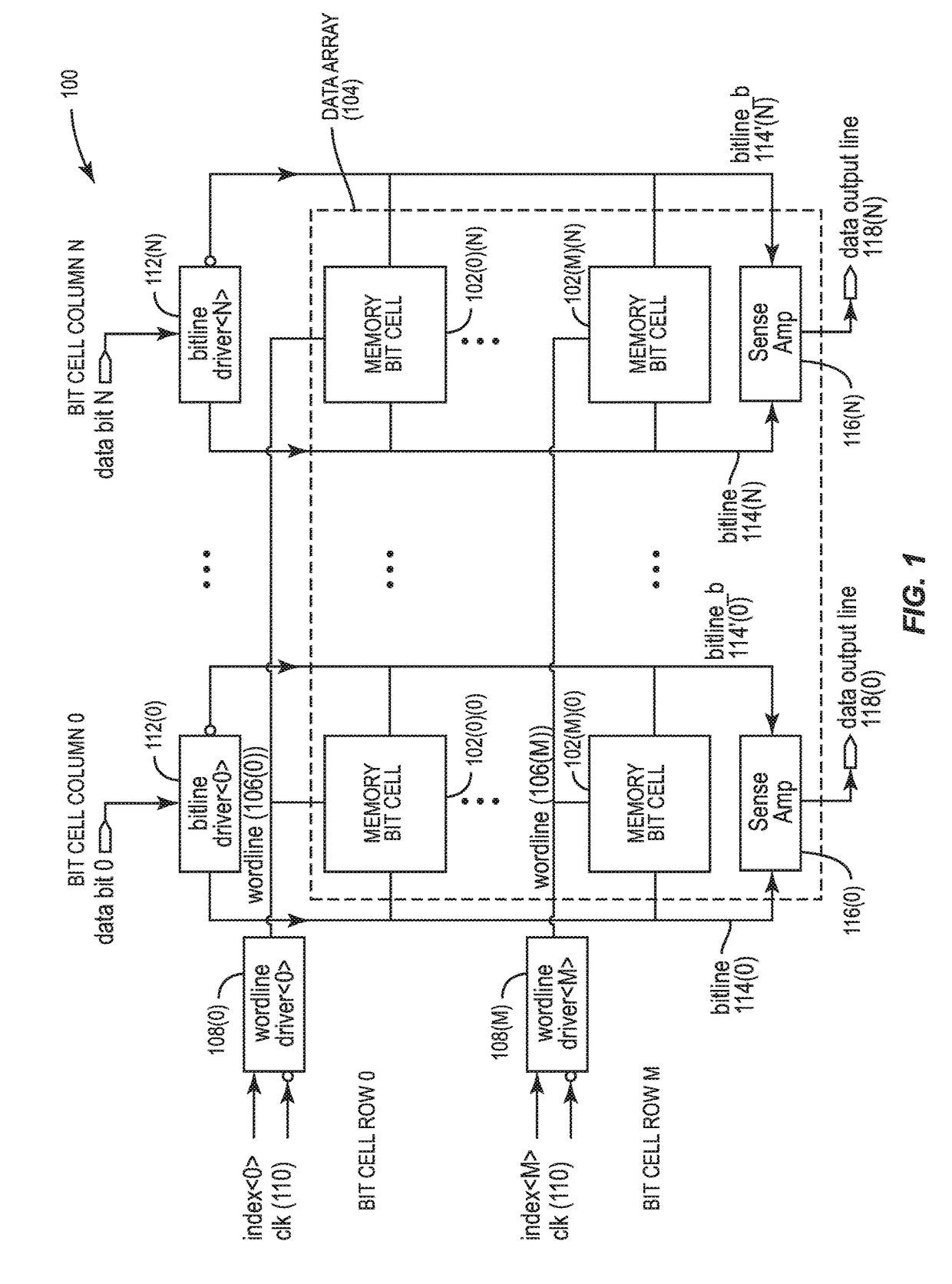

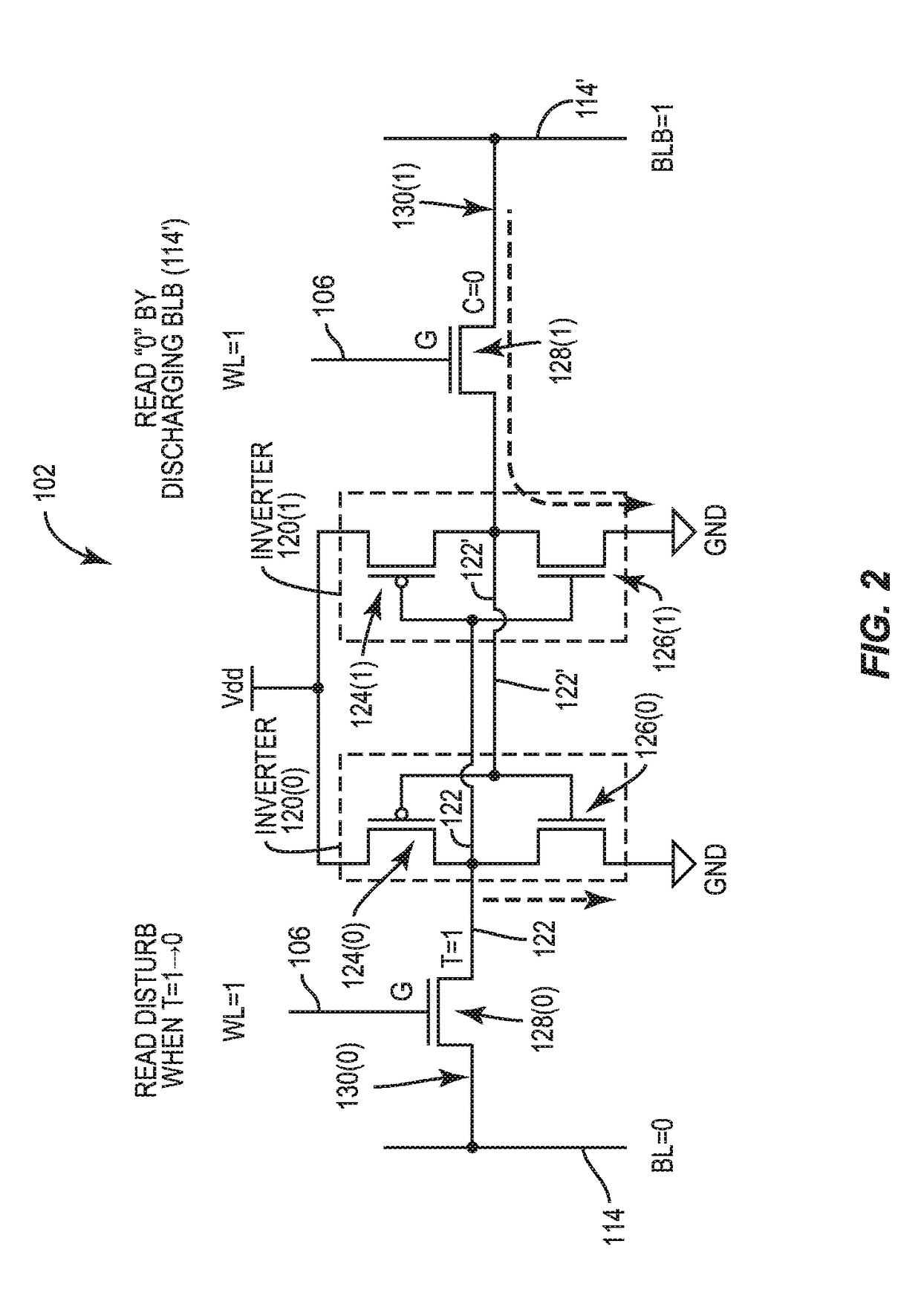

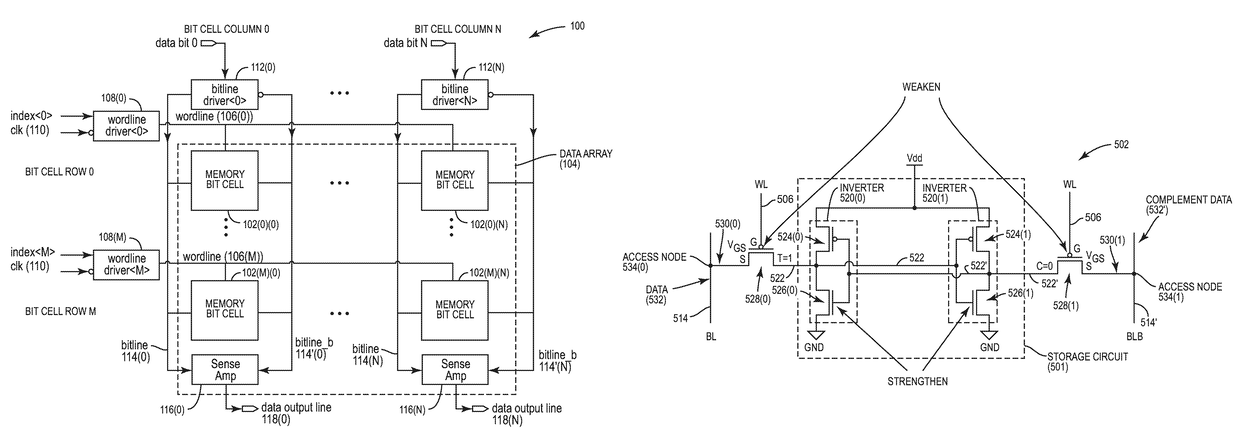

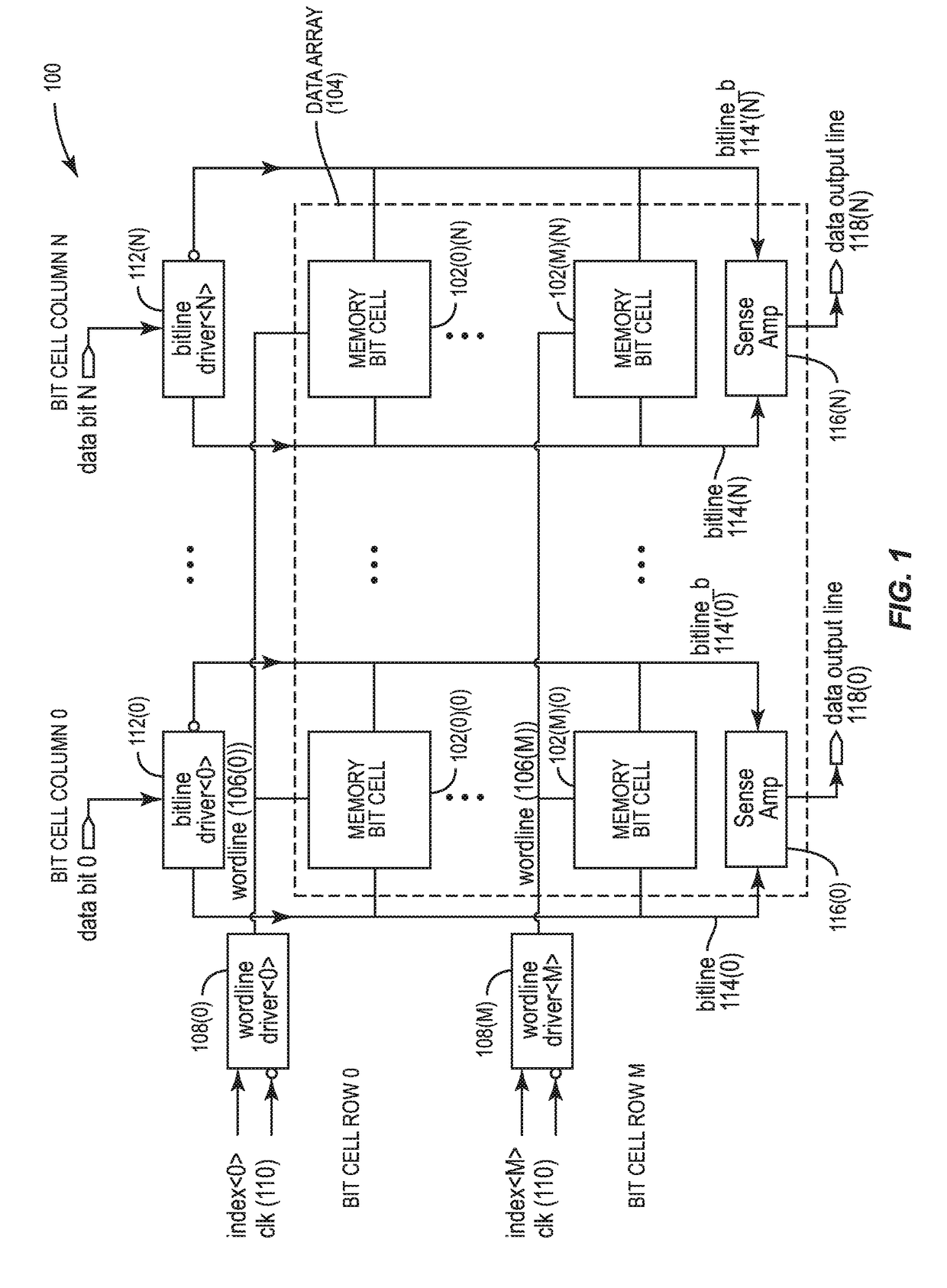

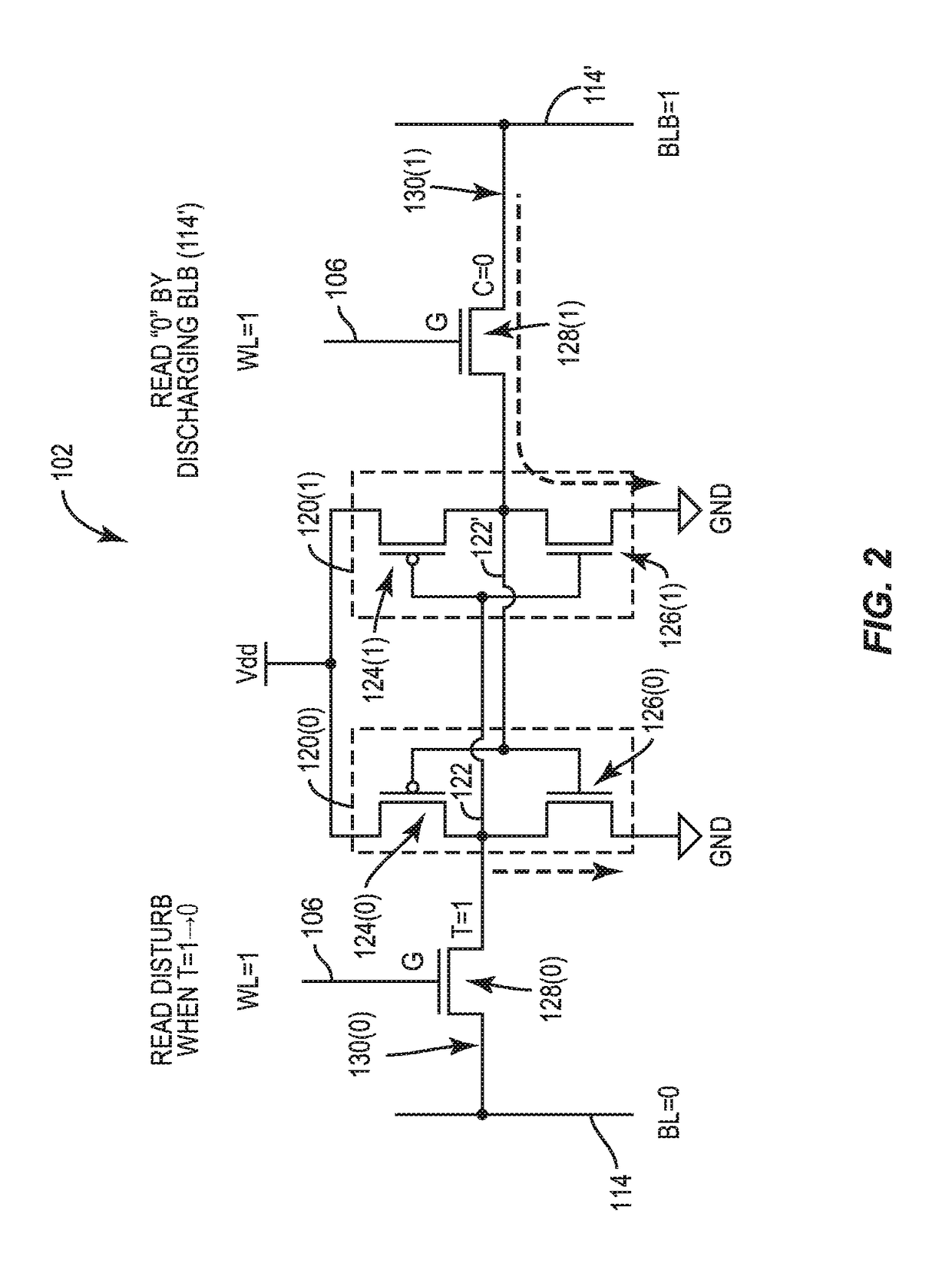

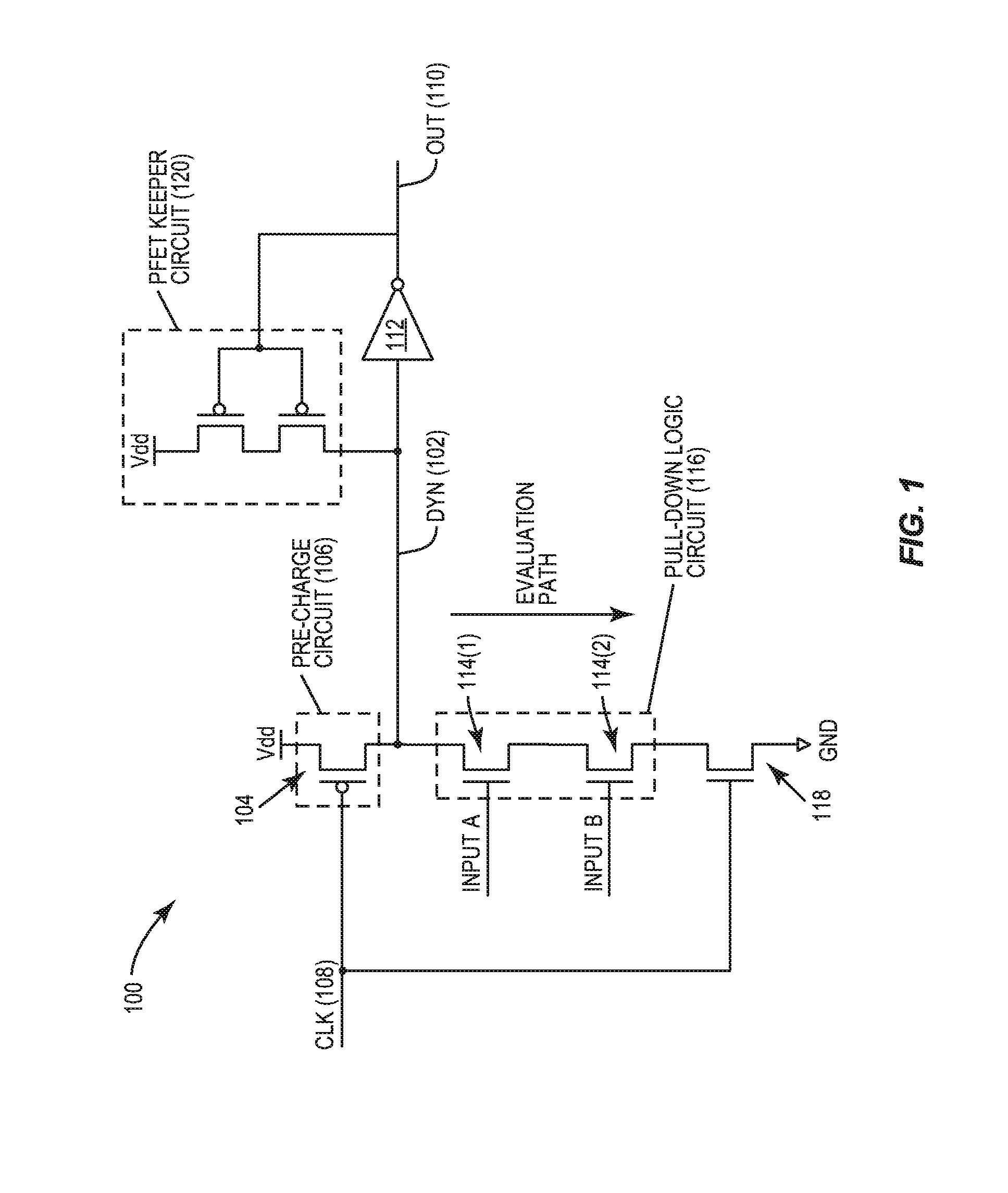

Read-assist circuits for memory bit cells employing a p-type field-effect transistor (PFET) read port(s), and related memory systems and methods

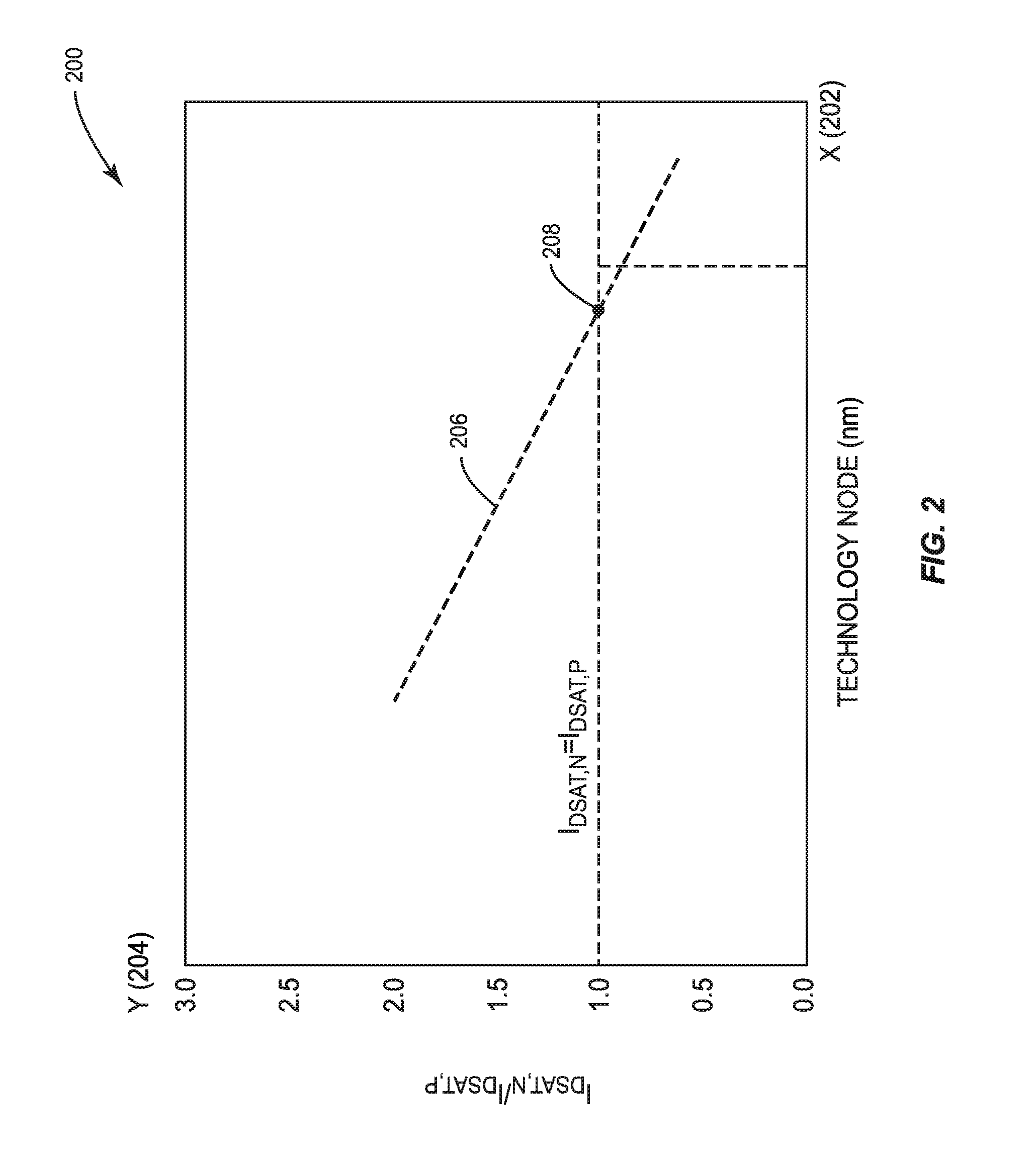

ActiveUS20160247559A1Effective mass reductionImprove memory read performanceDigital storageDriving currentComputer architecture

Read-assist circuits for memory bit cells employing a P-type Field-Effect Transistor (PFET) read port(s) are disclosed. Related memory systems and methods are also disclosed. It has been observed that as node technology is scaled down in size, PFET drive current (i.e., drive strength) exceeds N-type FET (NFET) drive current for like-dimensioned FETs. In this regard, in one aspect, it is desired to provide memory bit cells having PFET read ports, as opposed to NFET read ports, to increase memory read times to the memory bit cells, and thus improve memory read performance. To mitigate or avoid a read disturb condition that could otherwise occur when reading the memory bit cell, read-assist circuits are provided for memory bit cells having PFET read ports.

Owner:QUALCOMM INC

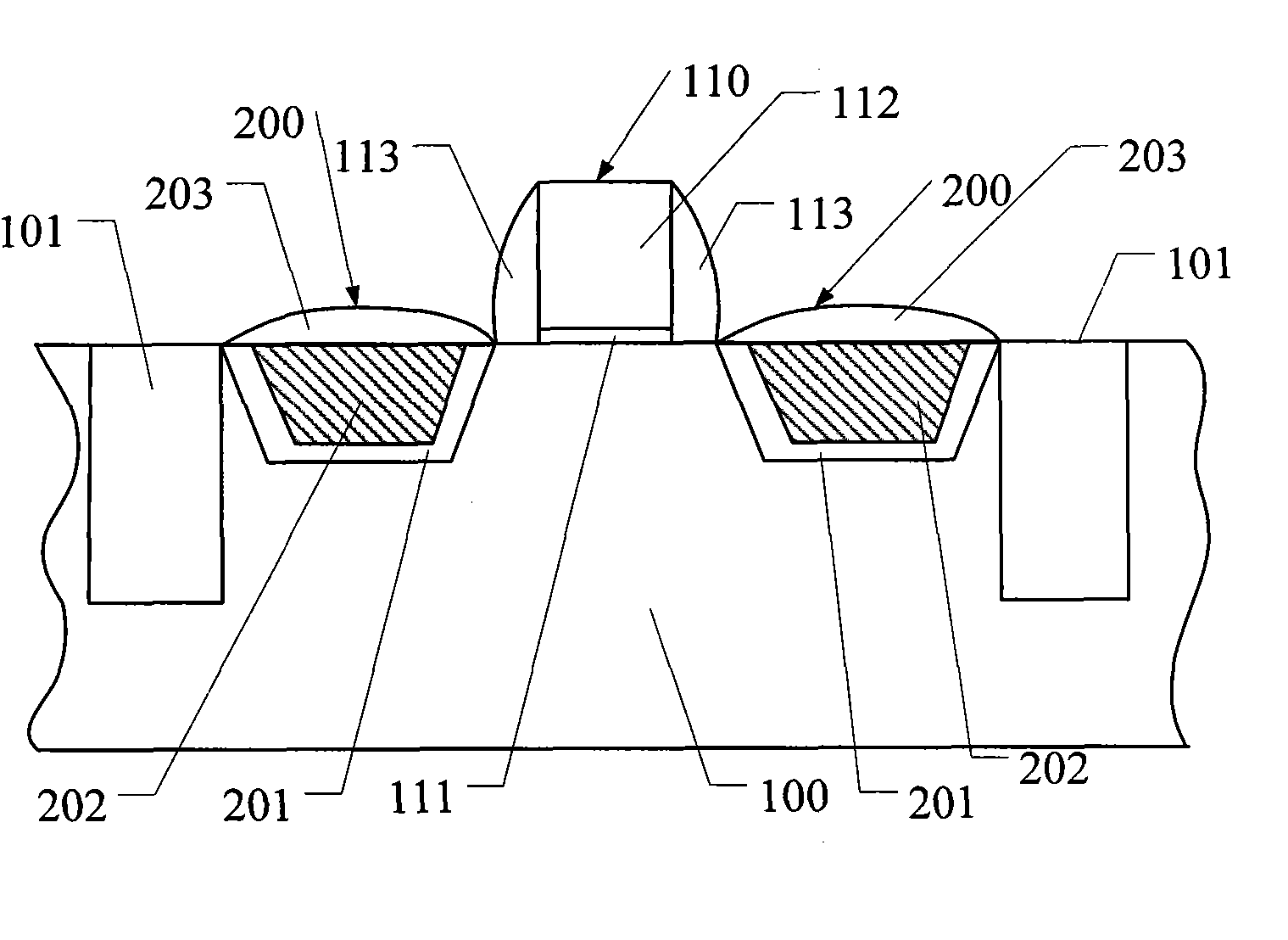

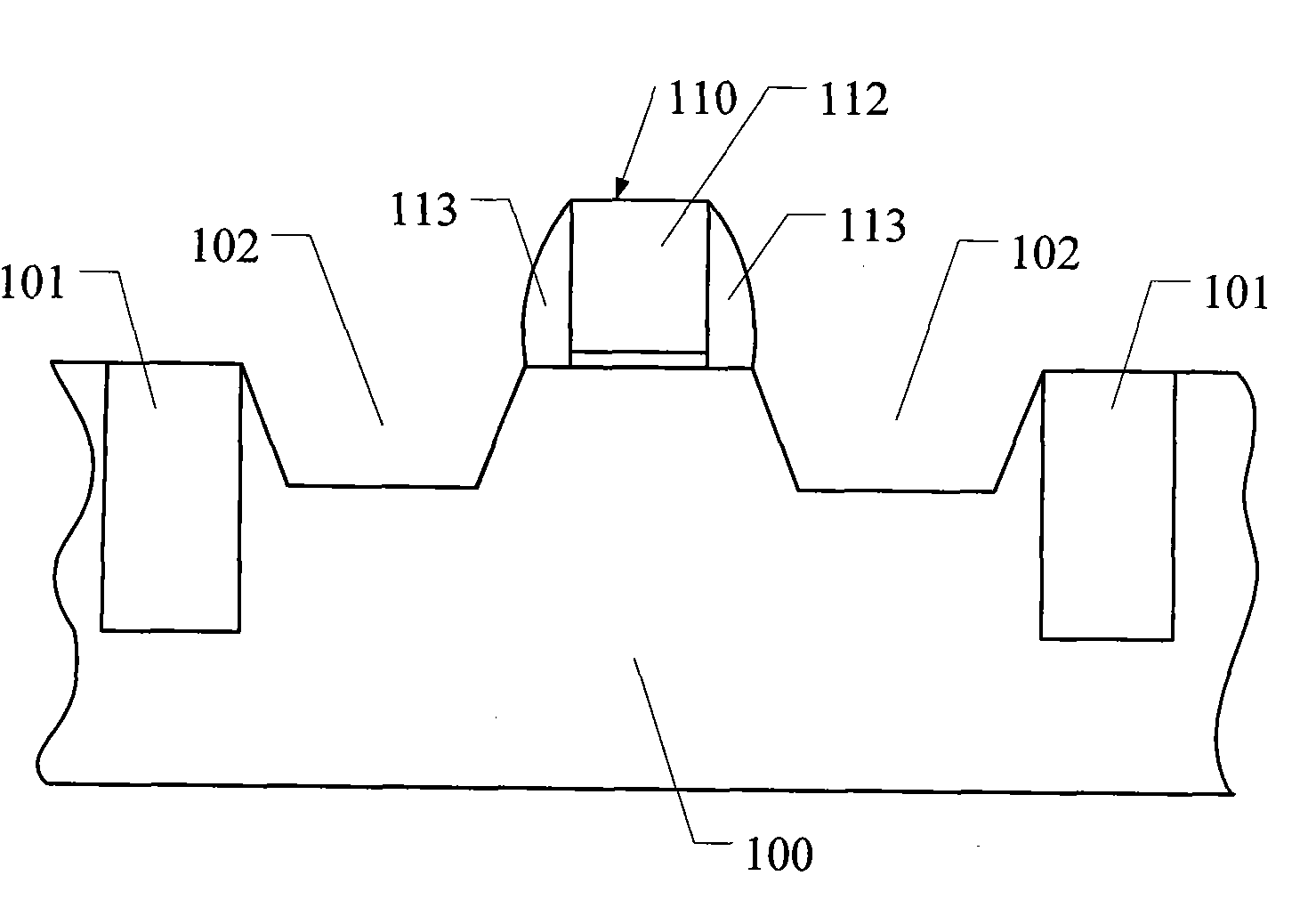

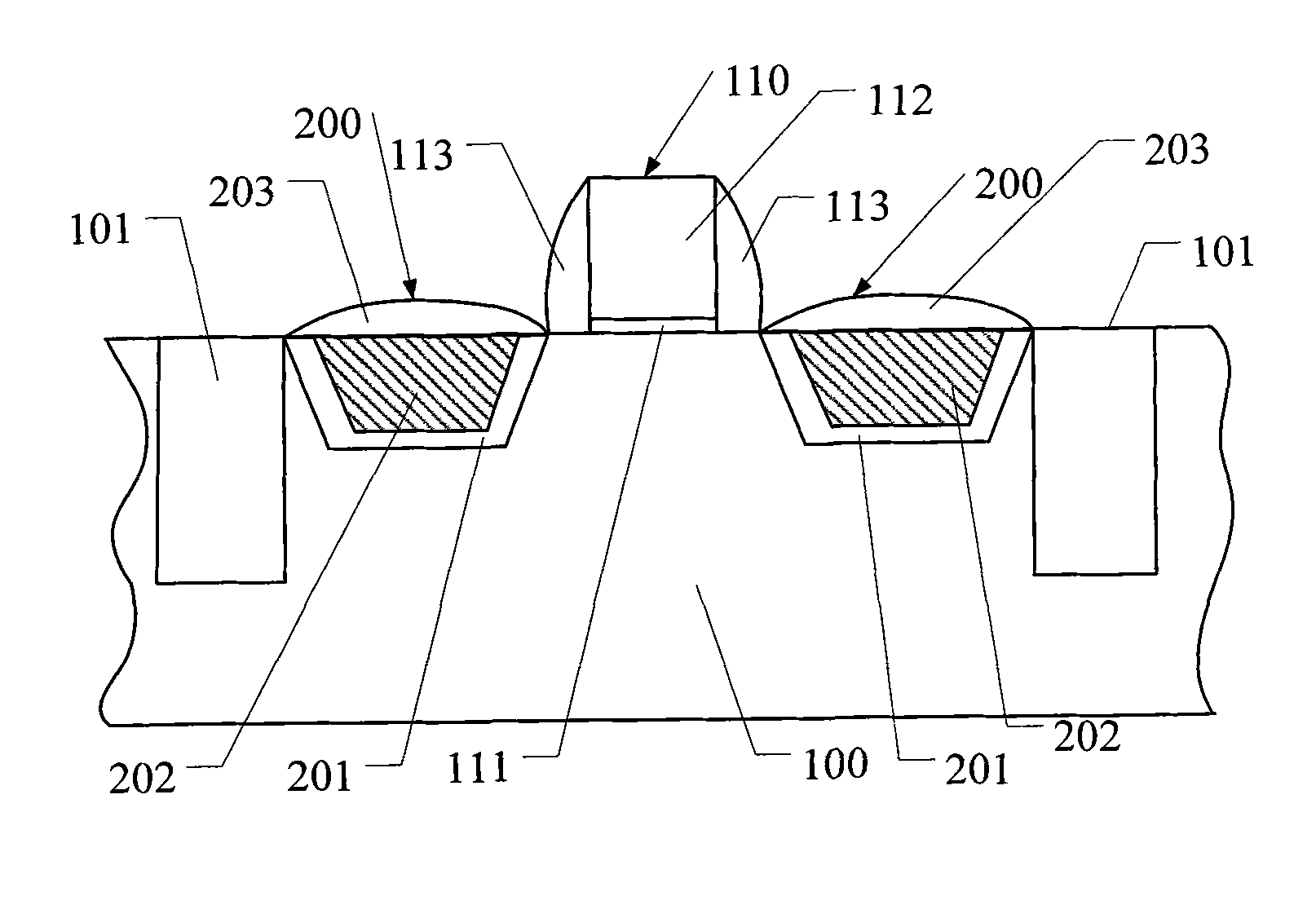

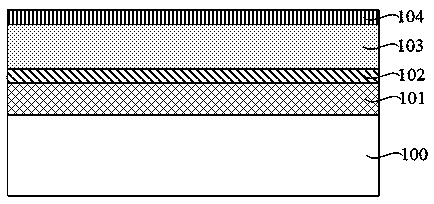

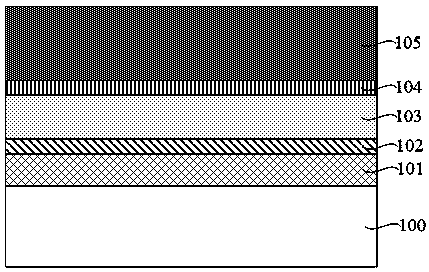

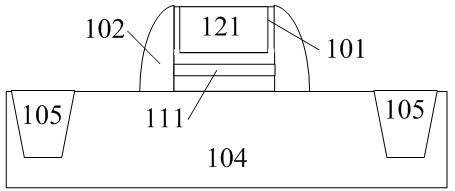

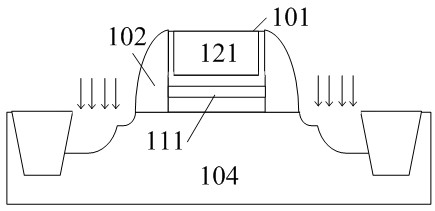

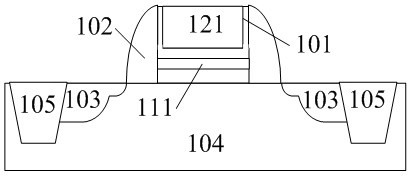

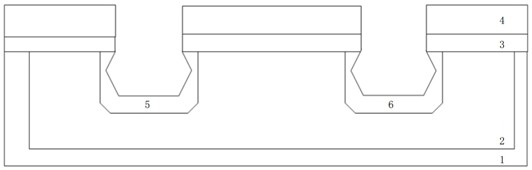

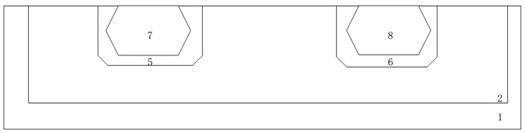

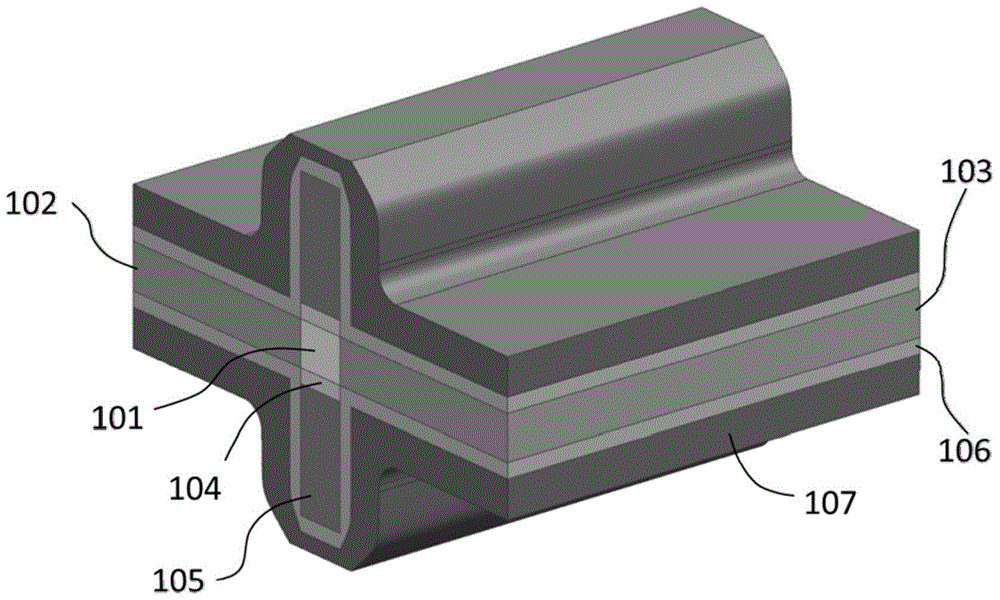

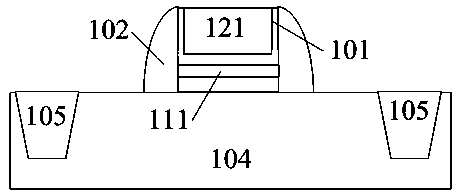

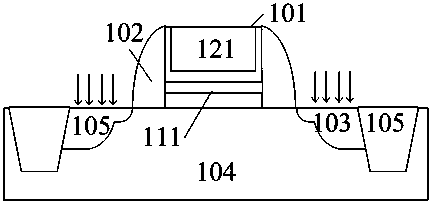

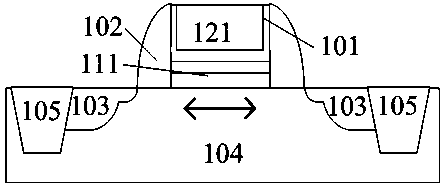

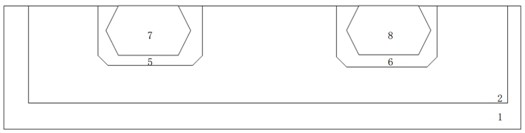

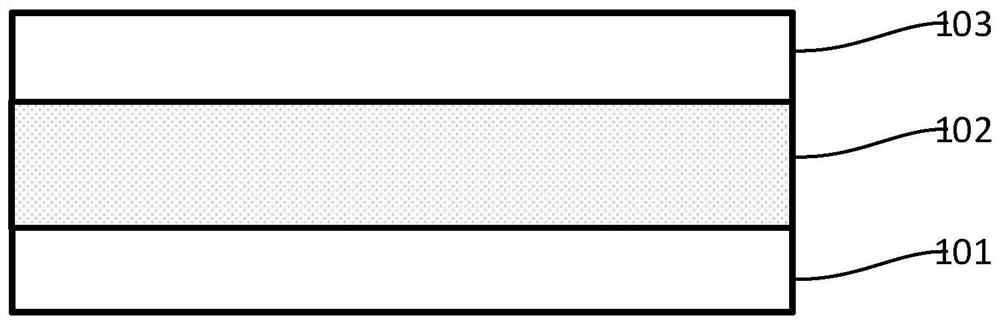

Transistor epitaxially growing source/drain region and manufacturing method thereof

InactiveCN102104067APromote growthIncrease the lattice constantSemiconductor/solid-state device manufacturingSemiconductor devicesStacking faultOptoelectronics

The invention provides a transistor epitaxially growing a source / drain region, comprising a substrate, a grid structure, a source region and a drain region, wherein the grid structure is positioned on the substrate; the source region and the drain region are formed in the substrate and positioned at both sides of the grid structure; the source region and the drain region comprise doped first homoepitaxial layers, doped heteroepitaxial layers and doped second homoepitaxial layers, wherein the doped heteroepitaxial layers are positioned on the doped first homoepitaxial layers, and the doped second homoepitaxial layers are positioned on the doped heteroepitaxial layers. The invention also provides a method for manufacturing the transistor. The transistor epitaxially growing the source / drain region can effectively reduce the defects of stacking faults and recesses.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Negative supply rail positive boost write-assist circuits for memory bit cells employing a p-type field-effect transistor (PFET) write port(s), and related systems and methods

InactiveUS20160247558A1Effective mass reductionImprove memory performanceDigital storageDriving currentEngineering

Write-assist circuits for memory bit cells (“bit cells”) employing a P-type Field-Effect transistor (PFET) write port(s) are disclosed. Related methods and systems are also disclosed. It has been observed that as node technology is scaled down in size, PFET drive current (i.e., drive strength) exceeds N-type Field-Effect transistor (NFET) drive current for like-dimensioned FETs. In this regard, in one aspect, it is desired to provide bit cells having PFET write ports, as opposed to NFET write ports, to reduce memory write times to the bit cells, and thus improve memory performance. To mitigate a write contention that could otherwise occur when writing data to bit cells, a write-assist circuit provided in the form of a negative supply rail positive boost circuit can be employed to weaken an NFET pull-down transistor in a storage circuit of a memory bit cells having a PFET write port(s).

Owner:QUALCOMM INC

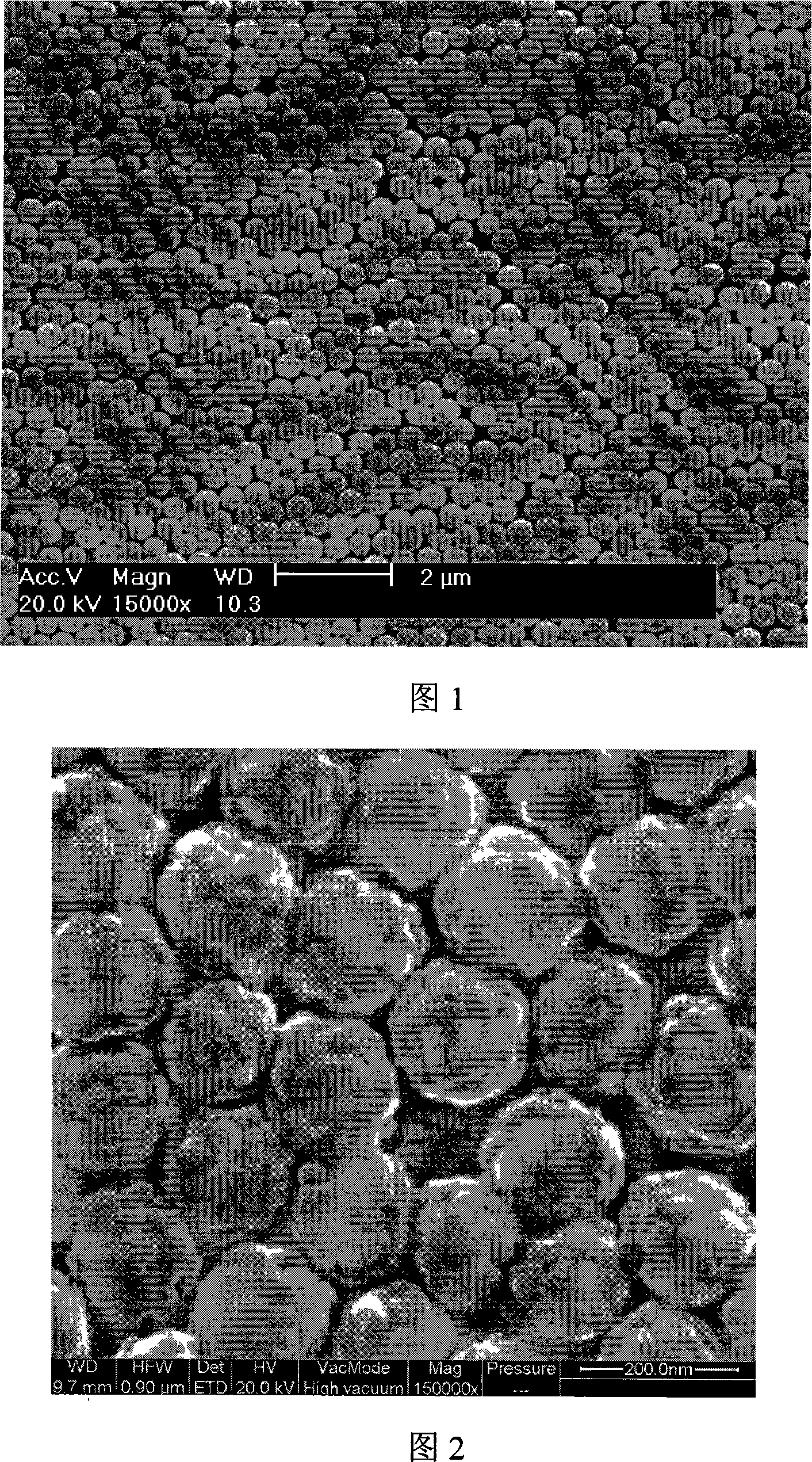

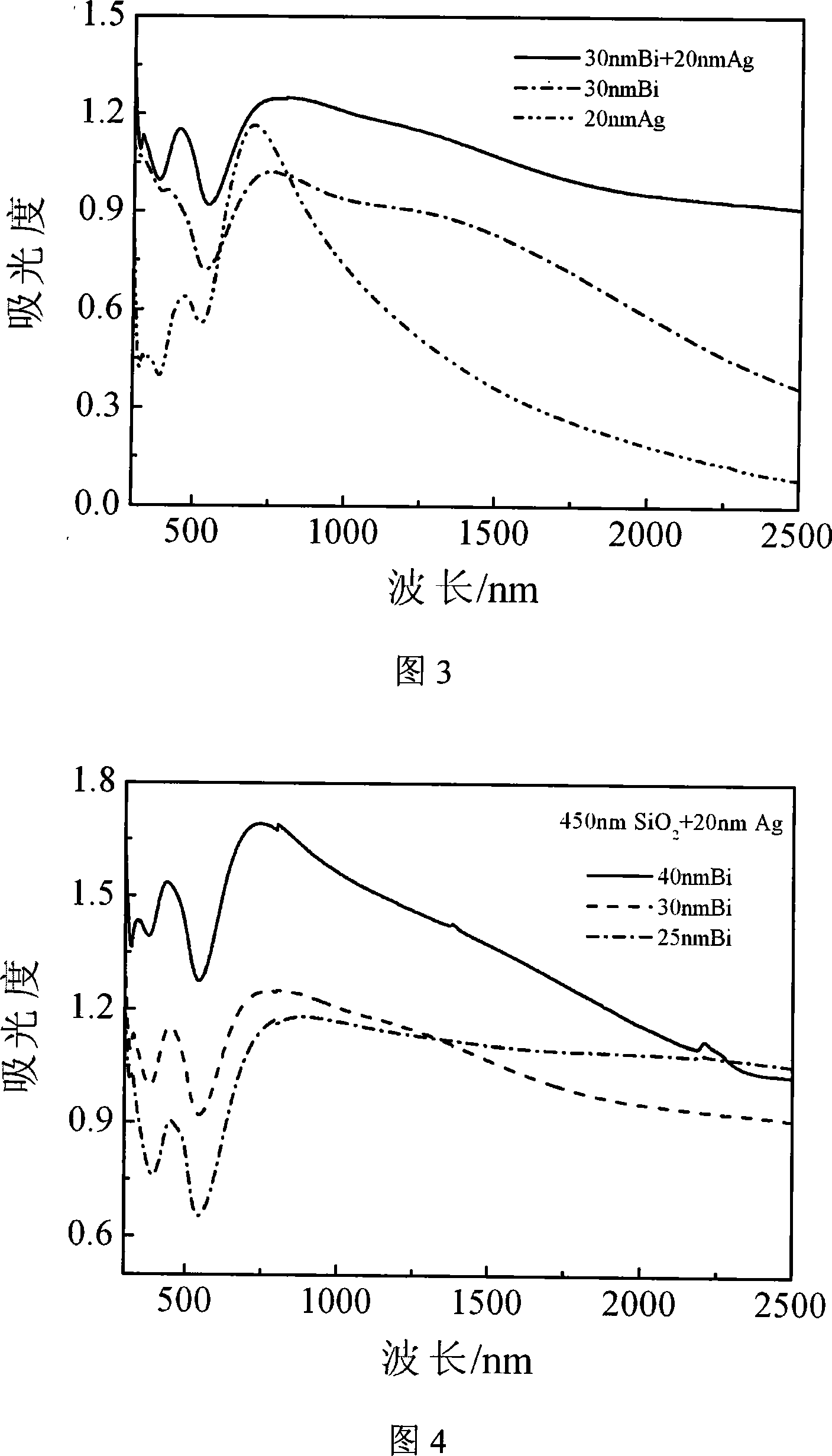

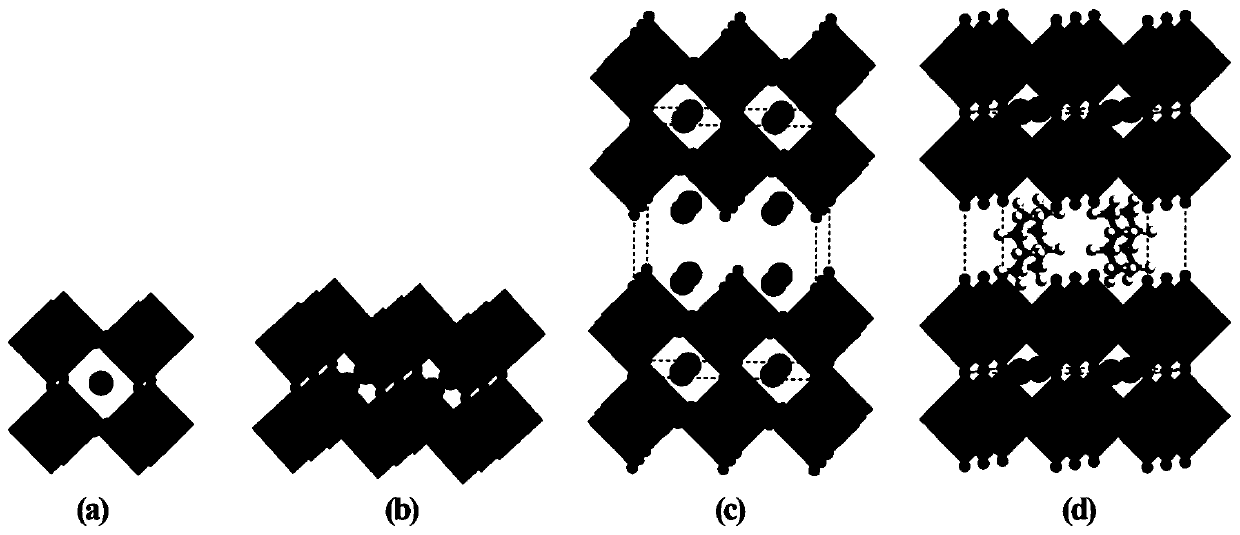

Silicon dioxide monocaryon bismuth-silver double cap shaped complex nanometer particle and its preparing method

The present invention discloses a silicon dioxide mononuclear bismuth-silver double-cap composite nano-particle and the making method thereof, the silicon dioxide mononuclear bismuth-silver double-cap composite nano-particle is provided with a layer of bismuth thin film on the silicon dioxide nano-particle and one layer of silver thin film is provided on the bismuth thin film; the preparing method comprises the steps of: (1) preparing silicon dioxide nano-particle with St ber method; (2) preparing silicon dioxide nano-particle single layer array on the surface of the piezoid with the self-assembling technique; (3) successively depositing the bismuth thin film and silver thin film on the surface of the piezoid which is covered with silicon dioxide nano-particle with heat evaporation method. The obtained composite nano-particle has excellent chemical stability and the absorption spectrum chart after depositing for one year is nearly unchanged. The preparing method has the advantages of easy operating, low cost, good repeatability, easy controlling of the nuclear diameter and cap thickness.

Owner:JINAN UNIVERSITY

Bitline positive boost write-assist circuits for memory bit cells employing a p-type field-effect transistor (PFET) write port(s), and related systems and methods

ActiveUS20160247557A1Reduce effective massImproving memory performanceDigital storageMemory performanceEngineering

Write-assist circuits for memory bit cells (“bit cells”) employing a P-type Field-Effect transistor (PFET) write port(s) are disclosed. Related methods and systems are also disclosed. It has been observed that as node technology is scaled down in size, PFET drive current (i.e., drive strength) exceeds N-type Field-Effect transistor (NFET) drive current for like-dimensioned FETs. In this regard, in one aspect, it is desired to provide bit cells having PFET write ports, as opposed to NFET write ports, to reduce memory write times to the bit cells, and thus improve memory performance. To mitigate a write contention that could otherwise occur when writing data to bit cells, a write-assist circuit provided in the form of positive bitline boost circuit can be employed to strengthen a PFET access transistor in a memory bit cell having a PFET write port(s).

Owner:QUALCOMM INC

Wordline negative boost write-assist circuits for memory bit cells employing a p-type field-effect transistor (PFET) write port(s), and related systems and methods

ActiveUS20160247556A1Effective mass reductionReduce memory write timeDigital storageDriving currentField-effect transistor

Write-assist circuits for memory bit cells (“bit cells”) employing a P-type Field-Effect transistor (PFET) write port(s) are disclosed. Related methods and systems are also disclosed. It has been observed that as node technology is scaled down in size, PFET drive current (i.e., drive strength) exceeds N-type Field-Effect transistor (NFET) drive current for like-dimensioned FETs. In this regard, in one aspect, it is desired to provide bit cells having PFET write ports, as opposed to NFET write ports, to reduce memory write times to the bit cells, and thus improve memory performance. To mitigate a write contention that could otherwise occur when writing data to bit cells, a write-assist circuit provided in the form of negative wordline boost circuit can be employed to strengthen a PFET access transistor in a memory bit cell having a PFET write port(s).

Owner:QUALCOMM INC

Wordline negative boost write-assist circuits for memory bit cells employing a P-type field-effect transistor (PFET) write port(s), and related systems and methods

ActiveUS9842634B2Effective mass reductionReduce memory write timeDigital storageDriving currentEngineering

Write-assist circuits for memory bit cells (“bit cells”) employing a P-type Field-Effect transistor (PFET) write port(s) are disclosed. Related methods and systems are also disclosed. It has been observed that as node technology is scaled down in size, PFET drive current (i.e., drive strength) exceeds N-type Field-Effect transistor (NFET) drive current for like-dimensioned FETs. In this regard, in one aspect, it is desired to provide bit cells having PFET write ports, as opposed to NFET write ports, to reduce memory write times to the bit cells, and thus improve memory performance. To mitigate a write contention that could otherwise occur when writing data to bit cells, a write-assist circuit provided in the form of negative wordline boost circuit can be employed to strengthen a PFET access transistor in a memory bit cell having a PFET write port(s).

Owner:QUALCOMM INC

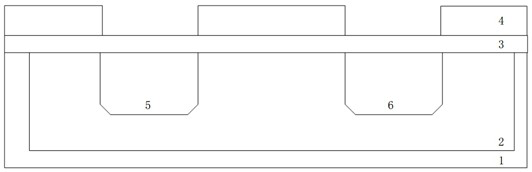

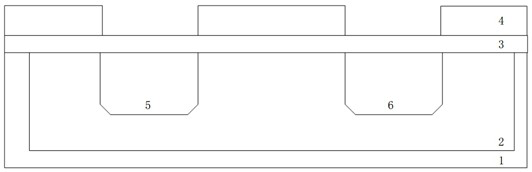

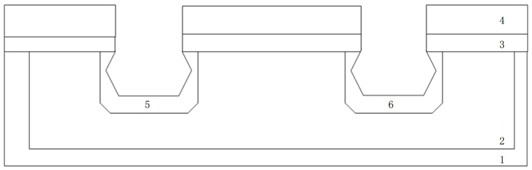

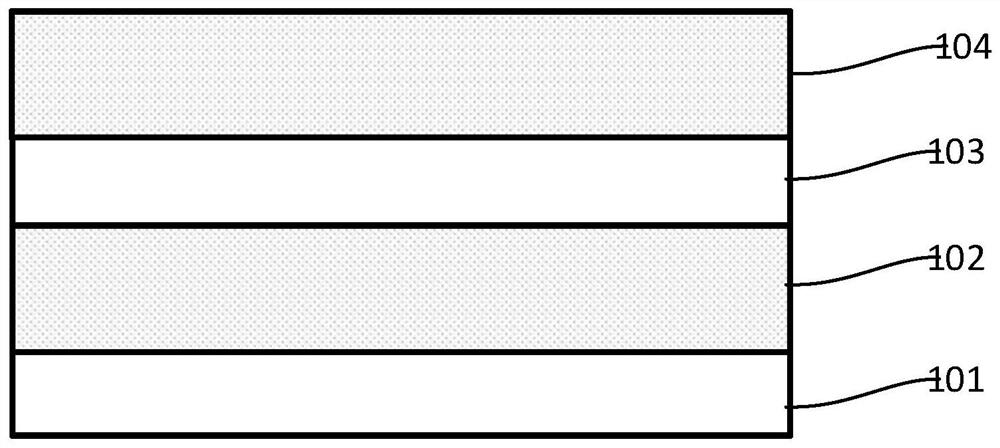

Double-gate p-channel MOSFET with compression strain thin film strain source and preparation method thereof

InactiveCN104022152AIncrease working currentEffective mass reductionSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSemiconductor materials

The invention provides a double-gate p-channel MOSFET with a compression strain thin film strain source and a preparation method of the double-gate p-channel MOSFET with the compression strain thin film strain source. The MOSFET comprises a source region, a drain region, a conducting channel region, a gate dielectric layer, a grid electrode, an insulating dielectric layer and a compression strain thin film strain layer. The gate dielectric layer is formed on a first surface of a semiconductor material and located on the side face of a first conducting surface and the side face of a second conducting surface of the conducting channel region. The grid electrode is formed on the first surface of the semiconductor material and located on the side face of the gate dielectric layer. The insulating dielectric layer is formed on the side wall of the grid electrode, the side wall of a source electrode and the side wall of a drain electrode. The compression strain thin film strain layer is formed on the side wall of the insulating dielectric layer and used for leading compression strain in the channel direction into the conducting channel region. The surface of the MOSFET is covered with the compression strain thin film strain layer, and the large compression strain in the channel direction is led into the conducting channel region; as a result, effective mass of holes can be reduced, the migration rate of the holes is increased, the working current of the MOSFET is increased, and on-resistance is lowered.

Owner:CHONGQING UNIV

Read-assist circuits for memory bit cells employing a P-type field-effect transistor (PFET) read port(s), and related memory systems and methods

ActiveUS9741452B2Effective mass reductionShorten read timeDigital storageDriving currentComputer architecture

Owner:QUALCOMM INC

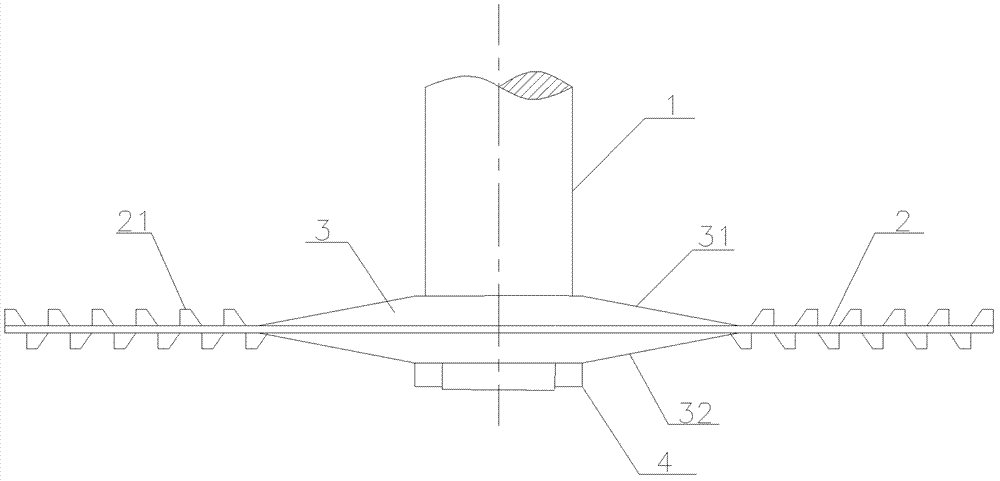

Toothed disk turbine-type stirring device

InactiveCN102895904AEffective mass reductionReduce weightRotary stirring mixersTransportation and packagingCircular discEngineering

The invention relates to a stirring device, and especially relates to a toothed disk turbine-type stirring device. The toothed disk turbine-type stirring device comprises a shaft sleeve and a dispersing disk. The shaft sleeve is connected with the dispersing disk through butterfly pressure plates. There are two butterfly pressure plates, which are a first butterfly pressure plate and a second butterfly pressure plate from top to bottom. The first butterfly pressure plate is positioned on the upper part of the dispersing plate, and the second butterfly pressure plate is positioned on the blower part of the dispersing plate. A round nut used for fixing the shaft sleeve is arranged on the lower part of the second butterfly pressure plate. According to the invention, the clamping-type butterfly pressure plates are used for fixing the dispersing plate and the shaft sleeve, and welding is not needed. With the pre-tightening force between the two butterfly pressure plates, the dispersing plate can be firmly clamped, and two planes can be completely flattened. The two butterfly pressure plates has butterfly shapes and light weights, such that the effective mass of the stirring device at the end of a stirring shaft is reduced, critical rotation speed is improved, shaft diameter is reduced, and cost is reduced.

Owner:江苏华东明茂机械有限公司

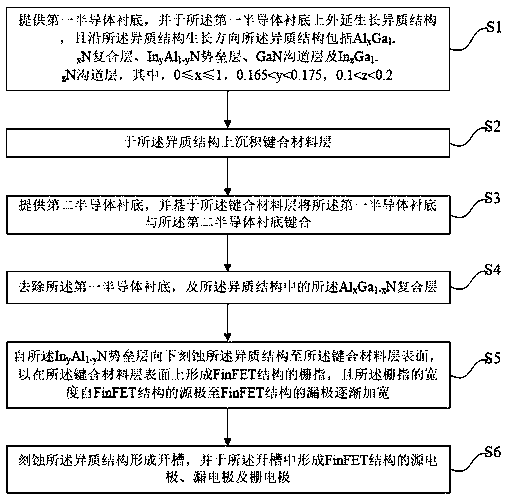

Gate finger gradually-widened GaN FinFET structure and preparation method thereof

ActiveCN111223928AImprove pressure resistanceEffective mass reductionSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsNarrow band

The invention provides a gate finger gradually-widened GaN FinFET structure and a preparation method thereof. The structure comprises a second semiconductor substrate, a bonding material layer locatedon the second semiconductor substrate, and a FinFET structure located on the bonding material layer, wherein the FinFET structure comprises a grid electrode, a source electrode, a drain electrode anda gate finger, the source electrode, the drain electrode and the gate finger are formed by an InyAl<1-y>N barrier layer, a GaN channel layer and an InzGa<1-z>N channel layer which are stacked in sequence, y is greater than 0.165 and less than 0.175, z is greater than 0.1 and less than 0.2, the two ends of the gate finger are connected with the source electrode and the drain electrode respectively, and the width of the gate finger is gradually increased from the source electrode to the drain electrode. GaN / InGaN double channels are adopted; on the one hand, the effective mass of carriers in the InGaN channel is lower than that of carriers in the GaN channel, so that the drift speed of upper limit carriers in the FinFET structure is effectively improved; meanwhile, two-dimensional electrongas (2DEG) can be better limited in the channel through a relatively narrow band gap of the InGaN material, and scattering and current collapse of the carriers are effectively relieved; in addition, the gate finger in the FinFET structure is designed to be in a gradually widened shape, so that the voltage withstanding performance of the FinFET structure is effectively improved.

Owner:浙江集迈科微电子有限公司

SONOS (Silicon Oxide Nitride Oxide Silicon) unit transistor with high erasing speed and manufacturing method thereof

InactiveCN102569408AImprove programming efficiencyImprove programming speedSemiconductor/solid-state device manufacturingSemiconductor devicesCarbon ionSilicon oxide

The invention discloses a method for increasing erasing speed of an SONOS (Silicon Oxide Nitride Oxide Silicon) unit transistor by using a strained silicon technology. The method is characterized by comprising the step of making a side wall of a gate on a P type substrate with a plurality of shallow trench isolation regions and also comprises the following steps of: (step 1) depositing a barrier layer to cover the transistor; (step 2) etching the barrier layer so as to remove the barrier layer covering above a NMOS (N-channel Mental-Oxide-Semiconductor) region so that the NMOS region is exposed; (step 3) carrying out carbon ion implantation on the P type substrate between the two sides of the gate and the shallow trench isolation regions; and (step 4) carrying out high temperature annealing so that tensile stresses are generated on the trenches through the silicon carbide. By using the method for increasing erasing speed of the SONOS unit transistor by using the strained silicon technology, disclosed by the invention, the energy band of the silicon is cracked and the electron effective mass is reduced along the trench direction due to the cracking result; meanwhile, the energy valley scattering probability of the electron is also reduced and the electron mobility of the SONOS unit transistor is obviously increased so that SONOS programming efficiency and speed of a hot electron injection mechanism are increased.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

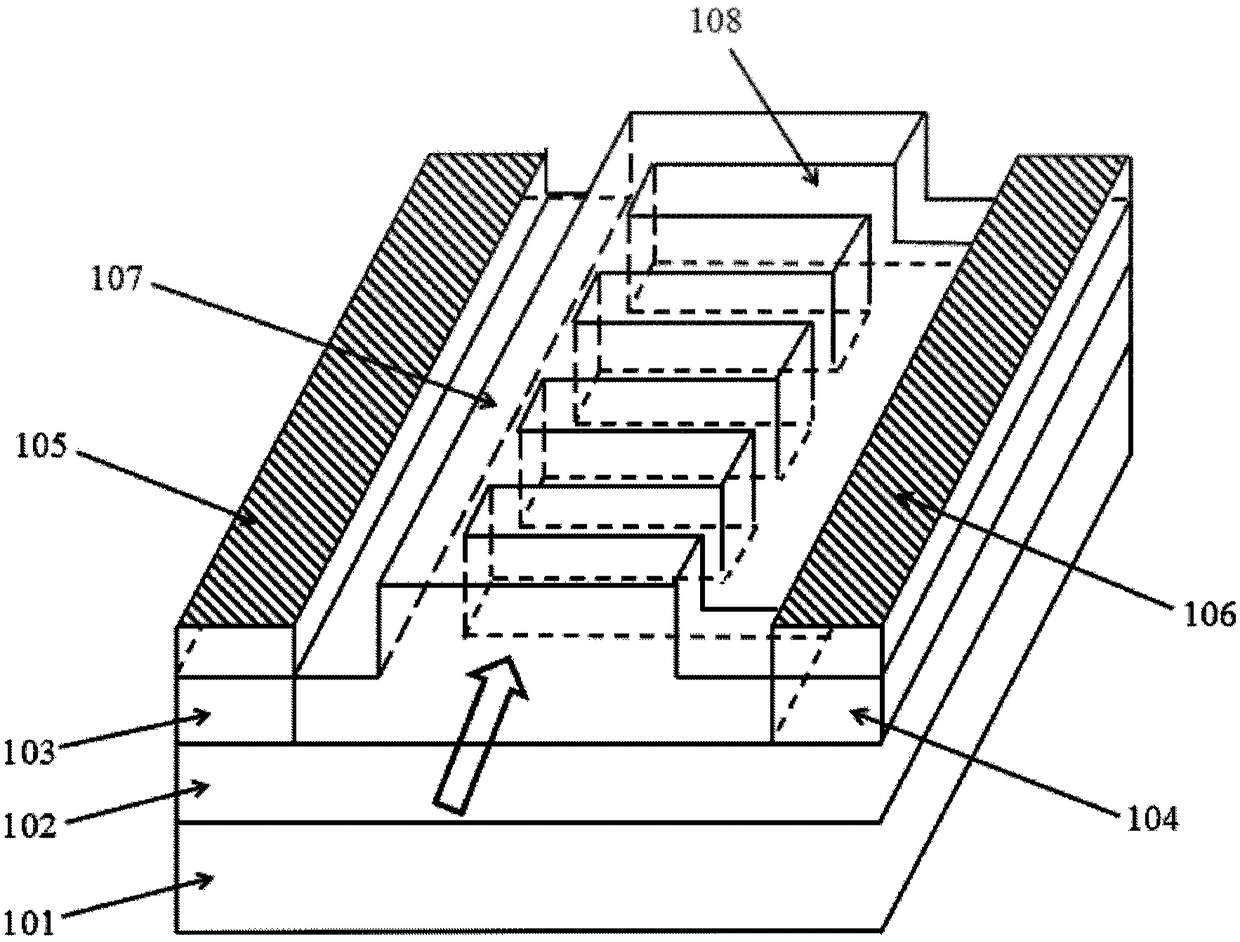

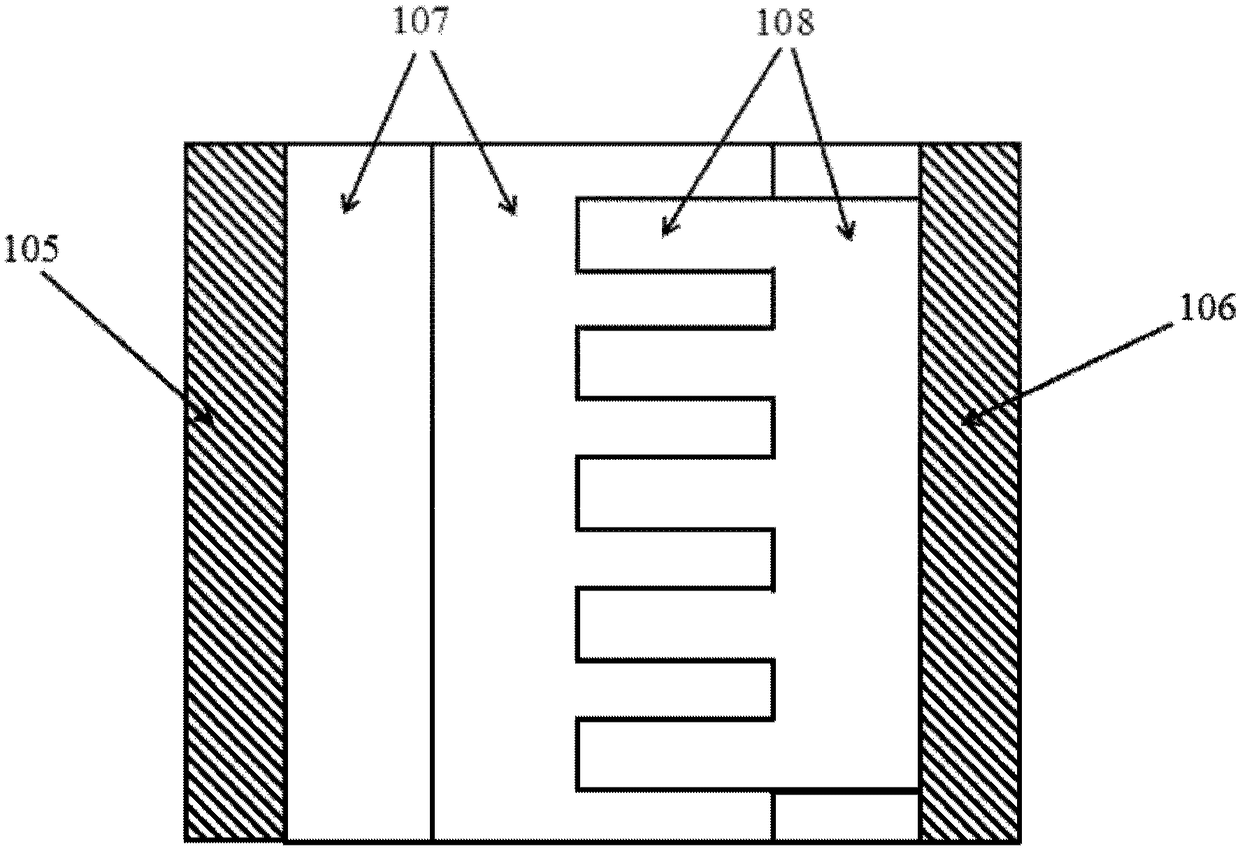

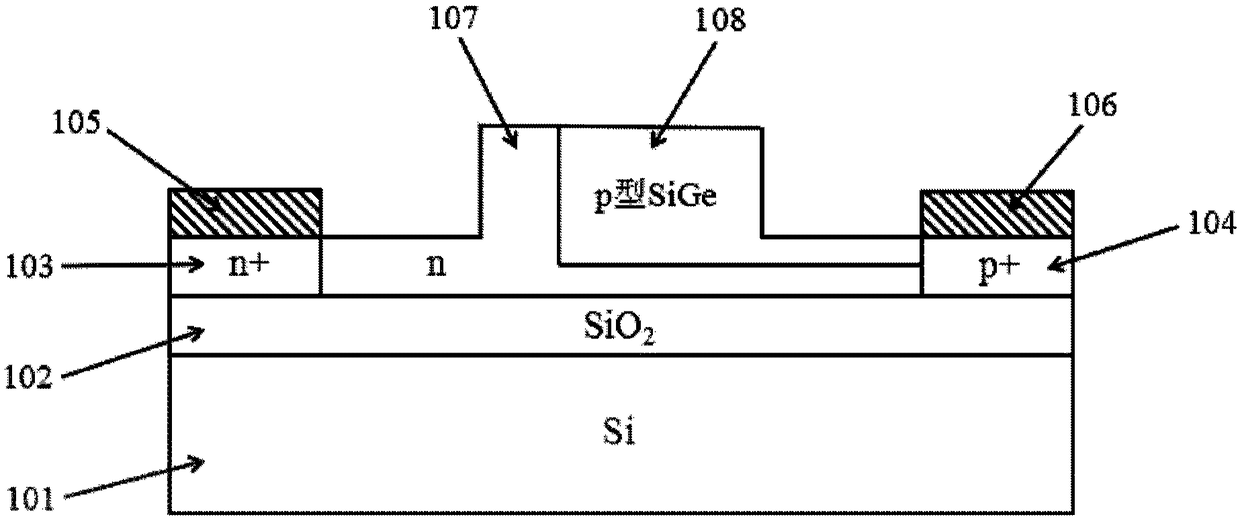

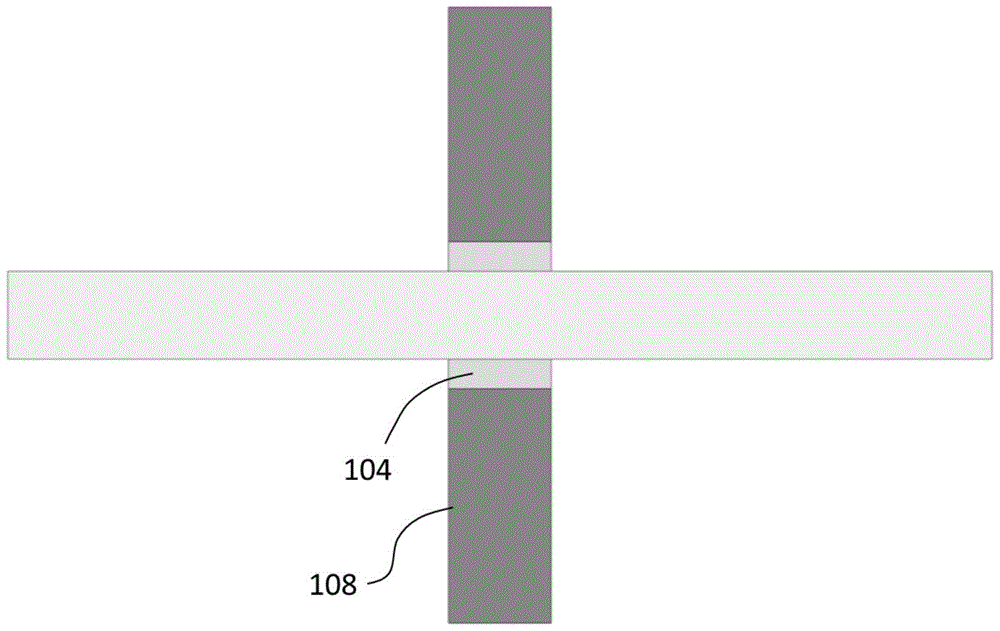

Periodic cross waveguide structure, electro-optical modulation structure and MZI (Mach-Zehnder Interference) structure

ActiveCN108490650AHigh refractive indexIncreased refractive index changeNon-linear opticsRefractive indexModulation efficiency

The invention provides a periodic cross waveguide structure, and an electro-optical modulation structure and an MZI (Mach-Zehnder Interference) structure both utilizing the same. The periodic cross waveguide structure is in the shape of ridge; strip-like interdigital n-type Si doped zones are formed at position, along a waveguide extension direction, at the ridge-shaped waveguide center; p-type SiGe doped zones are formed among the interdigital spaces; the n-type Si doped zones and the p-type SiGe doped zones are arranged in a periodic cross manner; the n-type Si doped zones are connected at one side of the interdigital spaces thereof and are connected with the bottom of the ridge-shaped waveguide center; gaps are formed between the interdigital bottoms of the n-type Si doped zones and theupper surface of the n-type Si doped zones connected at the bottom of ridge-shaped waveguide center, the p-type SiGe doped zones are arranged in the gaps, and thus, the p-type SiGe zones formed amongthe interdigital spaces are connected mutually. SiGe material carrier effective mass is reduced, free carrier plasma dispersion effect is improved, change of reflective index of the SiGe material isincreased, and accordingly, modulation efficiency, modulation speed, and modulation power consumption are optimized, and the effect of reducing size while improving modulation performance is achieved.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

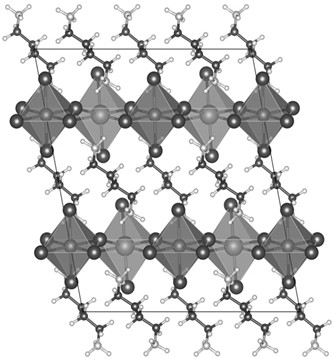

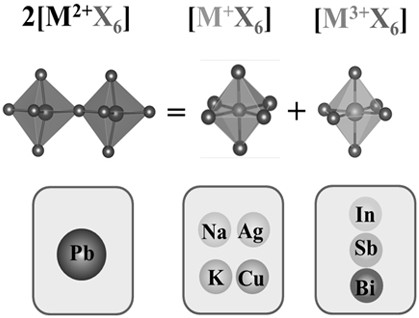

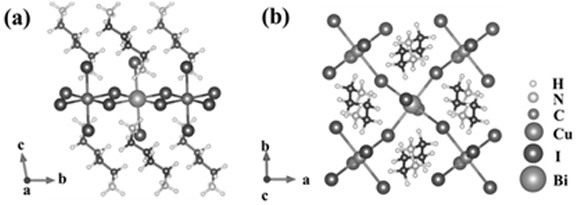

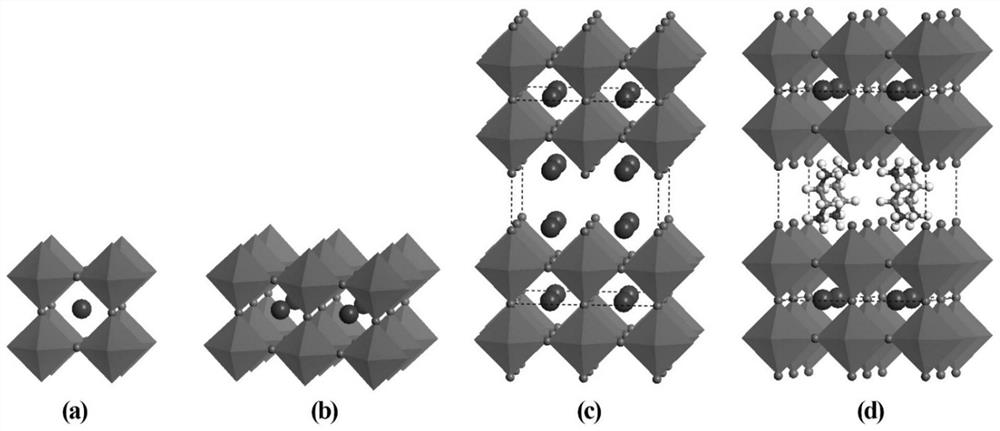

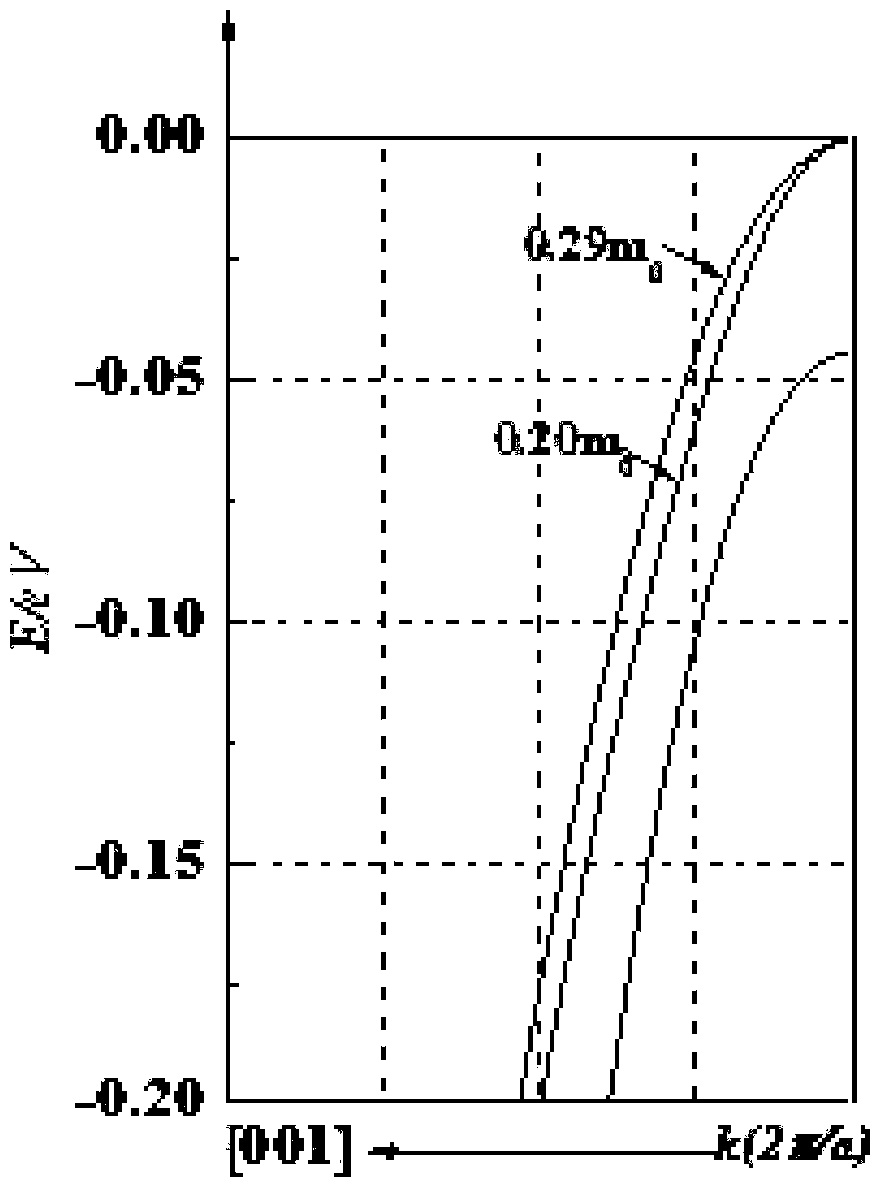

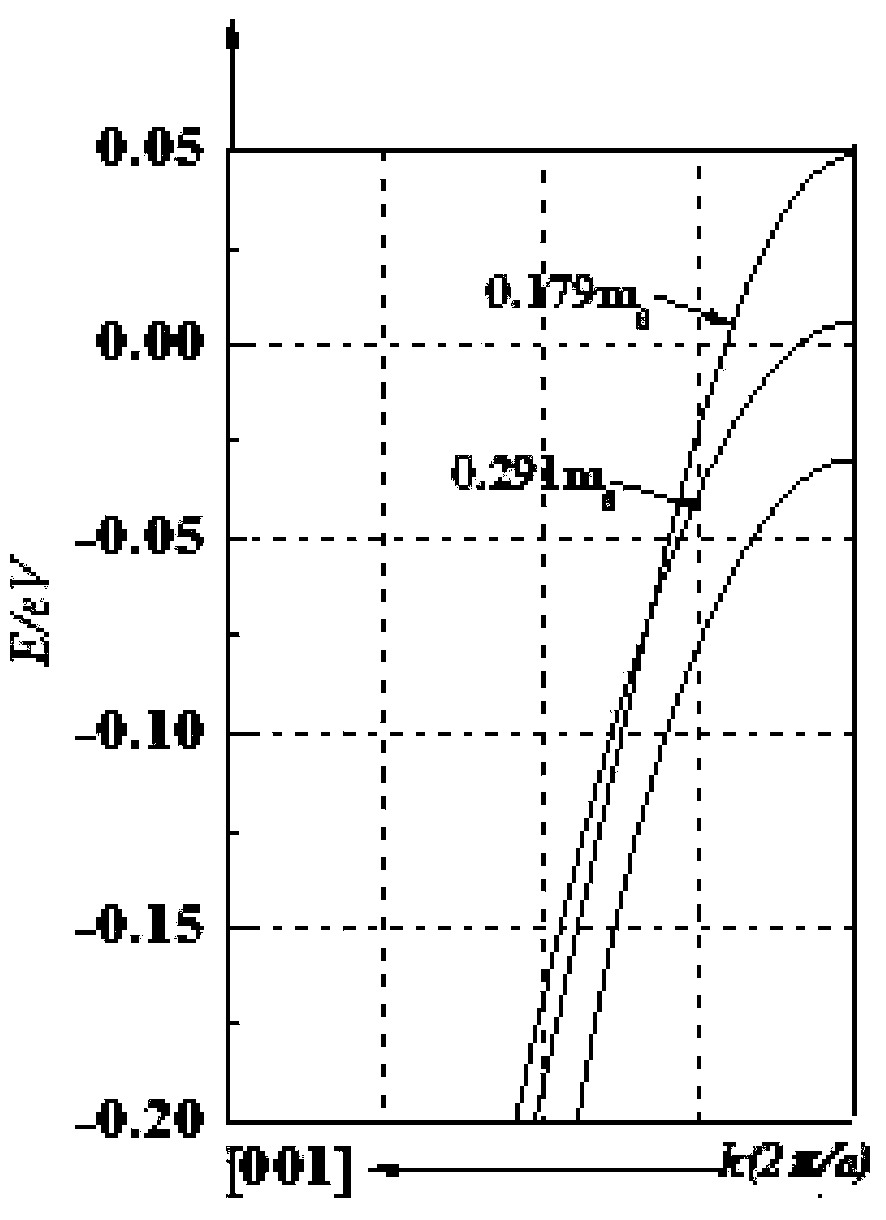

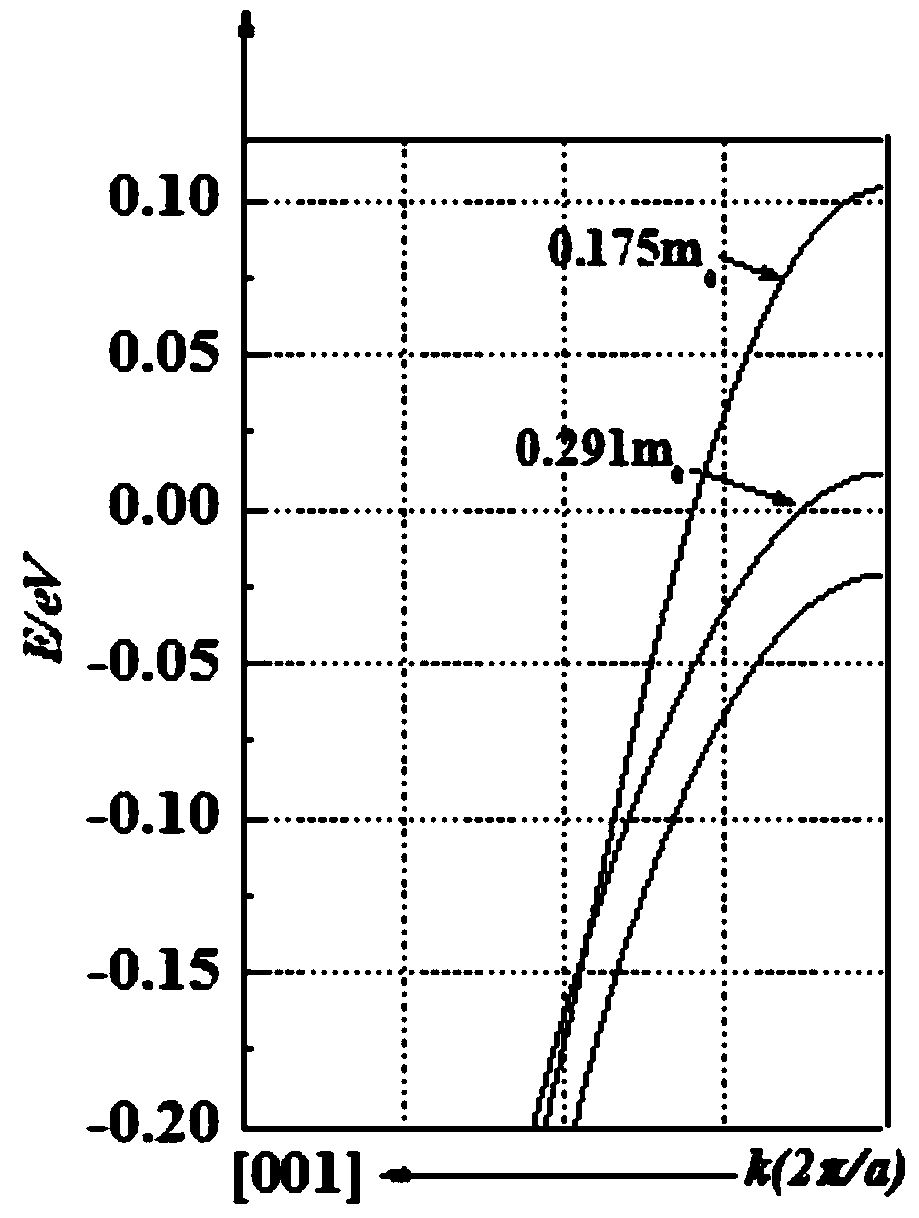

Narrow-band-gap, lead-free, stable and excellent-photoelectric-property DJ two-dimensional double perovskite

PendingCN113999121AEliminate toxicityNarrow bandgapOrganic chemistrySolid-state devicesNarrow bandBand gap

The invention discloses narrow-band-gap, lead-free, stable and excellent-photoelectric-property DJ two-dimensional double perovskite, belongs to the technical field of photovoltaic materials, and aims to provide a photovoltaic material with narrow direct band gap and high-stability photoelectric property, the band gap of the DJ two-dimensional double perovskite is smaller than 2eV, the structural general formula is BDA2M + M3 + X8, wherein M + is Cu + or Ag +, M3 + is Bi3 + or In3 + , and X is Br or I. According to the invention, firstly, two Pb (II) are completely substituted by B (I) / B (III) cations to eliminate the toxicity of Pb; and secondly, two-dimensional layered double perovskite is formed by introducing divalent organic cations, and the photoelectric property of the corresponding two-dimensional perovskite is improved. Results show that the layered double perovskite shows narrow direct band gap, better stability and photoelectric property equivalent to that of MAPbI3 in spectral limit maximum efficiency, and the perovskite is expected to become a novel potential photovoltaic material.

Owner:SHANXI UNIV

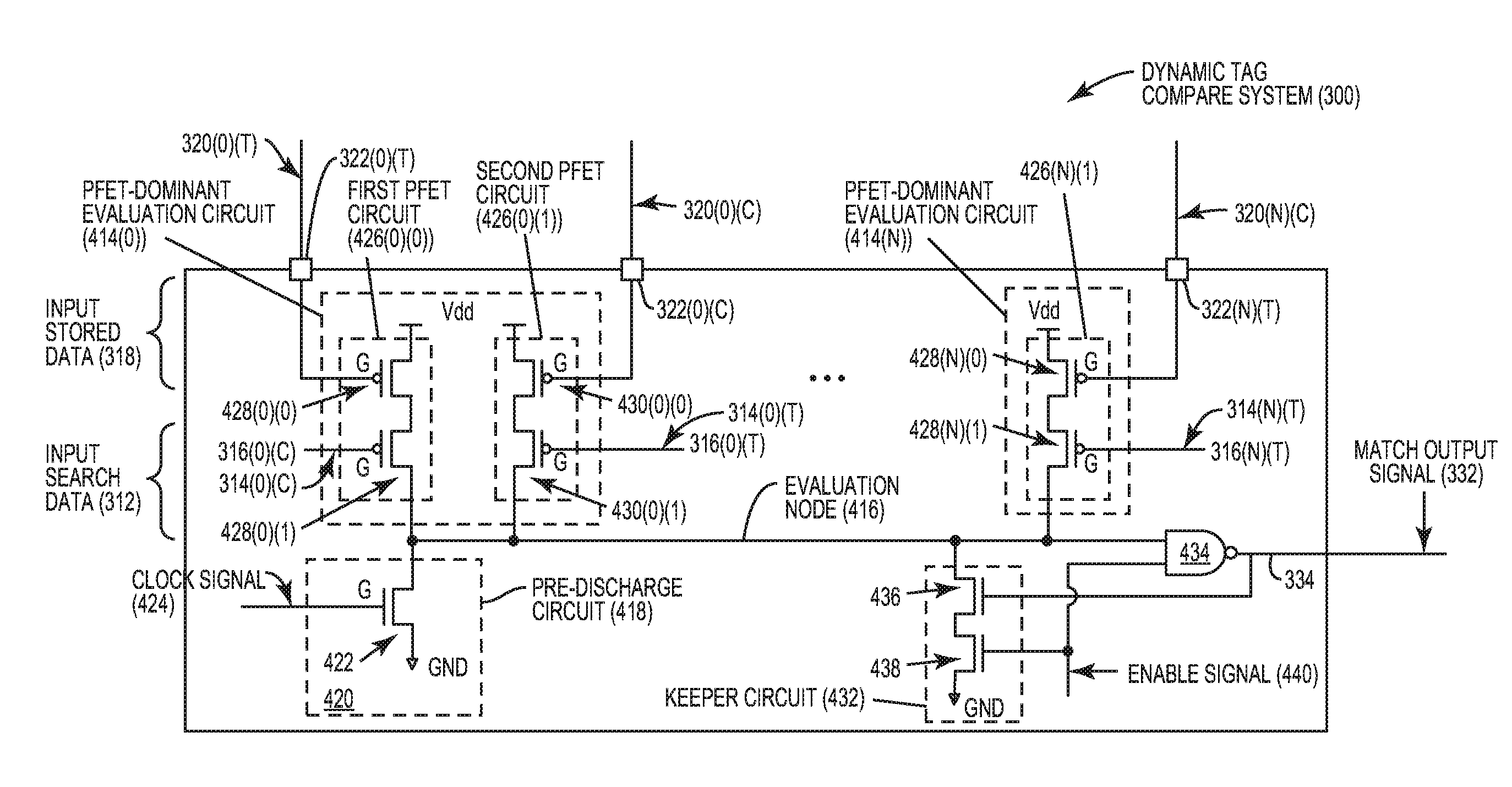

Dynamic tag compare circuits employing p-type field-effect transistor (PFET)-dominant evaluation circuits for reduced evaluation time, and related systems and methods

InactiveUS20160247568A1Effective mass reductionShorten assessment timeDigital storageReliability increase in field effect transistorsCamField-effect transistor

Dynamic tag compare circuits employing P-type Field-Effect Transistor (PFET)-dominant evaluation circuits for reduced evaluation time, and thus increased circuit performance, are provided. A dynamic tag compare circuit may be used or provided as part of searchable memory, such as a register file or content-addressable memory (CAM), as non-limiting examples. The dynamic tag compare circuit includes one or more PFET-dominant evaluation circuits comprised of one or more PFETs used as logic to perform a compare logic function. The PFET-dominant evaluation circuits are configured to receive and compare input search data to a tag(s) (e.g., addresses or data) contained in a searchable memory to determine if the input search data is contained in the memory. The PFET-dominant evaluation circuits are configured to control the voltage / value on a dynamic node in the dynamic tag compare circuit based on the evaluation of whether the received input search data is contained in the searchable memory.

Owner:QUALCOMM INC

Compressively strained si PMOS device based on channel orientation selection and its fabrication method

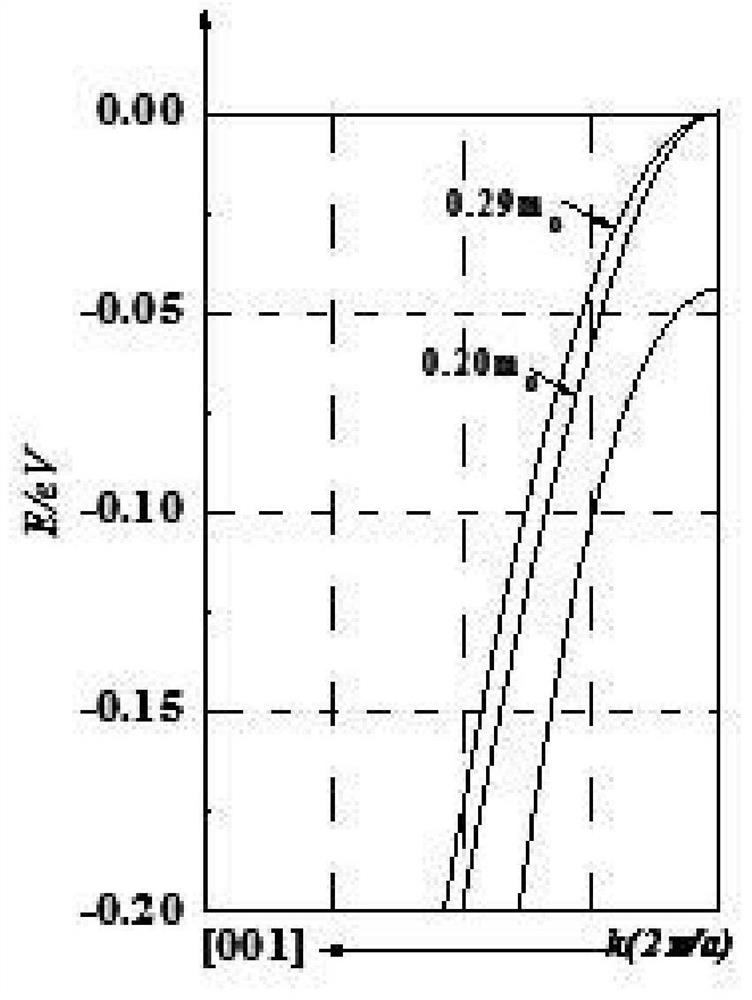

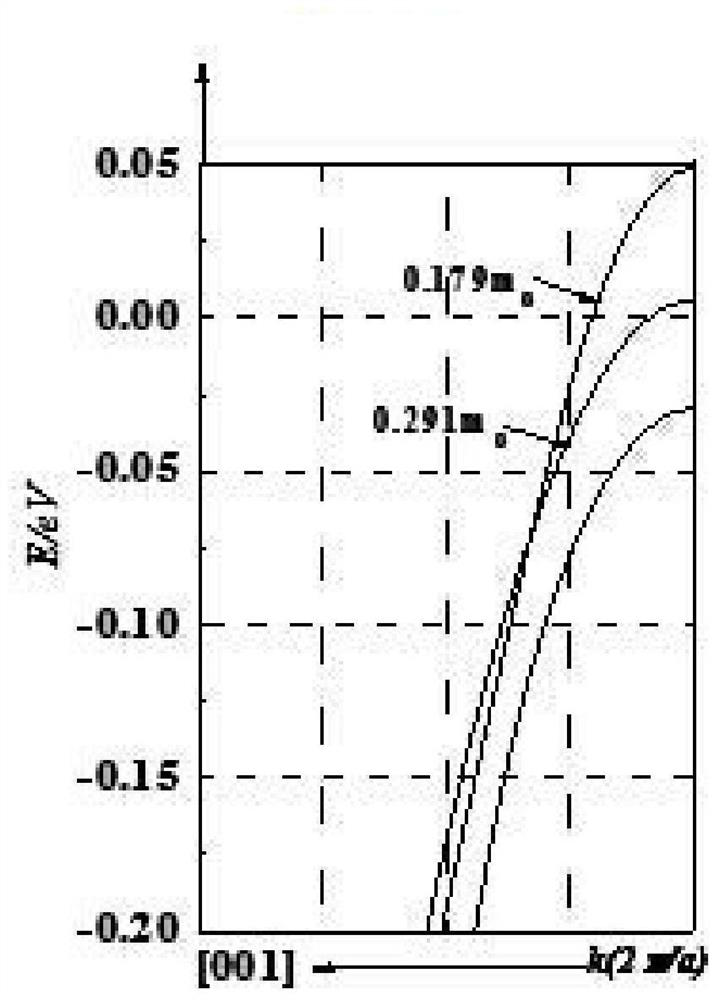

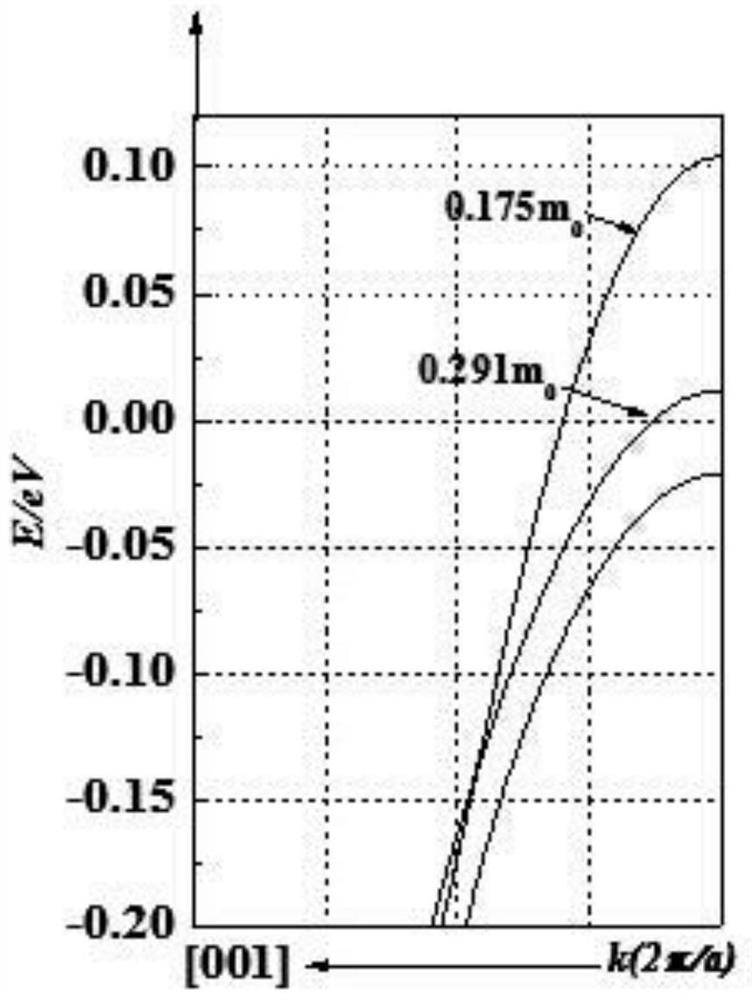

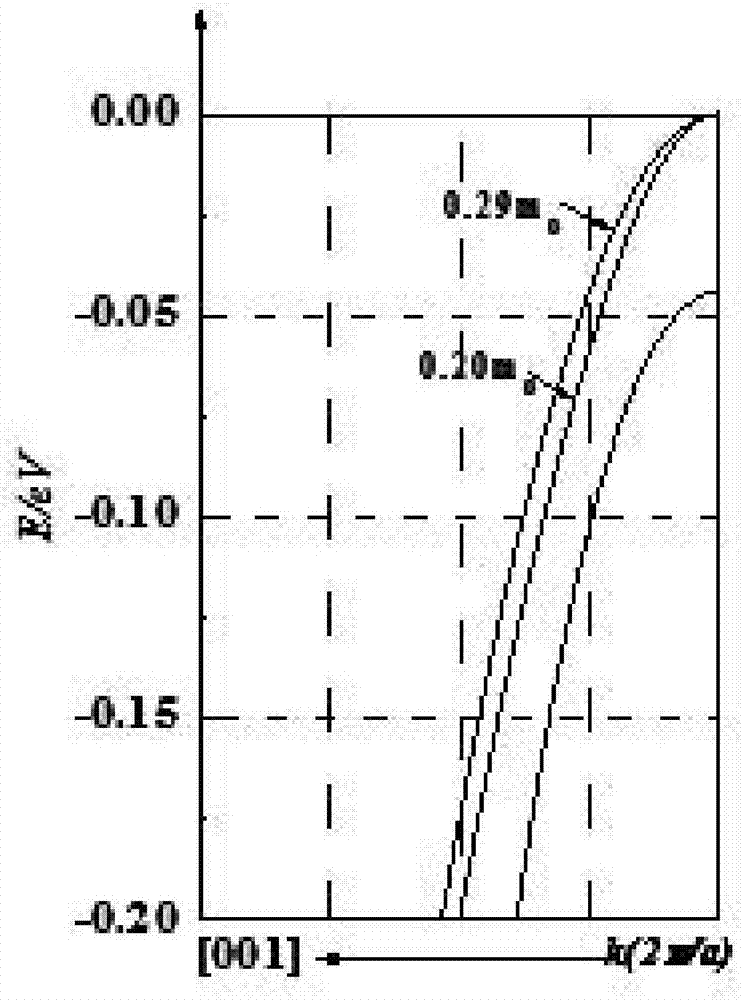

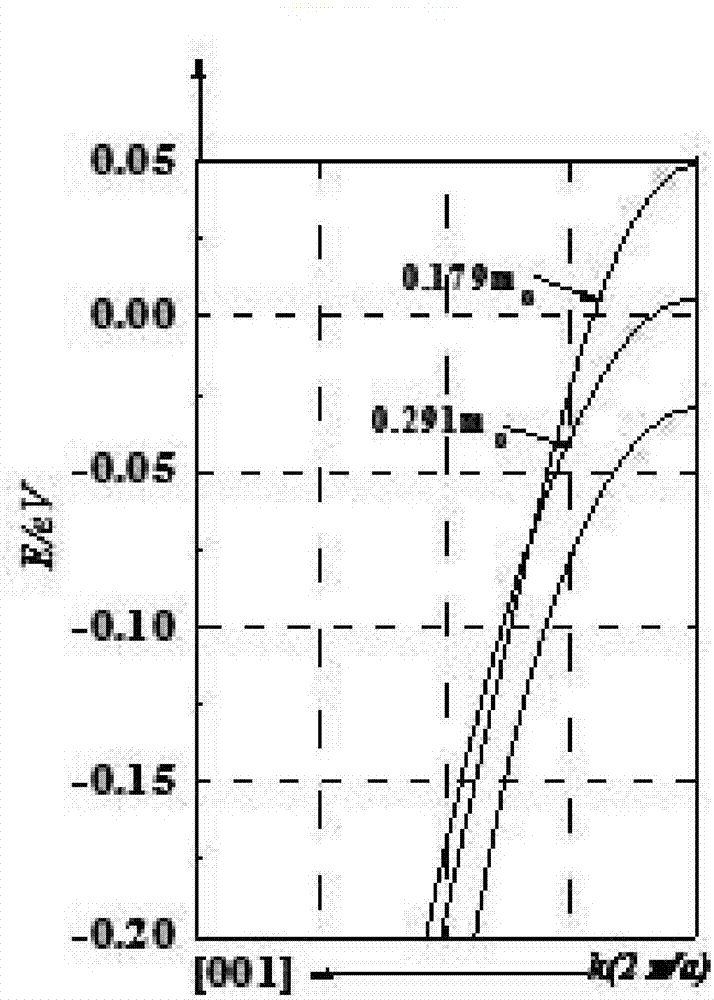

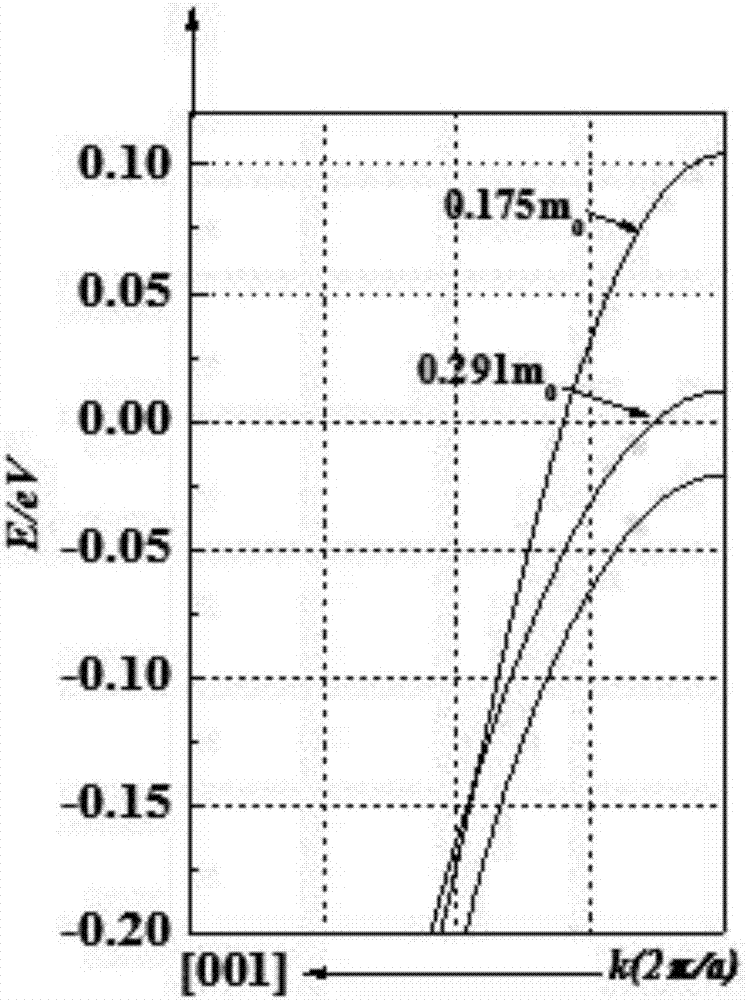

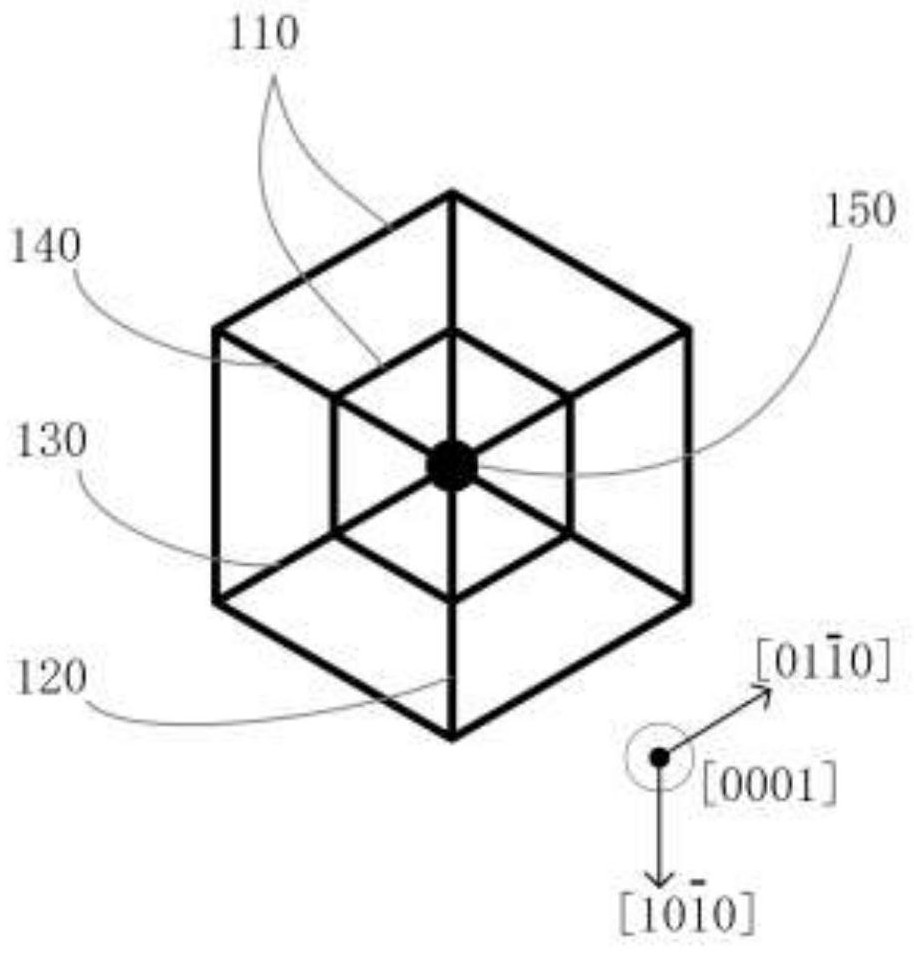

ActiveCN107507863BNo problem of "poor" mobility enhancementImprove drive characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricCrystal orientation

The invention relates to a compressive strain Si PMOS device based on channel crystal direction selection and a preparation method thereof. The preparation method comprises: selecting a single crystal Si substrate whose crystal plane is (001); growing a relaxed SiC epitaxial layer on the surface of the single crystal Si substrate; growing a strained Si layer on the surface of the relaxed SiC epitaxial layer; and growing a strained Si layer on the surface of the strained Si layer. Continuously grow the gate dielectric layer and the gate layer, and use the etching process to etch the gate layer and the gate dielectric layer to form the gate; use the self-alignment process to perform P-type ion implantation on the device surface different from the gate region to form the source and the drain; after passivation treatment on the surface of the device, a compressively strained SiPMOS device based on channel crystal orientation selection is formed. The present invention solves the traditional relaxation Si 1‑x Ge x The problem of poor hole mobility enhancement effect of substrate-induced biaxial strain Si material. At the same time, the [110] crystal orientation with low conductivity and effective mass is used as the biaxial Si / (001)Si 1‑x C x PMOS channel crystal orientation significantly improves biaxial strain Si / (001)Si 1‑x C x Material mobility and device performance.

Owner:XIDIAN UNIV

Compressive-strain Si PMOS device based on channel crystal orientation selection and preparation method thereof

ActiveCN107507863ANo problem of "poor" mobility enhancementImprove drive characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesCMOSGate dielectric

The invention relates to a compressive-strain Si PMOS device based on channel crystal orientation selection and a preparation method thereof. The preparation method comprises the following steps: selecting a single-crystal Si substrate with a (001) type crystal plane; growing a relaxed SiC epitaxial layer on the surface of the single-crystal Si substrate; growing a strained Si layer on the surface of the relaxed SiC epitaxial layer; growing a gate dielectric layer and a gate layer on the surface of the strained Si layer continuously and etching the gate layer and the gate dielectric layer by using the etching process to form a gate; carrying gout P type ion implantation on the device surface different from a gate region by using a self-aligned process so as to form a source and a drain; and carrying out passivation processing on the device surface to form a compressive-strain Si CMOS device based on channel crystal orientation selection. Therefore, a problem of poor hole mobility enhancement effect of the biaxial strained Si material due to the traditional relaxed Si(1-x)Gex substrate is solved. The low-conductivity effective-quality [110] crystal orientation is used as biaxial strained Si / (001) Si(1- x)Cx PMOS channel orientation, so that the mobility ratio of the biaxial strained Si / (001) Si(1-x)Cx material and the performance of the device are improved.

Owner:XIDIAN UNIV

Lateral double-diffusion field effect transistor, manufacturing method, chip and circuit

ActiveCN114267724AHigh speedEffective mass reductionSemiconductor/solid-state device manufacturingSemiconductor devicesTensile strainHemt circuits

The invention provides a lateral double-diffusion field effect transistor, a manufacturing method, a chip and a circuit, and the transistor comprises a substrate which is provided with a high-voltage N-type well; the first N-type drift region, the P-type body region and the second N-type drift region are adjacently arranged and are formed in the high-voltage N-type well; the first tensile strain region is formed in the first N-type drift region; the second tensile strain region is formed in the second N-type drift region; the first drain electrode is formed in the first tensile strain area; the second drain electrode is formed in the second tensile strain area; the first source electrode and the second source electrode are formed in the P-type body region; the substrate electrode is formed between the first source electrode and the second source electrode; the first grid electrode is formed on the upper surfaces of the first N-type drift region and the P-type body region; and the second grid electrode is formed on the upper surfaces of the P-type body region and the second N-type drift region, and a gap is formed between the second grid electrode and the first grid electrode. According to the transistor provided by the invention, the mobility of carriers in a channel can be improved, and the driving capability and speed of the transistor are improved.

Owner:BEIJING CHIP IDENTIFICATION TECH CO LTD +1

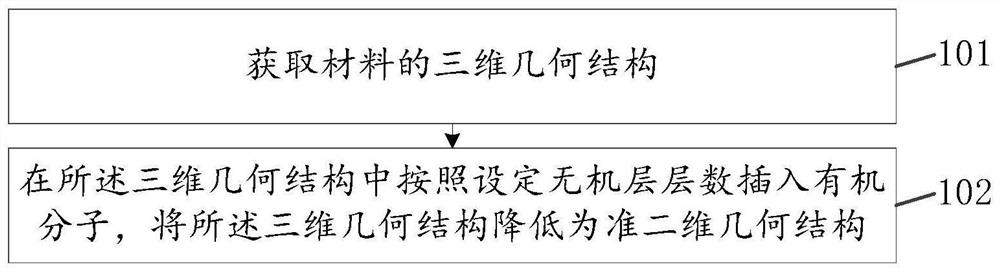

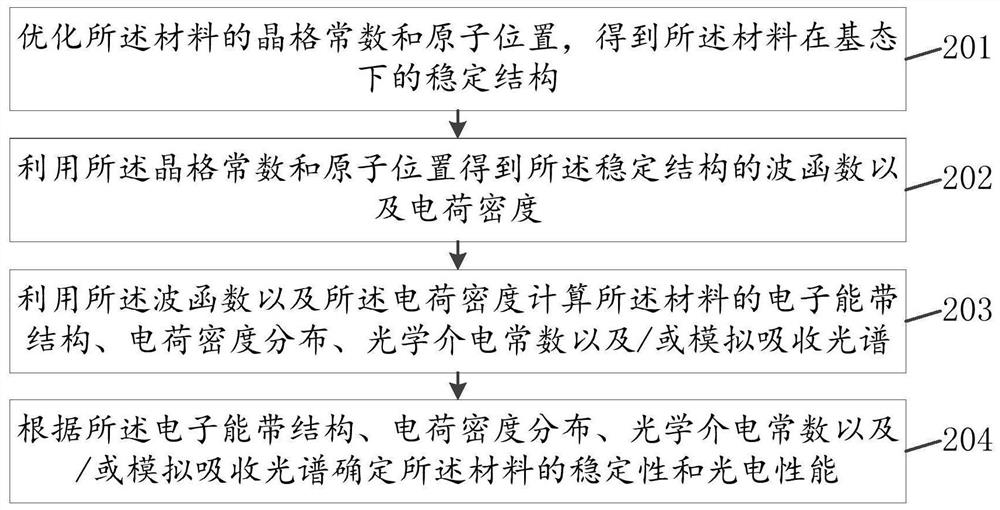

Organic Intercalation Methods, Devices, Materials, Test Methods, Applications, and Solar Panels

ActiveCN111180584BImprove stabilityImprove photoelectric performanceSolid-state devicesSemiconductor/solid-state device manufacturingMaterials scienceOrganic molecules

The invention discloses an organic intercalation method, device, material, testing method, application and solar panel, and relates to the field of materials, mainly in that the stability and photoelectric performance of the material can be improved, and the band gap of the material can be determined through the performance test conclusion. The width is adjusted to obtain a material that meets the band gap width requirements. The method includes: obtaining the three-dimensional geometric structure of the material; inserting organic molecules in the three-dimensional geometric structure according to the set number of inorganic layers, and reducing the three-dimensional geometric structure to a quasi-two-dimensional geometric structure; the organic molecules are used for Reduce the electronically effective mass of the material and / or increase the stability of the material. The present invention is applicable to the organic intercalation of materials.

Owner:NINGBO UNIVERSITY OF TECHNOLOGY

Dynamic tag compare circuits employing P-type field-effect transistor (PFET)-dominant evaluation circuits for reduced evaluation time, and related systems and methods

InactiveUS9627064B2Effective mass reductionShorten assessment timeDigital storageReliability increase in field effect transistorsProcessor registerCam

Owner:QUALCOMM INC

Compressively strained si CMOS device based on channel orientation selection and its fabrication method

ActiveCN107507806BNo problem of "poor" mobility enhancementImprove drive characteristicsTransistorSolid-state devicesGate dielectricCrystal orientation

The invention relates to a compressive-strain Si CMOS device based on channel crystal orientation selection and a preparation method thereof. The preparation method comprises: selecting a Si substrate; growing a relaxed Si epitaxial layer; growing a strained Si layer; forming a shallow trench isolation; forming an N type well region and a P type well region by using an ion implantation process; growing a gate dielectric layer and a gate electrode continuously on the surface of the strained Si layer and etching the gate layer and the gate dielectric layer by using an etching process to form gates respectively; forming a PMOS source-drain region and an NMOS source-drain region based on a self-aligned process; and forming source-drain contact in the source-drain regions and then forming a CMOS device finally. Therefore, a problem of poor hole mobility enhancement effect of the biaxial strained Si material due to the traditional relaxed Si(1-x)Gex substrate is solved. The low-conductivity effective-quality [110] crystal orientation is used as biaxial strained Si / (001) Si(1- x)Cx PMOS channel orientation and the high-electron-mobility [100] crystal orientation as biaxial strained Si / (001) Si(1-x)CxNMOS channel orientation, so that the mobility ratio of the biaxial strained Si / (001) Si(1-x)Cx material and the performance of the device are improved.

Owner:XIDIAN UNIV

Double-gate p-channel mosfet with compressive strain film strain source and its preparation method

InactiveCN104022152BIncrease working currentEffective mass reductionSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSemiconductor materials

The invention provides a double-gate p-channel MOSFET with a compression strain thin film strain source and a preparation method of the double-gate p-channel MOSFET with the compression strain thin film strain source. The MOSFET comprises a source region, a drain region, a conducting channel region, a gate dielectric layer, a grid electrode, an insulating dielectric layer and a compression strain thin film strain layer. The gate dielectric layer is formed on a first surface of a semiconductor material and located on the side face of a first conducting surface and the side face of a second conducting surface of the conducting channel region. The grid electrode is formed on the first surface of the semiconductor material and located on the side face of the gate dielectric layer. The insulating dielectric layer is formed on the side wall of the grid electrode, the side wall of a source electrode and the side wall of a drain electrode. The compression strain thin film strain layer is formed on the side wall of the insulating dielectric layer and used for leading compression strain in the channel direction into the conducting channel region. The surface of the MOSFET is covered with the compression strain thin film strain layer, and the large compression strain in the channel direction is led into the conducting channel region; as a result, effective mass of holes can be reduced, the migration rate of the holes is increased, the working current of the MOSFET is increased, and on-resistance is lowered.

Owner:CHONGQING UNIV

Method for improving erasing speed of SONOS (Silicon Oxide Nitride Oxide Silicon) by utilizing strained silicon technology

ActiveCN102543890BImprove programming efficiencyImprove programming speedSolid-state devicesSemiconductor/solid-state device manufacturingSilicon oxidePhysics

The invention discloses a method for manufacturing a SONOS unit transistor with high erasing and writing speed. It is characterized in that after forming the sidewalls of the gate on a P-type substrate that forms several shallow trench isolation areas, it also includes the following steps: 1. Precipitate a barrier layer to cover the transistor; Step 2, etch and remove the barrier layer covering the NMOS area to expose the NMOS area; Step 2, etch the silicon in the active areas on both sides of the gate electrode of the NMOS area; Step 3: Precipitate silicon carbide in the active area through a selective epitaxial process; Step 4: Perform high-temperature annealing to cause the silicon carbide to generate tensile stress on the channel. The energy band of silicon is split. The result of the split is that the effective mass of electrons along the channel direction is reduced. At the same time, the energy valley scattering probability of electrons is also reduced, which significantly increases the electron mobility of the SONOS unit transistor, thus improving the hot electron injection mechanism. SONOS programming efficiency and speed.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Lateral double diffused field effect transistor, manufacturing method, chip and circuit

ActiveCN114267724BHigh speedEffective mass reductionSemiconductor/solid-state device manufacturingSemiconductor devicesHemt circuitsEngineering

The invention provides a lateral double-diffused field effect transistor, a manufacturing method, a chip and a circuit. The transistor includes: a substrate with a high-voltage N-type well; a first N-type drift region, a P-type body region and a second The N-type drift region is formed in the high-voltage N-type well; the first strained region is formed in the first N-type drift region; the second strained region is formed in the second N-type drift region; the first drain is formed in the second N-type drift region. One strain region; the second drain, formed in the second strain region; the first source and the second source, formed in the P-type body region; the substrate electrode, formed in the first source and the second source between; the first gate, formed on the upper surface of the first N-type drift region and the P-type body region; the second gate, formed on the upper surface of the P-type body region and the second N-type drift region, and the second gate A space is formed between the electrode and the first grid. The transistor provided by the invention can improve the mobility of carriers in the channel, and improve the driving ability and speed of the transistor.

Owner:BEIJING CHIP IDENTIFICATION TECH CO LTD +1

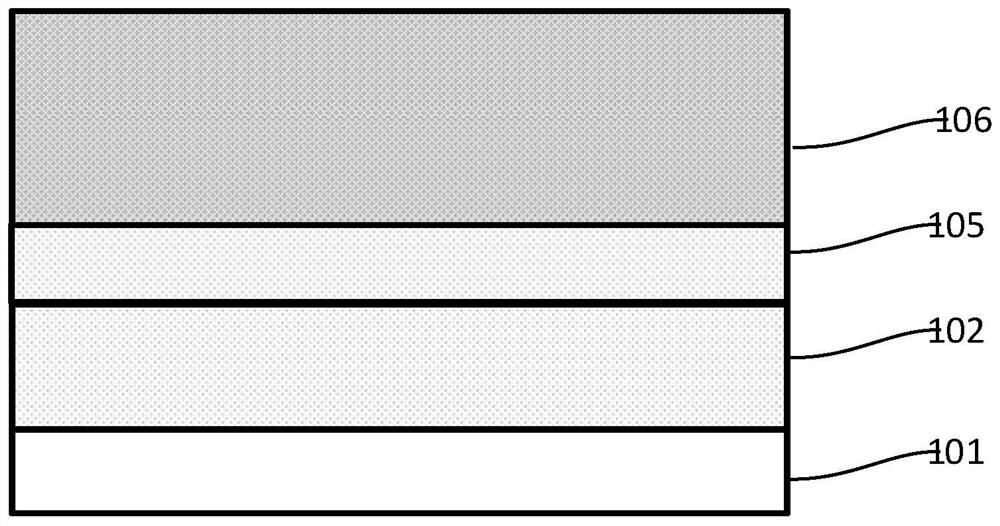

FD-SOI substrate structure and device structure

PendingCN113675218AImprove performanceFlow restrictionSolid-state devicesSemiconductor devicesCrystallographySoi substrate

The invention provides an FD-SOI substrate structure and device structure. The FD-SOI substrate structure comprises a silicon substrate, a buried oxide layer, a top germanium-silicon layer and a germanium oxynitride layer which are stacked in sequence. The substrate structure adopts a stack structure of the top germanium-silicon layer and the germanium oxynitride layer, the top germanium-silicon layer serves as a channel of the device, doping is not needed, the thickness is low, leakage current between a source electrode and a drain electrode can be greatly reduced, on the other hand, the top germanium-silicon layer can greatly improve the hole mobility, and then the performance of the device is improved. The germanium oxynitride layer covers the top germanium-silicon layer, so that water-soluble GeO2 or volatile GeO can be effectively prevented from being formed on the surface of the germanium-silicon channel, and the stability of the device is improved.

Owner:上海功成半导体科技有限公司

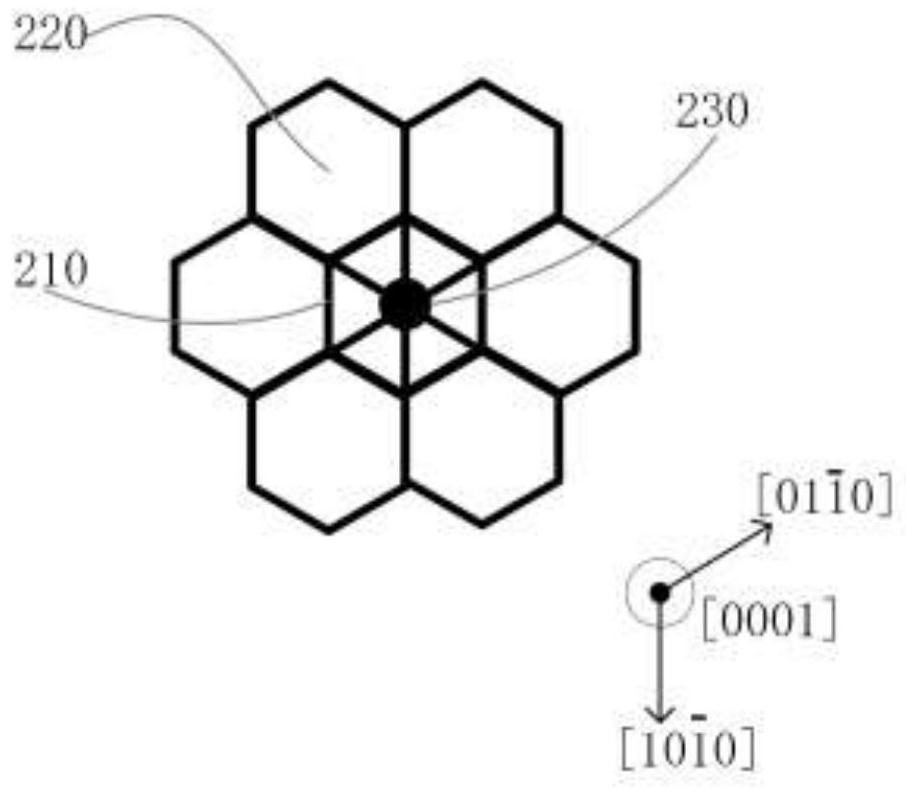

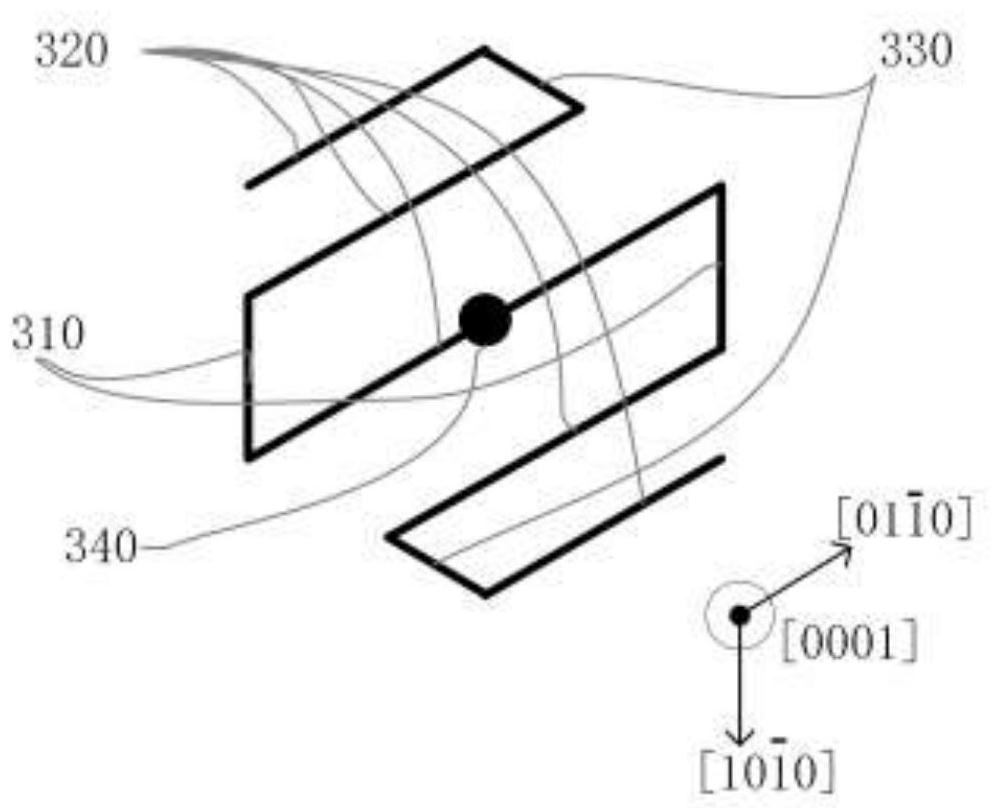

Group-III nitride p-type ohmic electrode structure with low contact resistance

ActiveCN109461770BImproved contact characteristicsEffective mass reductionLaser detailsSemiconductor lasersOhmic contactDevice material

The invention relates to the technical field of semiconductor devices, in particular to an III-nitrides p-type ohmic electrode structure with low contact resistance. The direction of an electrode pattern line body of the electrode structure is consistent with a first crystal orientation or a second crystal orientation and an equivalent crystal orientation of the first crystal orientation and the second crystal orientation of III-nitrides; after clockwise rotating for 120 degrees, the first crystal orientation is parallel to the second crystal orientation; and a bonding wire electrode part of the electrode structure is located at the geometric center of the electrode structure or at a cross point of any electrode pattern line body. The electrode structure in the invention aims to obtain good ohmic contact characteristic on the p-type III-nitrides material; the high tunneling probability characteristic of a hole in the crystal orientation and the equivalent crystal orientation of the III-nitrides material is effectively utilized by the proposed electrode structure along the crystal orientation, thereby reducing electrical resistivity of ohmic contact.

Owner:SUN YAT SEN UNIV

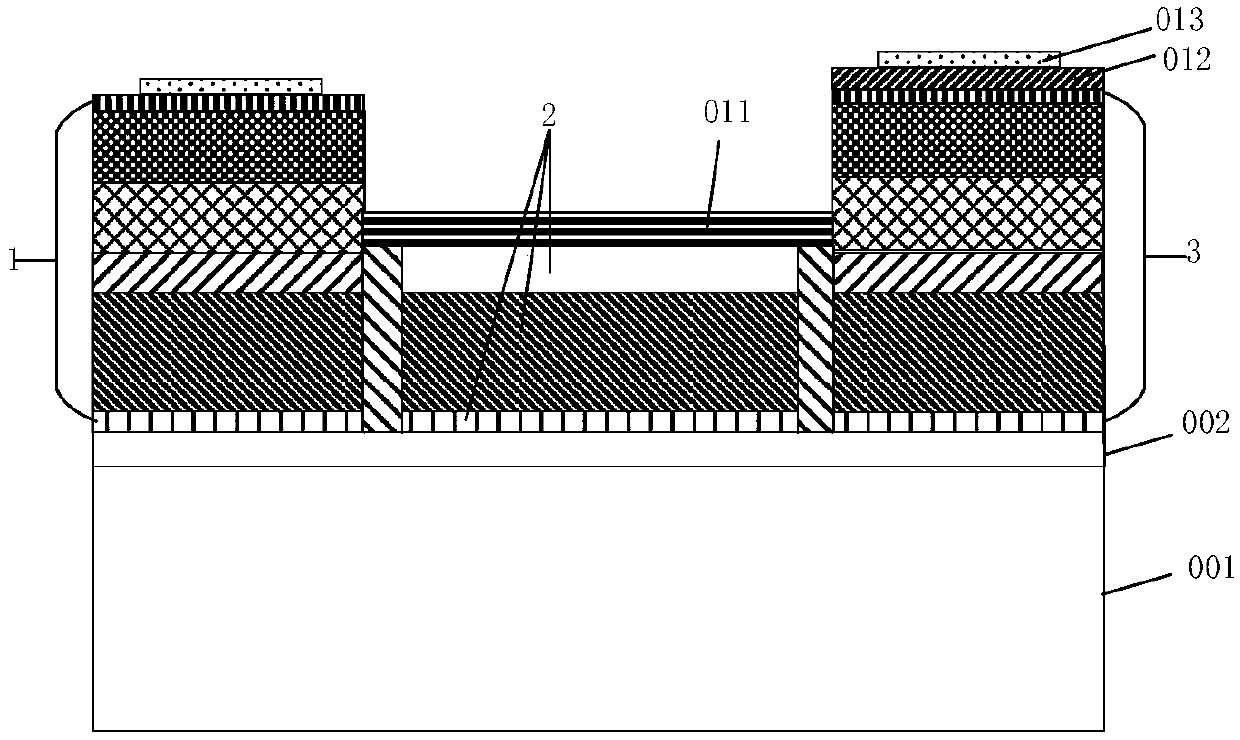

Si-based modified Ge monolithic same-layer photoelectric device

InactiveCN111354821AHighly integratedReduce processing costsFinal product manufactureSemiconductor devicesIsolation layerEngineering

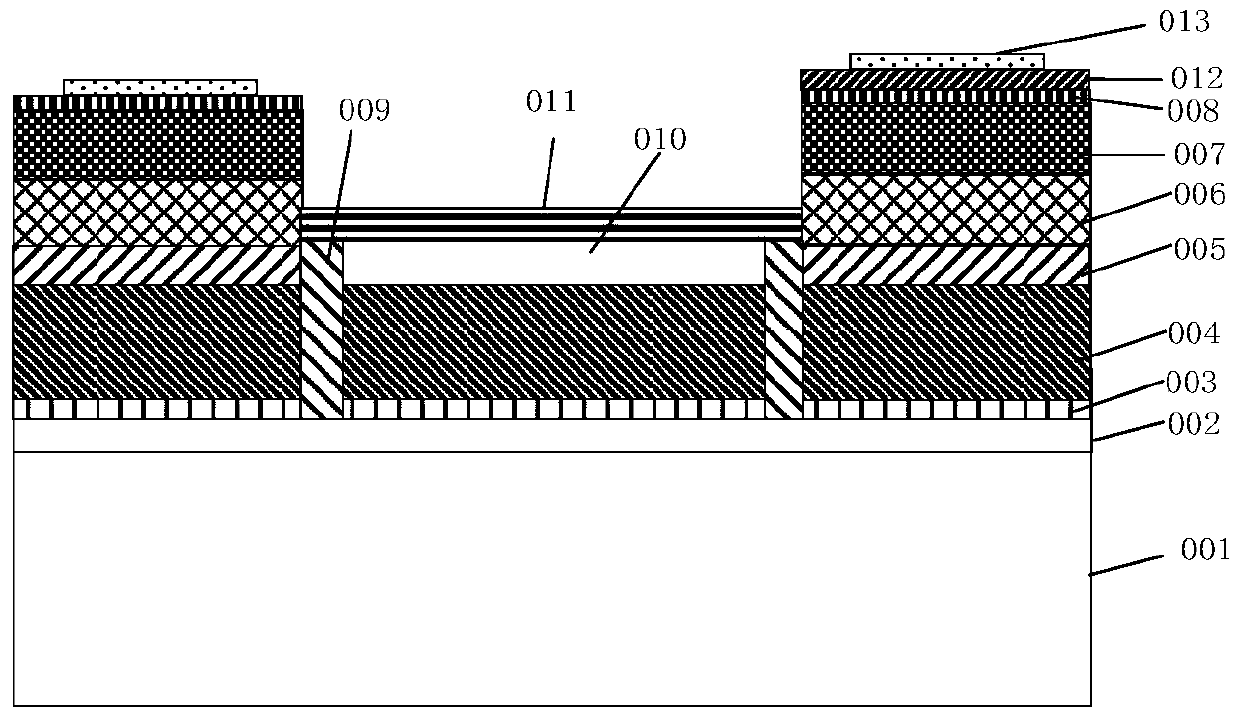

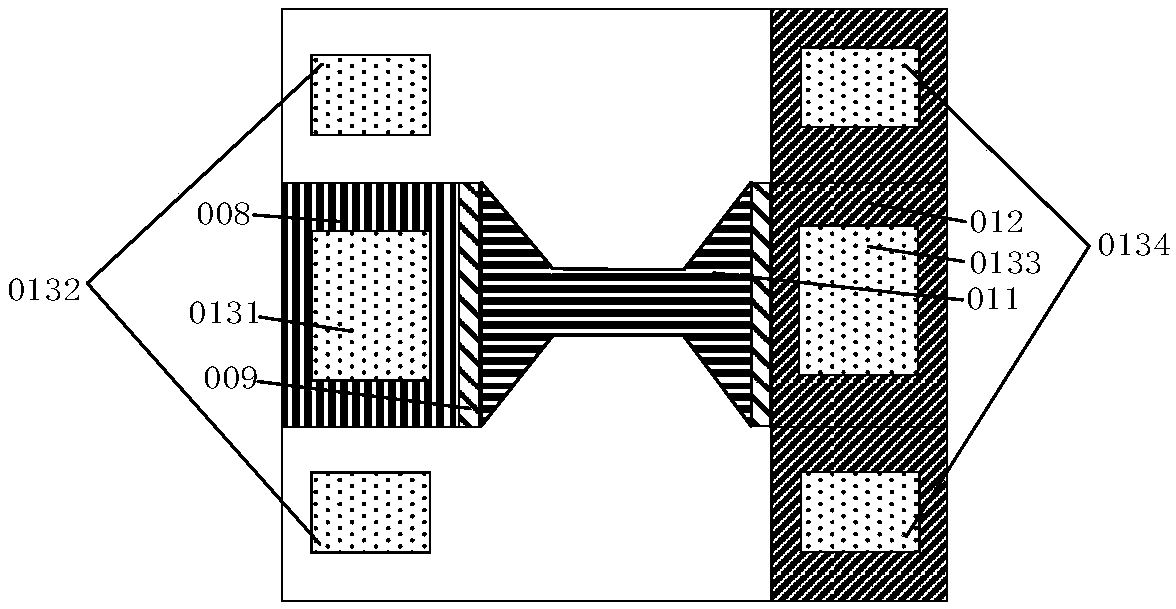

The invention relates to a Si-based modified Ge monolithic same-layer photoelectric device, which comprises a substrate (001), a buried layer (002), a light emitter part (1), a waveguide part (2), a detector part (3) and an electrode (013). Isolation layers (009) are respectively arranged between the waveguide part (2) and the light emitter part (1) and between the waveguide part (2) and the detector part (3); the outer surfaces of the waveguide part (2) and the isolation layer (3) are coated with a first stress film (011); and the outer surface of the detector part (3) and the upper surface of the buried layer (002) are coated with a second stress film (012). According to the technical scheme, the light emitter part (1), the waveguide part (2) and the detector part (3) are integrally arranged on the same substrate (001) and the buried layer (002), so that the device integration degree is high, and the process cost is low; and the waveguide part (2) and the detector part (3) are subjected to energy band modulation through the first stress film (011) and the second stress film (012), so that the forbidden band widths of the light emitter part (1), the waveguide part (2) and the detector part (3) meet the requirements.

Owner:XIAN CREATION KEJI CO LTD

Organic intercalation method, organic intercalation device, organic intercalation material, organic intercalation test method, application of material, and solar panel

ActiveCN111180584AImprove stabilityImprove photoelectric performanceSolid-state devicesSemiconductor/solid-state device manufacturingOrganic chemistryPolymer chemistry

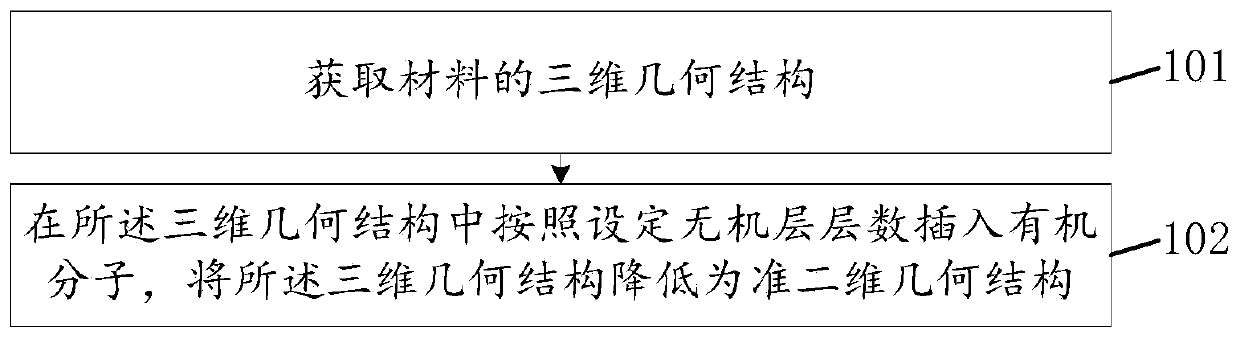

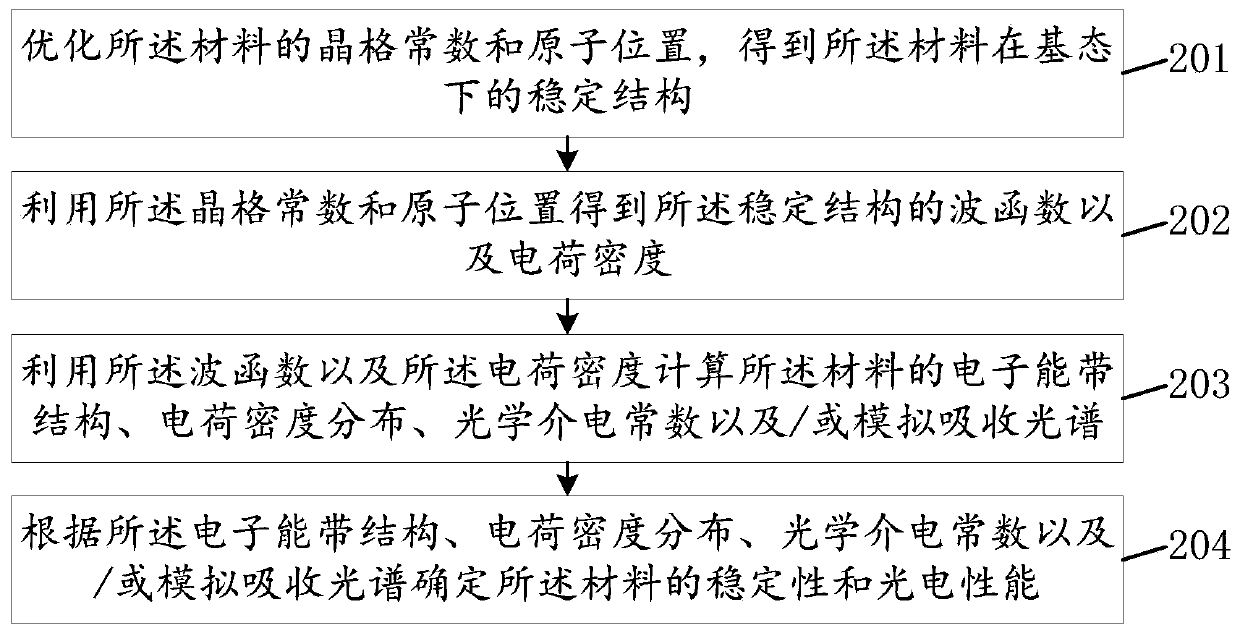

The invention discloses an organic intercalation method, an organic intercalation device, a material, a test method, application of material, and a solar panel, relates to the field of materials, andmainly aims to improve the stability and photoelectric properties of the material and adjust the band gap width of the material through a performance test conclusion so as to obtain the material meeting the band gap width requirement. The method comprises the following steps: acquiring a three-dimensional geometric structure of a material; inserting organic molecules into the three-dimensional geometric structure according to the set number of inorganic layers, and reducing the three-dimensional geometric structure into a quasi-two-dimensional geometric structure; and using the organic molecules for reducing the electron effective mass of the material and / or increasing the stability of the material. The organic intercalation method, the organic intercalation device, the material, the testmethod, application of material, and the solar panel are suitable for organic intercalation of materials.

Owner:NINGBO UNIVERSITY OF TECHNOLOGY