Gate finger gradually-widened GaN FinFET structure and preparation method thereof

A gate finger and heterostructure technology, which is applied in the field of GaNFinFET structure with gradually widened gate fingers and its preparation, can solve the problems that the FinFET structure is difficult to take into account the withstand voltage and frequency of the device, and it is difficult to realize high-power high-frequency devices, etc., to achieve relief Effects of current collapse, mitigation of scattering, and improvement of withstand voltage performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0046] This embodiment provides a method for fabricating a GaN FinFET structure with gradually wider gate fingers, using a GaN / InGaN double channel instead of a traditional GaN single channel. On the one hand, the effective mass of carriers in the InGaN channel is lower than that of the GaN channel. The effective mass of the carrier can effectively improve the drift velocity of the upper limit carrier in the FinFET structure, and realize the high frequency response of the FinFET structure. At the same time, the relatively narrow band gap of the InGaN material can make the two-dimensional electron gas (2DEG) better Confined in the channel, effectively alleviate carrier scattering and current collapse; in addition, the gate fingers in the FinFET structure are designed to gradually widen from the source to the drain direction, effectively improving the withstand voltage performance of the FinFET structure.

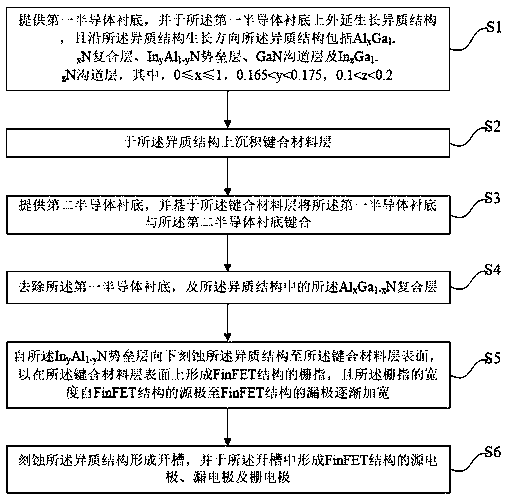

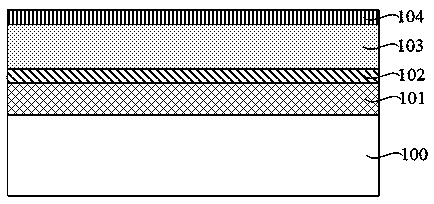

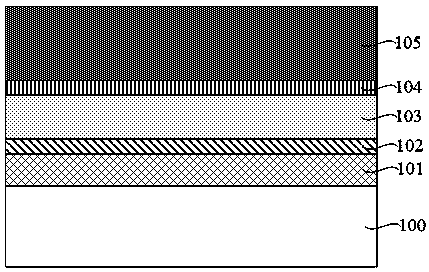

[0047] Such as Figure 1 to Figure 12 Shown, described preparation metho...

Embodiment 2

[0075] This embodiment provides a GaN FinFET structure with gradually wider gate fingers. The FinFET structure can be prepared by the preparation method of the first embodiment above, but is not limited to the preparation method described in the first embodiment, as long as the structure can be formed. For the beneficial effects achieved by the FinFET structure, please refer to Embodiment 1, which will not be described in detail below.

[0076] Such as Figure 6 to Figure 9 As shown, the FinFET structure includes:

[0077] a second semiconductor substrate 106;

[0078] a bonding material layer 105 located on the second semiconductor substrate 106;

[0079] The FinFET structure is located on the bonding material layer 105, and the FinFET structure includes: a gate 113, a source 108, a drain 109 and a gate finger 107, wherein the source 108, the drain 109 and the gate finger 107 are composed of Cascading In y al 1-y N barrier layer 102, GaN channel layer 103 and In z Ga 1...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More