Digital-to-analog converter capable of optimizing power consumption and output signal-to-noise ratio

A digital-to-analog converter and output signal-to-noise ratio technology, applied in digital-to-analog converters and other directions, can solve the problems of high circuit power consumption and high operating clock frequency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

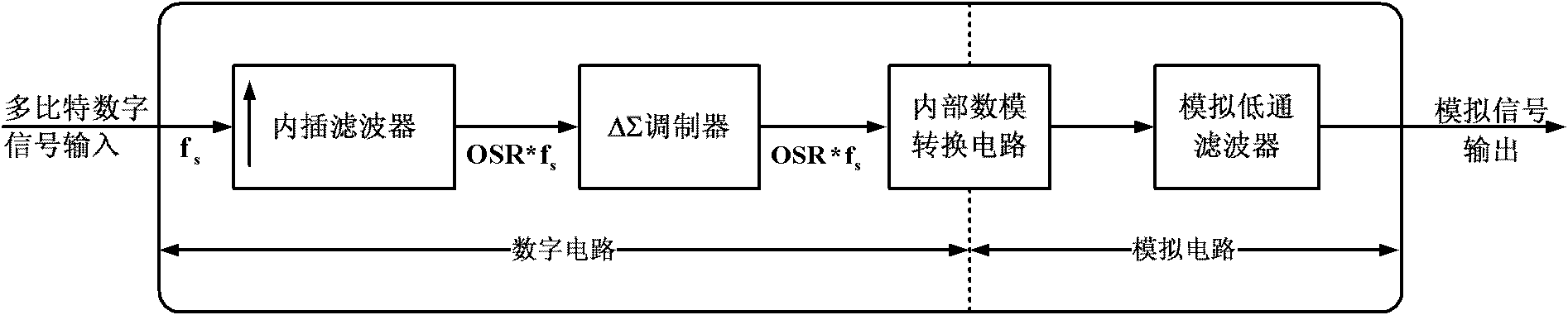

Problems solved by technology

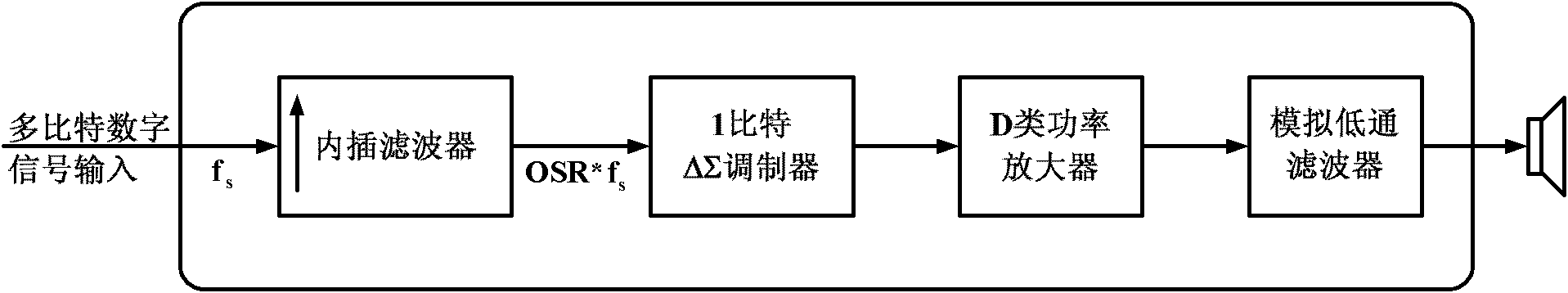

Method used

Image

Examples

Embodiment Construction

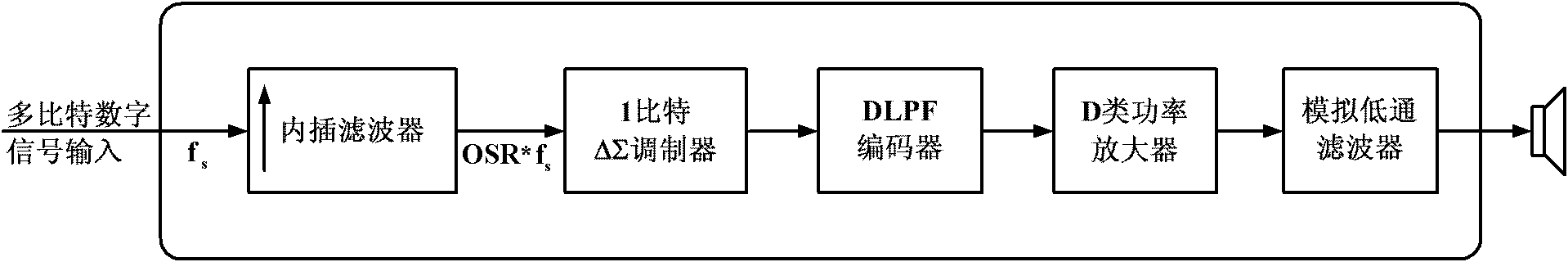

[0021] A ΔΣ digital-to-analog converter for optimizing power consumption and output signal-to-noise ratio proposed by the present invention is described in detail as follows with reference to the drawings and embodiments:

[0022] The digital-to-analog converter for optimizing power consumption and output signal-to-noise ratio of the present invention adopts a delta-sigma digital-to-analog converter, which includes an interpolation filter, a 1-bit delta-sigma modulator, a class D power amplifier and an analog low The pass filter is characterized in that it also includes a DLPF (Digital Low Pass Filter) encoder connected between the 1-bit ΔΣ modulator and the class D power amplifier; image 3 As shown; among them, the input multi-bit digital signal is up-sampled through the interpolation filter, and then the noise shaping is completed by the 1-bit ΔΣ modulator, and the 1-bit code output by the modulator is encoded by the DLPF encoder, DLPF The 2-bit code output by the encoder contr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More