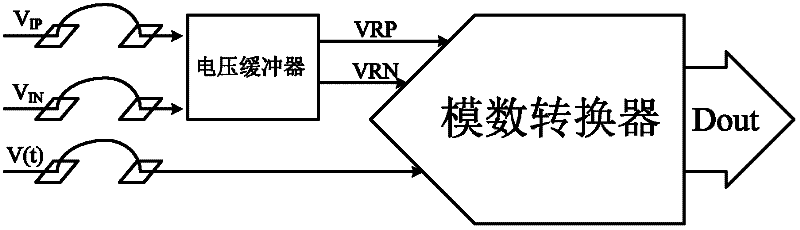

Voltage buffer applied to high-speed analogue-to-digital converter

A voltage buffer, analog-to-digital converter technology, applied in the direction of analog-to-digital converter, physical parameter compensation/prevention, etc., can solve problems such as limiting reference voltage speed and large time constant

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

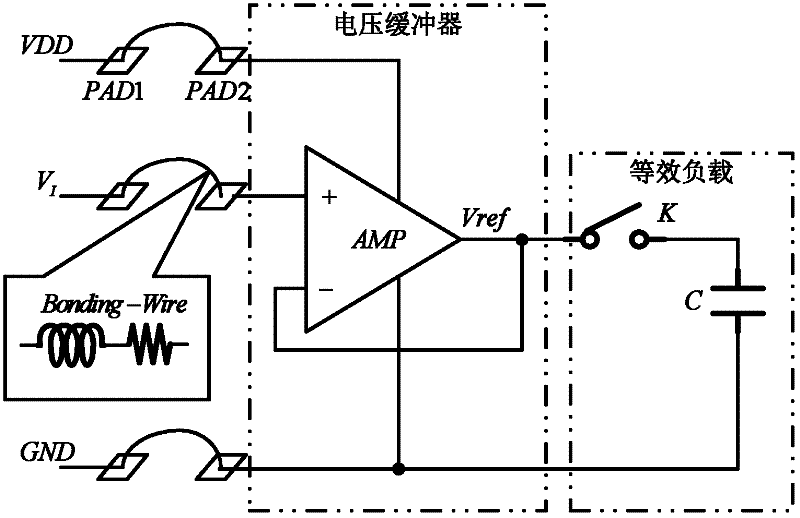

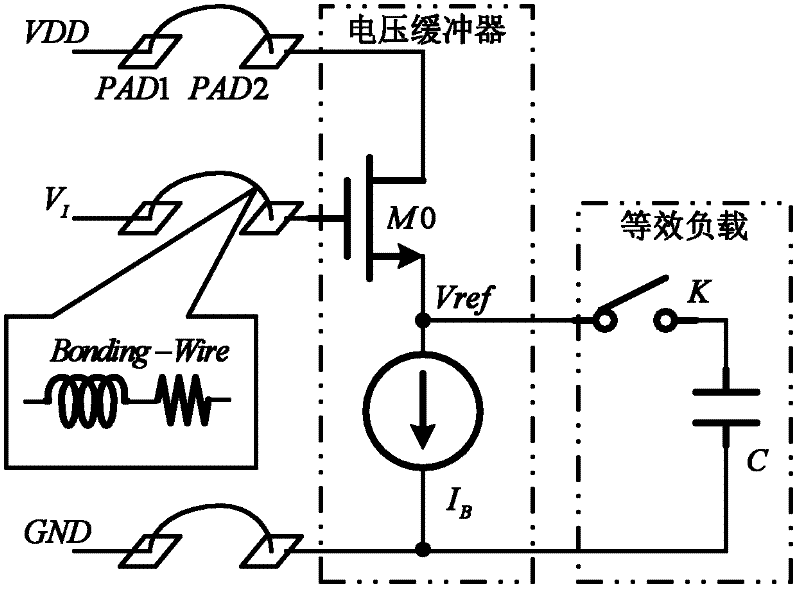

[0017] The voltage buffer suitable for high-speed analog-to-digital converter proposed by the present invention is described in detail as follows in conjunction with the accompanying drawings and embodiments:

[0018] The embodiment of the voltage buffer suitable for high-speed analog-to-digital converter proposed by the present invention is as follows Figure 4 indicated by the dotted box. It includes three PMOS transistors M3, M2 and M4; three NMOS transistors M1, M5 and M6; except for the power supply VDD and ground GND, the positive reference input voltage is V IP , the positive reference output voltage is VRP, and the negative reference input voltage is V IN , the negative reference output voltage is VRN. The positive end load is equivalent to capacitor C1 and switch K1, and the negative end load is equivalent to capacitor C2 and switch K2; in the figure, PAD1 is the substrate solder joint; PAD2 is the chip solder joint; the bonding-wire between PAD1 and PAD2 is Metal ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More