Circuit and method for cancellation of column pattern noise in CMOS imagers

a cmos imager and circuit technology, applied in the field of imaging devices, can solve the problems of ccd image sensors that are not easily integrated with cmos process peripheral circuitry, ccd image sensors also require relatively high power supply voltage, and require relatively high power to operate, so as to correct the non-linearity of isolated data

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031]The present invention will be described in connection with preferred embodiments; however, it will be understood that there is no intent to limit the present invention to the embodiments described herein. On the contrary, the intent is to cover all alternatives, modifications, and equivalents as may be included within the spirit and scope of the present invention as defined by the appended claims.

[0032]For a general understanding of the present invention, reference is made to the drawings. In the drawings, like reference numbering has been used throughout to designate identical or equivalent elements. It is also noted that the various drawings illustrating the present invention are not drawn to scale and that certain regions have been purposely drawn disproportionately so that the features and concepts of the present invention could be properly illustrated.

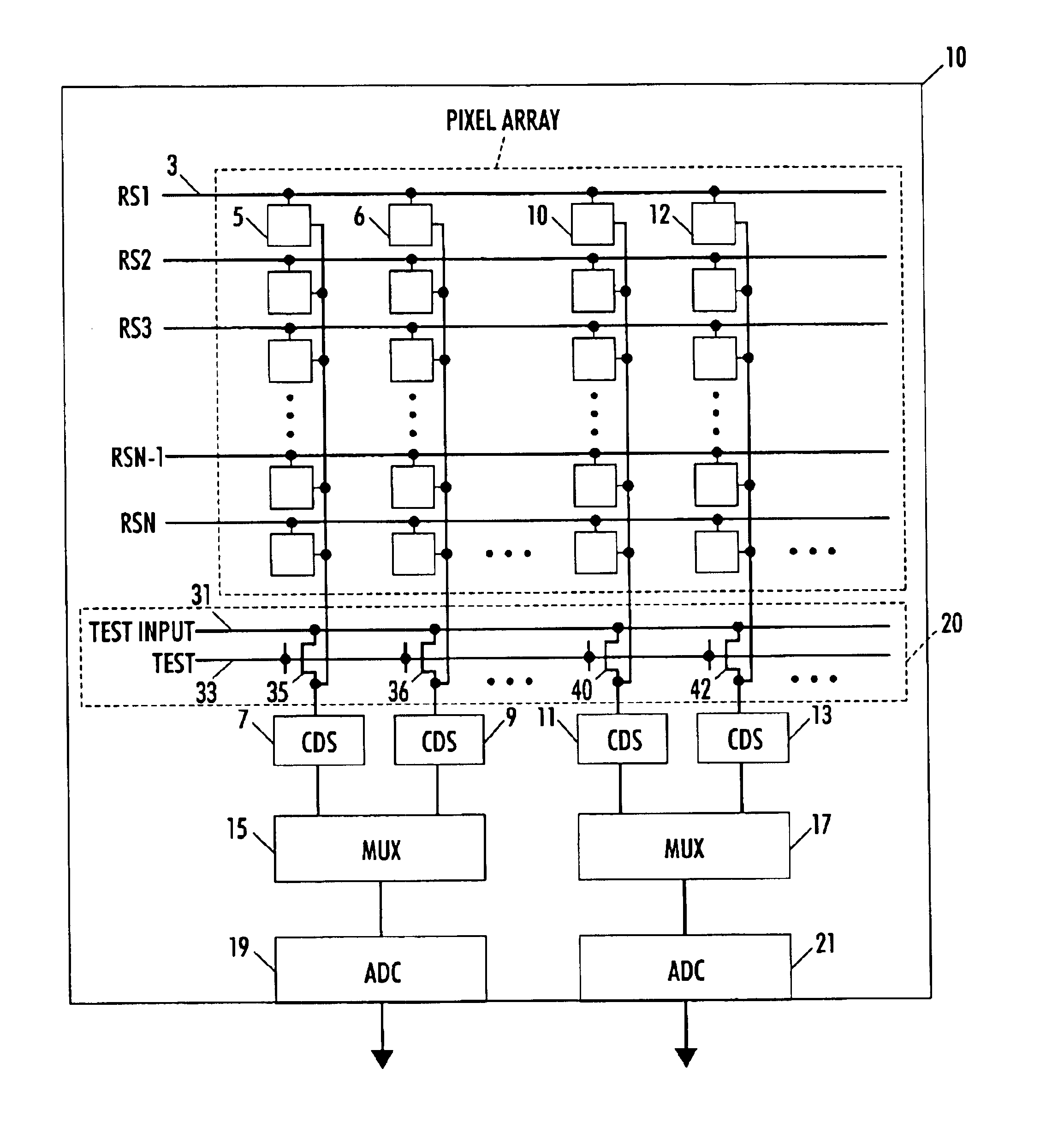

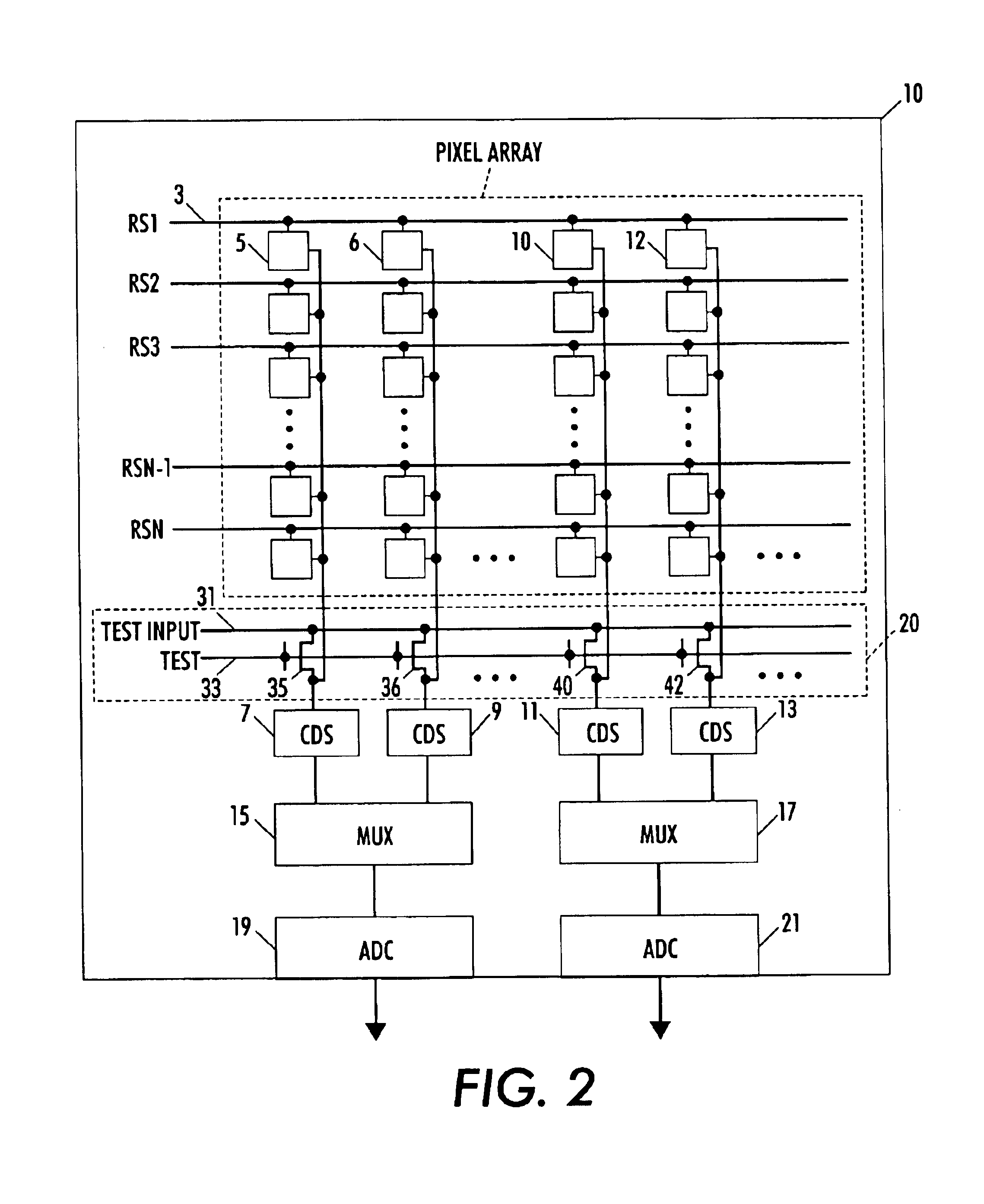

[0033]In accordance with the concepts of the present invention, FIG. 2 schematically illustrates a CMOS imager 10 of the i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More