Patents

Literature

115results about How to "Increase data bandwidth" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

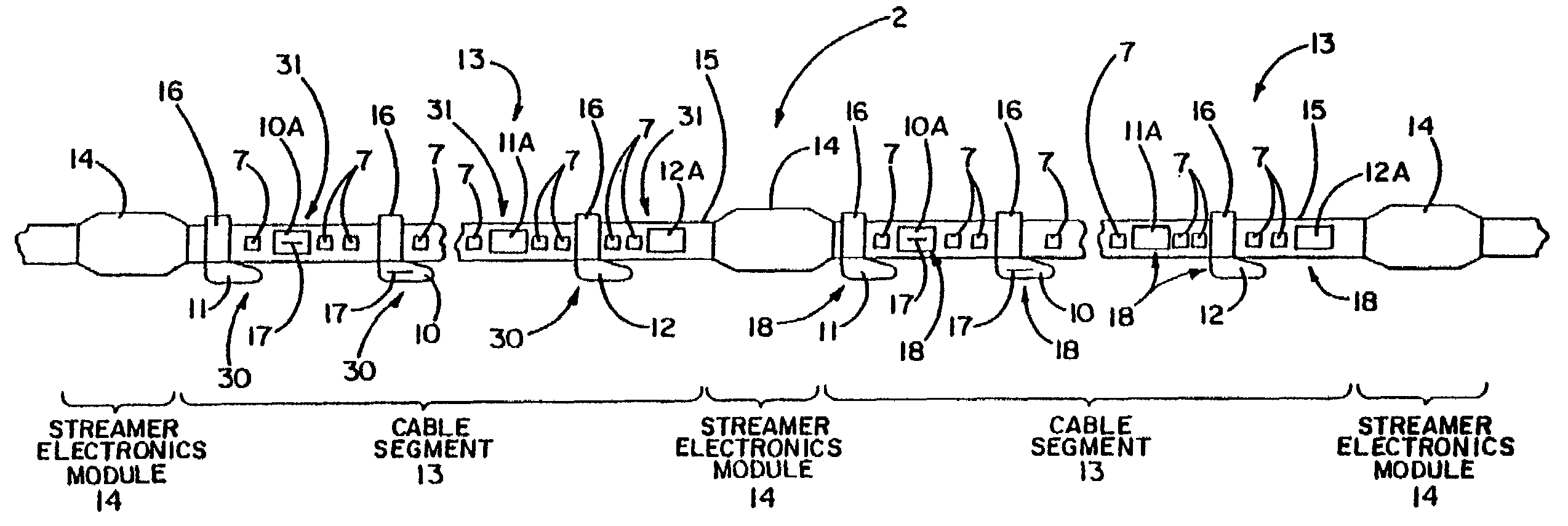

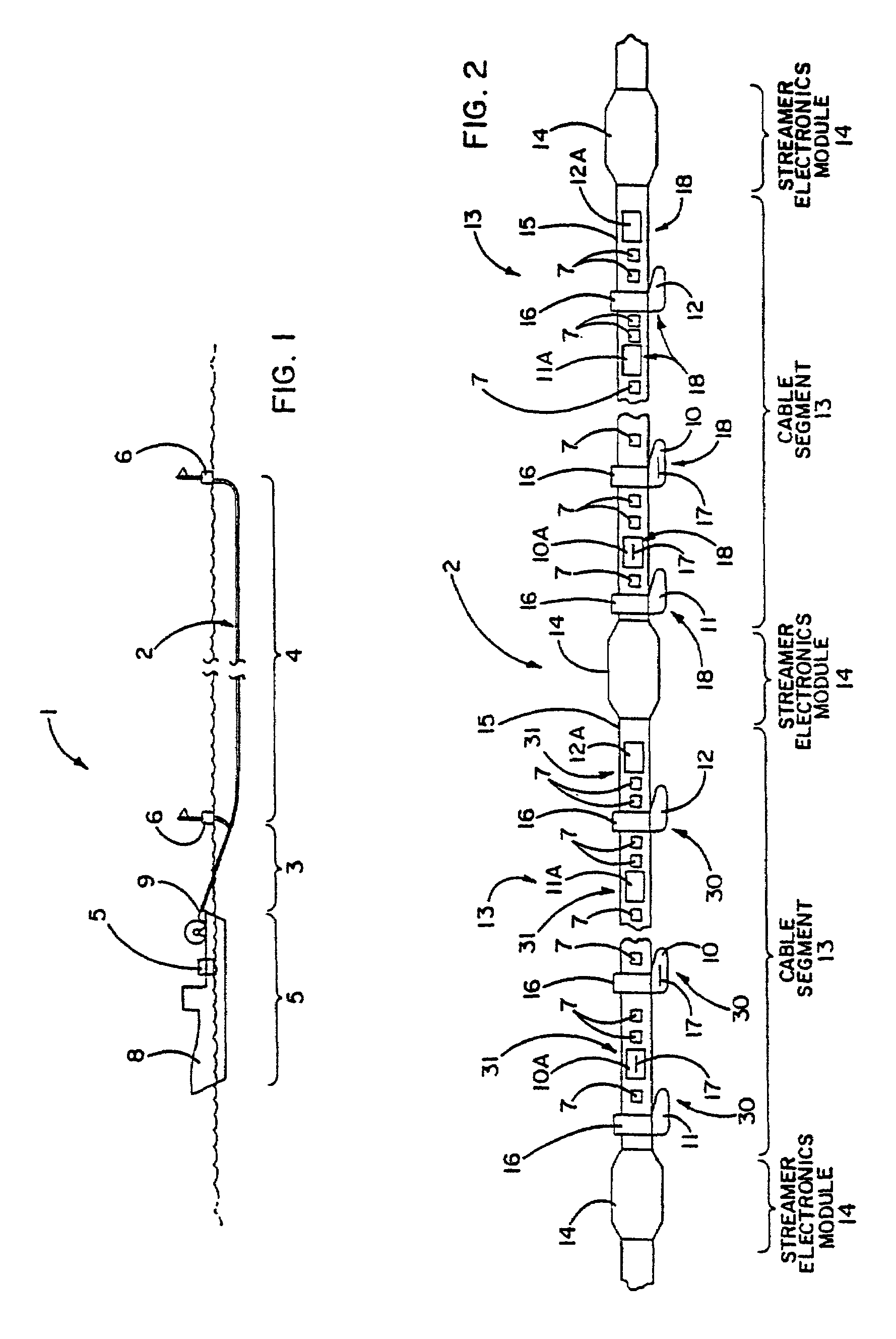

Electrical power distribution and communication system for an underwater cable

ActiveUS7176589B2Improve reliabilityImprove operationBus-bar/wiring layoutsInsulated cablesCommunications systemElectrical devices

An underwater cable arrangement includes systems and method for distributing and / or transferring power and / or data to internal devices and external devices disposed along an underwater cable. Under water coupling systems and underwater electrical devices may be used in the distribution and / or transfer of the power and / or data.

Owner:INPUT OUTPUT INC

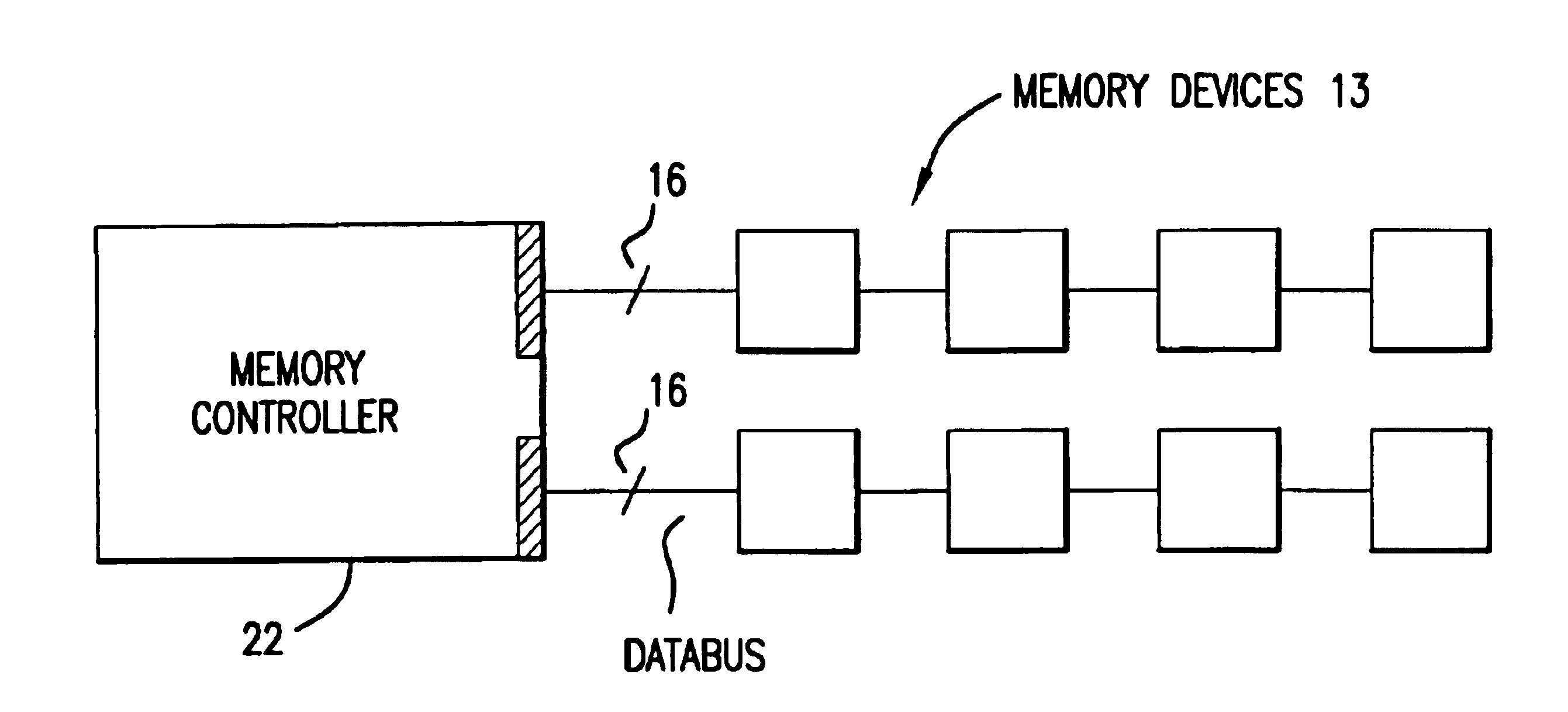

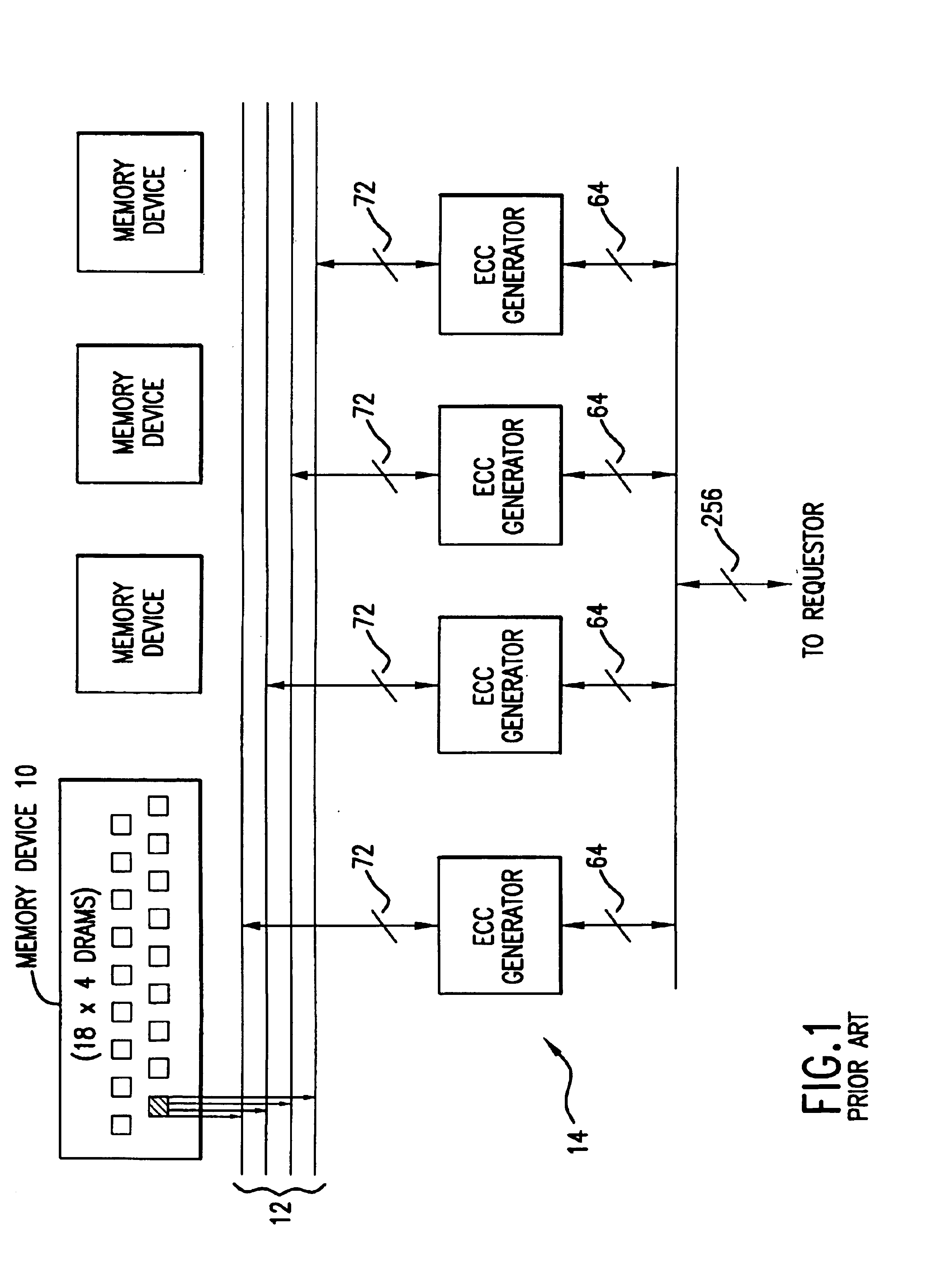

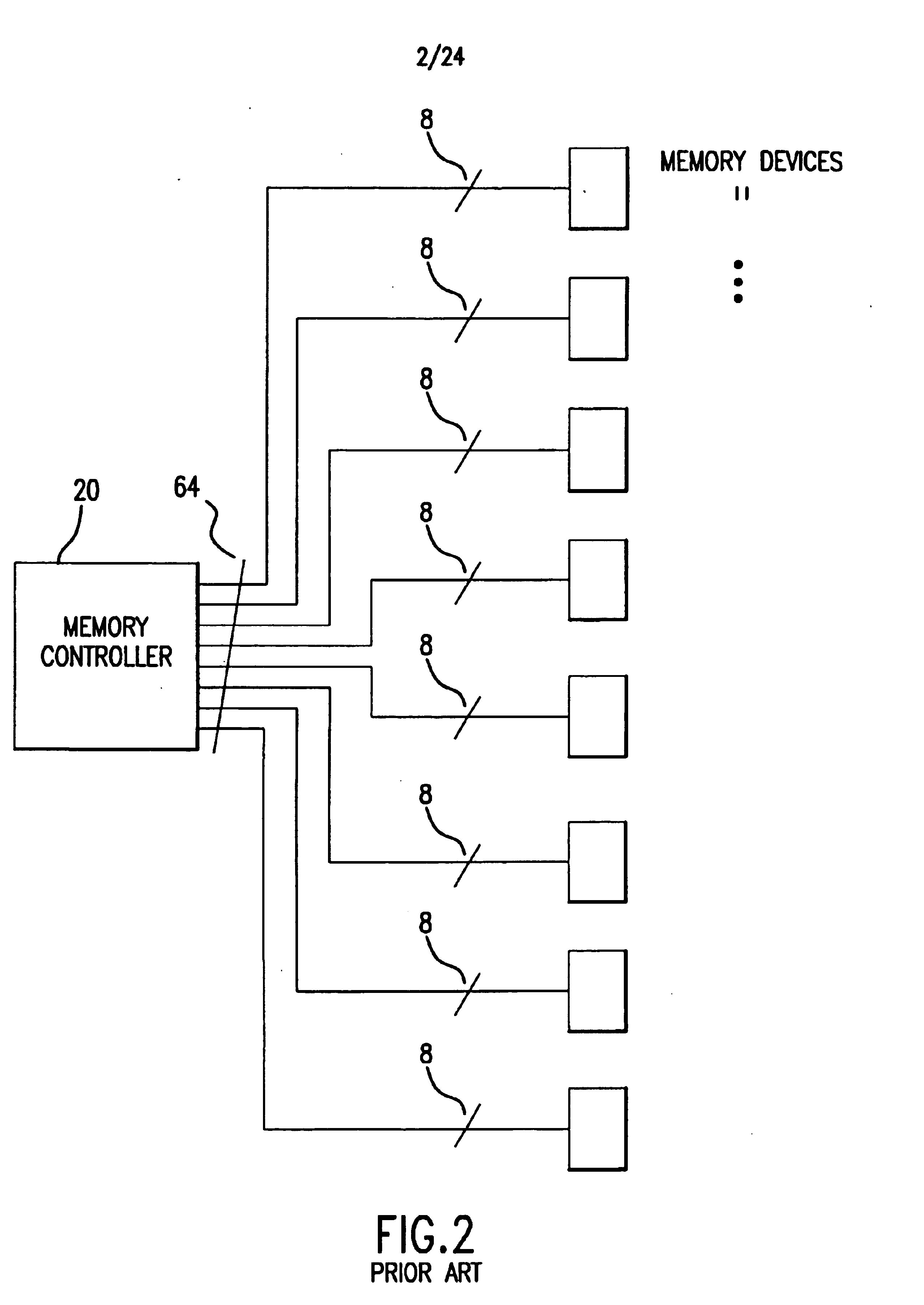

Memory module with offset data lines and bit line swizzle configuration

InactiveUS6839266B1Simplified bus architectureIncrease data bandwidthMemory adressing/allocation/relocationRead-only memoriesBit lineComputer science

A memory module includes an array of N memory devices, each memory device having M data pins, where N is greater than M, and M and N are positive integers; and N bit lines traversing the array of N memory devices, such that each one of the N bit lines is connected to M of the N memory devices.

Owner:RAMBUS INC

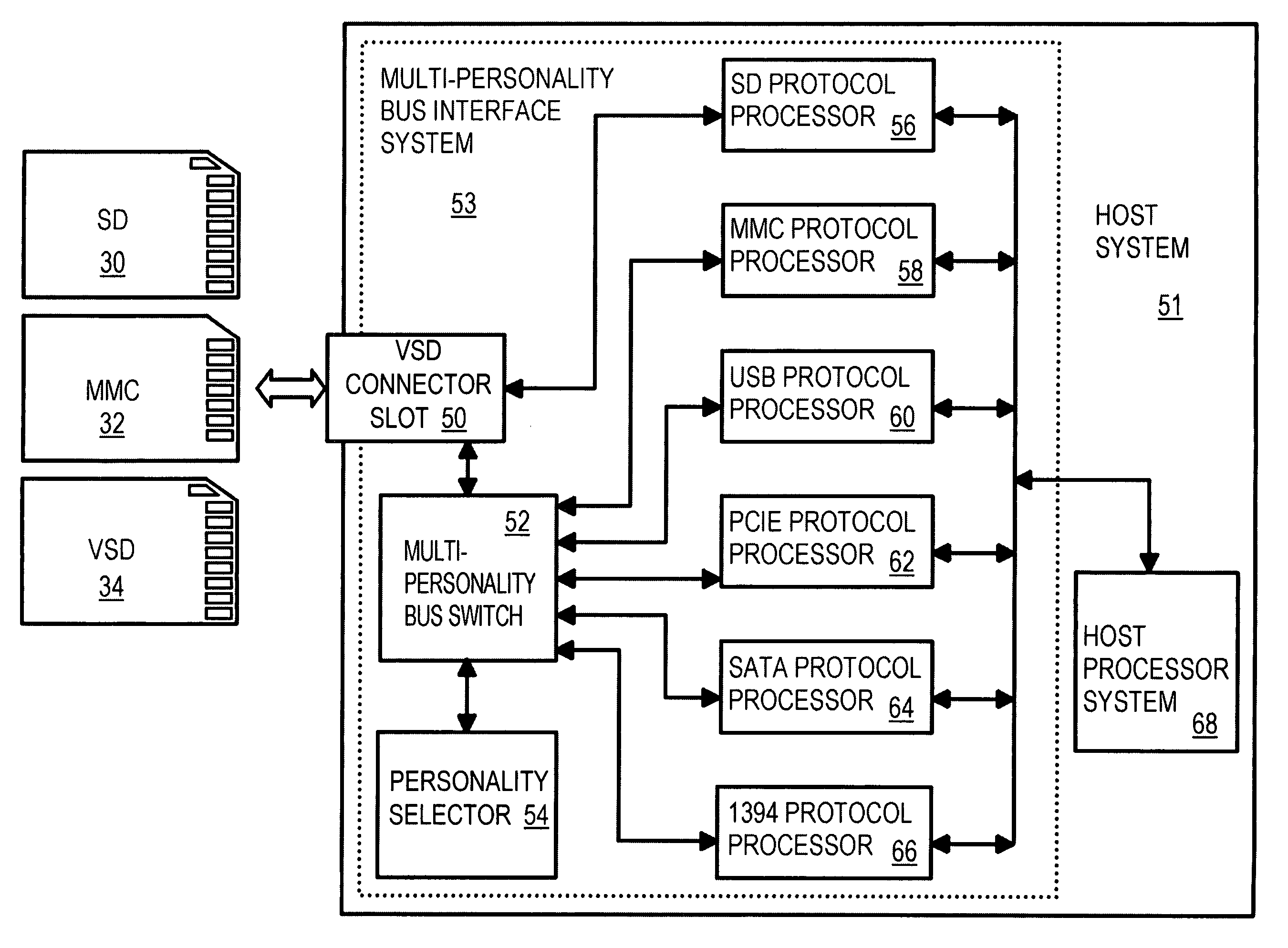

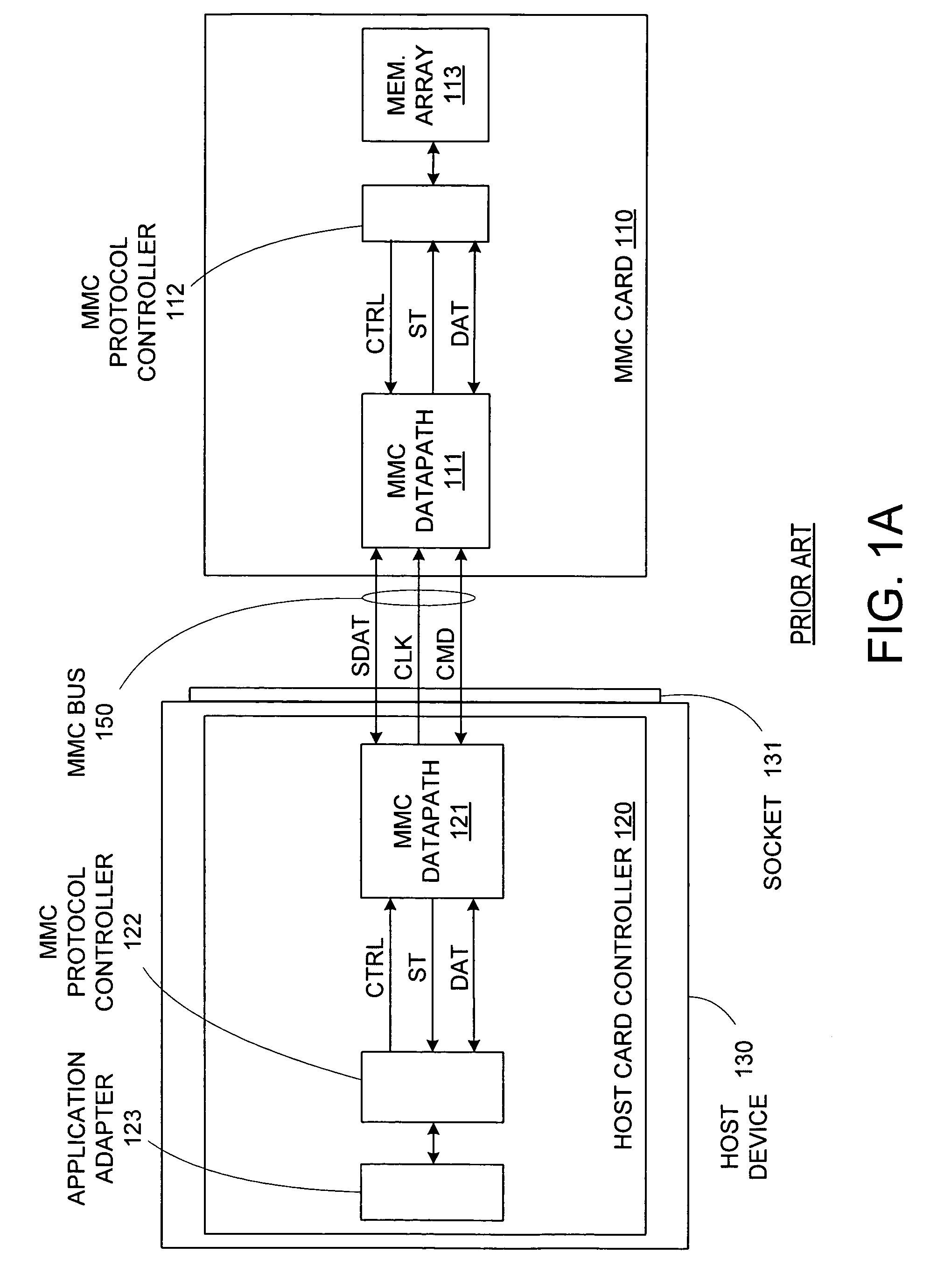

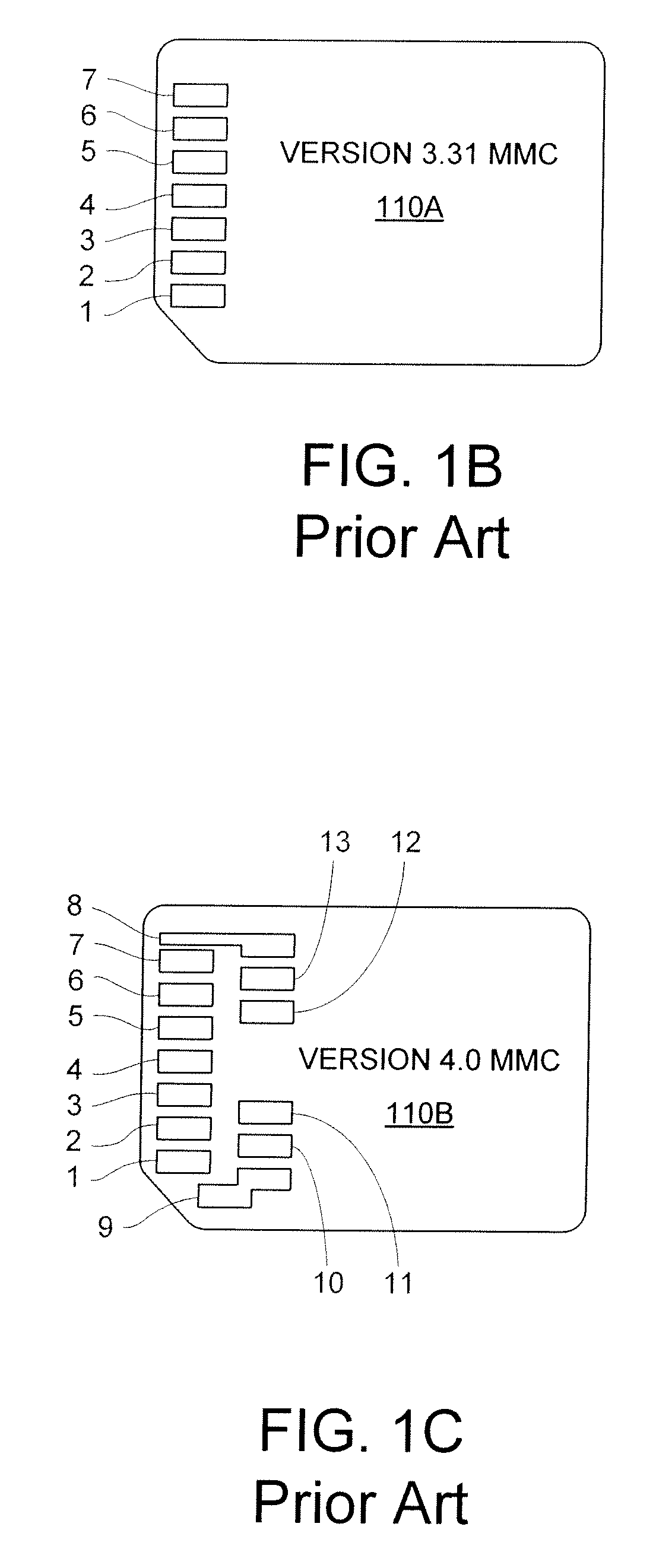

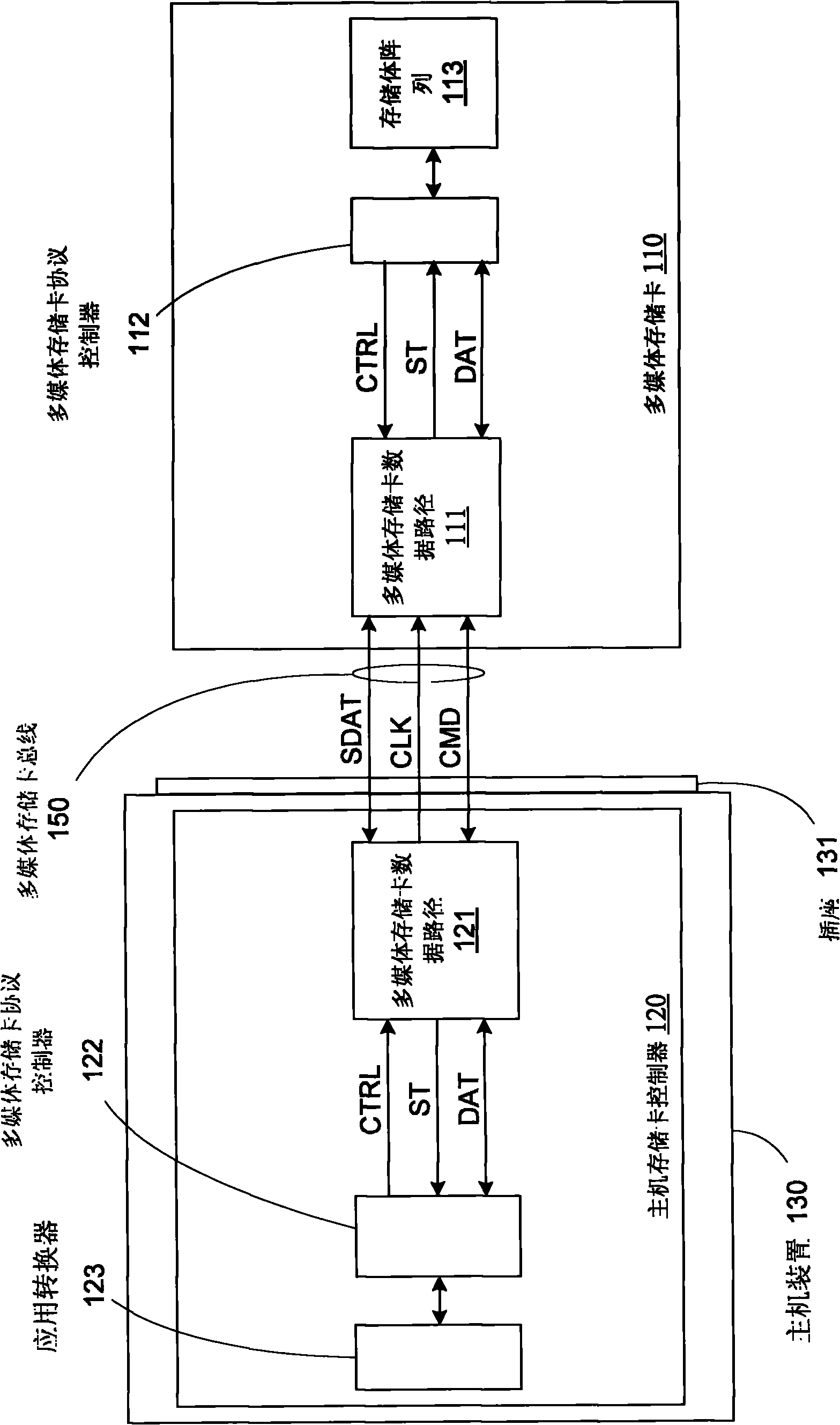

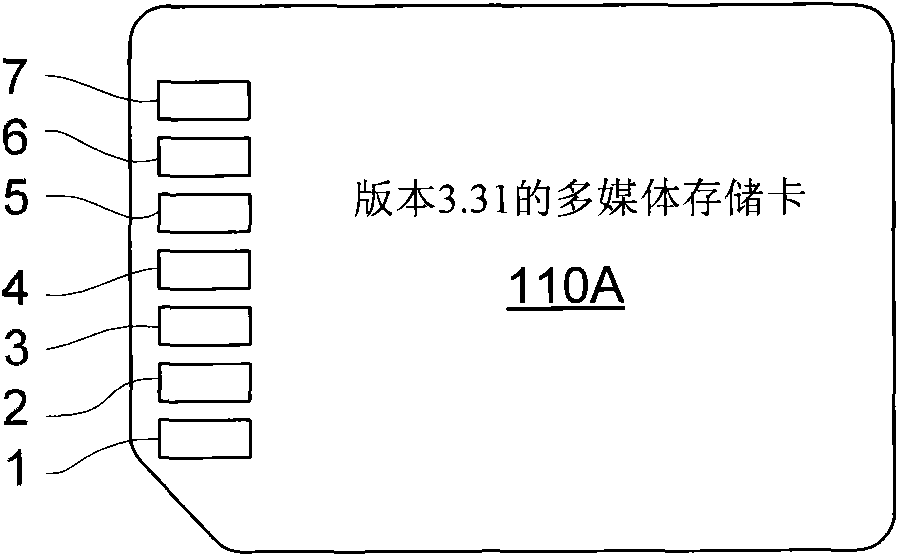

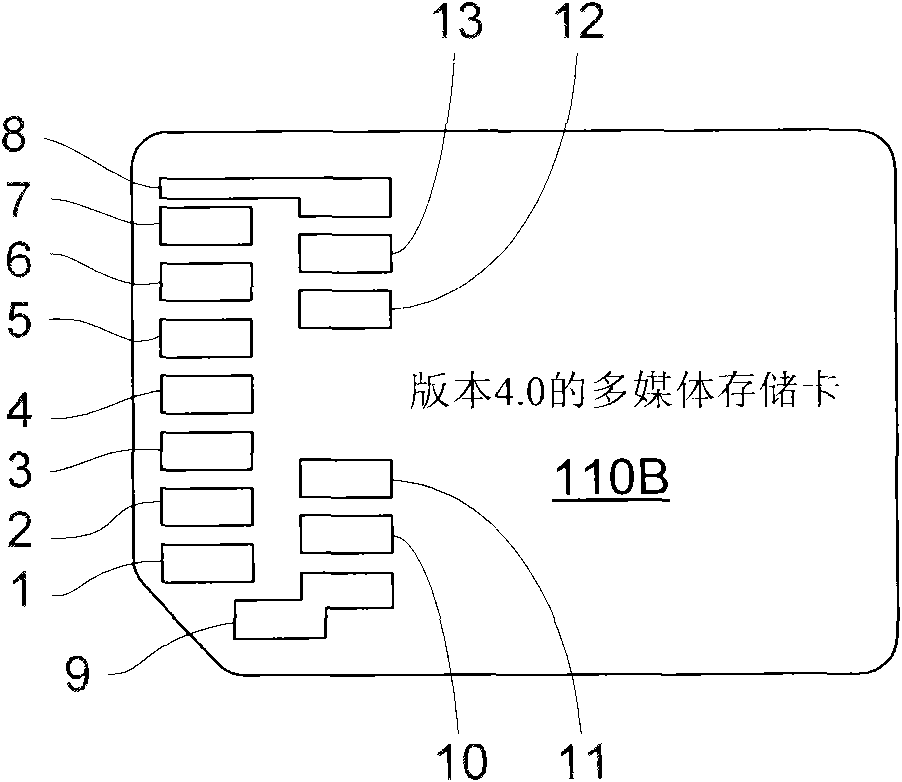

Differential data transfer for flash memory card

InactiveUS7673080B1Increase data bandwidthReduce power consumptionEnergy efficient ICTCoupling device connectionsDifferential signalingDatapath

A flash memory card includes a differential datapath that enables communications between the flash memory card and a host device to be performed using differential signals. The differential datapath can translate between the differential signals and card-specific signals that control read / write operations to the memory array of the flash memory card. The card-specific signals can be standard MultiMediaCard, Secure-Digital card, Memory Stick, or CompactFlash card signals, among others. A host device that provides differential data transfer capability can include a similar differential datapath. By using differential data transfer rather than conventional clocked data transfer, overall data bandwidth between a flash memory card and a host device can be significantly increased, while simultaneously decreasing power consumption and pin requirements.

Owner:SUPER TALENT TECH CORP

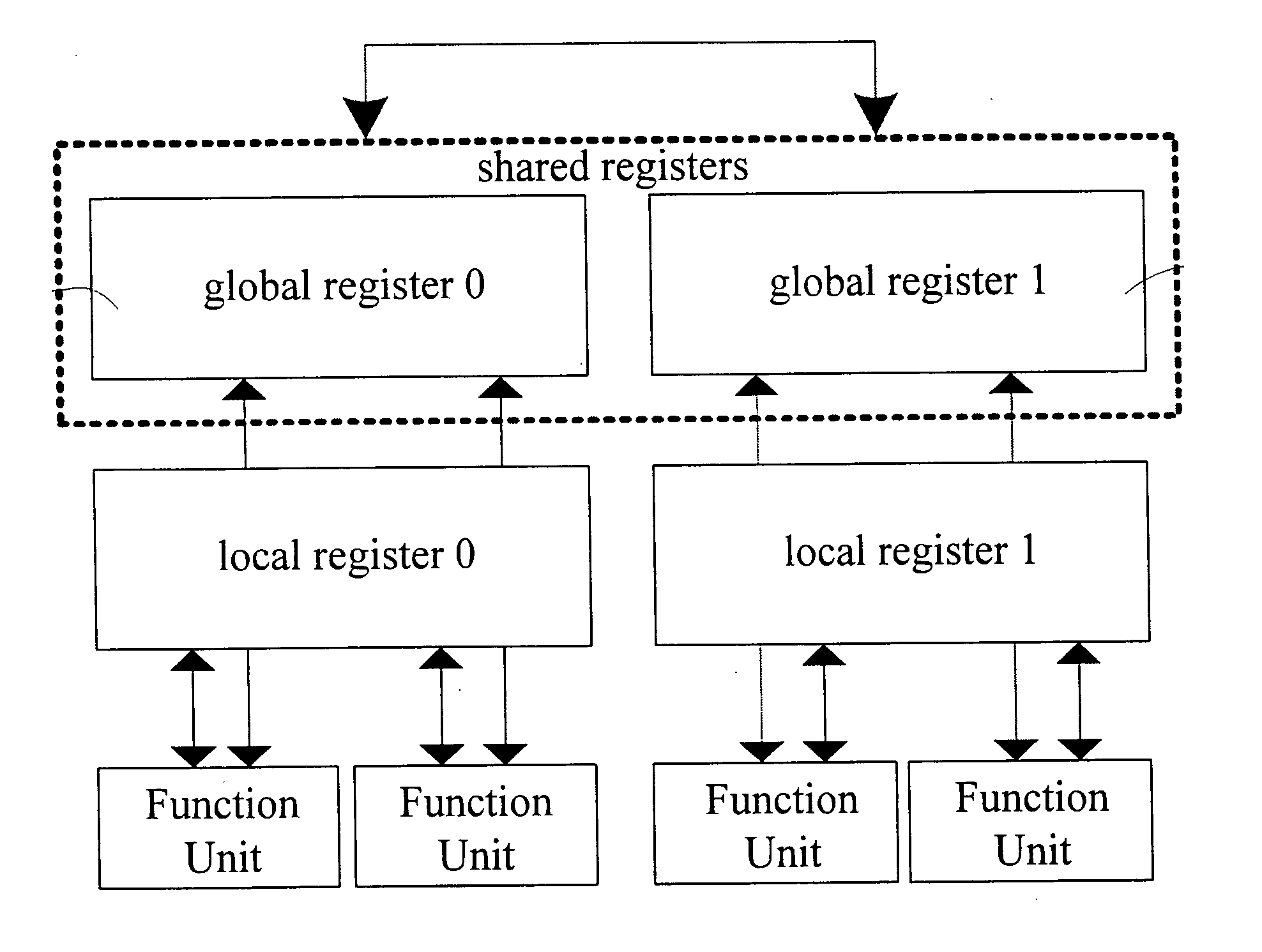

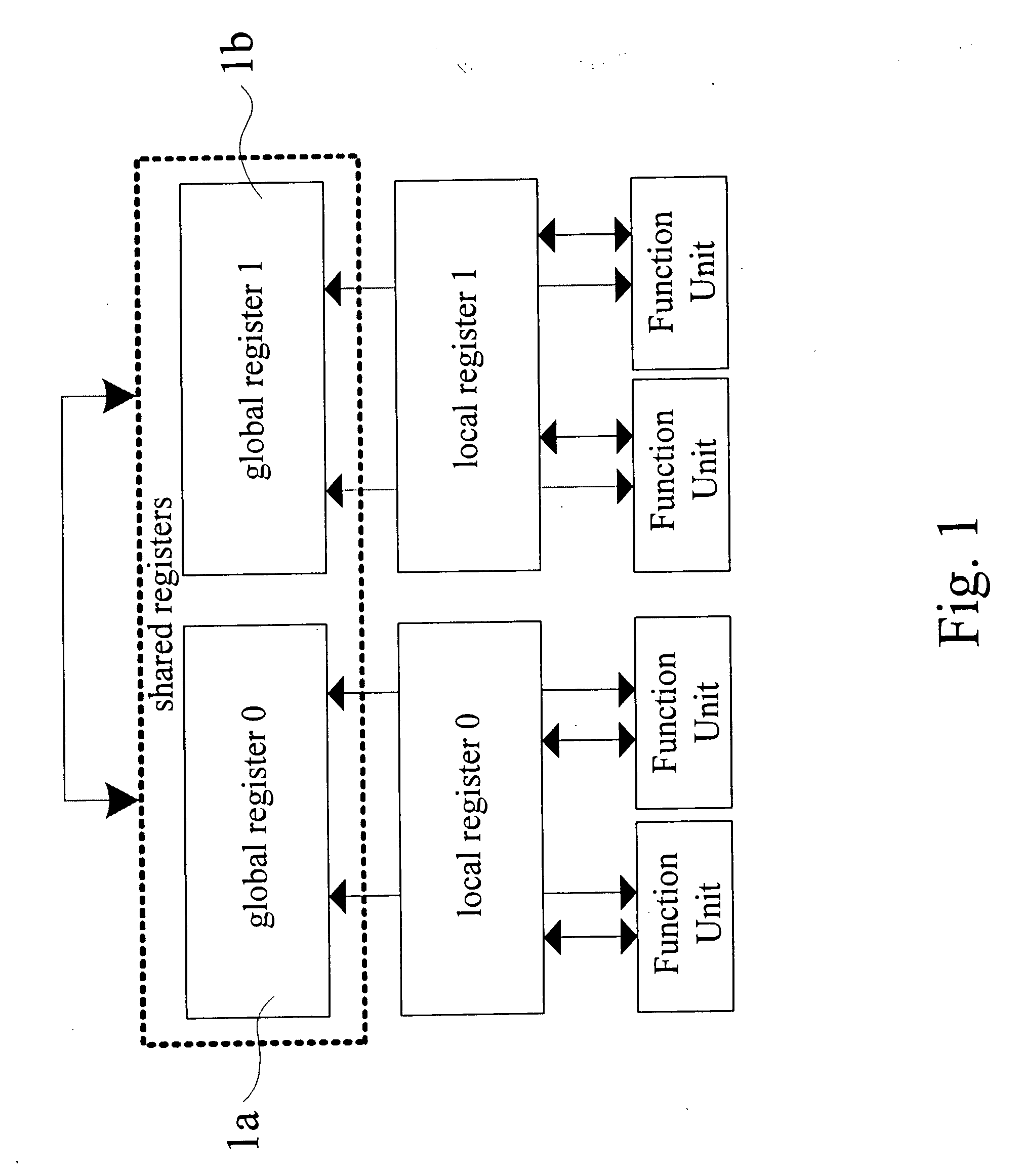

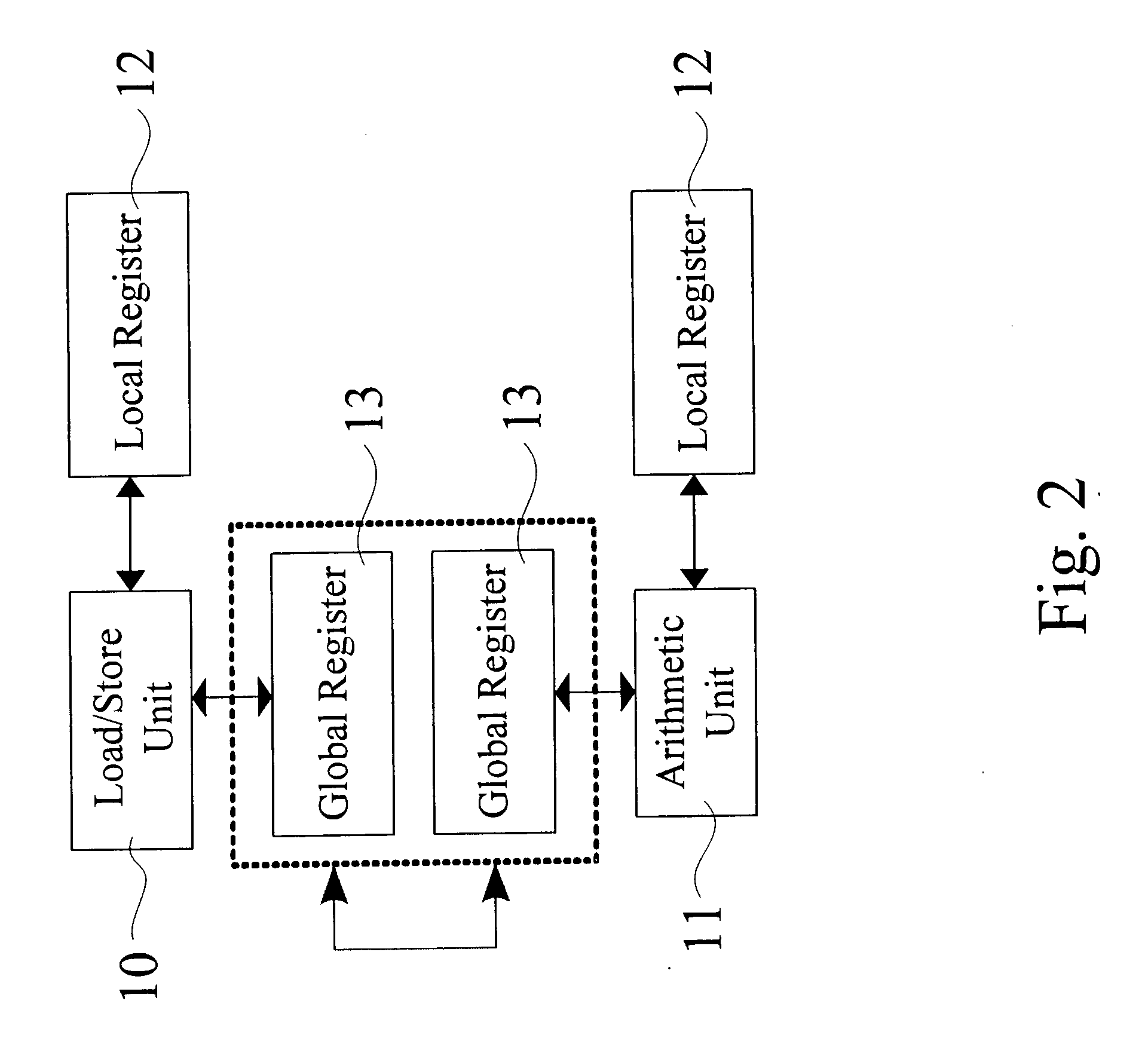

Method for inter-cluster communication that employs register permutation

InactiveUS20050204118A1Increase data bandwidthReduce power consumptionRegister arrangementsDigital computer detailsAccess timeComputer science

The present invention is a method for inter-cluster communication that employs register permutation by dynamically mapping the registers to the functional units. Because only the mapping between registers and functional units is changed and no actual data movement occurs, the present invention greatly diminishes the power consumption. Owing to the inter-cluster communication mechanism, a centralized register file can be replaced with small register sub-blocks, where the silicon area is greatly reduced, and the access time and the power consumption are also diminished.

Owner:NAT CHIAO TUNG UNIV

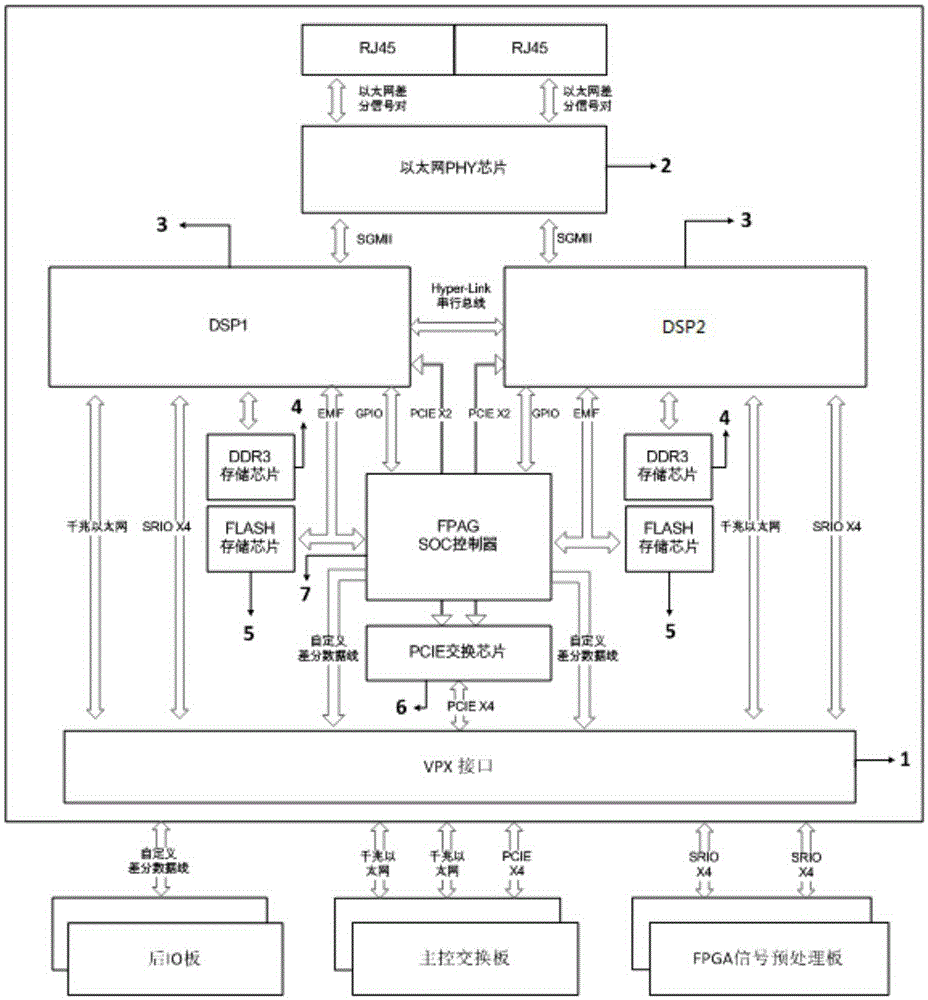

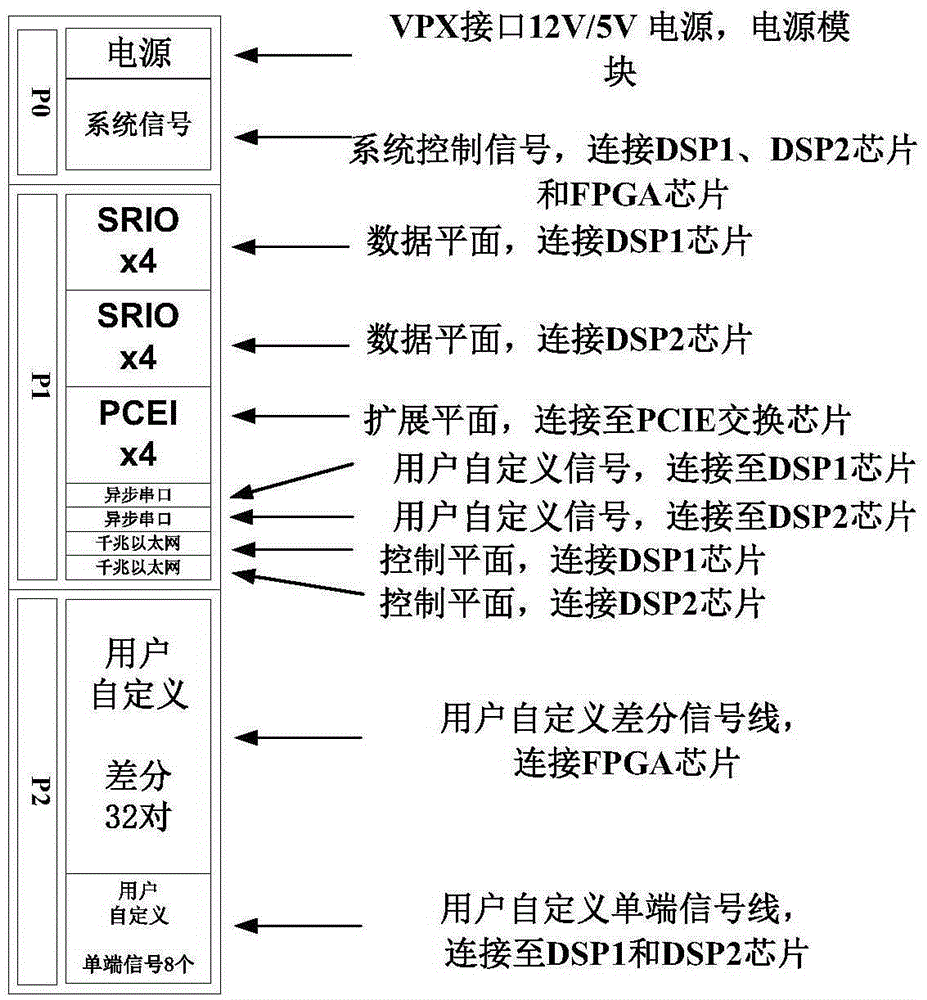

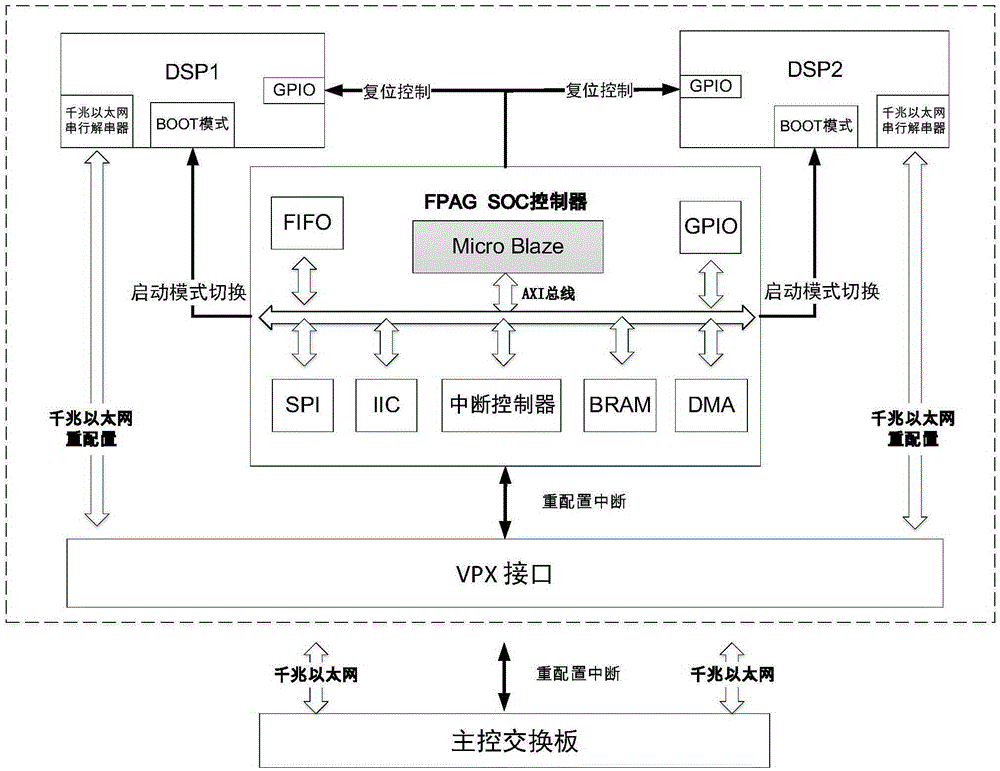

VPX parallel DSP signal processing board card based on SoC online reconstruction

InactiveCN105279133AIncrease flexibilityImprove real-time performanceDigital computer detailsElectric digital data processingDigital signal processingData signal

The invention discloses a VPX parallel DSP (Digital Signal Processing) board card based on SoC (System on a Chip) online reconstruction. An FPGA (Field Programmable Gate Array) chip is used as a board stage SoC controller; and two DSP chips are used as core operation chips of a DSP board card. During the practical configuration of the DSP chips, the FPGA chip used as the SoC controller can complete the dynamic re-configuration of work code by GE (Gigabit Ethernet) through the hardware resetting on the DSP and the switching on the starting mode; and the flexibility and the real-time performance during the DSP are greatly improved. The DSP chips receive two kinds of high-speed serial bus signals of SRIO (Serial Rapid Input Output) X4 and the GE transmitted through a VPX interface, repacking the transferred PCIE (Peripheral Component Interface Express) X2 high-speed serial bus signal through a PCIE exchange chip, and receives a data signal to be processed and a control instruction; or the DSP chips receive the GE protocol signal of a peripheral component through an RJ45 net port.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

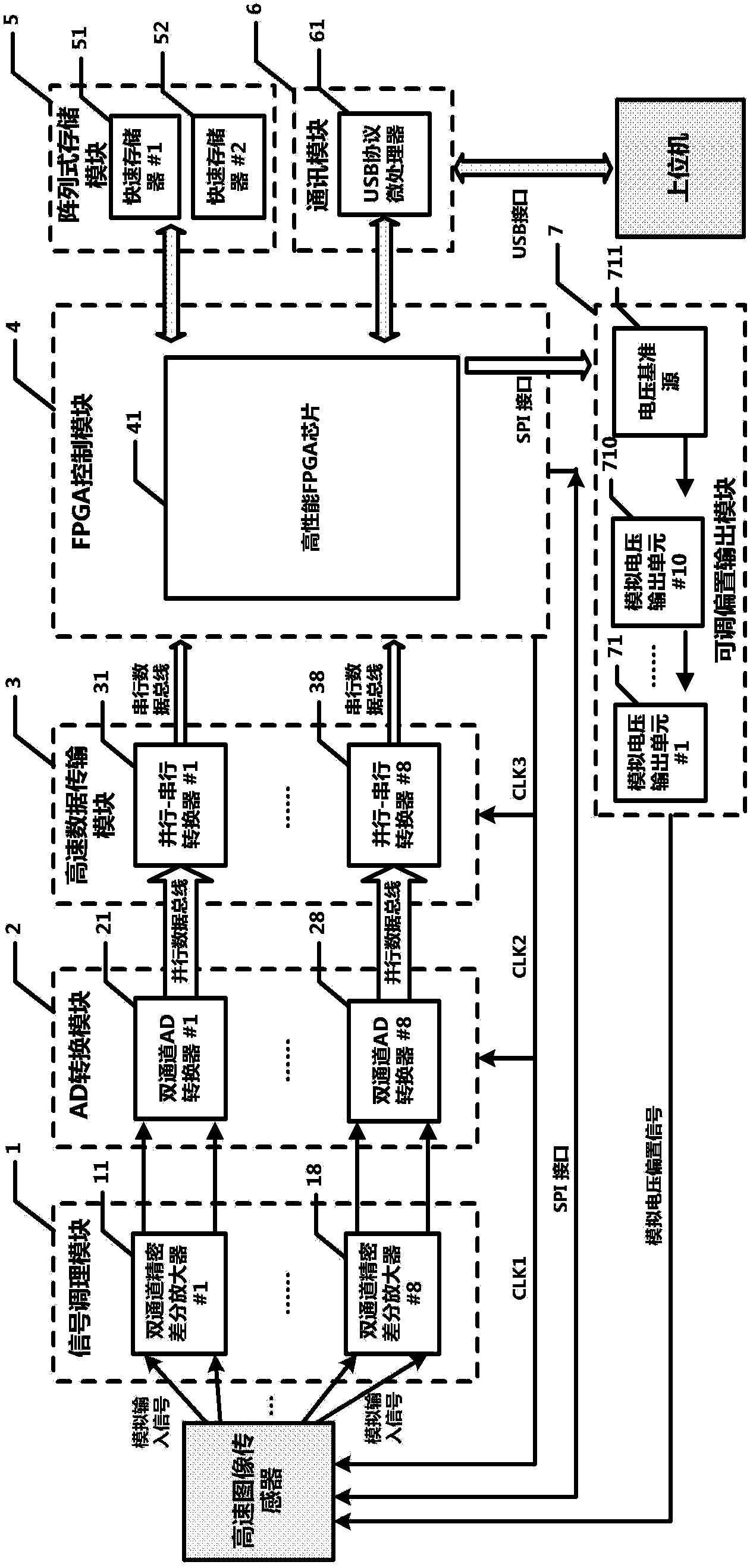

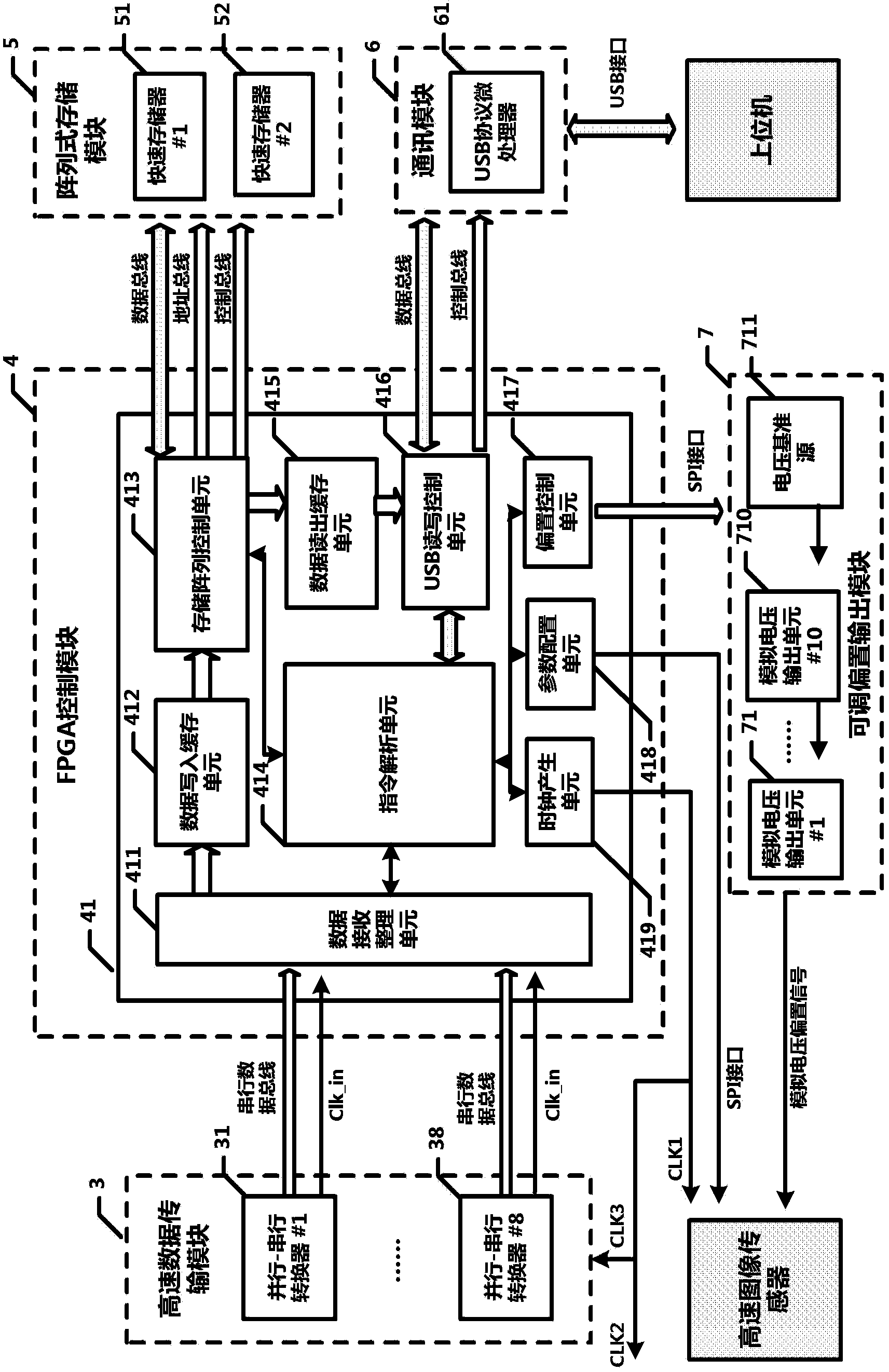

Field programmable gate array (FPGA) based multichannel high-speed image data acquisition and storage system

InactiveCN103647913AHigh speed storageReduce the numberTelevision system detailsColor television detailsSignal conditioningData acquisition

The invention discloses an FPGA based multichannel high-speed image data acquisition and storage system. The system is characterized by comprising a signal conditioning module, an analog / digital (A / D) conversion module, a high-speed data transmission module, an FPGA control module, an array type storage module, a communication module and an adjustable configuration module. The signal conditioning module, the A / D conversion module, the high-speed data transmission module and the FPGA control module are connected successively. The FPGA control module is connected with the array type storage module, the communication module and the adjustable configuration module simultaneously and performs data interaction with an upper computer. The system is capable of achieving data capturing and rapid storage of high-speed image sensors and can be widely applied in data acquisition and storage with similar requirements of high speed, high accuracy, high data rate and multiple channels.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Secure quantum key distribution using entangled photons

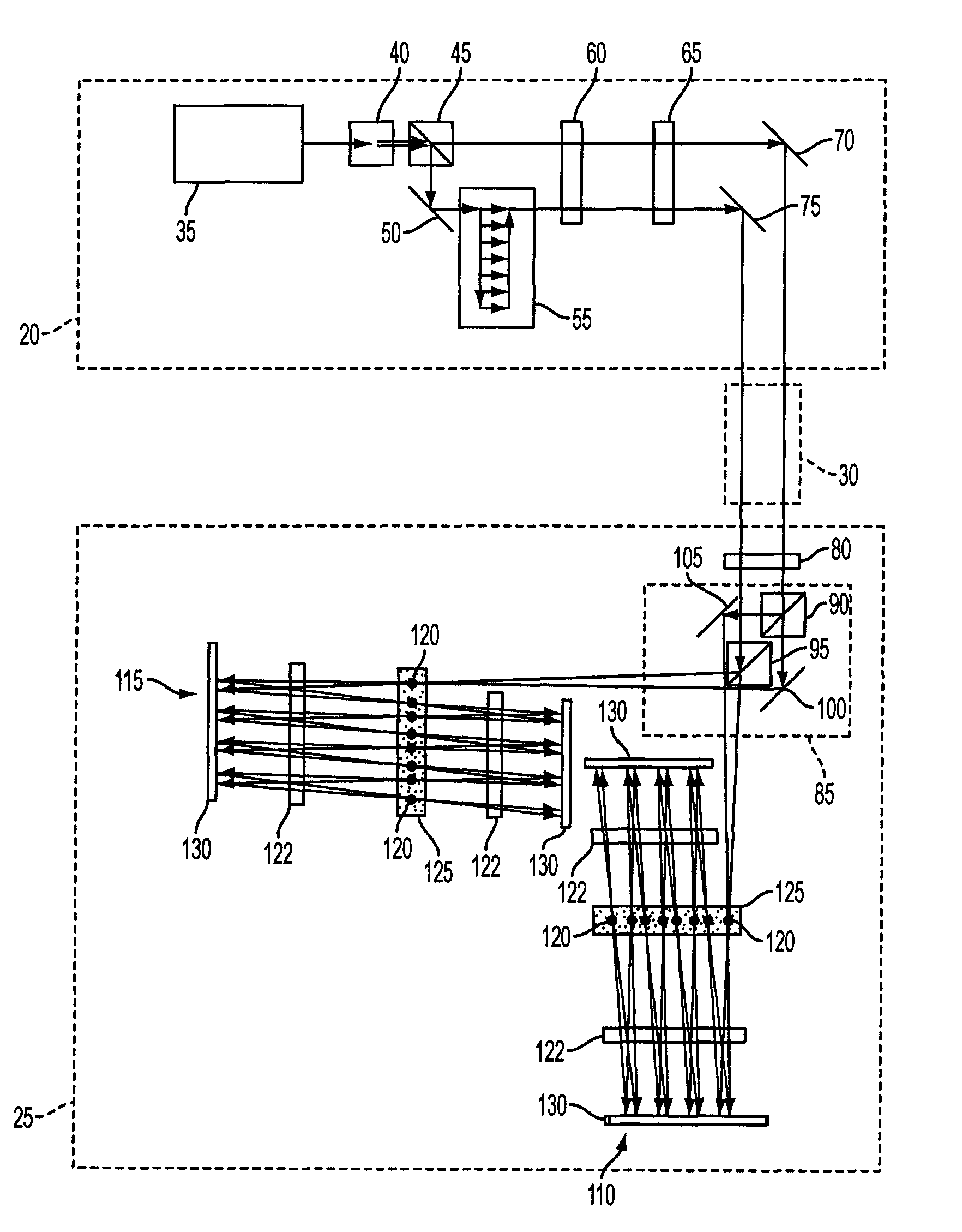

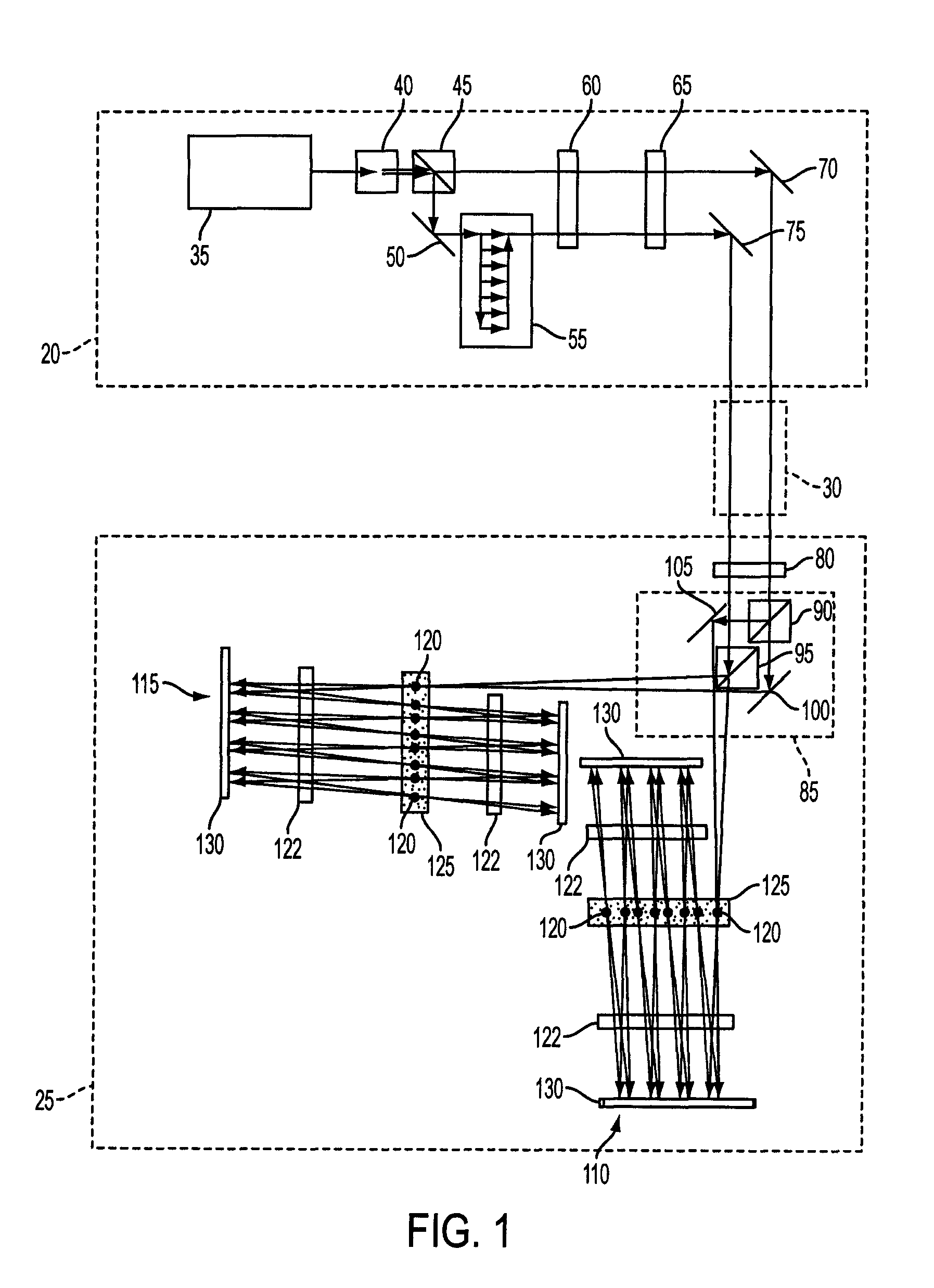

InactiveUS7831048B2Increase data bandwidthHigh data rateKey distribution for secure communicationSynchronising transmission/receiving encryption devicesComputer hardwareData rate

A system and method of implementing quantum key distribution are provided that possess increased data rates and enhanced security. These increased data rates are provided through the use of biphotons. Through encoding bits of information on the intra-biphoton delay time and enabling separate polarization bases for each of the photons comprising each biphoton, the system and method increase data bandwidth available for quantum key distribution.

Owner:GENERAL DYNAMICS ADVANCED INFORMATION SYST INC

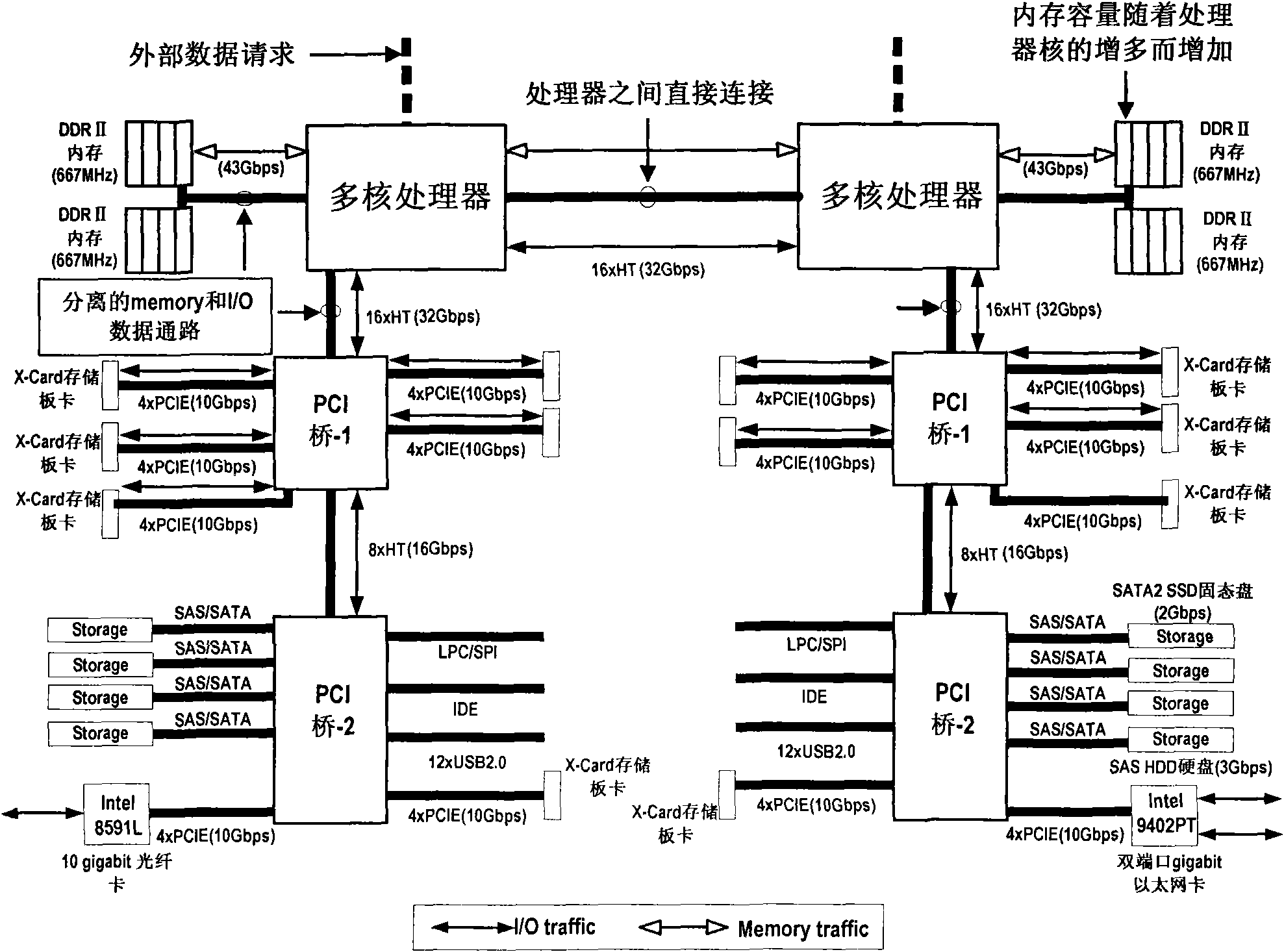

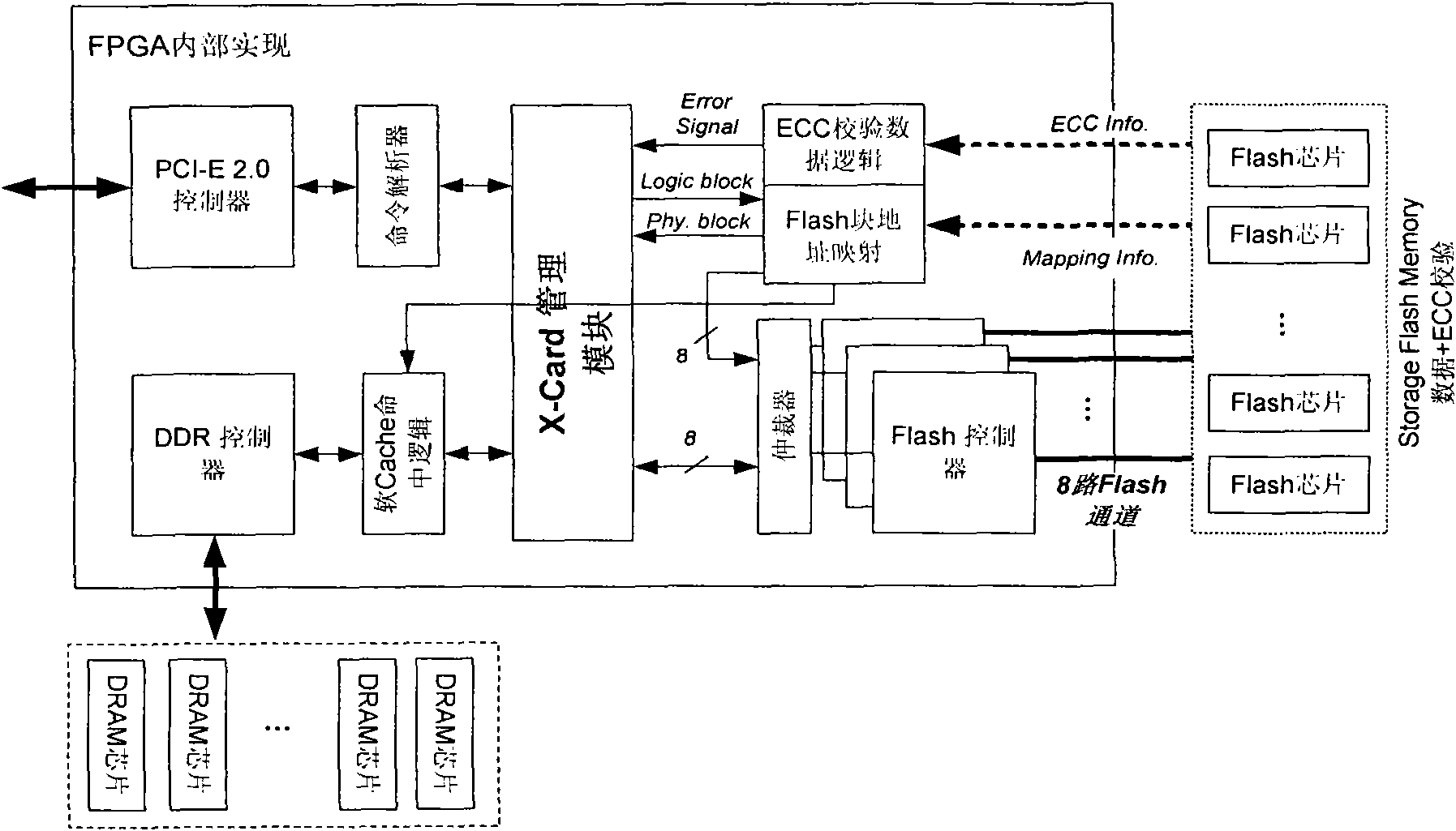

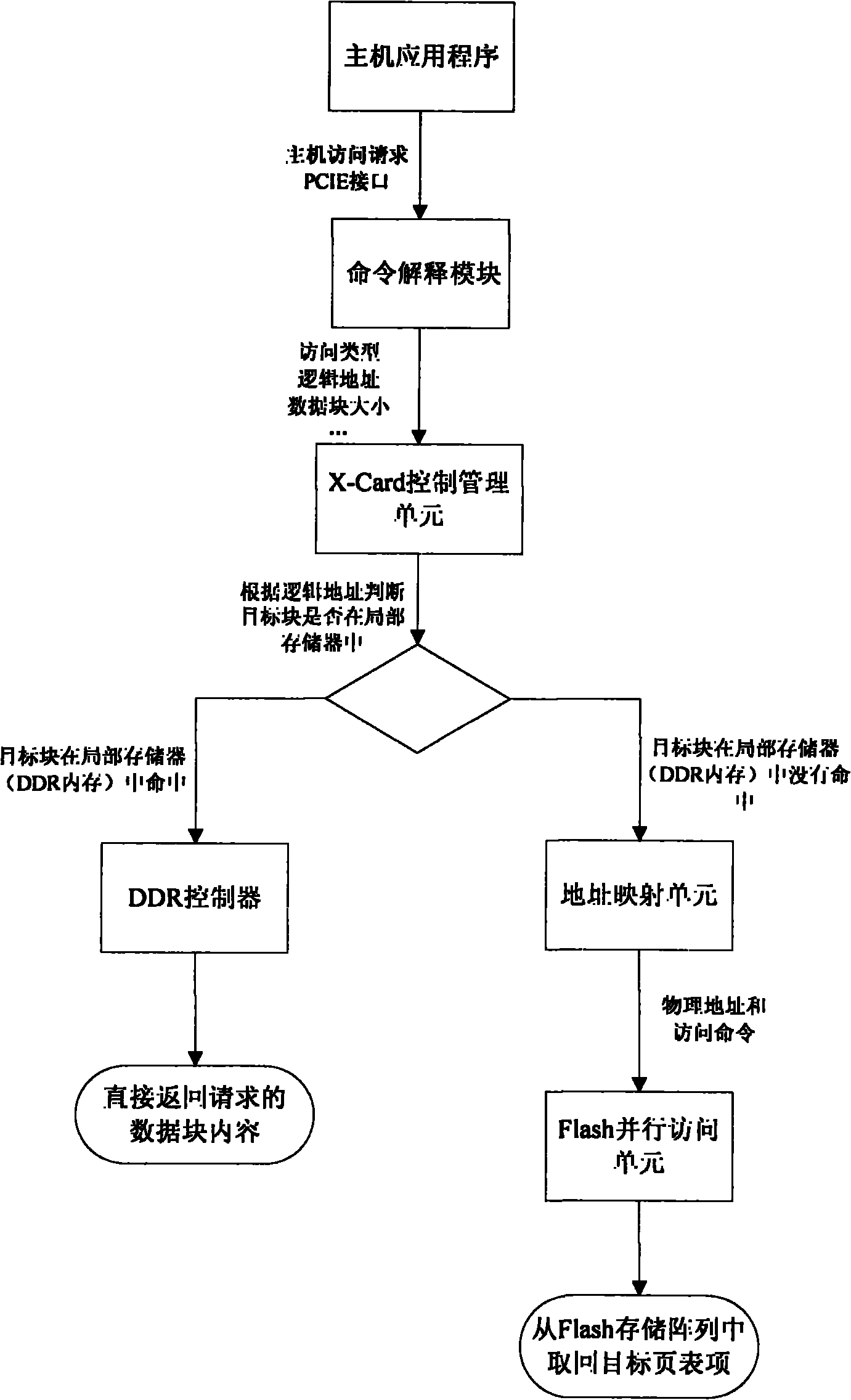

Flash based PCIE (peripheral component interface express) board for data storage

InactiveCN102012791AGuaranteed continuous correctnessAchieve service life consistencyInput/output to record carriersCommunication interfaceData synchronization

The invention discloses a Flash based PCIE (peripheral component interface express) board for data storage. The board is characterized in that an FPGA chip is used as the master control module, DDR memories are connected to serve as buffer modules and Flash chips are simultaneously connected to serve as storage modules; a PCIE controller, a DDR controller, a command parser, soft Cache hit logics,an X-Card management module, ECC check data logics, Flash block address mapping, an arbiter and a Flash controller are implemented inside FPGA and complete respective functions by downloading the programs to the FPGA. The communication interface adopts the PCIE interface which has high data transmission rate. PCI-E also supports advanced power management, hot plug and synchronous data transmission and optimizes the bandwidth for the preferentially transmitted data.

Owner:NAT UNIV OF DEFENSE TECH

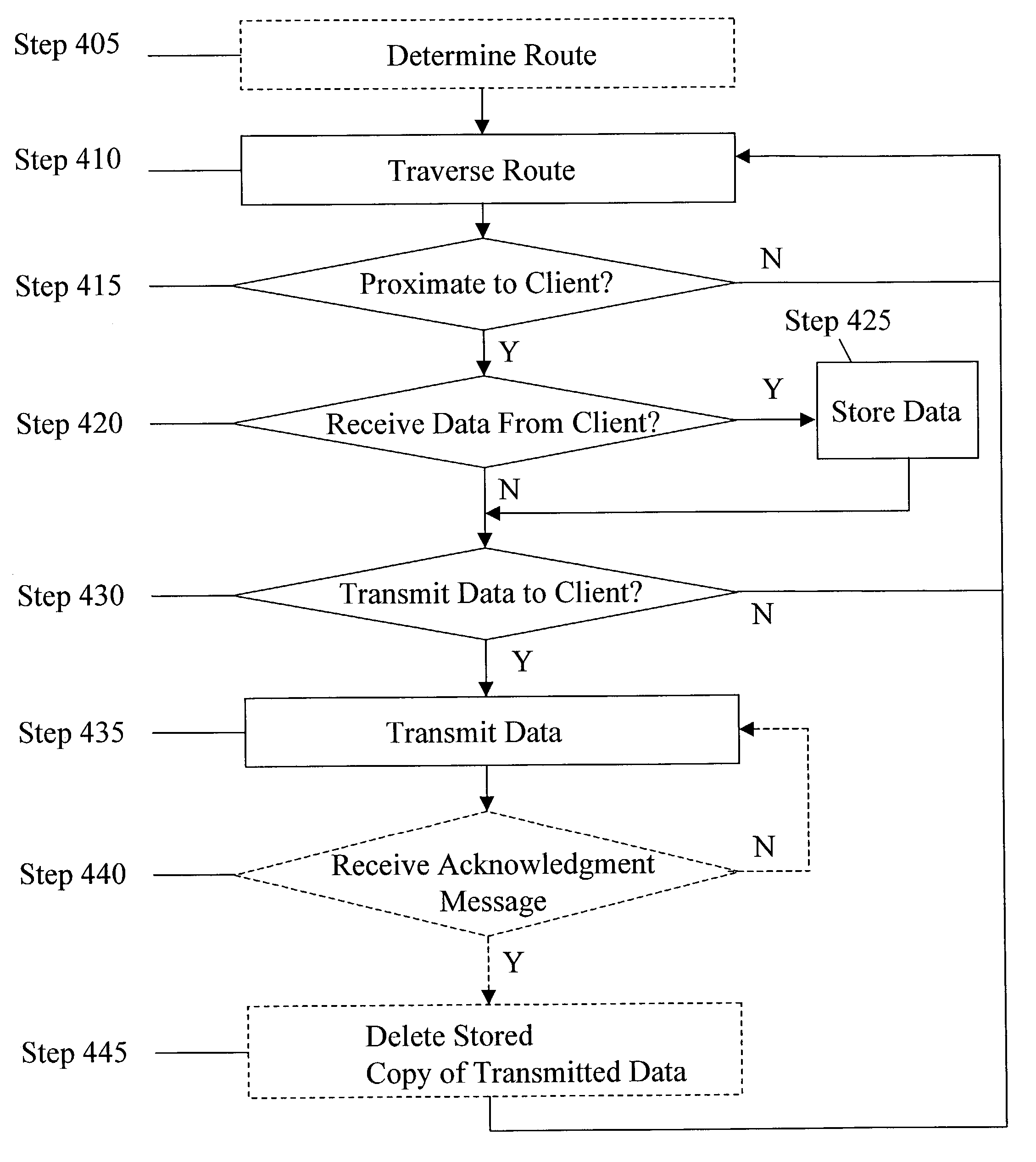

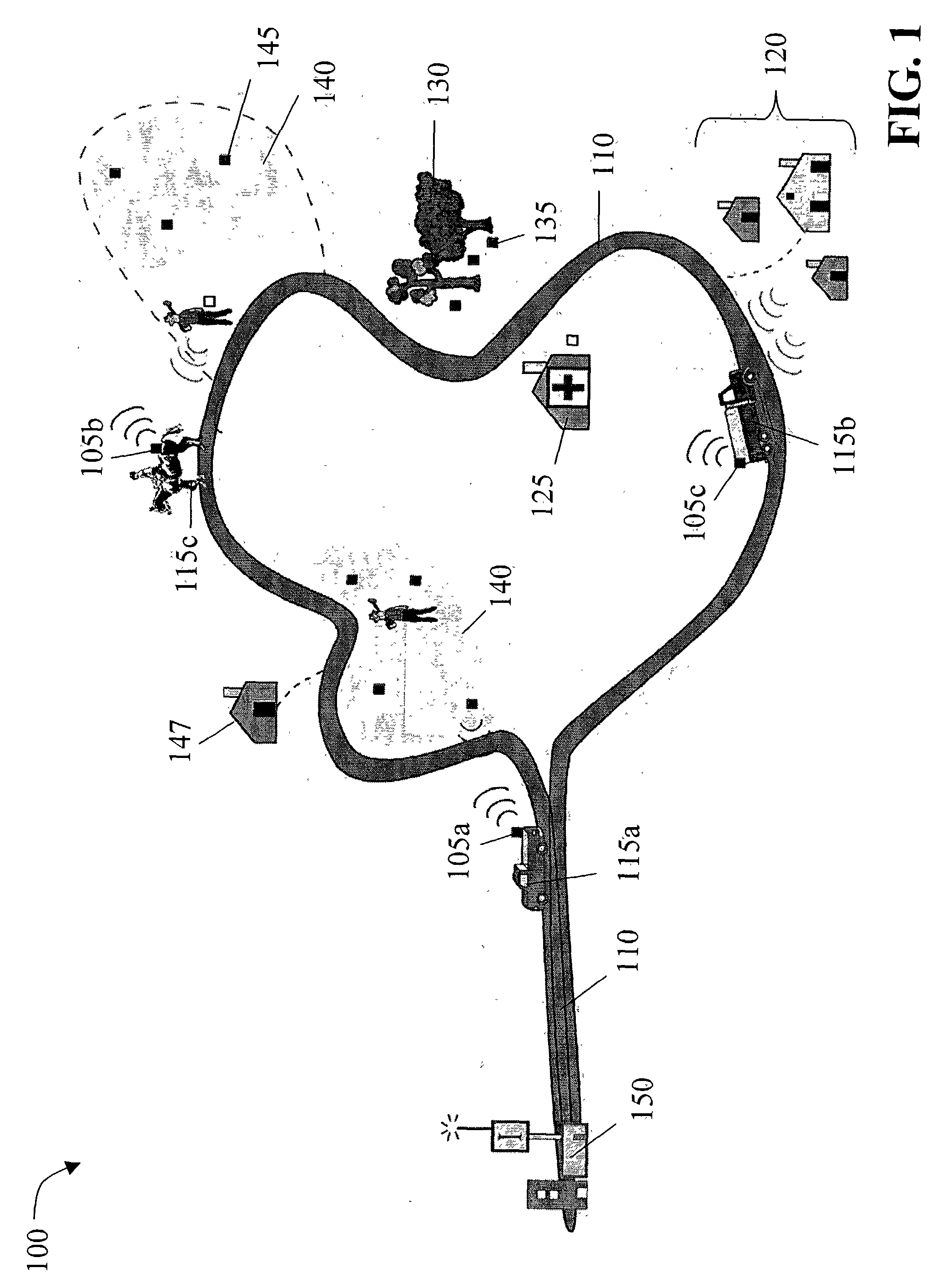

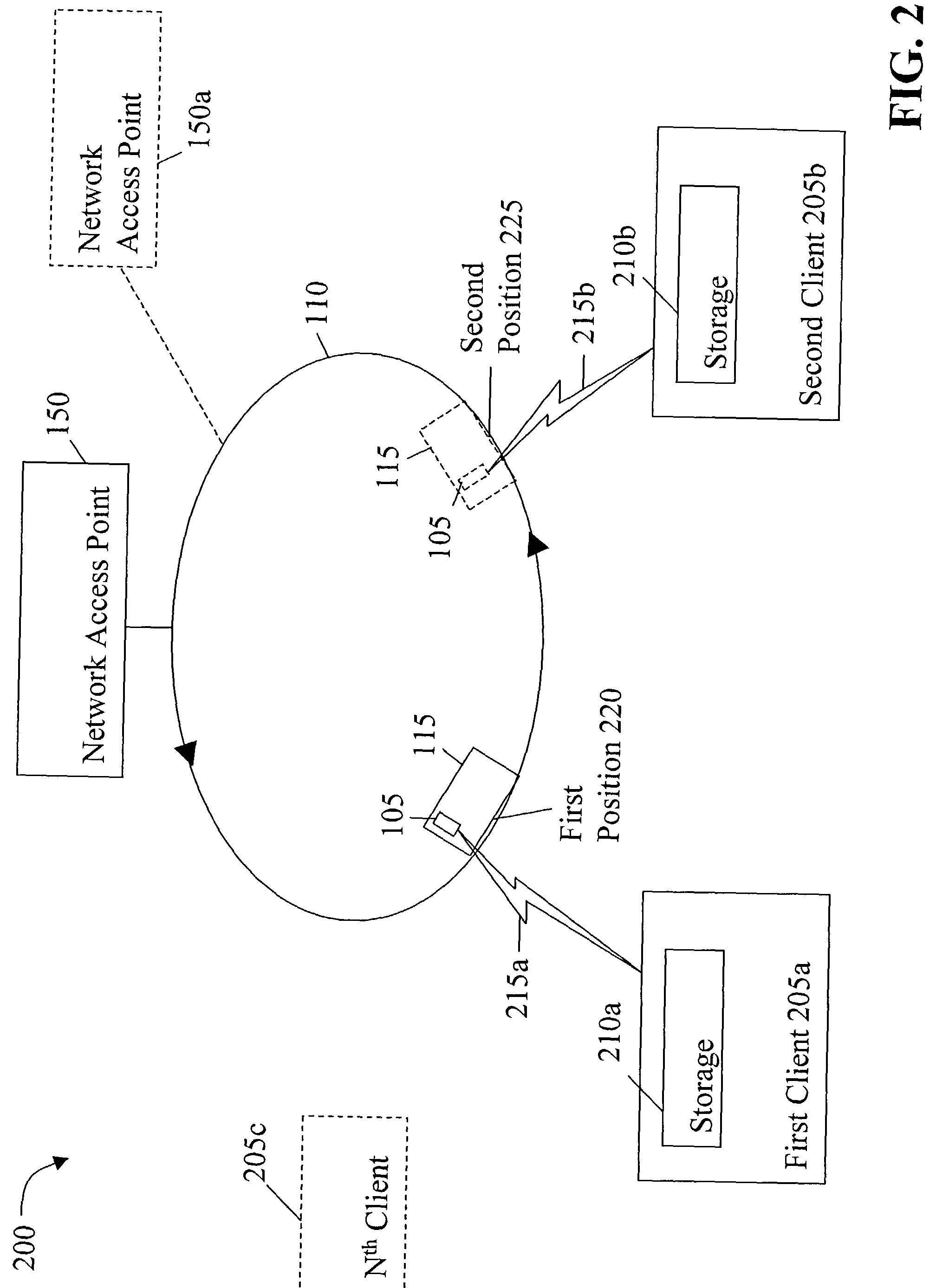

Hybrid wireless network for data collection and distribution

ActiveUS20040004948A1Increase data bandwidthMinimize power consumptionNetwork topologiesData switching by path configurationTelecommunicationsWireless transmission

An electronic data transport system includes a mobile access point and a carrier for moving the mobile access point over a surface and / or water route. The mobile access point includes a communications module for wirelessly transmitting data to and receiving data from one or more client devices when the client device is in proximity to the mobile access point.

Owner:MASSACHUSETTS INST OF TECH

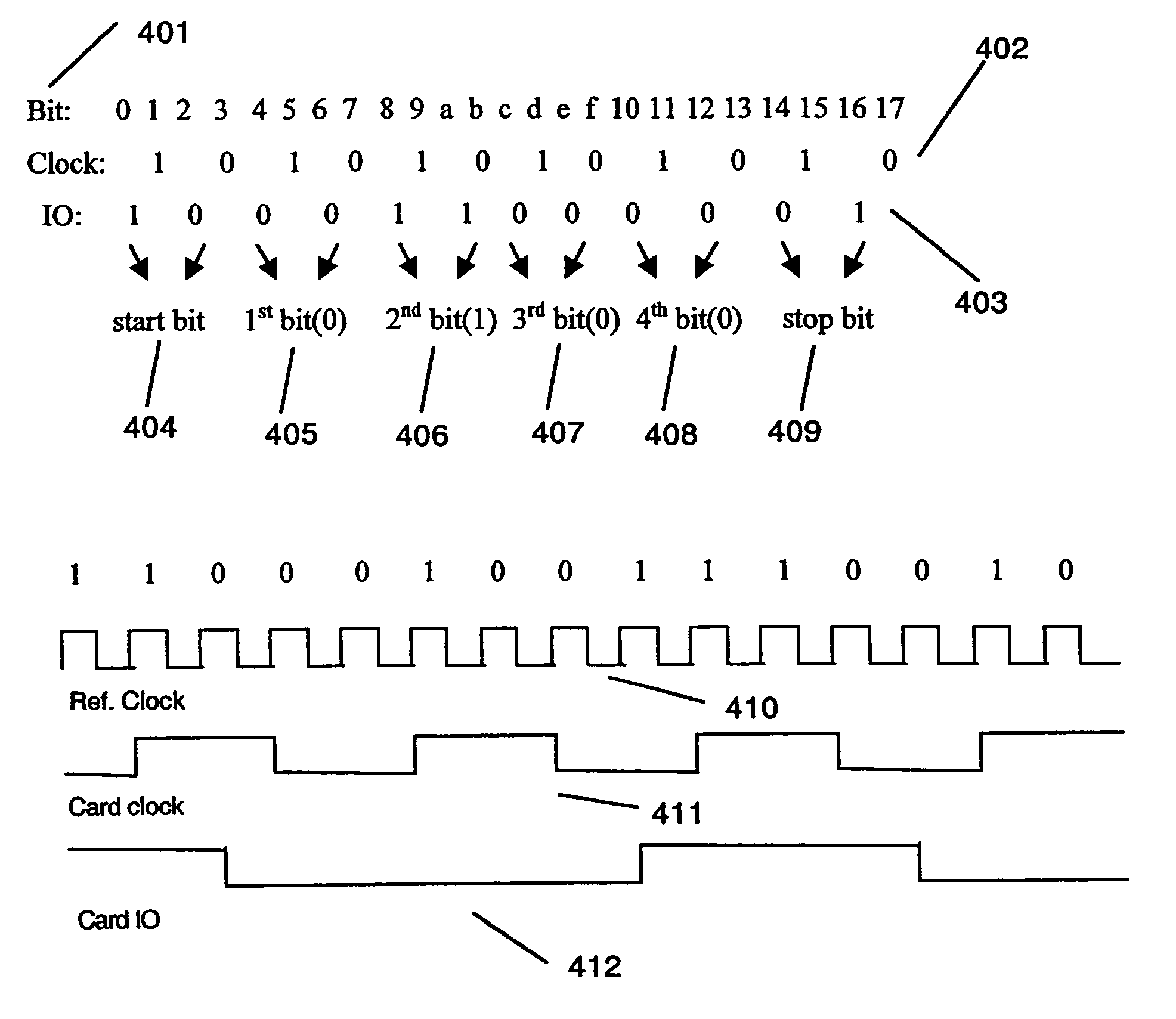

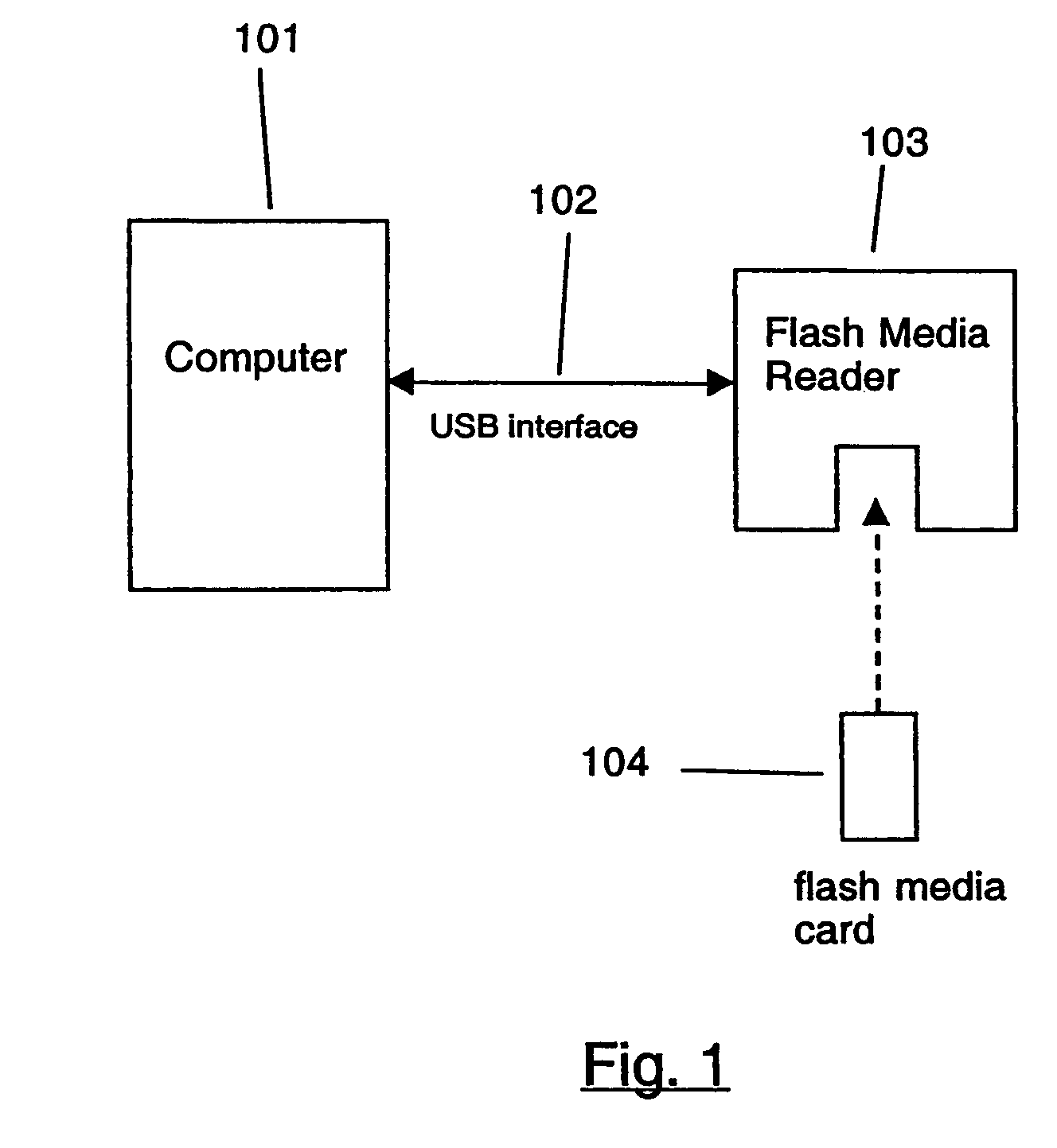

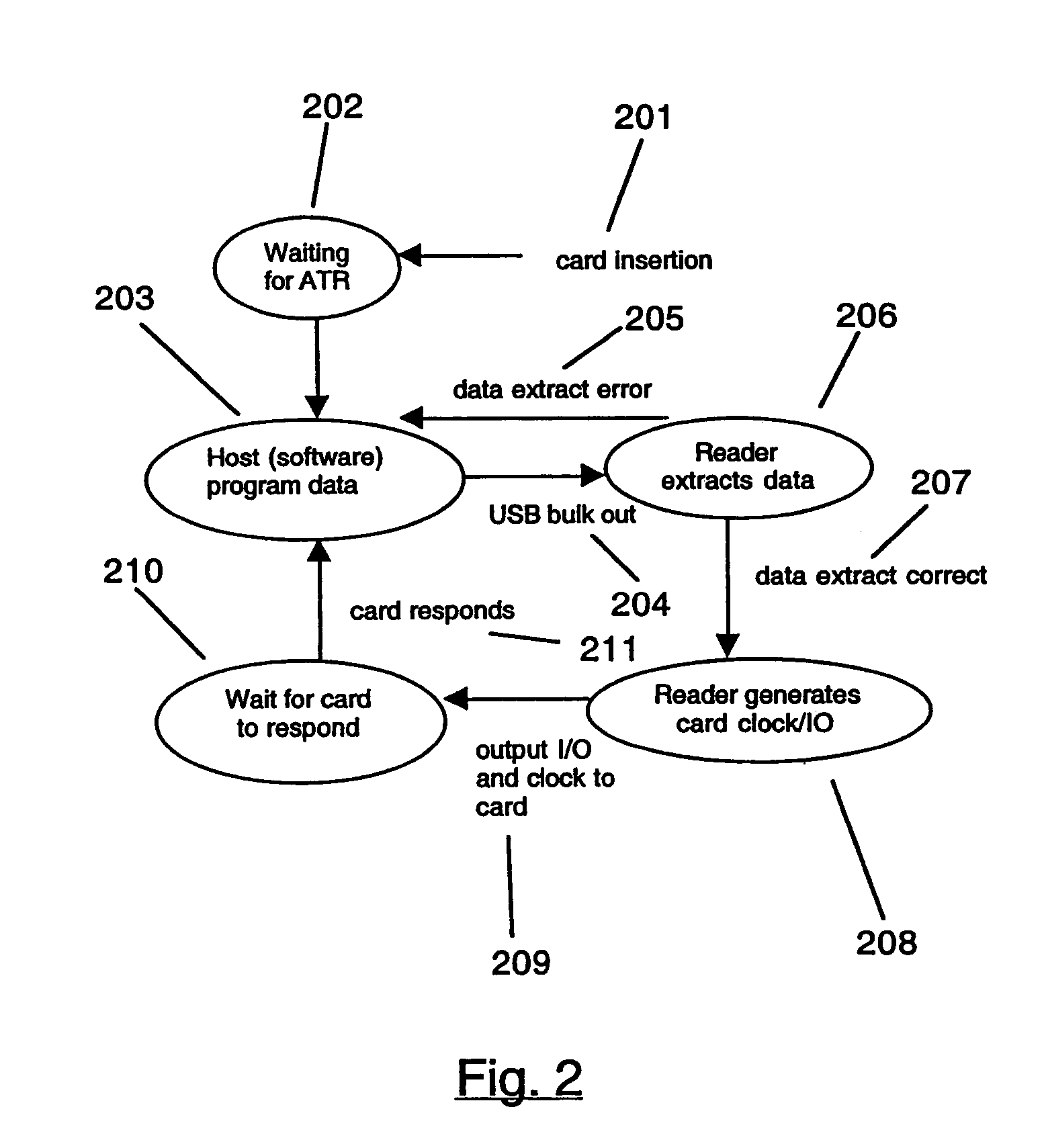

Reconfigurable flash media reader system

InactiveUS7065591B2Increase data bandwidthComponent plug-in assemblagesSensing record carriersData streamNetwork packet

A reconfigurable flash media reader system provides a flash media reader that accepts both asynchronous and synchronous flash media cards. The reader identifies the card type of the inserted flash media card and notifies the host computer of the card type. The host computer has a list of interface information for different types of flash media cards and references the card type in the list and sets the proper baud rate on the reader. If the flash media card is a synchronous card, data that is to written into the flash media card is gathered and converted to the proper card IO strobes for the card type which are interleaved with the proper card clock strobes for the card type into a bit stream in a bulk transfer packet. The reader extracts the data bit stream from said bulk transfer packet and clocks the data bit stream into the flash media card using the baud rate as a reference clock.

Owner:MAISHI ELECTRONICS (SHANGHAI) LTD

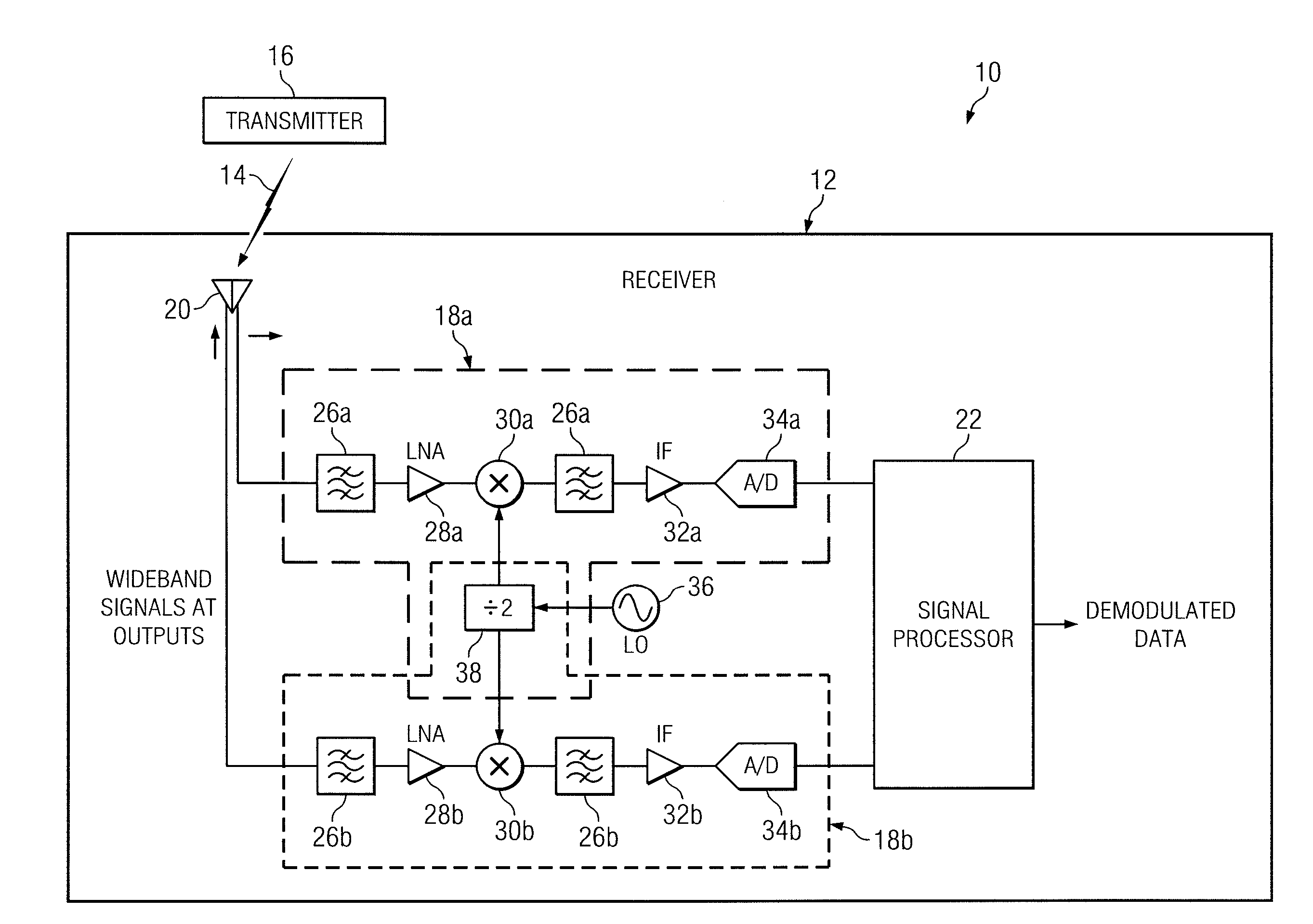

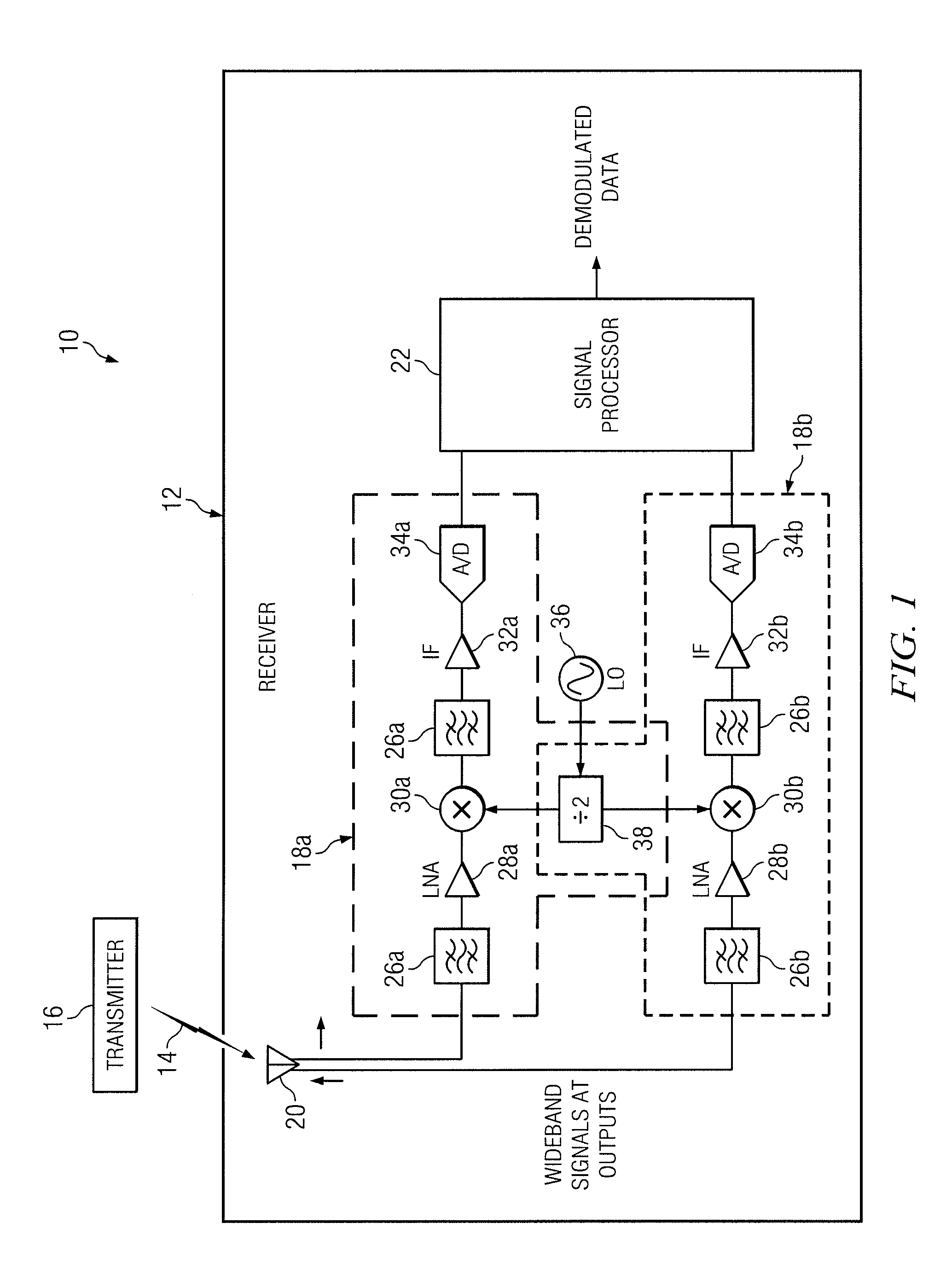

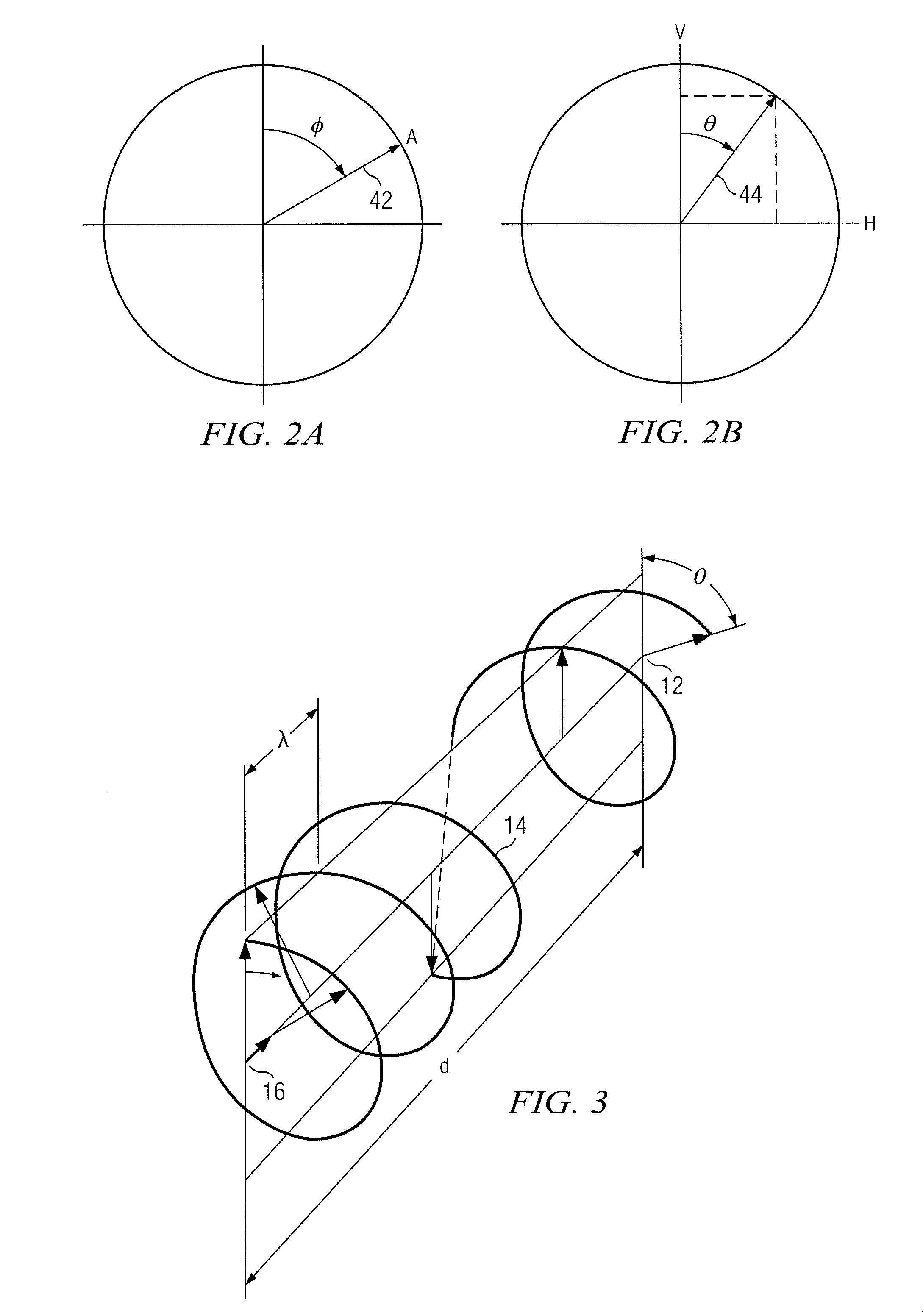

Cross Domain Modulation Scheme for a Wireless Communication Link

ActiveUS20110019630A1Disadvantages can be reduced eliminatedProblems can be reduced eliminatedMultiplex communicationFrequency-modulated carrier systemsTelecommunications linkCommunication link

In certain embodiments, a wireless communication link includes a wireless receiver that receives a circular polarized signal from a remotely configured transmitter. The circular polarized signal has a polarization vector that rotates at a radial velocity. The wireless receiver determines a phase deviation in the radial velocity of the polarization vector and demodulates information from the circular polarized signal according to the determined phase deviation. The phase deviation is caused by a frequency deviation of the circular polarized signal generated by the transmitter.

Owner:RAYTHEON CO

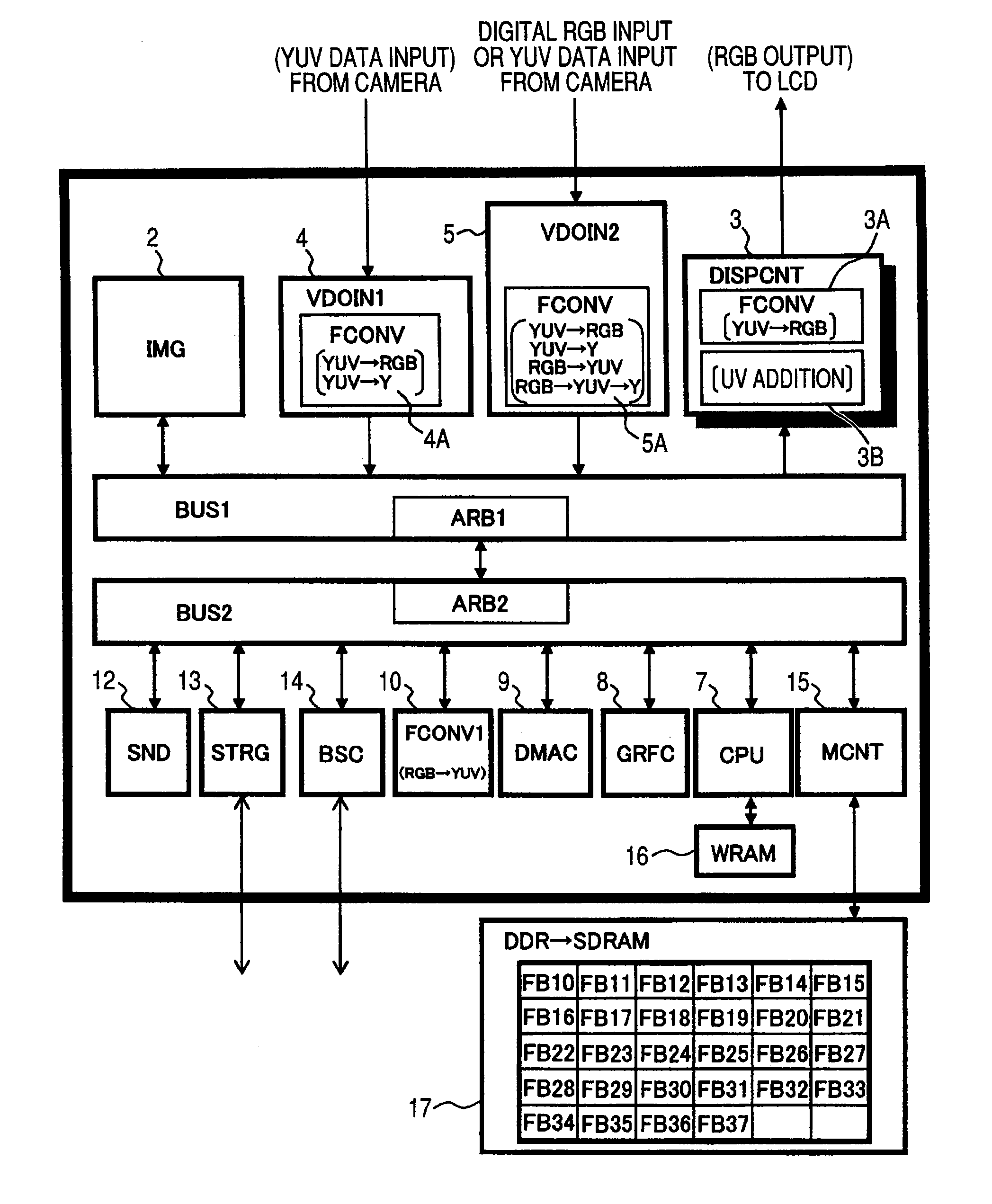

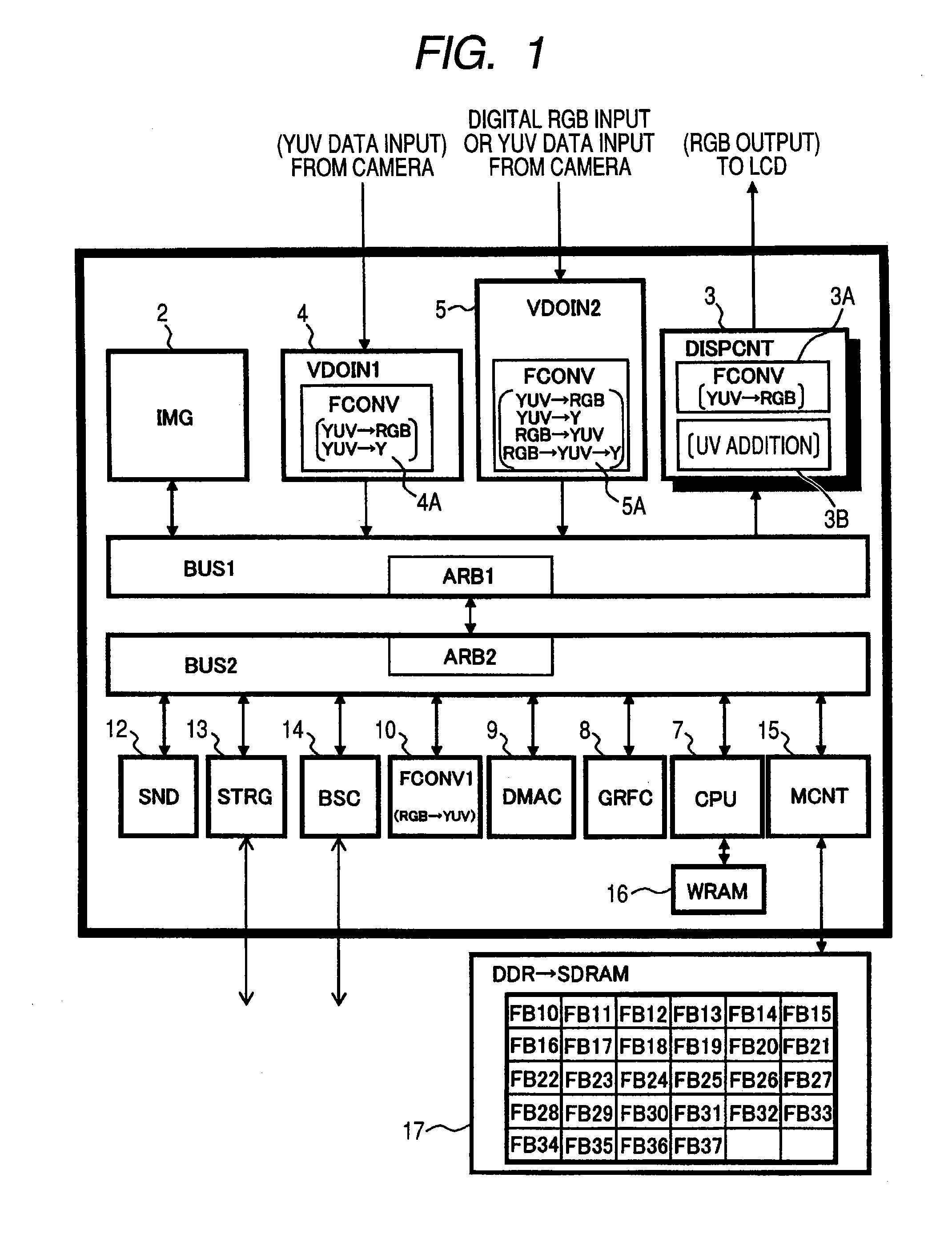

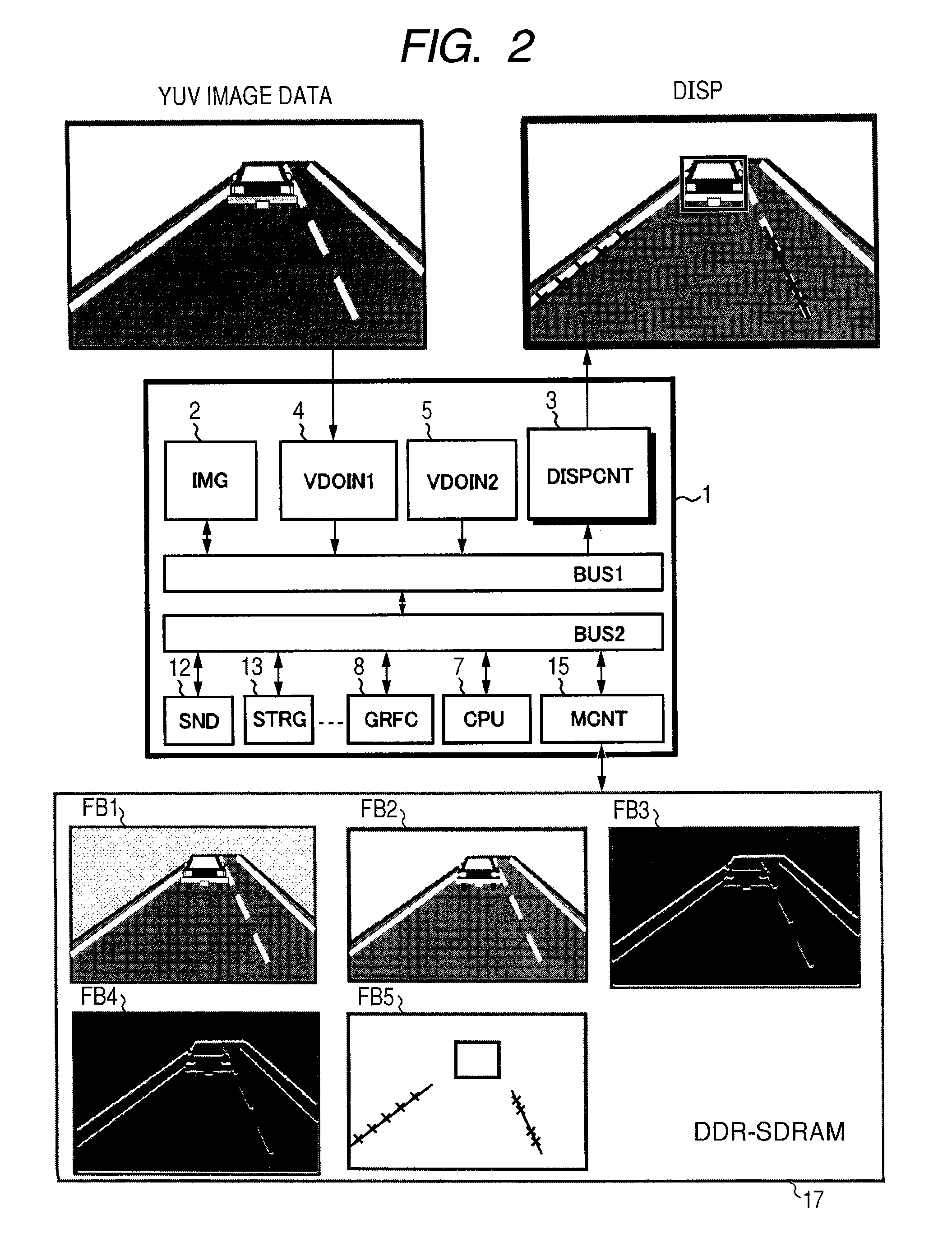

Data processor

ActiveUS20080049029A1Reduce system costReduce data processing costsImage analysisRoad vehicles traffic controlControl storeImaging data

The present invention is to contribute to reduction in cost of a system performing image recognition and display control on input image data. A data processor includes a central processing unit, a graphic controller, a display controller, an image recognizing module, a memory controller capable of controlling an access to an external memory, and image data input units for inputting image data from the outside and capable of performing necessary format conversion, and the components are formed on a single semiconductor substrate. The display controller performs display control on the image data read from the external memory via the memory controller. The image data input unit stores the image data input from the outside or the image data subjected to the necessary format conversion into a first area in the external memory via the memory controller. The image recognizing module or central processing unit executes an image process using the image data in the first area or image data in a second area, obtained by performing necessary data process on the image data, and stores a result of the process in a third area in the external memory.

Owner:RENESAS ELECTRONICS CORP

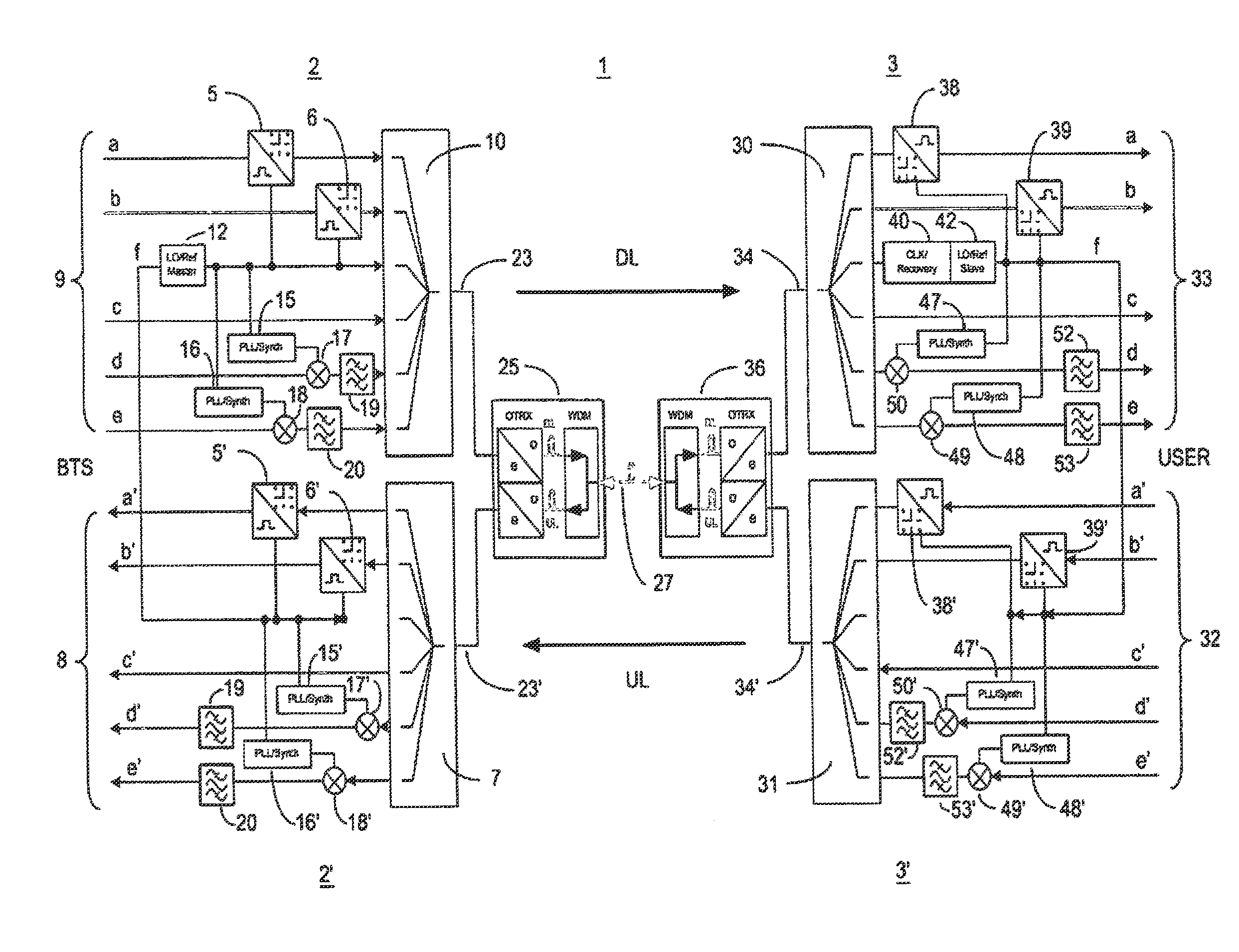

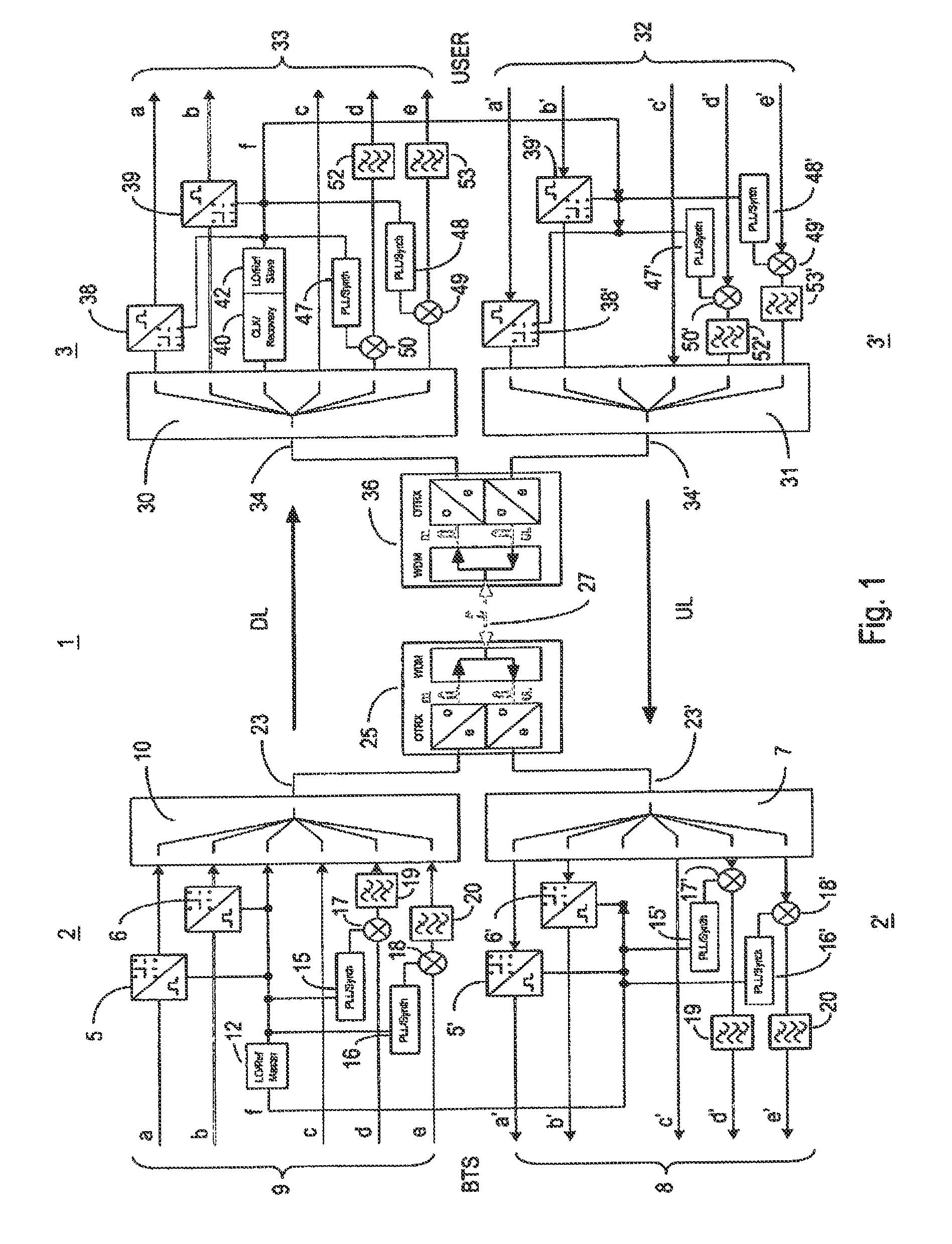

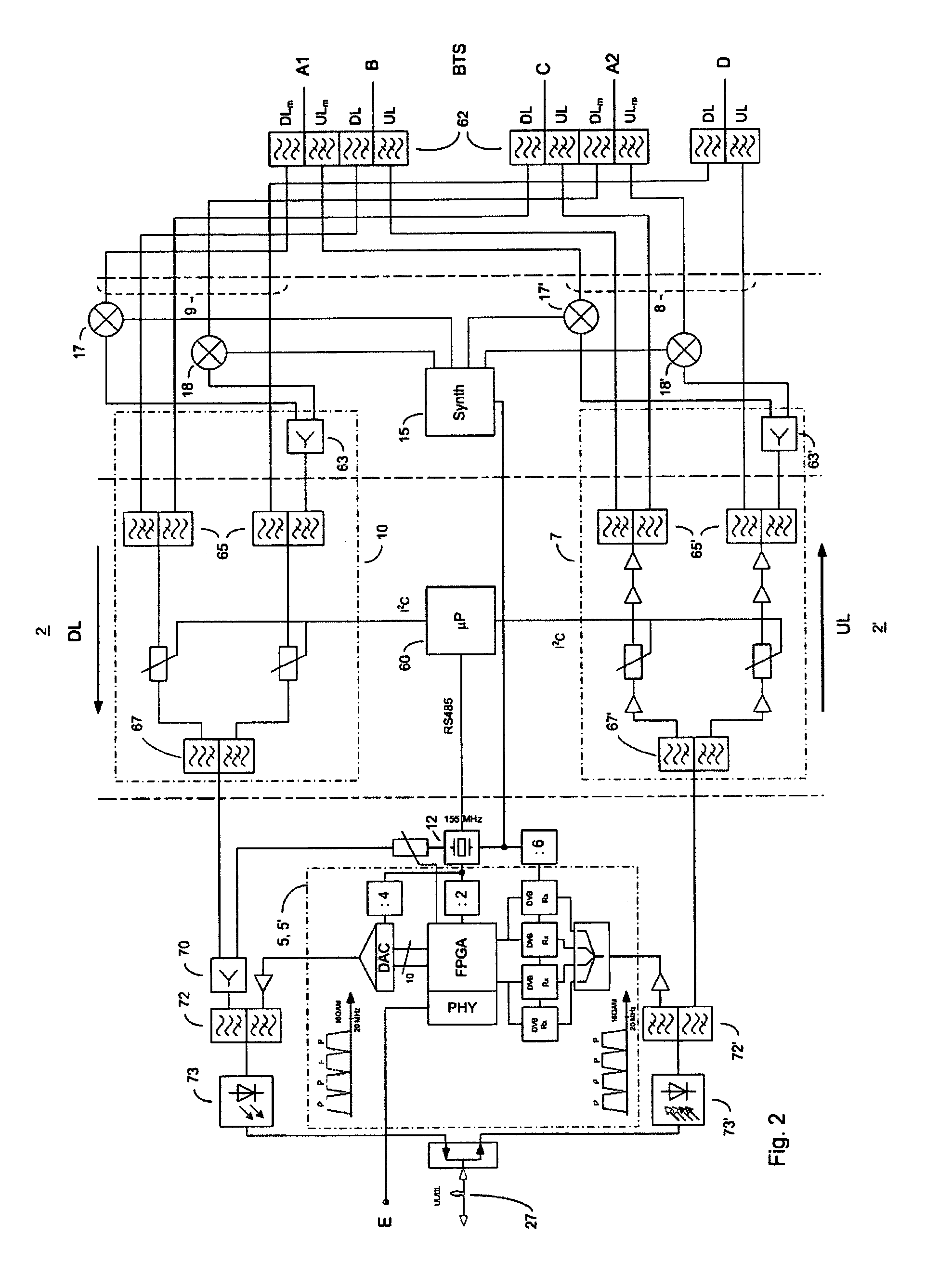

Master unit, remote unit and multiband transmission system

ActiveUS8681916B2Reduced strengthSufficient signal to noise ratioTime-division multiplexFrequency-division multiplexModem deviceTransport system

A master unit and a remote unit is provided for a multiband transmission system for distributing and combining signals of at least one wireless communication network and at least one digital network. A reference frequency generator is arranged in the master unit, the reference frequency generator being designed to clock a master modem for converting the signals of the at least one digital network. The reference frequency signal emitted by the reference frequency signal is restored via a reference frequency receiver and is used for closing a remote modem that is located there for demodulation.

Owner:ANDREW WIRELESS SYST GMBH

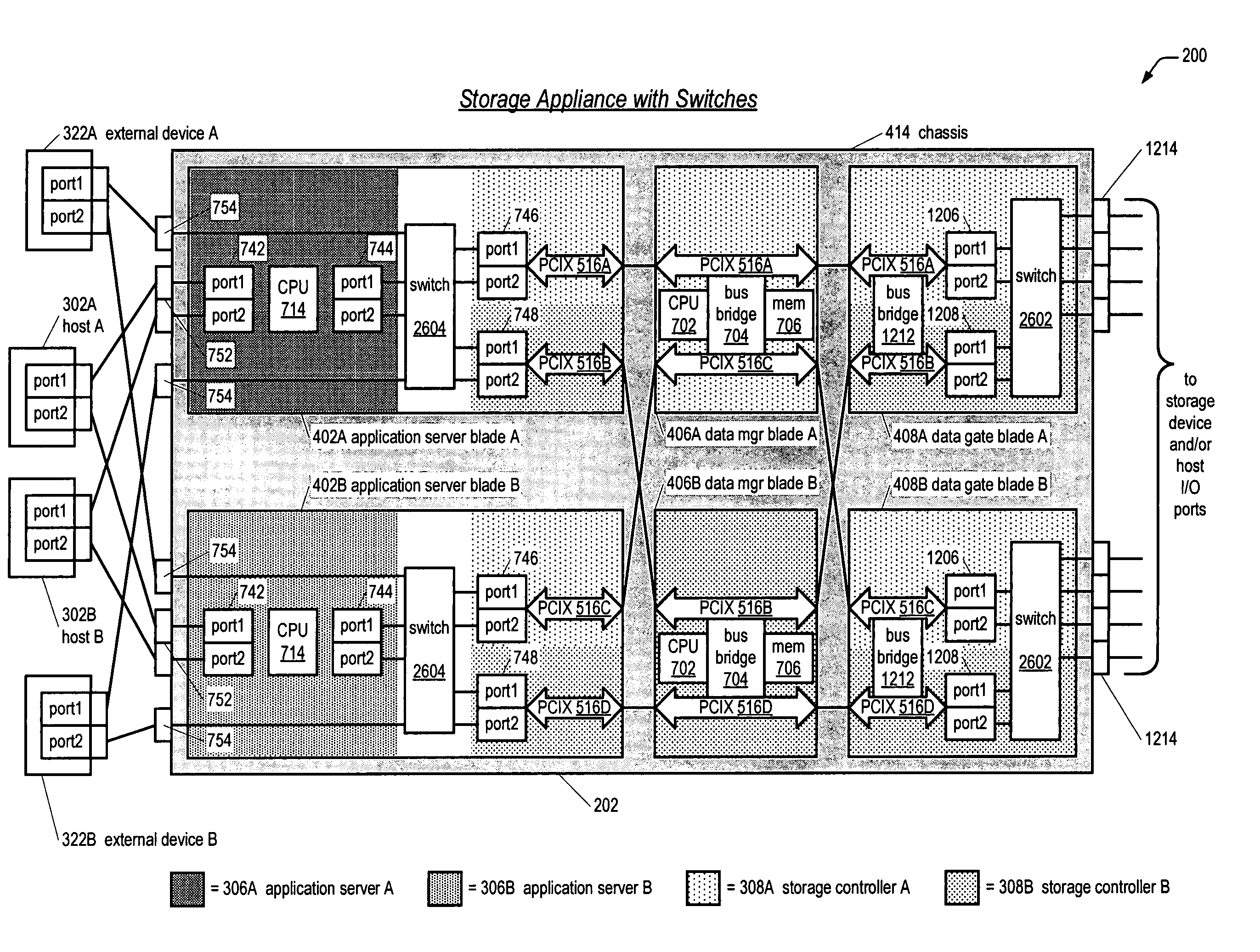

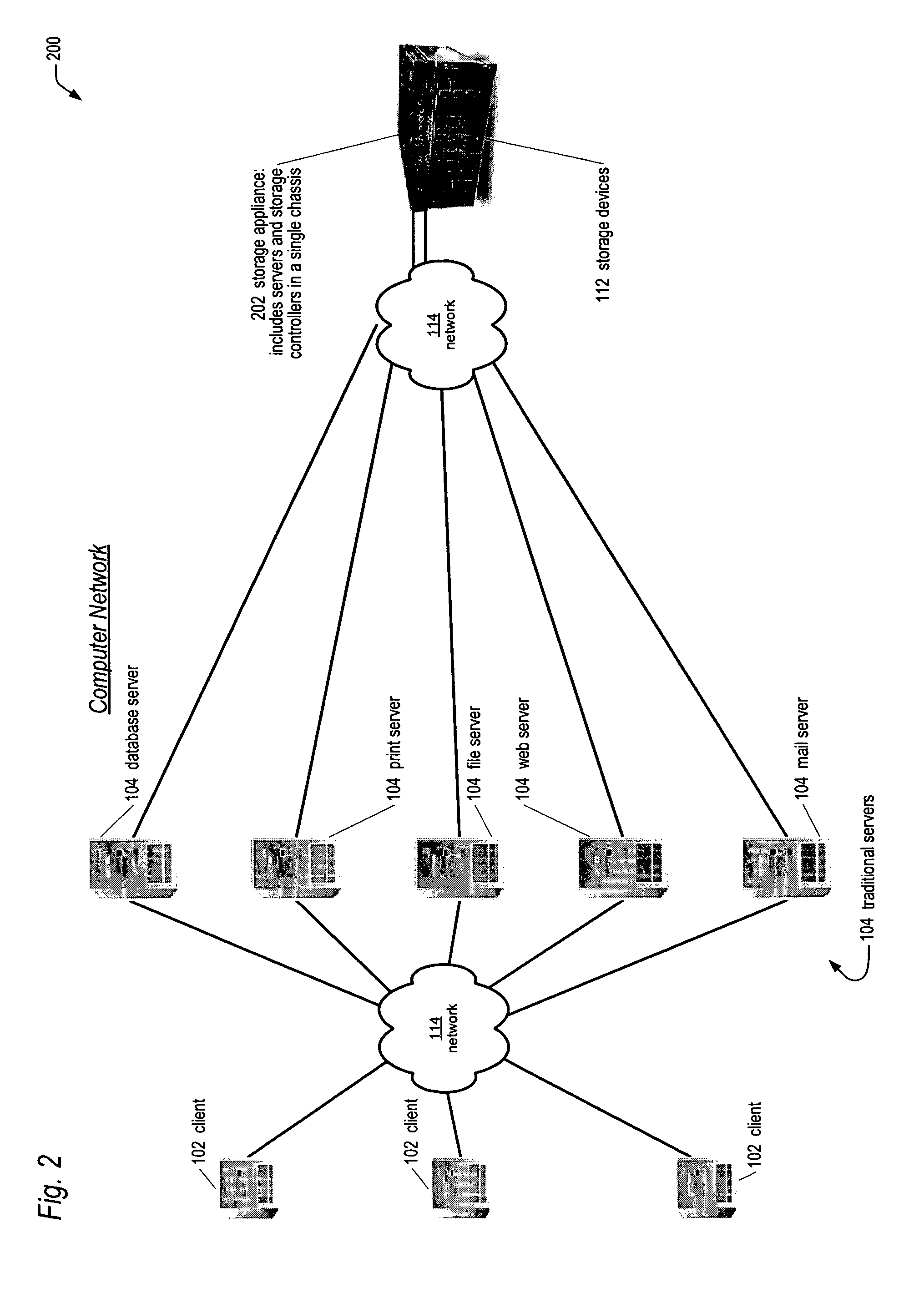

Network storage appliance with an integrated switch

InactiveUS7565566B2Improve performanceIncrease data bandwidthError detection/correctionDigital data processing detailsControl storeData transmission

Owner:DOT HILL SYST

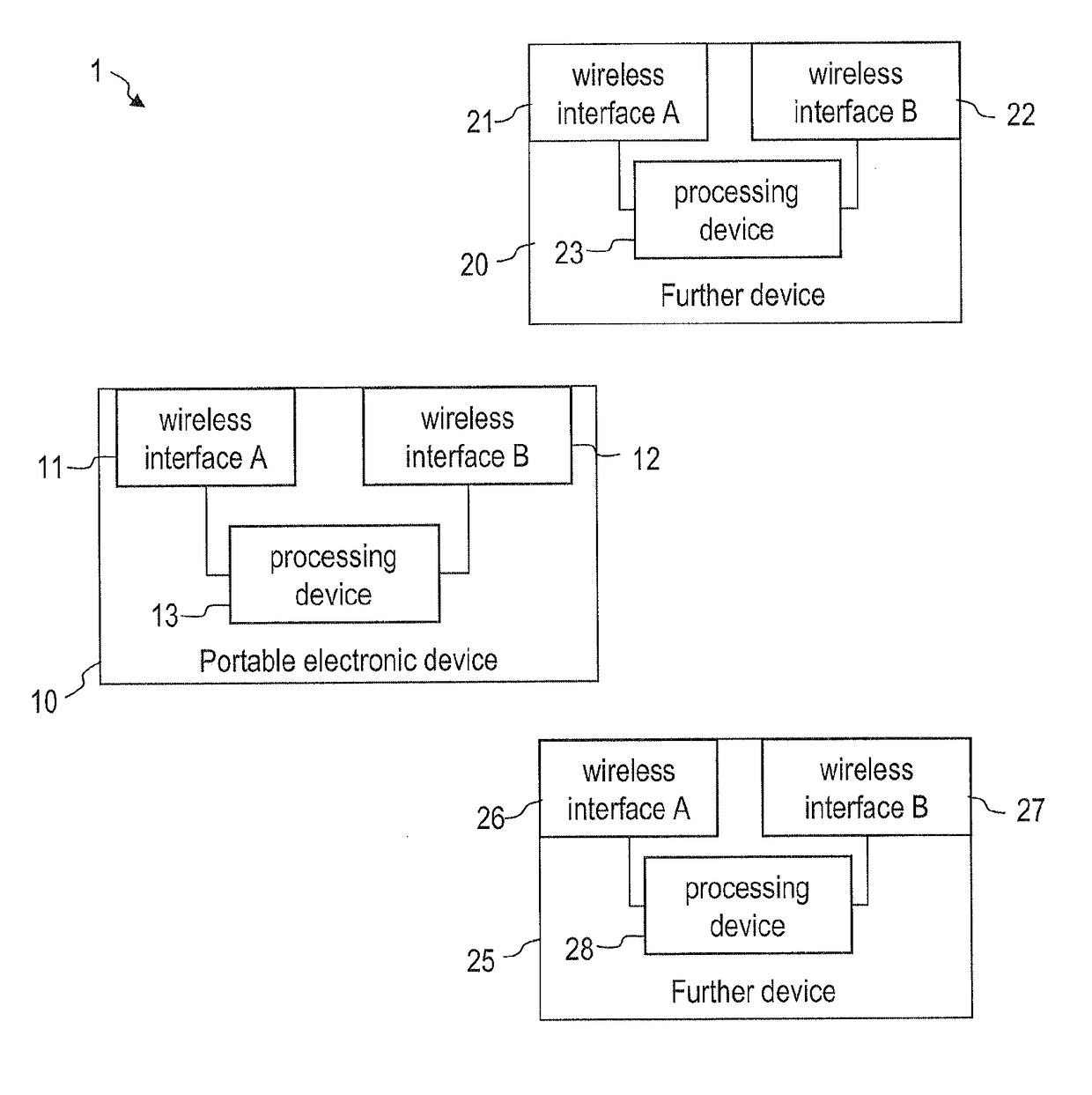

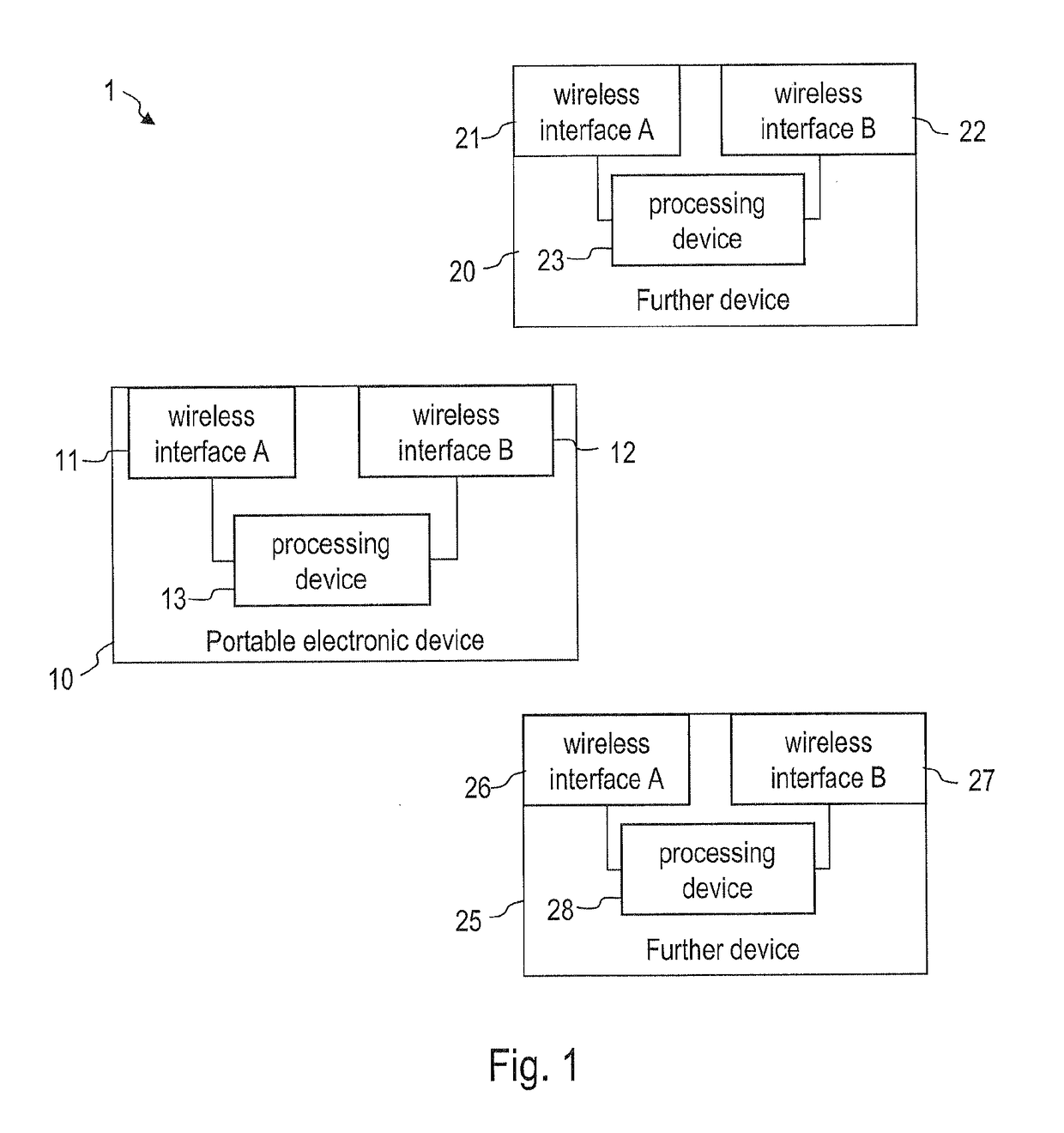

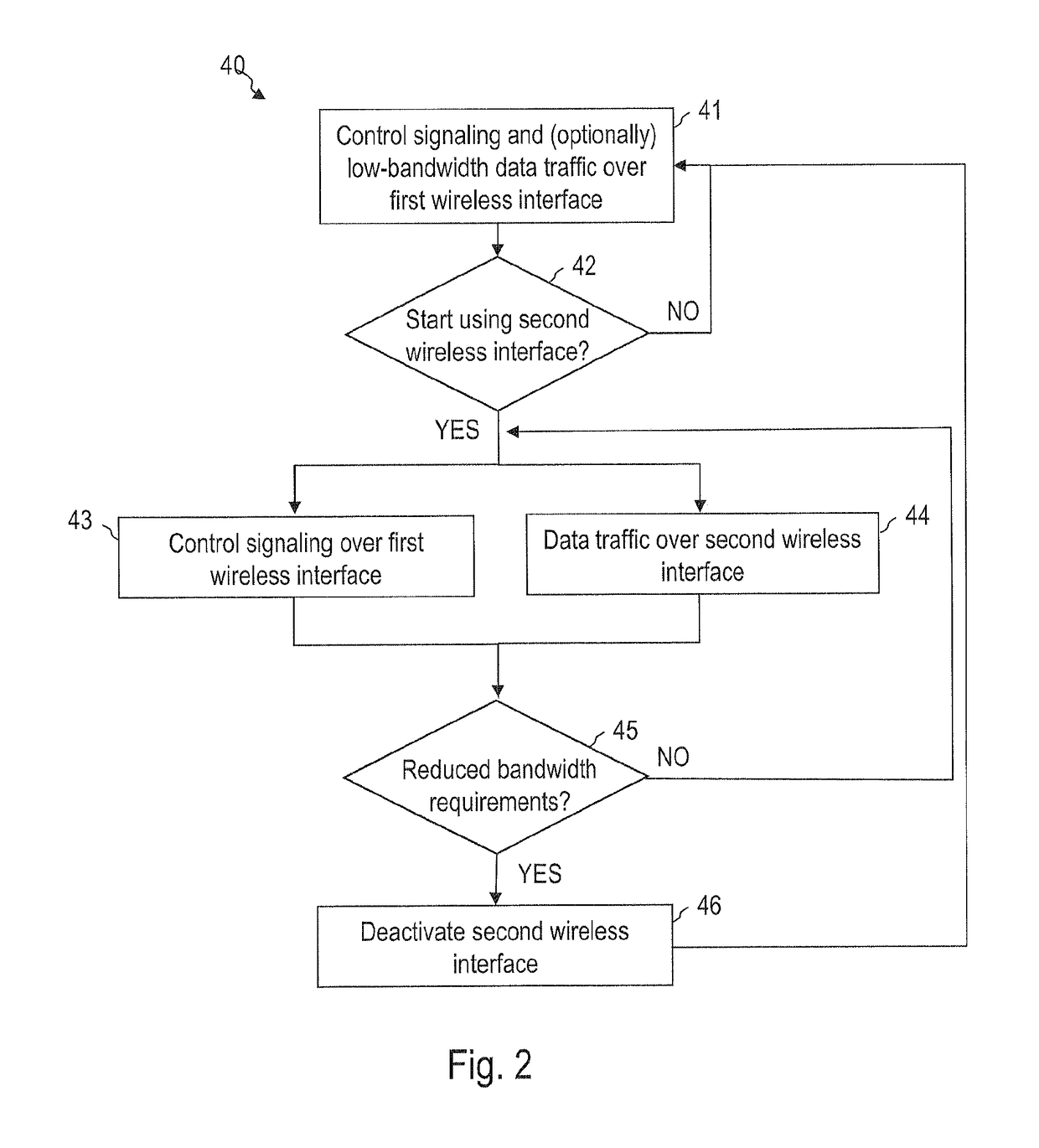

Devices and methods for multi bearer network communication

ActiveUS20170196044A1High bit rateAccommodate largePower managementNetwork traffic/resource managementExecution controlTelecommunications

A portable electronic device comprises a first wireless interface and a second wireless interface. The first wireless interface is controlled to perform a control signaling with a further device over the first wireless interface. The second wireless interface is selectively activated to transmit data traffic to the further device and / or to receive the data traffic from the further device over the second wireless interface. The first wireless interface is maintained in an activated state to control the data traffic over the second wireless interface by the control signaling over the first wireless interface while the second wireless interface is activated.

Owner:SONY CORP

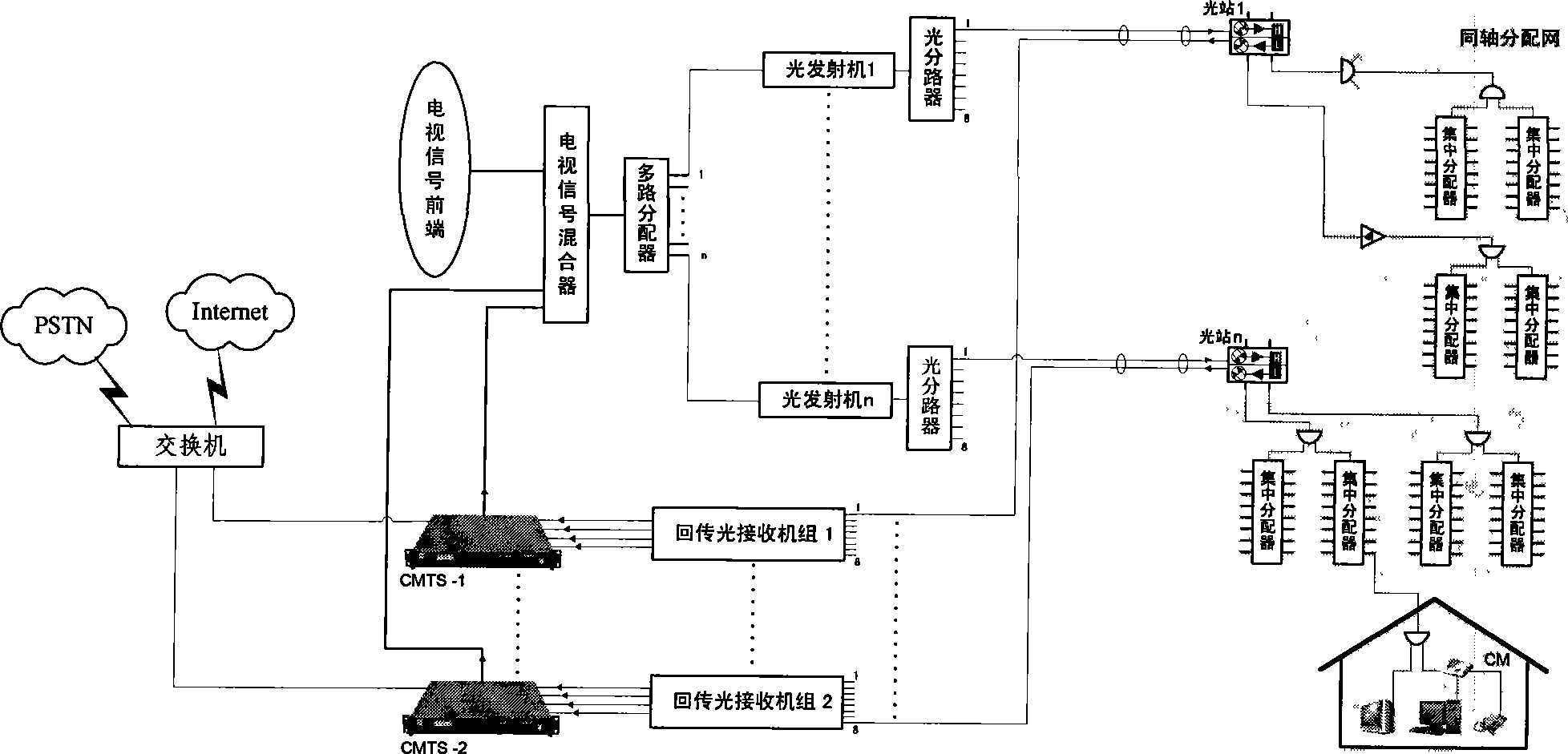

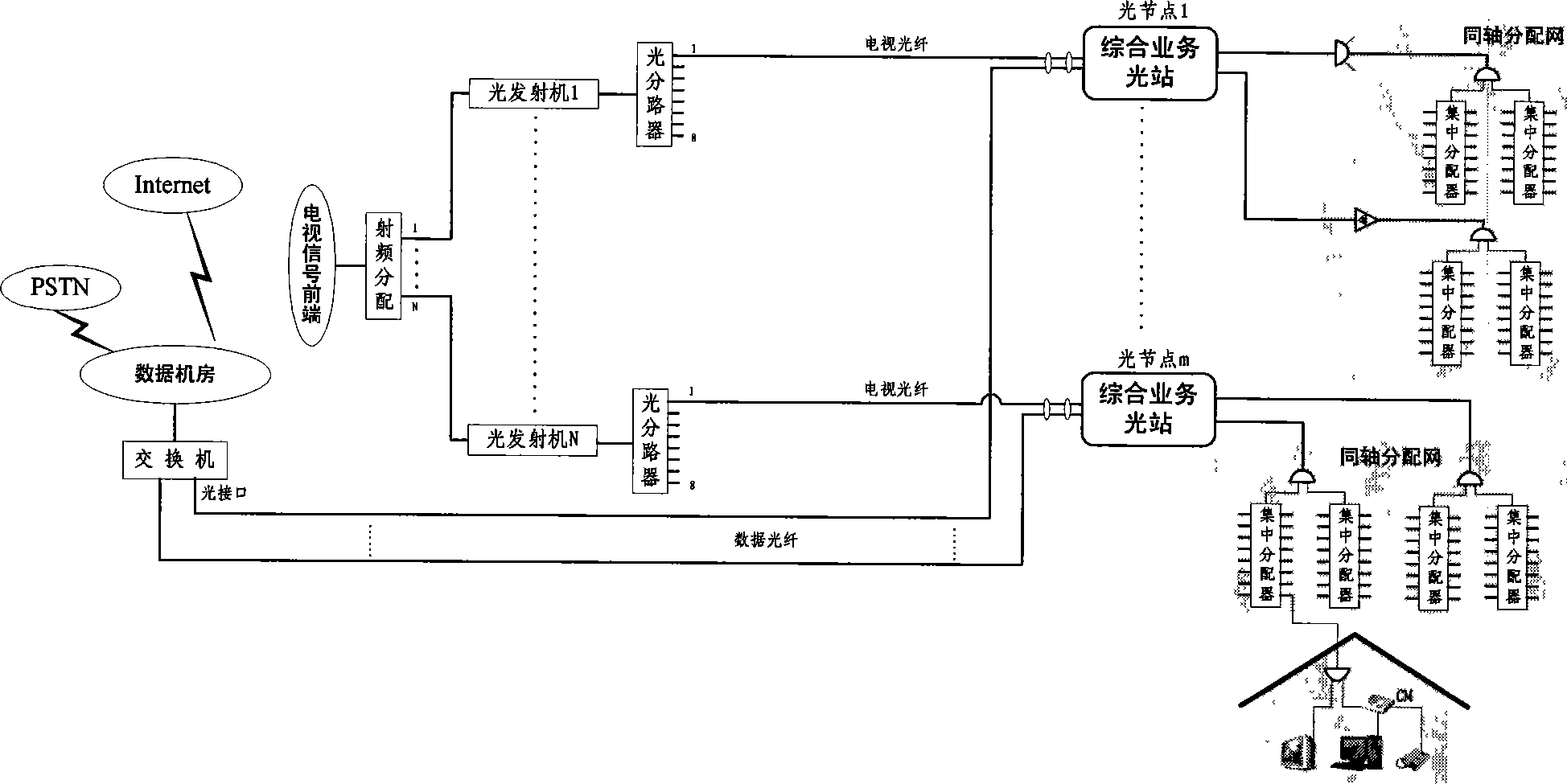

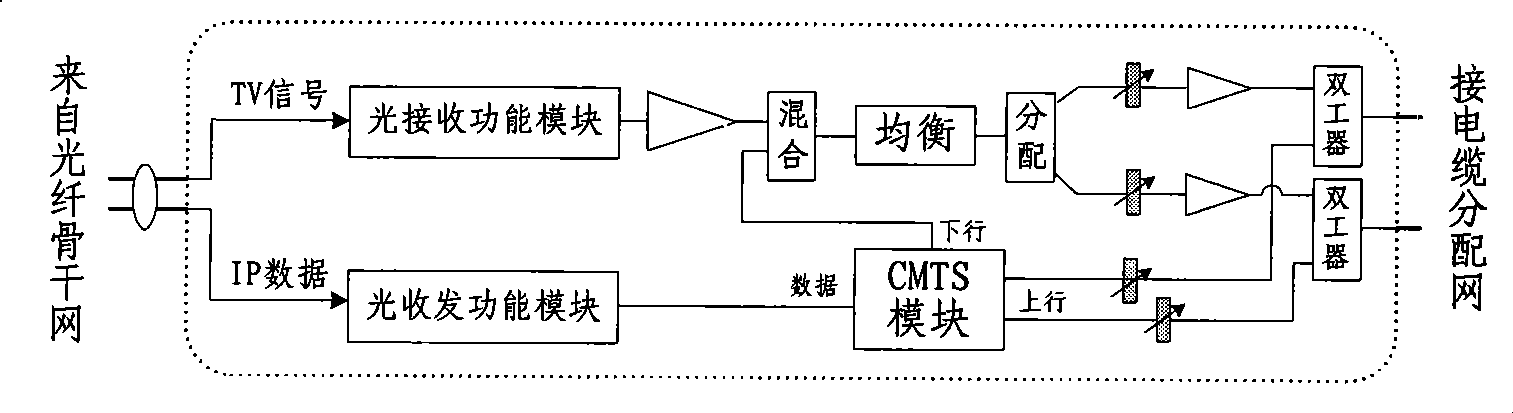

Synthesis business networking method based on HFC broadband network, and synthesis business optical station equipment

InactiveCN101511043AReduce distractionsStable jobData switching networksTime-division multiplexing selectionNetwork deploymentNetwork packet

The invention discloses an integrated service network deployment method based on HFC brand band network and a special equipment - an integrated service light station equipment. A traditional CMTS, a RF signal photoelectric converter and a data signal photoelectric converter are integrated as a whole for forming an integrated service light station that is installed on a light node of HFC for realizing photoelectric convert of the television signal and IP data signal simultaneously, and transmitting IP data packet. The equipment also has a remote monitor function for realizing centralized monitoring and managing each integrated service light station equipment and the loaded brand bane user distributed arrangement. Compared with the prior art, the method and the equipment provided by the invention has advantages of reducing filler noise disturbance, increasing average family brand band of the user, simplifying the network structure, reducing network deployment cost and easy to maintenance.

Owner:重庆景宏视信科技有限公司

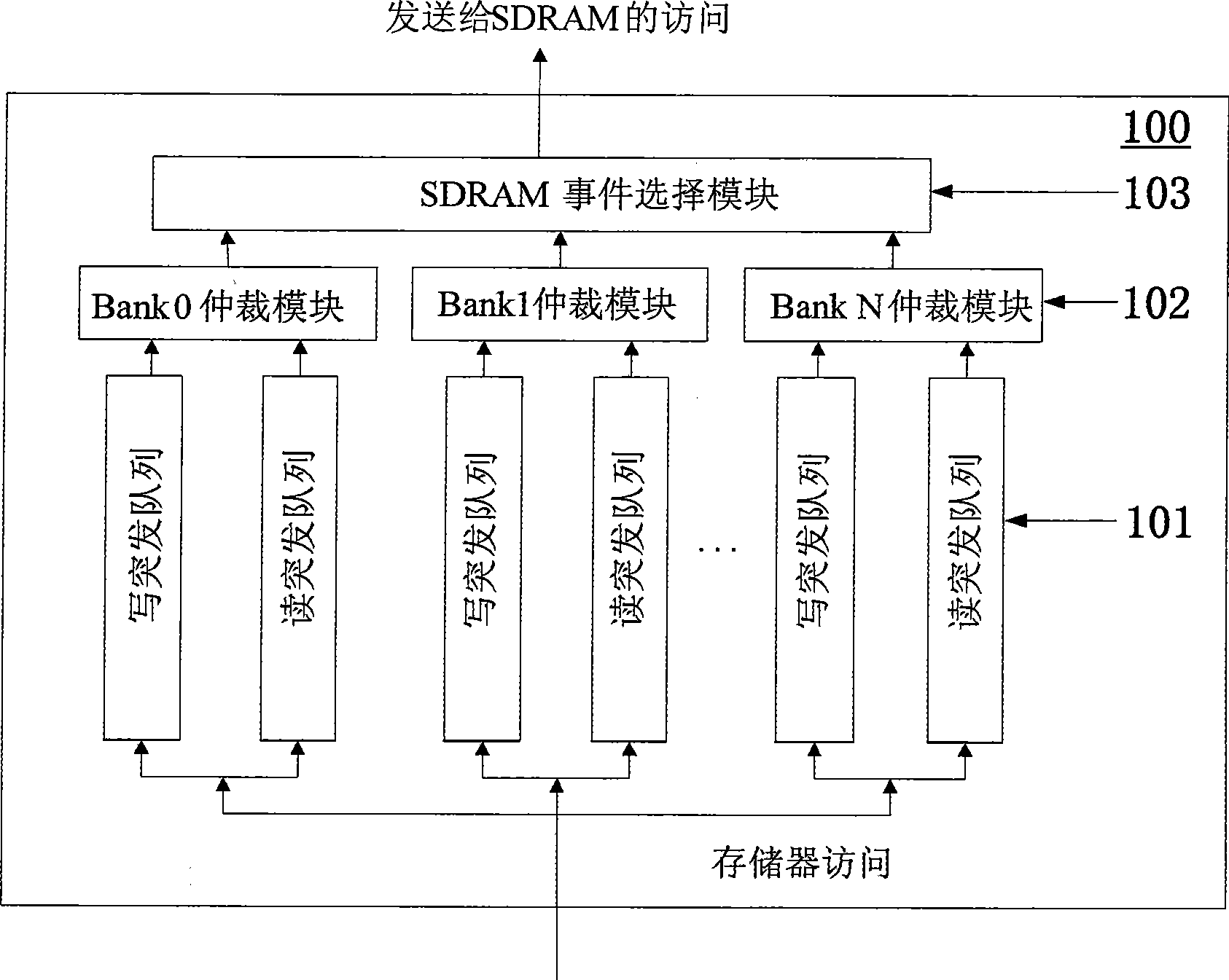

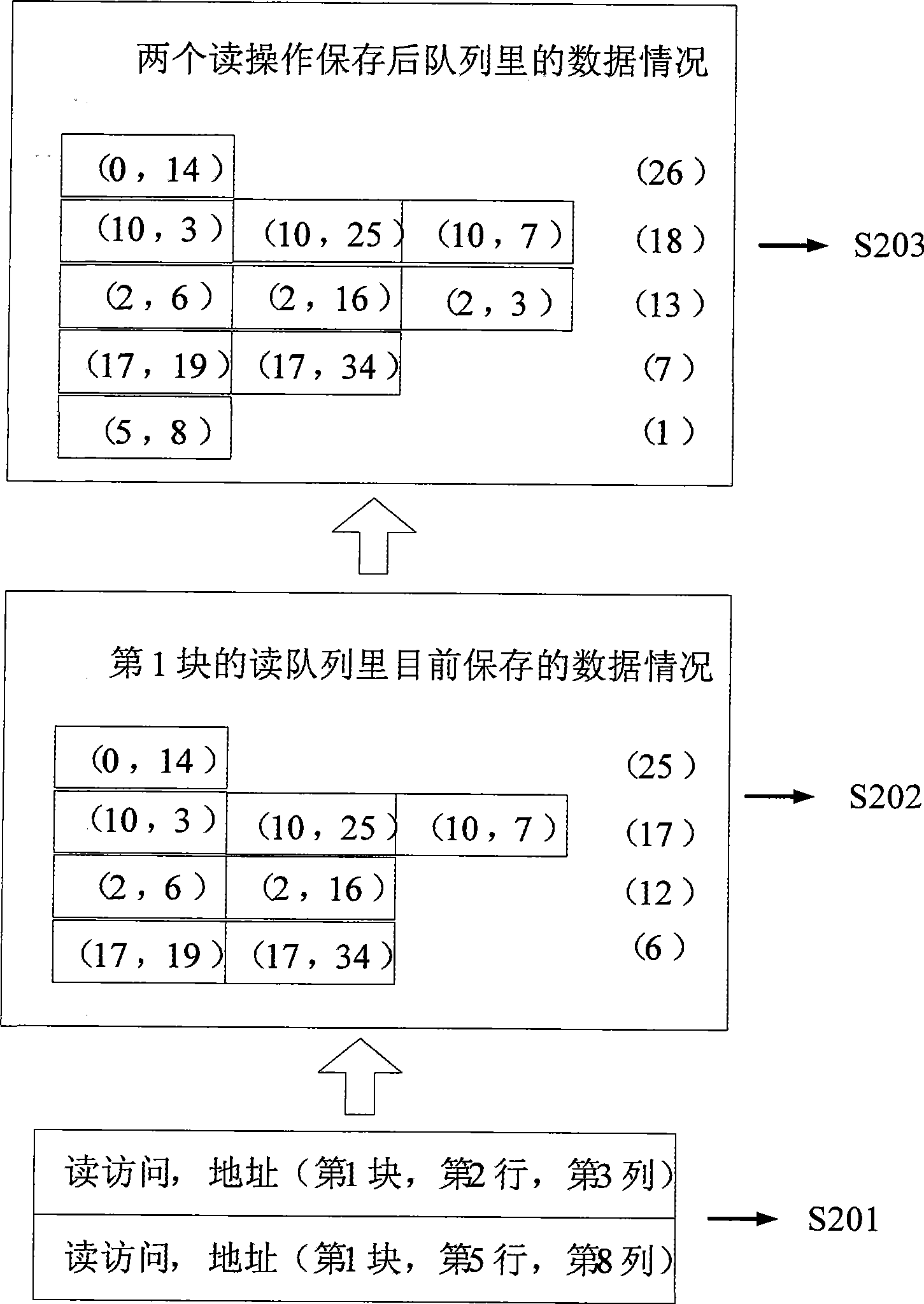

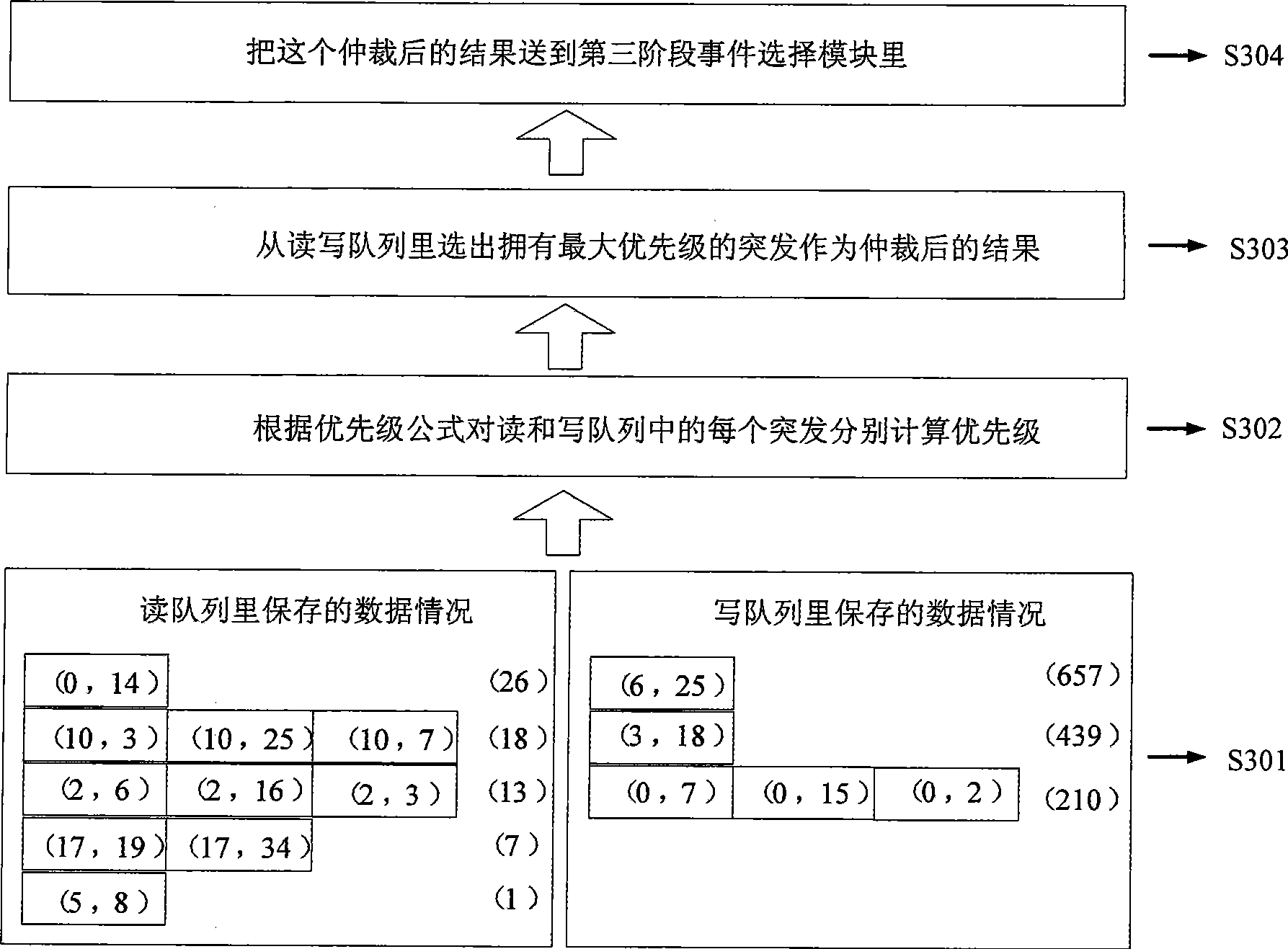

Outburst disorder based memory controller, system and its access scheduling method

InactiveCN101470678ASolve Bandwidth BottlenecksIncrease data bandwidthElectric digital data processingUniform memory accessDirect memory access

The invention provides a memory controller based on the burst disorder memory access dispatching, which is used to the burst disorder memory access dispatching accessed by a memory, and comprises a reading-writing queue module for storing the reading-writing memory access from a processor in a two-dimension mode, a block arbitration module for arbitrating a burst memory access from each block in each memory clock period, and an event selection module for selecting the final memory access operation from the burst of each block after arbitrated to send to the memory. The block is conducted with the burst arbitration to dispatch the disorder memory access through changing the structure of a queue and adopting the priority expression provided by the invention, thereby increasing the data bandwidth of the memory, and reducing the executing time of the processor.

Owner:INST OF ACOUSTICS CHINESE ACAD OF SCI

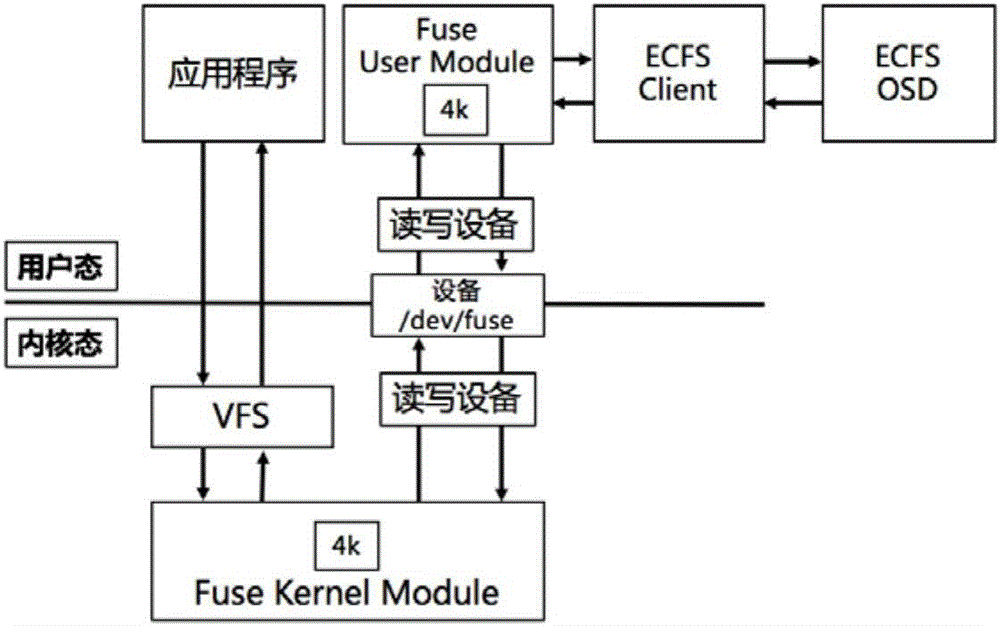

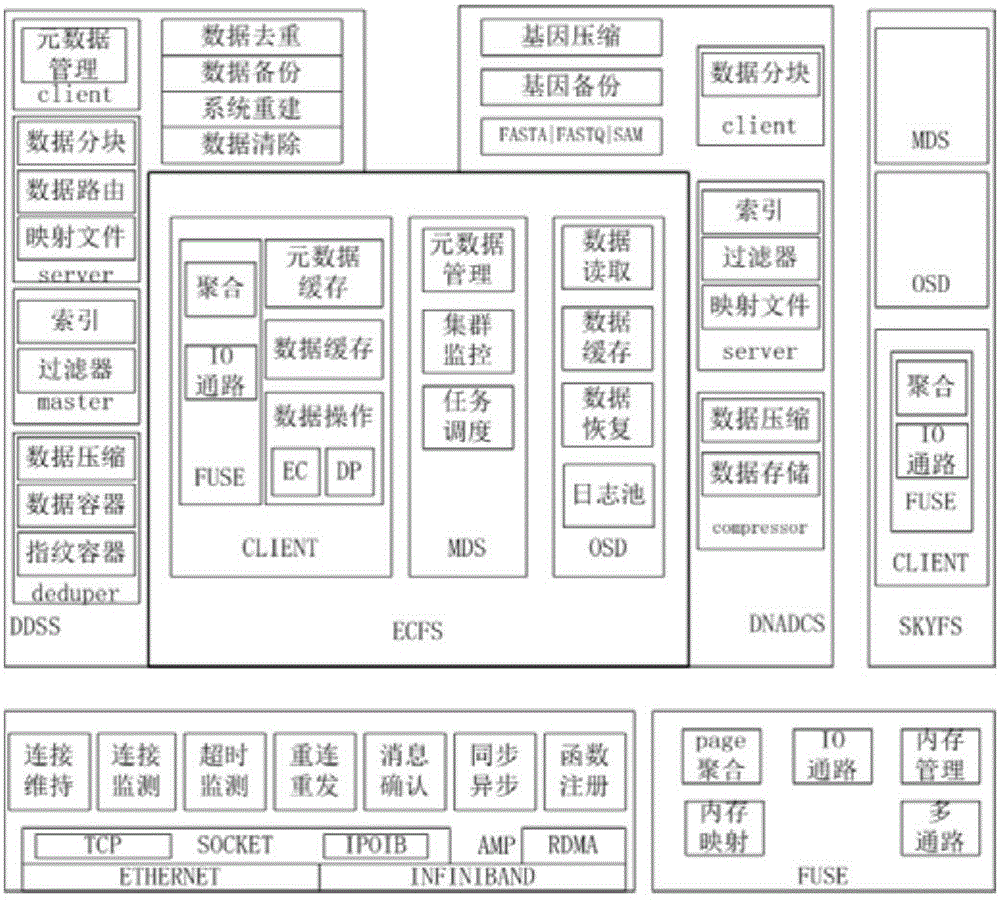

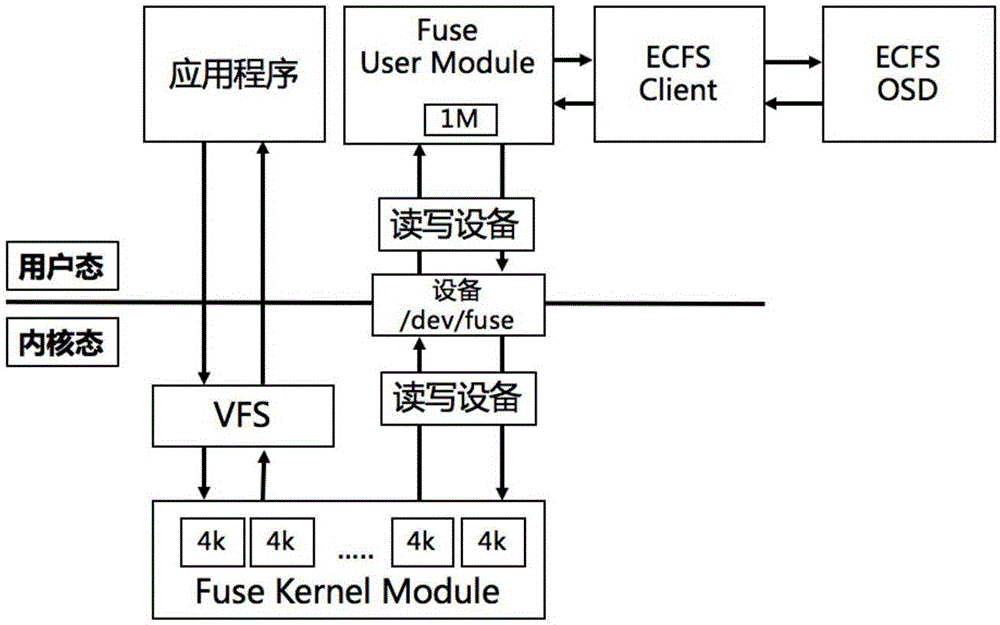

Multi-virtual-machine mapping and multipath fuse acceleration method and system based on kvm

ActiveCN106708627ARelieve pressureAbundant resourcesResource allocationSoftware simulation/interpretation/emulationSystem callClient-side

The invention provides a multi-virtual-machine mapping and multipath fuse acceleration method and system based on a kvm. The method comprises the steps that 1, a delayed writing function is added for a data path of an existing FUSE kernel module, wherein the delayed writing function is that data is aggregated in the FUSE kernel module through a VFS layer and is directly returned to the system for calling when passing through a kernel, and the data is transmitted to a user-mode client-side for data trading operation only when the aggregated data meets a certain size or is added no longer in a certain timer period; 2, multi-mounting-point mounting is conducted on the FUSE kernel module. Multi-virtual-machine data is mapped to a host machine by stripping the FUSE module function and a multi-virtual-machine mapping mechanism, the handling operation on a stripping client-side is issued to a host machine side to reduce the pressure of virtual machines, and more resources are provided for the virtual machines to perform calculating and processing tasks.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI +1

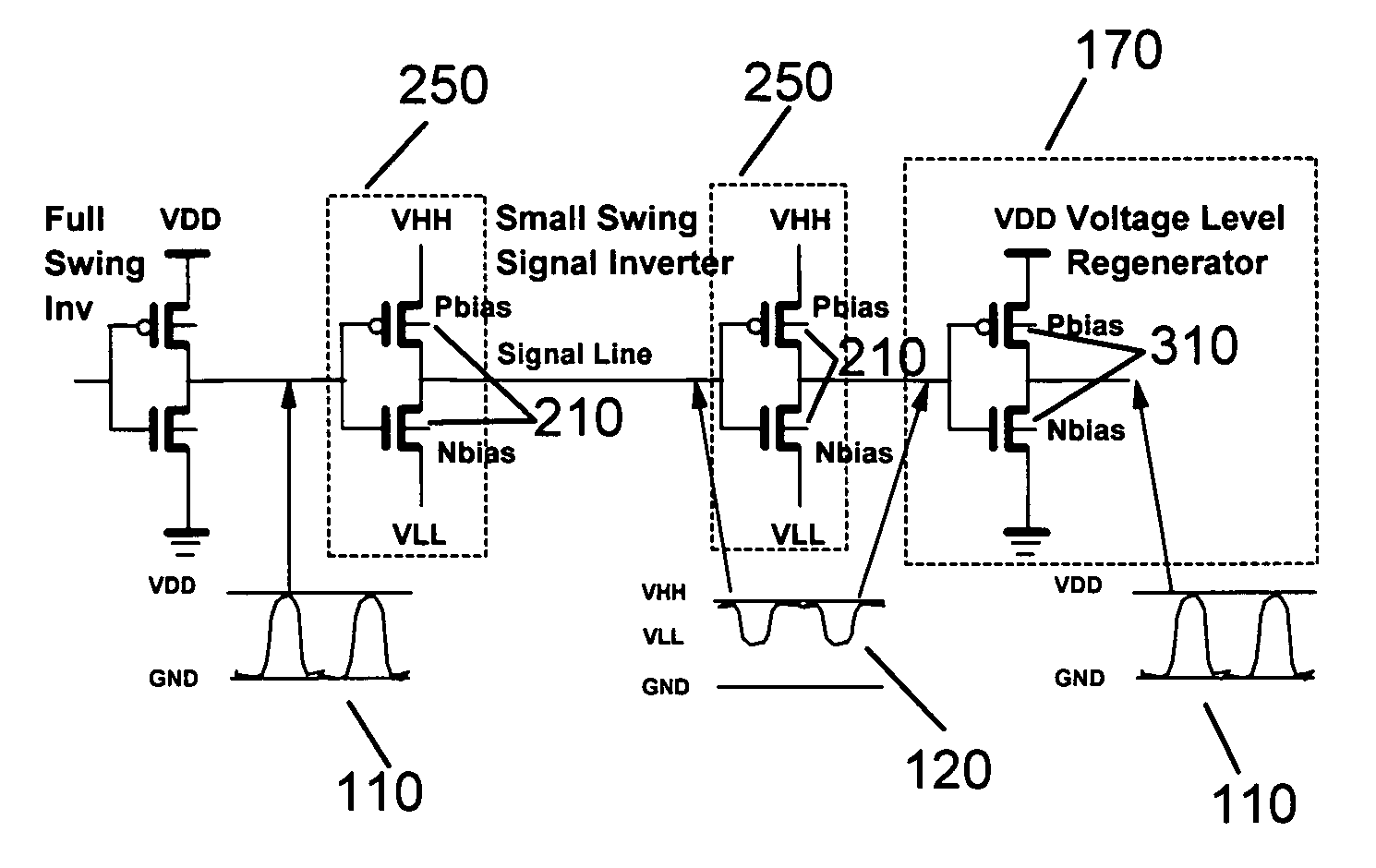

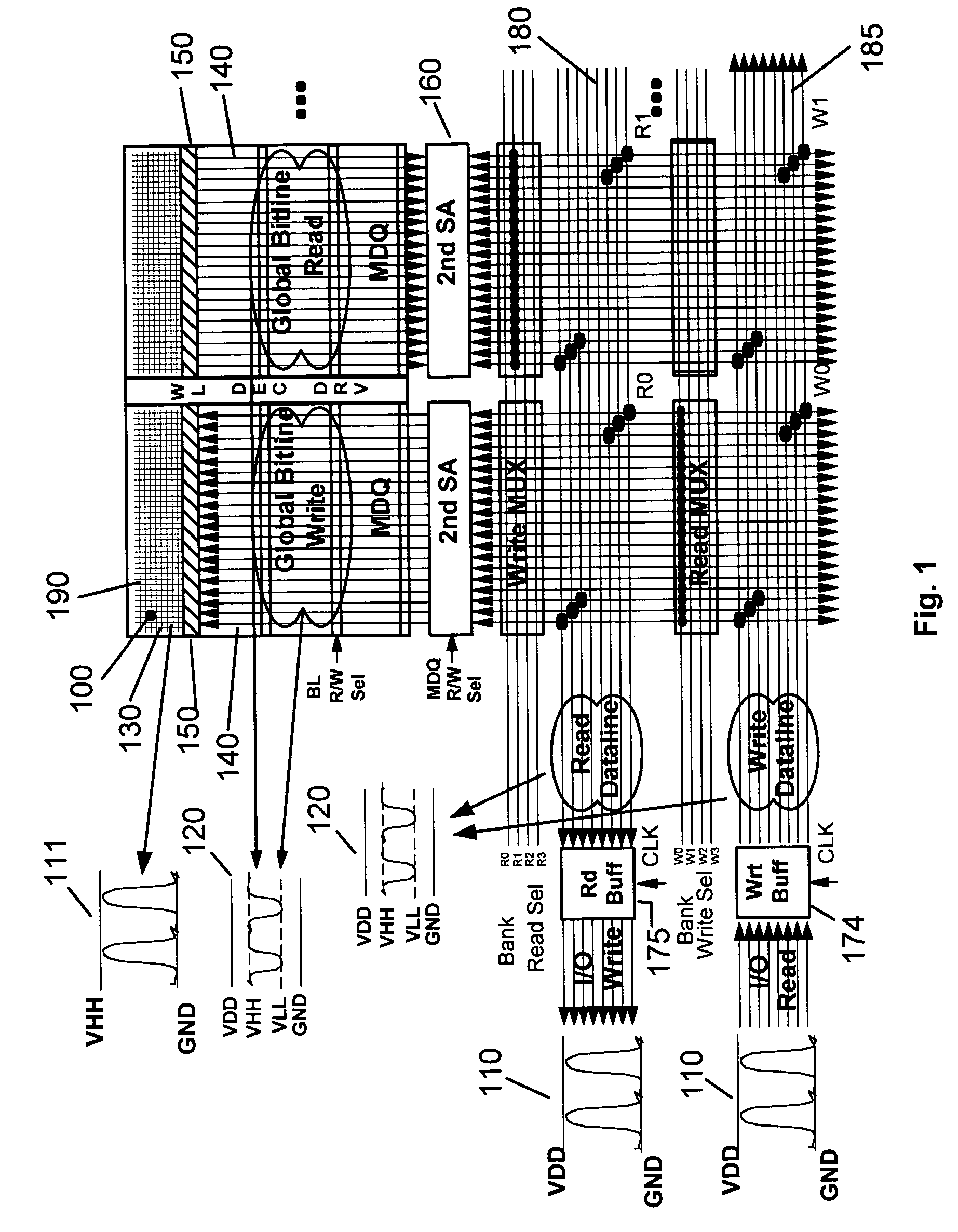

Low power circuits with small voltage swing transmission, voltage regeneration, and wide bandwidth architecture

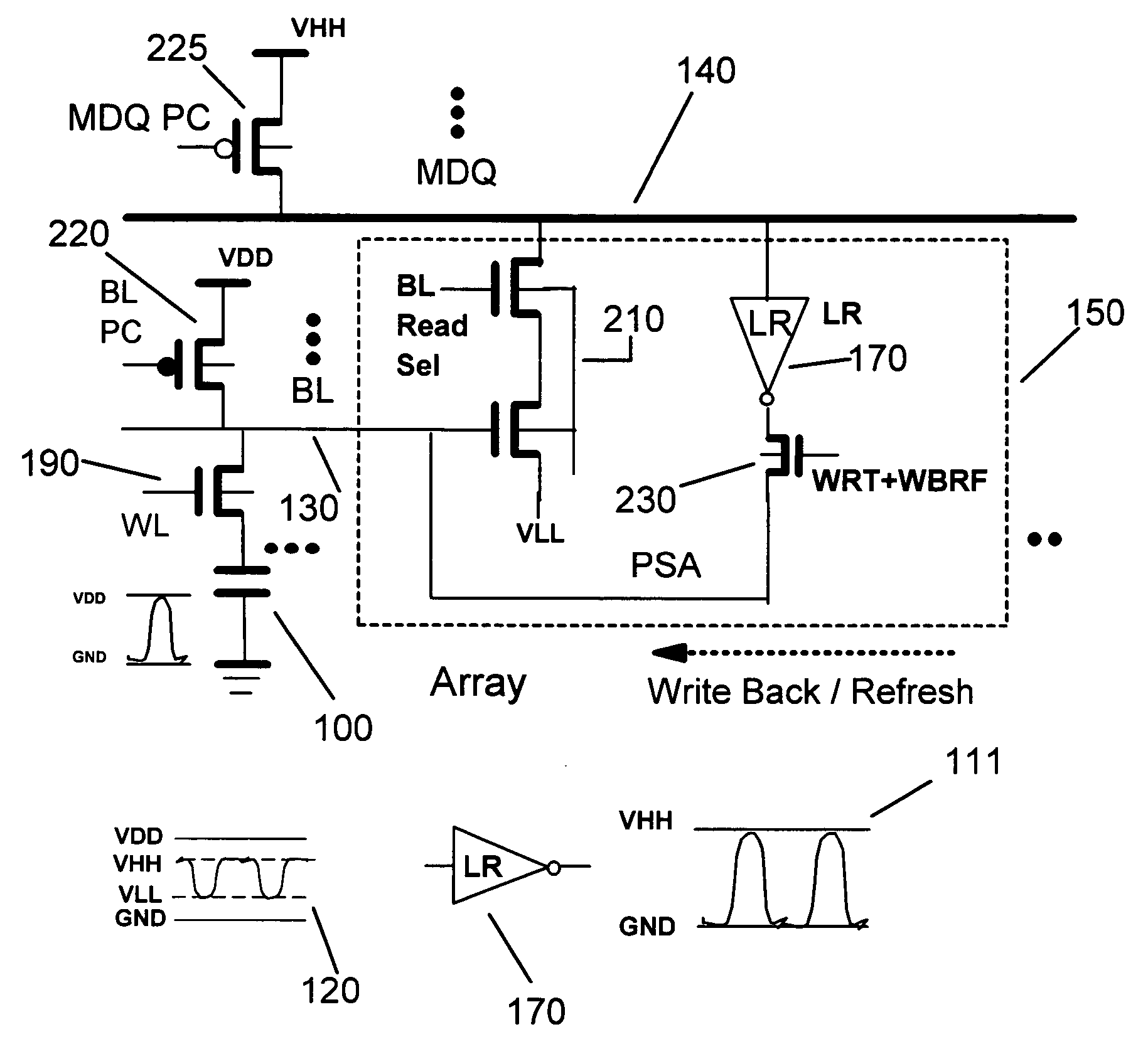

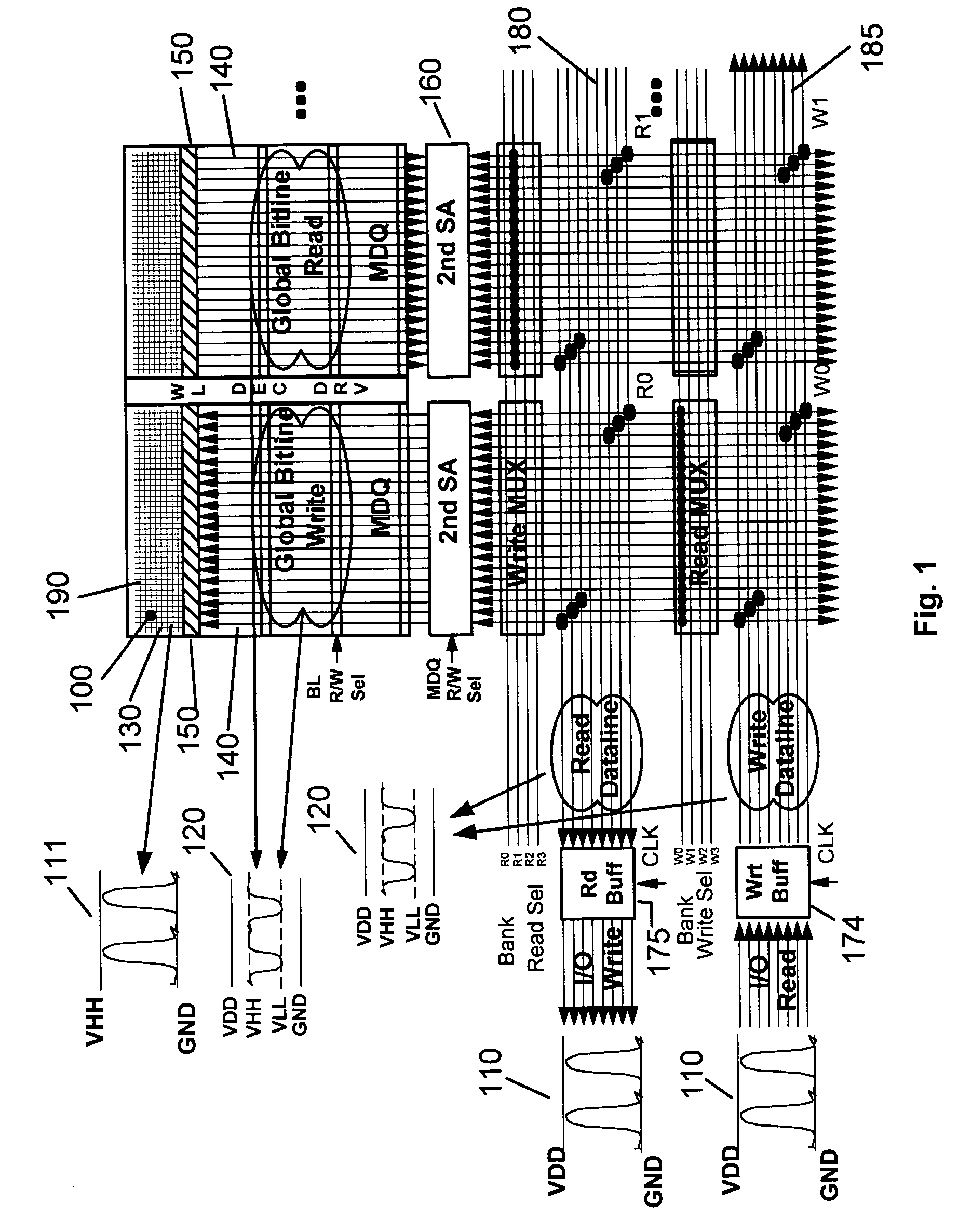

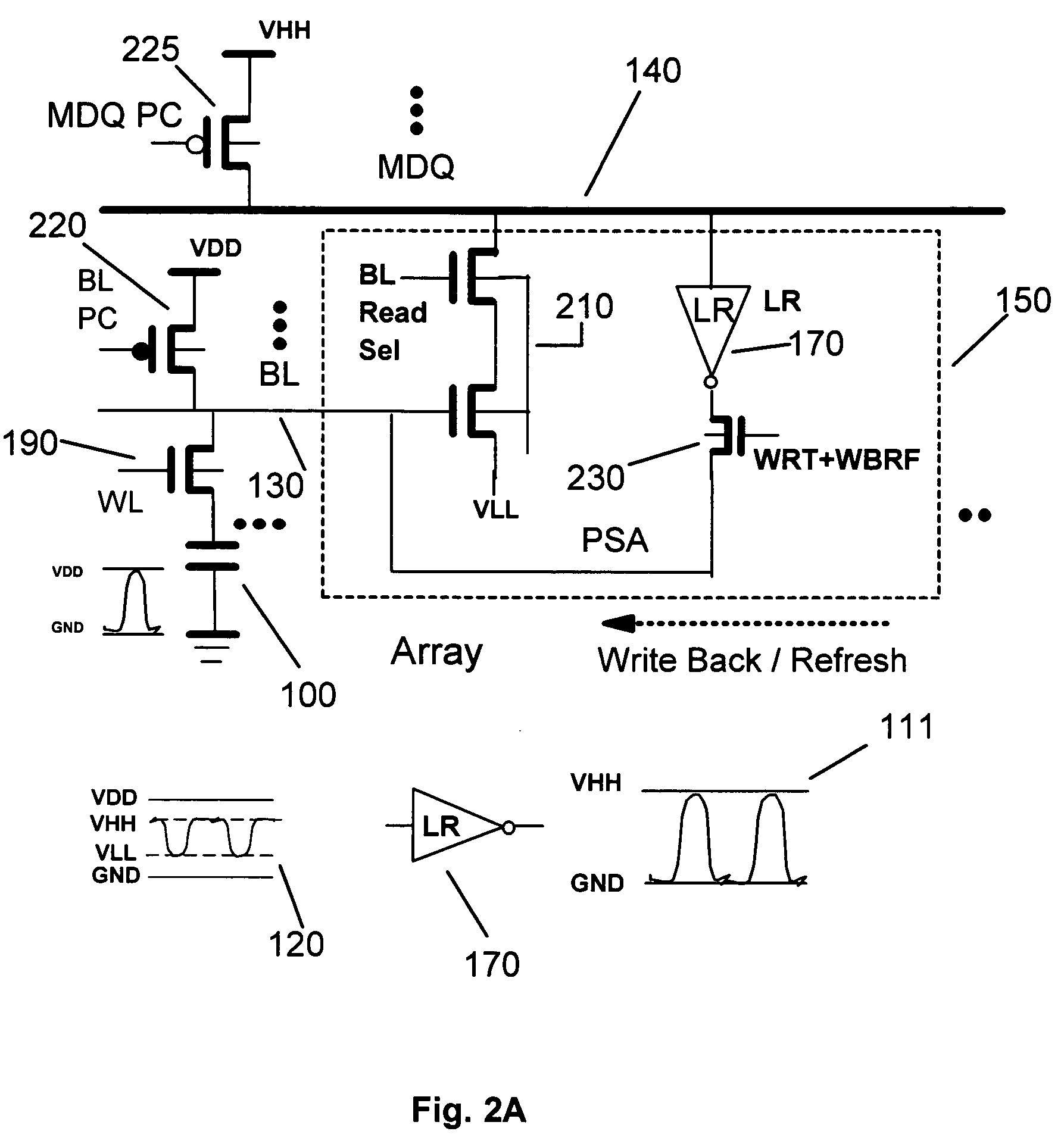

ActiveUS6999370B2Small swing operationClean signal marginsDigital storageHemt circuitsRegenerative circuit

An integrated circuit, such as a memory macro, includes multiple power rails supporting first and second voltage differentials, with the second voltage differential being smaller than the first voltage differential. Signal lines in the integrated circuit are driven with the small voltage swing, which is generated by small swing circuits. The integrated circuit further includes regeneration circuits, which are receiving small voltage swing inputs and are outputting first, or full voltage swings. The application of the small voltage swing to the signal lines saves power in the integrated circuit. A wide bandwidth, full-wordline I / O, memory integrated circuit has simultaneously operable connection paths between essentially all the memory cells that are attached to the same wordline and the corresponding I / O terminals, and it has a single ended data-line structure.

Owner:TAHOE RES LTD

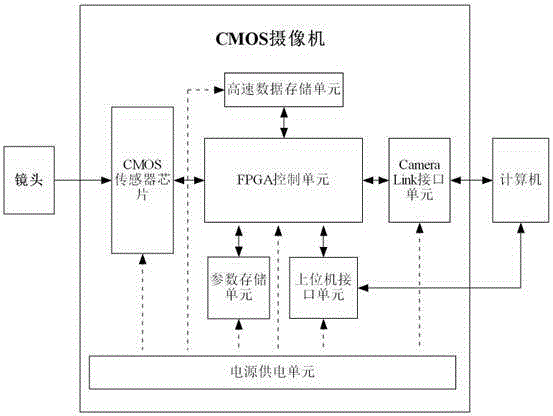

High-speed high-definition CMOS imaging system

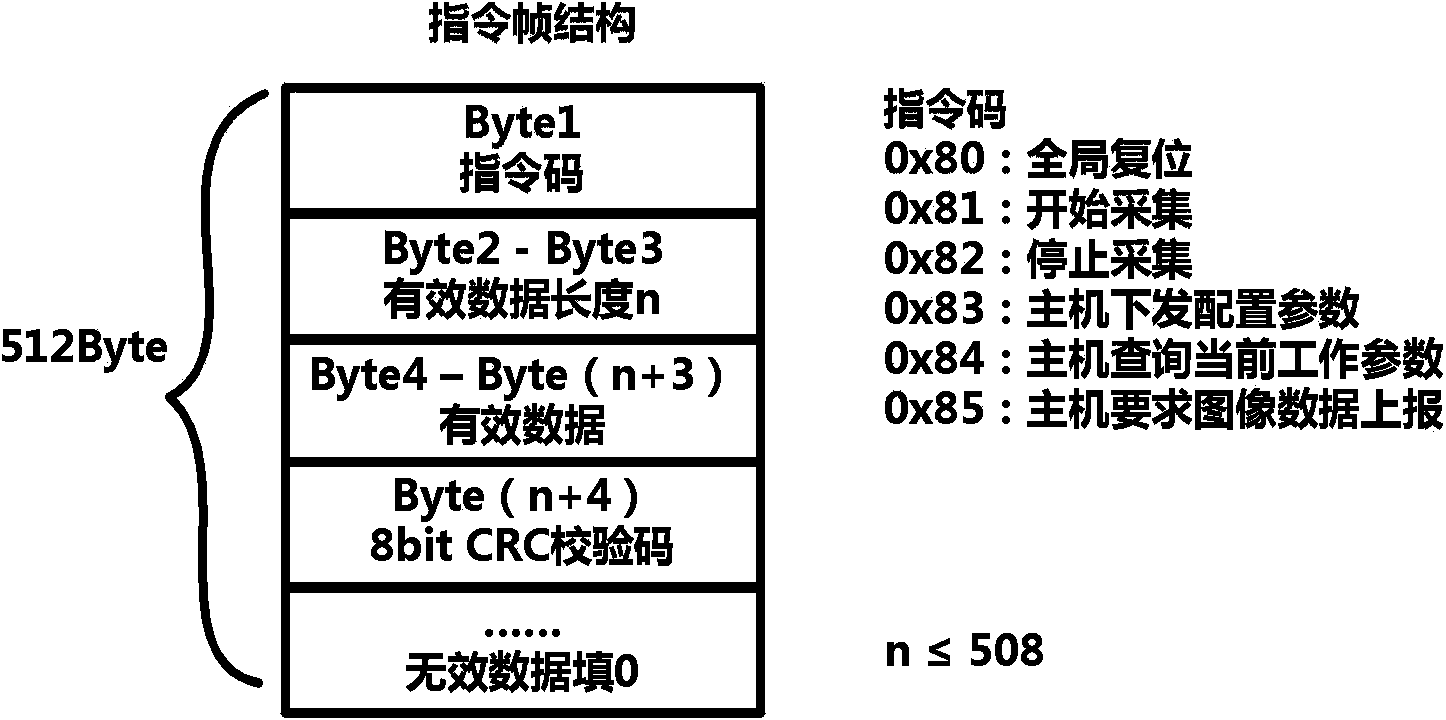

PendingCN106791288AIncrease storage capacityIncrease data bandwidthTelevision system detailsColor television detailsCMOS sensorImaging quality

The invention discloses a high-speed high-definition CMOS imaging system. The system comprises a lens, a CMOS camera and a computer. The CMOS camera comprises a power supply unit, a CMOS sensor chip, a FPGA control unit, a high speed data memory cell, a CameraLink interface unit, a parameter memory cell and an upper computer interface unit. Through using a high-speed high-definition CMOS chip, a 1280*1024 resolution of the CMOS camera is realized; through using a DDR3 high speed image memory cell, high speed image data is stored in real time, a storage capacity is increased, a data transmission bandwidth is increased too, and during the 1280*1024 resolution, a work speed whose frame frequency is 1000 frame / second is realized; through using a DC-DC power supply and a LDO power supply to provide power, a system noise is small, power consumption is low and imaging quality is good; and through using a CameraLink interface to transmit image data, real-time image display below 400 frame / second (the resolution is 1280*1024) can be realized, and a high-speed high-definition shooting requirement is satisfied. Besides, the system can configure parameters of a work mode and the like of a CMOS detector through an upper computer, and usage is simple and convenient.

Owner:NANJING UNIV OF SCI & TECH

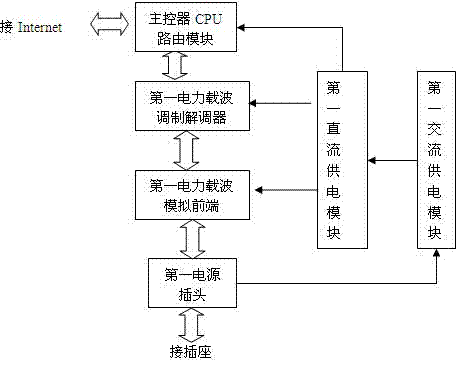

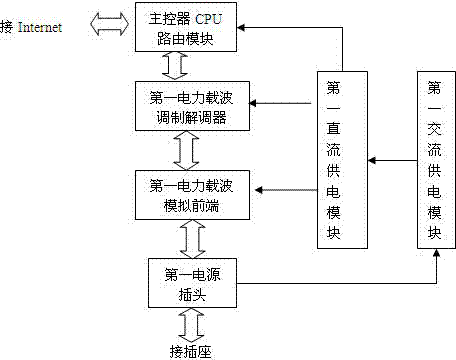

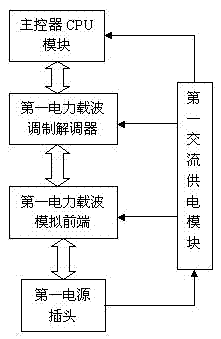

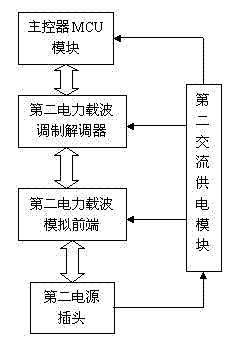

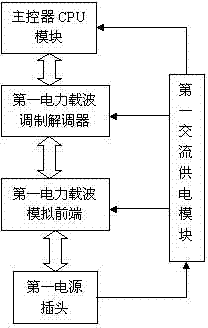

Routing communication device based on power line carrier

ActiveCN102195879AImprove transmission reliabilityActive connectionPower distribution line transmissionData switching networksNetwork packetCarrier signal

The invention relates to a routing communication device based on a power line carrier. The routing communication device is connected with superior routing equipment or a server and is characterized by comprising a communication head end and user sides, wherein the communication head end communicates with a power line through a first PHY (Physical Layer) interface and communicates with external Internet through a second PHY interface; the user sides perform Ethernet communication with the communication head end through the power line; and the communication head end is used for receiving data packet information of a plurality of user sides and transmitting the data packet information to the superior routing equipment or the server according to a routing list. The entire network has the characteristics of large data bandwidth and high transmission reliability of the conventional Ethernet; more importantly, networking is convenient; and the user sides have plug and play functions.

Owner:ZHEJIANG NEW ZAILING TECH CO LTD

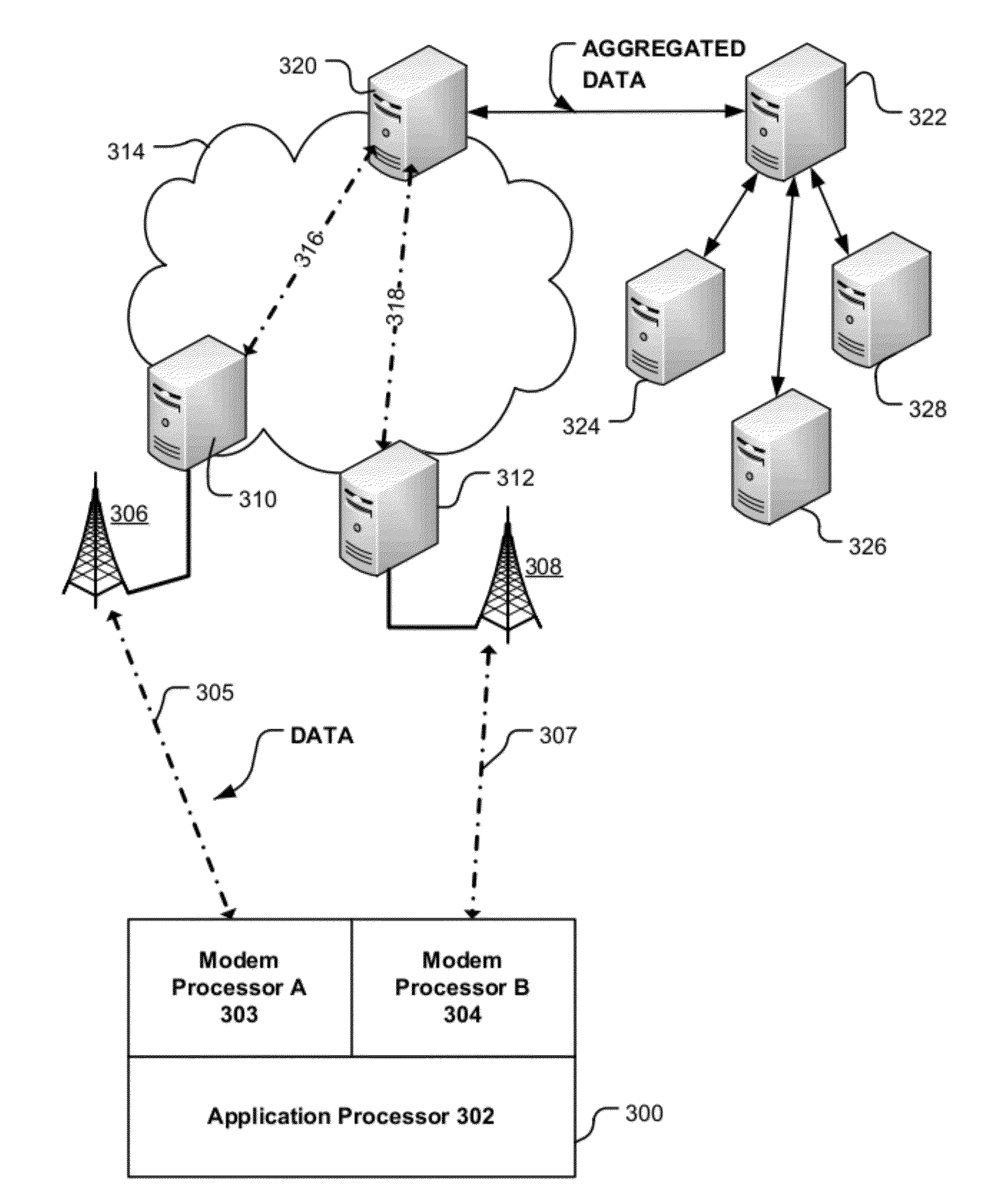

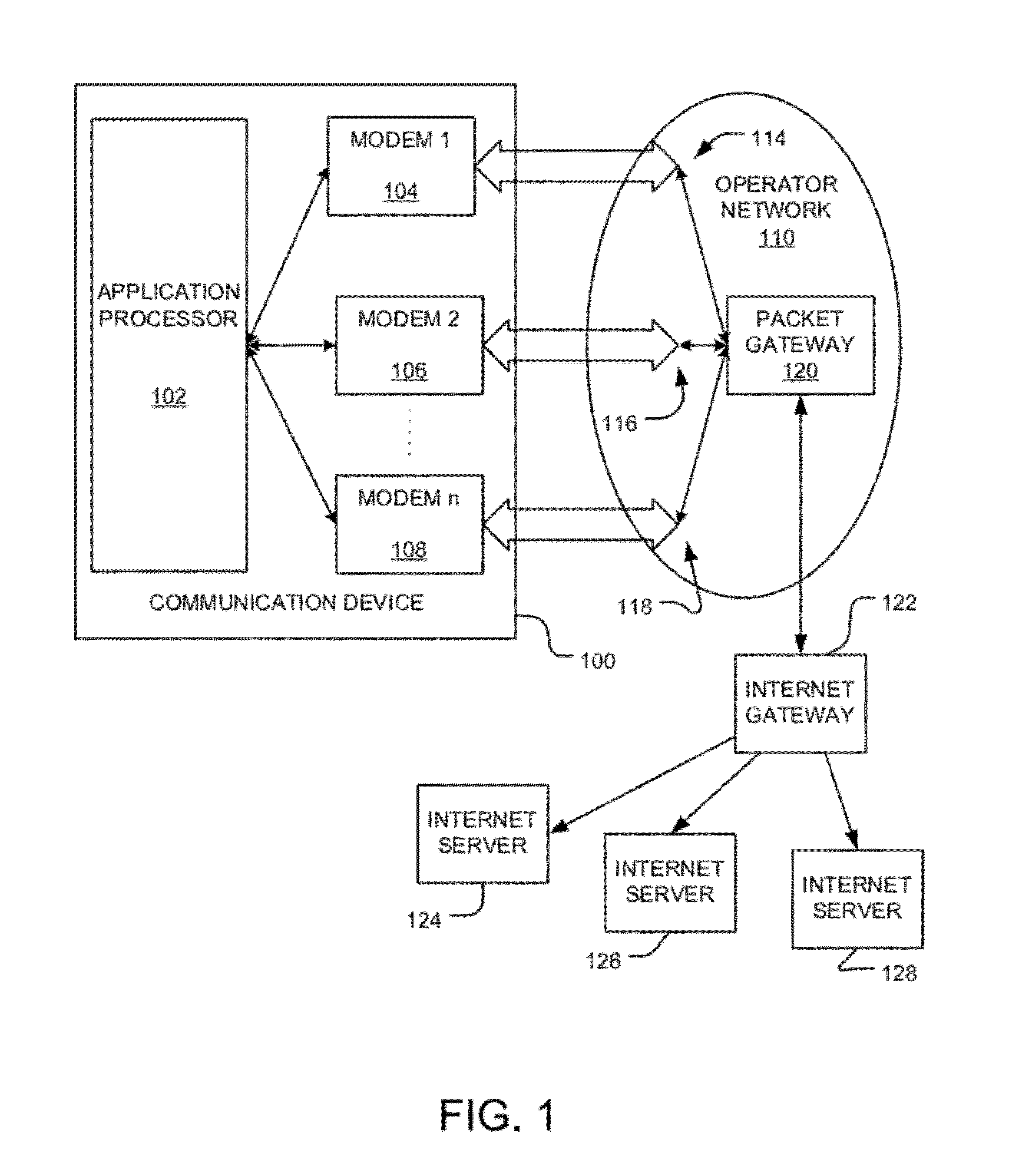

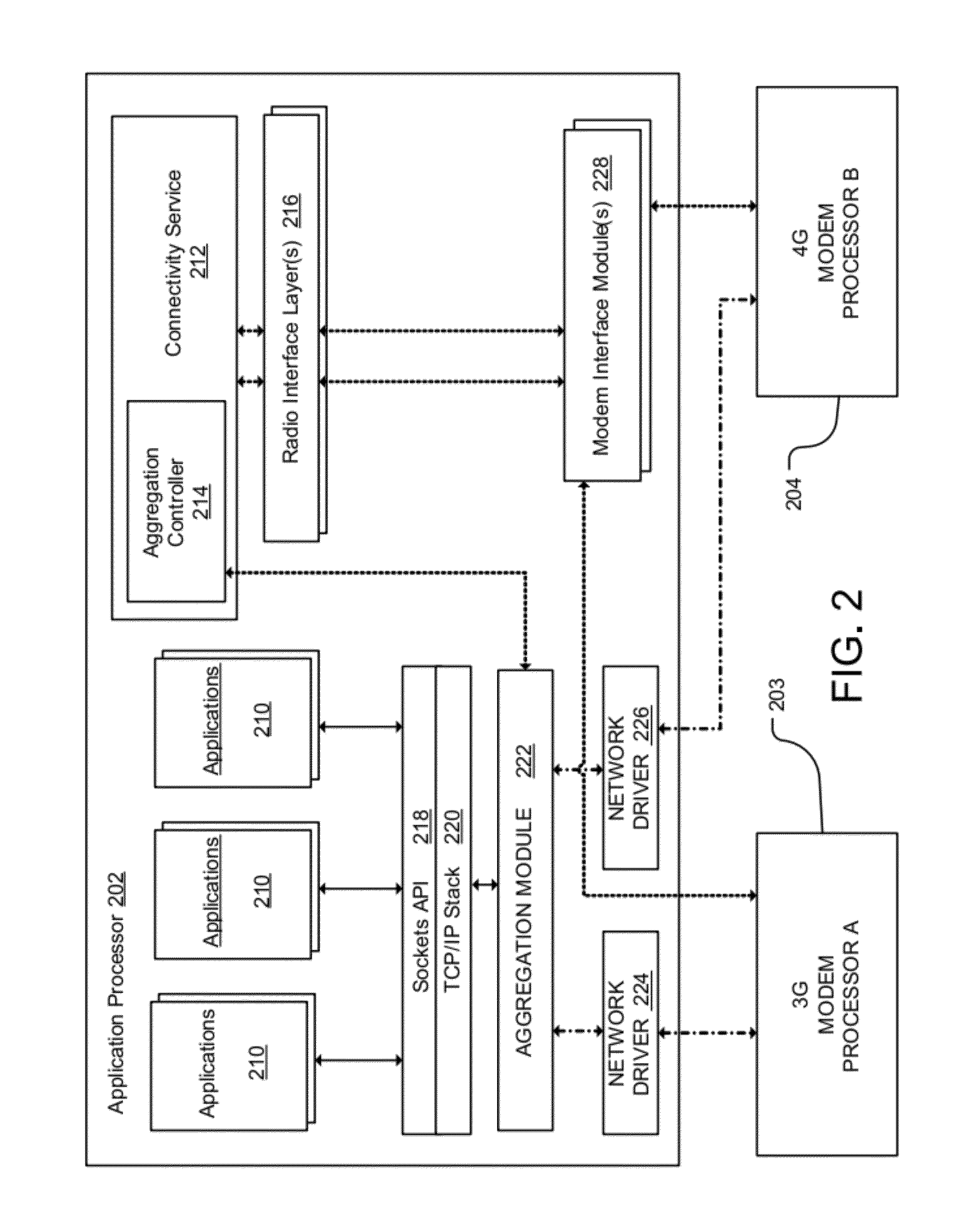

Aggregating multiple radio links from multiple modems in a communication device

InactiveUS8514701B2Increase data bandwidthImprove data transfer rateError preventionFrequency-division multiplex detailsModem deviceLink aggregation

Aggregating multiple modems in a communication device into a radio-frequency-link aggregation group increases the limited data bandwidth of RF data transmission between a communication device and its operator network. An aggregation controller in the communication device monitors the availability of its modems and selects modems to be used in a radio-frequency-link aggregation group. The aggregation controller also selects an aggregation algorithm. A radio-frequency-link aggregation module in the communication device distributes data to modems in the radio-frequency-link aggregation group in accordance with the aggregation algorithm. A connectivity service in the communication device notifies the operator network of the modems in the radio-frequency-link aggregation group and acknowledges that the operator network agrees to handle transmission from the radio-frequency-link aggregation group.

Owner:QUALCOMM INNOVATION CENT

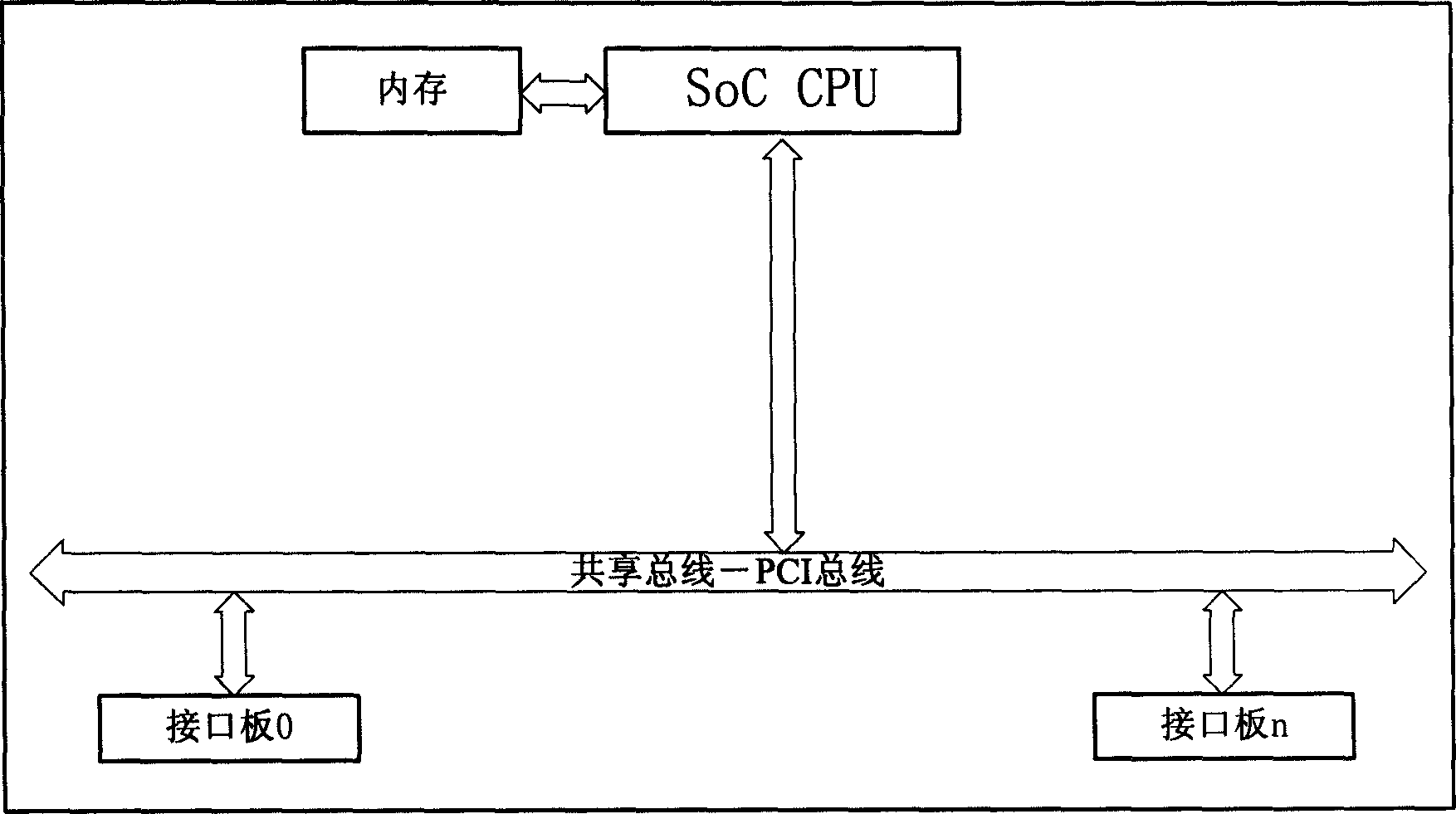

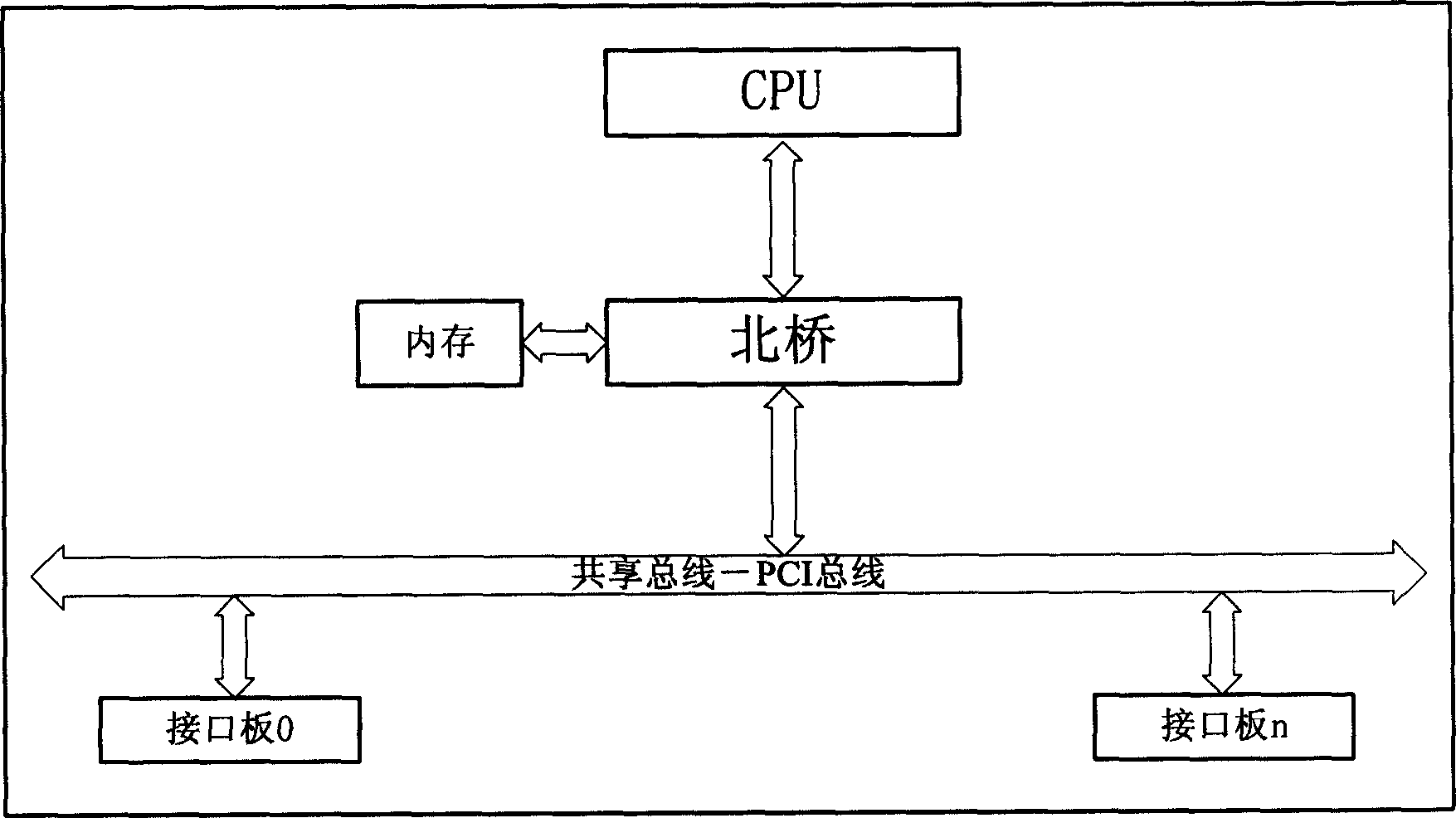

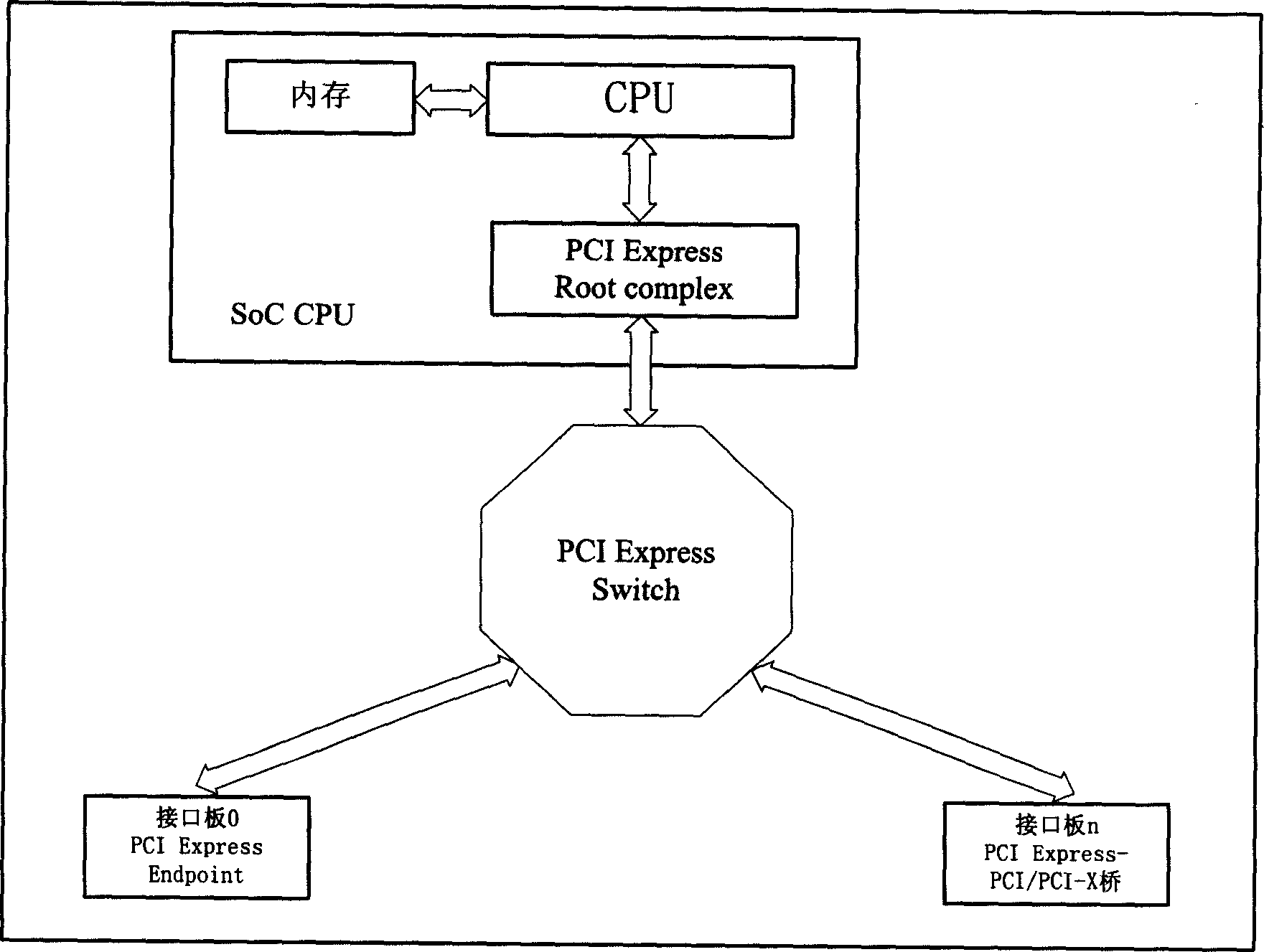

Integrated router based on PCI Express bus

ActiveCN1747453AIncrease data bandwidthMeet the rapid developmentData switching networksData transmissionPCI Express

A centralized router based on PCI Express bus as its internal bus for wide bandwidth features that such units in the router as root multiplexer, PCI Express switch and interfaces are connected via PCI Express bus for data transmission.

Owner:NEW H3C TECH CO LTD

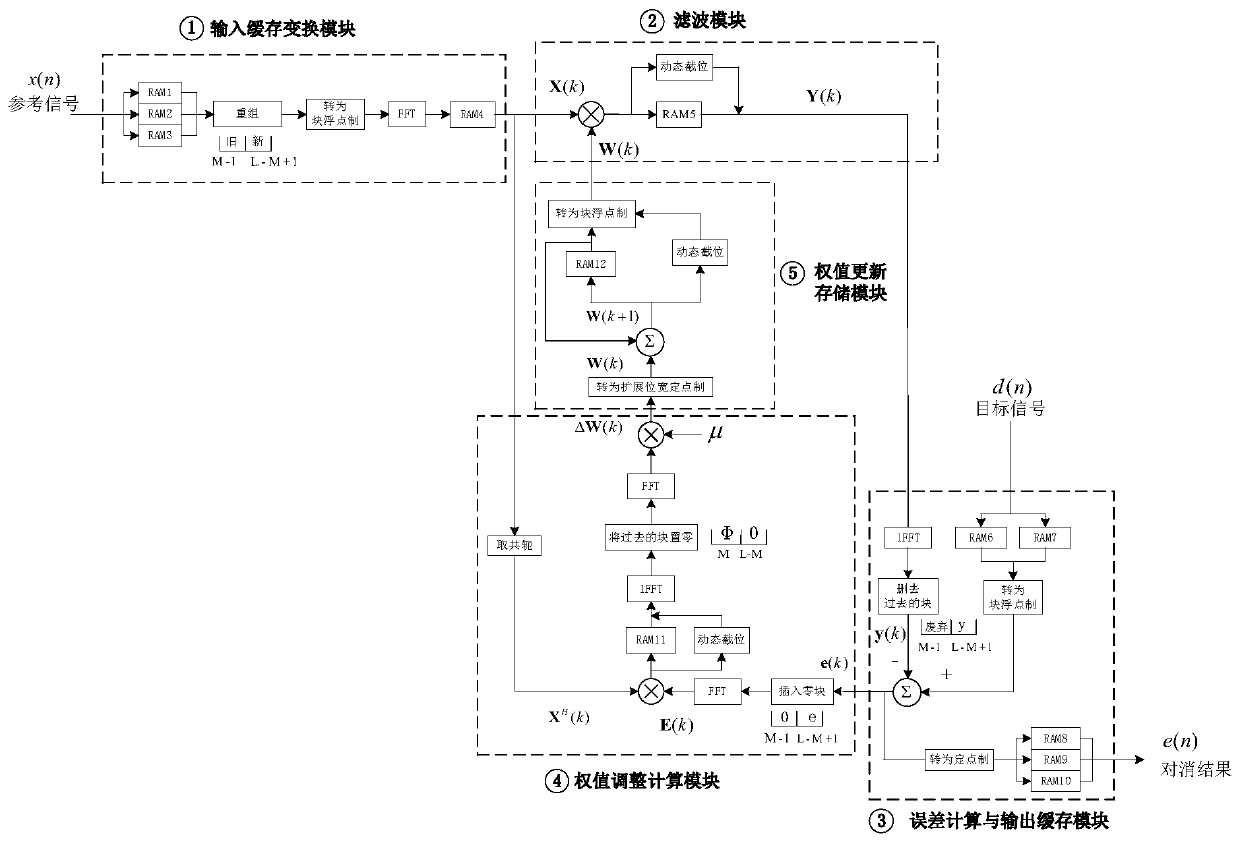

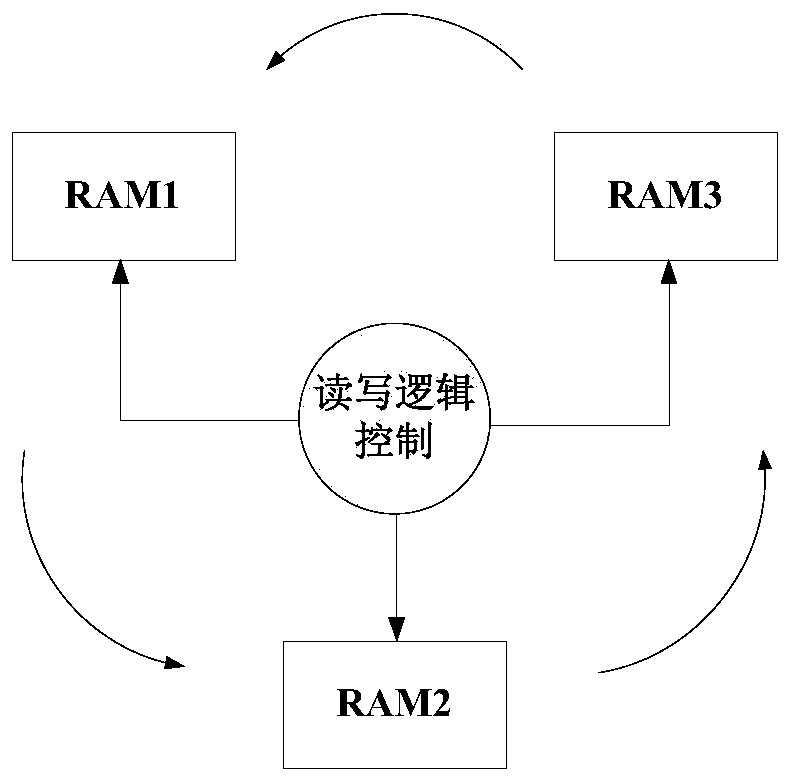

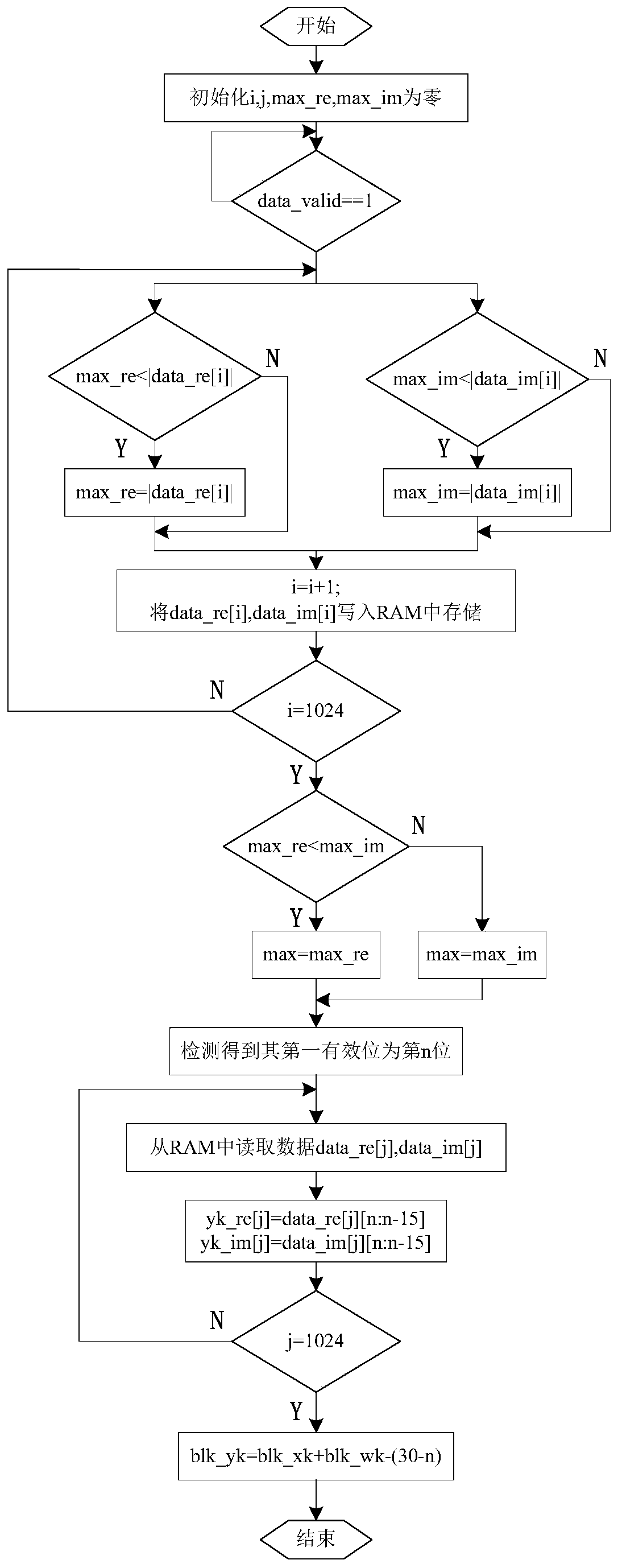

FPGA implementation device and method based on FBLMS algorithm of block floating points

ActiveCN111506294AGuaranteed accuracyHigh precisionDigital data processing detailsCAD circuit designModularityBlock floating-point

The invention belongs to the technical field of real-time adaptive signal processing, particularly relates to an FPGA implementation device and method of an FBLMS algorithm based on a block floating point, and aims to solve the problem that conflicts exist among performance, speed and resources when an existing FPGA device implements the FBLMS algorithm. The method comprises the following steps that an input cache transformation module performs block cache recombination on a reference signal, converts the reference signal into block floating points and then performs FFT transformation; a filtering module carries out filtering in a frequency domain and carries out dynamic bit cutting; an error calculation and output caching module performs block caching on the target signal, subtracts the filtered output after the target signal is converted into a block floating point, and converts the result into a fixed-point system to obtain a final cancellation result; and a weight adjustment calculation module and a weight update storage module obtain the adjustment amount of the weight and update the weight block by block. Aiming at a recursive structure of the FBLMS algorithm, a block floating point data format and a dynamic bit cutting method are adopted, so the data is ensured to have a large dynamic range and high precision, conflicts among performance, speed and resources are solved,and the reusability and expansibility are also improved through modular design.

Owner:INST OF AUTOMATION CHINESE ACAD OF SCI +1

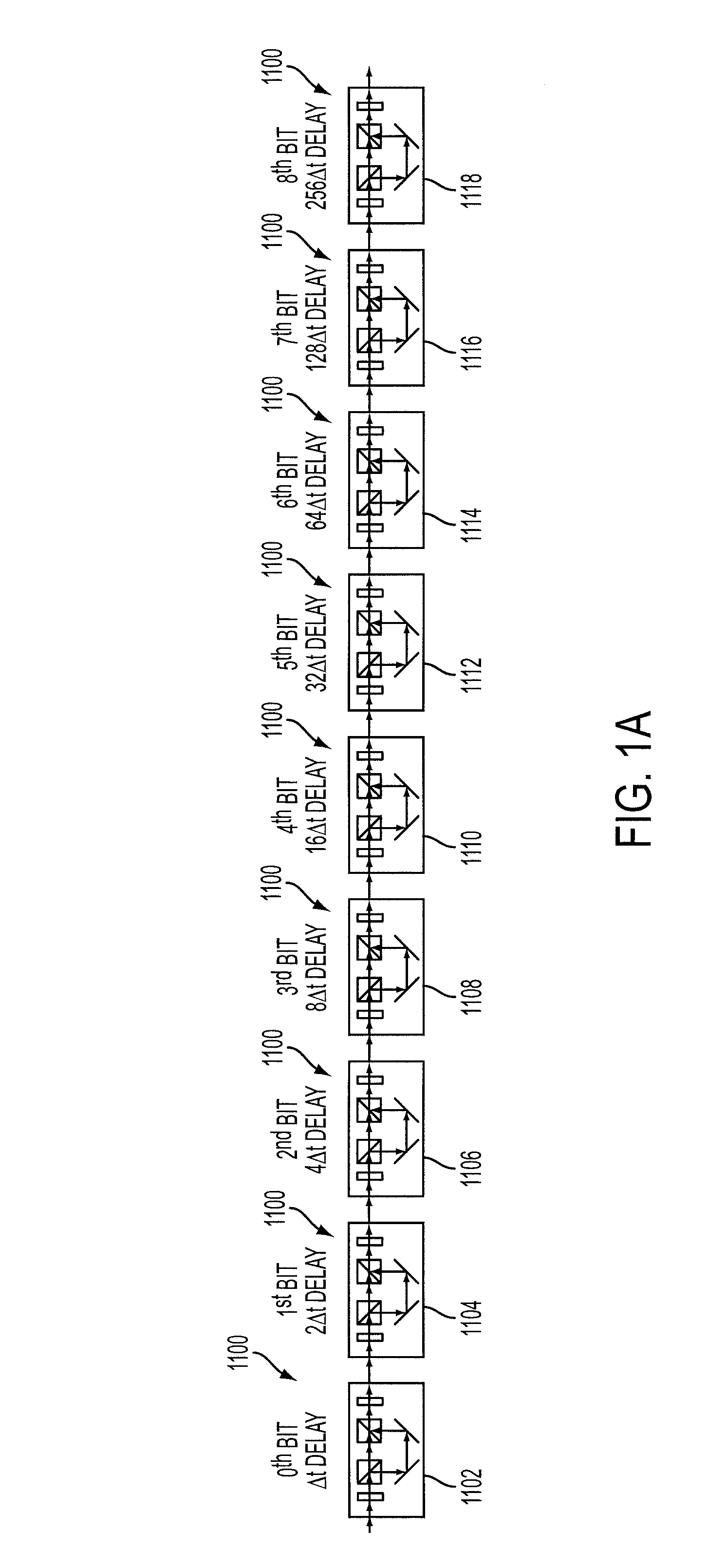

Low power circuits with small voltage swing transmission, voltage regeneration, and wide bandwidth architecture

ActiveUS20050030817A1Low powerIncrease data bandwidthDigital storageVoltage swingRegenerative circuit

An integrated circuit, such as a memory macro, includes multiple power rails supporting first and second voltage differentials, with the second voltage differential being smaller than the first voltage differential. Signal lines in the integrated circuit are driven with the small voltage swing, which is generated by small swing circuits. The integrated circuit further includes regeneration circuits, which are receiving small voltage swing inputs and are outputting first, or full voltage swings. The application of the small voltage swing to the signal lines saves power in the integrated circuit. A wide bandwidth, full-wordline I / O, memory integrated circuit has simultaneously operable connection paths between essentially all the memory cells that are attached to the same wordline and the corresponding I / O terminals, and it has a single ended data-line structure.

Owner:TAHOE RES LTD

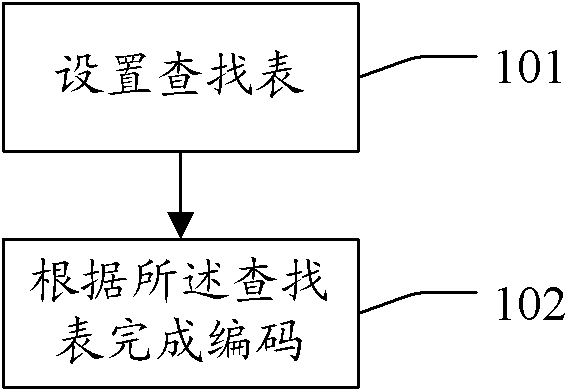

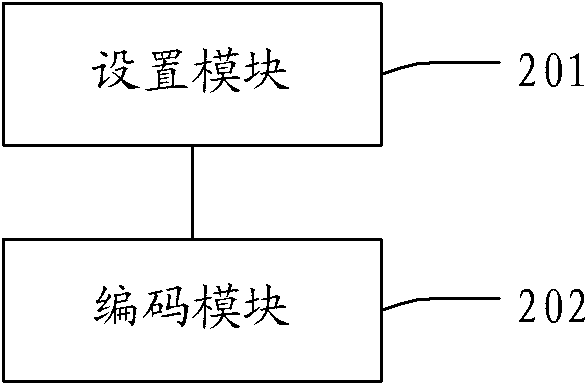

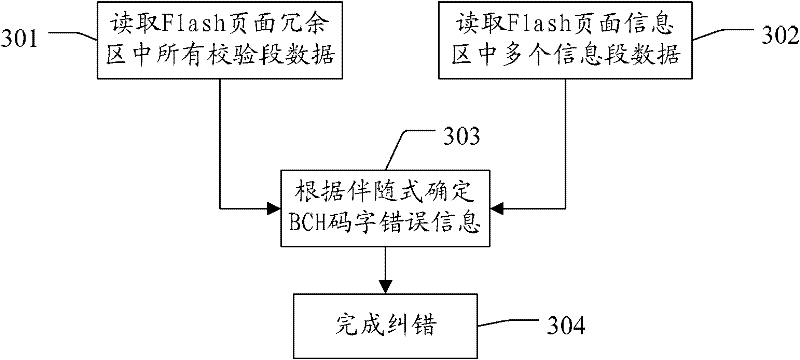

BCH (Broadcast Channel) encoding and decoding method and device

ActiveCN102545914AIncrease data bandwidthImprove data transfer efficiencyError preventionCyclic codesDecoding methodsBroadcast channels

The invention discloses a BCH (Broadcast Channel) encoding and decoding method and a device. The BCH encoding method comprises the following steps of: setting a lookup table; pre-storing all levels of coefficient of a residue polynomial in the lookup table; and combining the lookup table to obtain a state of an encoding state register at the next moment according to the state of the encoding state register at the present moment and 8-bit data to be encoded. Meanwhile, the embodiment of the invention also provides a BCH decoding method, comprising the following steps of: reading data of all verification sections of a page redundancy area in a flash memory and storing the data into a data cache; reading the data of a plurality of information sections of a page information area in the flash memory; determining the position of each error according to the corresponding accompany type of the data in each information section and storing the positions of the errors into the data cache; and finishing error correction by a data reading part of an on-chip system according to the error information in the data cache. The BCH encoding and decoding method and the device are suitable for the BCH encoding and decoding of the flash memory application facing to the on-chip system.

Owner:LEADCORE TECH

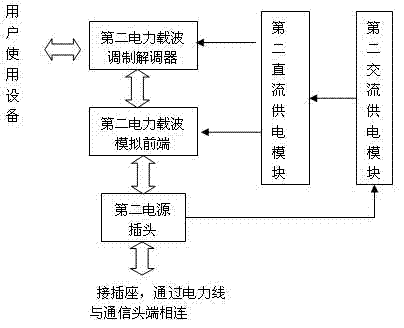

Communication device on basis of power line and GPRS (General Packet Radio Service)

ActiveCN102255635AHigh bandwidthStrong anti-interference abilityPower distribution line transmissionEthernet communicationPower grid

The invention relates to a communication device on the basis of a power line and a GPRS (General Packet Radio Service), which is characterized by comprising a communication head end, a communication terminal and a GPRS wireless terminal, wherein the communication head end is communicated with the GPRS wireless terminal through a first serial interface; and the communication head end carries out Ethernet communication with the communication terminal through the power line. The GPRS wireless terminal, the communication head end and the communication terminal are combined to form a complete remote wireless multipoint Ethernet transmission control platform. The communication device has the characteristics of large data bandwidth and high transmission reliability, so that the communication device is suitable for application to monitoring various power networks or industrial control and the like.

Owner:ZHEJIANG NEW ZAILING TECH CO LTD

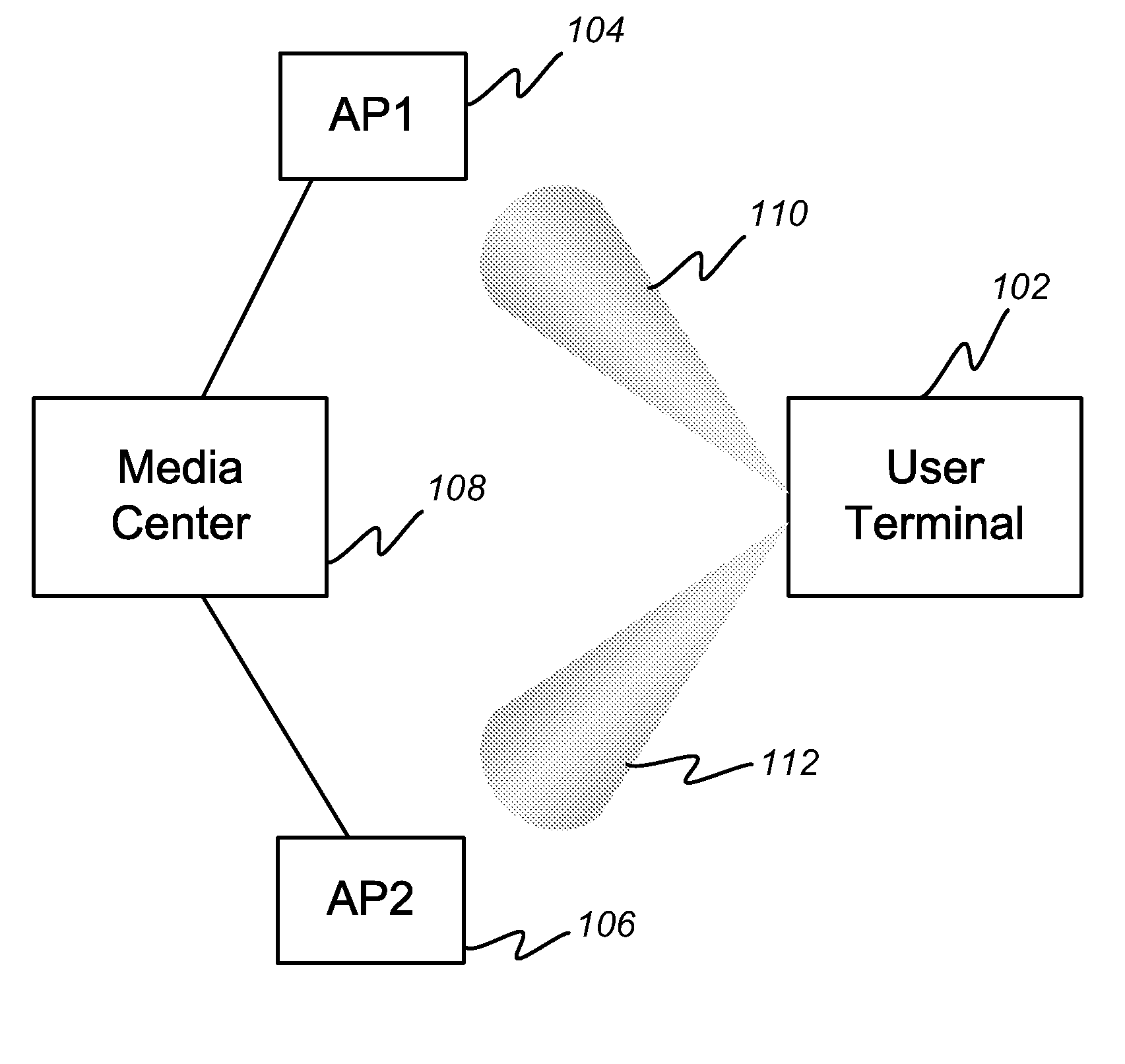

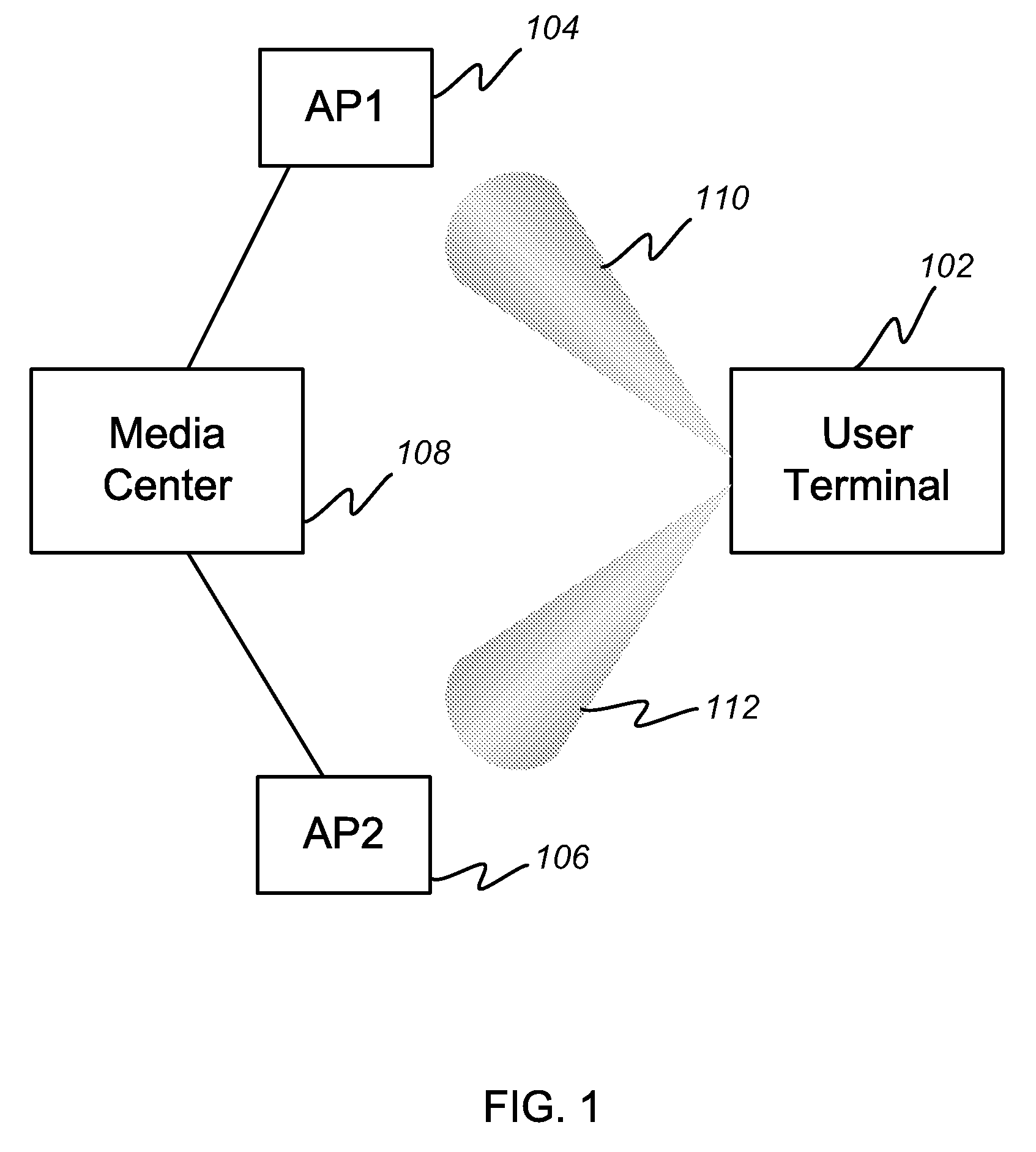

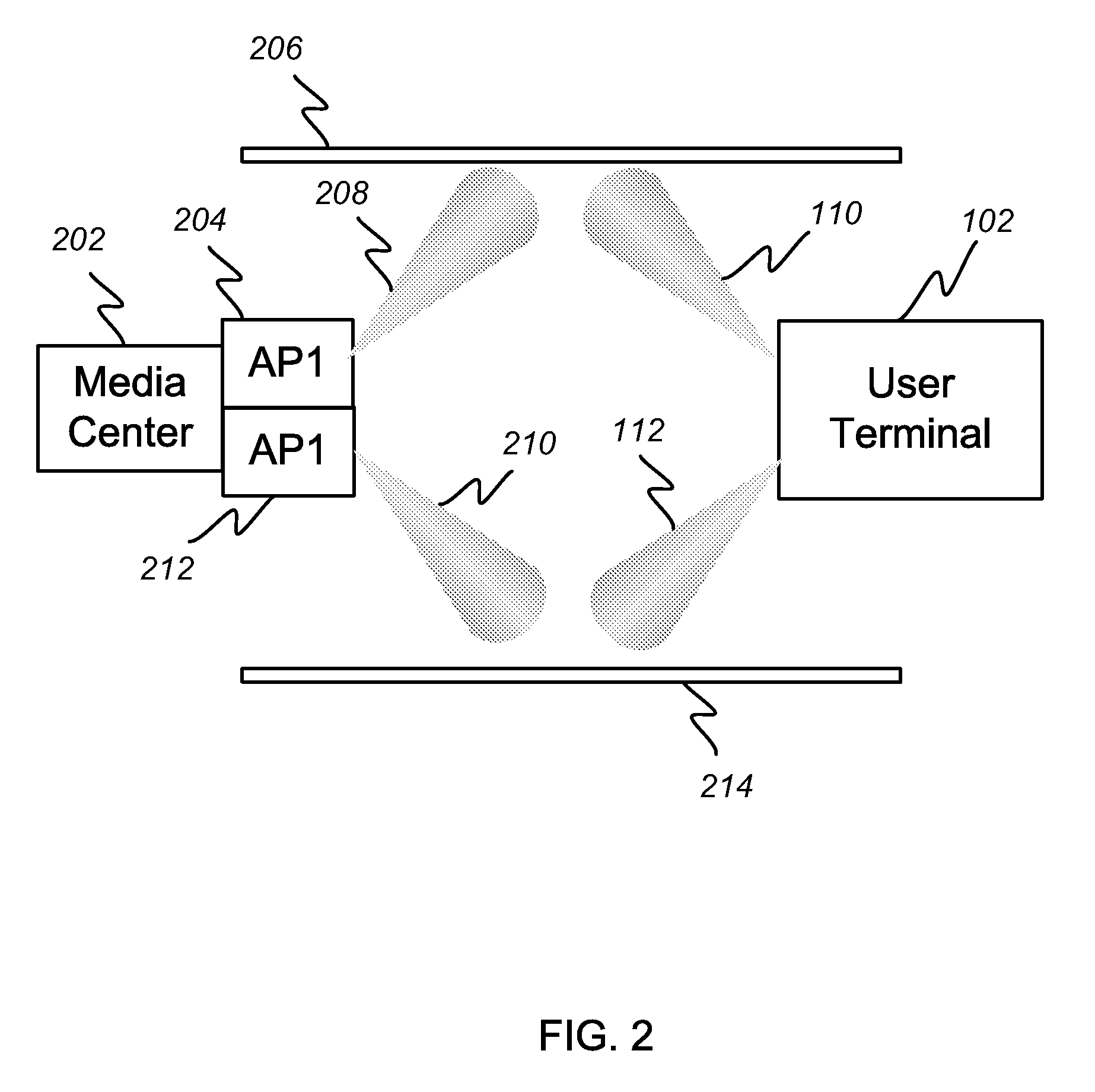

Method and apparatus for channel bonding using a multiple-beam antenna

ActiveUS8107569B2Enhances throughput and reliabilityIncrease data bandwidthPolarisation/directional diversityTransmission noise suppressionGeneral purposeTelecommunications

A system is provided that enhances the throughput and reliability of wireless communications by providing multi-beam user terminals that exhibit directional discrimination. Multiple wireless communication channels are matched with multiple beams created from an array antenna by a beam-forming processor. The multiple wireless communication channels are bonded into a single virtual channel, thereby increasing data bandwidth while reducing interference and multi-path effects that can degrade communications. The beam-forming function may be performed in a dedicated beam-forming processor or may reside within a general-purpose microprocessor located in the user terminal.

Owner:SPATIAL DIGITAL SYST

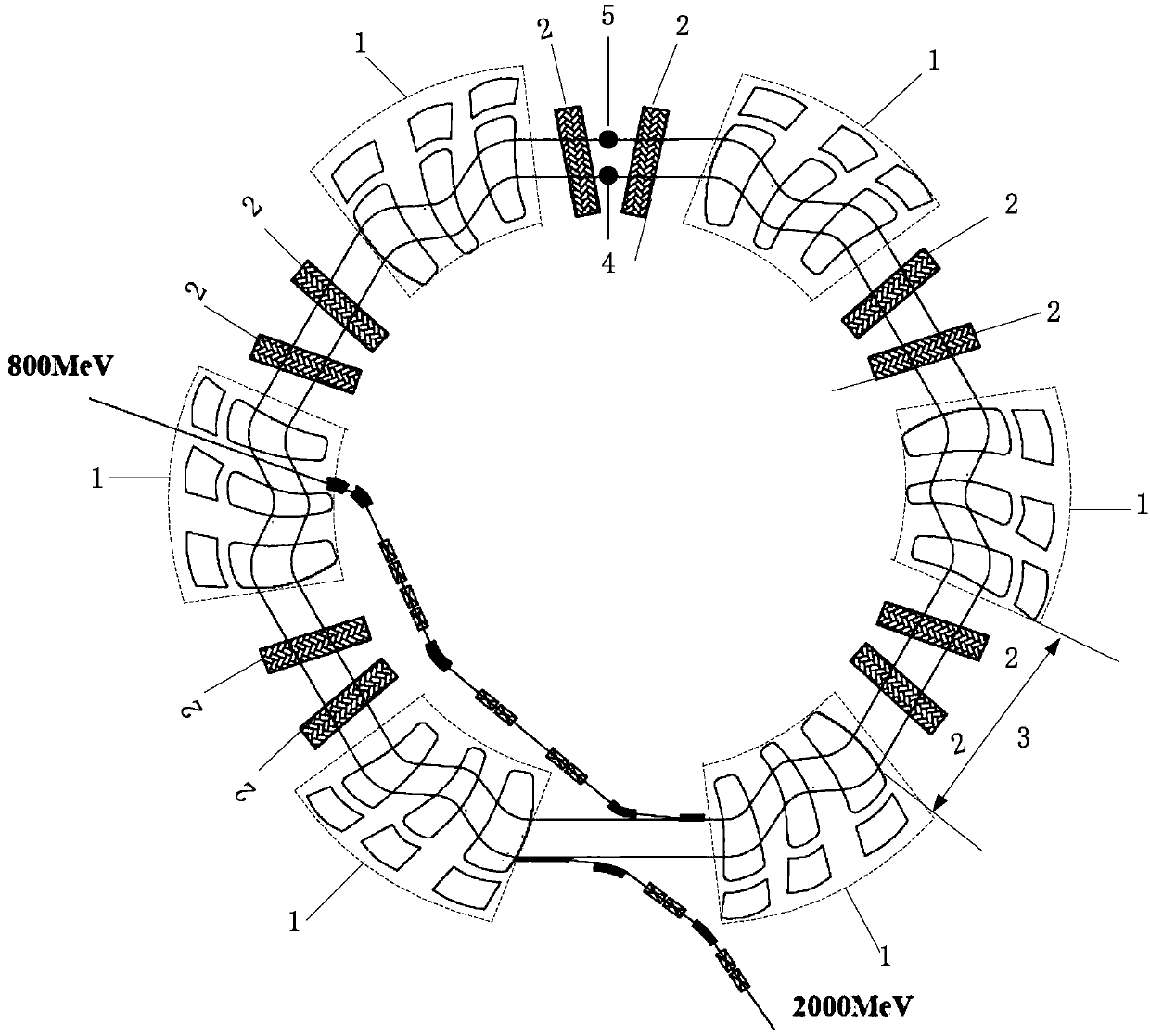

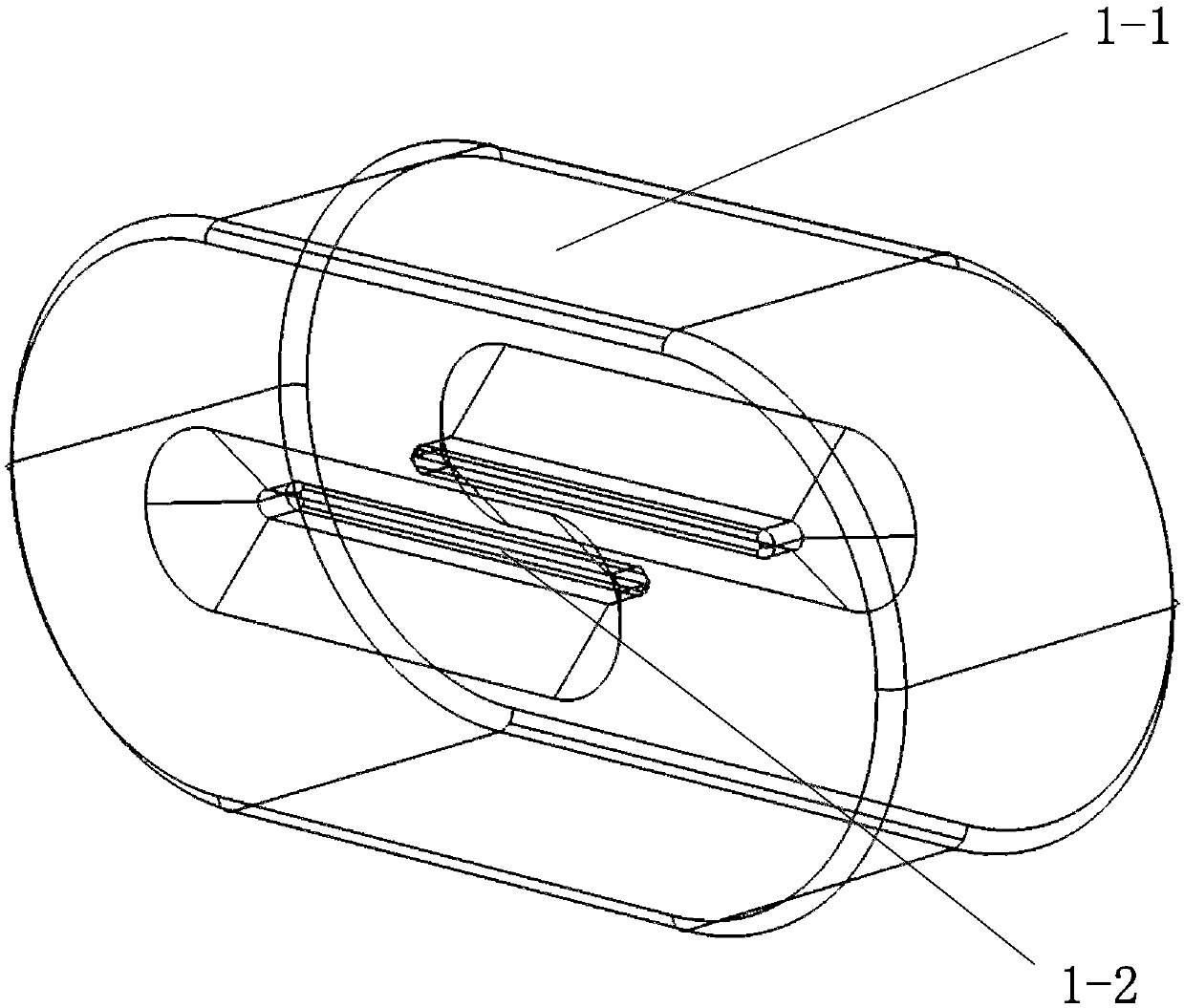

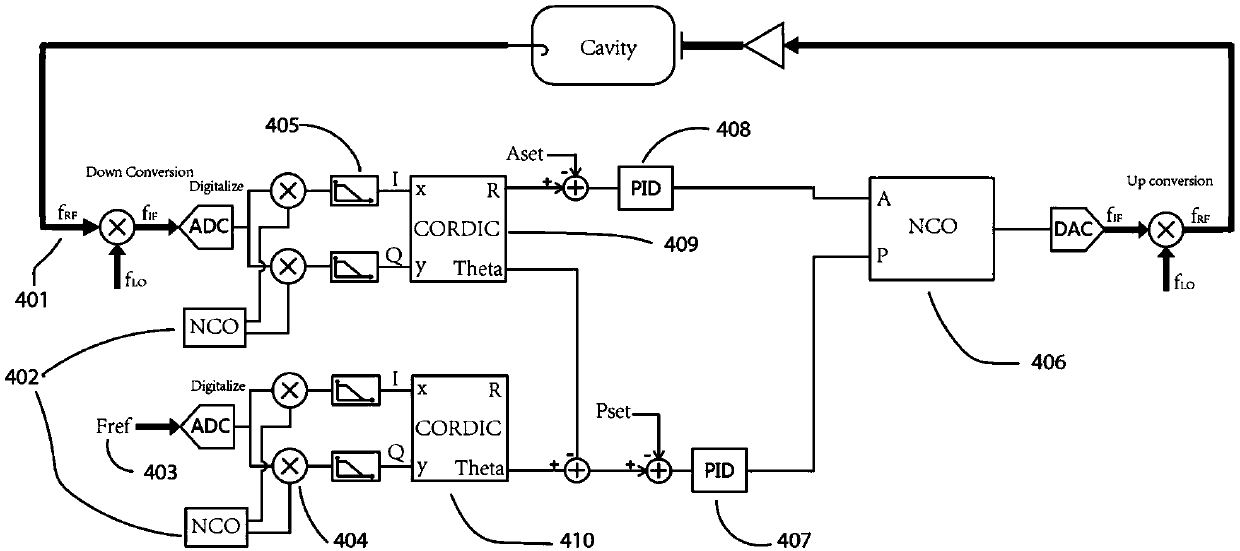

High-power high-stability variable-load high-frequency acceleration system

ActiveCN109561567ASolve the problem of low structural Q value and low accelerating voltageReduce processing difficultyMagnetic resonance acceleratorsAuto regulationHigh frequency power

The invention discloses a high-power high-stability variable-load high-frequency acceleration system. The high-power high-stability variable-load high-frequency acceleration system comprises a low-level high-frequency controller, a power amplification and transmission system and a high-frequency cavity; the power amplification and transmission system comprises a high-frequency machine, a transmission line and a coupling window; the low-level high-frequency controller is responsible for generating low-level high-frequency signals with appropriate values, and driving the high-frequency machine by the generated low-level high-frequency signals; the high-frequency machine is responsible for amplifying the low-power high-frequency signals into high-power high-frequency electromagnetic waves, and then transmitting the electromagnetic waves to the coupling window through the transmission line; the coupling window is used for coupling high-frequency power from the amplification system to the high-frequency cavity, and is characterized in that the coupling window is a dynamic adjustable coupling window; the high-frequency cavity is of a runway cavity structure; the invention further discloses an automatic adjustment coupling degree algorithm of the high-power high-stability variable-load high-frequency acceleration system, wherein the algorithm comprises the steps that a dynamic reflection power adjustment coupling degree algorithm is initialized; and the final calculation formula of the dynamic reflection power adjustment coupling degree is obtained.

Owner:CHINA INSTITUTE OF ATOMIC ENERGY

Flash memory card used for differential data transmission

InactiveCN102214315AIncrease data bandwidthReduce energy consumptionCo-operative working arrangementsRecord carriers used with machinesMemory bankDigital storage

A flash memory card used for differential data transmission comprises a differential data path which can be used for communication between the flash memory card and a host device, a differential signal is used for execution, the differential data path can be used for translation between differential signals and specific storage card signals so as to control reading / writing-in operations of a memory bank array of the flash memory card, the specific memory card signals can be signals of standard multimedia memory cards, safety digital memory cards, memory stick memory cards or compact flash memory cards and the like, the host device can contain a similar differential data path so as to provide the differential data transmission capability; and the differential data transmission is utilized instead of non-known clock data transmission, so that the integral data bandwidth between the flash memory card and the host device can be greatly increased, and the energy consumption and pin demands can be reduced.

Owner:SUPER TALENT ELECTRONICS