Patents

Literature

49 results about "Residue number system" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A residue numeral system (RNS) is a numeral system representing integers by their values modulo several pairwise coprime integers called the moduli. This representation is allowed by the Chinese remainder theorem, which asserts that, if N is the product of the moduli, there is, in an interval of length N, exactly one integer having any given set of modular values. The arithmetic of a residue numeral system is also called multi-modular arithmetic.

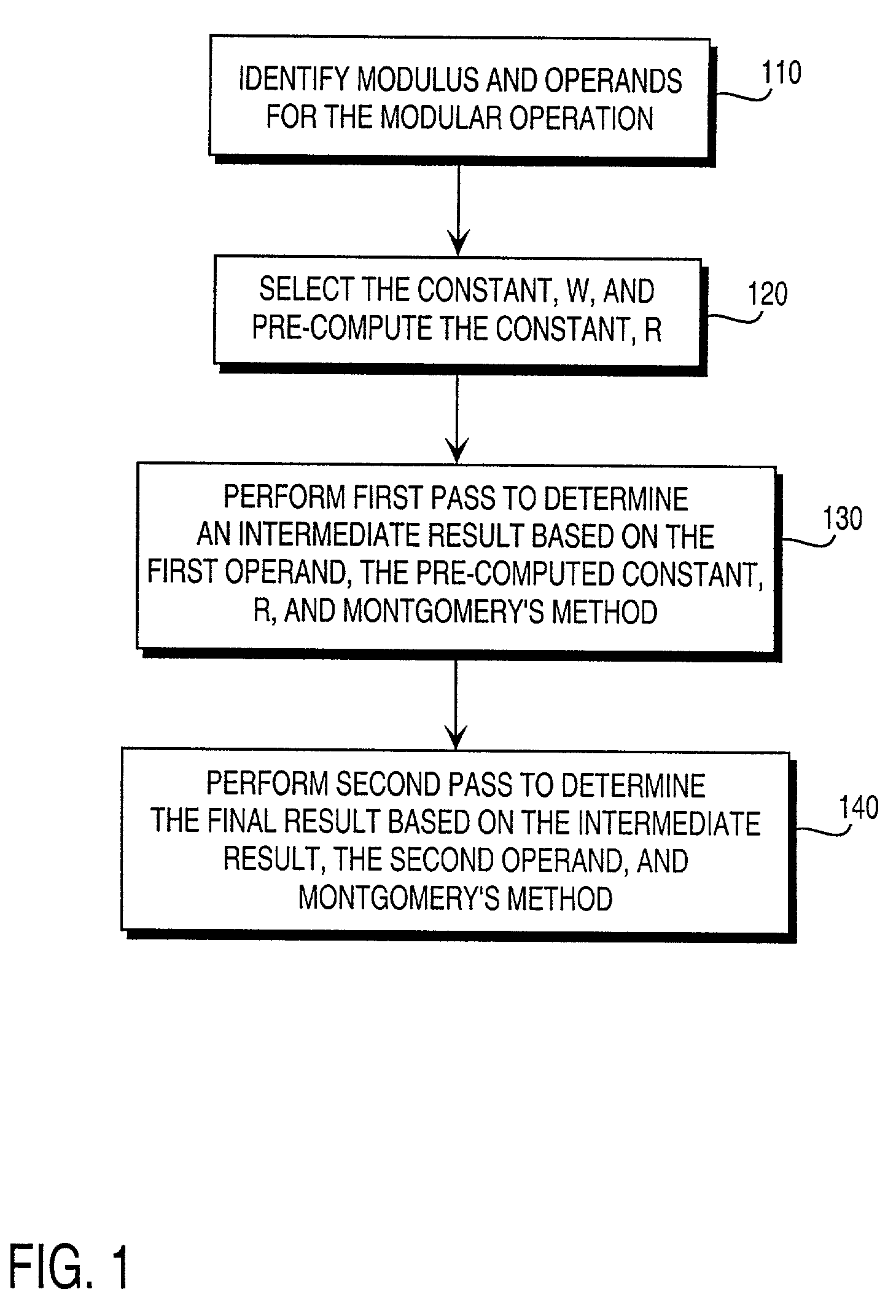

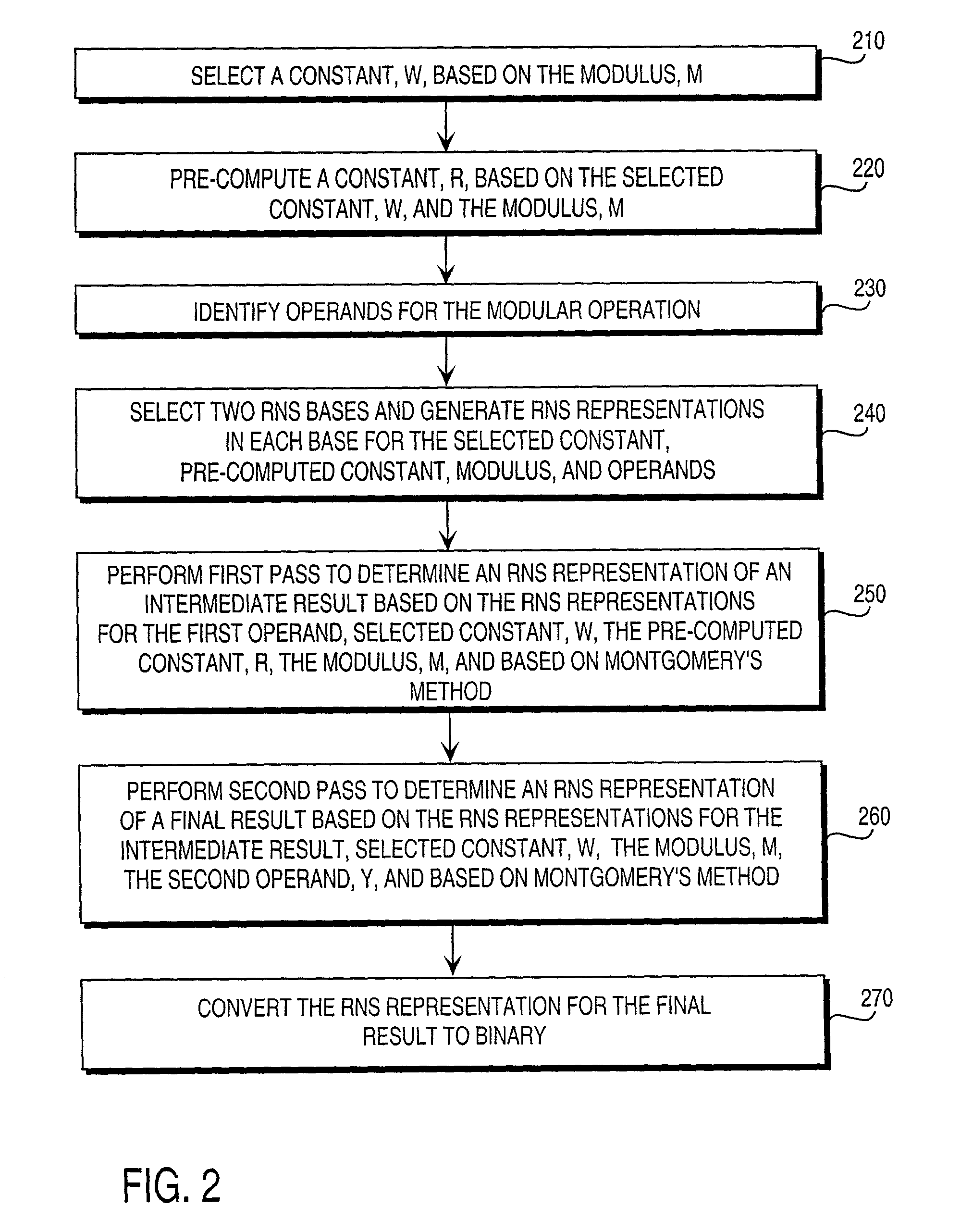

Residue number system based pre-computation and dual-pass arithmetic modular operation approach to implement encryption protocols efficiently in electronic integrated circuits

InactiveUS7027598B1Computations using contact-making devicesComputation using non-contact making devicesProcessor registerModularity

A pre-computation and dual-pass modular operation approach to implement encryption protocols efficiently in electronic integrated circuits is disclosed. An encrypted electronic message is received and another electronic message generated based on the encryption protocol. Two passes of Montgomery's method are used for a modular operation that is associated with the encryption protocol along with pre-computation of a constant based on a modulus. The modular operation may be a modular multiplication or a modular exponentiation. Modular arithmetic may be performed using the residue number system (RNS) and two RNS bases with conversions between the two RNS bases. A minimal number of register files are used for the computations along with an array of multiplier circuits and an array of modular reduction circuits. The approach described allows for high throughput for large encryption keys with a relatively small number of logical gates.

Owner:CISCO TECH INC

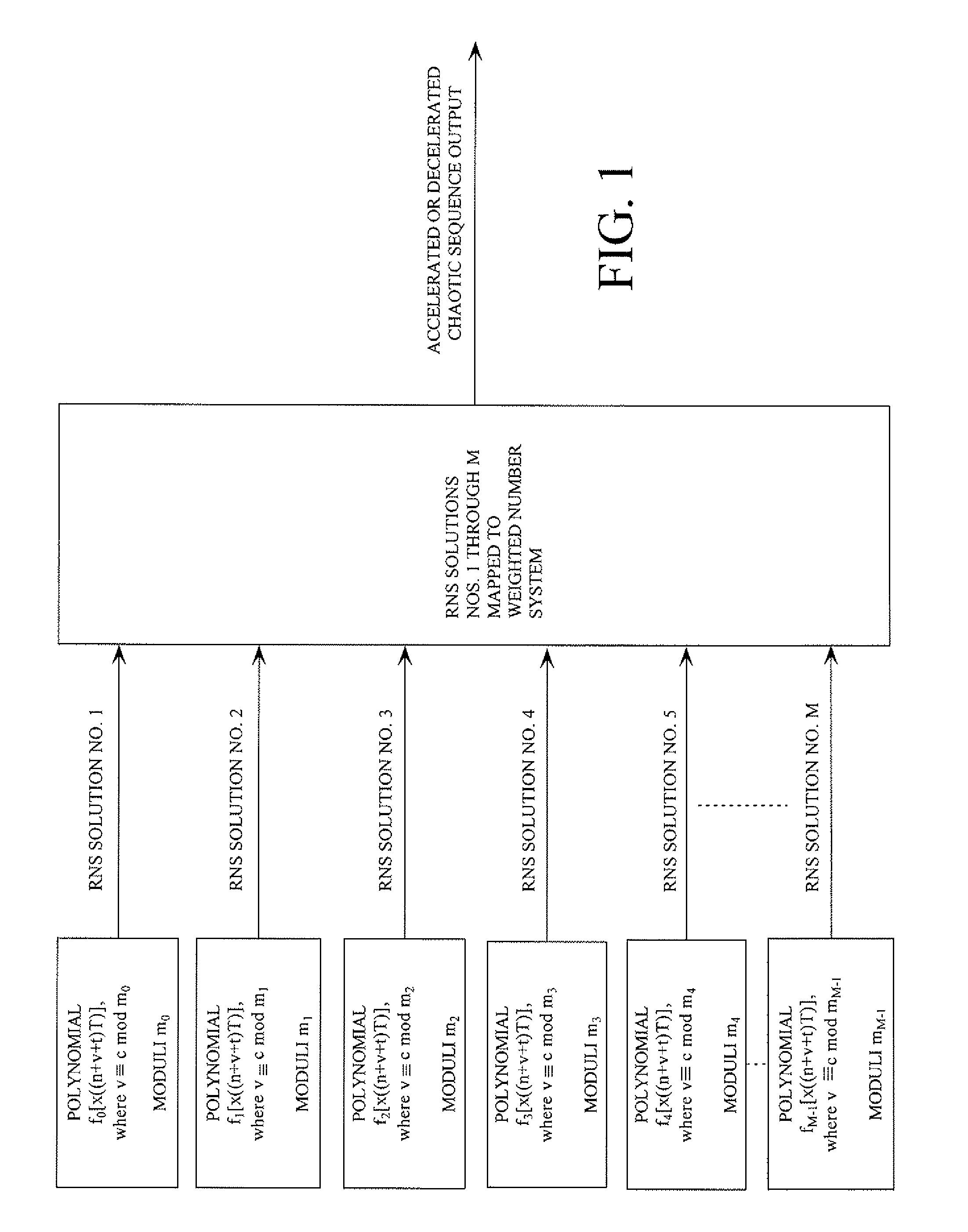

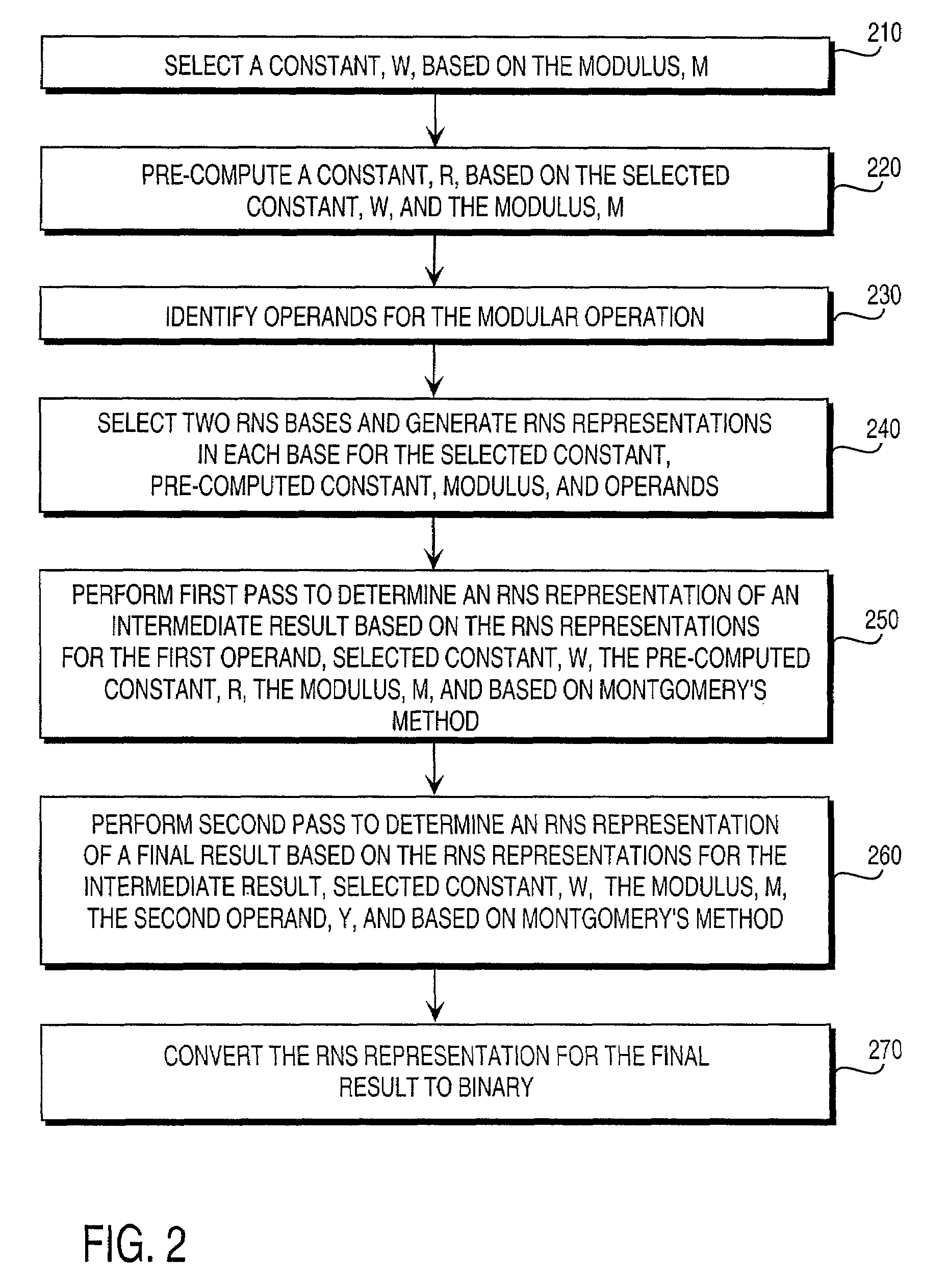

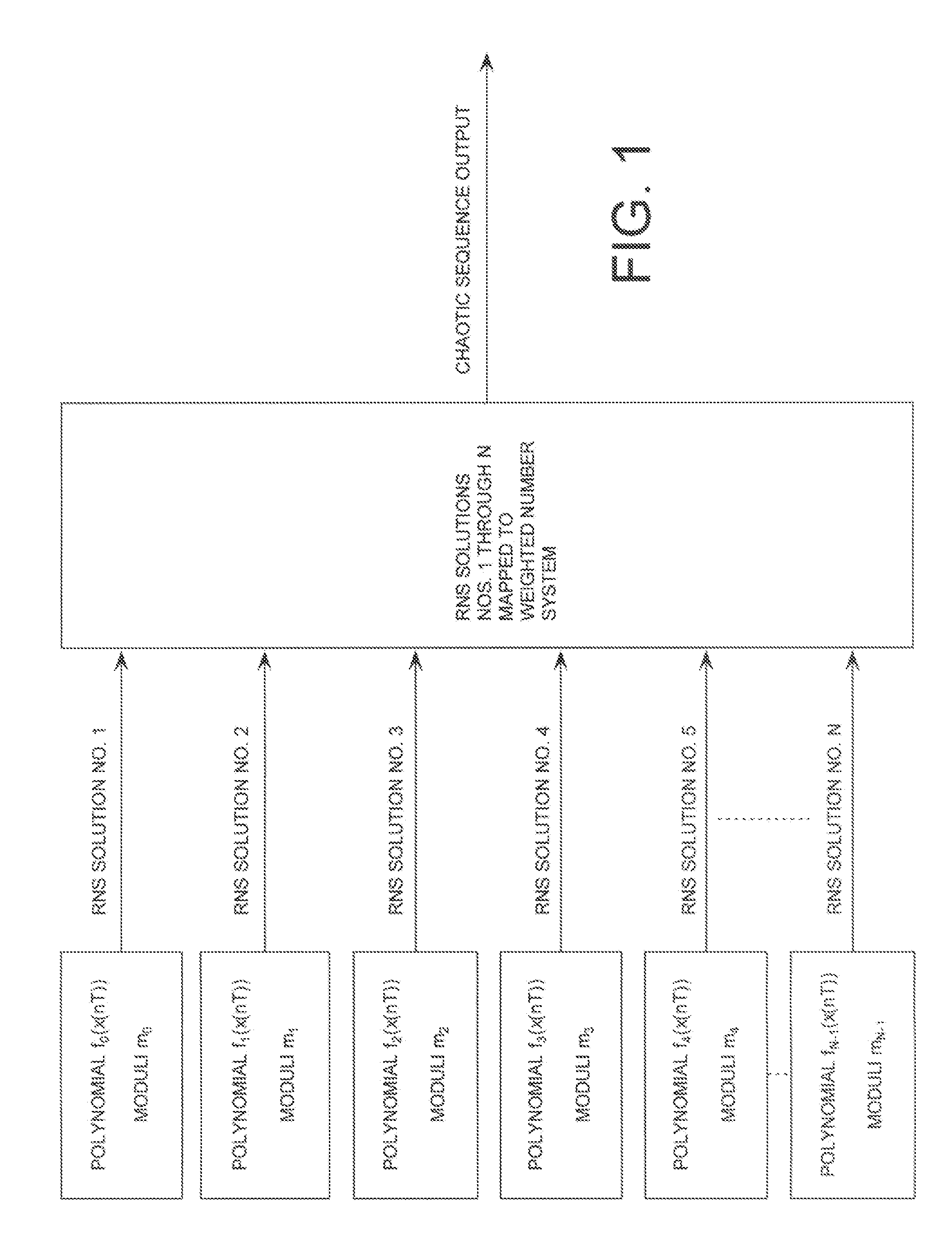

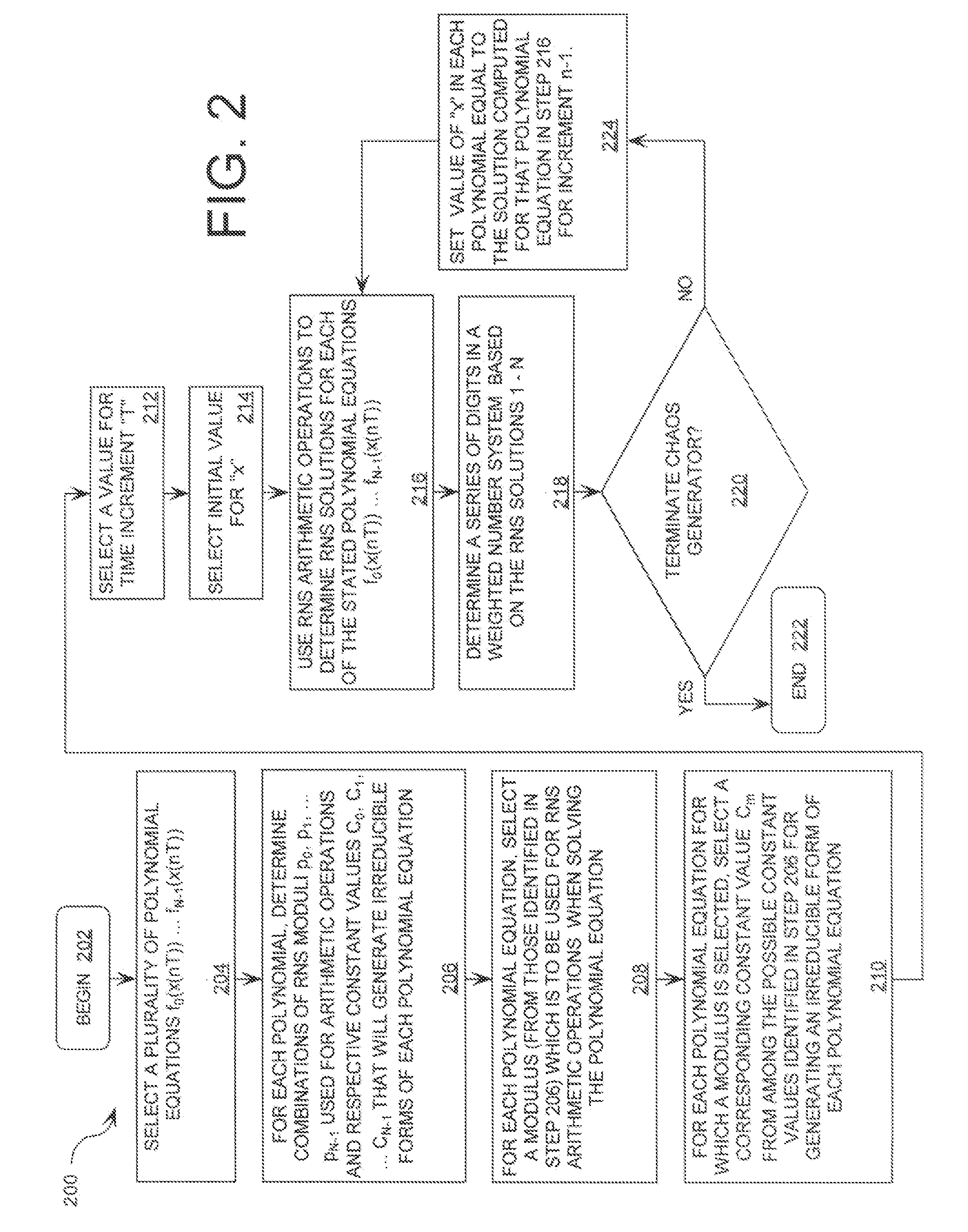

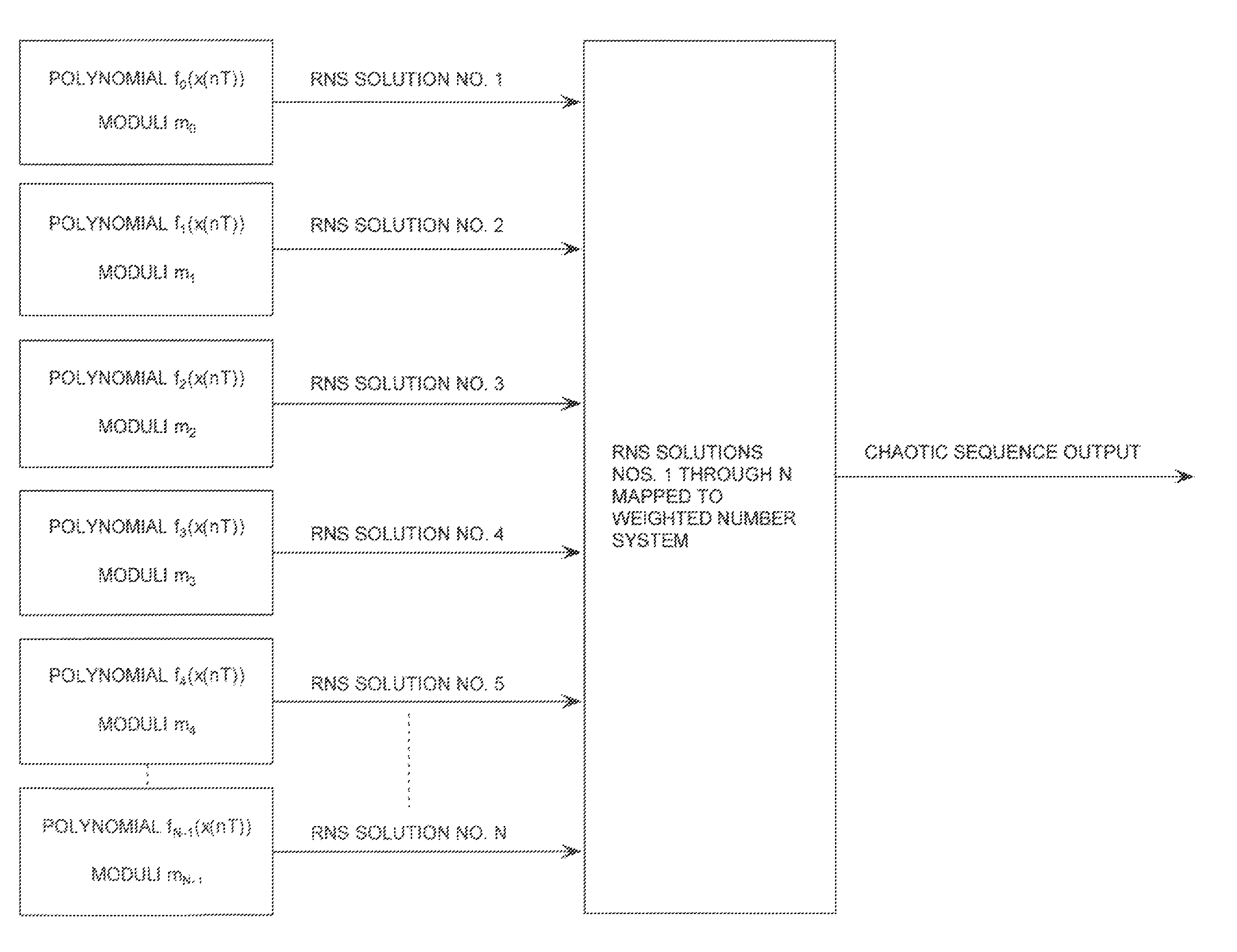

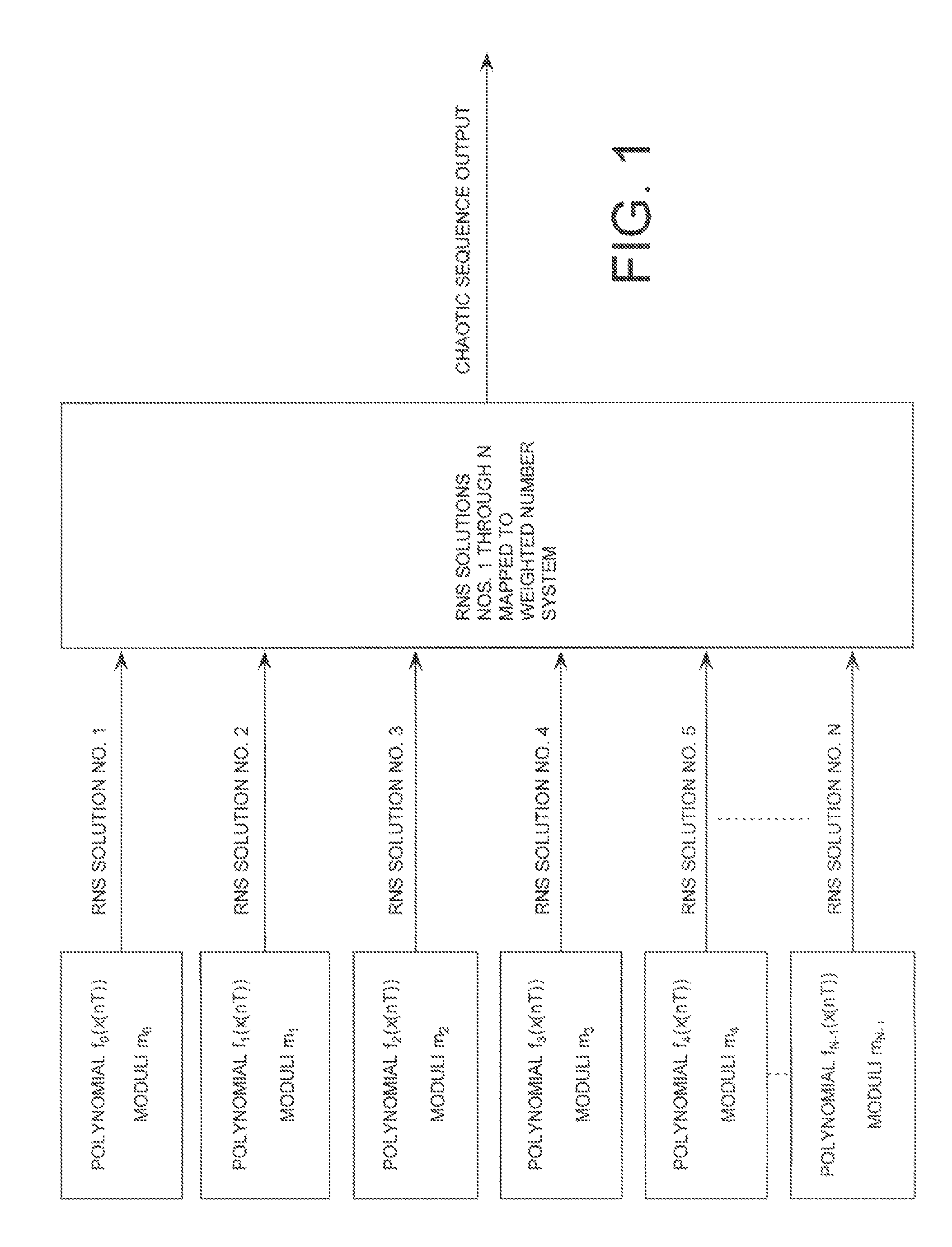

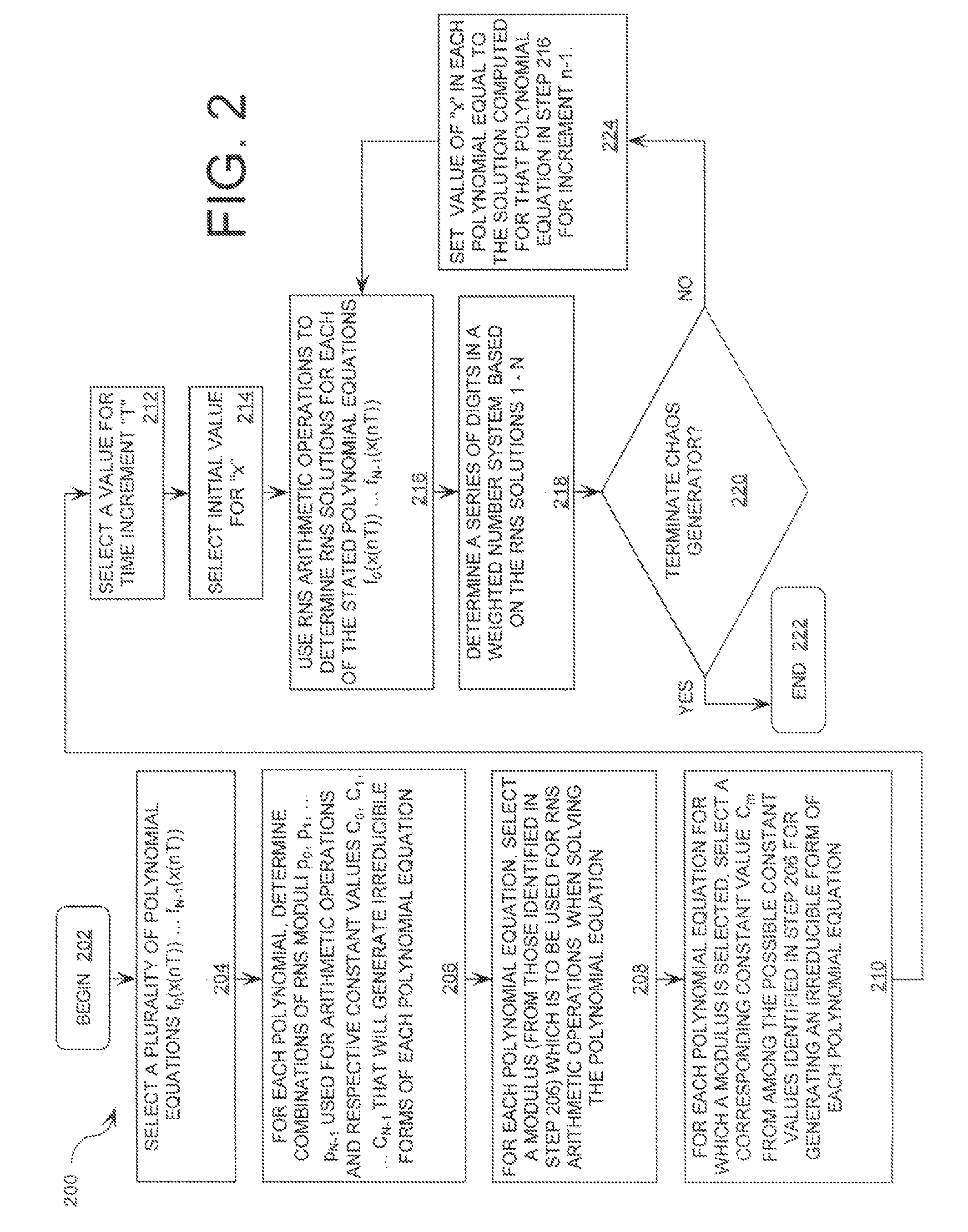

Digital Generation of a Chaotic Numerical Sequence

ActiveUS20080263119A1Random number generatorsComputations using residue arithmeticNumbering systemChinese remainder theorem

A method is provided for generating a chaotic sequence. The method includes selecting a plurality of polynomial equations. The method also includes using residue number system (RNS) arithmetic operations to respectively determine solutions for the polynomial equations. The solutions are iteratively computed and expressed as RNS residue values. The method further includes determining a series of digits in a weighted number system (e.g., a binary number system) based on the RNS residue values. According to an aspect of the invention, the method includes using a Chinese Remainder Theorem process to determine a series of digits in the weighted number system based on the RNS residue values. According to another aspect of the invention, the determining step comprises identifying a number in the weighted number system that is defined by the RNS residue values.

Owner:HARRIS CORP

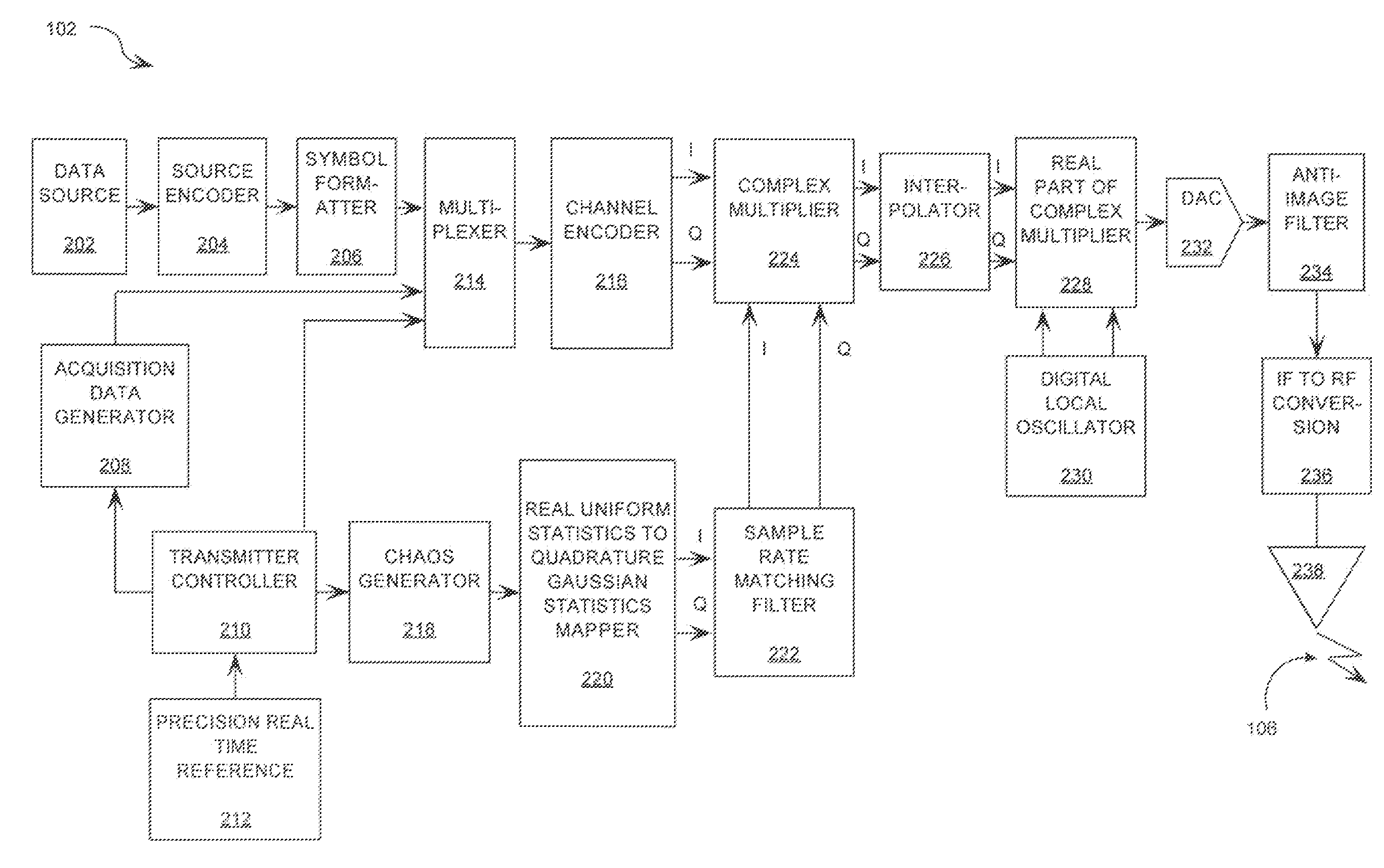

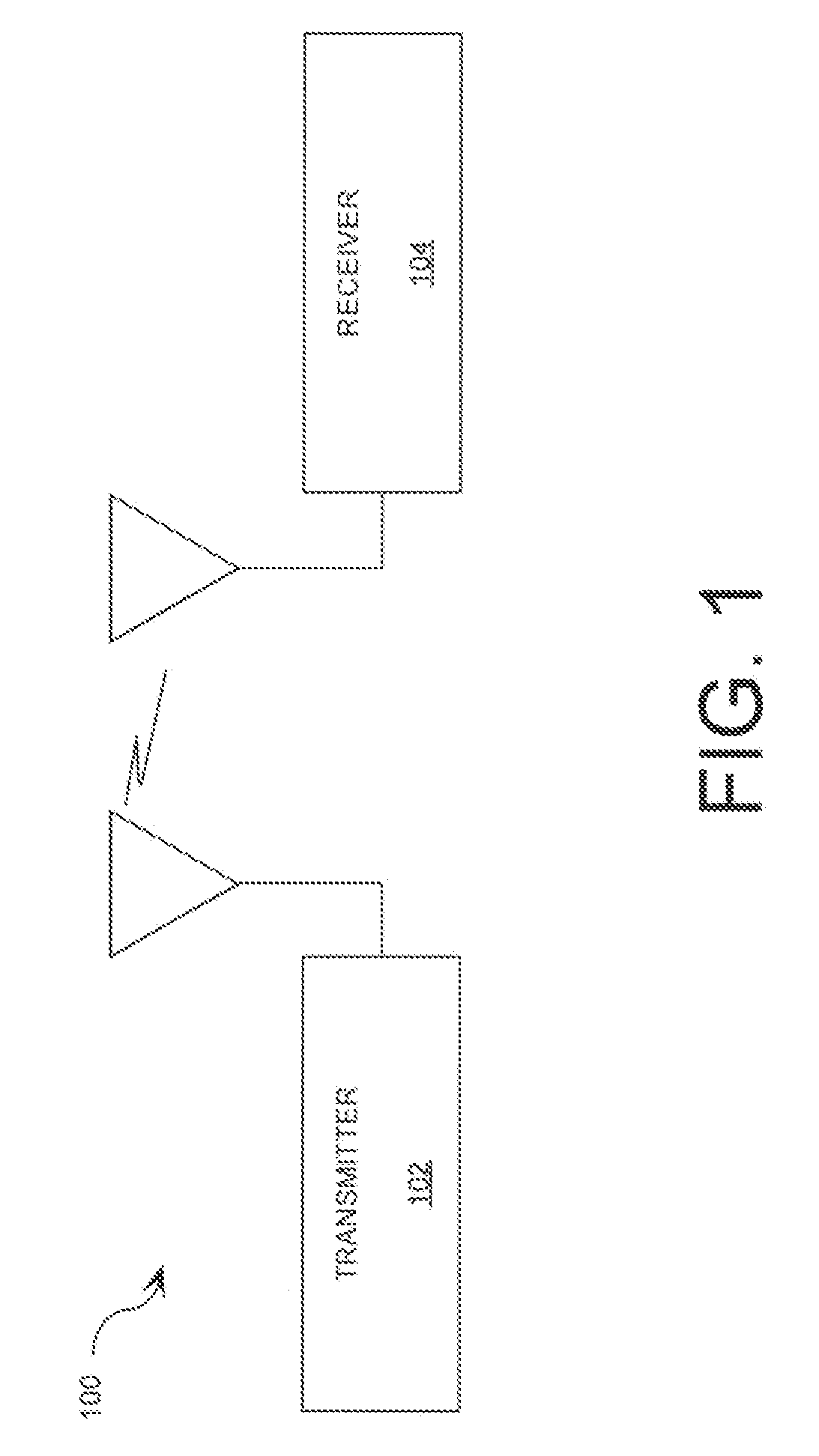

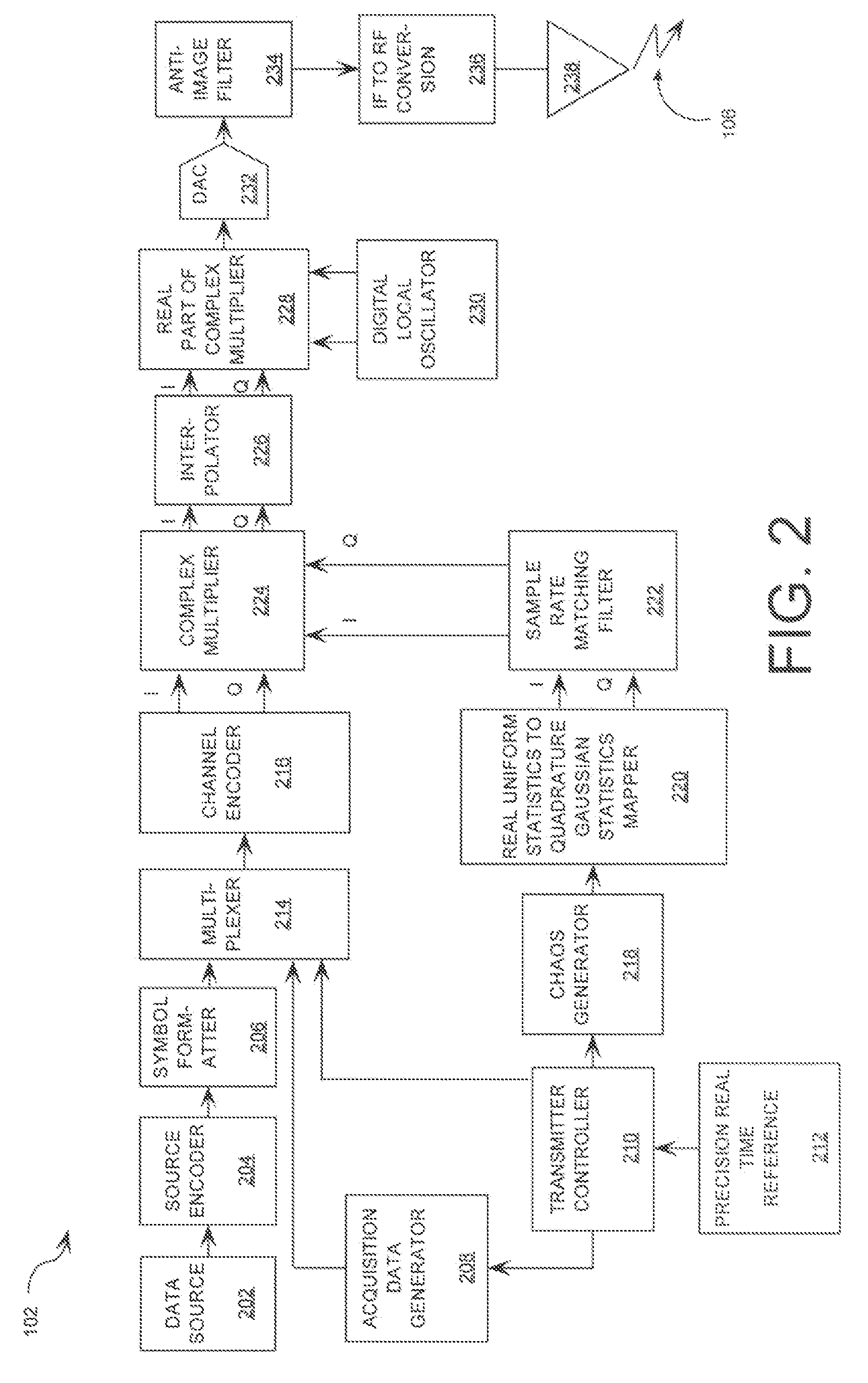

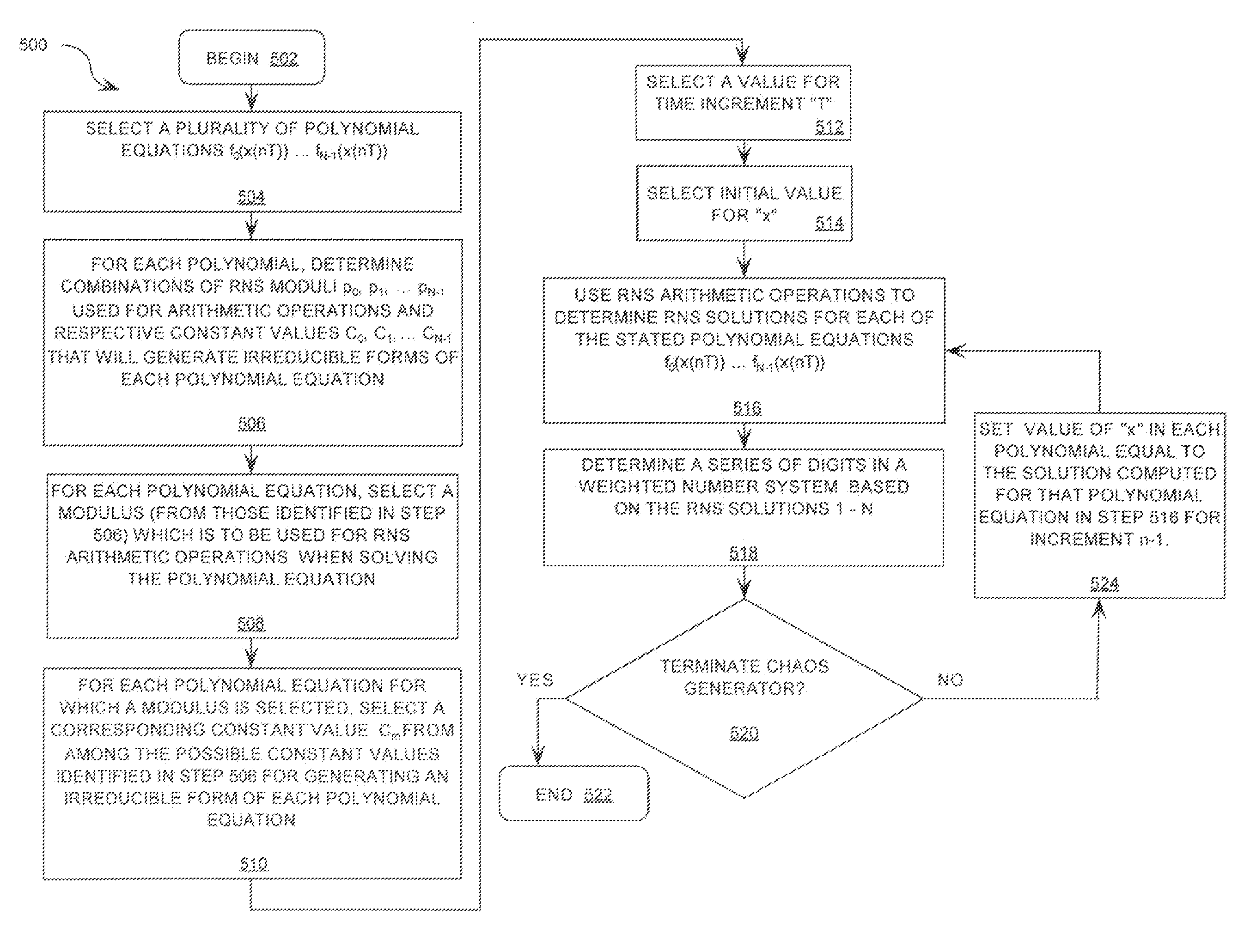

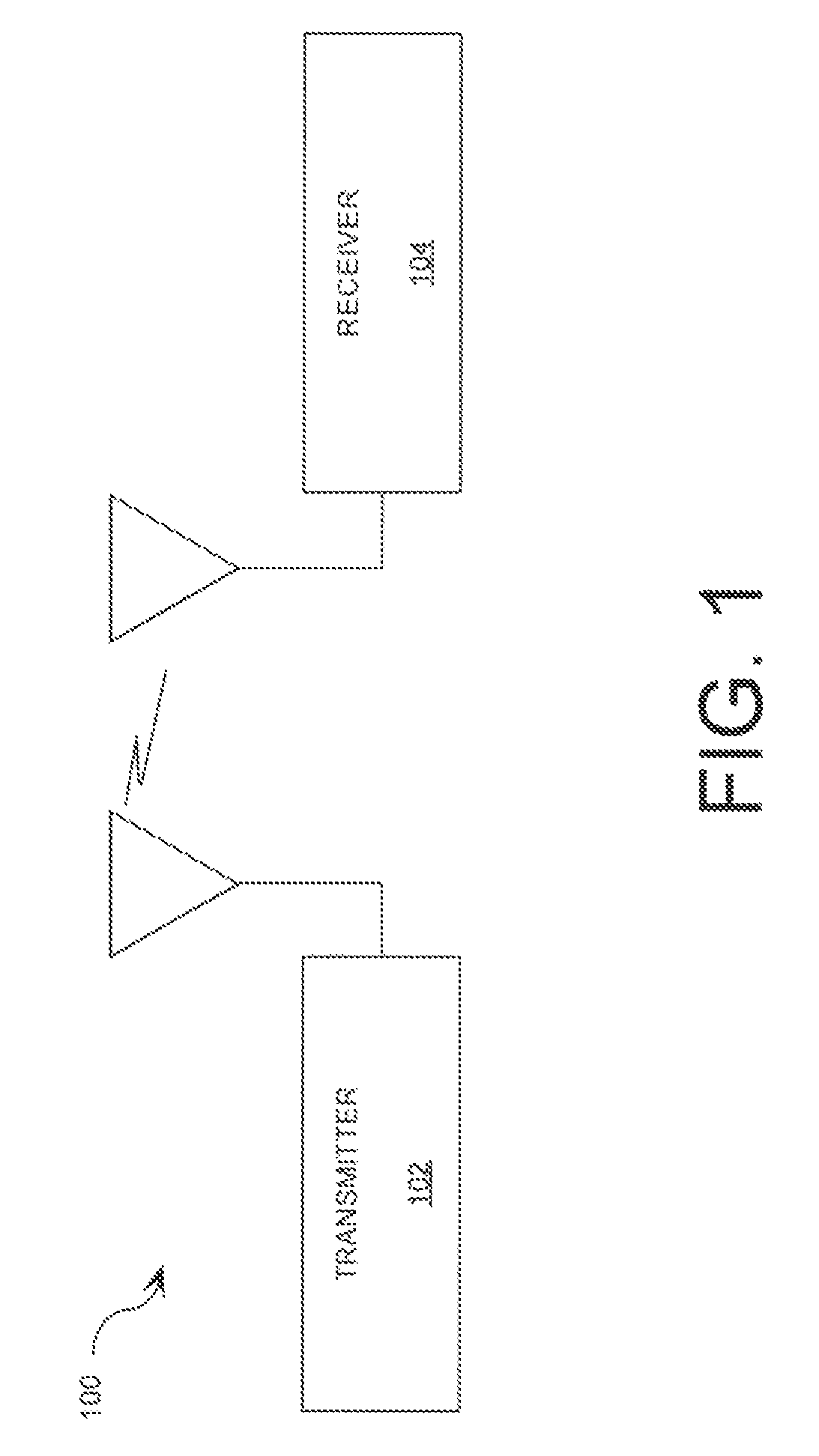

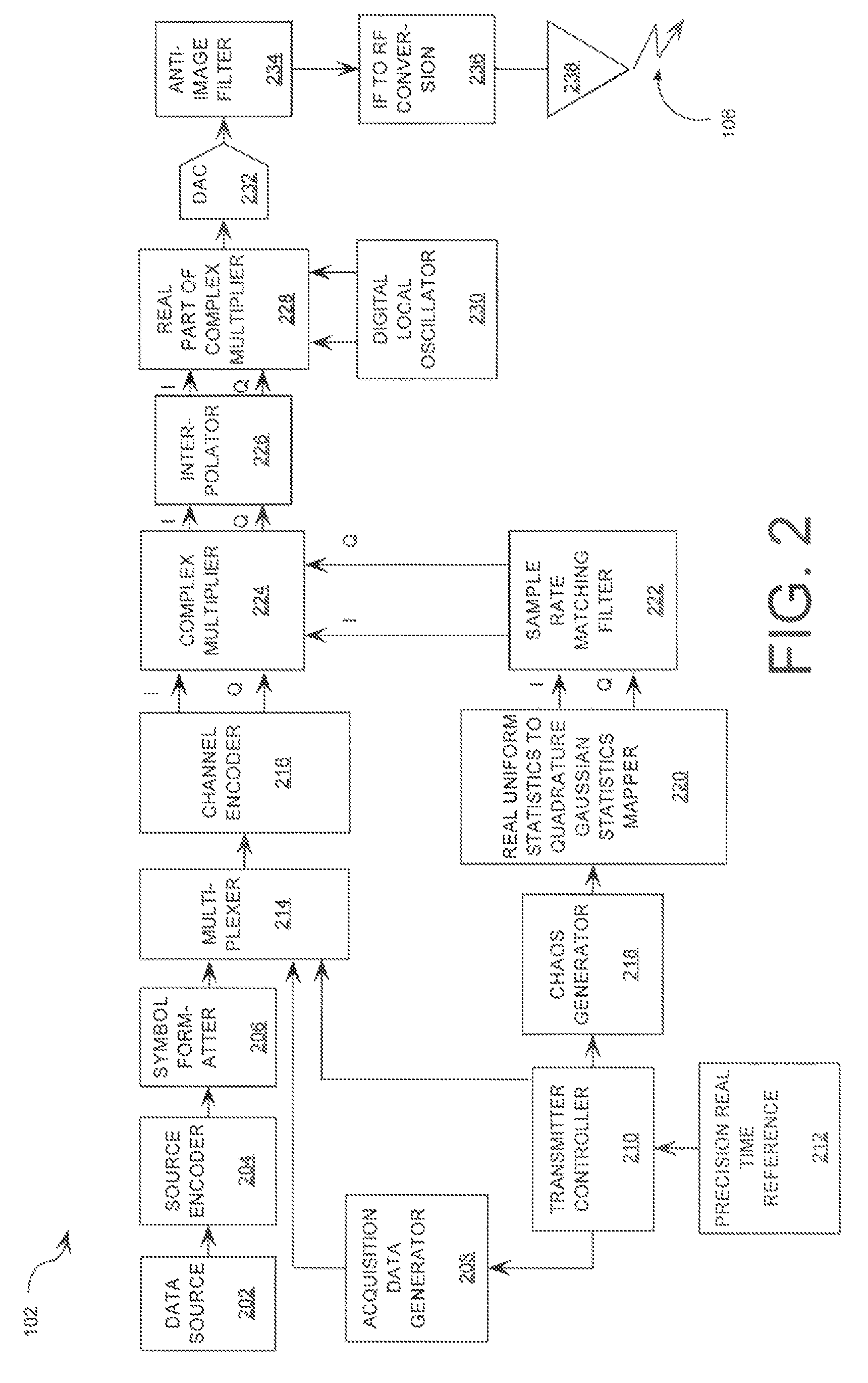

Spread Spectrum Communications System and Method Utilizing Chaotic Sequence

ActiveUS20080304666A1Minimize timing difference uncertaintyMinimize the differenceMultiplex code generationSecuring communicationCommunications systemNumbering system

A method is provided for generating a coherent chaotic sequence spread spectrum communications system. The method includes phase modulating a carrier with information symbols. The method also includes generating a string of discrete time chaotic samples. The method further includes modulating the carrier in a chaotic manner using the string of discrete time chaotic samples. Each of the discrete time chaotic samples has a shorter sample time interval than the duration of the information symbols. The generating step includes selecting a plurality of polynomial equations. The generating step also includes using residue number system (RNS) arithmetic operations to respectively determine solutions for the polynomial equations. The solutions are iteratively computed and expressed as RNS residue values. The generating step further includes determining a series of digits in the weighted number system based on the RNS residue values. The method further includes synchronizing the chaos generated at the receiver with that generated at the transmitter without periodic transfer of state update information.

Owner:HARRIS CORP

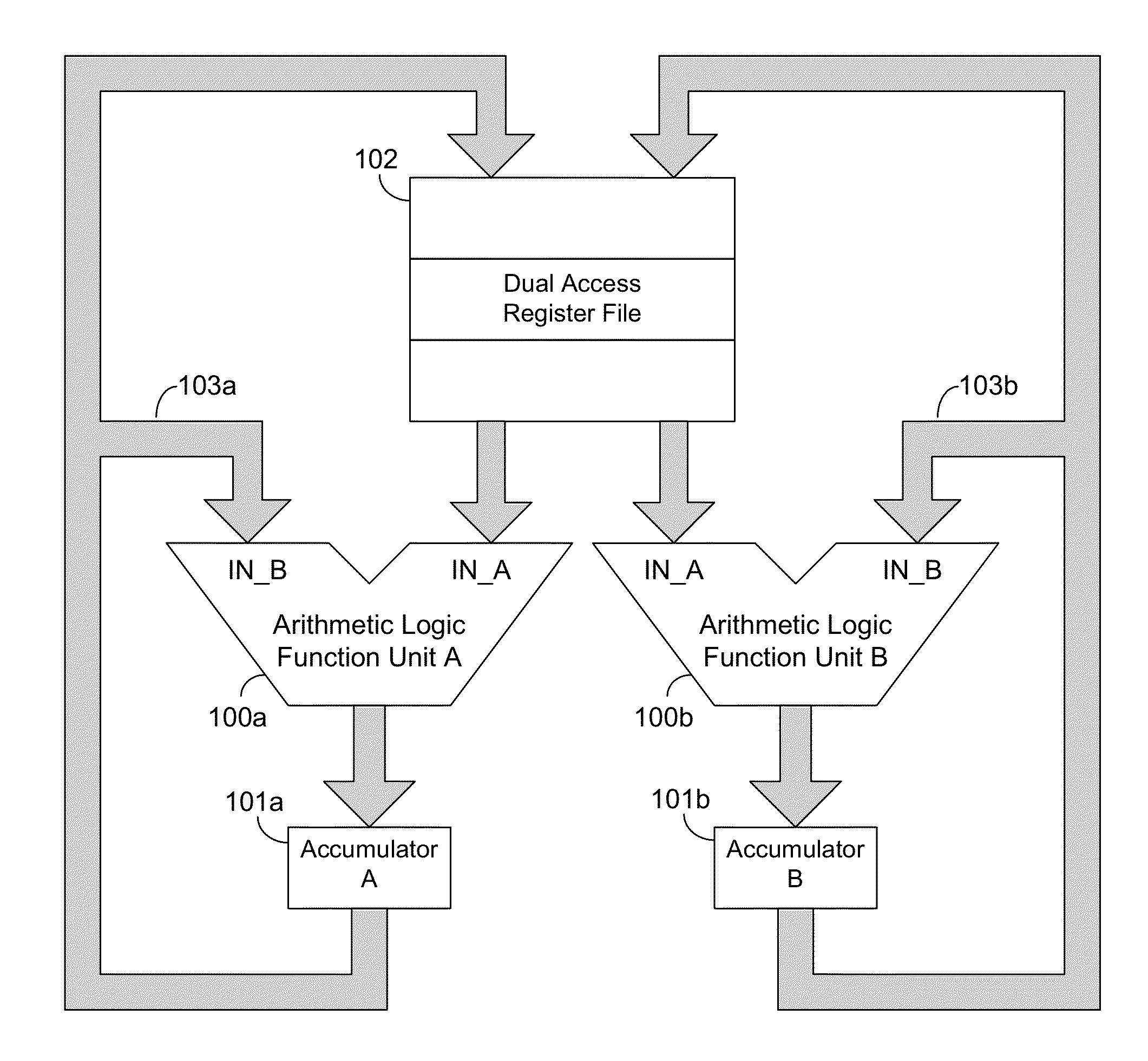

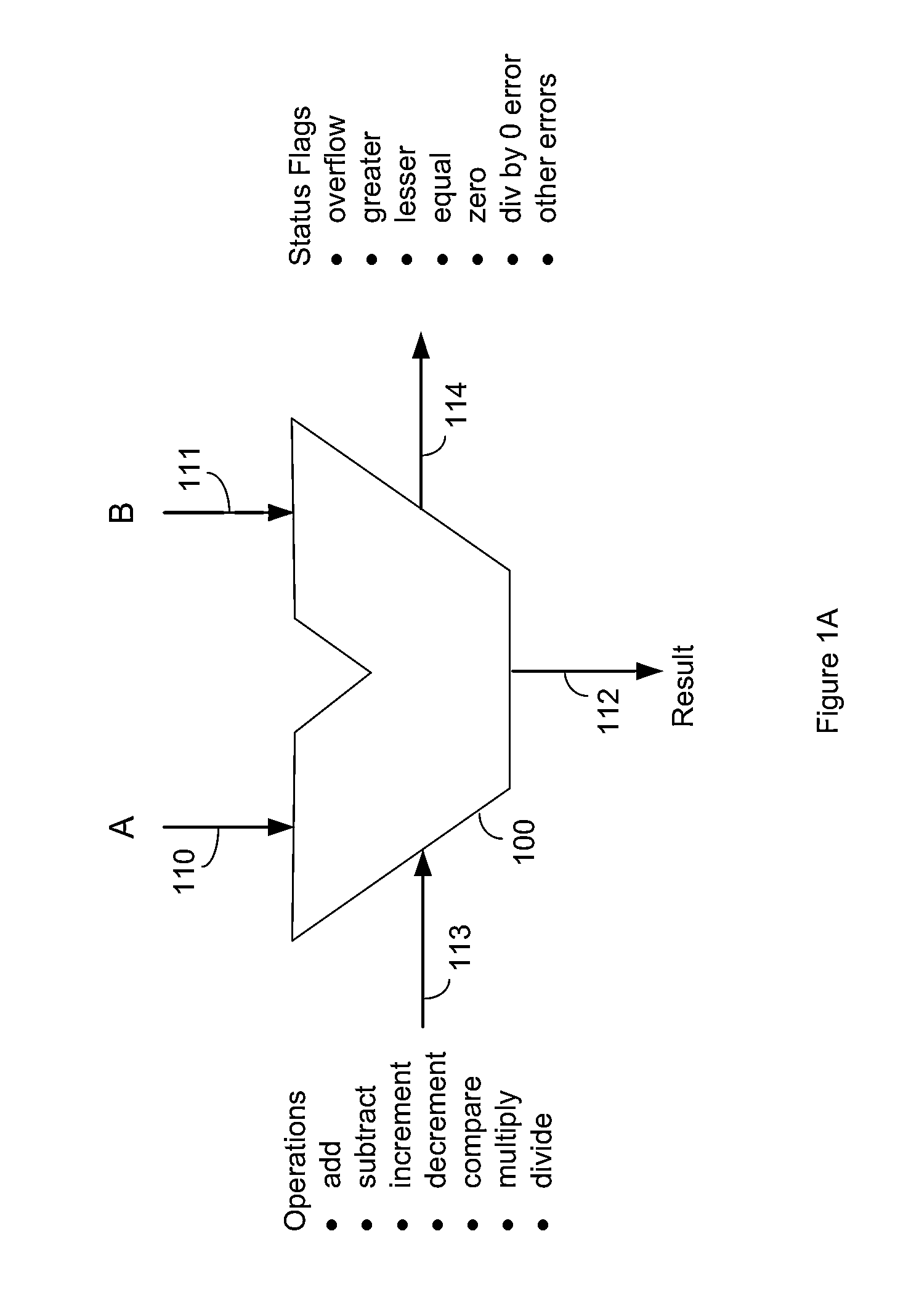

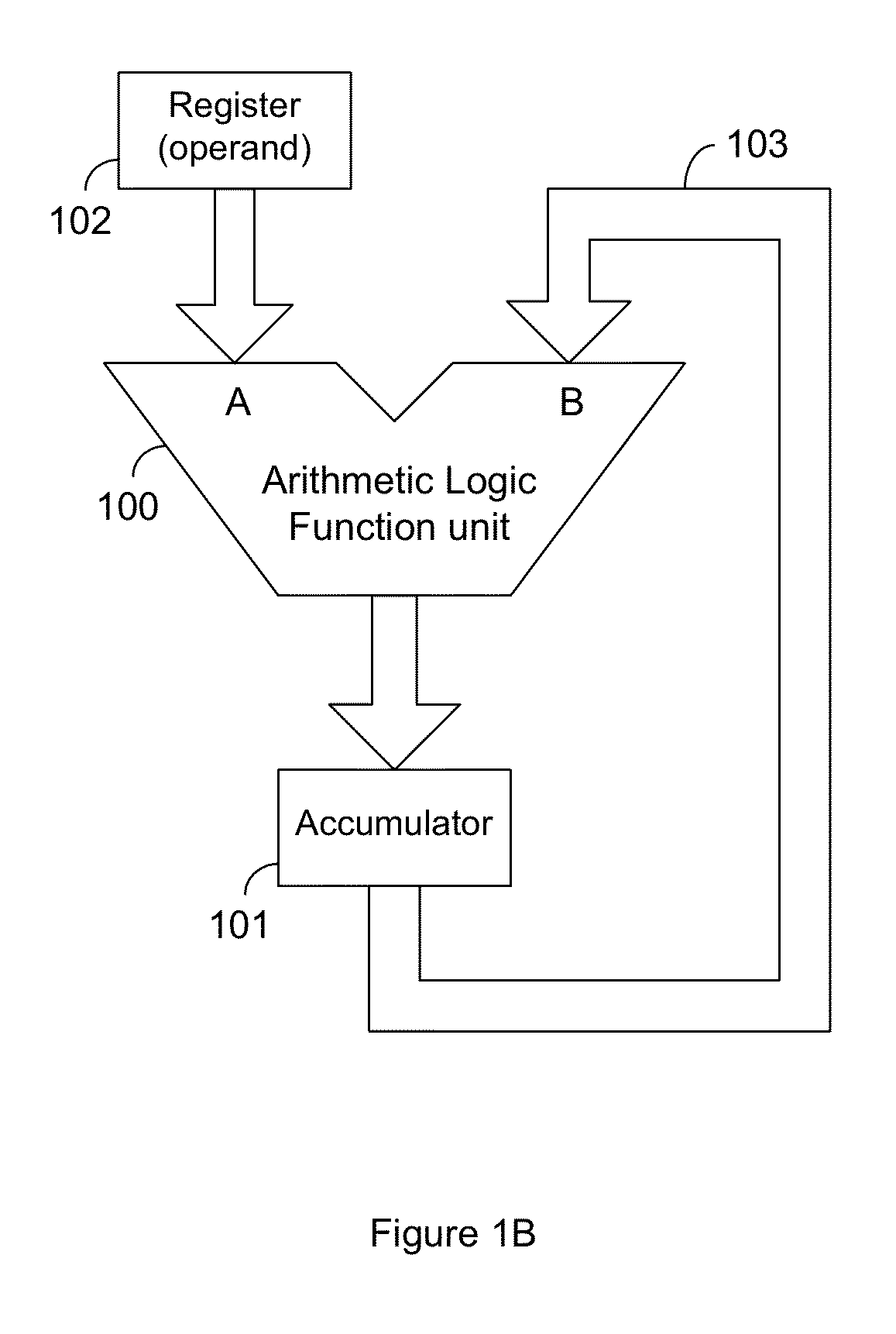

Residue number arithmetic logic unit

ActiveUS20130311532A1Improve performanceConservingProgram controlComputation using denominational number representationArithmetic logic unitNumbering system

Methods and systems for residue number system based ALUs, processors, and other hardware provide the full range of arithmetic operations while taking advantage of the benefits of the residue numbers in certain operations. In one or more embodiments, an RNS ALU or processor comprises a plurality of digit slices configured to perform modular arithmetic functions. Operation of the digit slices may be controlled by a controller. Residue numbers may be converted to and from fixed or mixed radix number systems for internal use and for use in various computing systems.

Owner:OLSEN IP RESERVE

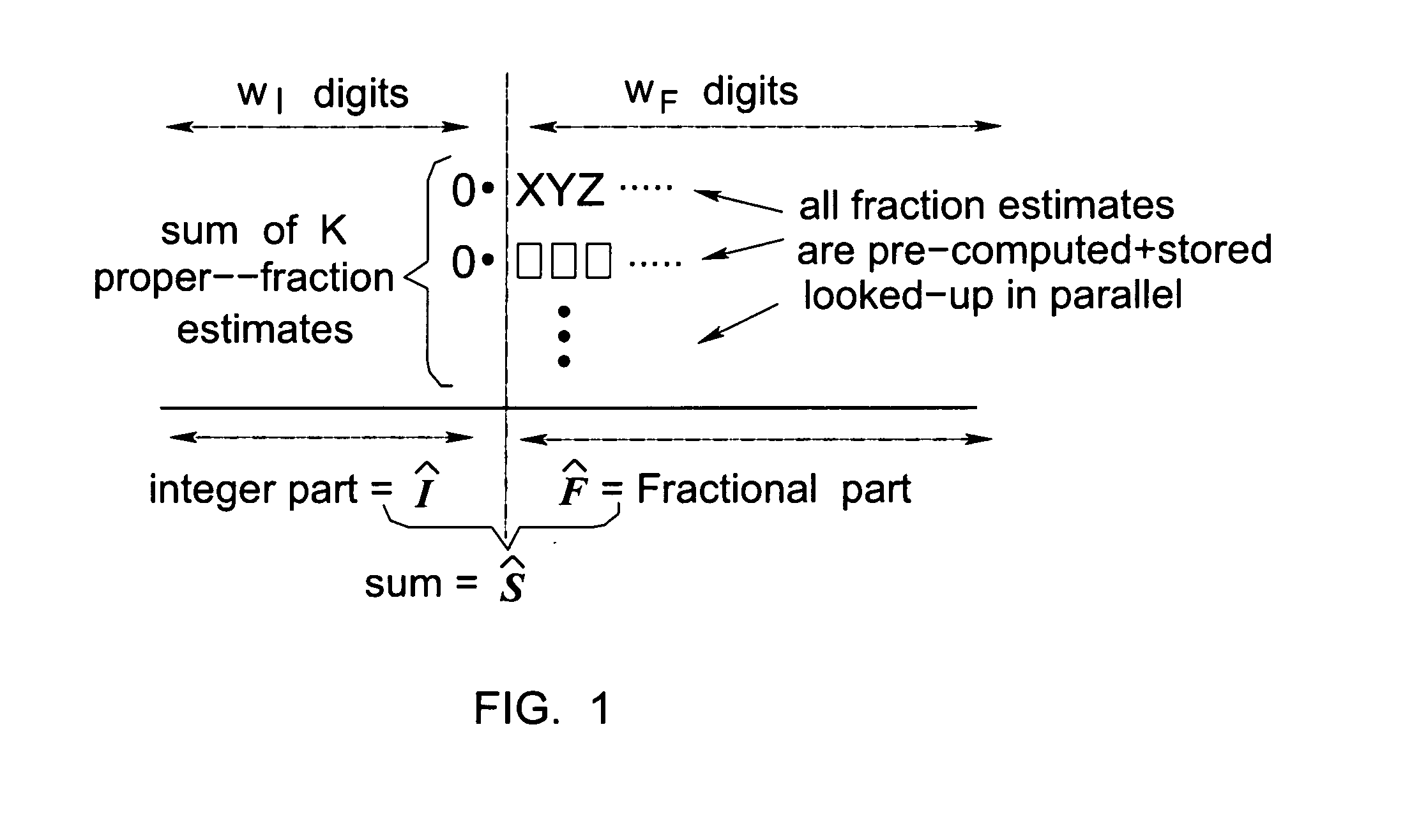

Residue Number Systems Methods and Apparatuses

InactiveUS20110231465A1Well formedComputations using residue arithmeticComputation using denominational number representationSystems approachesComputer science

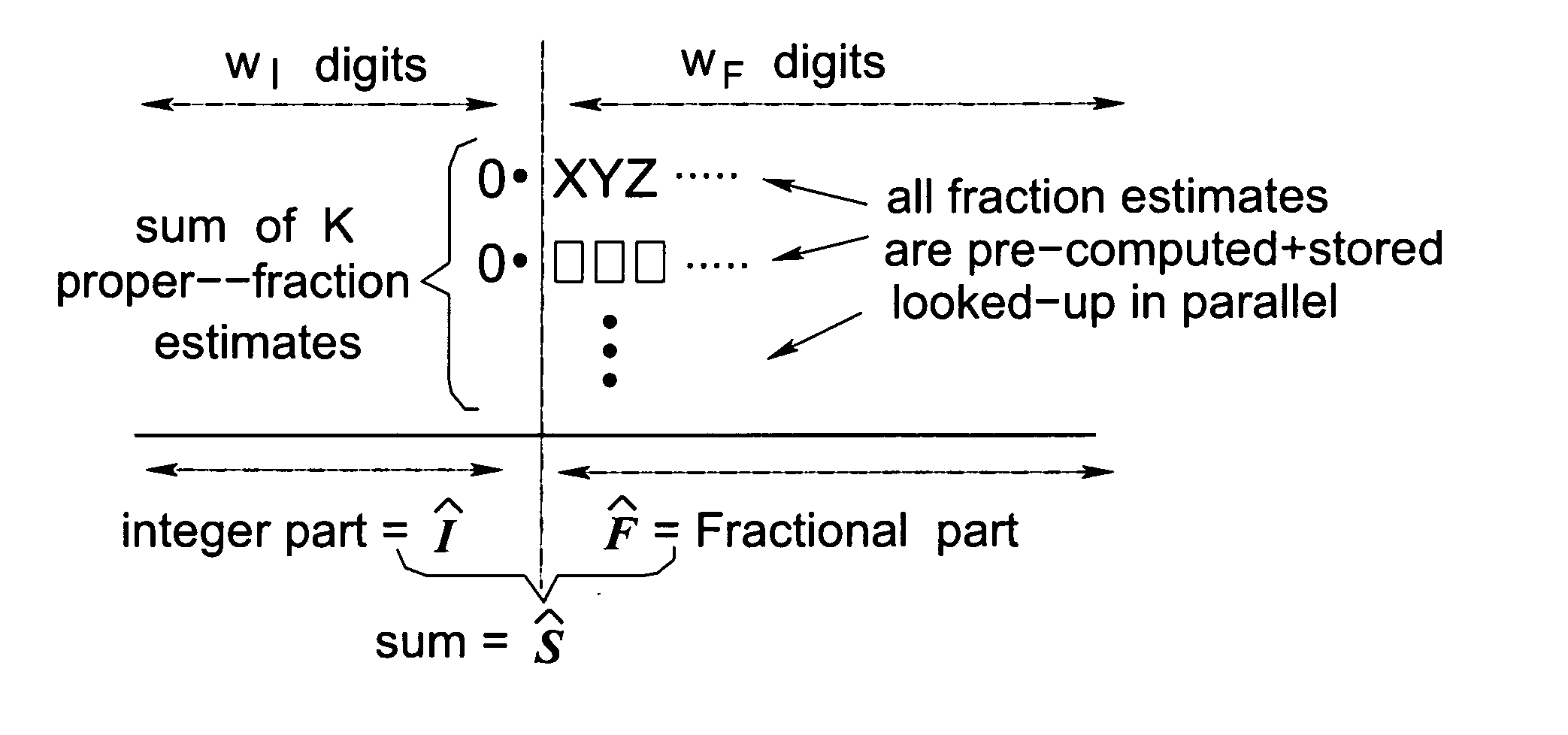

A method for performing reconstruction using a residue number system includes selecting a set of moduli. A reconstruction coefficient is estimated based on the selected set of moduli. A reconstruction operation is performed using the reconstruction coefficient.

Owner:PHATAK DHANANJAY S

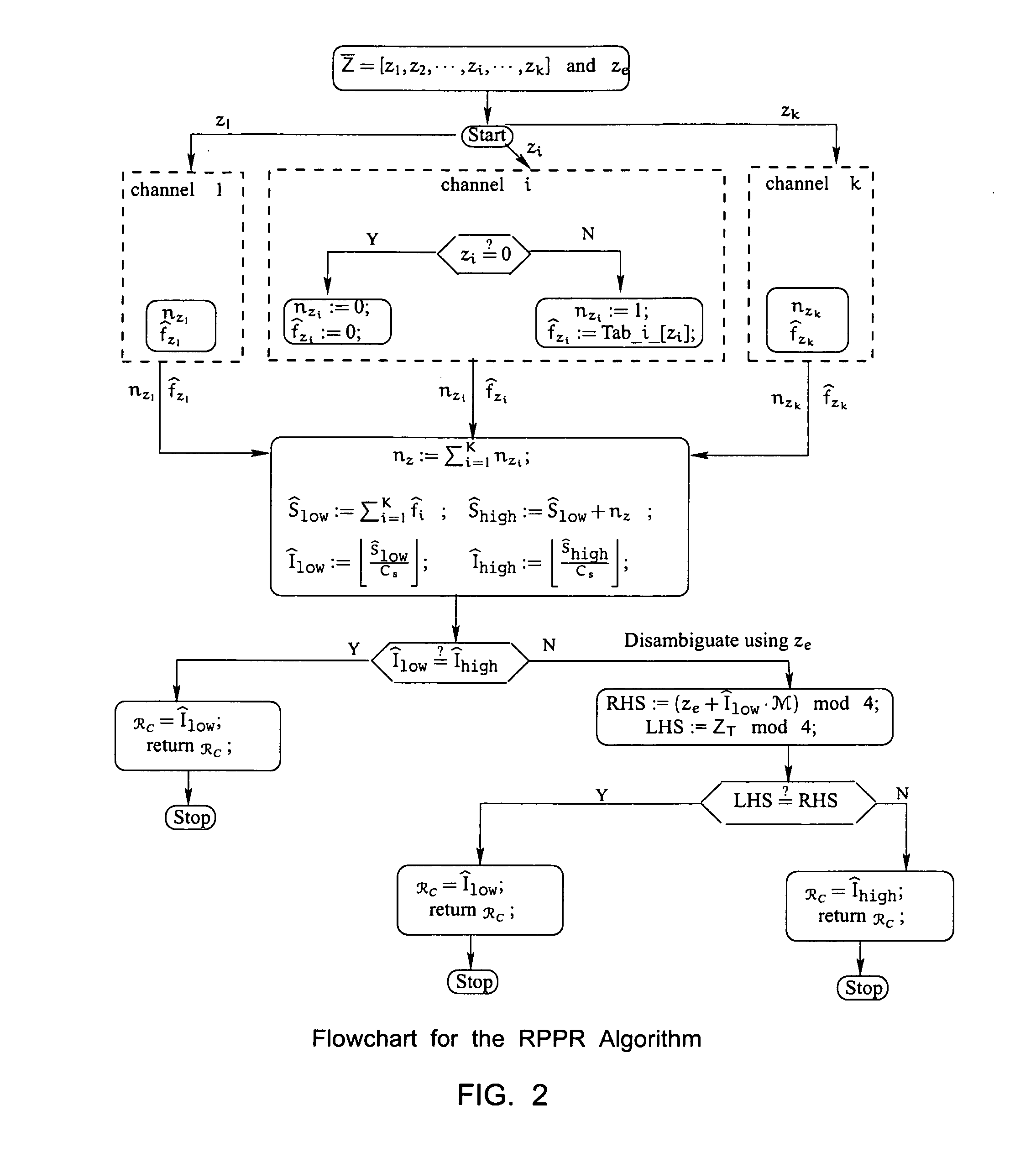

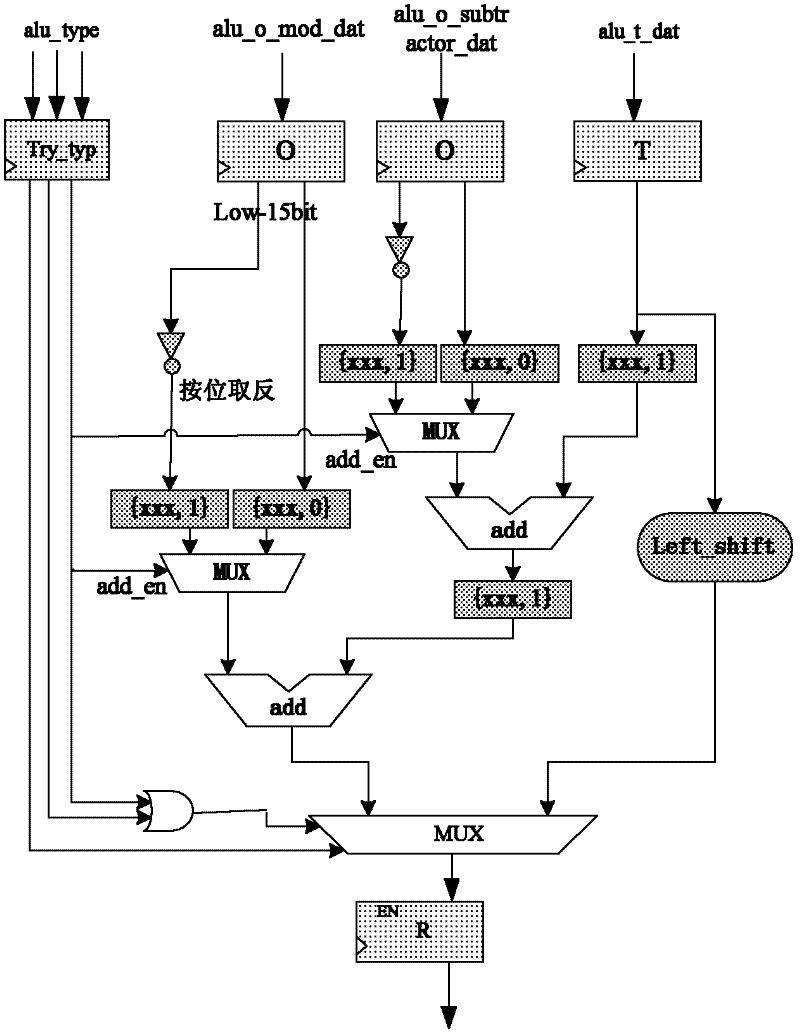

Method for processing RSA password based on residue number system and coprocessor

ActiveCN102231102AImprove decryption performanceImprove parallelismComputations using residue arithmeticCoprocessorPassword

The invention relates to information technology security and microprocessor design. Aiming at increasing RSA (Ron Rivest, Adi Shamirh and LenAdleman) modular multiplication operation speed and improving RSA encryption and decryption performances, the invention provides the technical scheme as follows: a method for processing an RSA password based on a residue number system comprises the followingsteps of performs encryption and decryption operations by using an RSA algorithm and performing large-number modular exponentiation of the RSA algorithm by using an L-R (Left-Right) binary scanning modular power algorithm; an improved Montgomery algorithm is specifically as follows: 1024-bit large numbers with are expressed as numbers under the residue number system, namely two sets of 33 32-bit decimal numbers and one 32-bit number expressed under a redundancy base; an expression process is a mould solving process; the decomposed 32-bit decimal numbers respectively participate in 32-bit modular multiplication, modular multiplication accumulation and modular addition operation independently; furthermore, 32-bit data performs parallel execution operation without dependence; and the method disclosed by the invention is mainly applicable for the information technology security and microprocessor design.

Owner:PHYTIUM TECH CO LTD

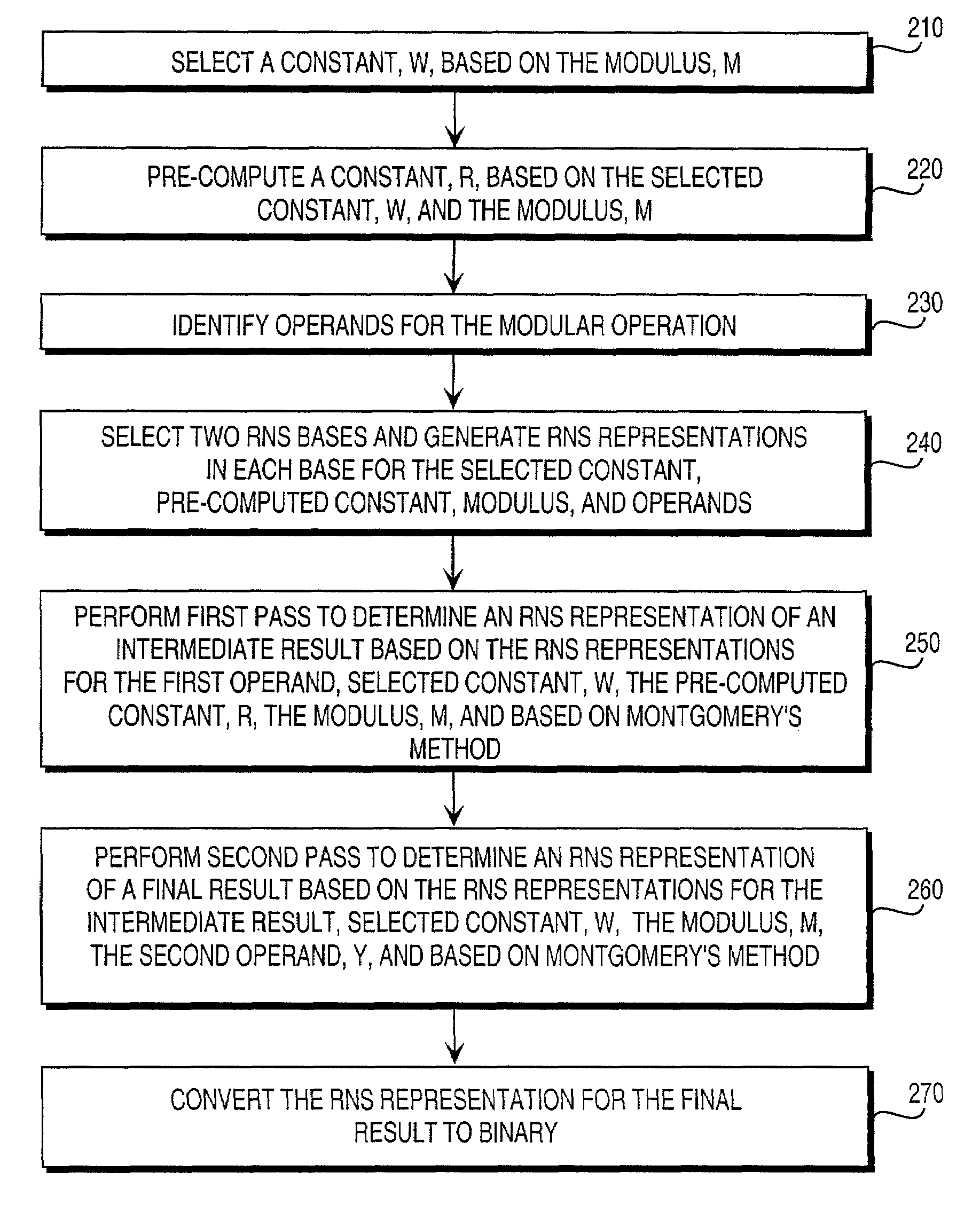

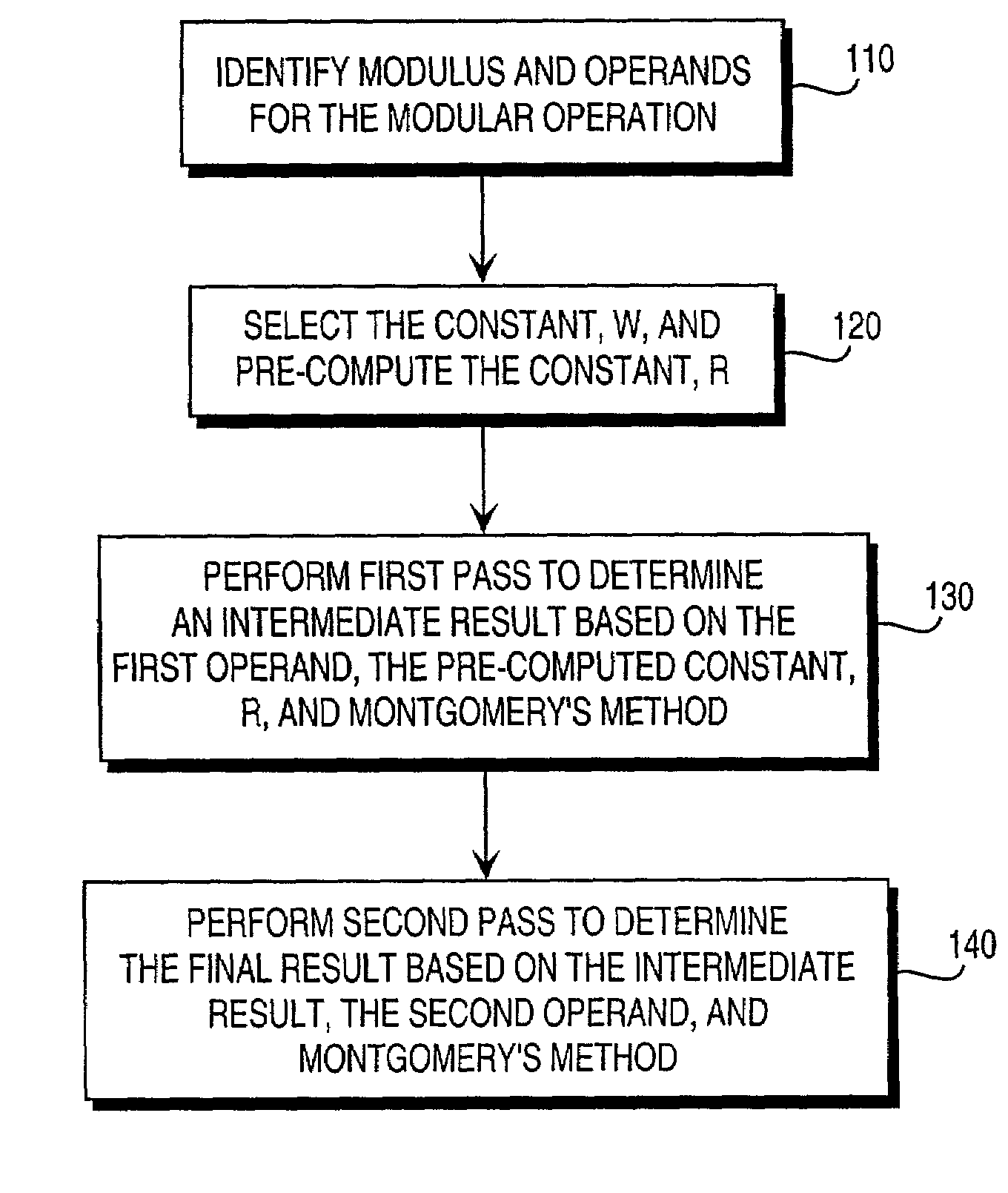

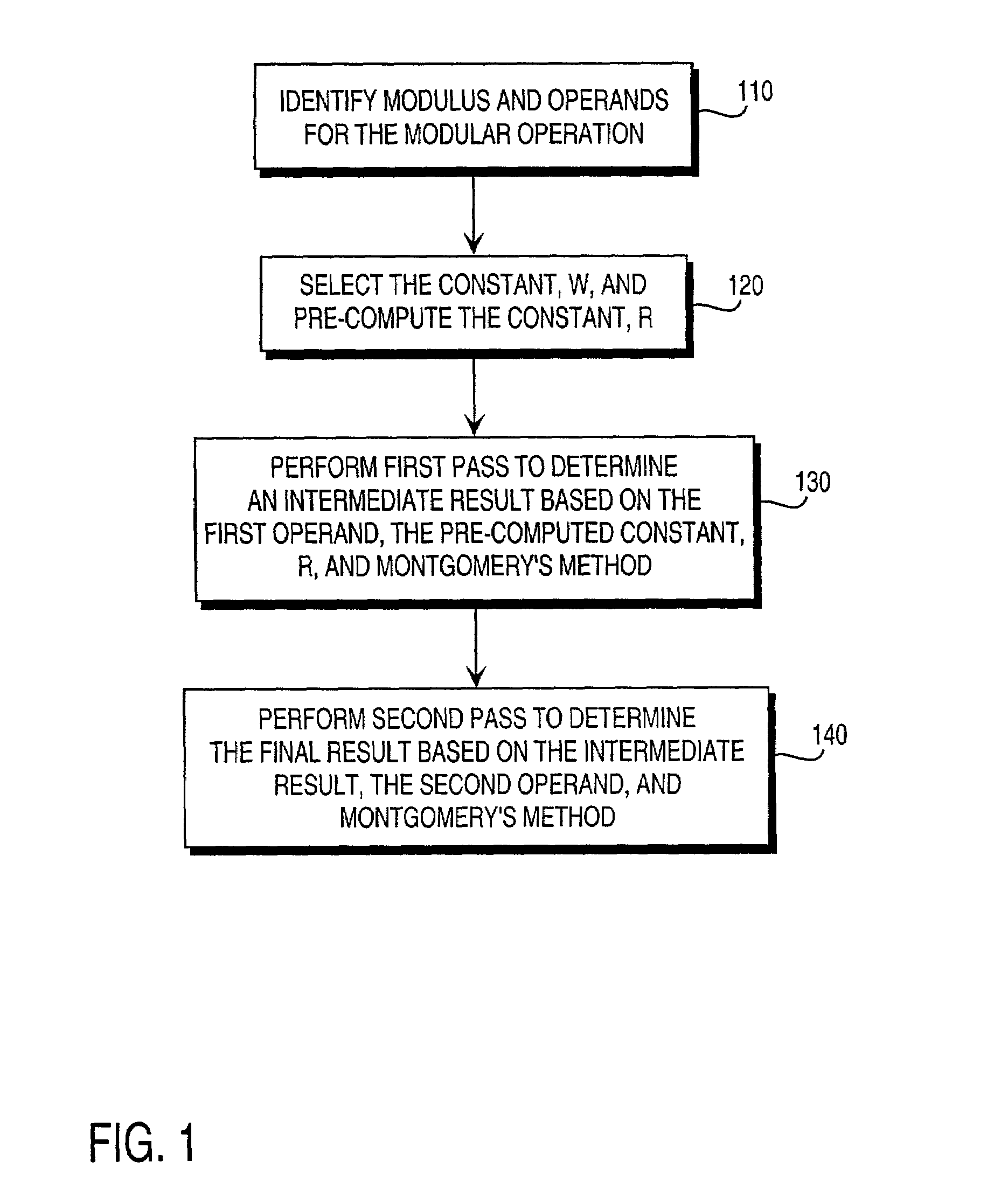

Pre-computation and dual-pass modular arithmetic operation approach to implement encryption protocols efficiently in electronic integrated circuits

InactiveUS7027597B1Effective encryptionEfficient implementationComputations using contact-making devicesComputation using non-contact making devicesProcessor registerModularity

A pre-computation and dual-pass modular operation approach to implement encryption protocols efficiently in electronic integrated circuits is disclosed. An encrypted electronic message is received and another electronic message generated based on the encryption protocol. Two passes of Montgomery's method are used for a modular operation that is associated with the encryption protocol along with pre-computation of a constant based on a modulus. The modular operation may be a modular multiplication or a modular exponentiation. Modular arithmetic may be performed using the residue number system (RNS) and two RNS bases with conversions between the two RNS bases. A minimal number of register files are used for the computations along with an array of multiplier circuits and an array of modular reduction circuits. The approach described allows for high throughput for large encryption keys with a relatively small number of logical gates.

Owner:CISCO TECH INC

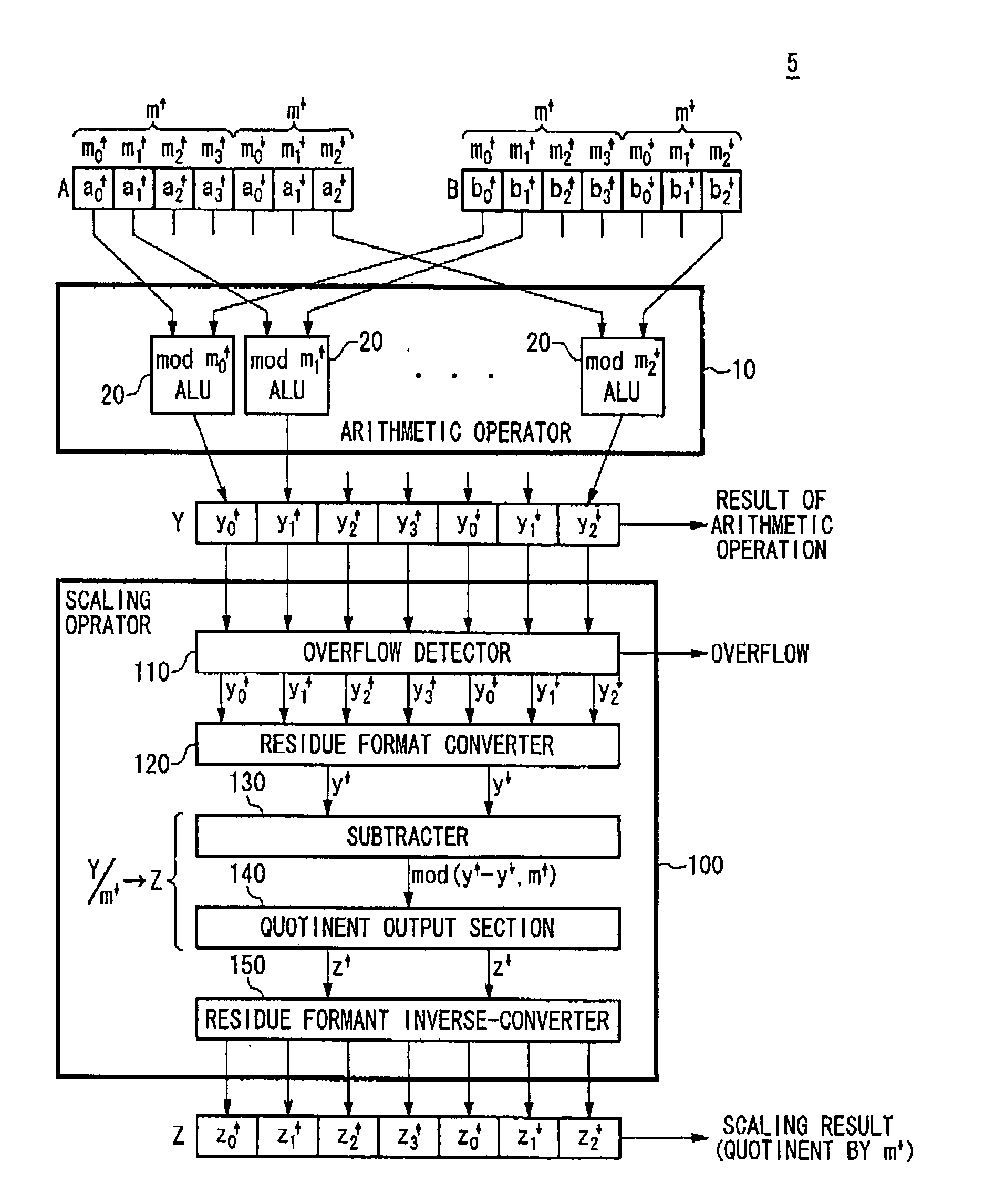

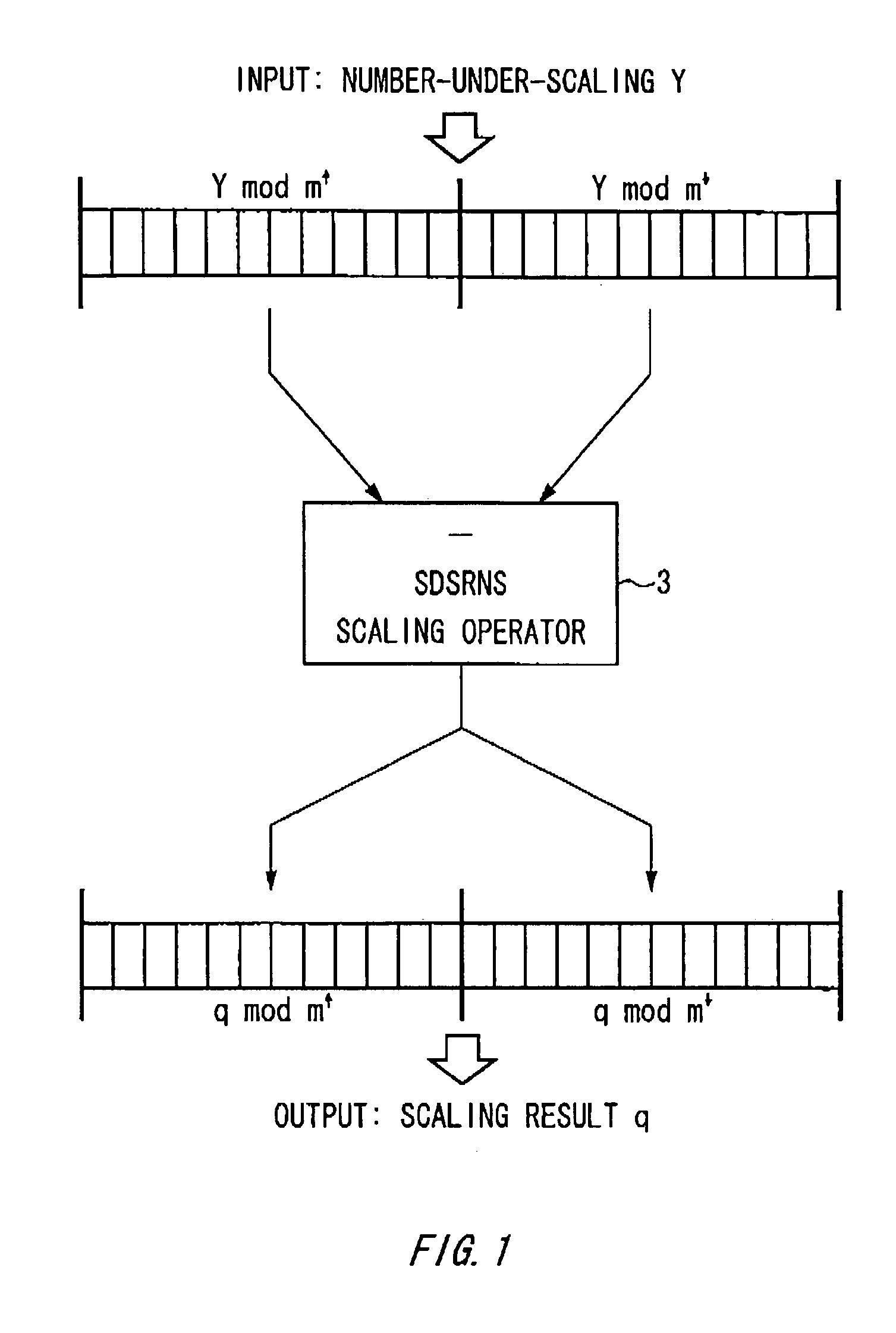

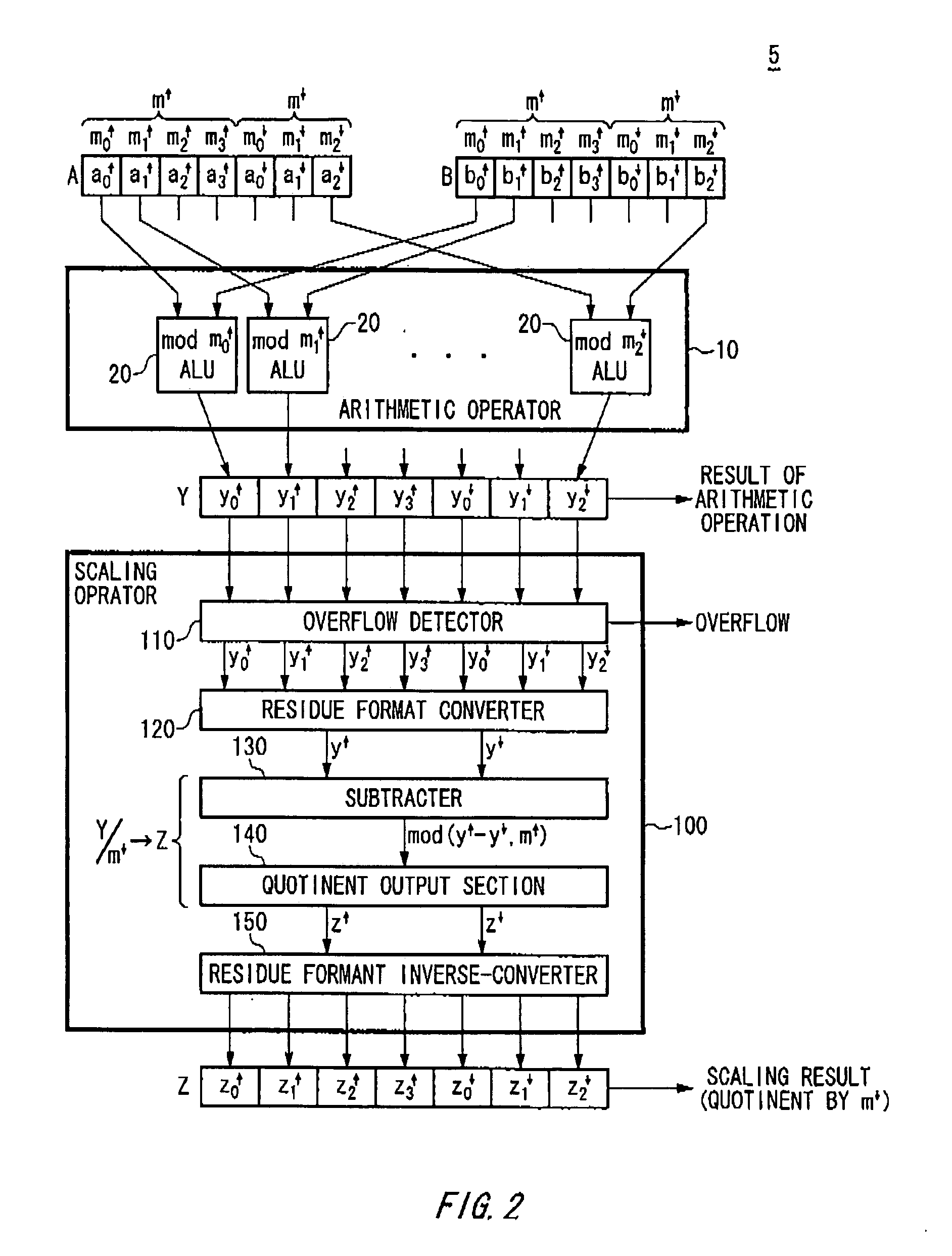

Residue number system arithmetic operating system, scaling operator, scaling operation method and program and recording medium of the same

InactiveUS20060184600A1Increase speedIncrease of speed of scalingComputations using residue arithmeticCoding/ciphering apparatusComputer scienceRecording media

There is provided a scaling operator for calculating a quotient in a first residue format obtained by dividing an input number in the first residue format by a second modulus in a residue number system for representing numbers by the first residue format of a set of residues obtained with respect to first modulus and residues obtained with respect to second modulus, having a subtracter for outputting inter-moduli values of difference which are values of difference between the residues obtained with respect to the first modulus and the residues obtained with respect to the second modulus and a quotient outputting section for outputting a set of residues of the quotient obtained with respect to the first modulus and residues of the quotient obtained with respect to the second modulus as the quotient based on the inter-moduli values of difference.

Owner:ADVANTEST CORP

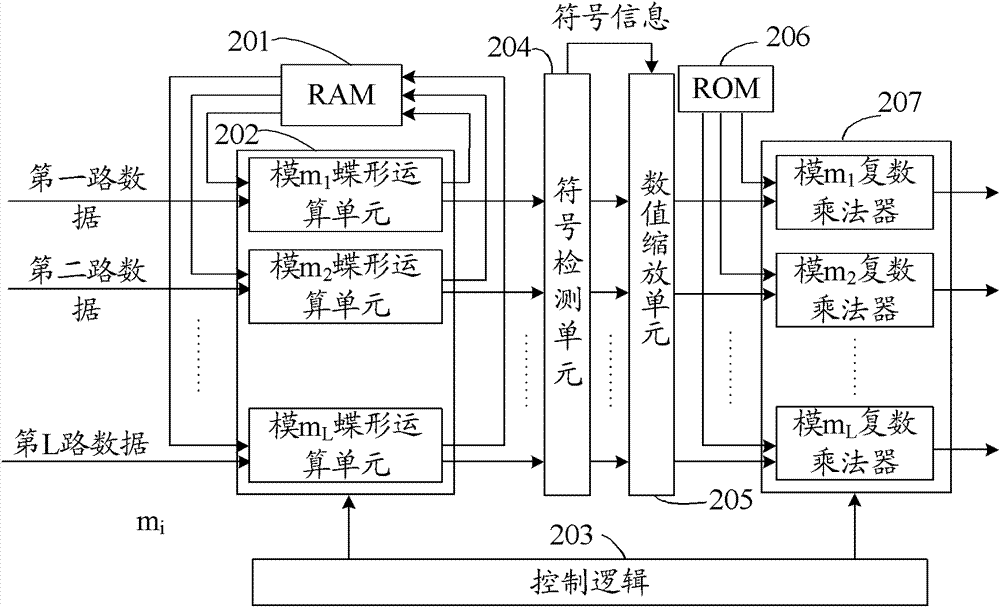

Matrix inversion device and method based on residue number system

The invention discloses a matrix inversion device and a matrix inversion method based on a residue number system. Conventional matrix inversion calculation based on a binary complement numerical representation system is divided into a plurality of parallel independent data channels according to a specific residue number base, so that the system complexity and the key path time delay are reduced. Therefore, a matrix inversion calculation structure based on the residue number system comprises a mapping and demapping module, a residue number system and a binary system conversion module, an n-order following matrix calculation module based on the residue number system, an n-order row and column type calculation unit and a sign detection and value zooming module for the residue number system (RNS) integer. A realizing structure based on the residue number system is designed by taking four-order positive definite Hermite matrix inversion as an example; and finally according to the definition of an inverse matrix, only a row and column type value of an original matrix and a following matrix of the original matrix are output.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

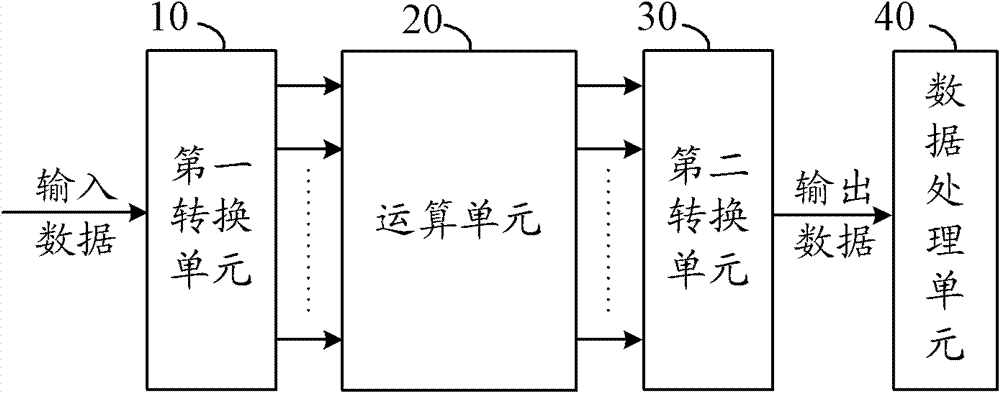

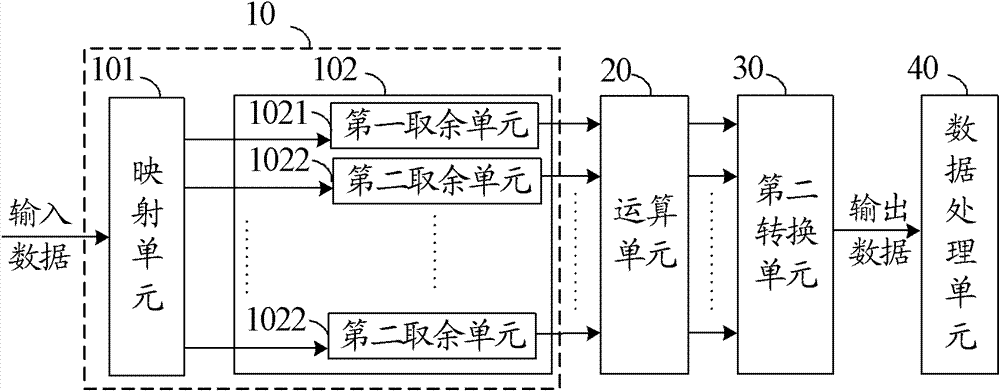

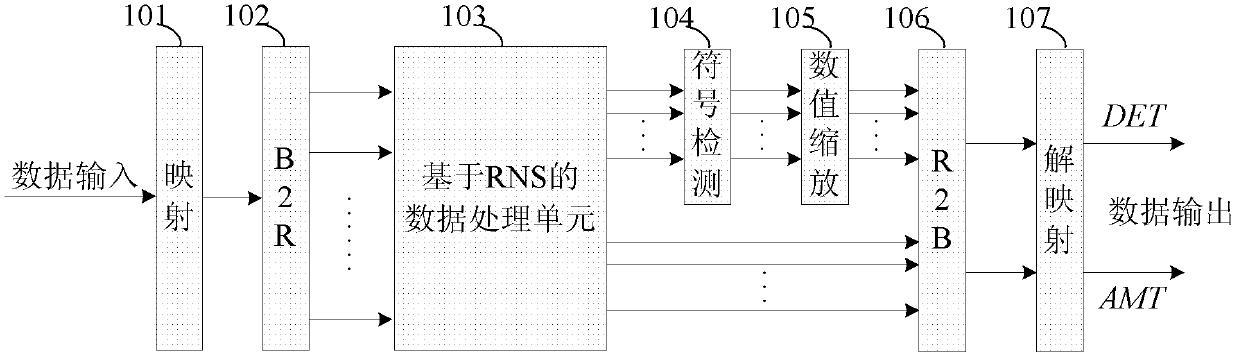

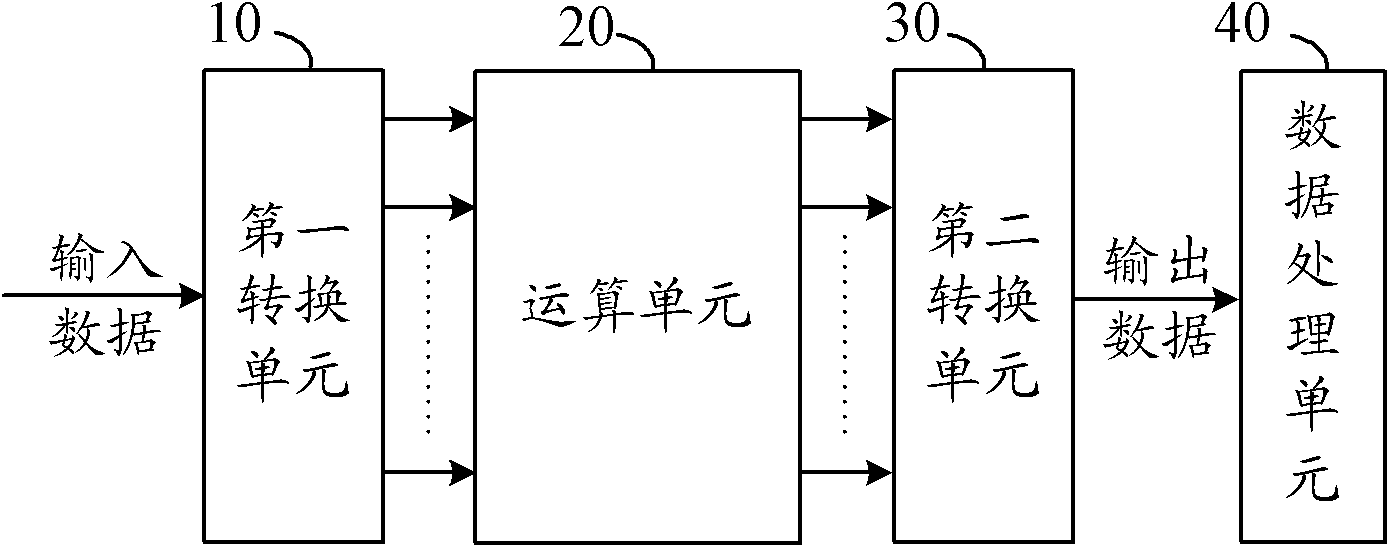

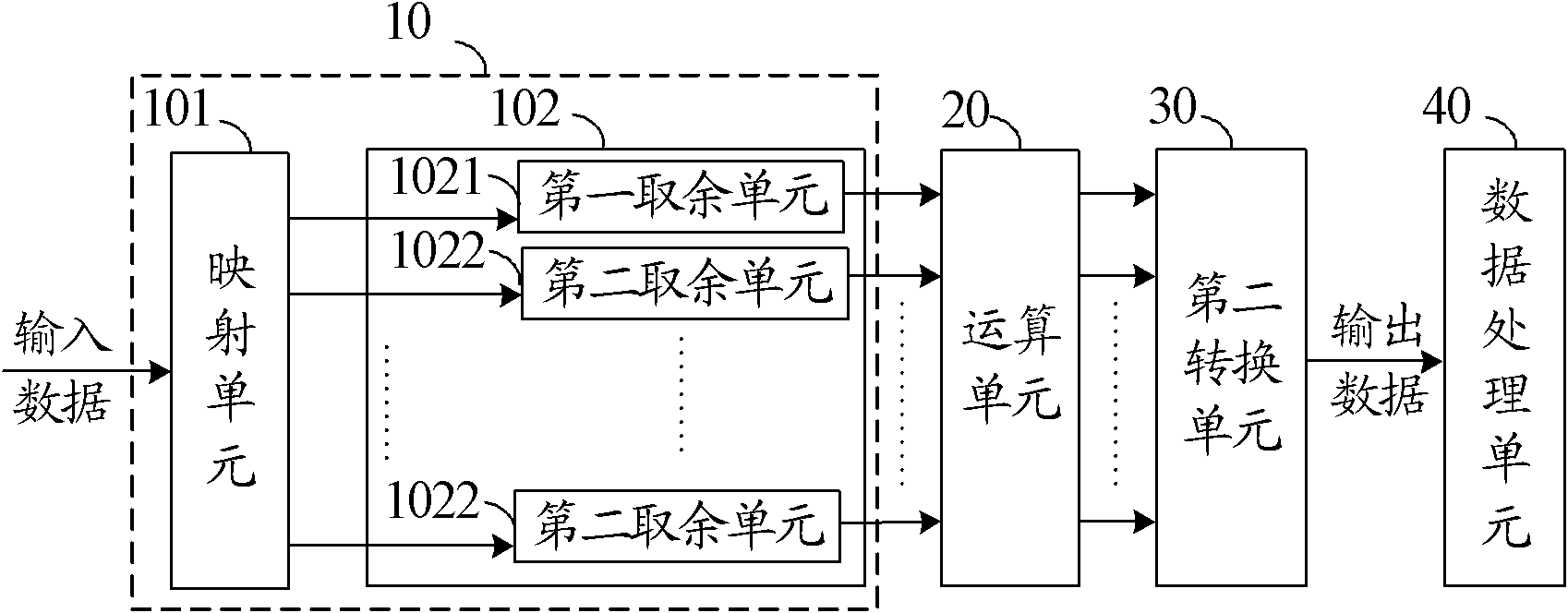

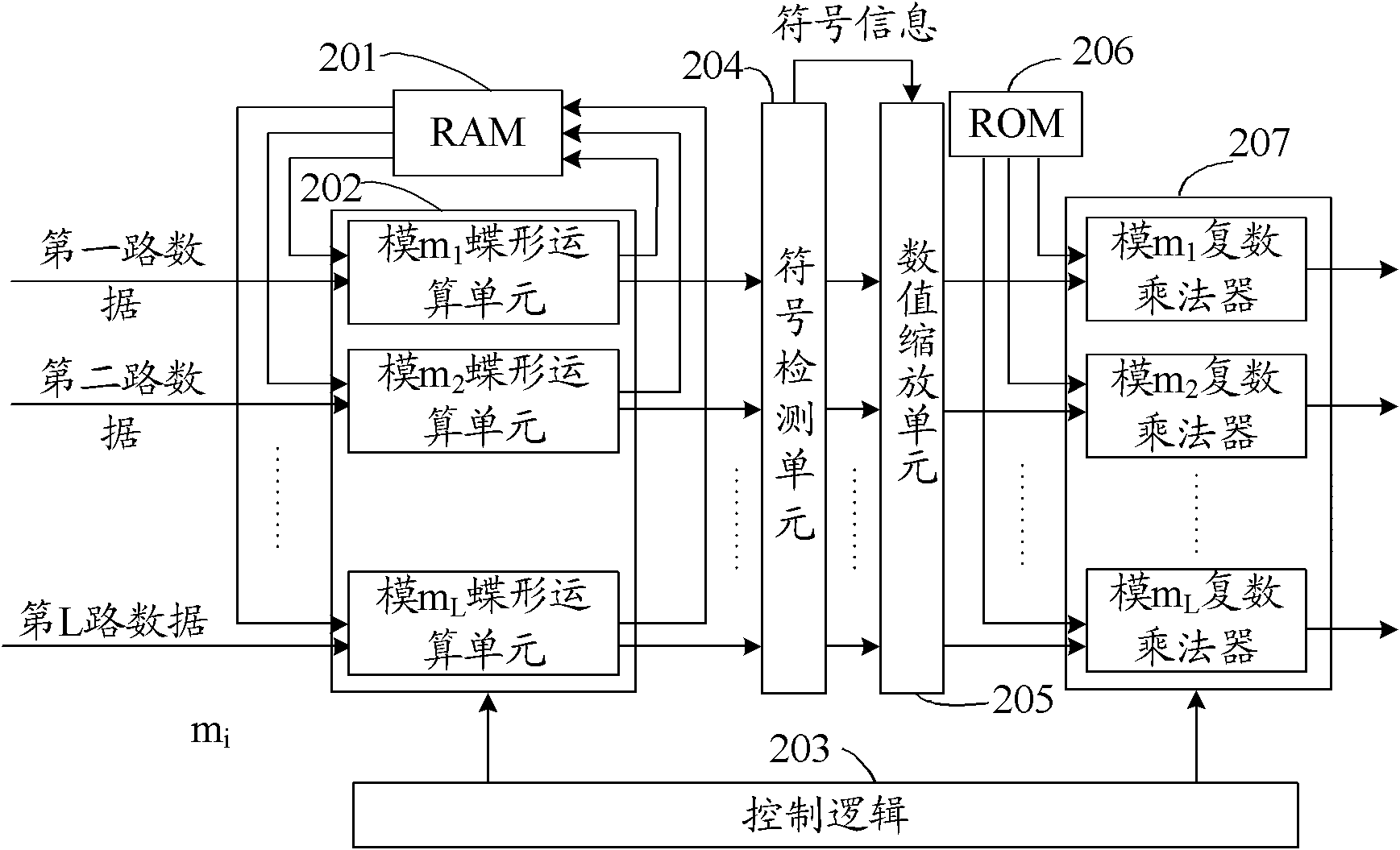

Data processing method and system

ActiveCN102043760AReduce processing timeShorten the pathComplex mathematical operationsData processing systemComputer science

The embodiment of the invention discloses a data processing system and method which are applied in the technical field of data processing. In the data processing system of the embodiment in the invention, a first conversion unit utilizes multiple remainder groups which are mutually prime numbers to convert the input data represented by binary weight values to L-path conversion data represented bythe residue number system; a computing unit performs Fourier operation on the L-path conversion data independently, a second conversion unit converts the calculated data to the output data represented by binary weight values again; and a data processing unit is used to perform data processing. In the system of the embodiment in the invention, the Fourier operation of each path of conversion data is independent; and the processed bits of the data represented by the residue number system are fewer, thus the calculated path is shortened relatively, the data processing time is reduced and the working efficiency of the system can be increased.

Owner:SHANGHAI HUAWEI TECH CO LTD

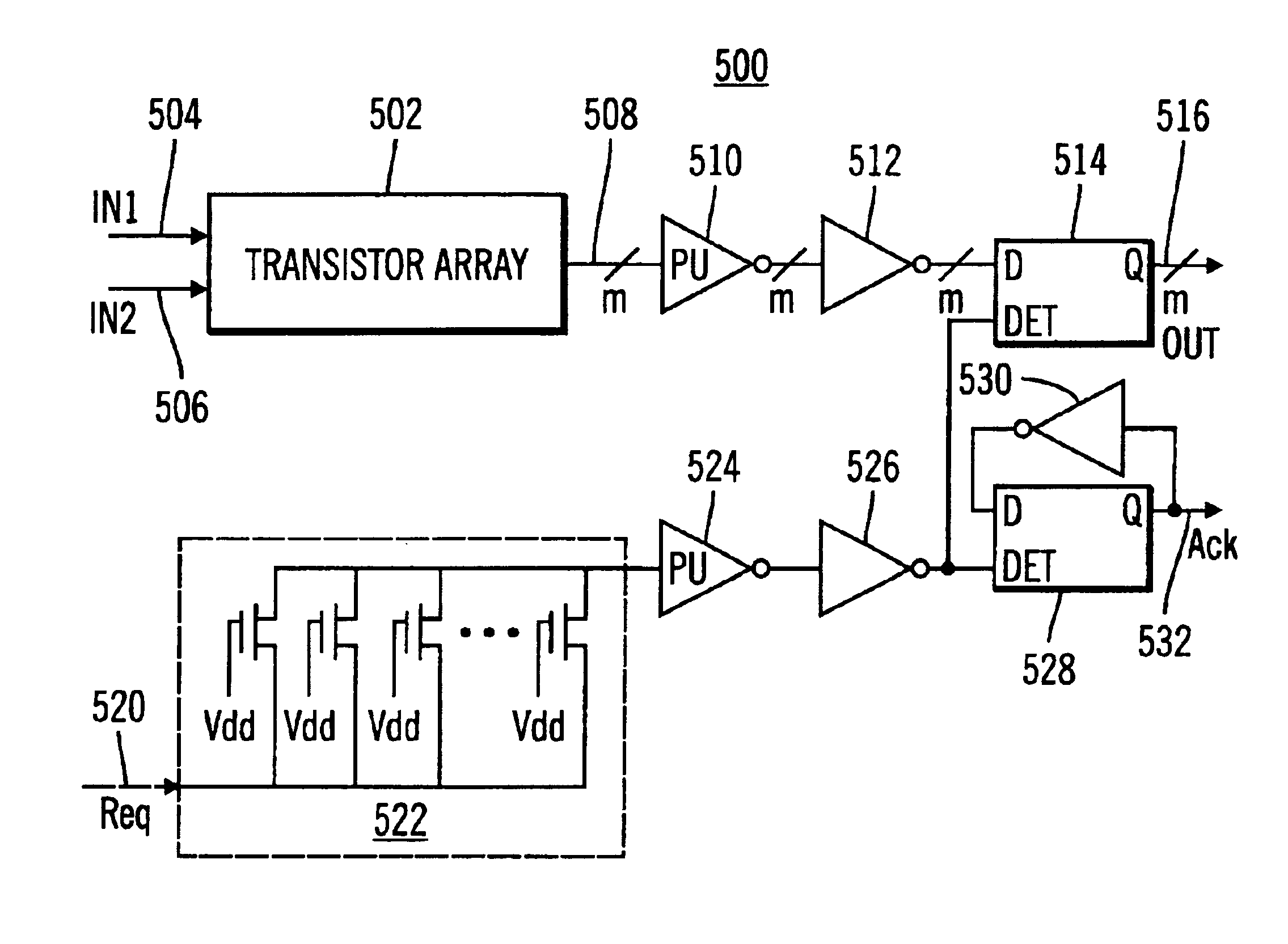

Self-timed digital processing circuits

ActiveUS6959315B2Reduce power consumptionIncrease speedCode conversionComputations using residue arithmeticPropagation delayOne-hot

A self-timed data processing circuit module is provided. Data is provided to the data processing circuit along with a Req handshaking input. The data processing circuit has an isochronous processing delay for all data inputs. An example of a data processing circuit with isochronous processing delay is a One Hot Residue Number System arithmetic processing circuit. The data processing circuit processes the input data while the Req input propagates through a delay circuit that has substantially the same processing delay as the data processing circuit. Thus, the propagation delay of the Req signal is substantially equal to the data processing circuit's processing time. This allows the output of the delay circuit to be used to both latch the output of the data processing circuit and provide a “data ready” output.

Owner:STMICROELECTRONICS SRL

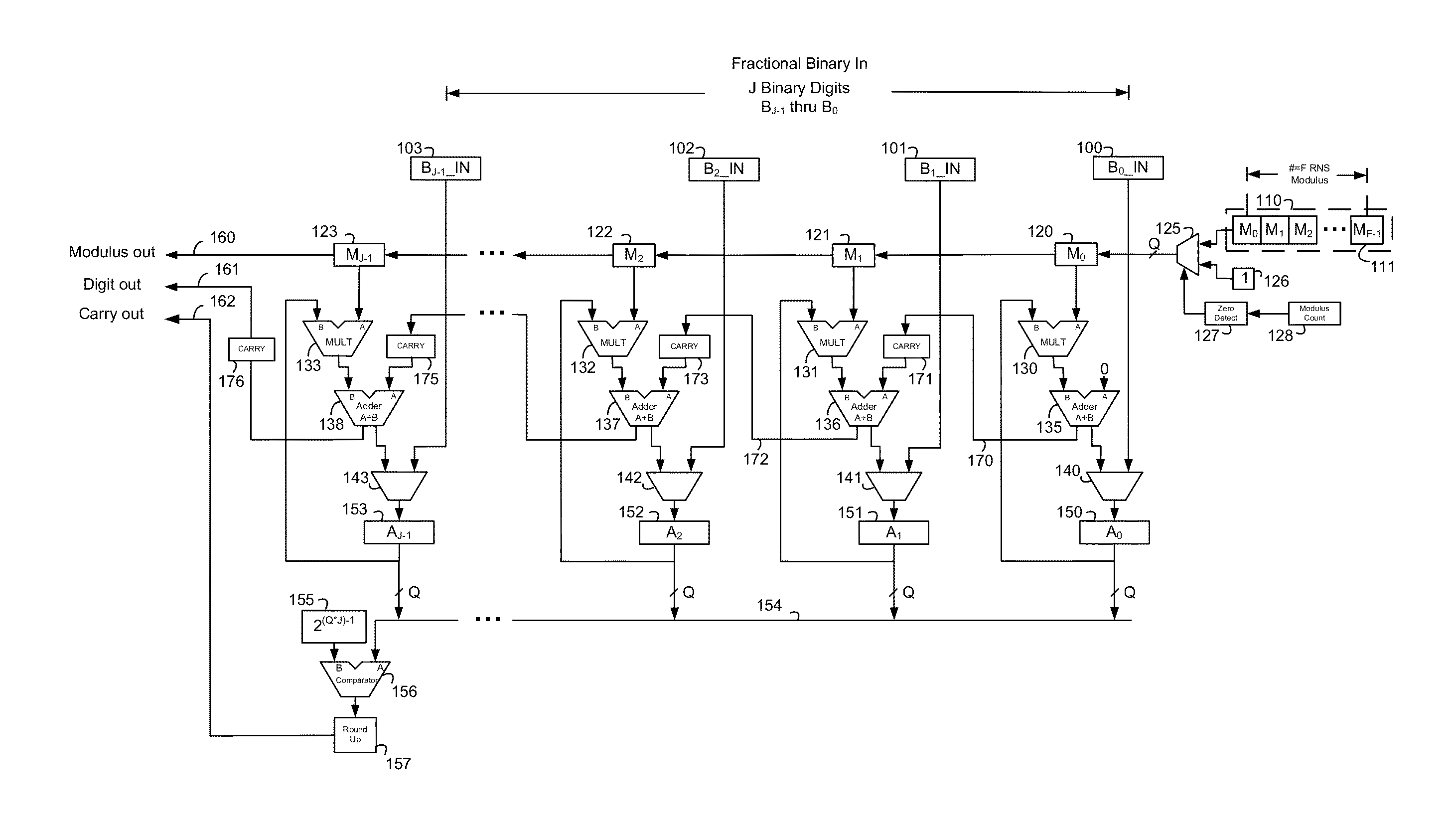

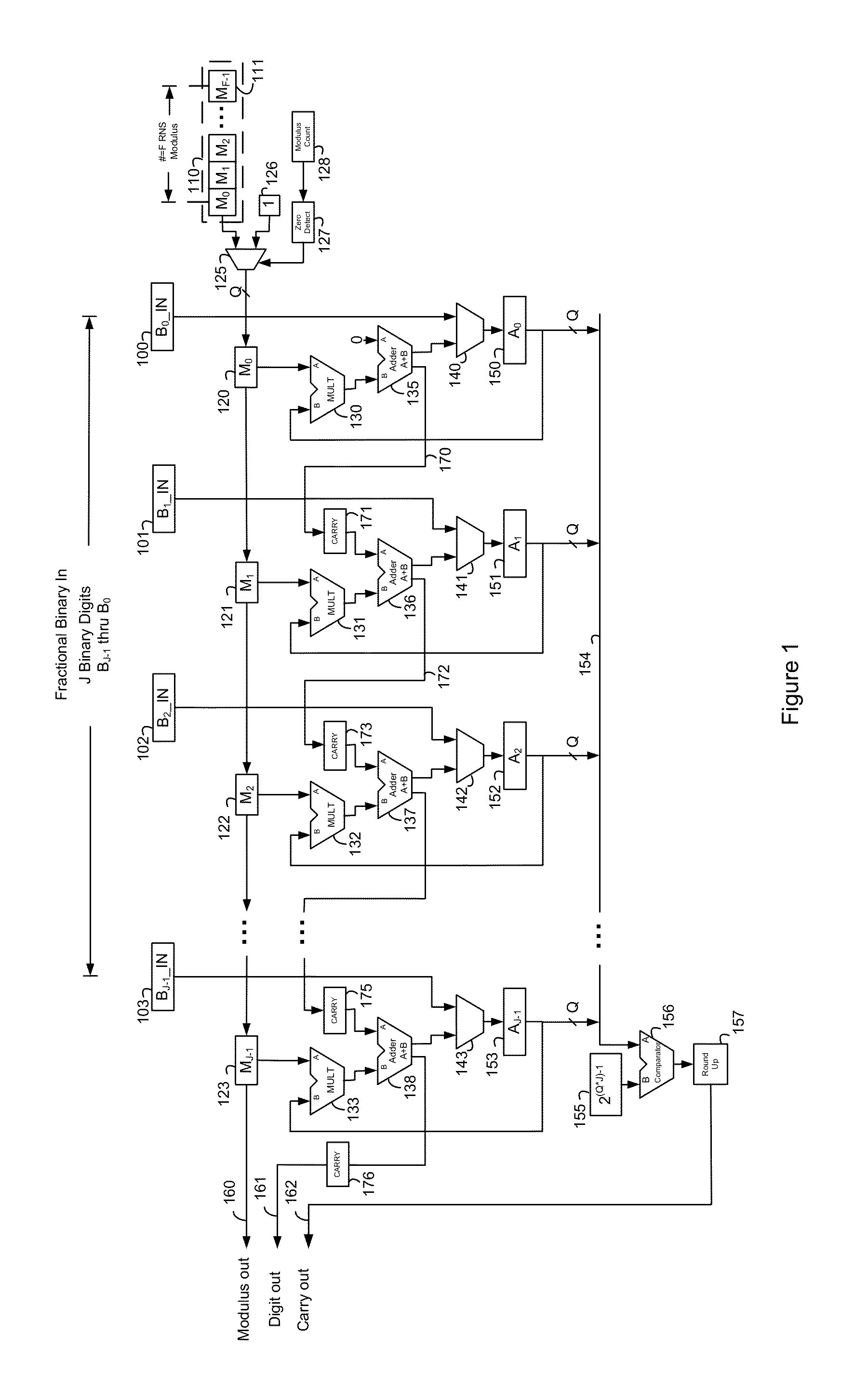

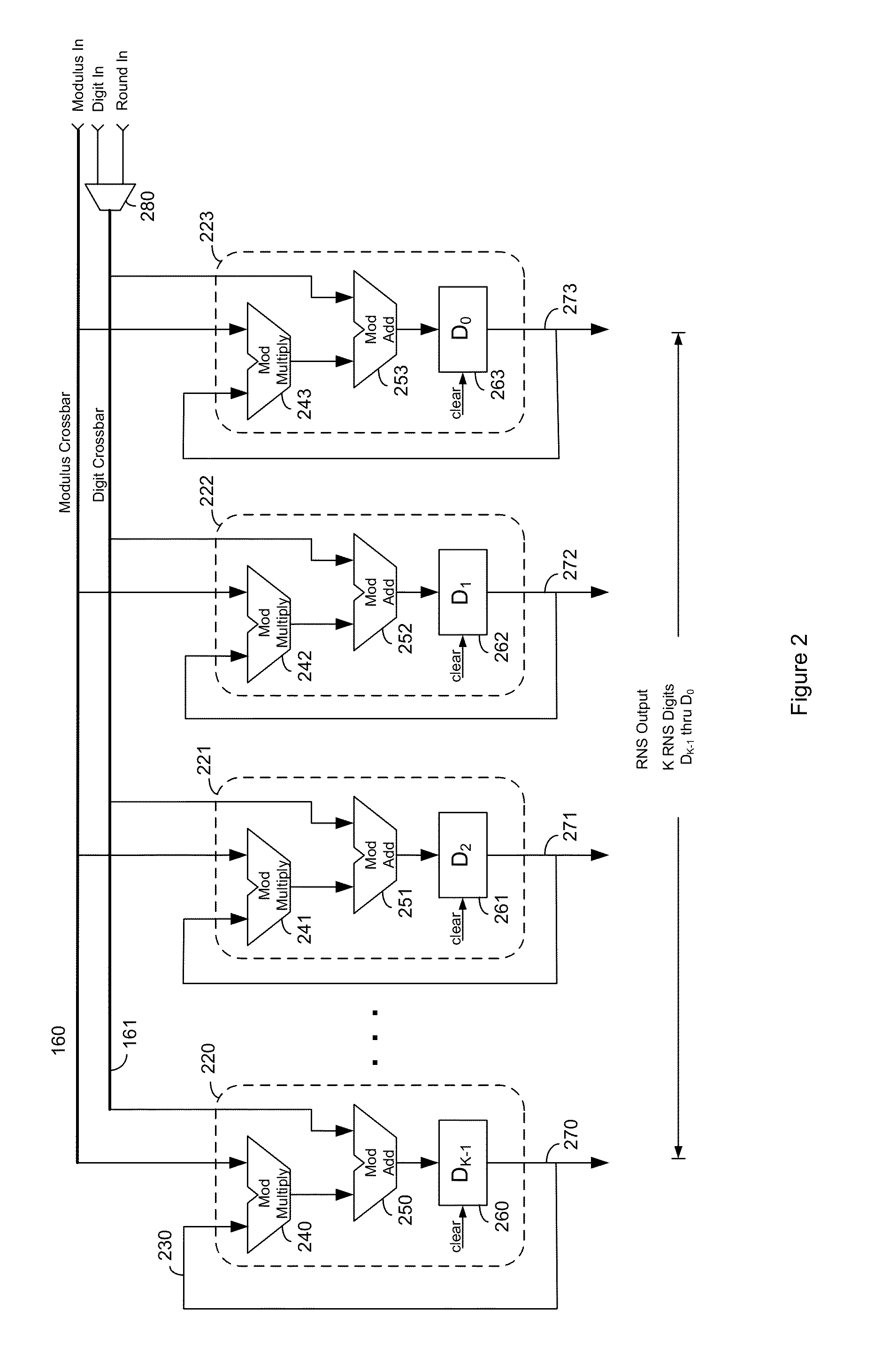

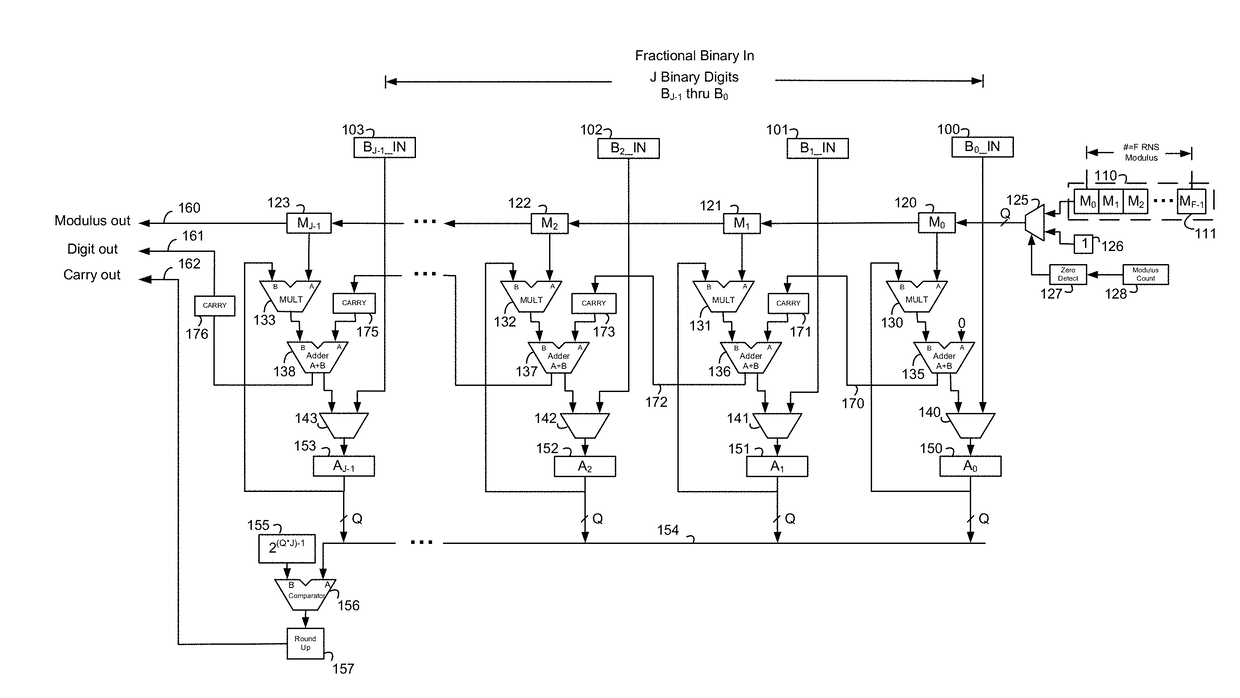

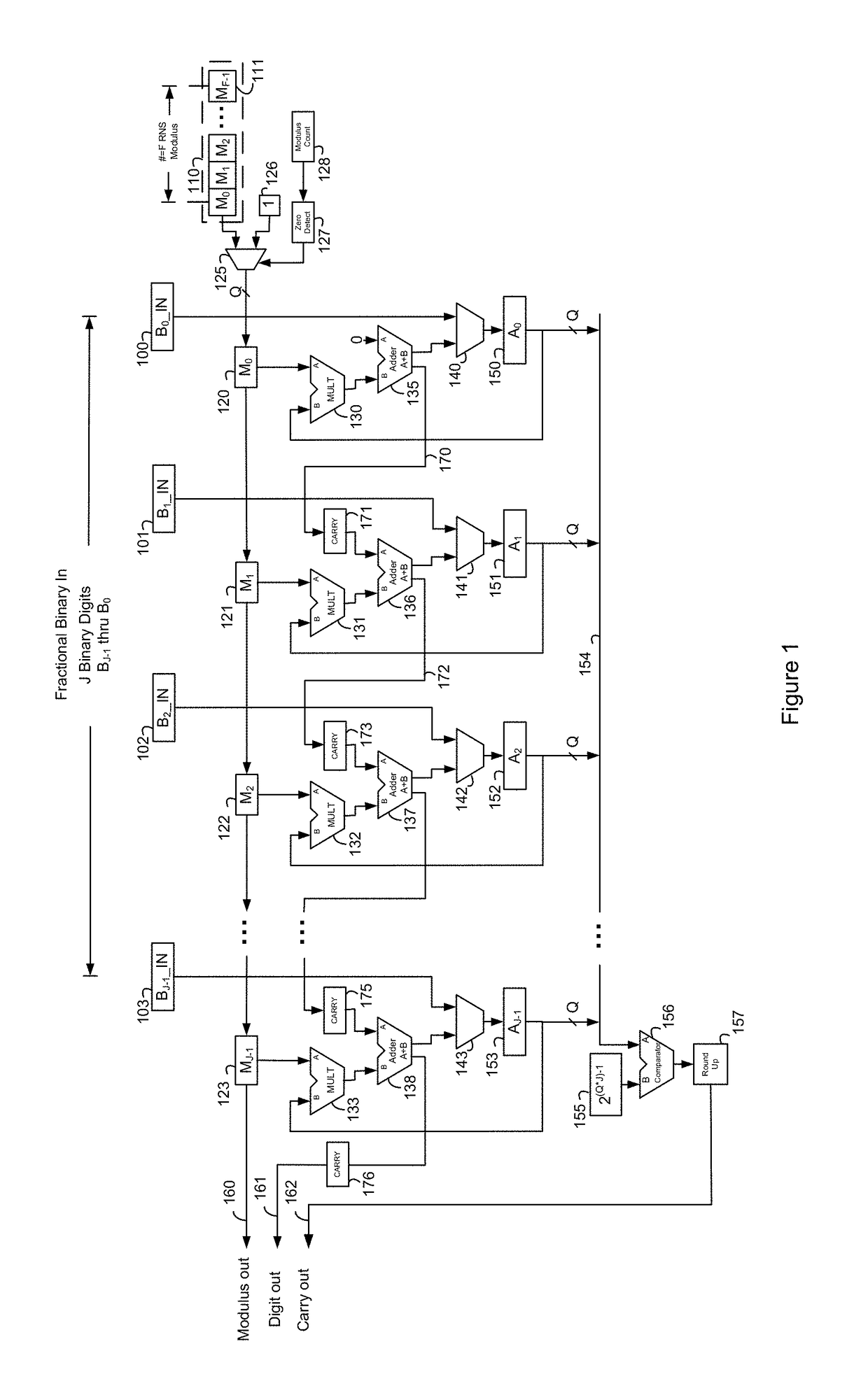

System and method for improved fractional binary to fractional residue converter and multipler

Methods and systems for residue number system based ALUs, processors, and other hardware provide the full range of arithmetic operations while taking advantage of the benefits of the residue numbers in certain operations.

Owner:OLSEN IP RESERVE

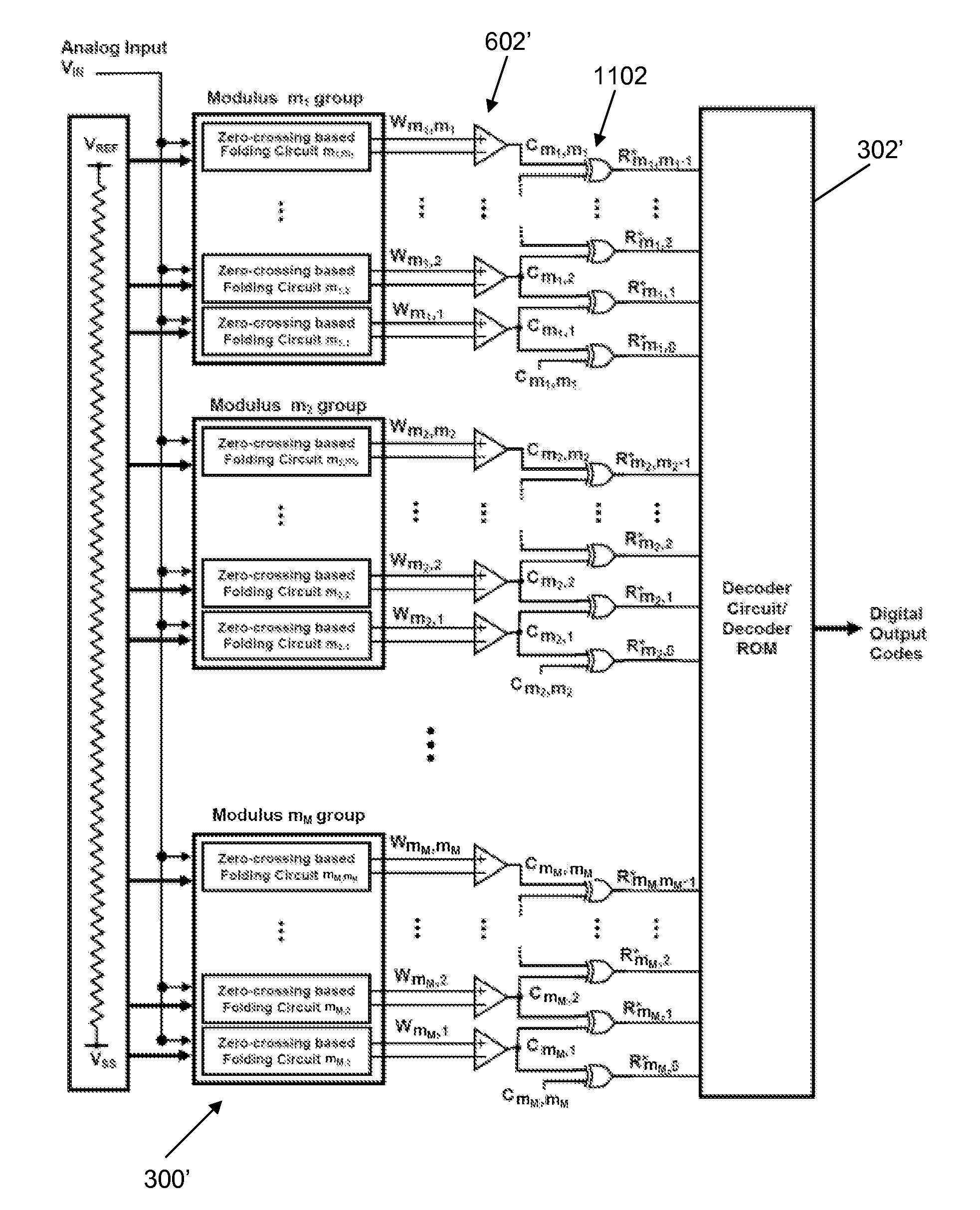

System for rns based analog-to-digital conversion and inner product computation

InactiveUS20140139365A1Improve accuracyReduce the numberElectric signal transmission systemsDigital data processing detailsComputer scienceComparator

A system is proposed for forming the inner product of an input signal having a number of signal entries, with a pre-known vector. Each signal entry is represented in an RNS format. The residue for each modulus is represented as a string in which the number of components taking a first value is equal to the residue. Corresponding components of the strings for different input entries are used to obtain a summation value, and the summation values are accumulated. Since the components of the string are not associated with weight values, the accumulation of the summation values can be performed without using a scaling accumulator. Furthermore, an ADC is proposed which uses the input signal to generate an RNS representation of the signal based on a plurality of moduli. For each modulus, there is a corresponding Residue Number System (RNS) converter which includes a number of zero-crossing-based folding circuits equal to the modulus, and a comparator for each zero-crossing based folding circuit. The output of the comparators is used to form the RNS representation. This ADC is efficient in terms of the number of comparators it uses. Optionally, the RNS representation may be converted into a different digital representation.

Owner:VUN CHAN HUA +1

Digital generation of a chaotic numerical sequence

ActiveUS7937427B2Random number generatorsComputations using residue arithmeticNumbering systemChinese remainder theorem

Owner:HARRIS CORP

Spread spectrum communications system and method utilizing chaotic sequence

ActiveUS7974413B2Minimize the differenceMultiplex code generationSecuring communicationNumbering systemCommunications system

A method is provided for generating a coherent chaotic sequence spread spectrum communications system. The method includes phase modulating a carrier with information symbols. The method also includes generating a string of discrete time chaotic samples. The method further includes modulating the carrier in a chaotic manner using the string of discrete time chaotic samples. Each of the discrete time chaotic samples has a shorter sample time interval than the duration of the information symbols. The generating step includes selecting a plurality of polynomial equations. The generating step also includes using residue number system (RNS) arithmetic operations to respectively determine solutions for the polynomial equations. The solutions are iteratively computed and expressed as RNS residue values. The generating step further includes determining a series of digits in the weighted number system based on the RNS residue values. The method further includes synchronizing the chaos generated at the receiver with that generated at the transmitter without periodic transfer of state update information.

Owner:HARRIS CORP

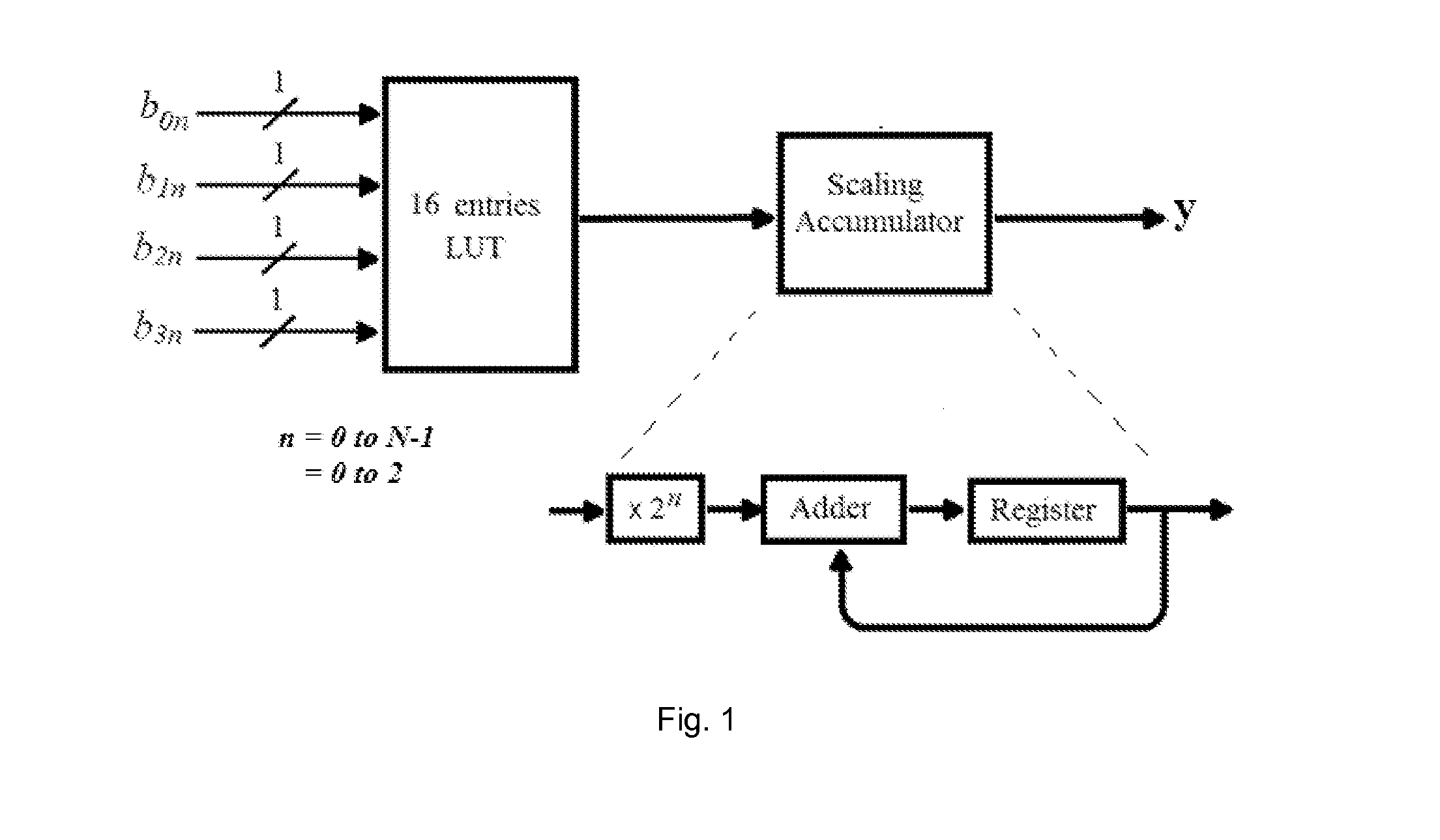

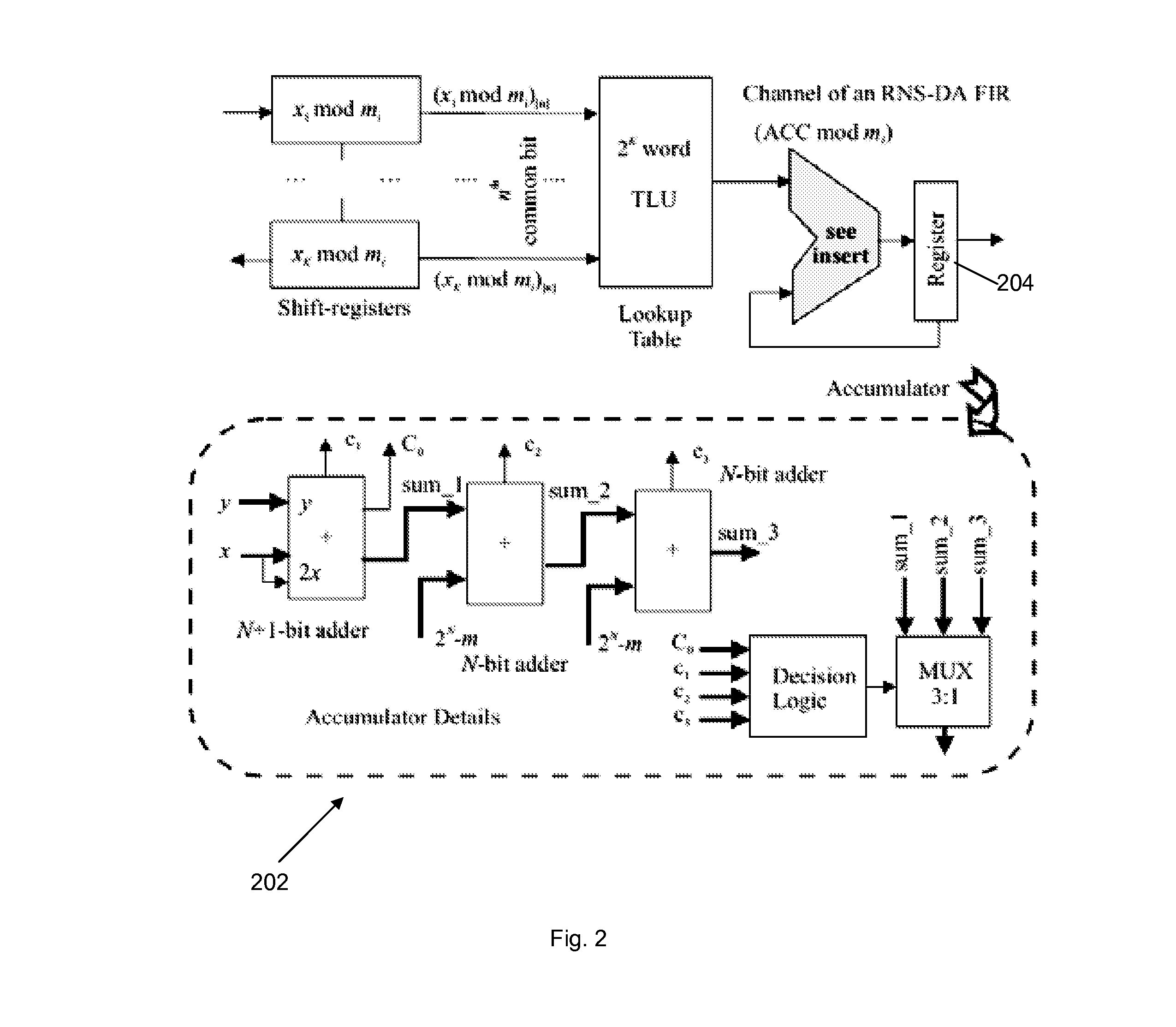

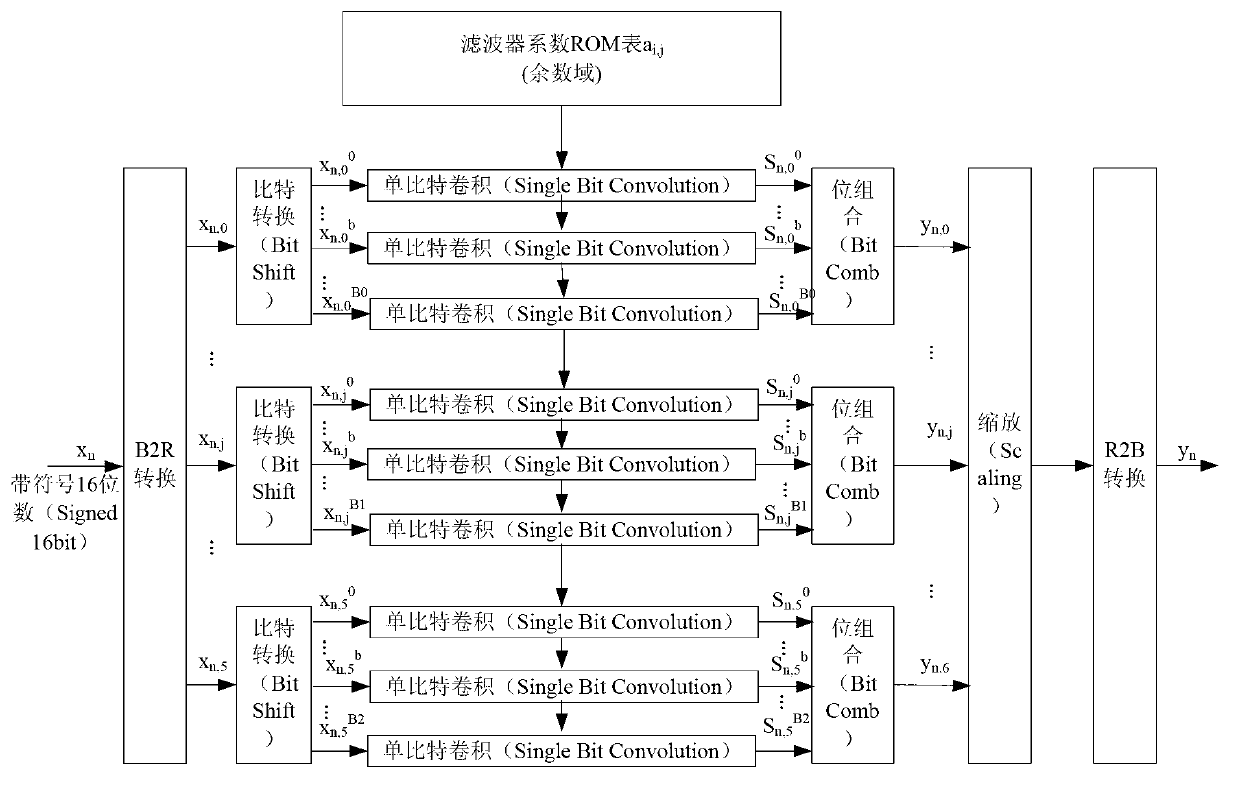

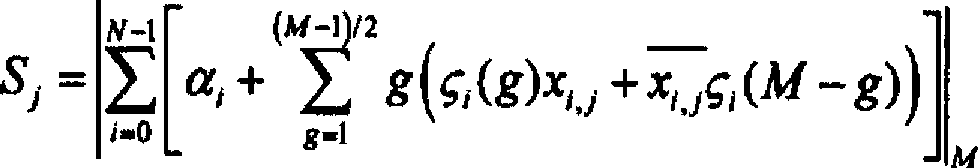

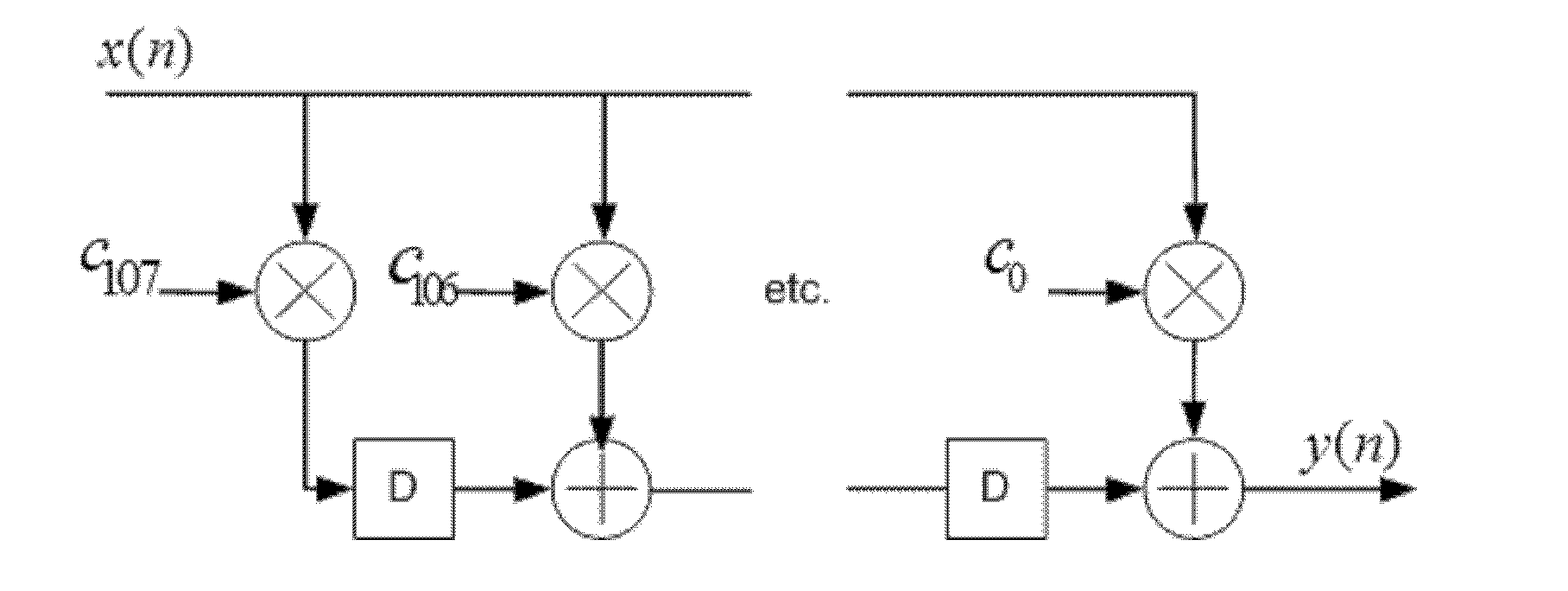

DA-RNS (distributed arithmetic-residue number system) algorithm based FIR (finite impulse response) filter realizing method

ActiveCN103001605AReduce areaReduce power consumptionDigital technique networkChinese remainder theoremLow resource

The invention relates to a DA-RNS (distributed arithmetic-residue number system) algorithm based FIR (finite impulse response) filter realizing method. The DA-RNS algorithm based FIR filter realizing method includes steps of firstly, subjecting filter input and filter coefficient to conversion from decimal weighting system to remainder non-weighting system by means of step-by-step table lookup; secondly, decomposing filter input into a single-byte mode; thirdly, subjecting the filter input and the filter coefficient to single-byte convolution operation; fourthly, scaling the filter input after remainder of the filter input is subjected to convolution operation under the remainder non-weighting system; and fifthly, restoring the remainder to decimal system by means of China remainder theorem. Compared with the prior art, the DA-RNS algorithm based FIR filter realizing method has the advantages of low resource consumption, high throughput and the like.

Owner:TONGJI UNIV

System and method for improved fractional binary to fractional residue converter and multipler

ActiveUS9712185B2Code conversionComputations using residue arithmeticParallel computingTheoretical computer science

Methods and systems for residue number system based ALUs, processors, and other hardware provide the full range of arithmetic operations while taking advantage of the benefits of the residue numbers in certain operations.

Owner:OLSEN IP RESERVE

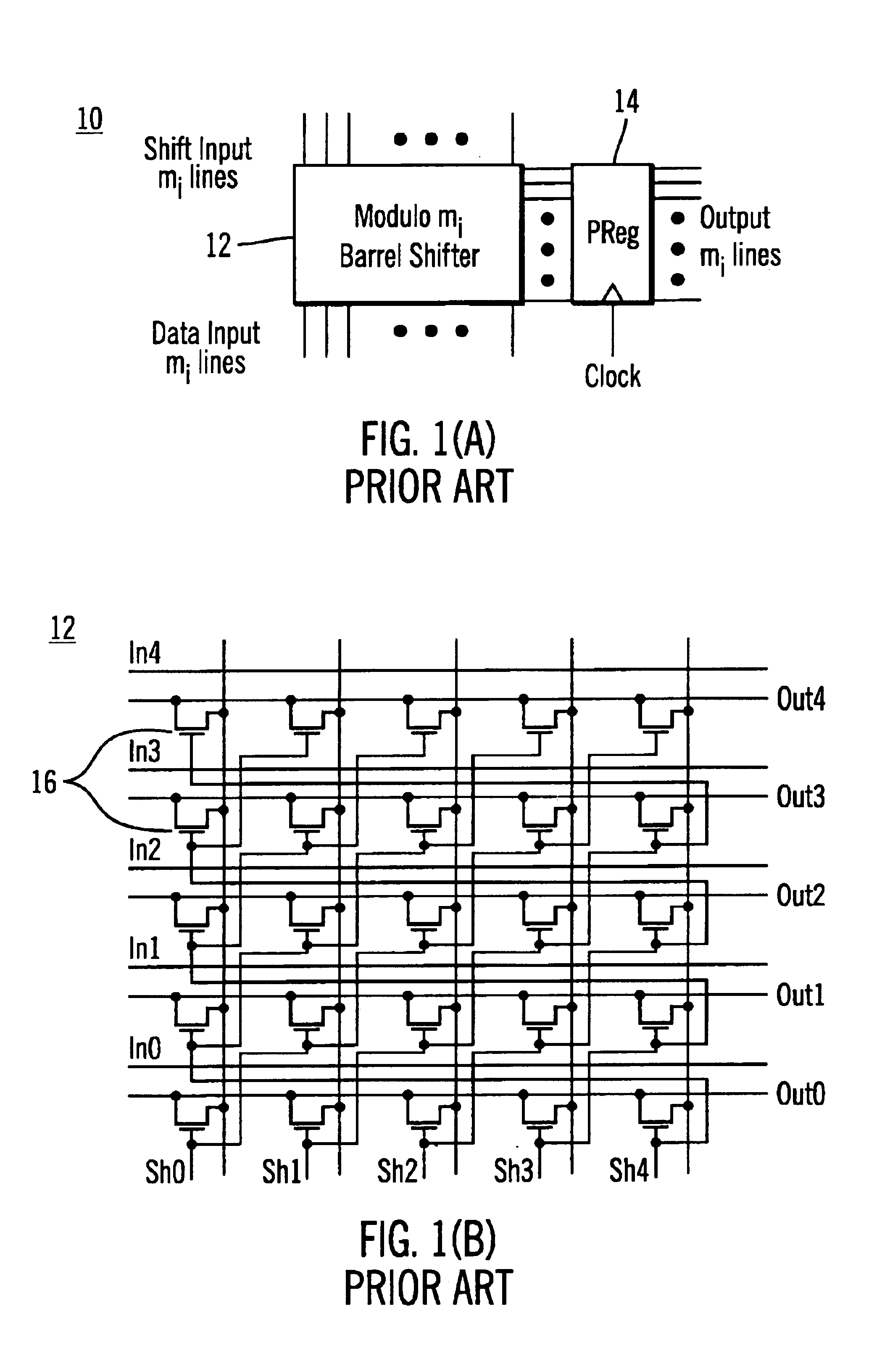

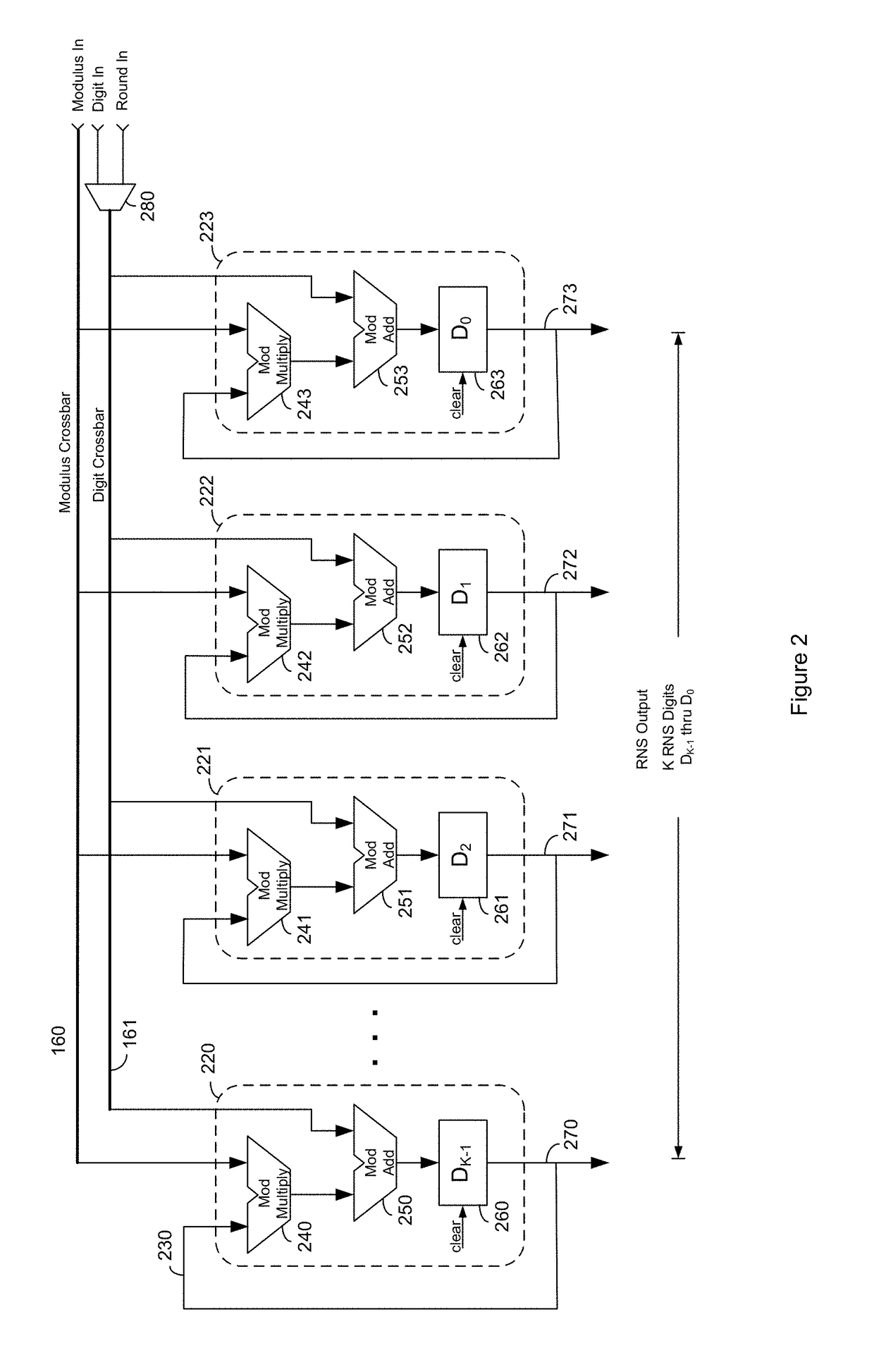

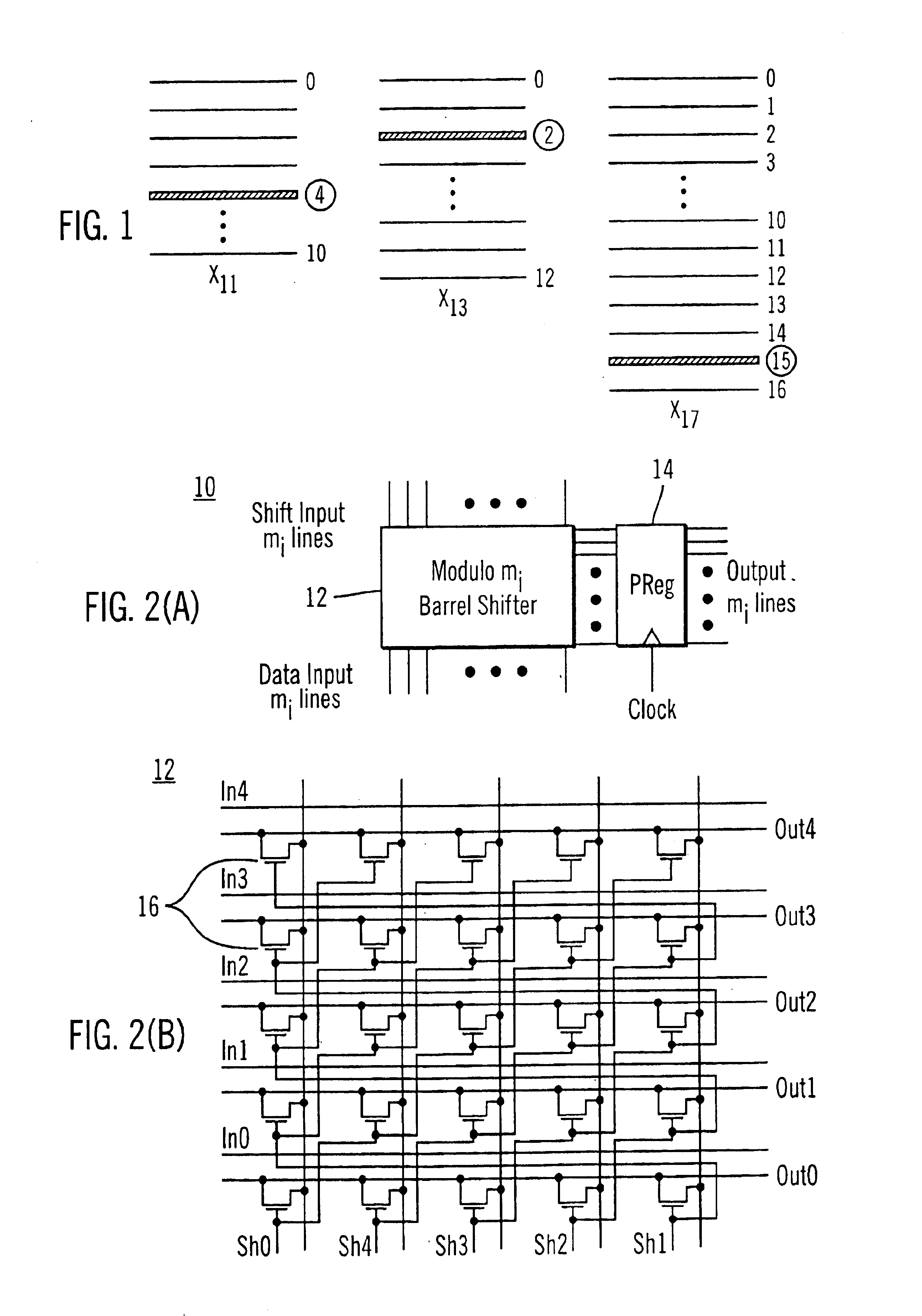

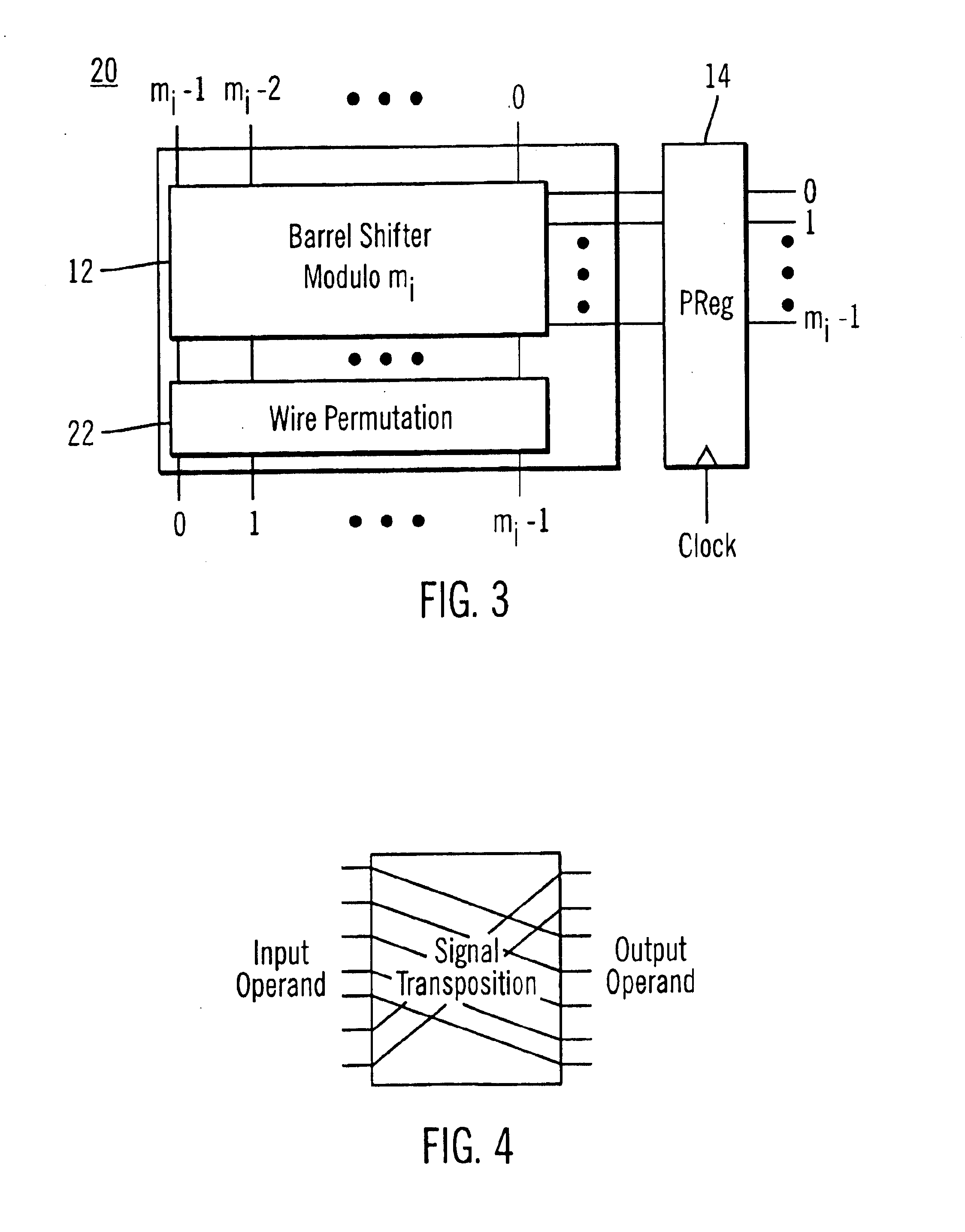

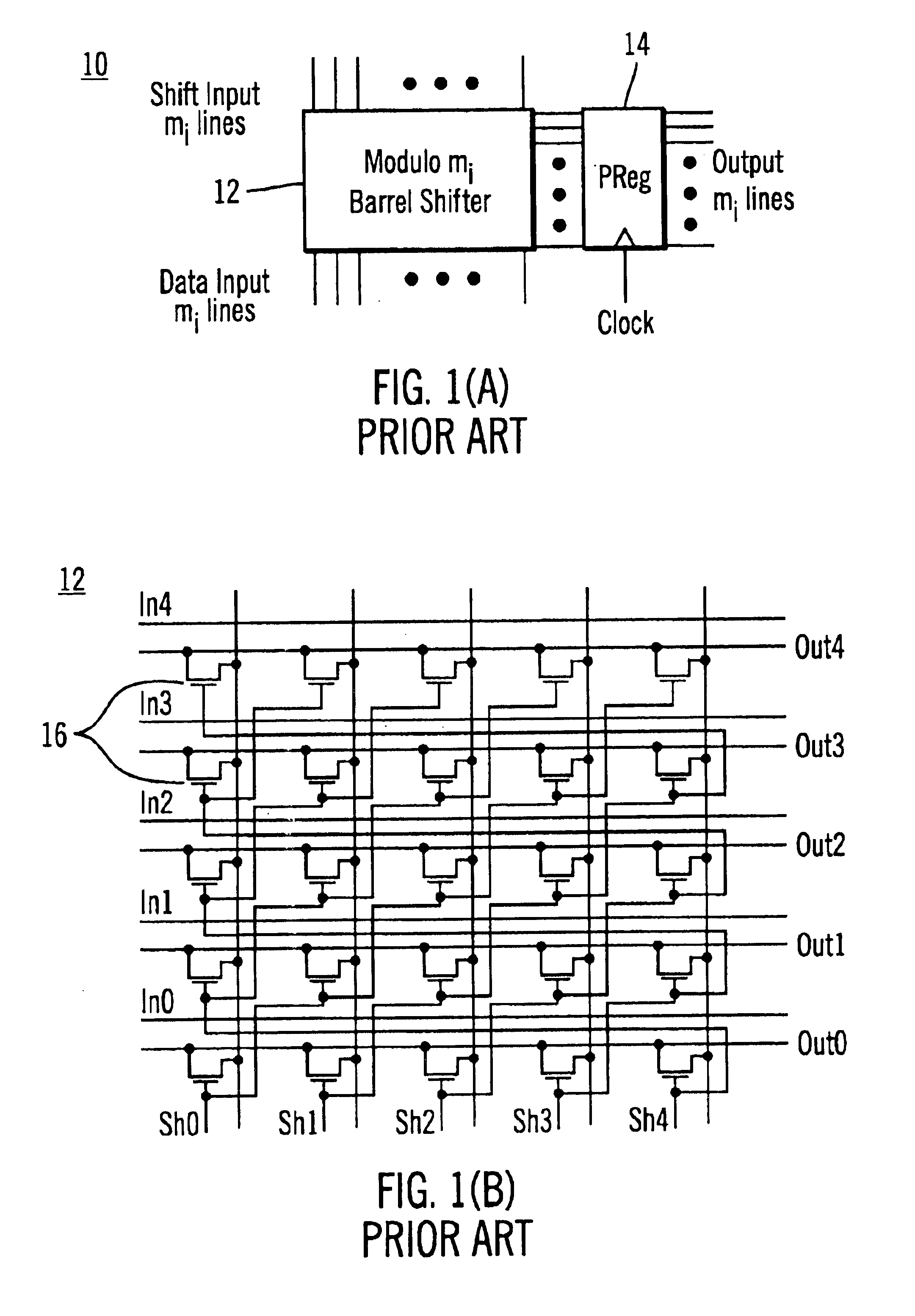

Arithmetic circuits for use with the residue number system

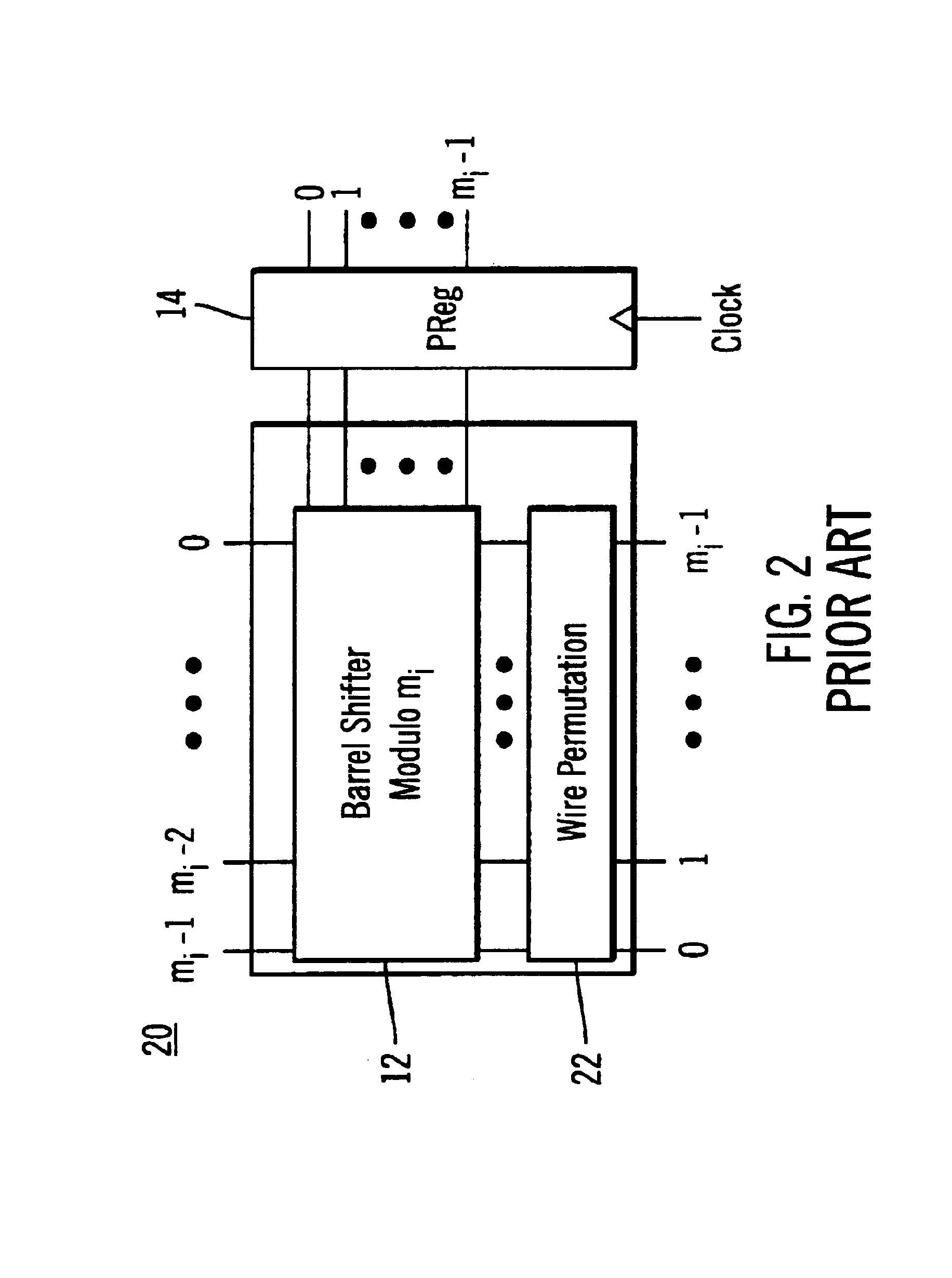

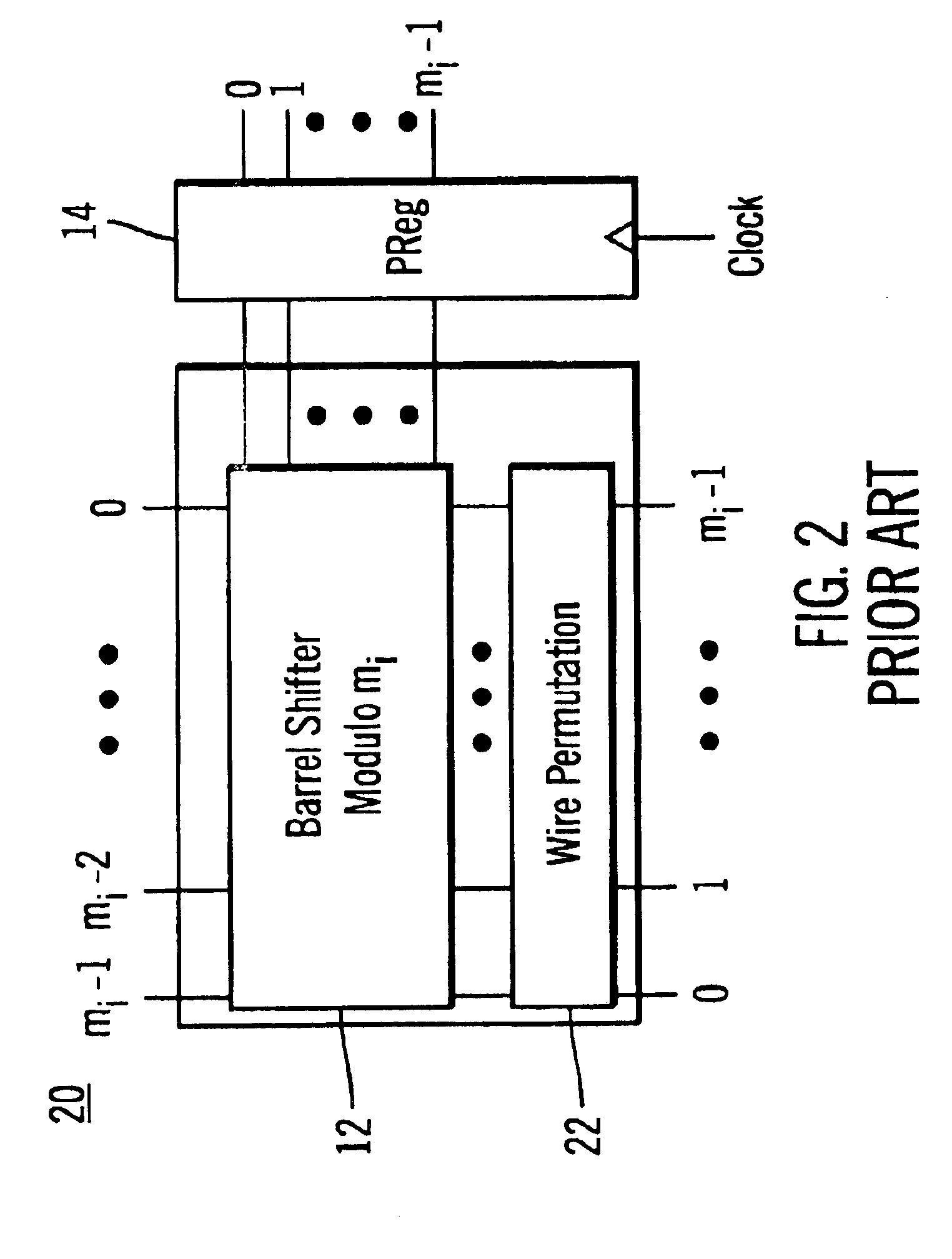

InactiveUS6898613B1Reduce power consumptionIncrease speedComputations using residue arithmeticData conversionDynamic storageScale unit

A modulo mi adder and a modulo mi,j scaling unit for use with an RNS. The adder includes a modulo mi barrel shifter, and a dynamic storage unit coupled to the barrel shifter to store the output of the barrel shifter. In a preferred embodiment, the dynamic storage unit includes one dynamic latch for each output line of the barrel shifter, with each of the dynamic latches including a clocked inverter in cascade with an inverter. One modulo mi,j scaling unit includes a modified modulo mi barrel shifter that performs both residue conversion and an arithmetic operation. The residue conversion is performed without using combinational logic. In one preferred embodiment, the modified barrel shifter performs the residue conversion though mi-mj additional columns that replicate normal columns for all modulo mi input lines that are congruent modulo mj. Another modulo mi,j scaling unit includes a barrel shifter-based arithmetic circuit, and a dynamic storage unit coupled to the arithmetic circuit to store the output of the arithmetic circuit.

Owner:STMICROELECTRONICS SRL

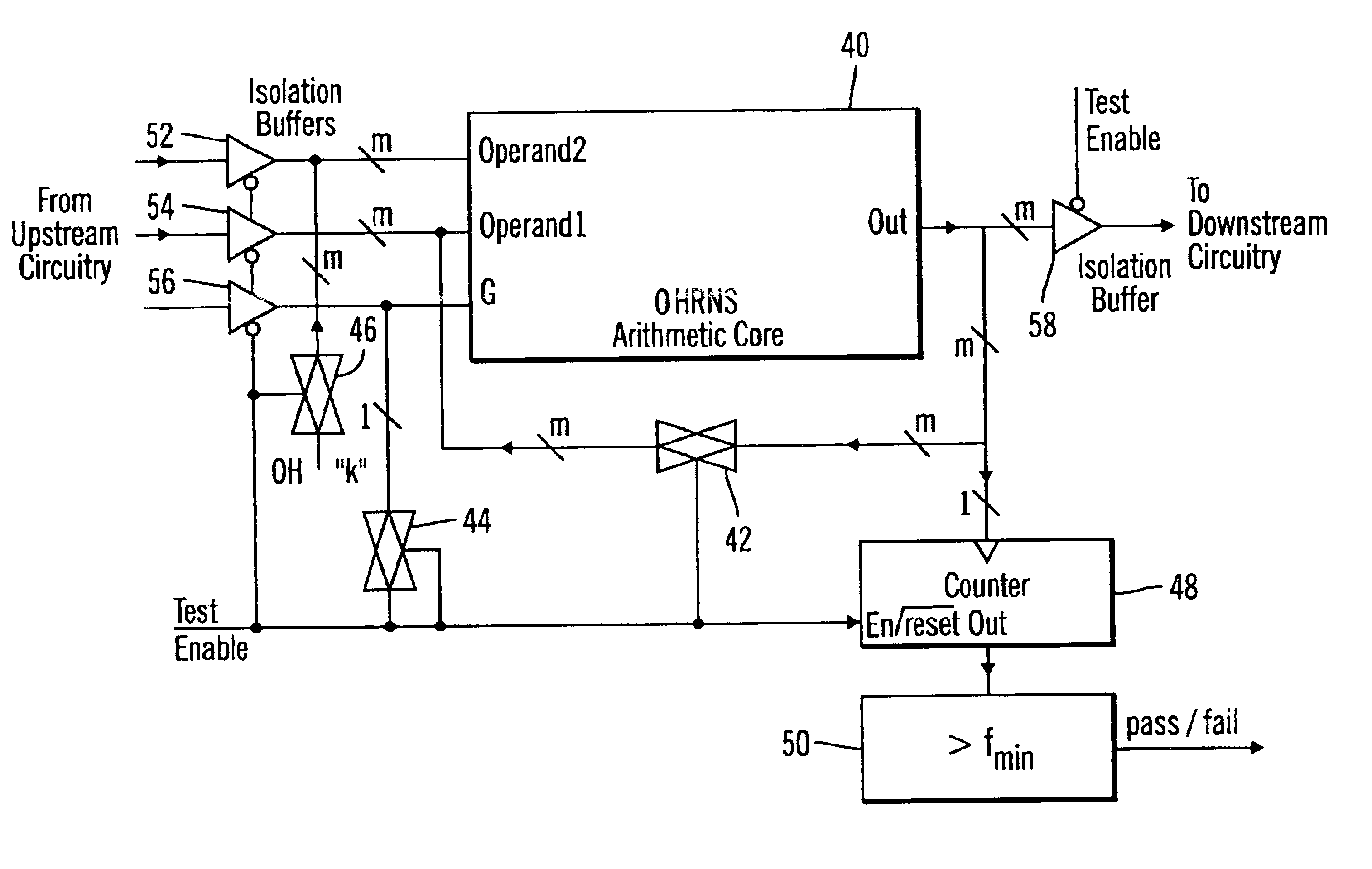

Residue number system arithmetic circuits with built-in self test

InactiveUS6886123B1Simple circuitElectronic circuit testingRecord information storagePropagation delayCircuit delay

An arithmetic circuit for use with an RNS is provided. The arithmetic circuit includes an arithmetic core, test circuitry, and logic circuitry. The arithmetic core performs an RNS arithmetic operation, and the test circuitry verifies proper circuit delay by inducing oscillation at the output of the arithmetic core during testing. The logic circuitry produces a pass / fail signal based on whether the oscillation frequency of the arithmetic core is at least equal to a minimum threshold value. In one preferred embodiment, the logic circuitry includes a counter that counts oscillations of the output of the arithmetic core during testing, and a comparator that compares the output of the counter after a predetermined test period with the minimum threshold value. Also provided is a method for testing the propagation delay of an RNS arithmetic circuit having an arithmetic core.

Owner:STMICROELECTRONICS SRL

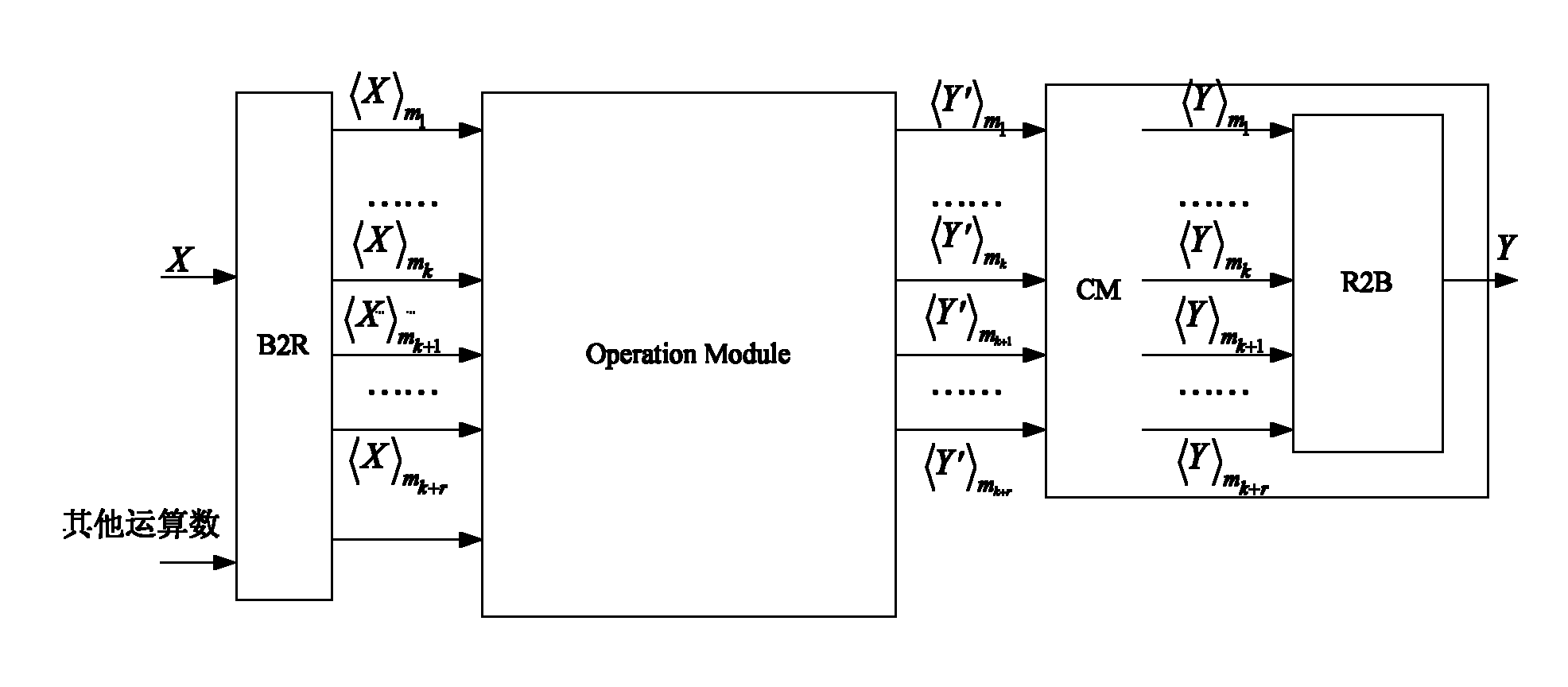

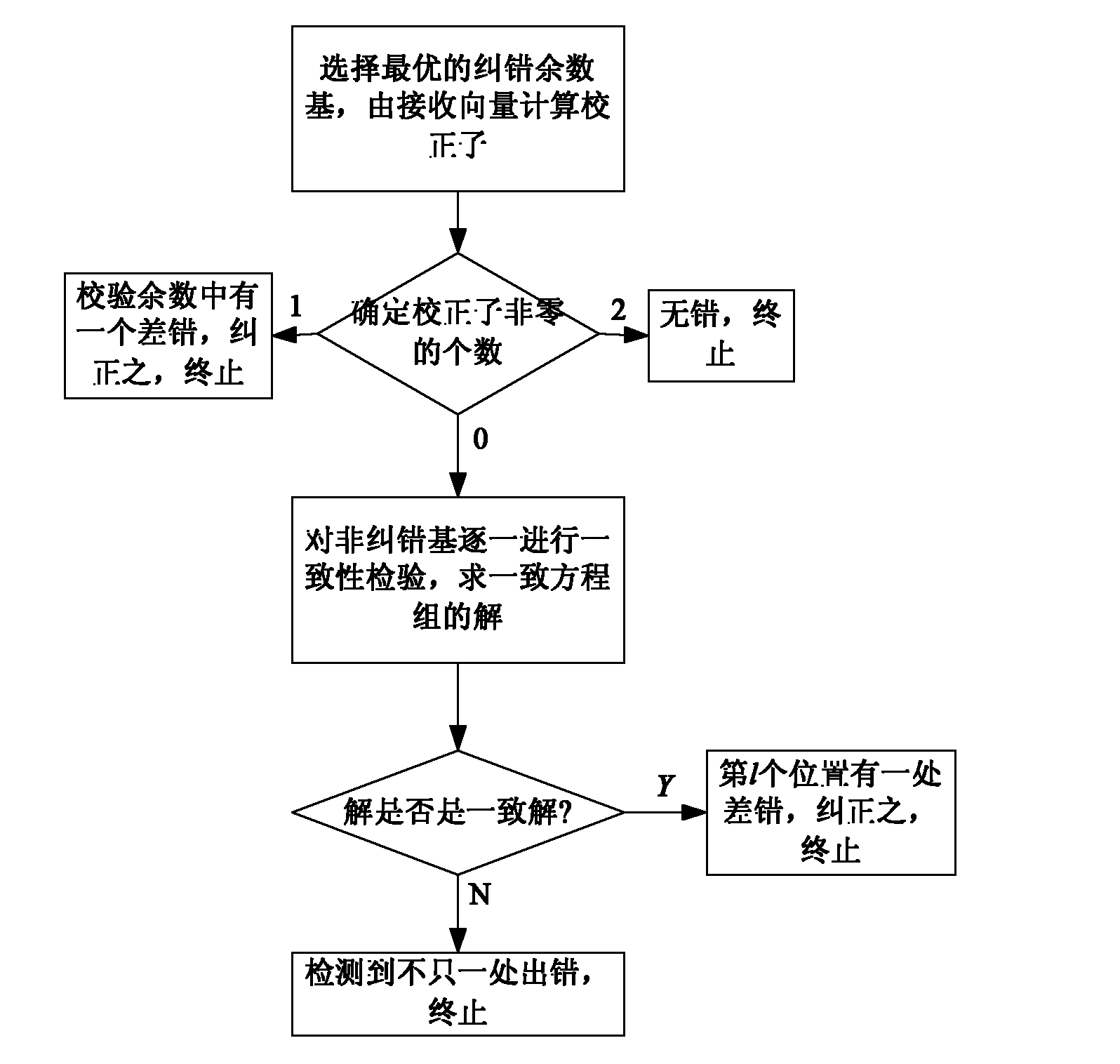

Redundant-residue-number-system-based irradiation-resisting reinforcing method and device

InactiveCN102163250AAbility to resist radiationSimple methodSpecial data processing applicationsOperandDatapath

The invention relates to a redundant-residue-number-system (RRNS)-based irradiation-resisting reinforcing method, which is characterized in that: the method is based on the reinforcing framework of an RRNS, and the redundant numbers of the RRNS can participate in operation. The method mainly comprises the following steps of: converting binary operands into the operands of the RRNS, performing a calculation and correcting errors. Due to the data route of a new RRNS-based design framework, the irradiation-resisting performance of the system is ensured, and the overhead of the system can be lowered compared with those of the conventional system.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

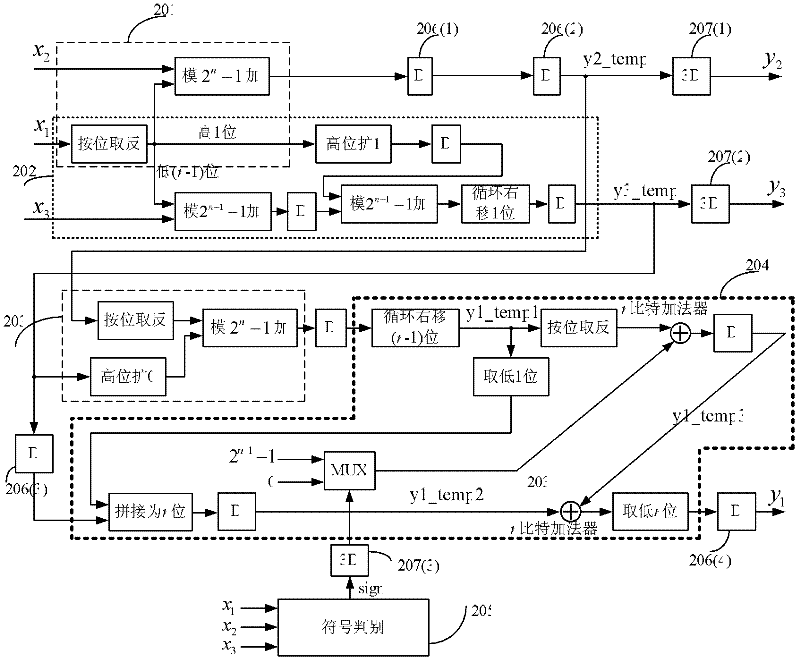

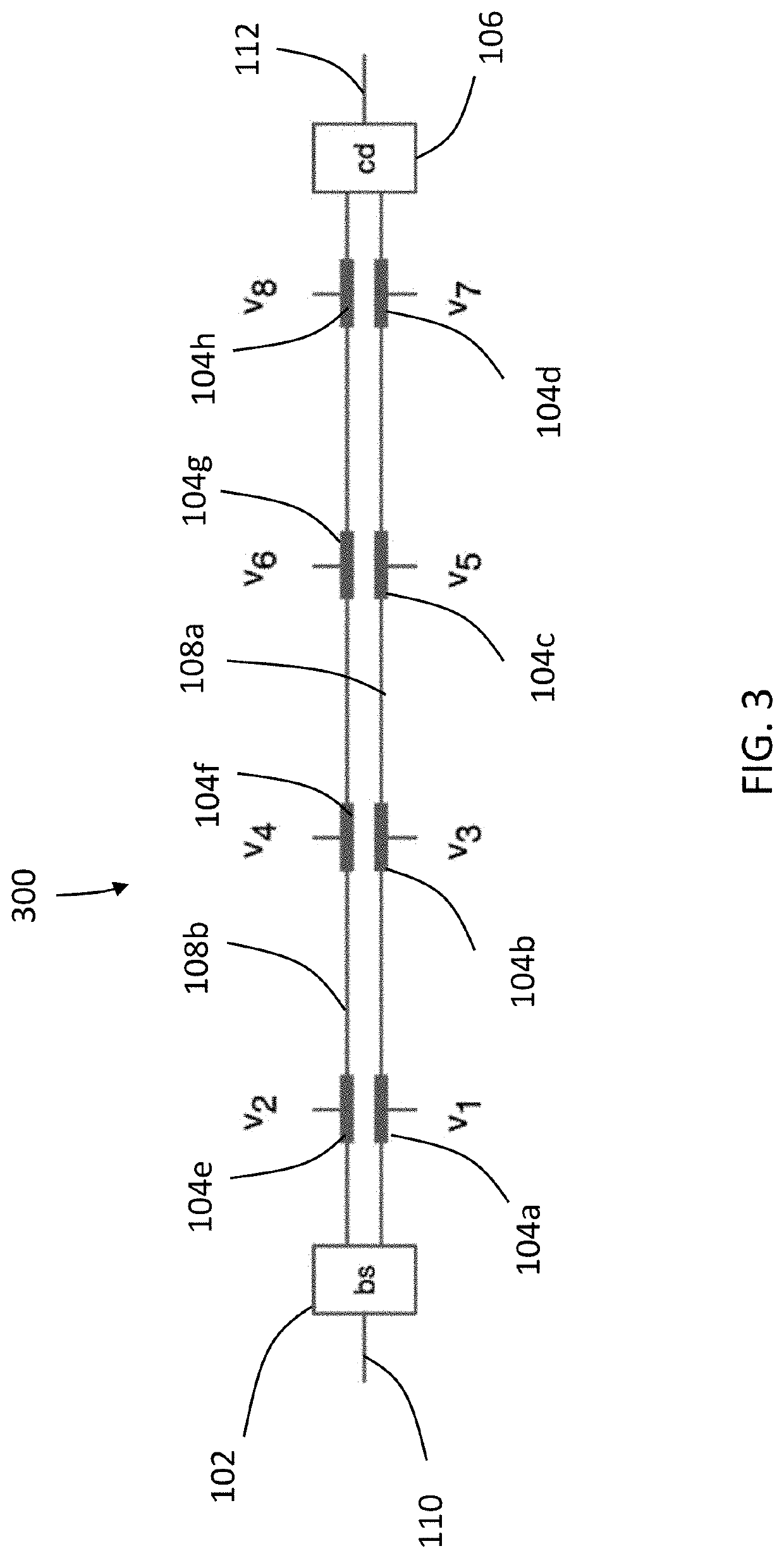

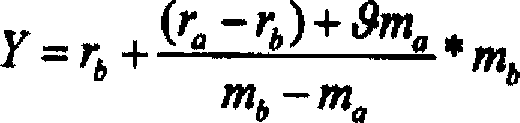

Backward conversion device and method of residue number system with bases of [2<n-1>,2<n+1>,2<n>] and [2<n-1>,2<n+1>,2<2n+1>]

InactiveCN102184159AModule Design ReuseAvoid the hassle of redesigningComplex mathematical operationsDigital signal processingComputer science

The invention discloses a backward conversion (R2B) device and method of a residue number system (RNS) with bases of M1=[2<n-1>,2<n+1>,2<n>] and M2=[2<n-1>,2<n+1>,2<2n+1>]. An integer of the RNS is converted into a binary integer. In the invention, according to the characteristics of M2 and M1, M1 and M2 have one common group of sub residue bases MS=[2<n-1>,2<n+1>], firstly, backward conversion of the MS is completed, and then backward conversions of M12=[2<2n-1>,2<n>] and M22=[2<2n-1>,2<2n+1>] are respectively completed, and results of the backward conversions are conversion results of M1 and M2. In addition, the form of M22 is similar to the form of MS, therefore, M22 is realized by adopting the structure similar to MS, the module design is better reused, and the trouble of repeated design is avoided. The invention plays a positive pole in application of the RNS with a base of M1 or M2 in a digital signal processing system.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

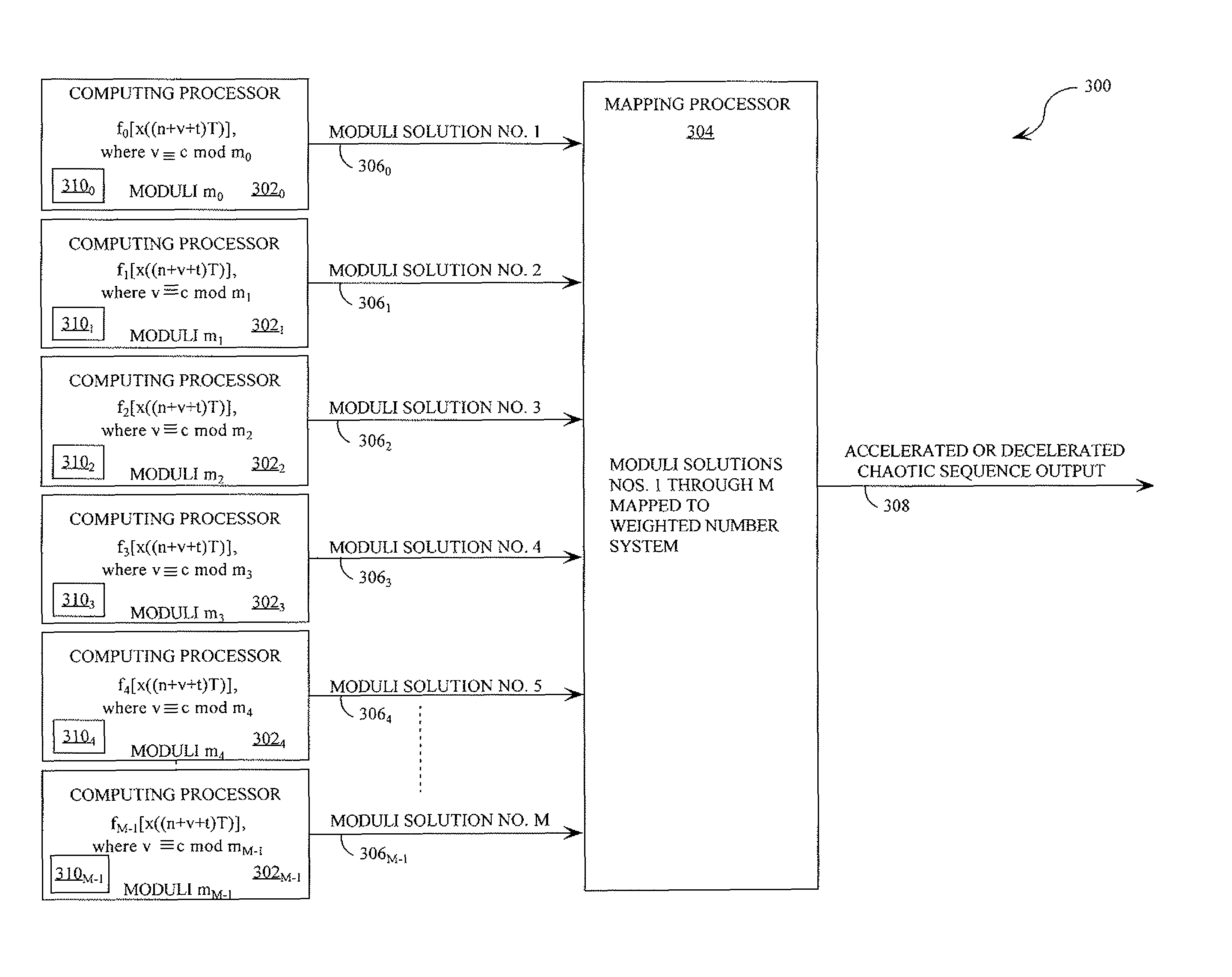

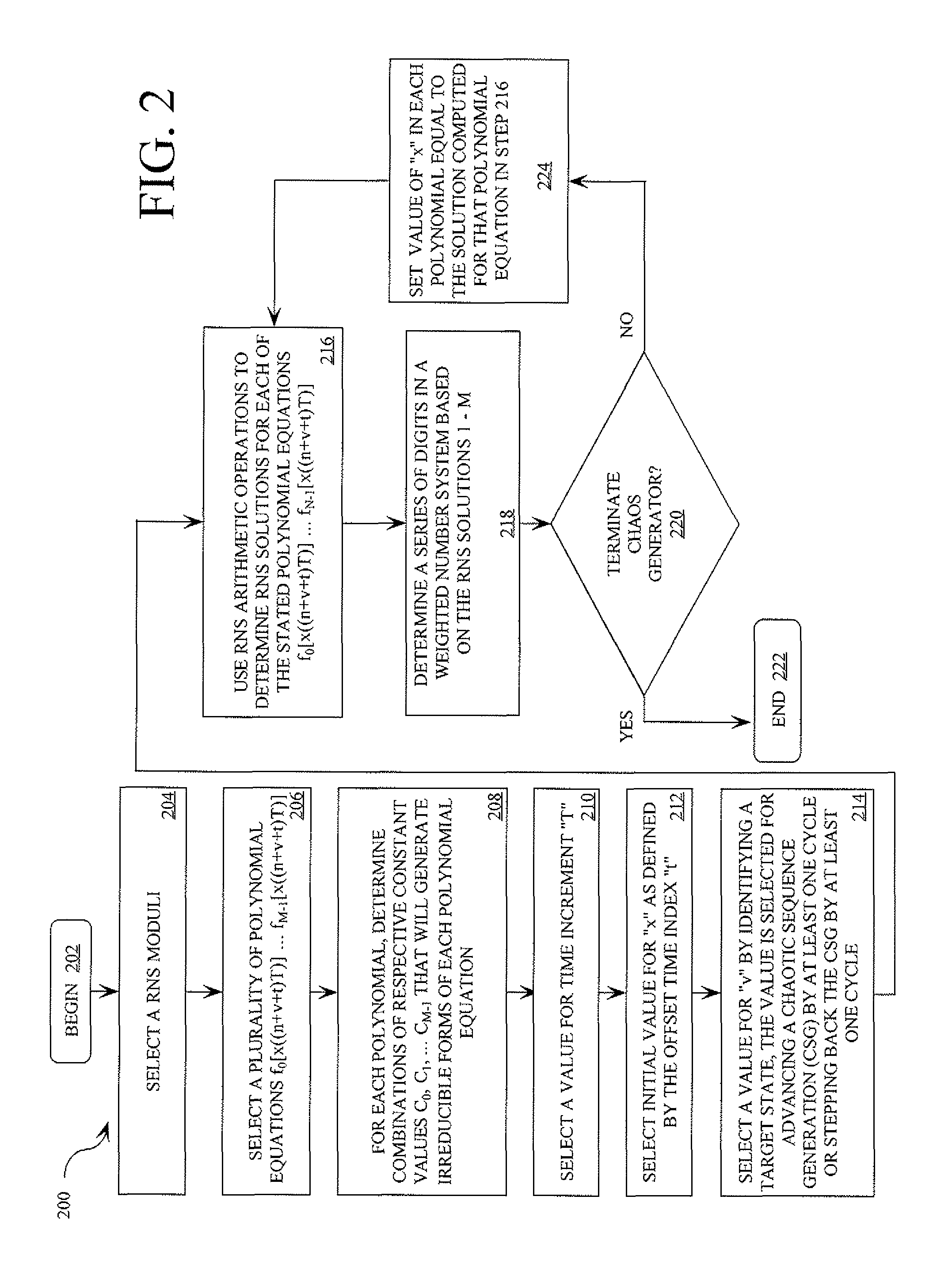

Digital generation of an accelerated or decelerated chaotic numerical sequence

ActiveUS8145692B2Random number generatorsDigital computer detailsNumbering systemTheoretical computer science

A method for generating an accelerated and / or decelerated chaotic sequence. The method involves selecting a plurality of polynomial equations constructed from an acc-dec variable v. The method also involves selecting a value for the acc-dec variable v for advancing or stepping back a chaotic sequence generation by at least one cycle at a given time. The method further involves using residue number system (RNS) arithmetic operations to respectively determine solutions for the polynomial equations using the acc-dec variable v. The solutions iteratively computed and expressed as RNS residue values. The method involves determining a series of digits in a weighted number system based on the RNS residue values.

Owner:HARRIS CORP

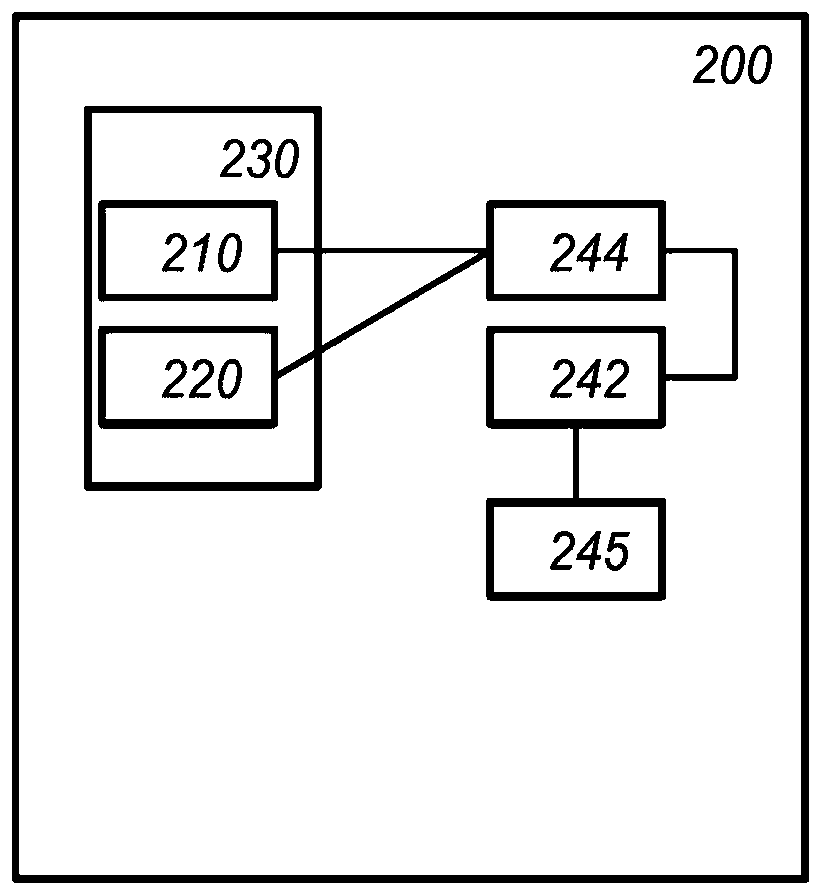

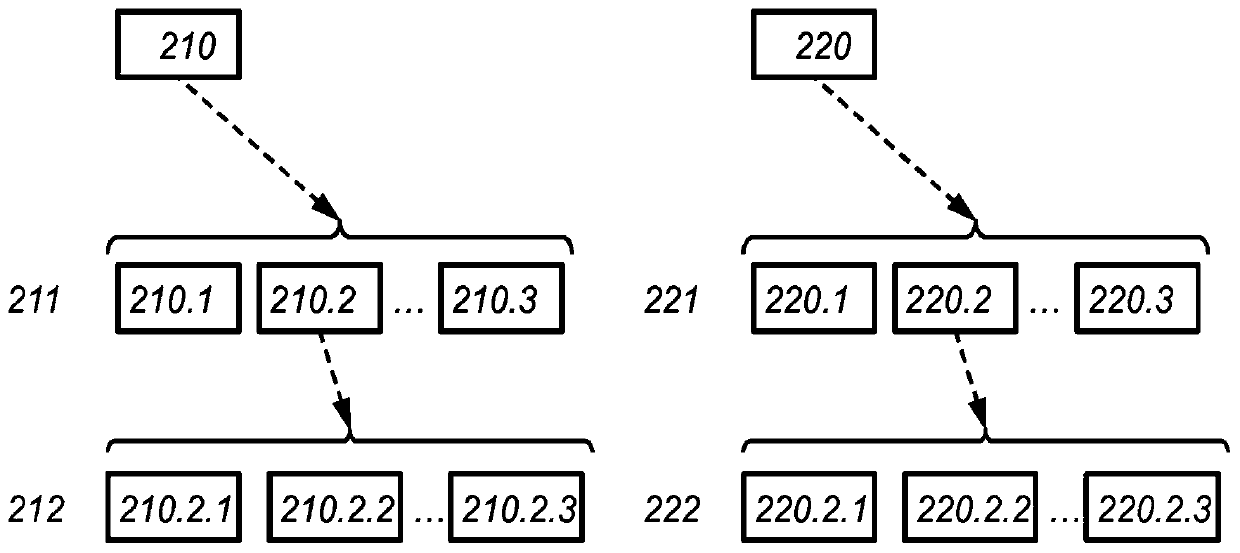

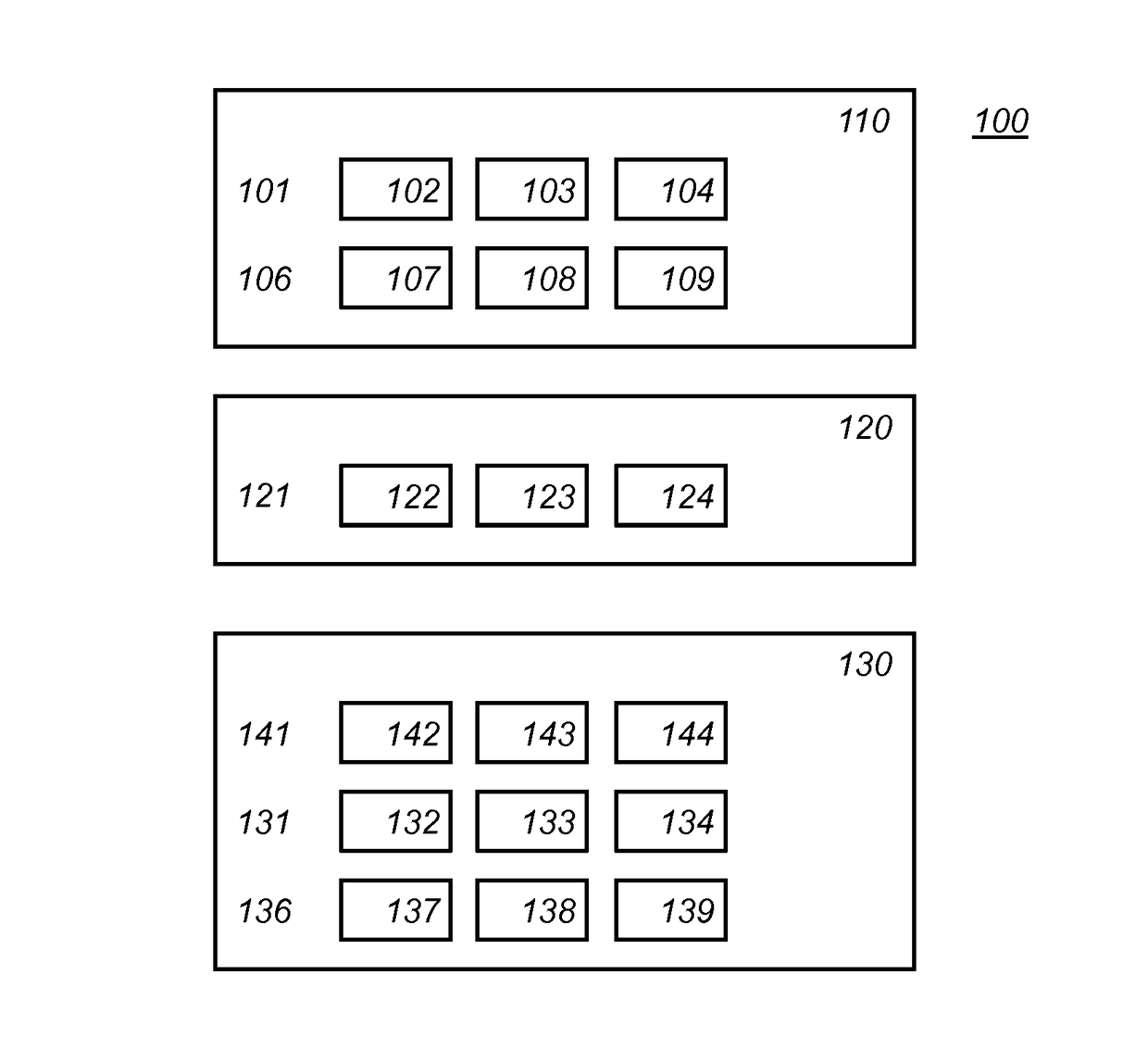

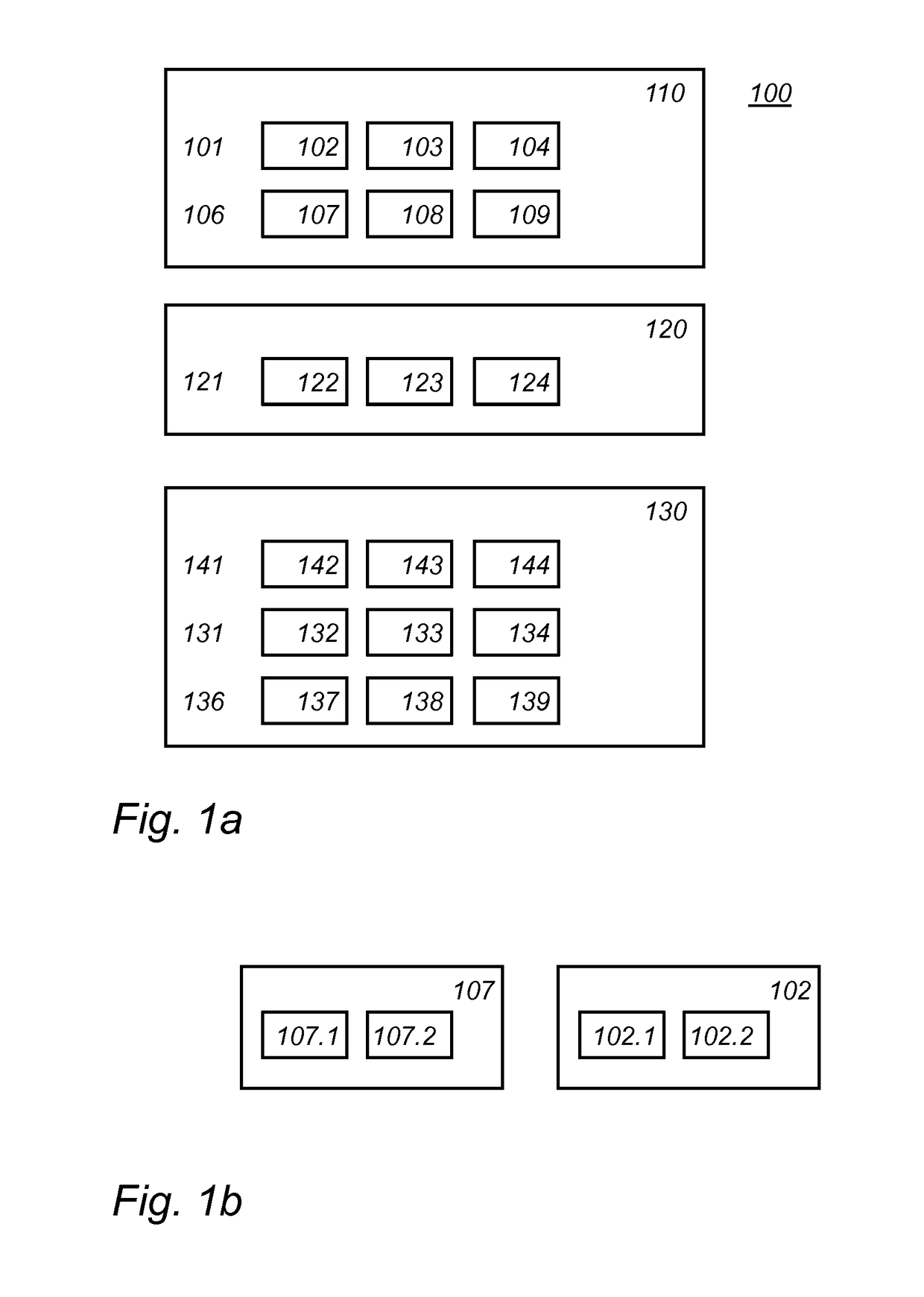

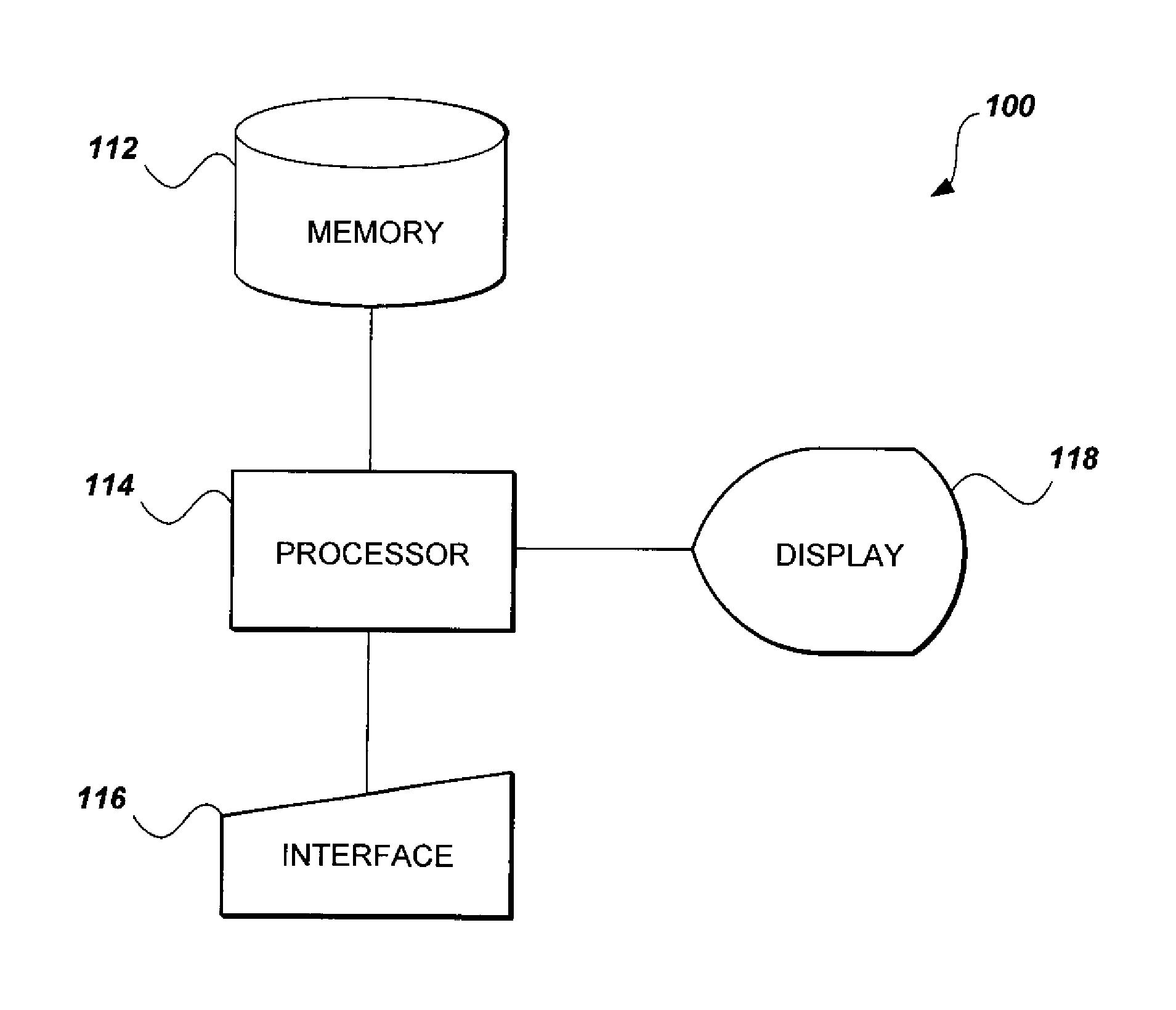

An electronic calculating device arranged to calculate the product of integers

An electronic calculating device (100; 200) arranged to calculate the product of integers, the device comprising a storage (110) configured to store integers (210, 220) in a multi-layer residue numbersystem (RNS) representation, the multi-layer RNS representation having at least an upper layer RNS and a lower layer RNS, the upper layer RNS being a residue number system for a sequence of multipleupper moduli (M i ), the lower layer RNS being a residue number system for a sequence of multiple lower moduli (m i ), an integer (x) being represented in the storage by a sequence of multiple upper residues (x i = (x) Mi ; 211, 221) modulo the sequence of upper moduli (M i ), upper residues (x j ; 210.2, 220.2) for at least one particular upper modulus (M j ) being further-represented in the storage by a sequence of multiple lower residues ((x j ) mj , 212, 222) of the upper residue (x j ) modulo the sequence of lower moduli (m i ), wherein at least one of the multiple lower moduli (m i ) does not divide a modulus of the multiple upper moduli (M j ).

Owner:KONINKLJIJKE PHILIPS NV

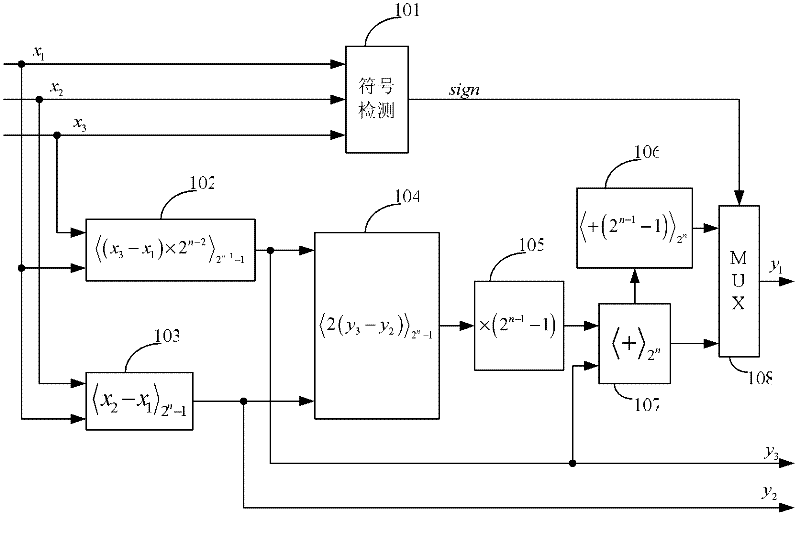

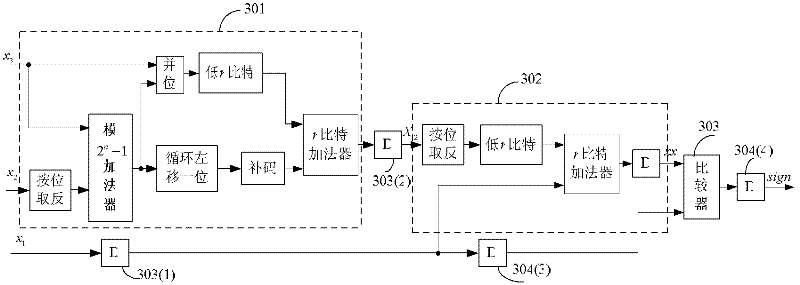

Zoom device for residue number system

InactiveCN102214082AReduce latencySimple structureComputations using residue arithmeticDigital signal processingNegation

The invention discloses a 2n zoom device for a residue number system (RNS) of which the base is {2<n>, 2<n>-1 and 2<n-1>-1}. The zoom device comprises a modulus 2<n>-1 adder, a modulus 2<n-1>-1 adder, an n-bit common binary adder, a sign detection module, a selector and some simple logic operation such as cyclic shift, bitwise negation and the like. The implementation structure is simple and clear; by adding a pipeline register at a proper position, a key route becomes smaller; therefore, an active effect on reduction of the time delay of the key route of the RNS during application of a digital signal processing system is achieved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Data processing method and system

ActiveCN102043760BReduce processing timeShorten the pathComplex mathematical operationsData processing systemComputer science

The embodiment of the invention discloses a data processing system and method which are applied in the technical field of data processing. In the data processing system of the embodiment in the invention, a first conversion unit utilizes multiple remainder groups which are mutually prime numbers to convert the input data represented by binary weight values to L-path conversion data represented bythe residue number system; a computing unit performs Fourier operation on the L-path conversion data independently, a second conversion unit converts the calculated data to the output data represented by binary weight values again; and a data processing unit is used to perform data processing. In the system of the embodiment in the invention, the Fourier operation of each path of conversion data is independent; and the processed bits of the data represented by the residue number system are fewer, thus the calculated path is shortened relatively, the data processing time is reduced and the working efficiency of the system can be increased.

Owner:SHANGHAI HUAWEI TECH CO LTD

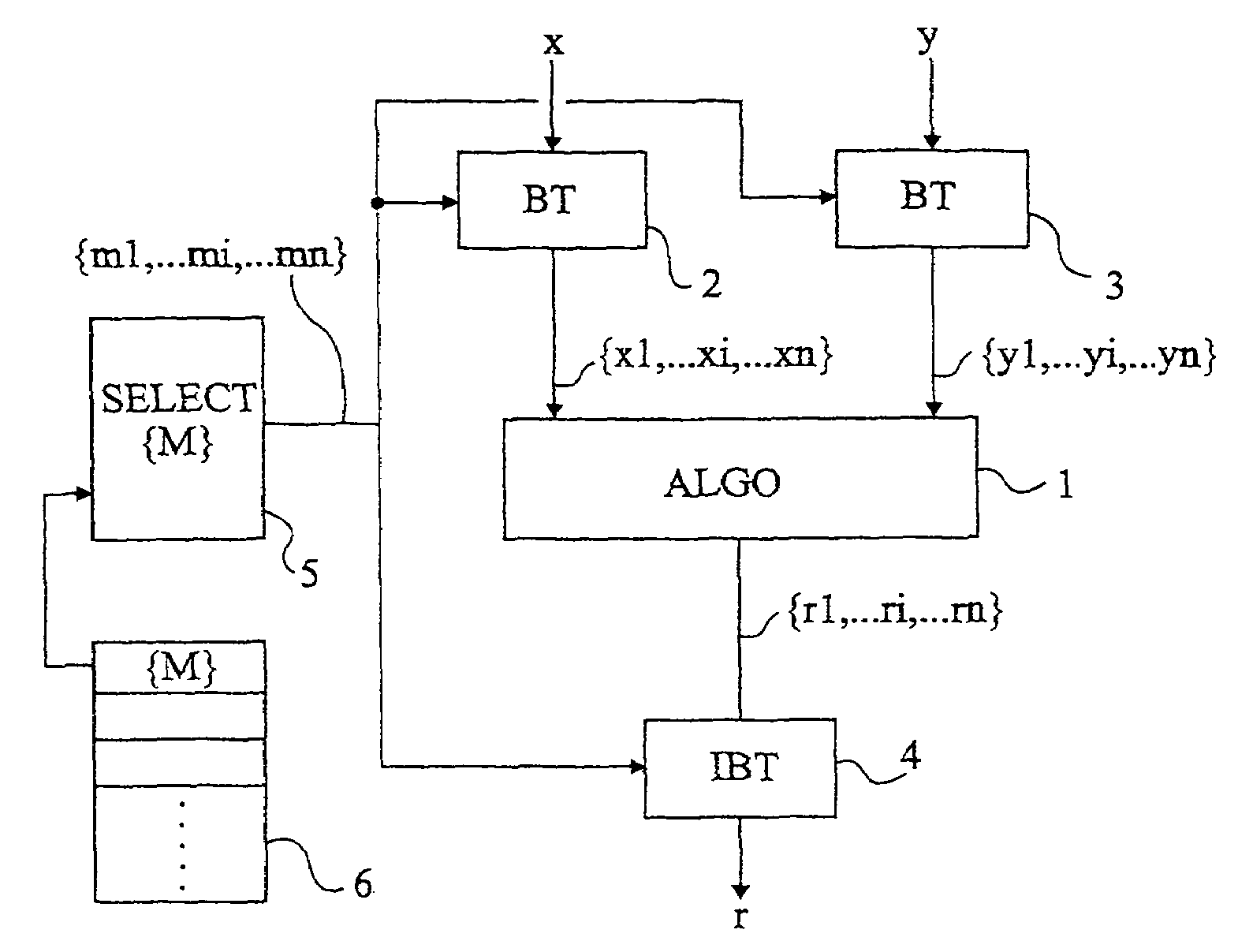

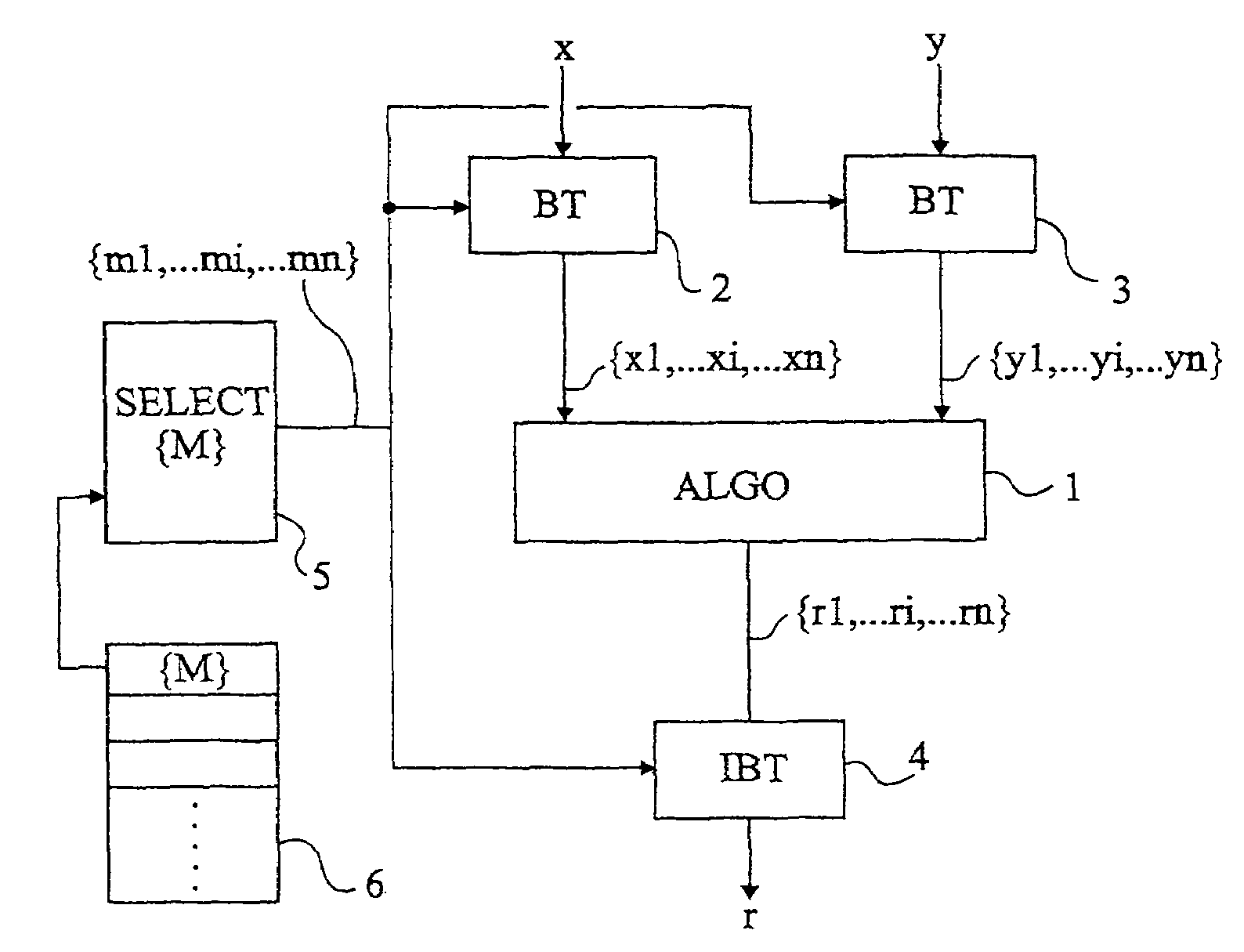

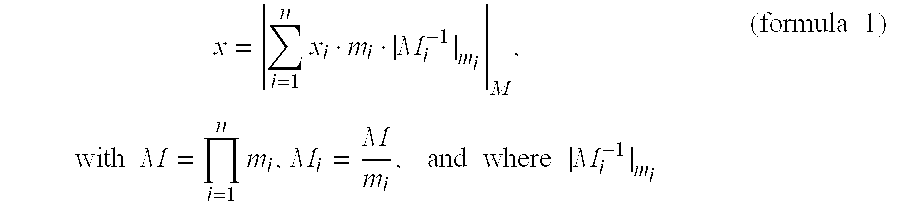

Masking of factorized data in a residue number system

ActiveUS7254600B2Not adversely affect the execution rapidity of the algorithmReduce stepsComputations using residue arithmeticComputation using denominational number representationDigital dataTheoretical computer science

A method and a circuit for masking digital data handled by an algorithm and factorized by a residue number system based on a finite base of numbers or polynomials prime to one another, comprising making the factorization base variable.

Owner:STMICROELECTRONICS SRL

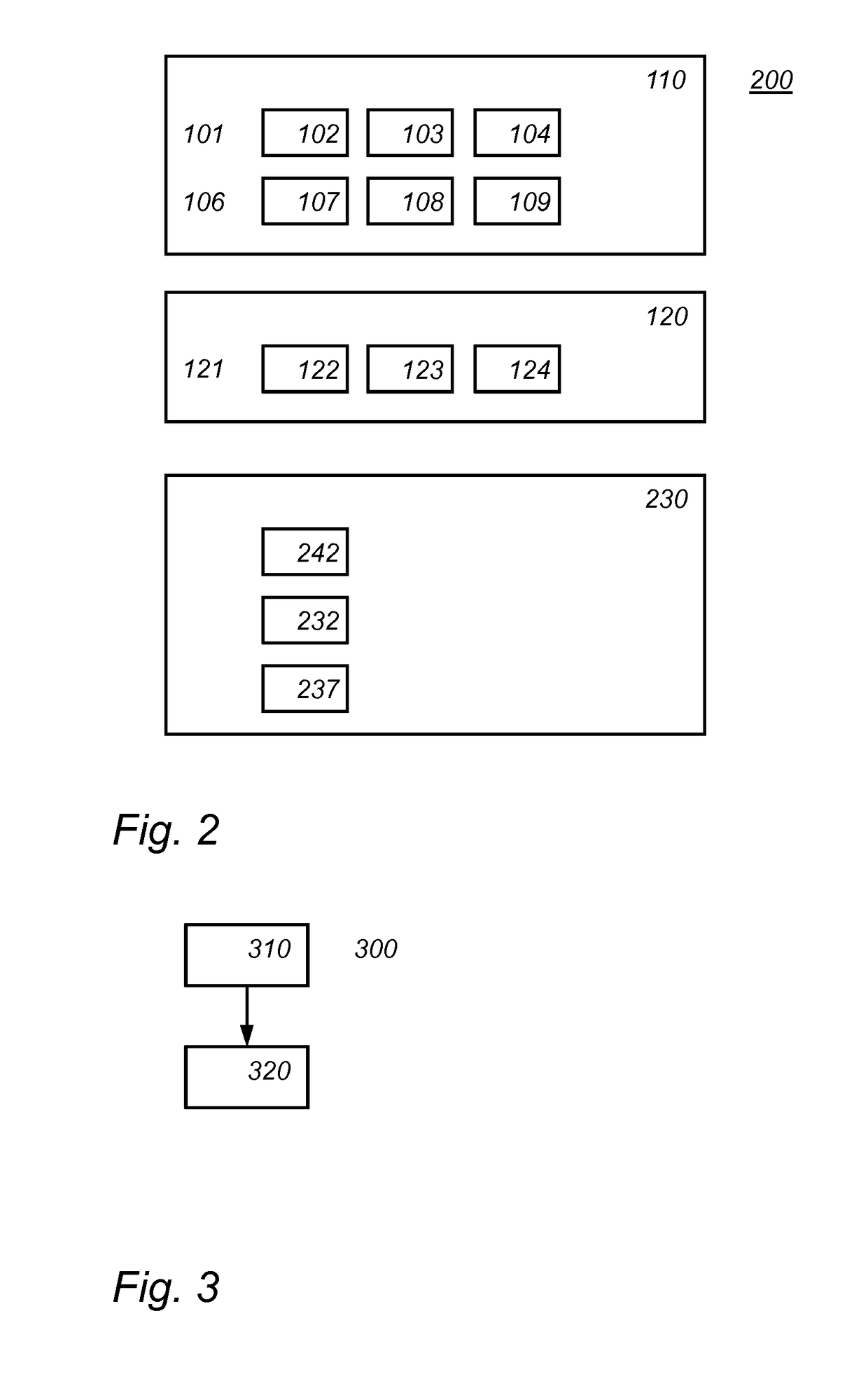

Electronic calculating device

ActiveUS20170353294A1Suppresses increase in code sizeIncrease confusionCryptographic attack countermeasuresComputations using residue arithmeticComputer scienceResidue number system

An electronic calculating device (100) arranged to perform obfuscated arithmetic in a commutative ring (ZM; Zn[x] / M(x)) defined by a combined modulus (M; M(x)) in a residue number system, the residue number system being defined for a series of moduli (m1, m2, . . . , mN), each modulus defining a commutative ring (ZM1; Zn[x] / m1(x)), for each modulus (mi) of the series there exists an associated base element (ui) satisfying the condition that each ring element (xj) modulo the modulus (mj) may be expressed as an integer-list ((aj, bj)) such that the ring elements equal a linear combination of powers of the base element (xj=uiaj−uibj), wherein the powers have exponents determined by the integer-list.

Owner:KONINKLJIJKE PHILIPS NV

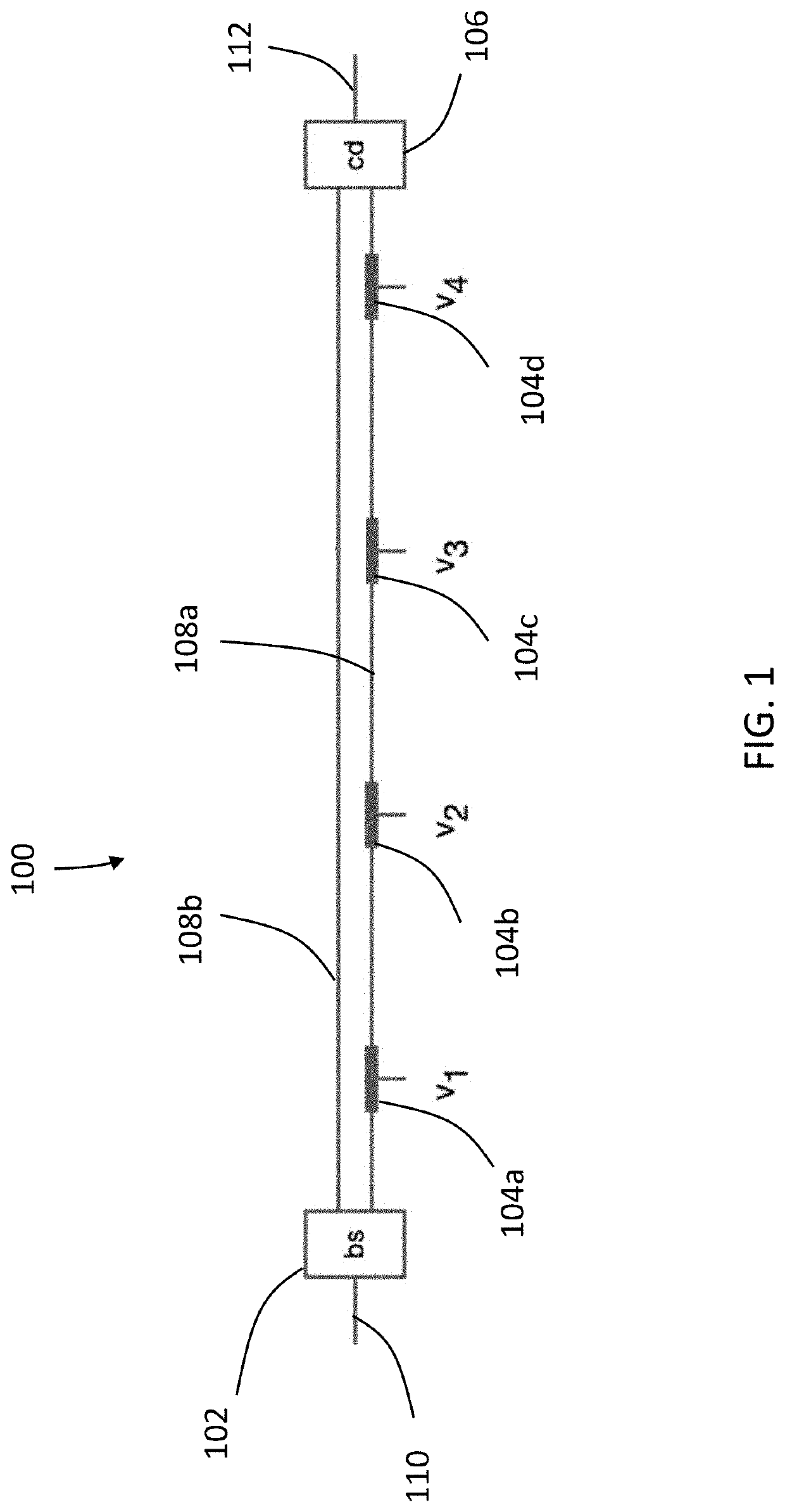

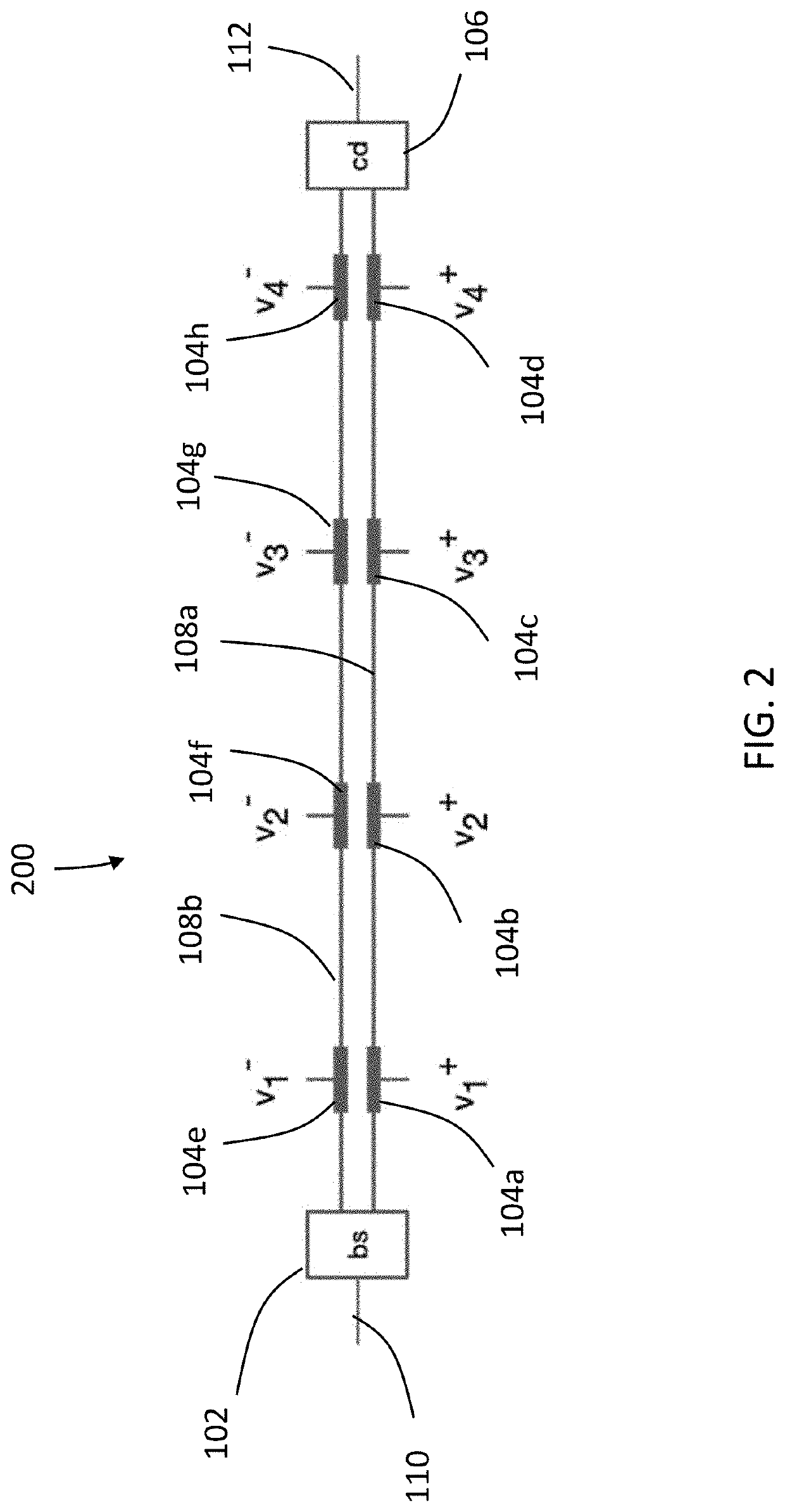

Residue number system in a photonic matrix accelerator

A photonic processor uses light signals and a residue number system (RNS) to perform calculations. The processor sums two or more values by shifting the phase of a light signal with phase shifters and reading out the summed phase with a coherent detector. Because phase winds back every 2π radians, the photonic processor performs addition modulo 2π. A photonic processor may use the summation of phases to perform dot products and correct erroneous residues. A photonic processor may use the RNS in combination with a positional number system (PNS) to extend the numerical range of the photonic processor, which may be used to accelerate homomorphic encryption (HE)-based deep learning.

Owner:LIGHTMATTER INC

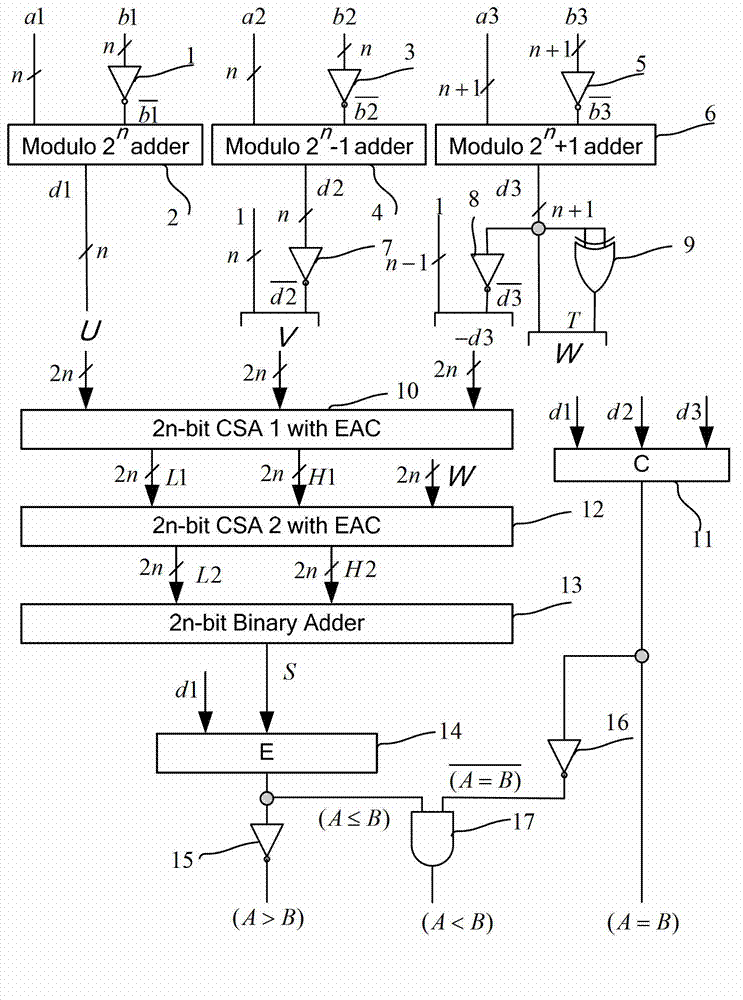

Residue number systems (RNS) comparator

InactiveCN102930097ASimplify the comparison processSave resourcesSpecial data processing applicationsResource consumptionComputer module

The invention discloses a residue number systems (RNS) comparator, which comprises a first n-position phase inverter array, a modulus 2<n> adder, a second n-position phase inverter array, a modulus 2<n>-1 adder, a first n+1-position phase inverter array, a modulus 2<n>+1 adder, a third n-position phase inverter array, a second n+1-position phase inverter array, two input exclusive OR gates, a first carry save adder with end around carry, a second carry save adder with end around carry, a 2n-position binary adder, a first operational module, a second operational module, a first 1-position phase inverter, a second 1-position phase inverter and two input AND gates. According to the RNS comparator, subtraction operation is directly carried out in a residue number system, and an operation result in the residue number system is then converted to a binary system, so that the contrast process of the comparison is simplified, the resource consumption is reduced, and the operation speed is also improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

RNS-based cryptographic system and method

InactiveUS8462939B2Blind factorization even morePublic key for secure communicationUser identity/authority verificationCiphertextCollision attack

The RNS-based cryptographic system and method uses a symmetric residue number system (RNS) for encryption and decryption of messages, i.e., the sender and receiver agree upon a set of relatively prime numbers, referred to as the basis, whose product is an integer, and both the RNS and the integer are kept secret. To break the cipher, an attacker must factor the secret integer, which is unknown to the attacker, given only the upper bound of the unknown integer, a problem referred to as blind factorization of the unknown integer, which is a computationally hard problem. The method may be combined with a discrete logarithm problem, and the ciphertext may be padded with random values to hide the upper bound of the unknown integer. When the ciphertext requires multiple blocks, subsets of the basis and / or the random number padding may be used to prevent collision attacks.

Owner:KING FAHD UNIVERSITY OF PETROLEUM AND MINERALS

![Backward conversion device and method of residue number system with bases of [2<n-1>,2<n+1>,2<n>] and [2<n-1>,2<n+1>,2<2n+1>] Backward conversion device and method of residue number system with bases of [2<n-1>,2<n+1>,2<n>] and [2<n-1>,2<n+1>,2<2n+1>]](https://images-eureka.patsnap.com/patent_img/cee0ff63-6ddb-405f-9c28-90063edd2882/BDA0000063994570000022.png)

![Backward conversion device and method of residue number system with bases of [2<n-1>,2<n+1>,2<n>] and [2<n-1>,2<n+1>,2<2n+1>] Backward conversion device and method of residue number system with bases of [2<n-1>,2<n+1>,2<n>] and [2<n-1>,2<n+1>,2<2n+1>]](https://images-eureka.patsnap.com/patent_img/cee0ff63-6ddb-405f-9c28-90063edd2882/HDA0000063994580000011.png)

![Backward conversion device and method of residue number system with bases of [2<n-1>,2<n+1>,2<n>] and [2<n-1>,2<n+1>,2<2n+1>] Backward conversion device and method of residue number system with bases of [2<n-1>,2<n+1>,2<n>] and [2<n-1>,2<n+1>,2<2n+1>]](https://images-eureka.patsnap.com/patent_img/cee0ff63-6ddb-405f-9c28-90063edd2882/HDA0000063994580000012.png)