Patents

Literature

31 results about "Distributed arithmetic" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

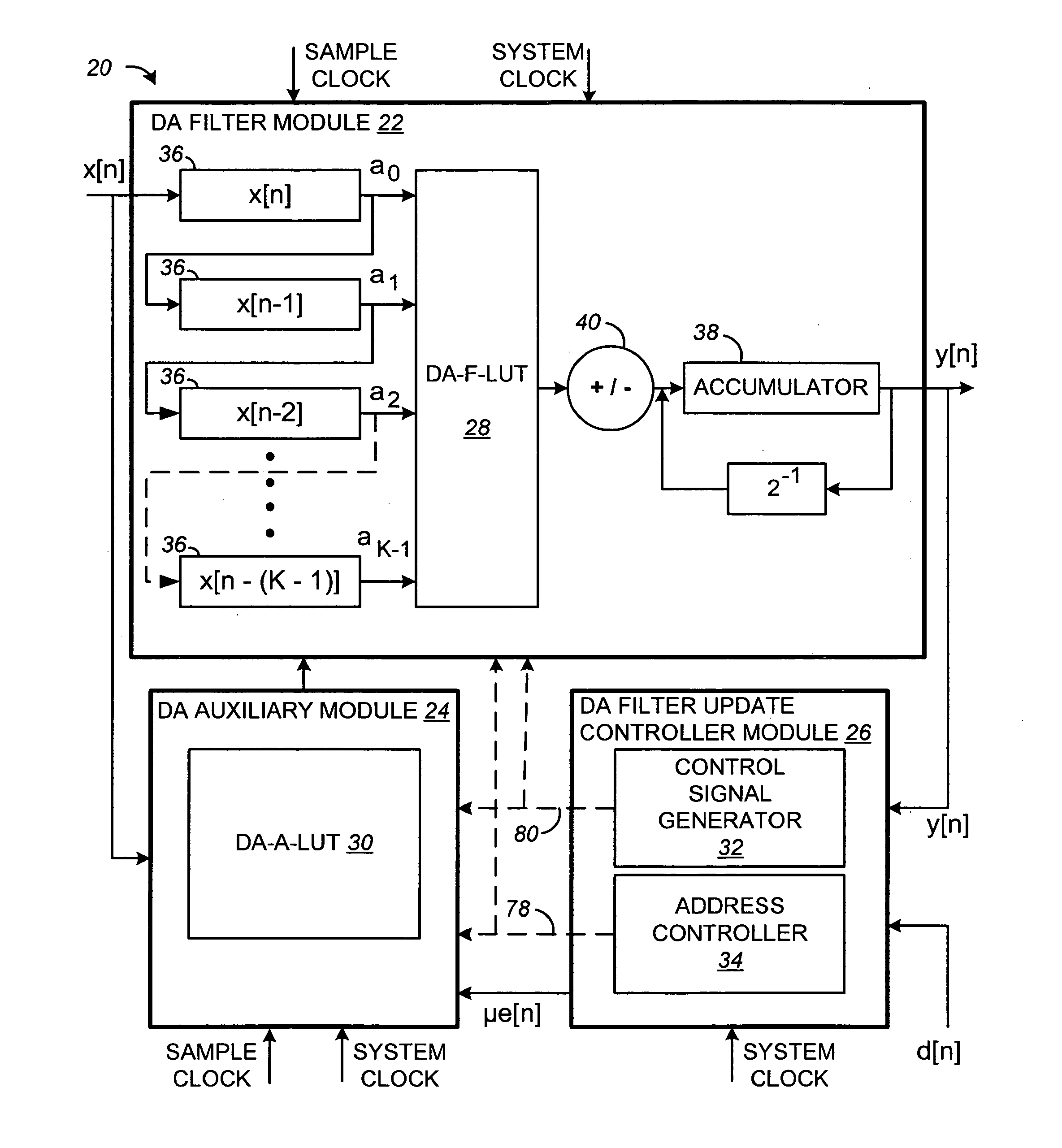

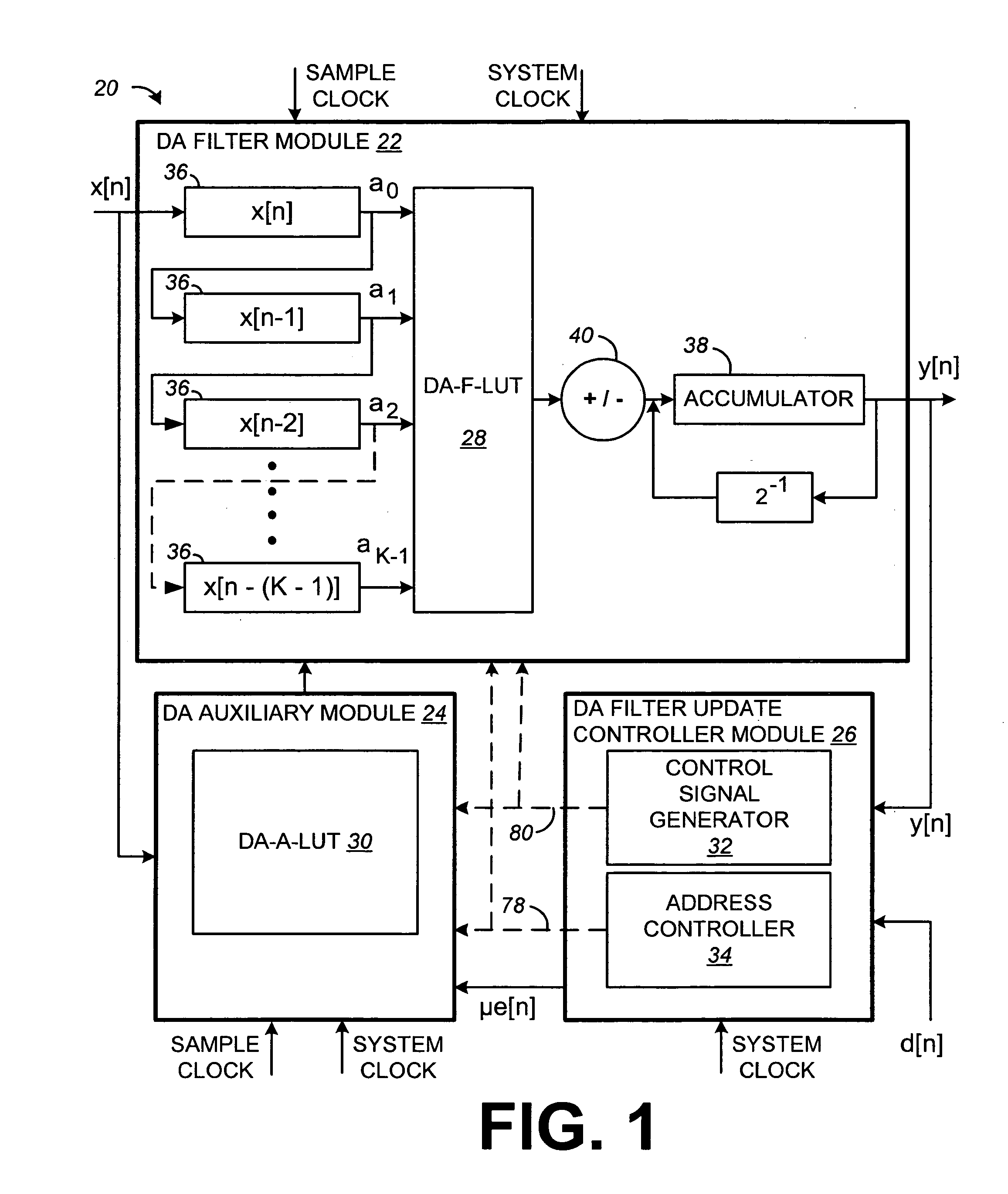

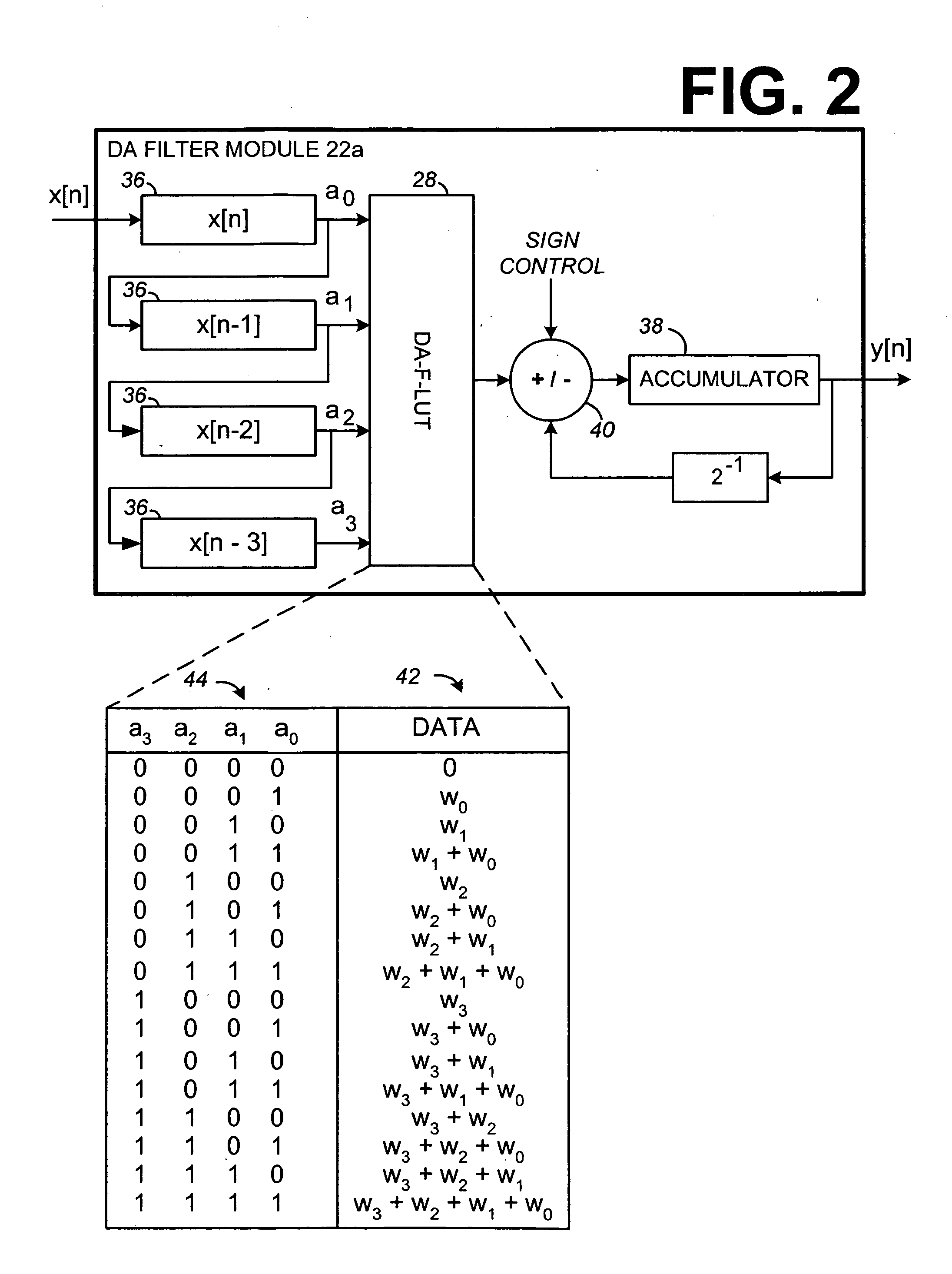

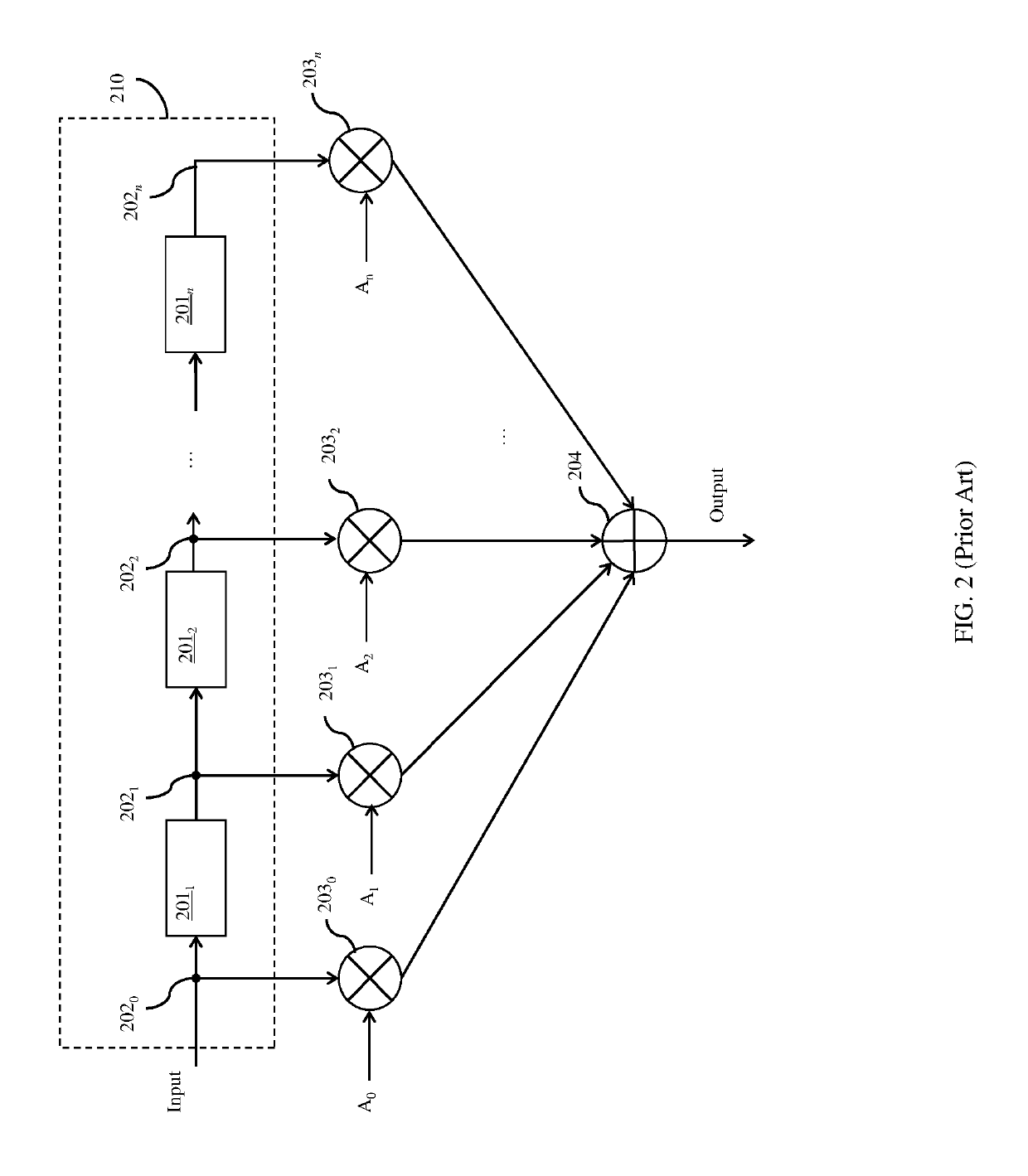

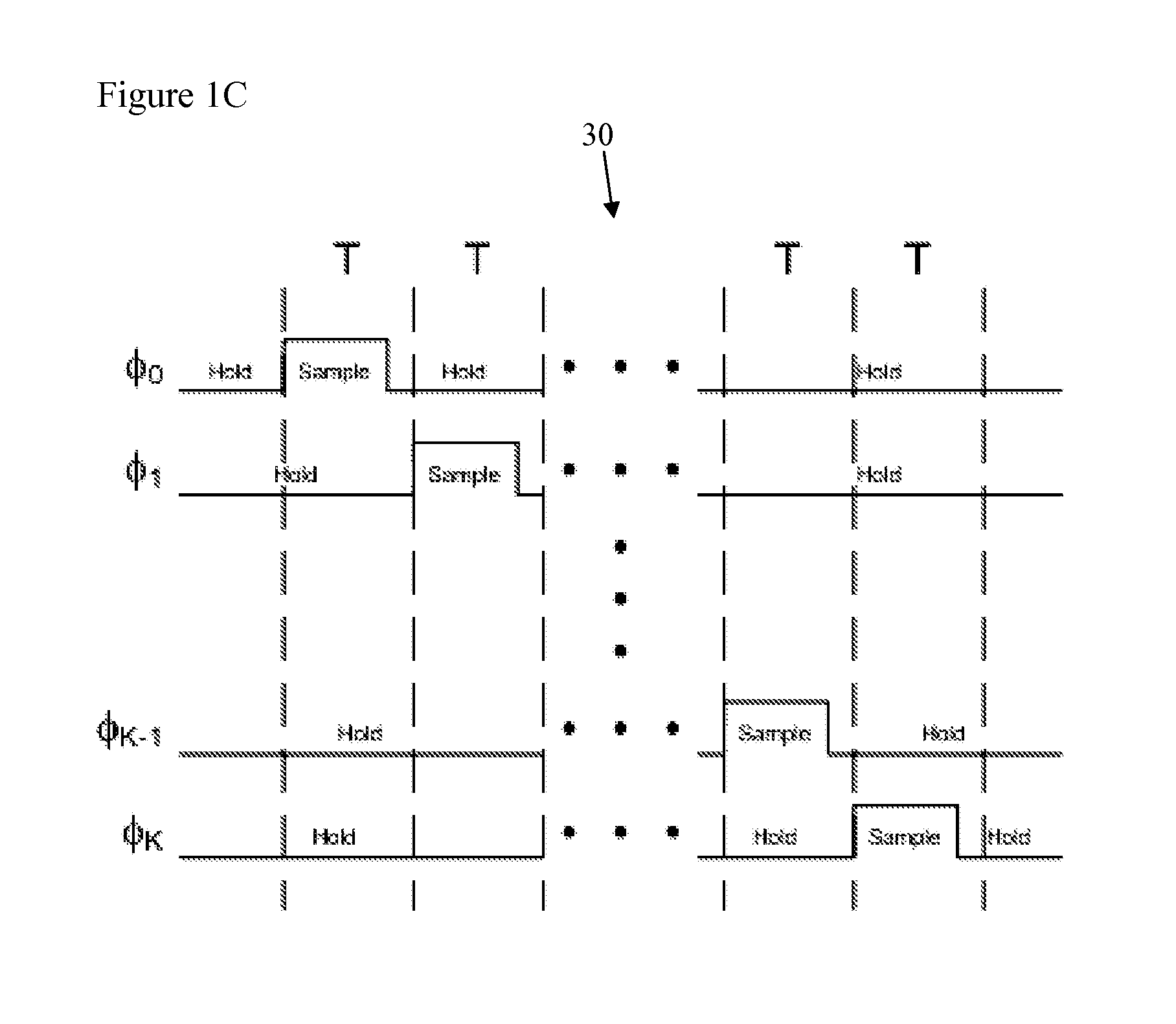

Distributed arithmetic adaptive filter and method

Systems and methods for very high throughput adaptive filtering using distributed arithmetic are disclosed. One distributed arithmetic adaptive filter may include a memory for storing a first and second lookup table. The first lookup table may include 2K filter weights addressed by the rightmost bits of each of K signal samples stored in a plurality of registers. The filter may include a controller configured to update the second lookup table with each possible combination of the sums of the K most recent input samples and update each of the 2K filter weights of the first lookup table based on the combination of the sums of the K most recent input samples stored in the second lookup table. The second lookup-table may be updated during a filtering operation that uses the first lookup-table. One filter may include a plurality of sub-filters with each sub-filter having first and second lookup tables.

Owner:GEORGIA TECH RES CORP

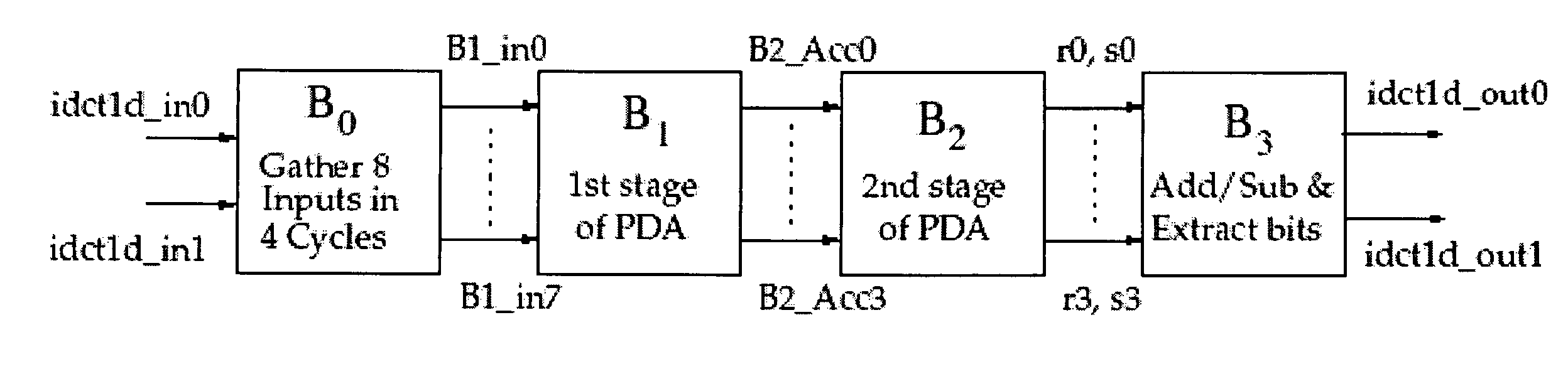

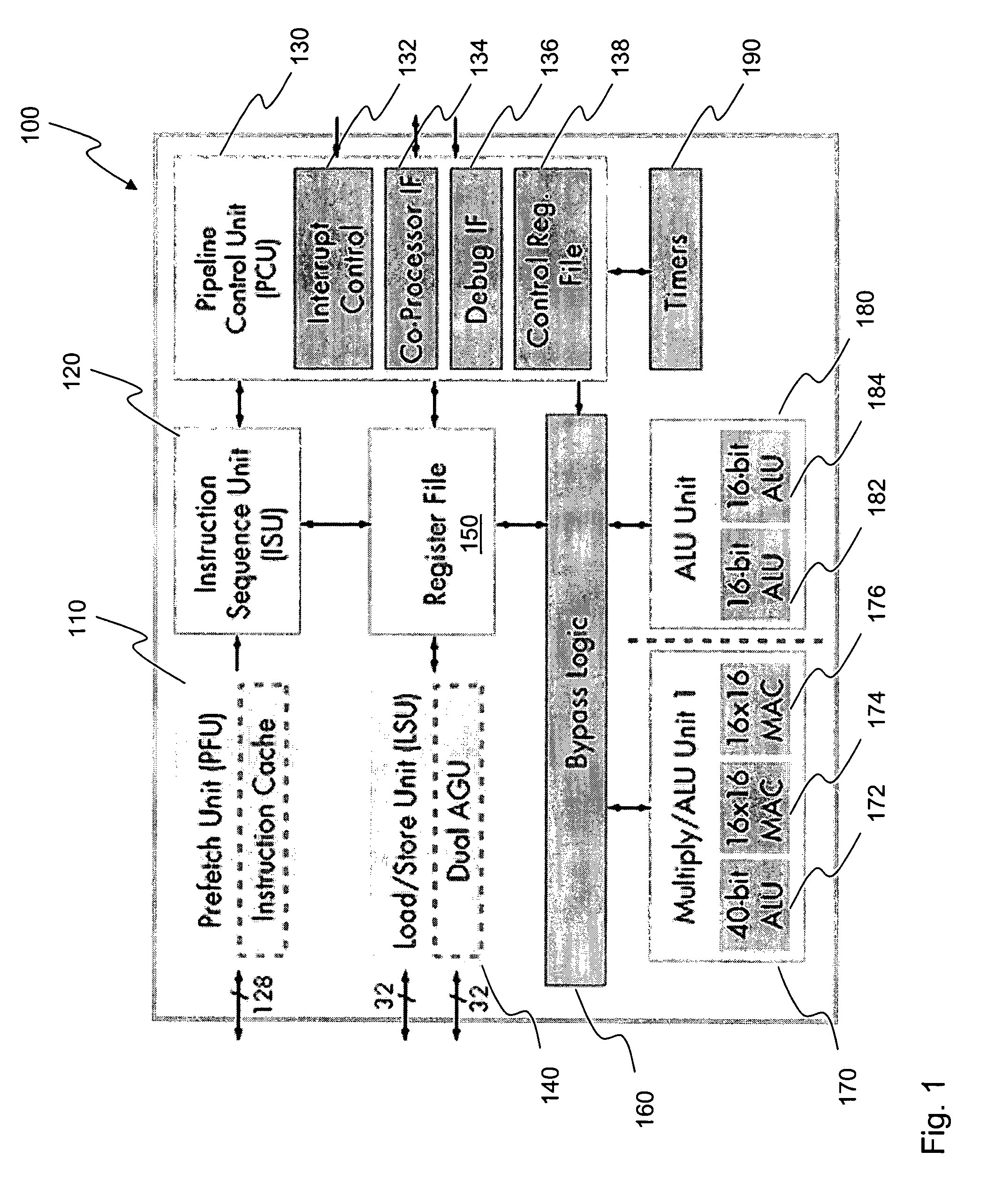

Digital signal processor having inverse discrete cosine transform engine for video decoding and partitioned distributed arithmetic multiply/accumulate unit therefor

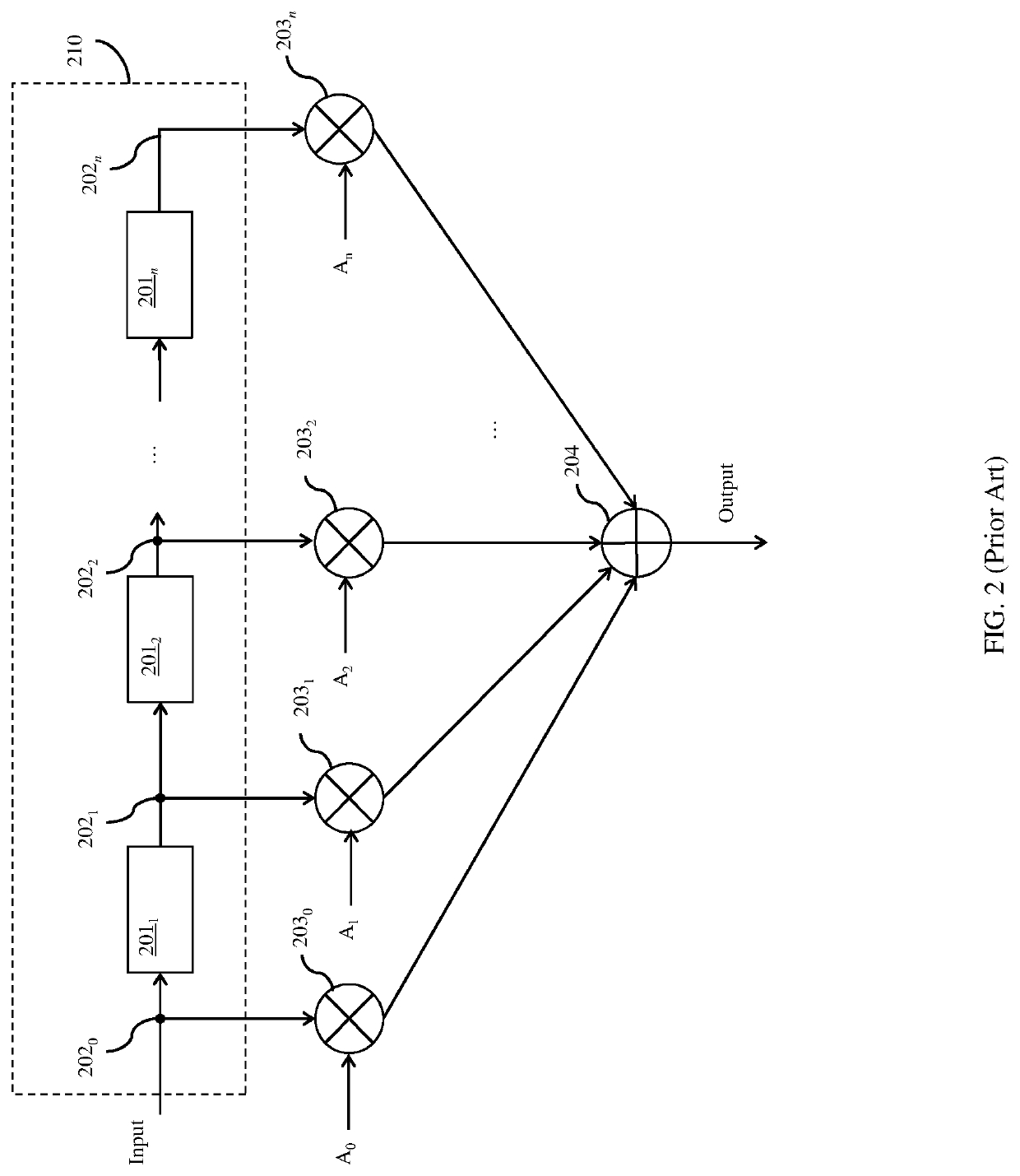

A distributed arithmetic multiply / accumulate (MAC) unit for computing inverse discrete cosine transformations (IDCTs). In one embodiment, the distributed arithmetic MAC unit includes: (1) a first pipeline stage configured to perform dot products on received sequential input data and (2) a second pipeline stage coupled to the first pipeline stage and configured to compute additions and subtractions of the dot products to yield sequential output data.

Owner:VERISILICON HLDGCO LTD

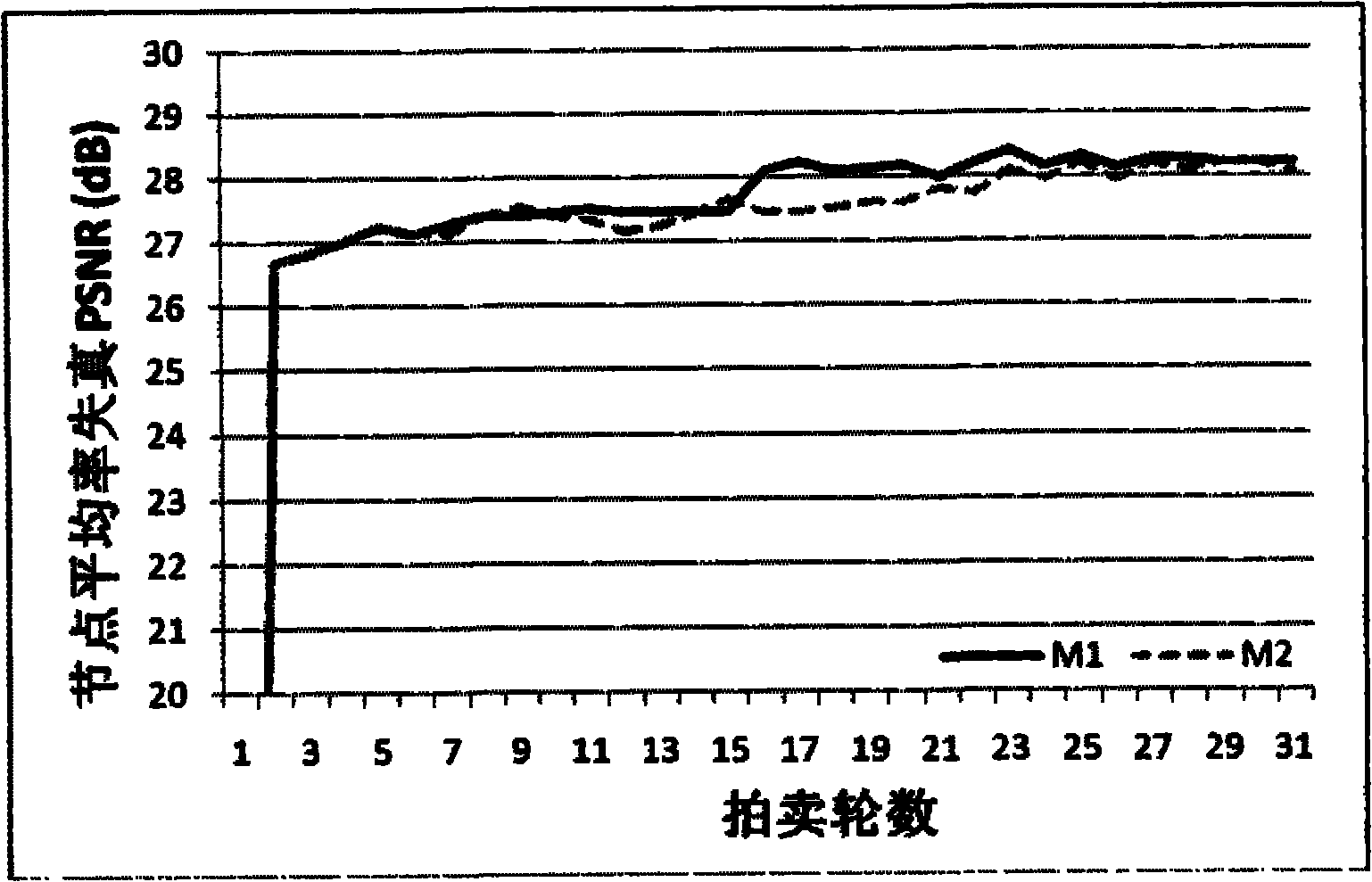

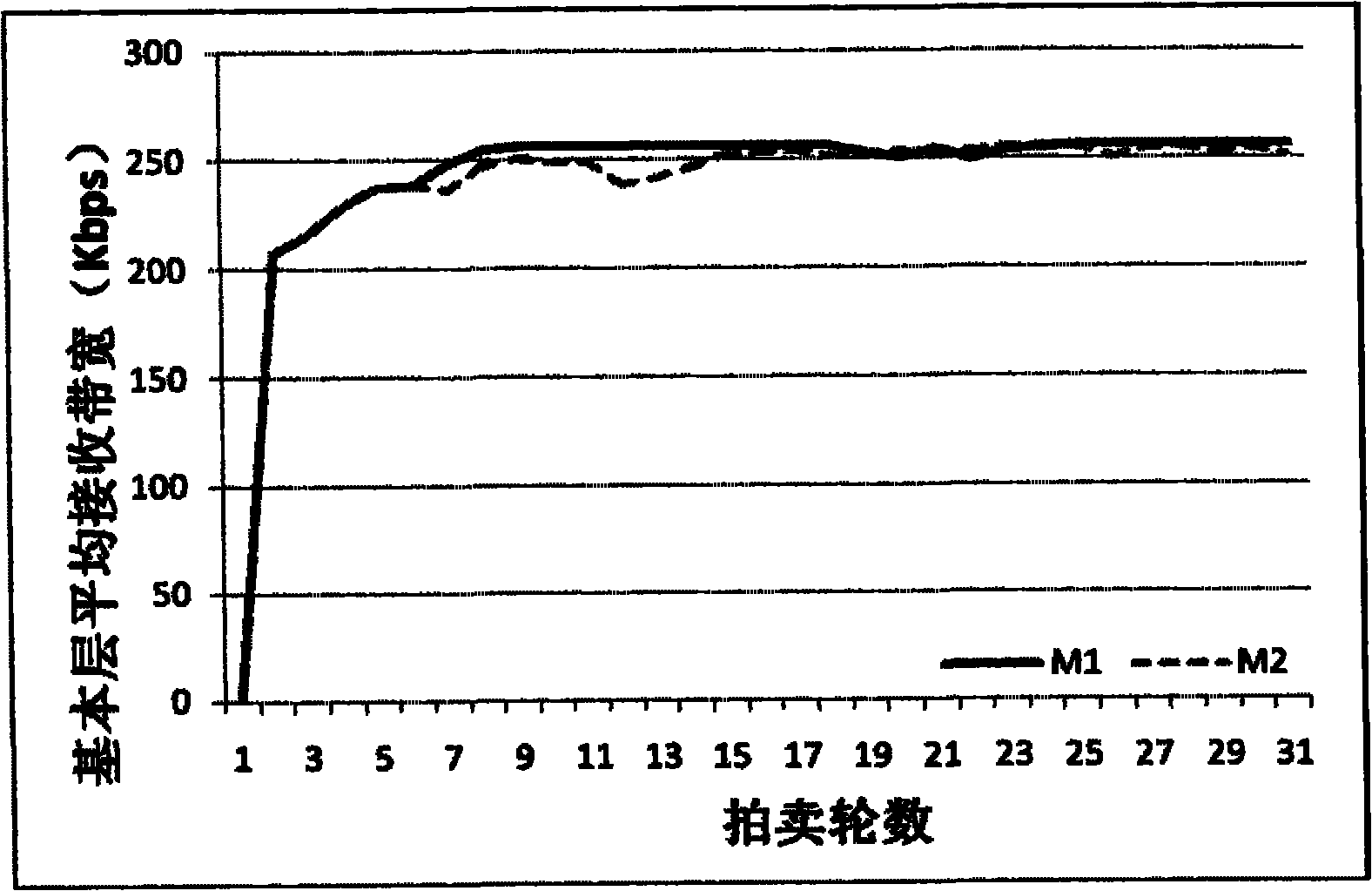

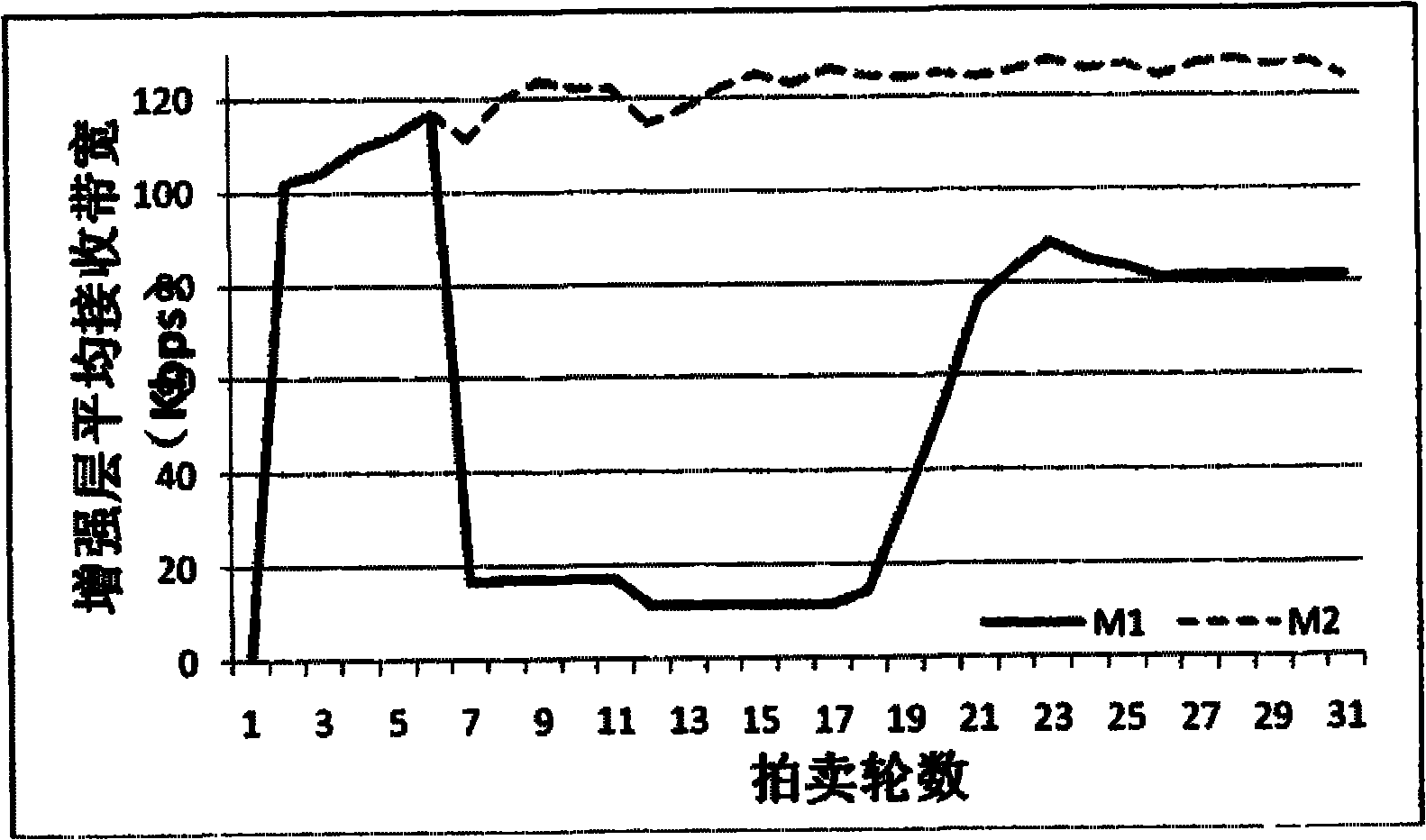

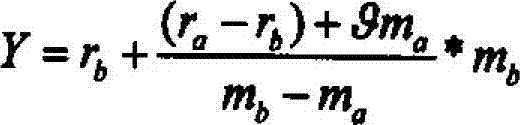

Bandwidth allocation method for scalable video streaming in multi-overlay network based on auction

ActiveCN101895580ASolving Bandwidth ConflictsIncrease profitTelevision systemsSelective content distributionComputation complexityNetwork conditions

Owner:SHANGHAI UNIV

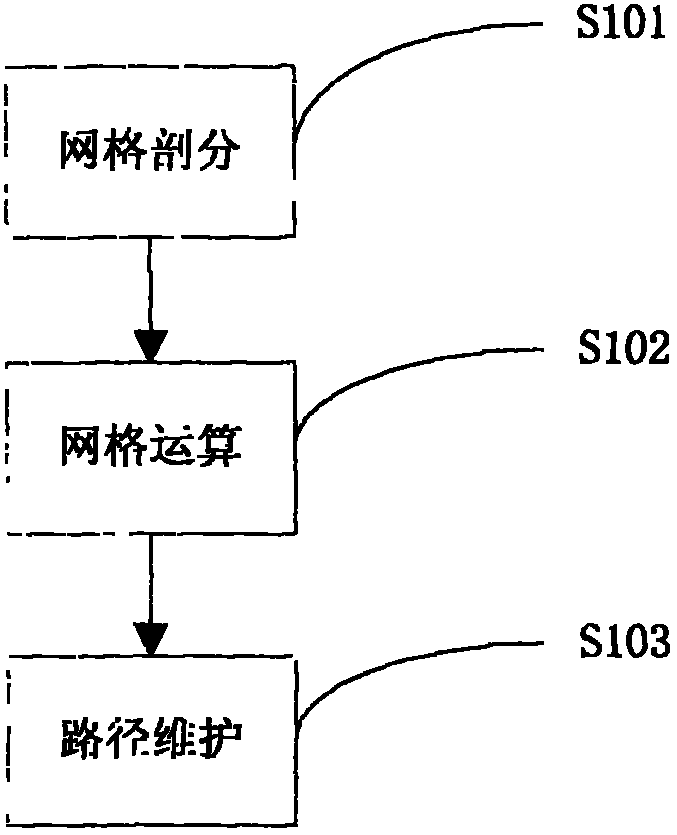

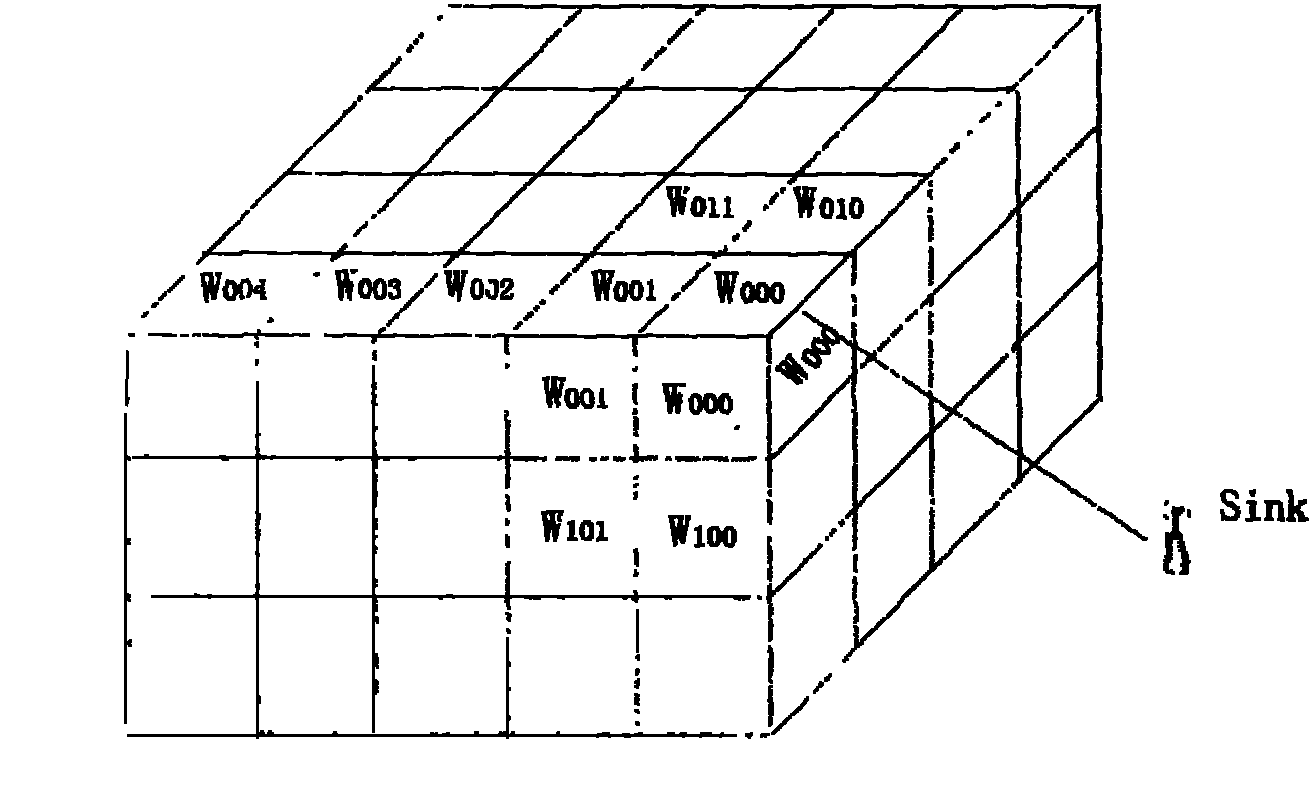

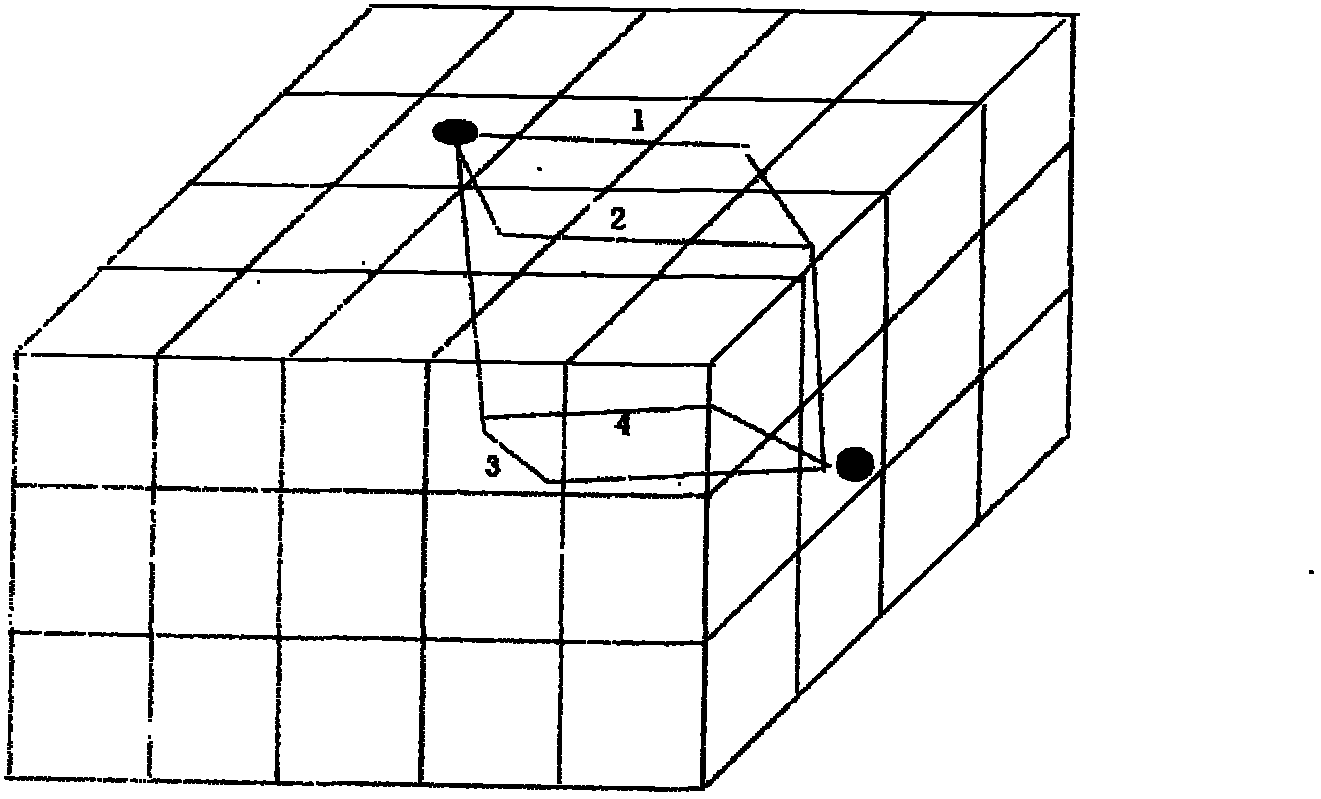

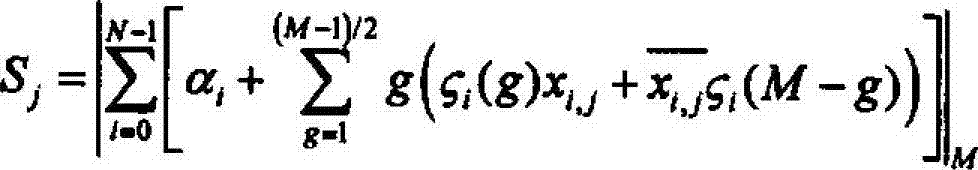

Determination method of QOS (quality of service) route longevity path of wireless sensor network in water environment

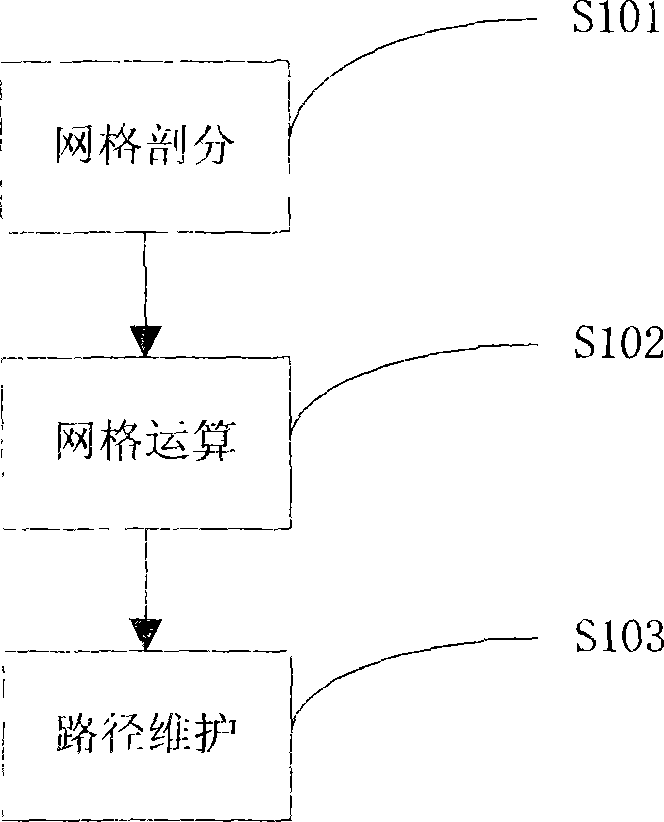

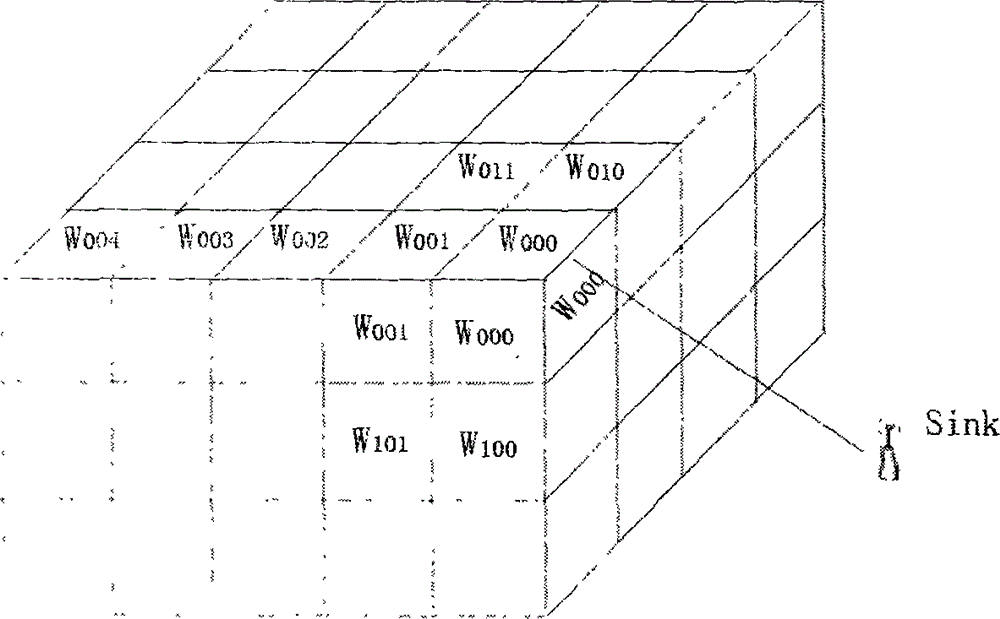

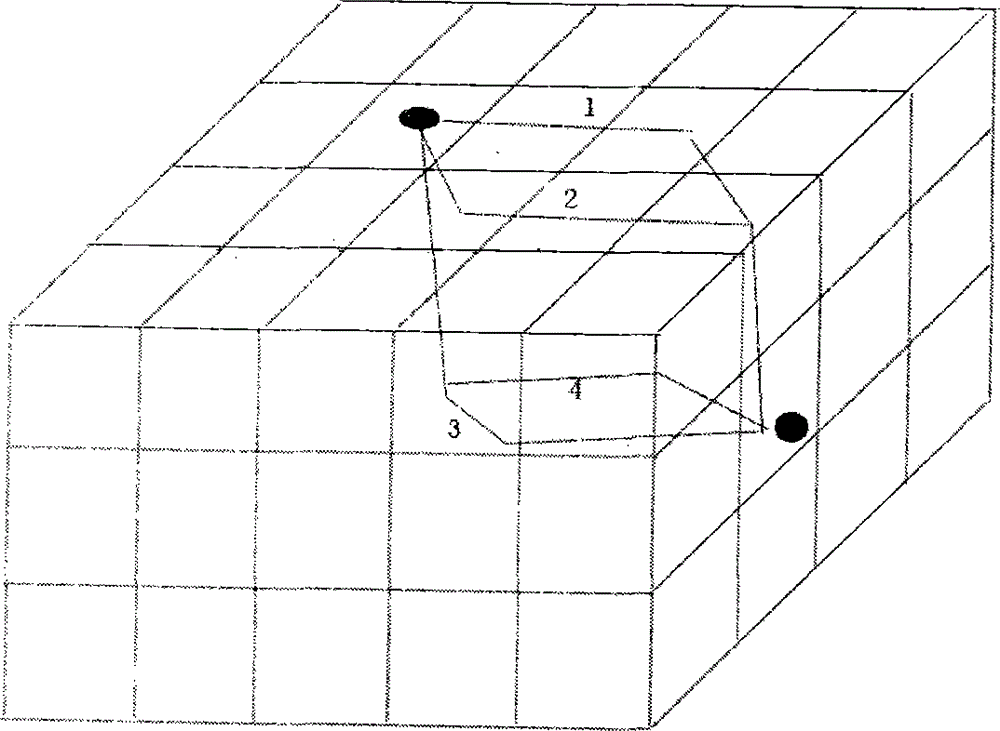

The invention discloses a determination method of a QOS (quality of service) route longevity path of a wireless sensor network in water environment. The determination method comprises the following steps of: firstly, carrying out a network split on an information acquisition region, enabling a Sink node to broadcast all the information after split, and enabling each node to know the taken framework and position; then, carrying out distributed arithmetic on each framework, seeking one or more than one shortest framework path from each framework to the Sink node, and enabling only can two adjacent frameworks transmit data, so as to ensure that the network transmission energy consumption is least when the network is in normal operation; and finally, seeking a suitable path based on an entropy idea, utilizing the entropy to carry out auto patching on the path after operation for a certain time, namely, achieving the self-healing of the structure of the whole network route after the node is vitiate. Compared with algorithms such as Long-term, DBR, DTN(delay / disruption tolerant network), the QOS route algorithm has better properties on the aspects of route reconstruction times, route success rate, network energy consumption and network delay.

Owner:CHONGQING COLLEGE OF ELECTRONICS ENG

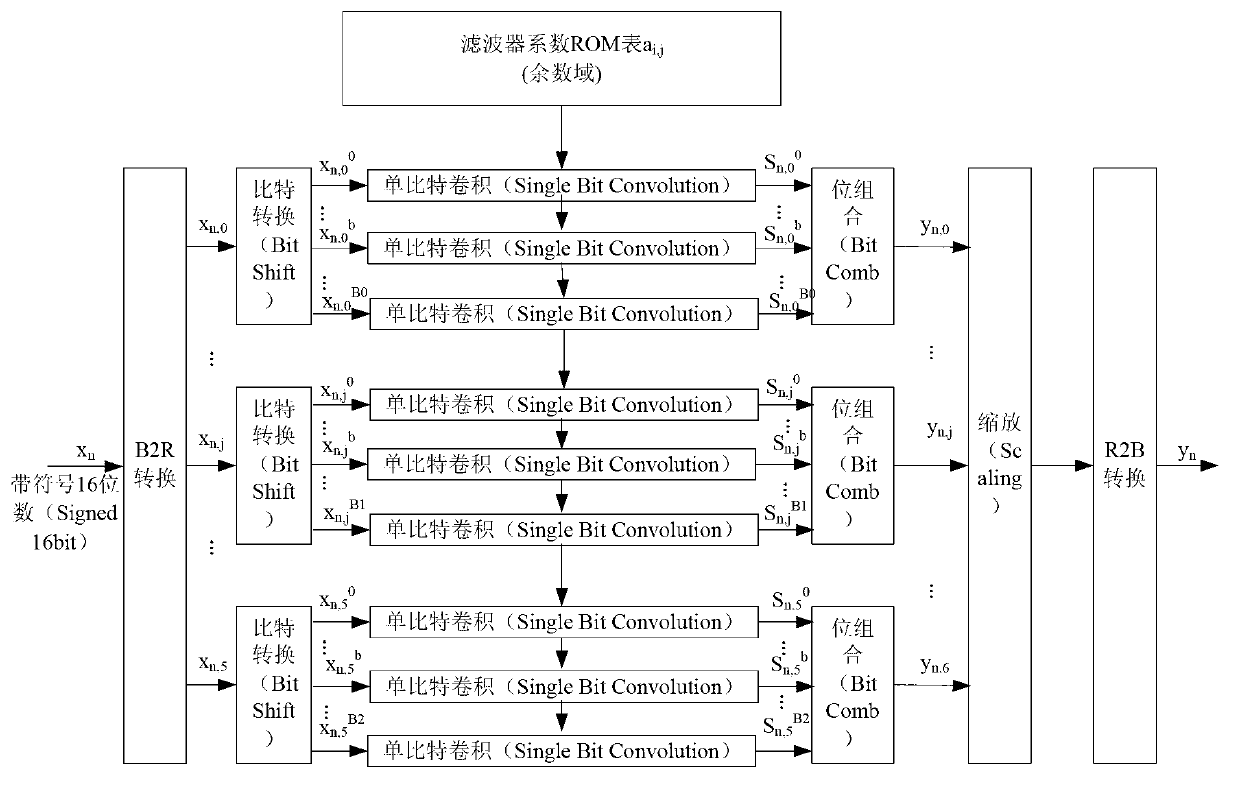

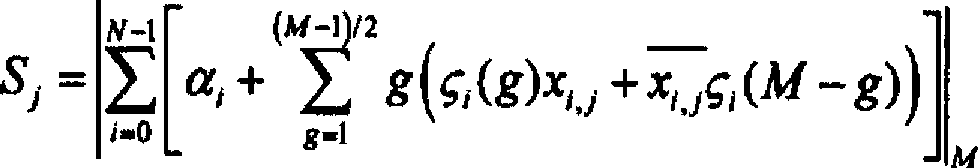

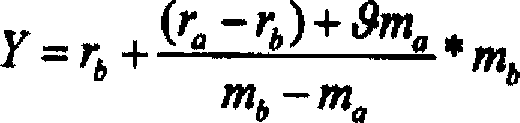

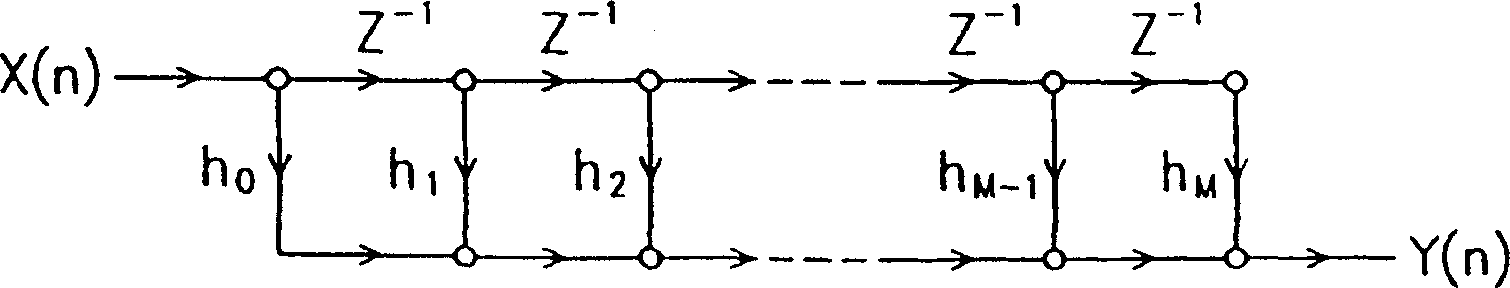

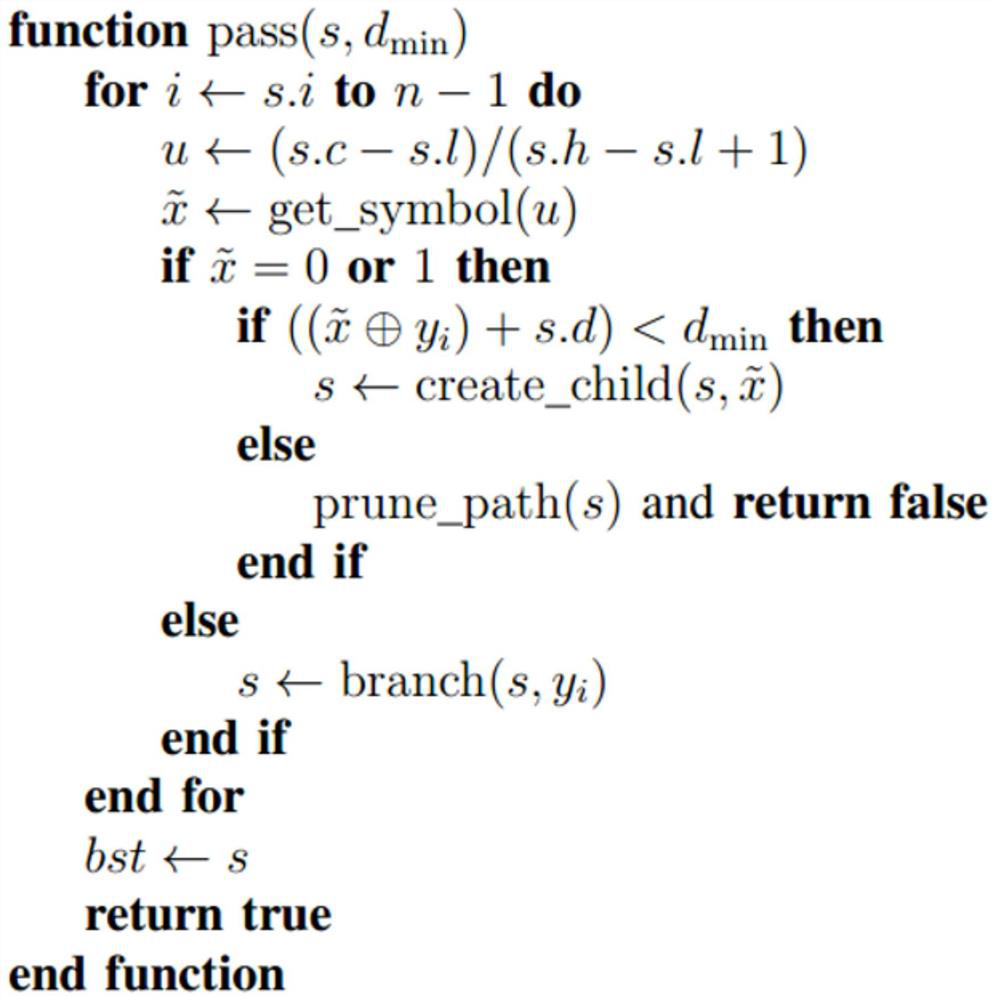

DA-RNS (distributed arithmetic-residue number system) algorithm based FIR (finite impulse response) filter realizing method

ActiveCN103001605AReduce areaReduce power consumptionDigital technique networkChinese remainder theoremLow resource

The invention relates to a DA-RNS (distributed arithmetic-residue number system) algorithm based FIR (finite impulse response) filter realizing method. The DA-RNS algorithm based FIR filter realizing method includes steps of firstly, subjecting filter input and filter coefficient to conversion from decimal weighting system to remainder non-weighting system by means of step-by-step table lookup; secondly, decomposing filter input into a single-byte mode; thirdly, subjecting the filter input and the filter coefficient to single-byte convolution operation; fourthly, scaling the filter input after remainder of the filter input is subjected to convolution operation under the remainder non-weighting system; and fifthly, restoring the remainder to decimal system by means of China remainder theorem. Compared with the prior art, the DA-RNS algorithm based FIR filter realizing method has the advantages of low resource consumption, high throughput and the like.

Owner:TONGJI UNIV

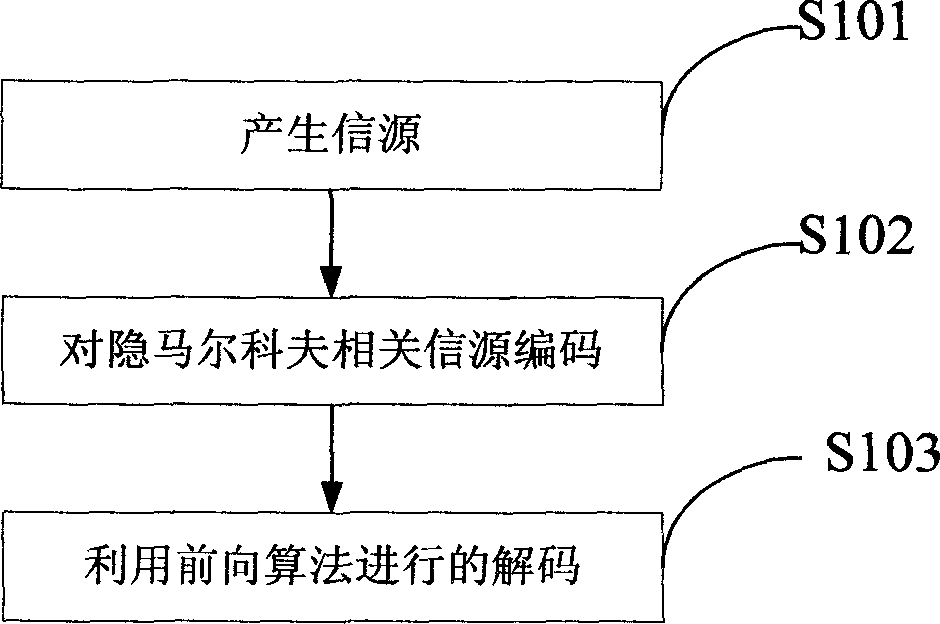

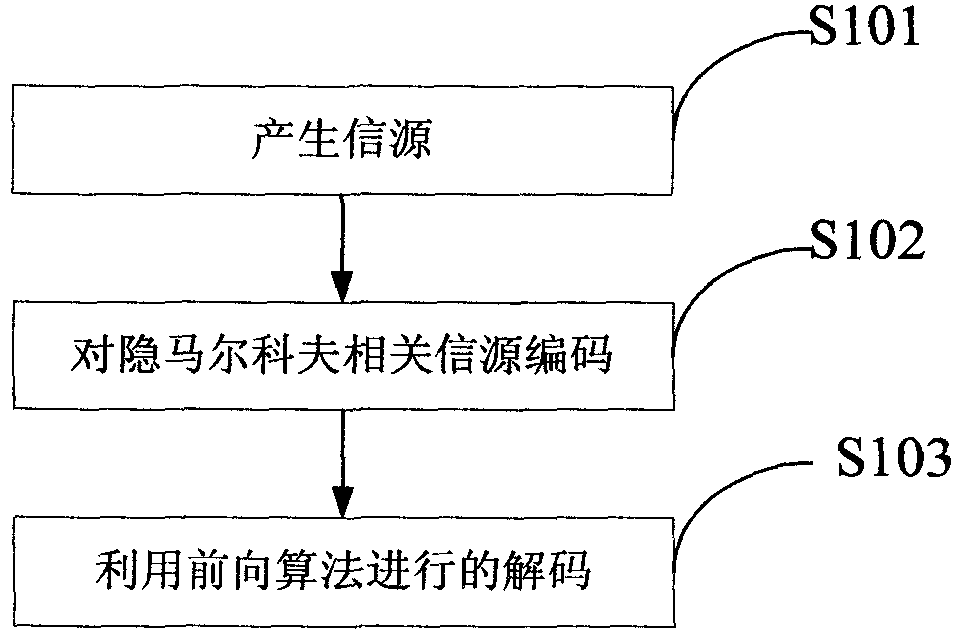

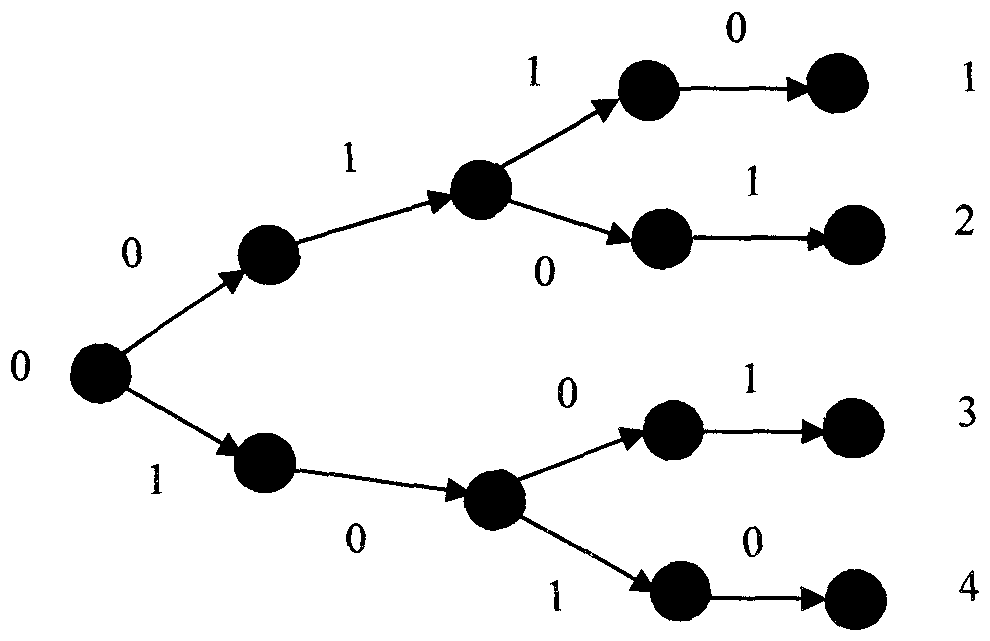

Hidden Markov related source coding method based on distributed arithmetic coding

The invention discloses a hidden Markov related source coding method based on distributed arithmetic coding. The hidden Markov related source coding method includes the following steps of generating sources, coding the Markov related sources, and decoding the Markov related sources by utilizing a forward algorithm. According to the hidden Markov related source coding method, the sources related to memory are compressed through a DAC. In the concrete realization process, the dependency among the sources is modeled to be one hidden Markov process. Experimental results show that execution results of the new scheme are close to the Slepian-Wolf theory bound, and the problems that ambiguous code words can exist on decoding ends and an SWC is asymmetrical after areas are overlapped in the existing SWC technology based on entropy coding are well solved. According to the hidden Markov related source coding method, the existing technology is well utilized, experimental results are good, and good application value is possessed.

Owner:NORTHWEST A & F UNIV

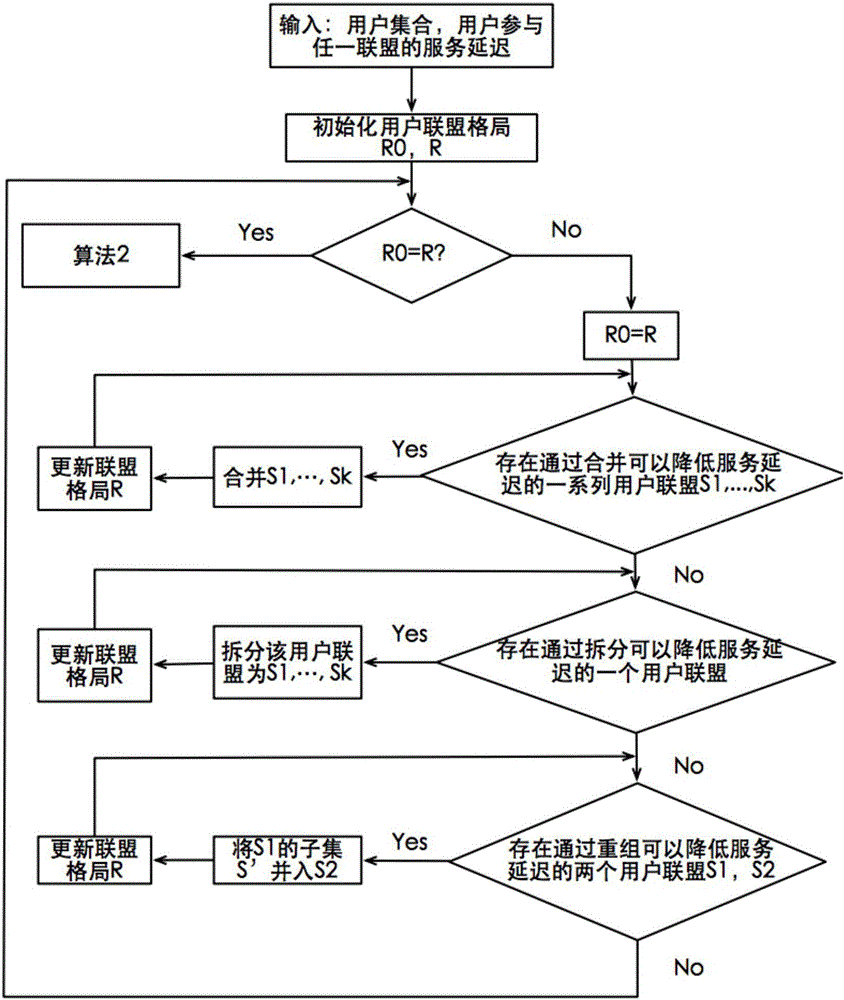

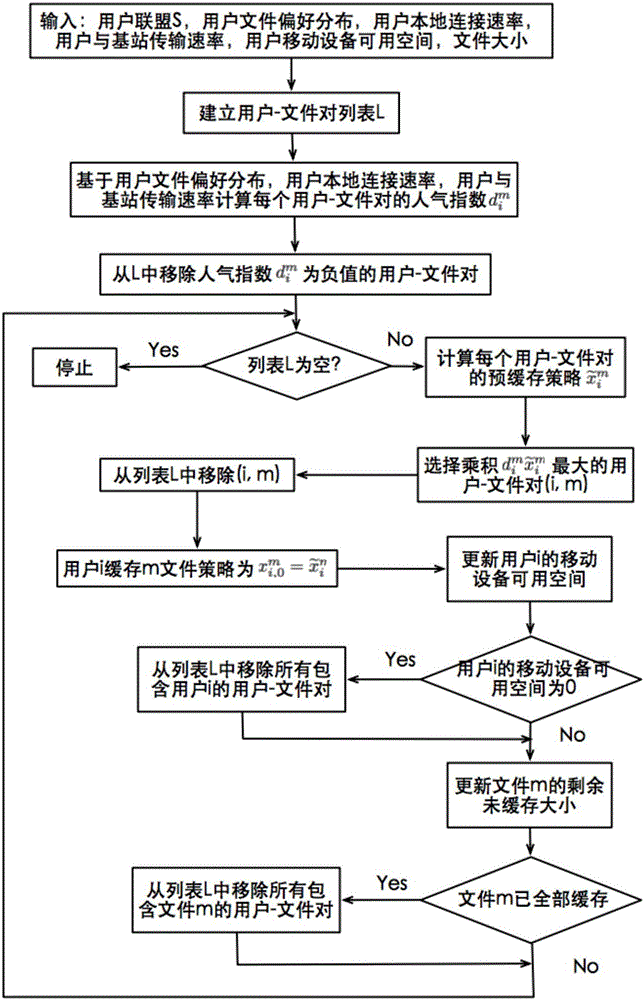

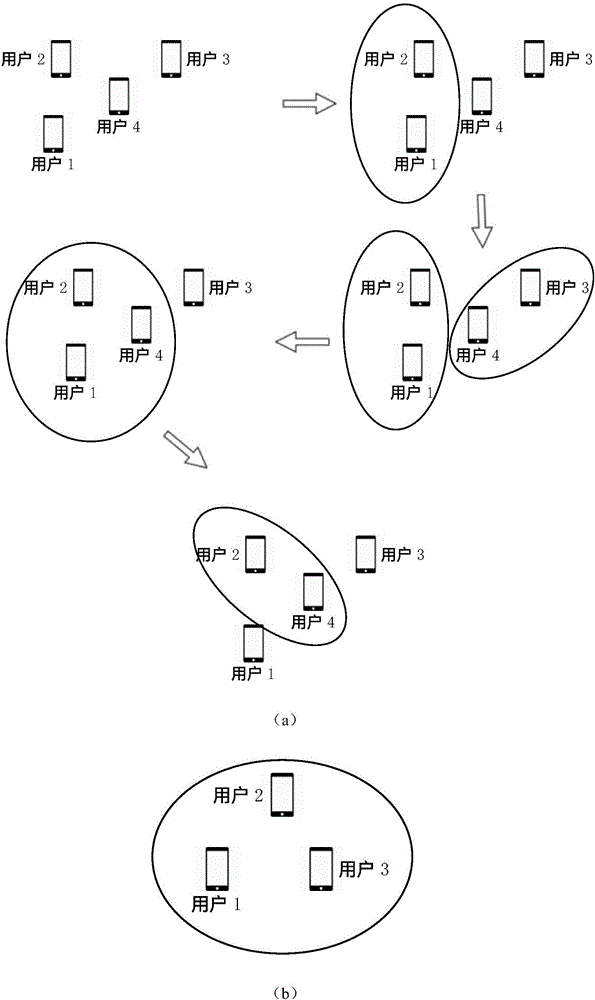

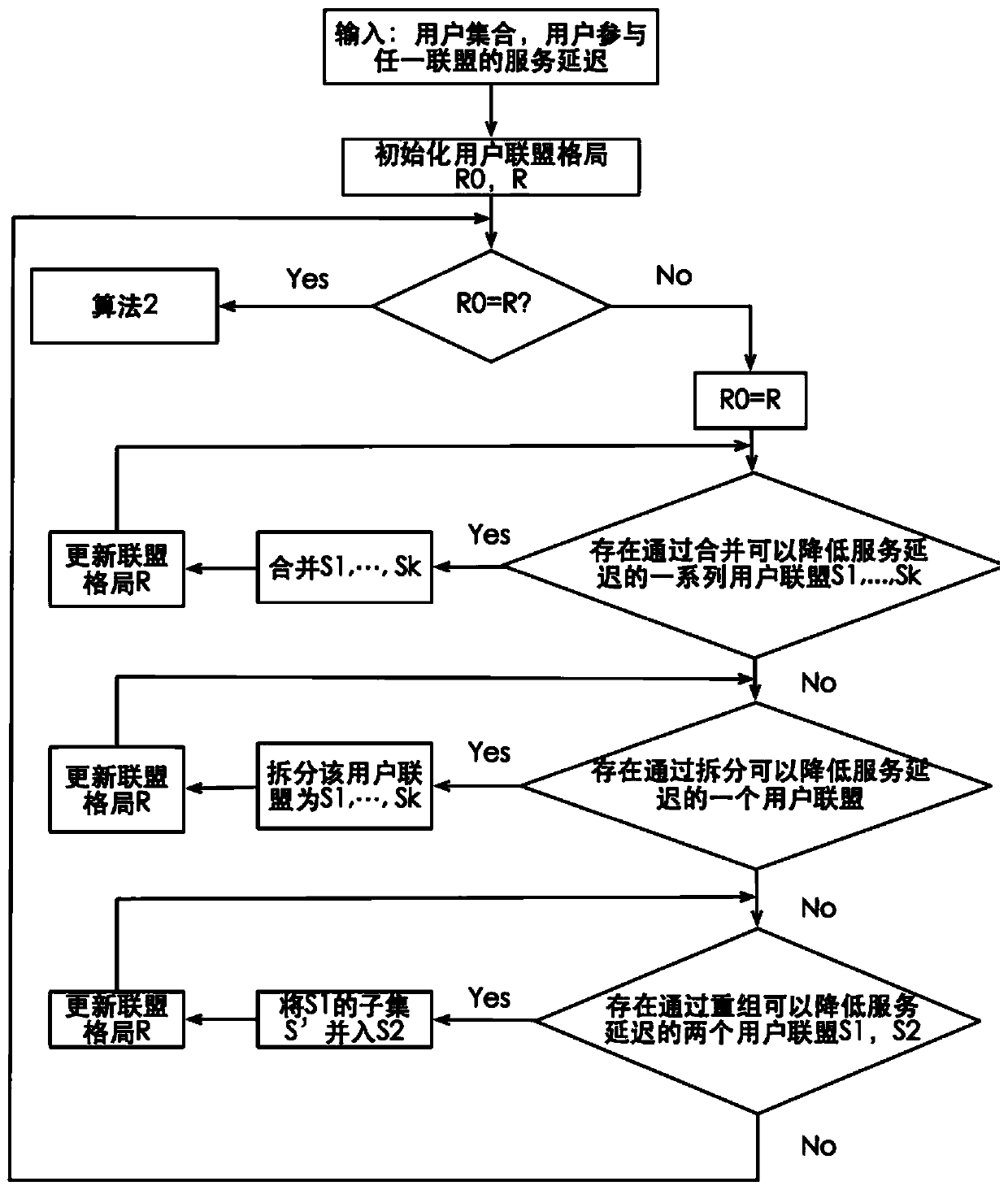

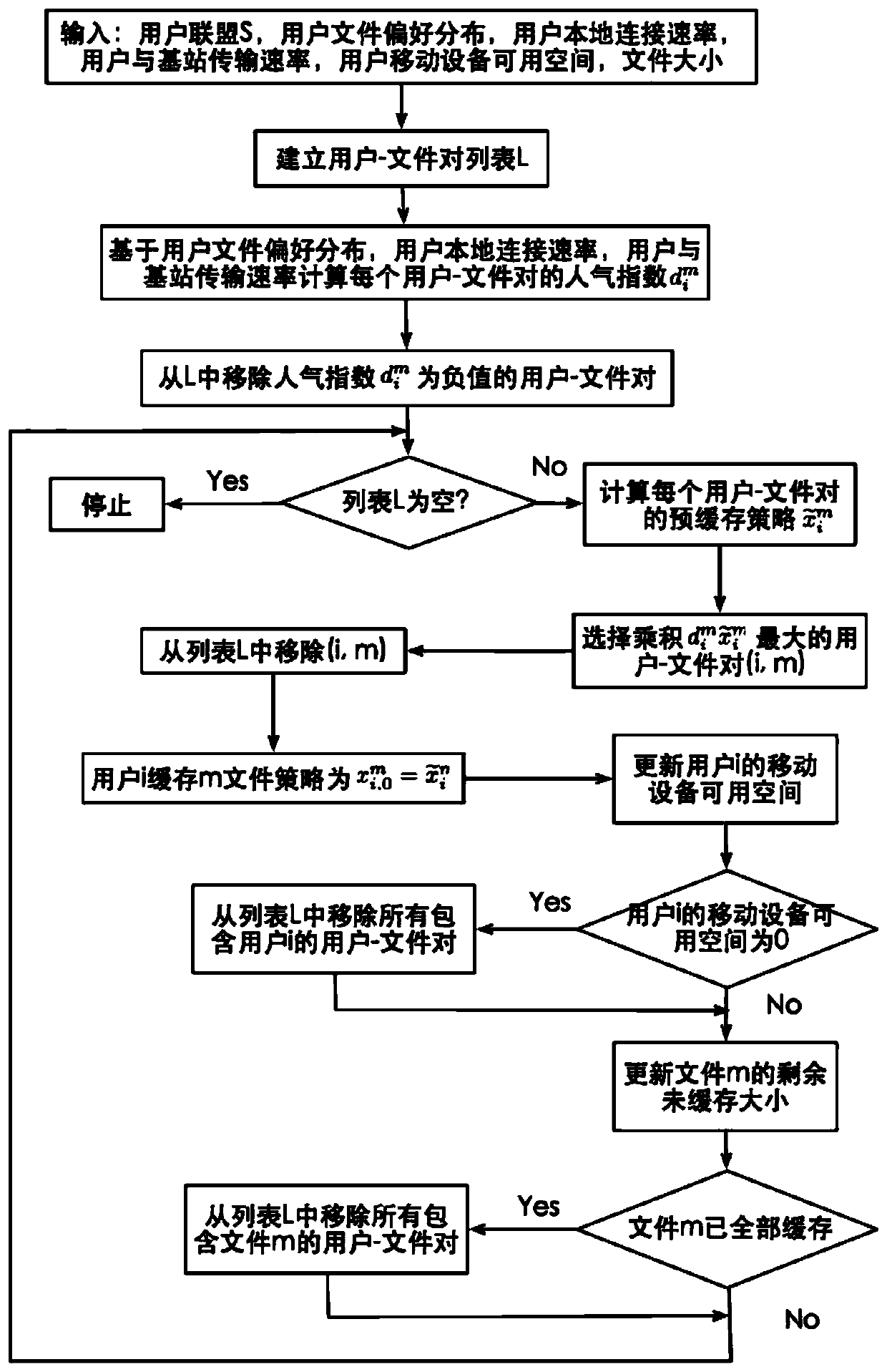

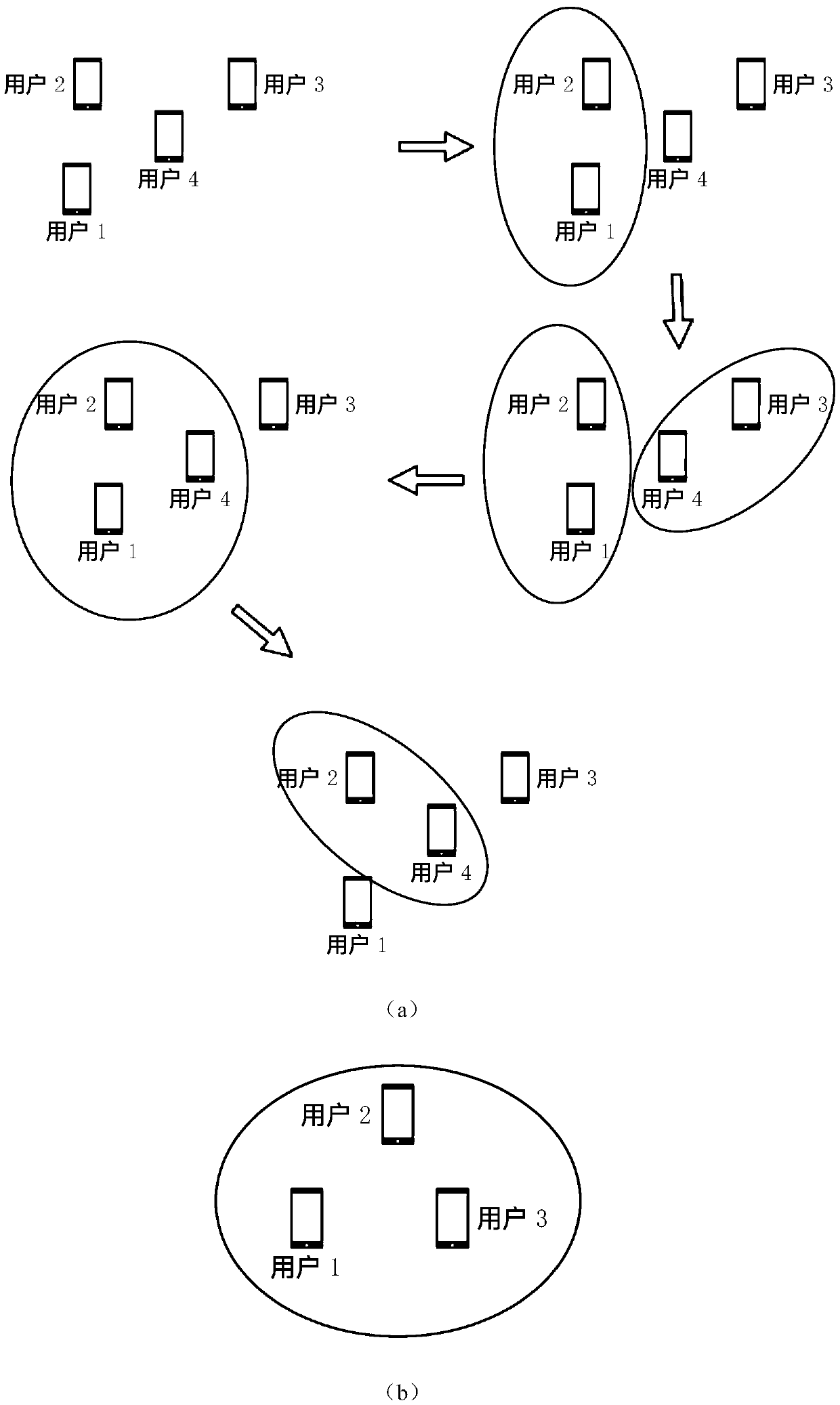

Shared method of native cache file based on mobile intelligence network

ActiveCN106708923AImprove satisfactionReduce transmission delayTransmissionSpecial data processing applicationsMobile deviceFile sharing

The invention discloses a shared method of native cache file based on mobile intelligence network. First builds a user alliance pattern based on gunz file shared network through cooperative game model, the user alliance pattern shares allied gather for muti-user file for user; formulates a best file cache strategy and a file shared strategy fora specific user alliance by adopting the user alliance pattern; user downloads from base station corresponding proportional file to local mobile device by the file cache strategy and the file shared strategy. The shared method main forms the shared user alliance of file based on the intelligence network, reduces transmission delay through a local connectivity; a distributed arithmetic of the user alliance pattern is achieved and has unit reasonability, Dhp stability and agreement stability; introduces concept of file popularity index, confirms the best cache strategy through minimized total transmission delay of the user alliance, the mobile network transmission delay can be reduced.

Owner:WUHAN UNIV

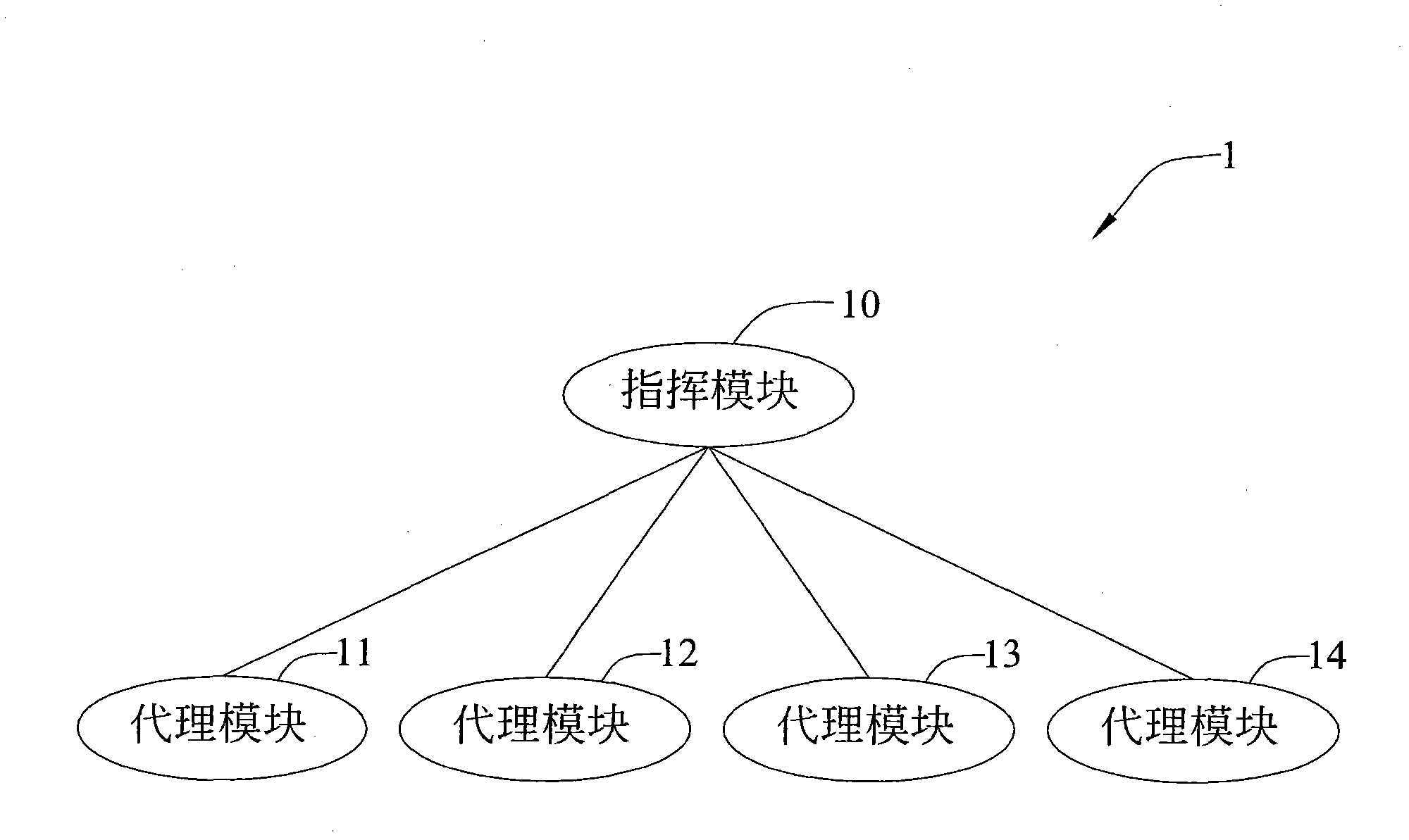

Distributed arithmetic system applied to video monitoring platform

InactiveCN102882910ADoes not affect processing performanceTransmissionVideo monitoringComputer module

A distributed arithmetic system applied to a video monitoring platform comprises a command module (Headquarter), and a plurality of agent modules connected with the command module. The command module is used to cut the video data received by the video monitoring platform into a plurality of video units, and send the plurality of video units to the agent modules respectively, so that the agent modules can carry out video identification and analysis on the received video units; after the agent modules identifies and analyzes the video, the identification and analysis results are transmitted back to the command module, so that the command module can carry out integration.

Owner:CHUNGHWA TELECOM CO LTD

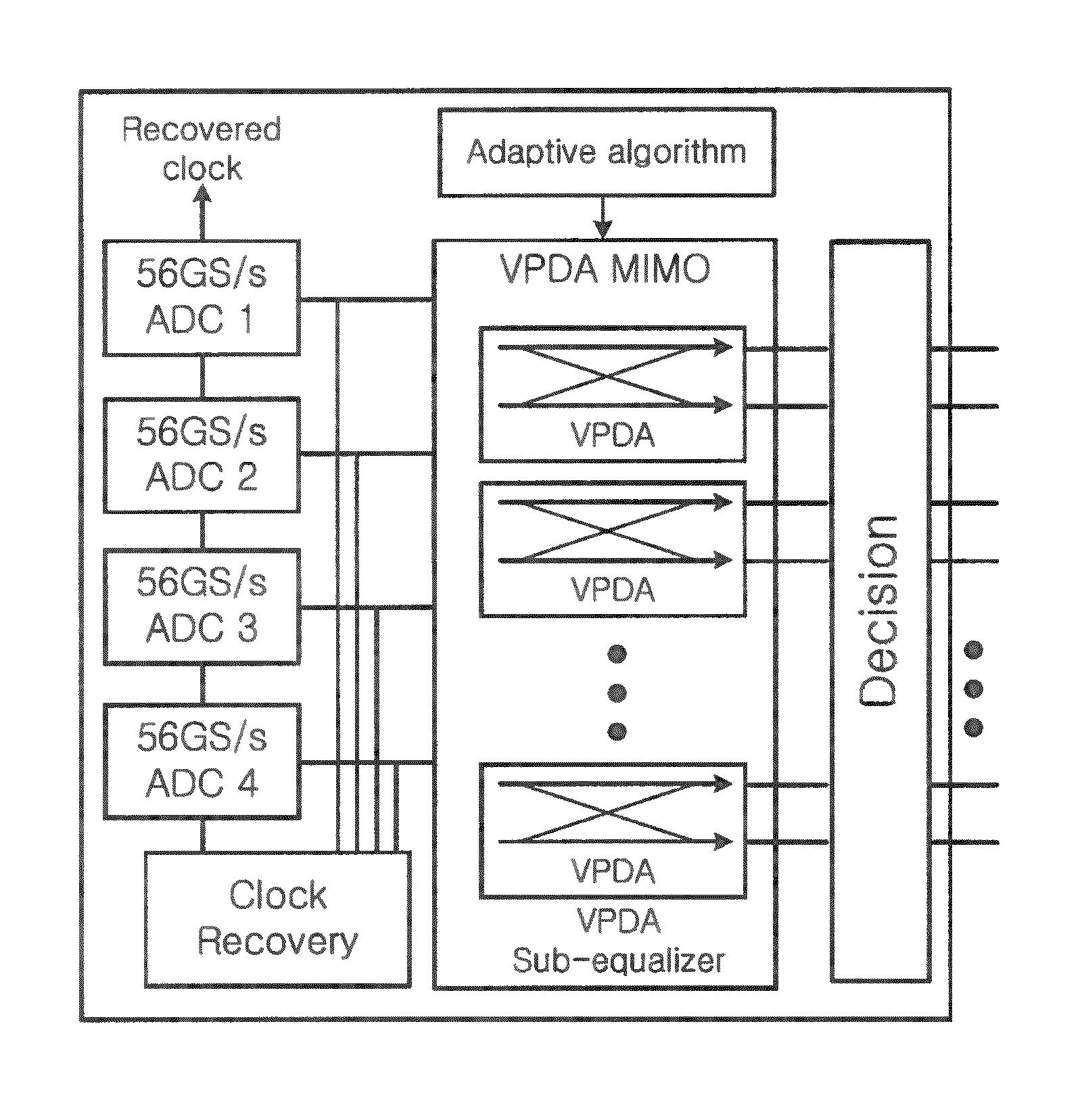

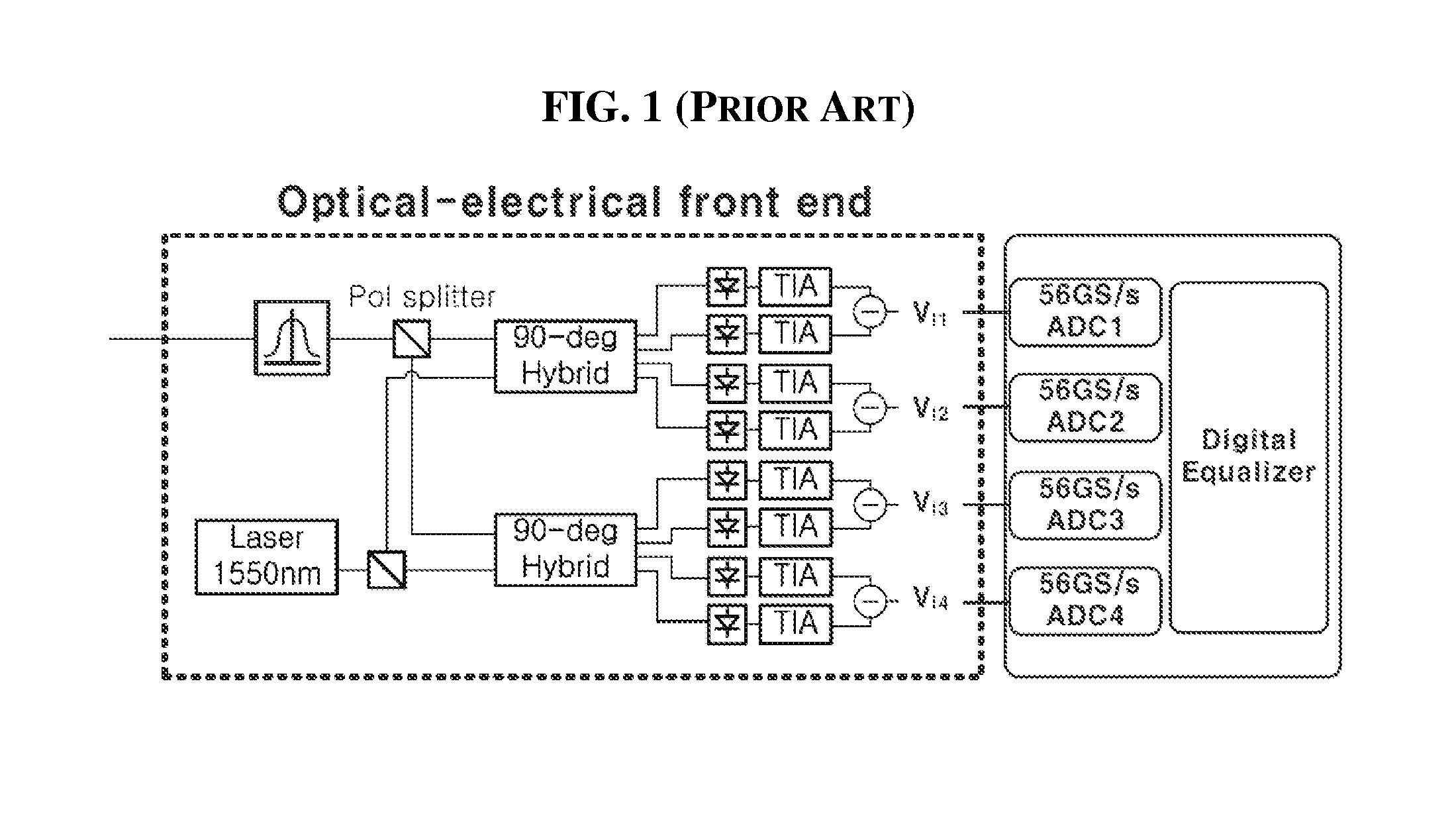

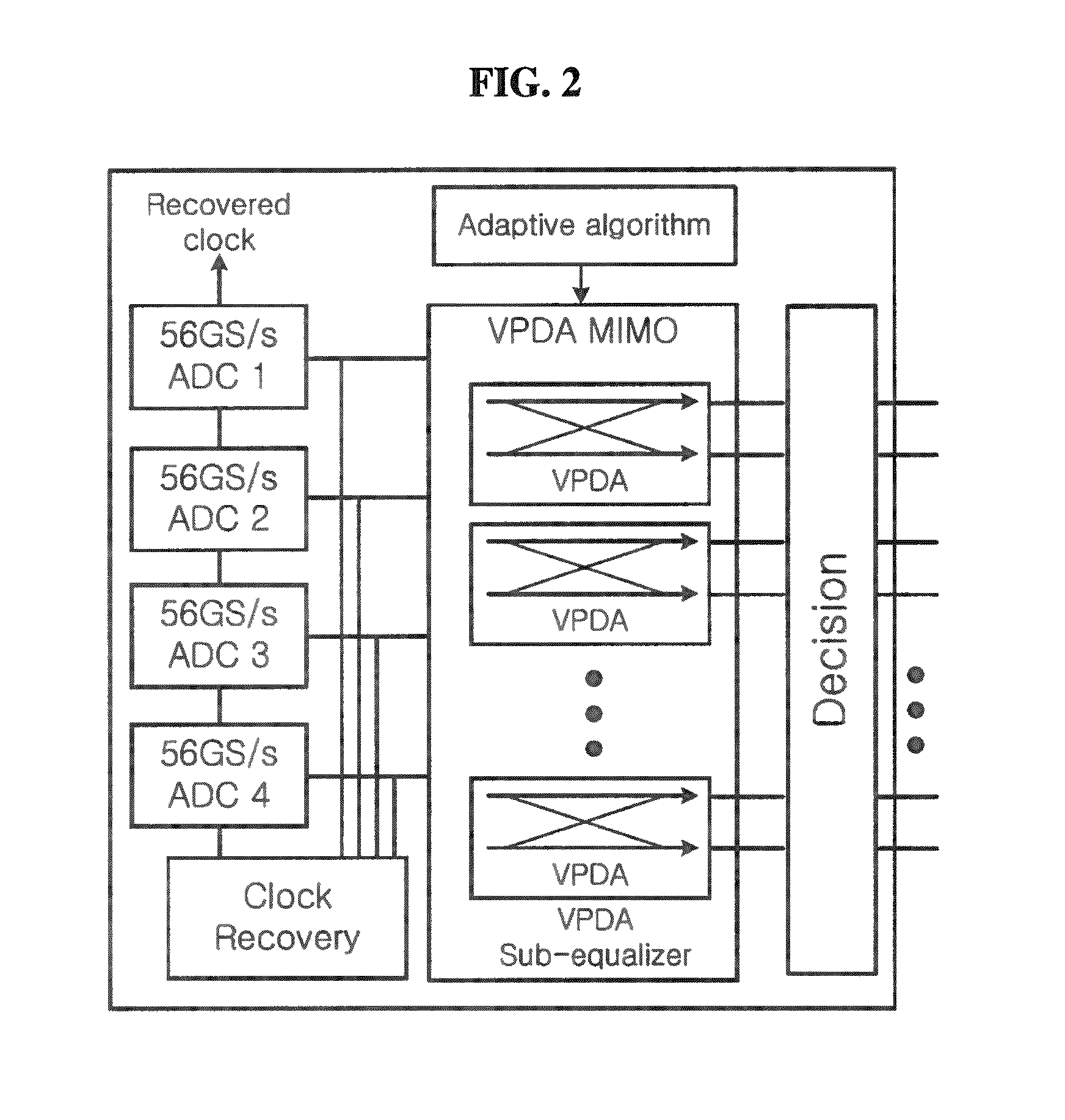

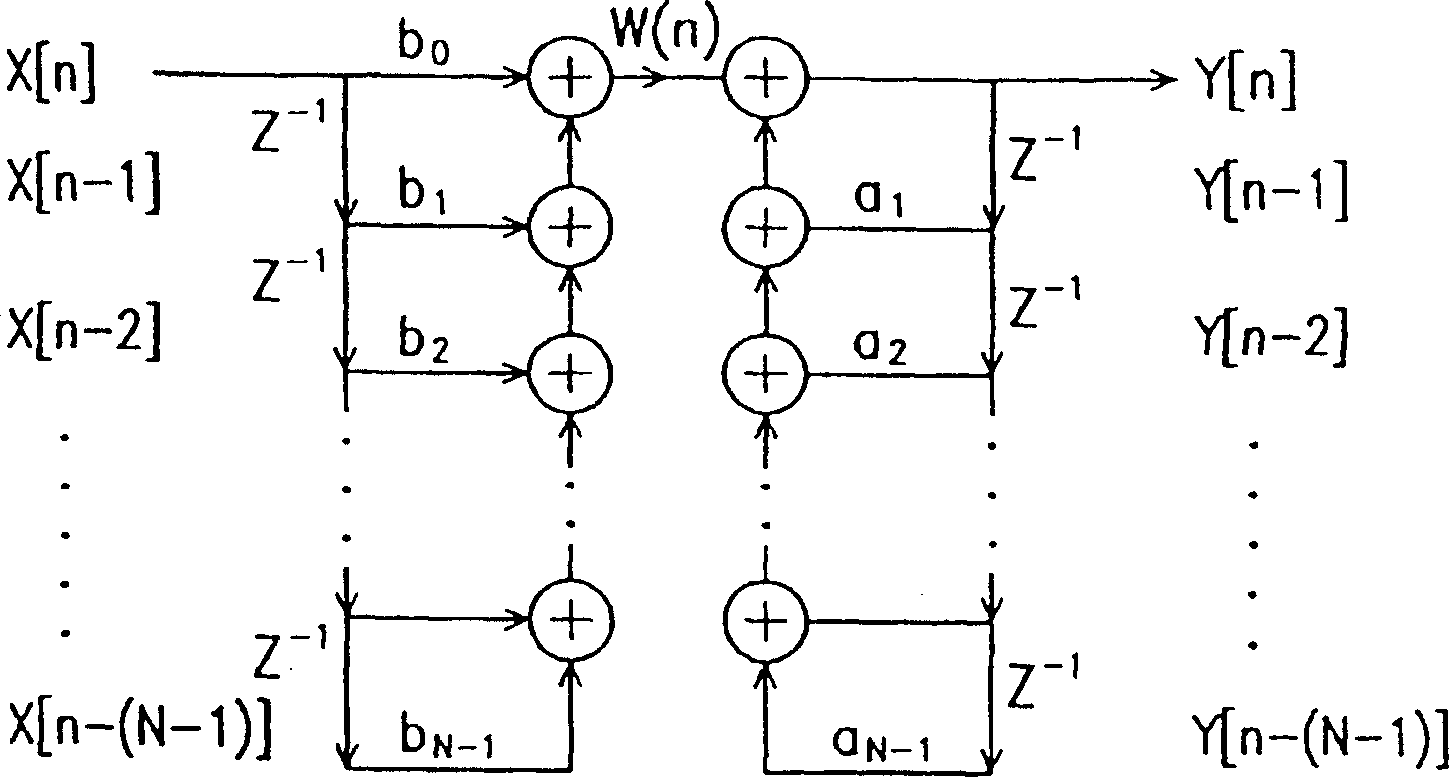

Variable-precision distributed arithmetic multi-input multi-output equalizer for power-and-area-efficient optical dual-polarization quadrature phase-shift-keying system

A variable-precision distributed arithmetic (VPDA) multi-input multi-output (MIMO) equalizer is presented to reduce the size and dynamic power of 112 Gbps dual-polarization quadrature phase-shift-keying (DP-QPSK) coherent optical communication receivers. The VPDA MIMO equalizer compensates for channel dispersion as well as various non-idealities of a time-interleaved successive approximation register (SAR) based analog-to-digital converter (ADC) simultaneously by using a least mean square (LMS) algorithm. As a result, area-hungry analog domain calibration circuits are not required. In addition, the VPDA MIMO equalizer achieves 45% dynamic power reduction over conventional finite impulse response (FIR) equalizers by utilizing the minimum required resolution for the equalization of each dispersed symbol.

Owner:INTEGRATED DEVICE TECH INC

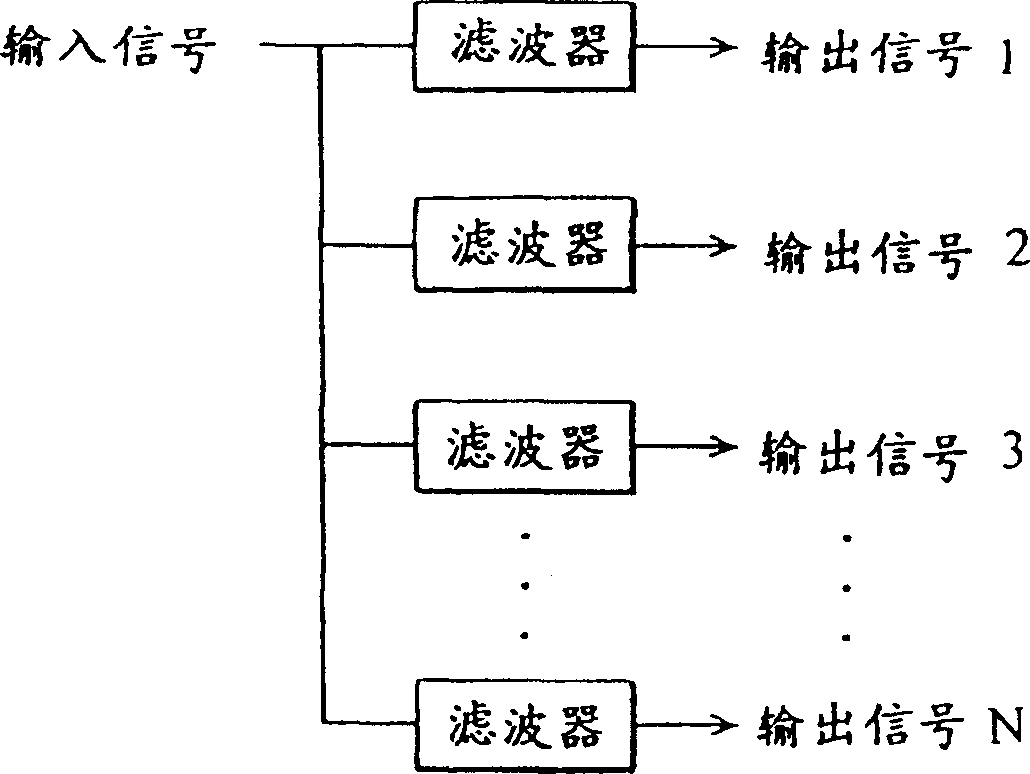

Method for implementing digit filter group structure

InactiveCN1448865ASmall structureReduce the numberComplex mathematical operationsDigital filterTime-division multiplexing

The digital filter combination structure includes input signal selecting unit, filter combination unit and frequency band selecting unit; and has combined discrete sampling multiple rate system and distributive mathematical algorithm. The discrete sampling multiple rate system operates on discrete sampling principle and has dendritic structure, time division multiplexing and circulative feedbackto reduce hardware size of the digital filter combination structure. The digital filter combination with distributive mathematical algorithm, table look-up technique and hardware with memory is usedin processing language, music tone, image, etc.

Owner:UNITED MICROELECTRONICS CORP

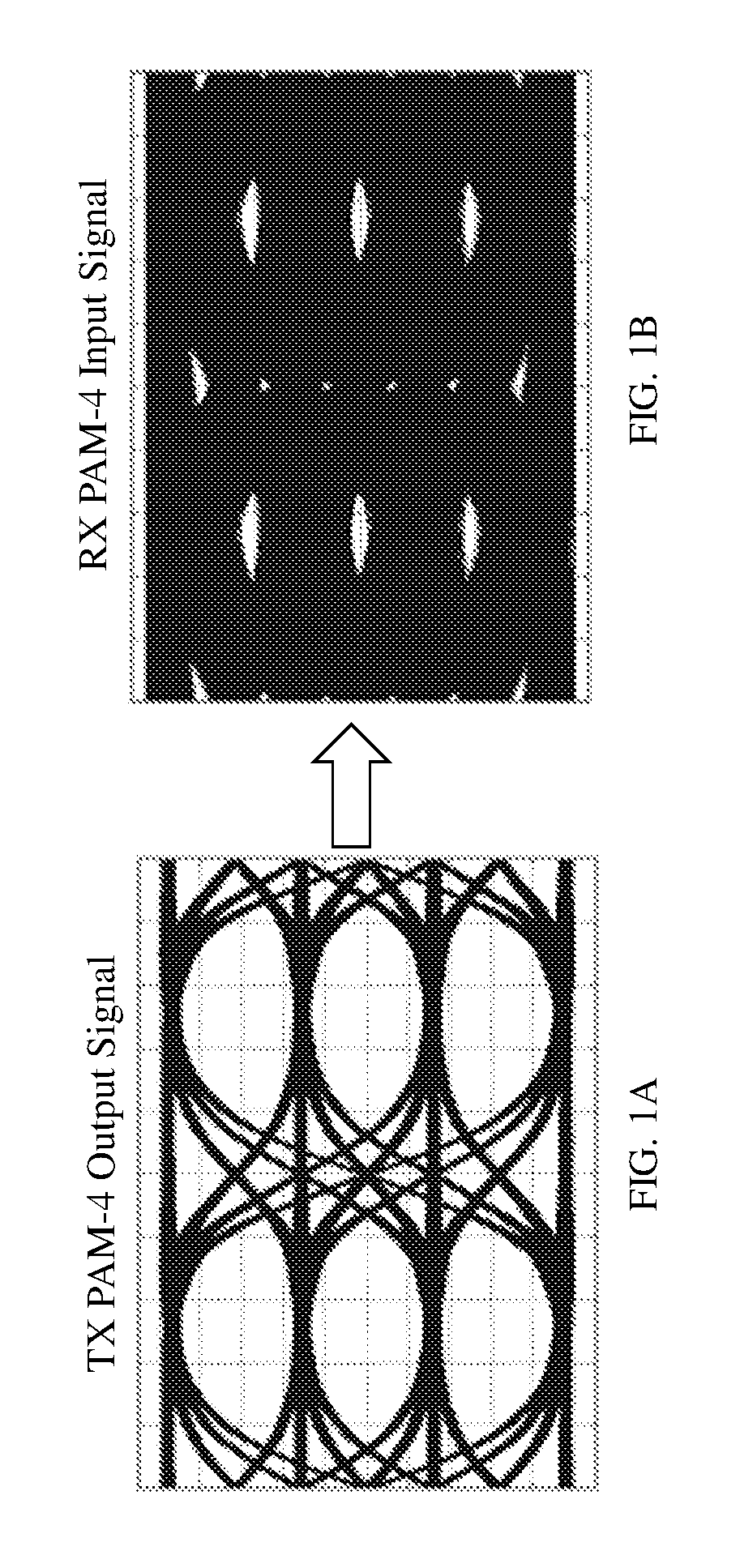

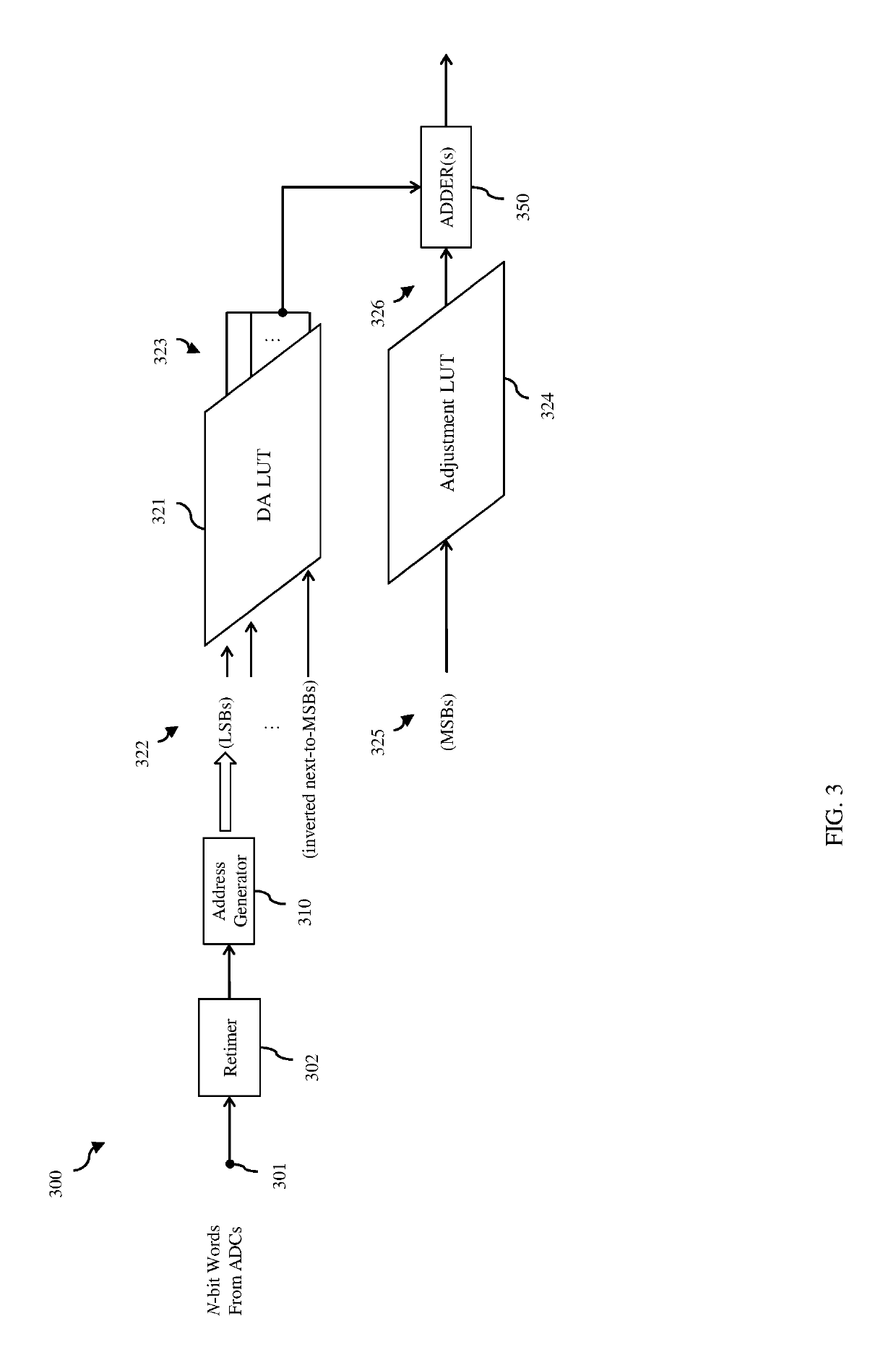

Feed forward equalizer with power-optimized distributed arithmetic architecture and method

ActiveUS10432436B1Reduce complexityReduce power consumptionDigital data processing detailsCode conversionParallel computingPartial product

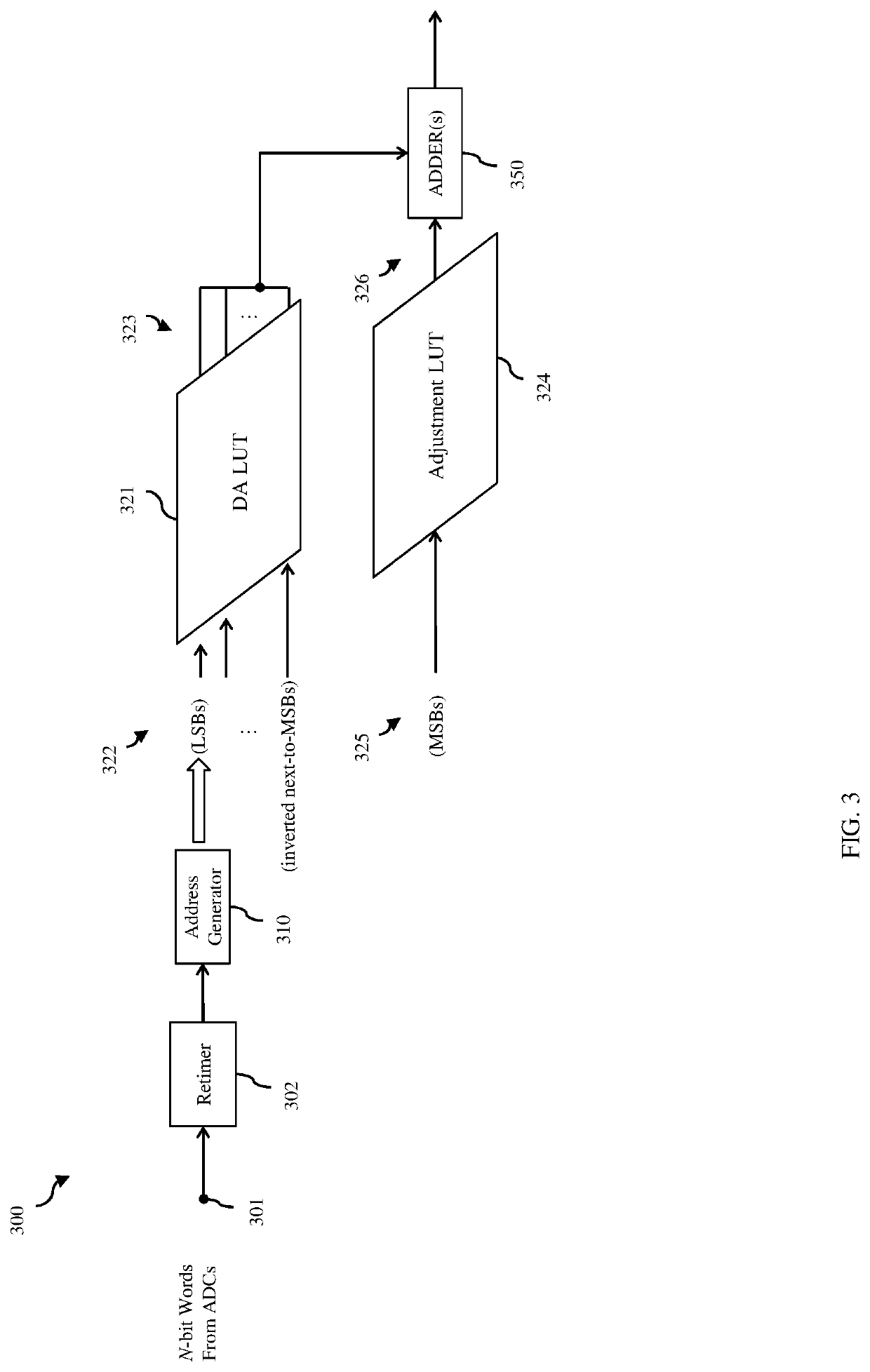

A distributed arithmetic feed forward equalizer (DAFFE) and method. The DAFFE includes look-up tables (LUTs) in offset binary format. A DA LUT stores sum of partial products values and an adjustment LUT stores adjustment values. DA LUT addresses are formed from same-position bits from all but the most significant bits (MSBs) of a set of digital words of taps and an adjustment LUT address is formed using the MSBs. Sum of partial products values and an adjustment value are acquired from the DA LUT and the adjustment LUT using the DA LUT addresses and the adjustment LUT address, respectively. Reduced complexity downstream adder(s) (which result in reduced power consumption) compute a total sum of the sum of partial products values and the adjustment value (which compensates for using the offset binary format and dropping of the MSBs when forming the DA LUT addresses) to correctly solve a DA equation.

Owner:MARVELL ASIA PTE LTD

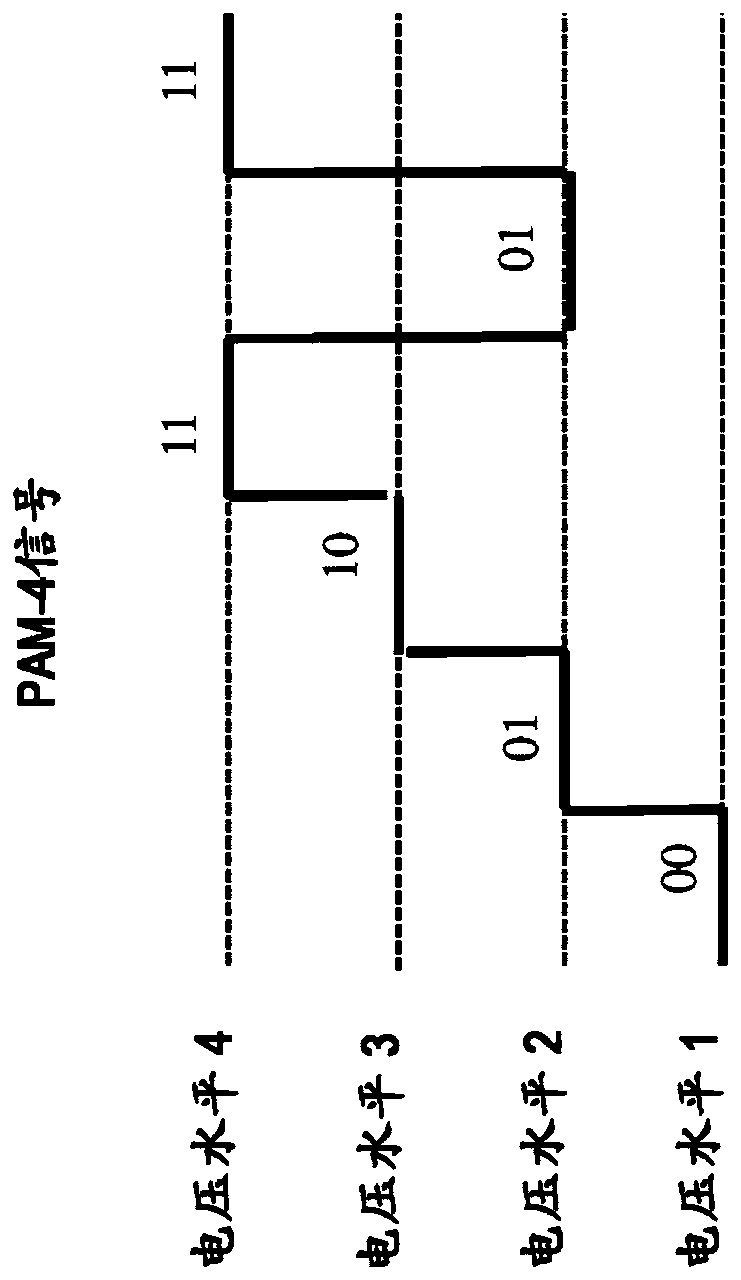

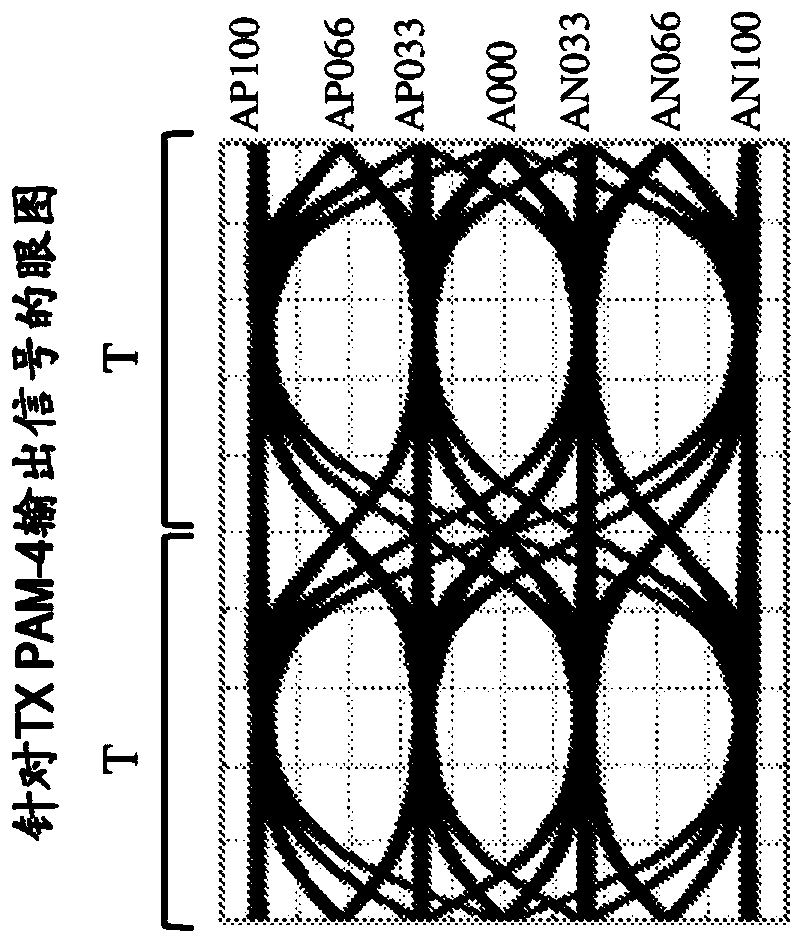

On-demand feed forward equalizer with distributed arithmetic architecture and method

The invention relates to an On-demand feed forward equalizer with distributed arithmetic architecture and a method. Disclosed is a power-optimized distributed arithmetic (DA)-based feed forward equalizer (FFE) that performs on-demand equalization processing of a data sample. Specifically, a data stream is represented by digital words, which indicate signal levels at taps on a transmission medium.A screener applies formulas to selected taps as opposed to all taps (e.g., to the main cursor tap, which corresponds to the current data sample, and to specific pre-cursor and post-cursor taps, whichcorrespond to immediately proceeding and following data samples) to determine whether the current data sample (which should indicate a specific two-bit symbol) has degraded during transmission to a point where equalization processing is required. If so, a bypass flag is set to a first level so that the data sample is subjected to equalization processing. If not, the bypass flag is set to a secondlevel so that such processing is bypassed. Also disclosed is a corresponding method.

Owner:MARVELL ASIA PTE LTD

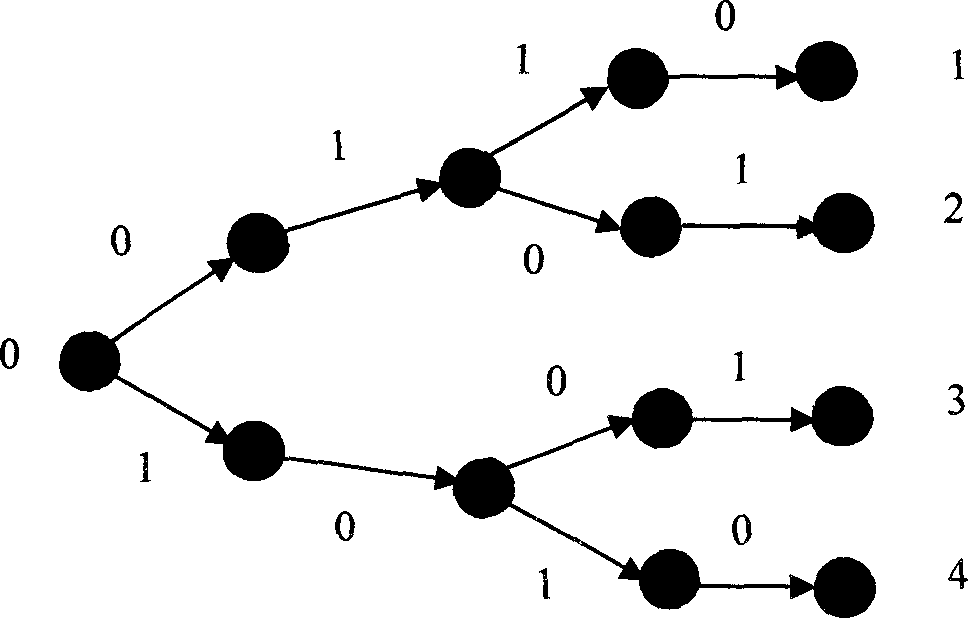

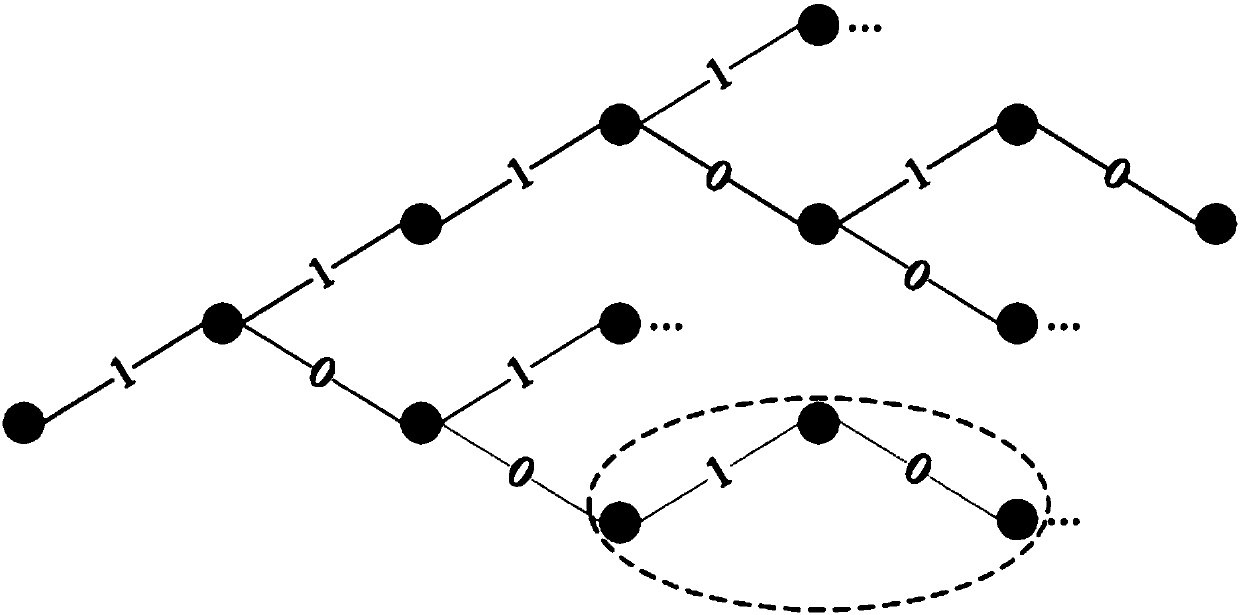

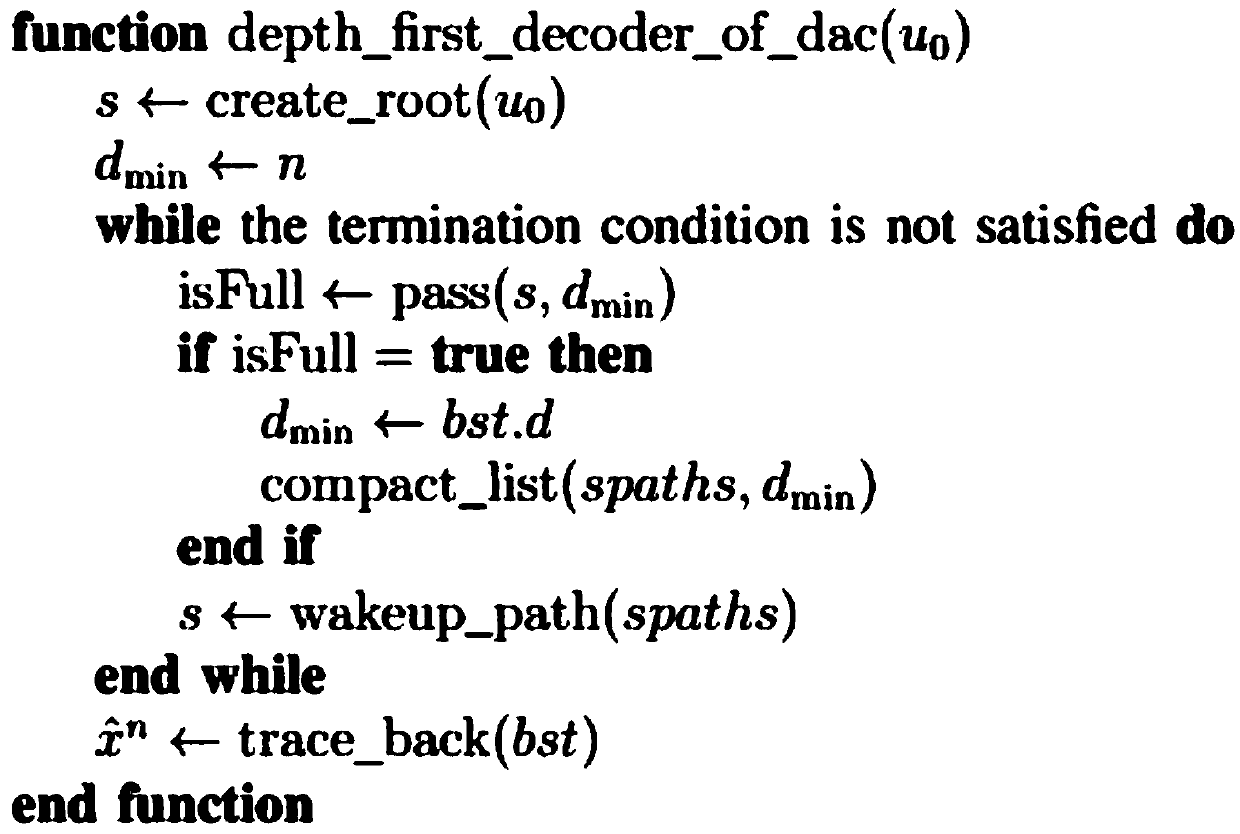

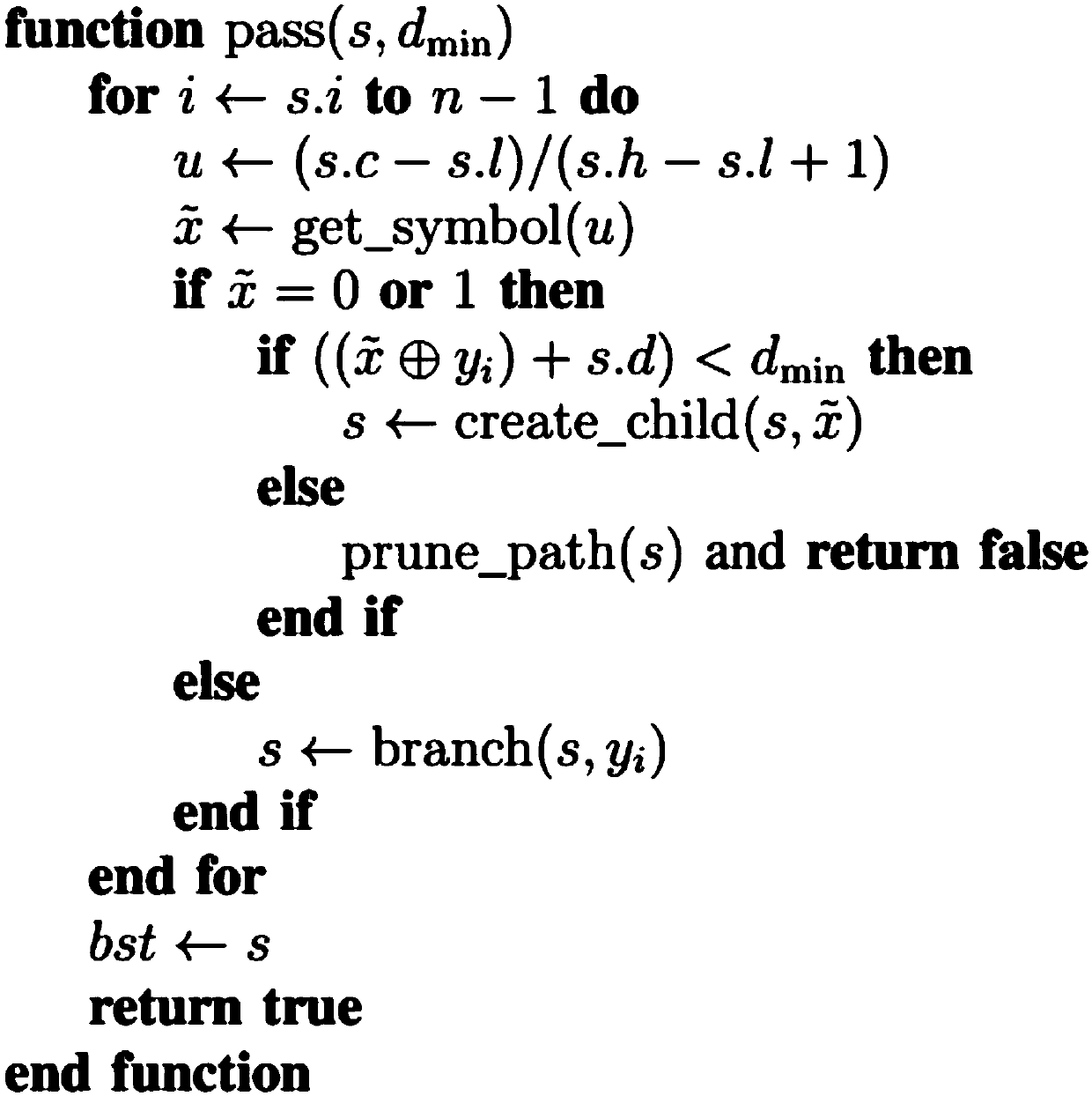

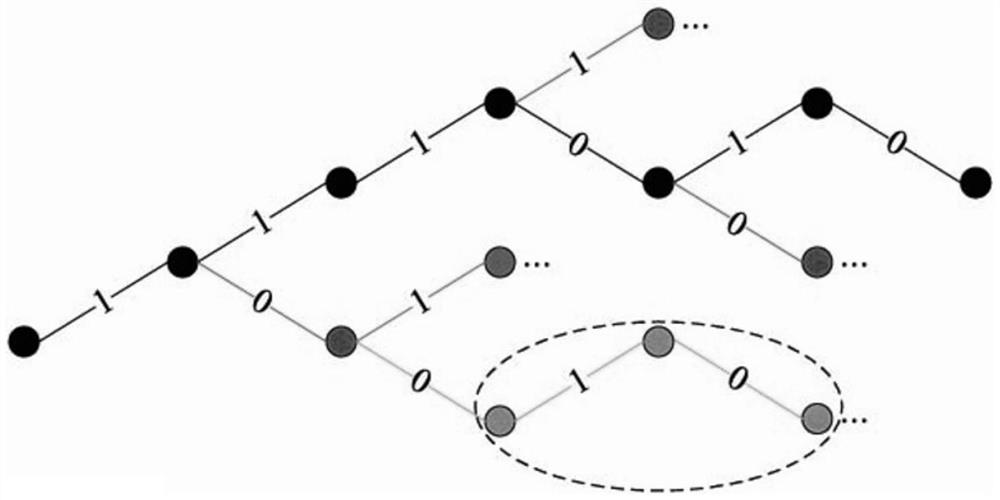

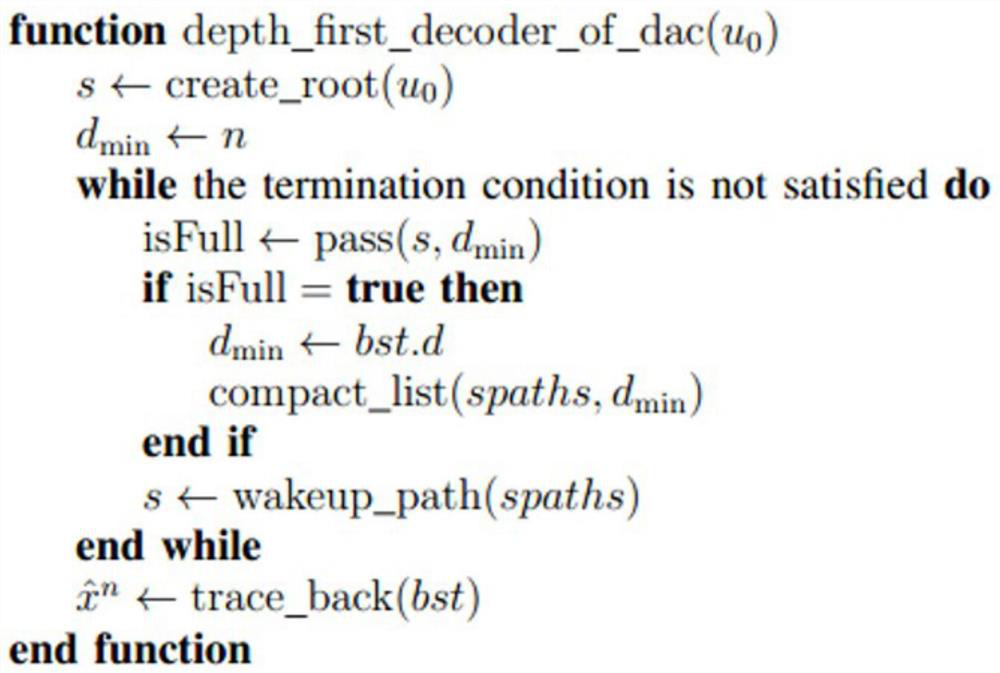

Distributed arithmetic code decoding method based on depth-first

InactiveCN107294656AEasy to implementError preventionCode conversionCoding decodingArithmetic coding

The invention discloses a distributed arithmetic code decoding method based on depth-first, and the method comprises the following contents: a data structure and a global variable; depth-first decoding summary; single-path searching; decoder behaviors at a fork node; compression end node pause path list; online memory releasing; optimal pause path selection; and ending conditions. According to the invention, compared with the conventional breadth-first decoding, the depth-first decoding is better in short code execution.

Owner:CHANGAN UNIV

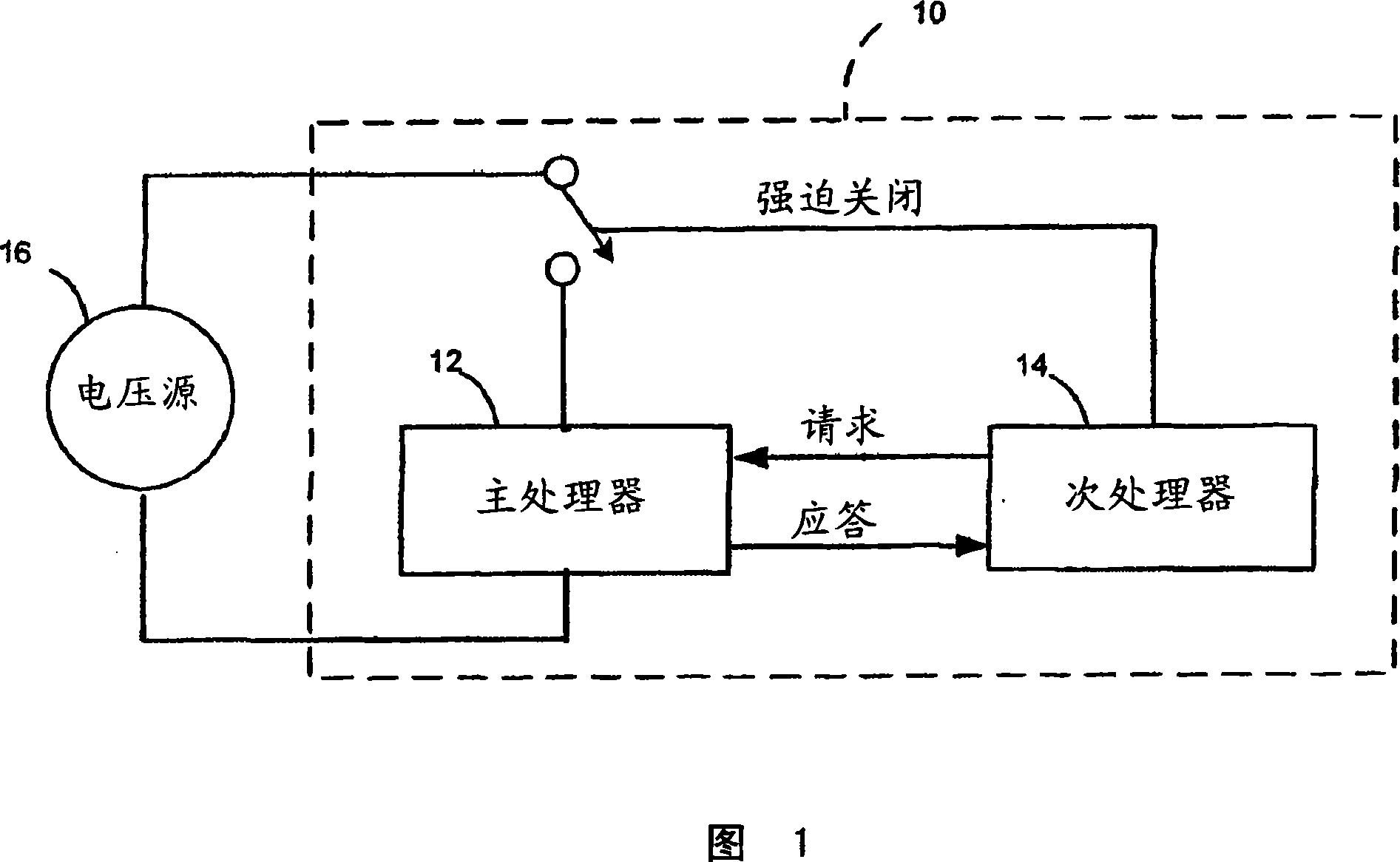

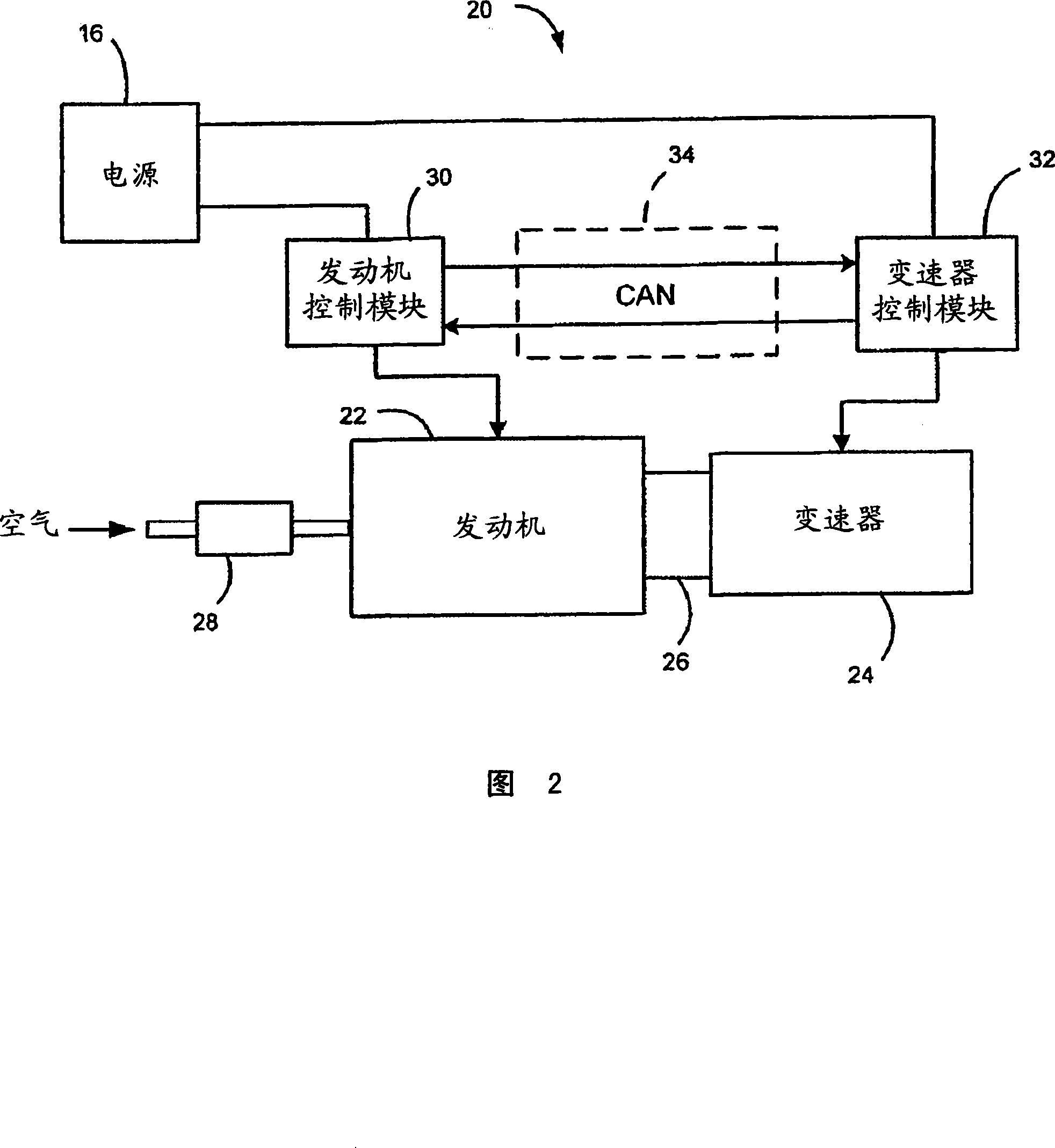

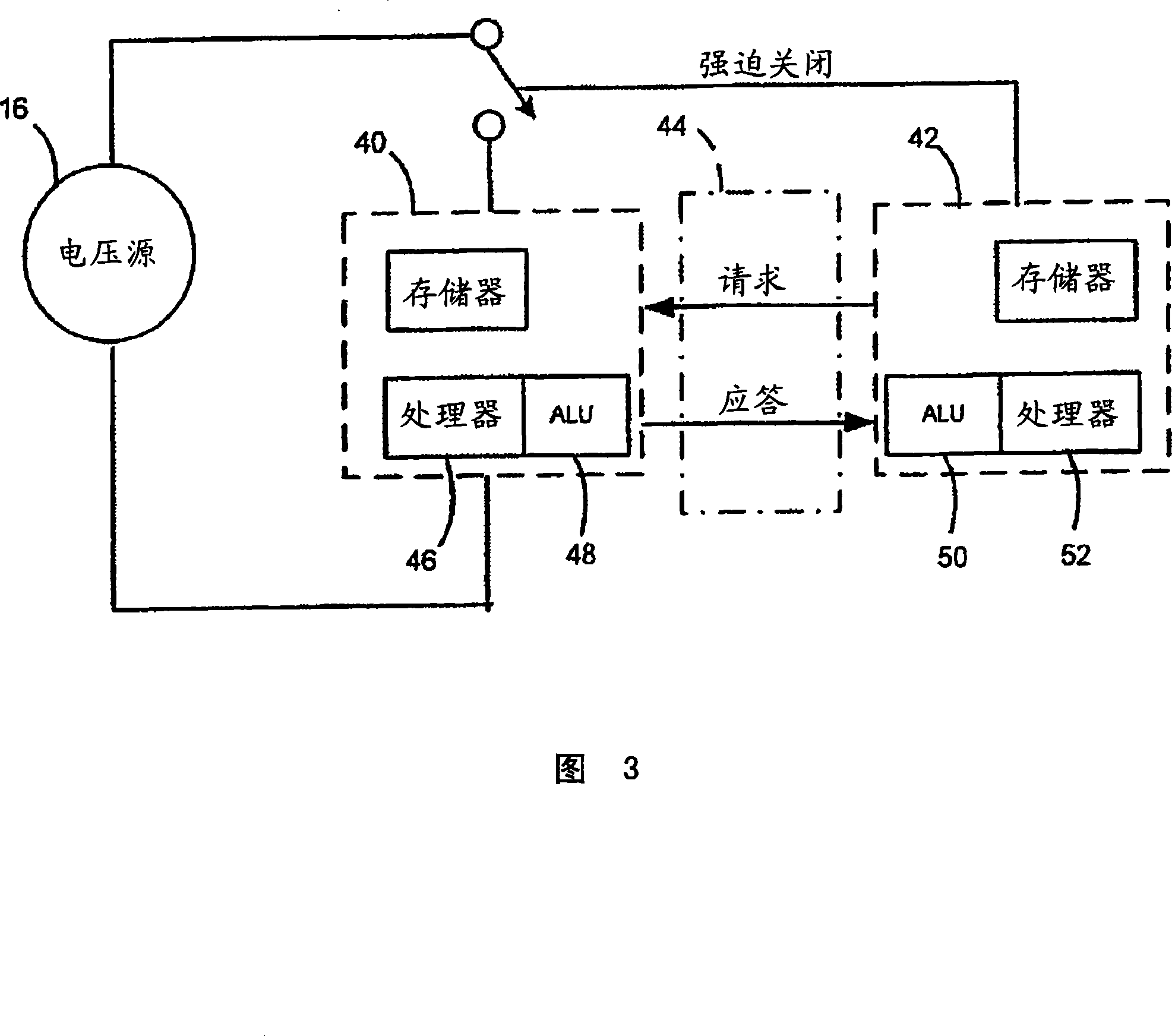

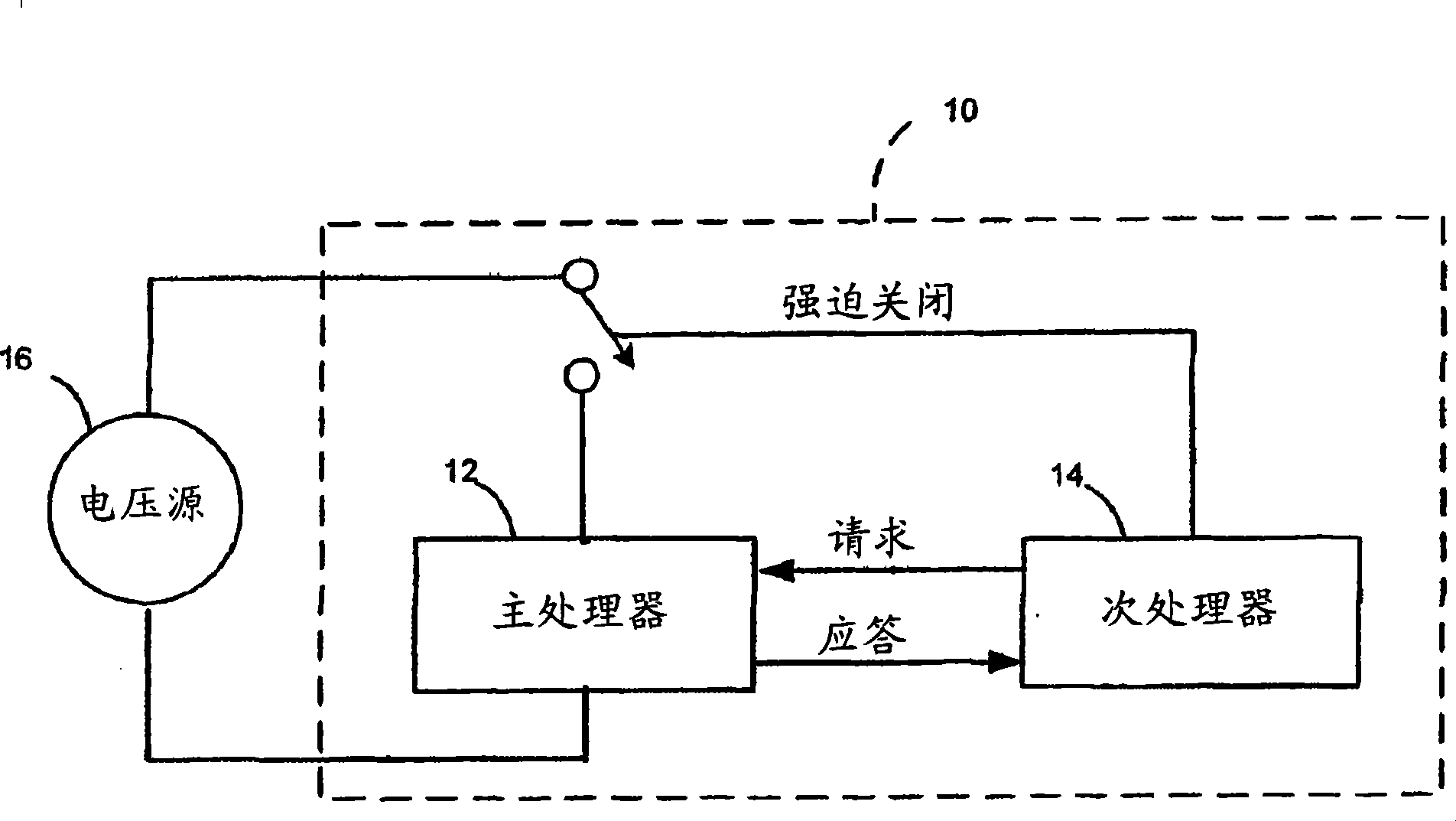

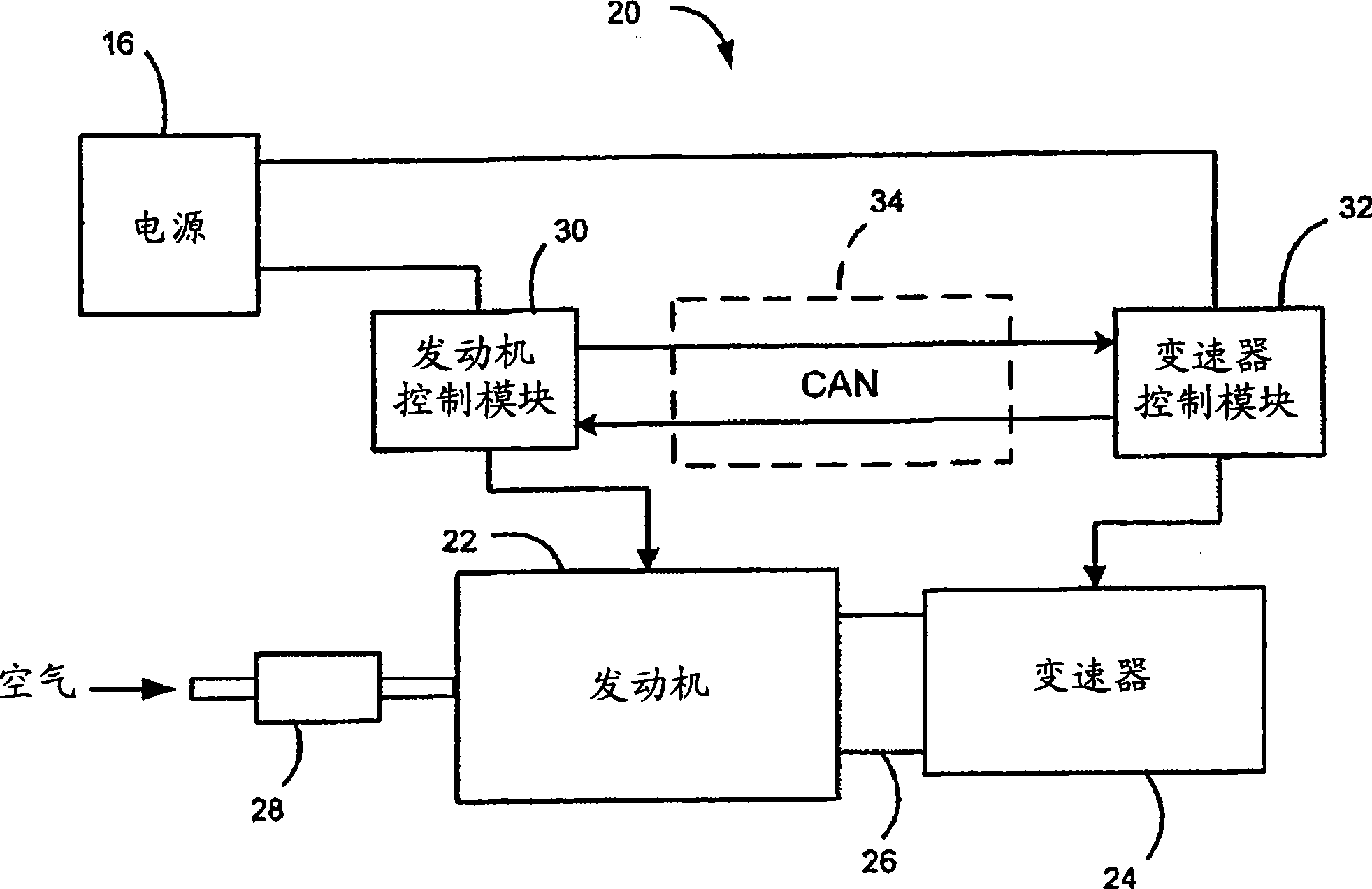

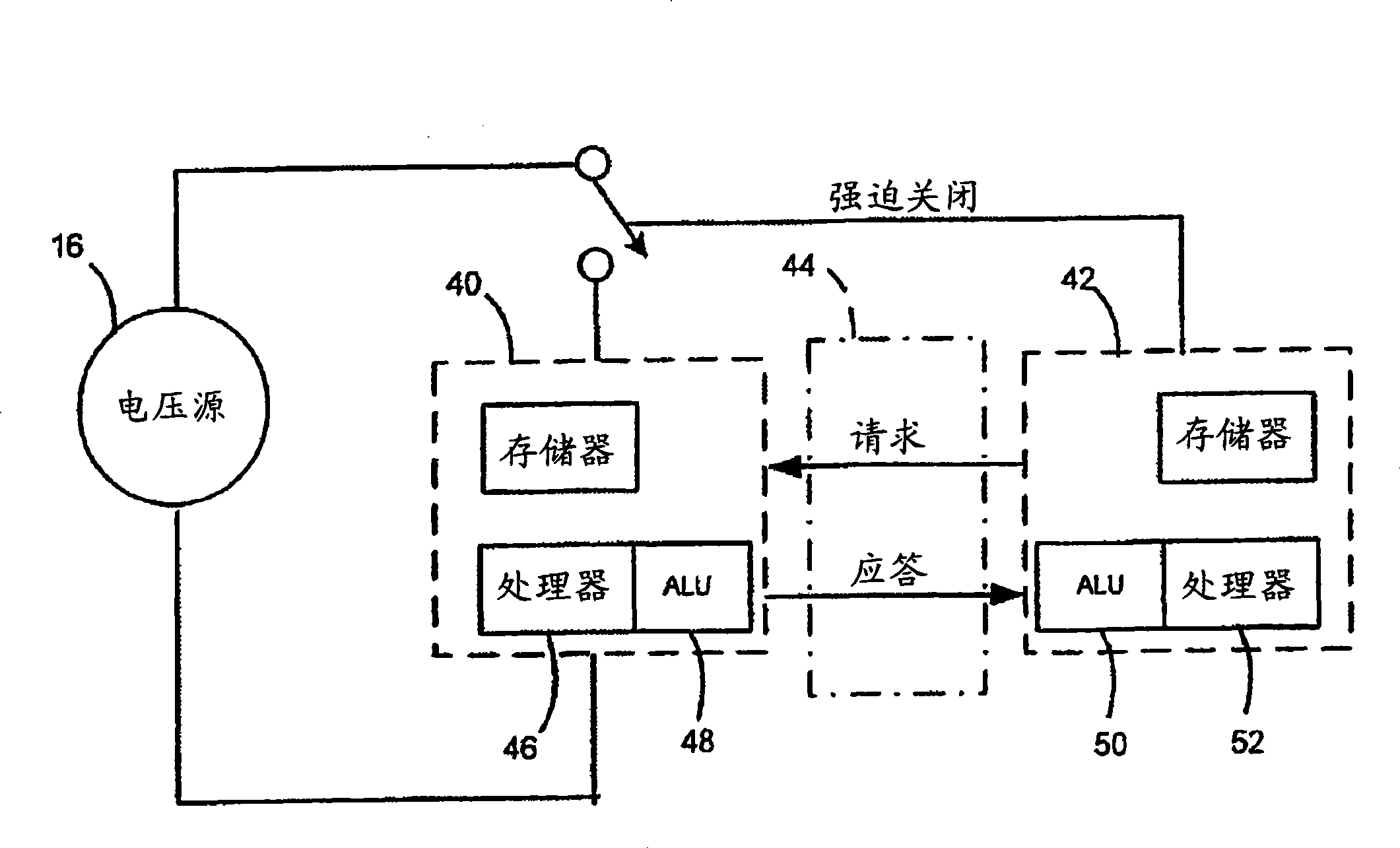

Distributed arithmetic logic unit security check

InactiveCN101221444ASafety arrangmentsRegistering/indicating working of vehiclesSecurity checkDiagnostic system

A vehicle diagnostic system is provided. The system includes: a first control module that includes a first processor and that controls a first vehicle subsystem; and second control module that controls a second vehicle subsystem and that validates the functionality of the first processor of the first control module wherein if the second control module determines that the first processor of the first control module is faulty, the second control module shuts down the first control module.

Owner:GM GLOBAL TECH OPERATIONS LLC

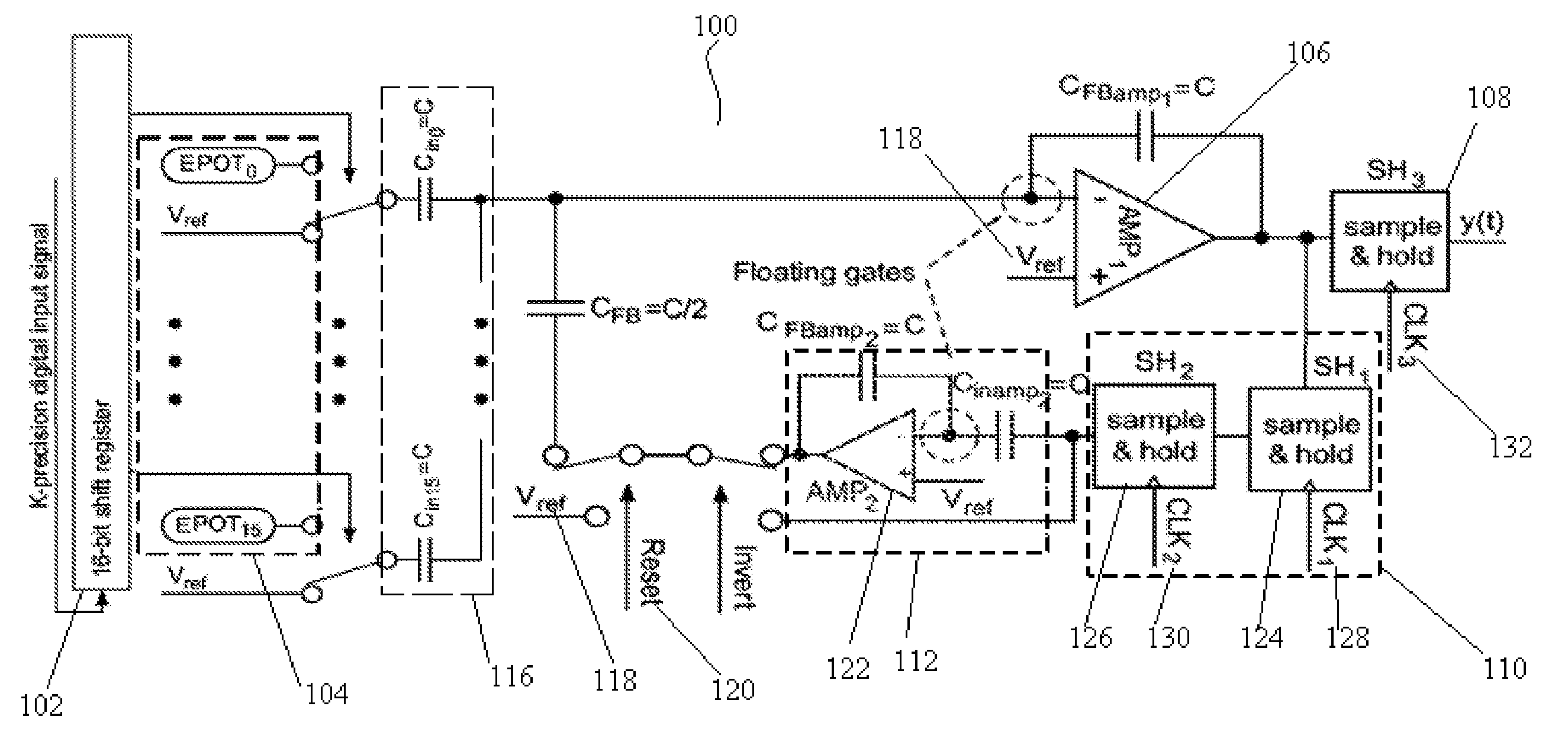

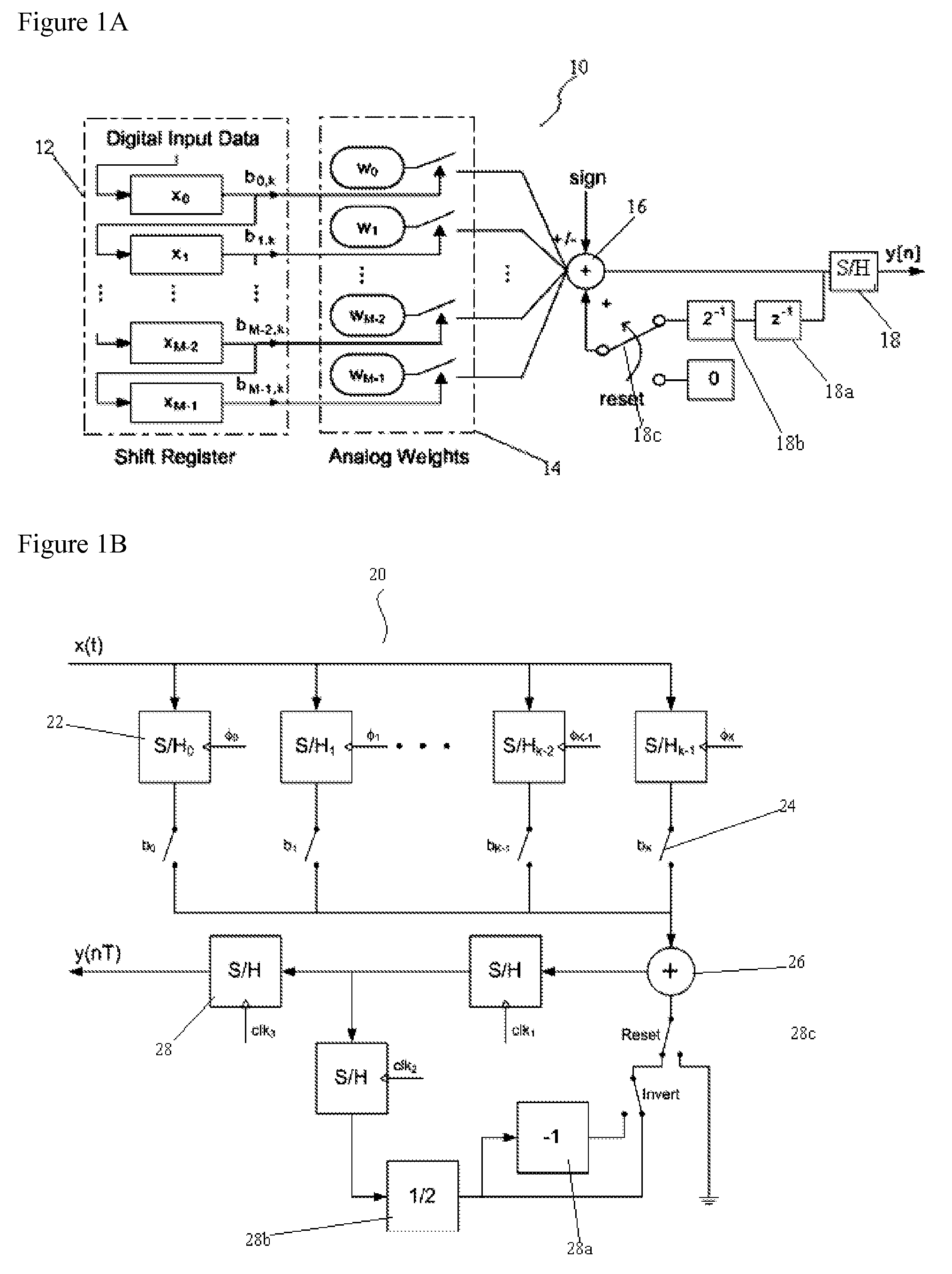

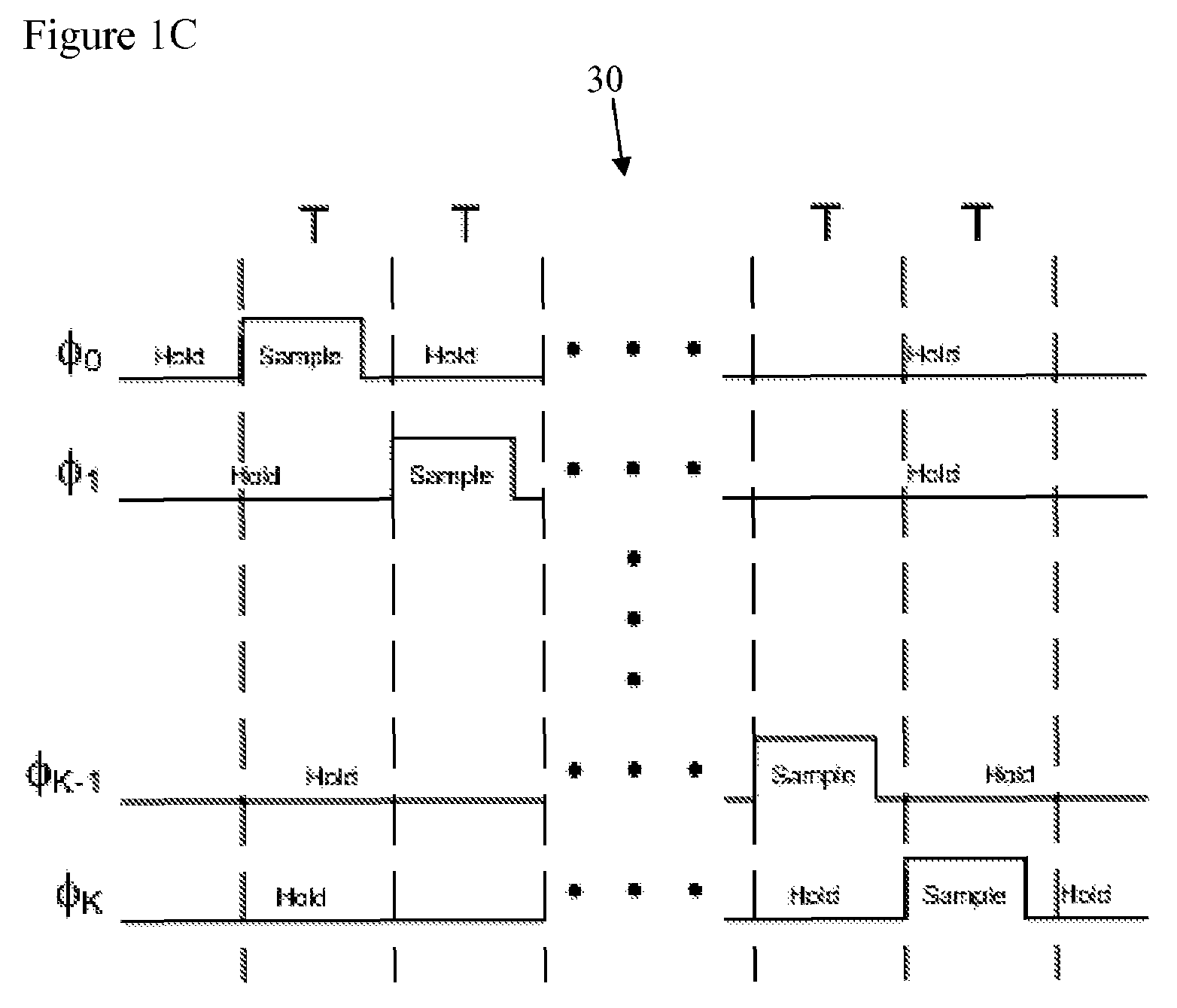

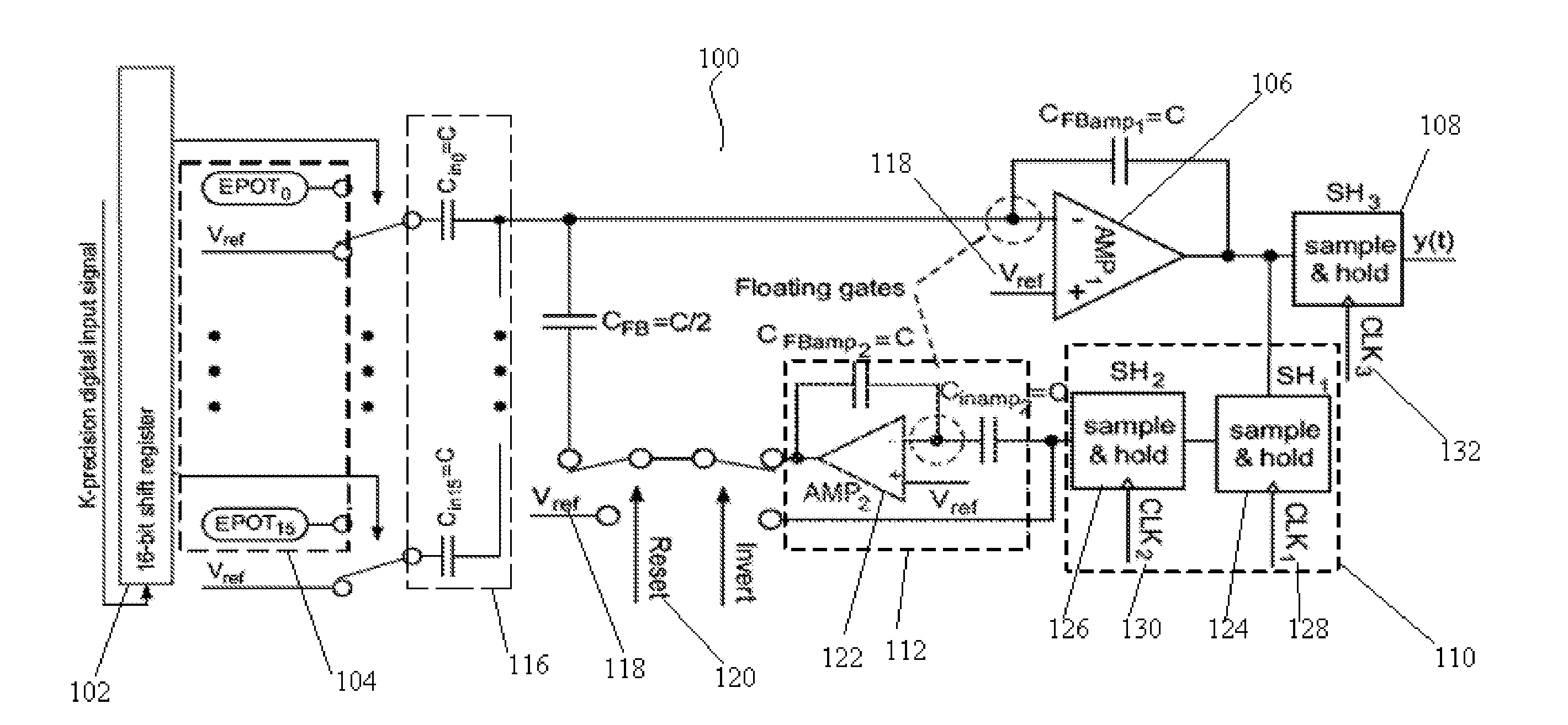

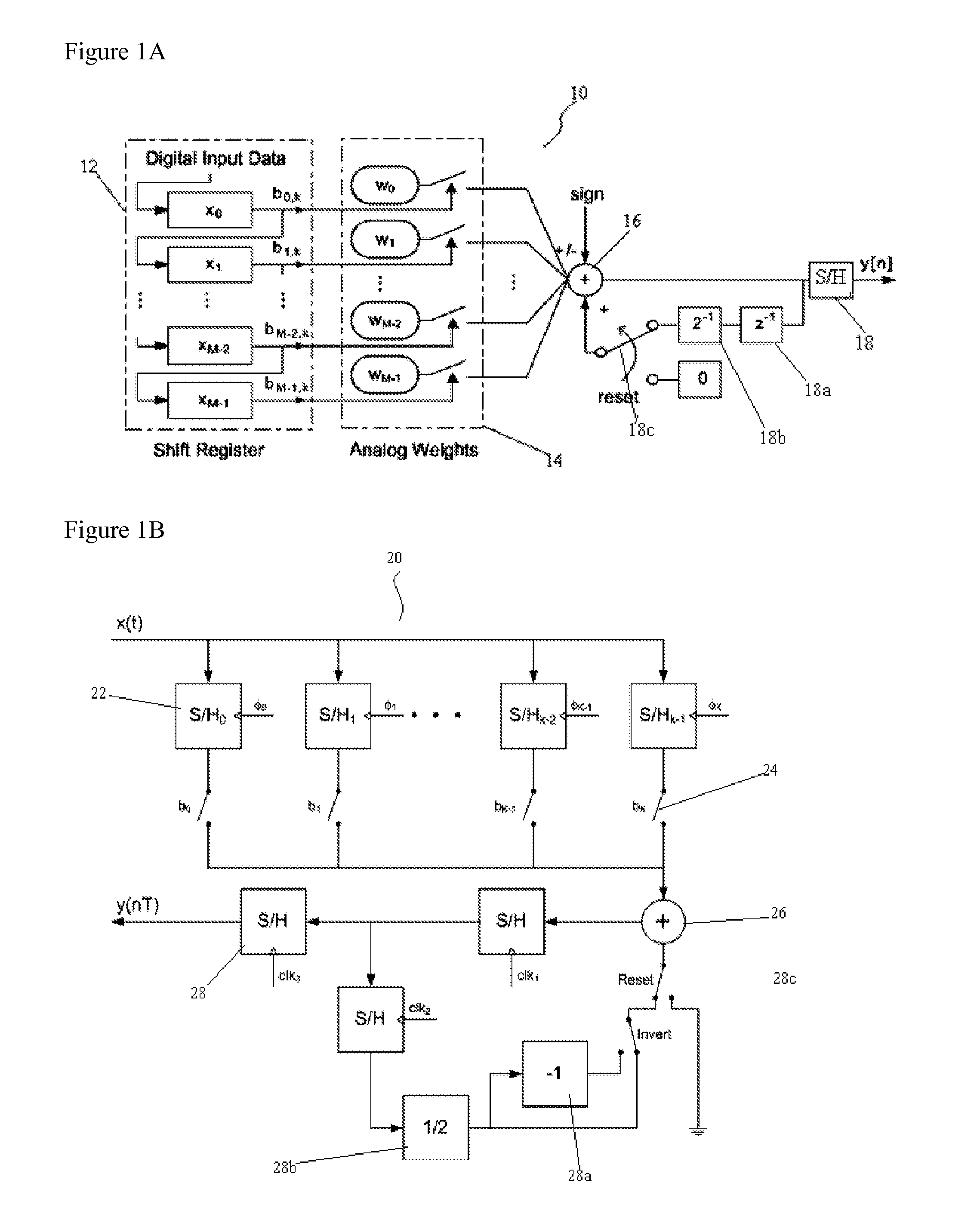

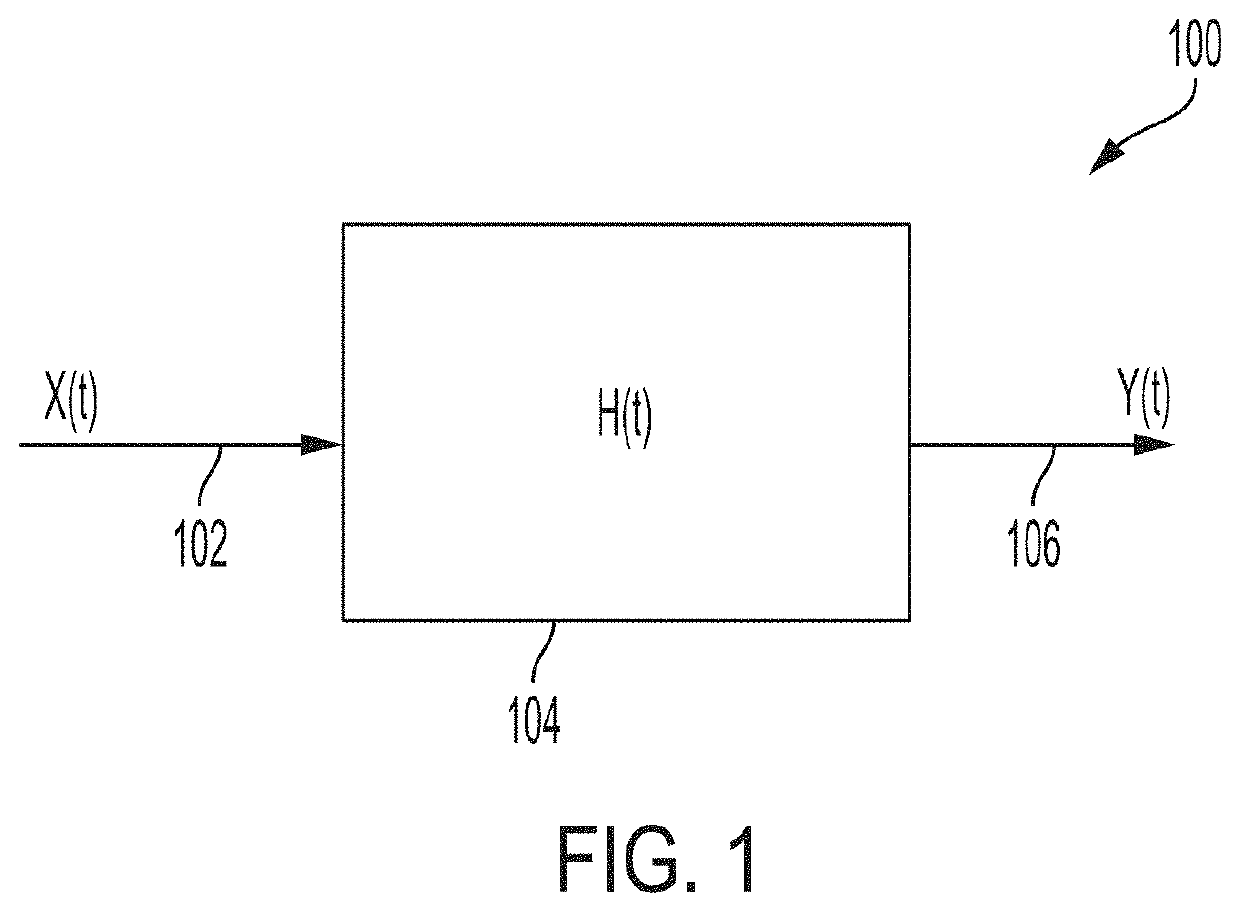

Reconfigurable mixed-signal VLSI implementation of distributed arithmetic

ActiveUS7348909B2Electric signal transmission systemsDigital-analogue convertorsVoltage referenceGate voltage

Disclosed herein is a reconfigurable mixed signal distributed arithmetic system including: an array of tunable voltage references operable for receiving a delayed digital input signal; a combination device in electrical communication with the array of tunable floating-gate voltage references that selectively combines an output of the array of tunable voltage references into an analog output signal; and a feedback element in electrical communication with the combination device, wherein the array of tunable voltages and the delayed digital input signal combine to perform a distributed arithmetic function and the reconfigurable mixed signal distributed arithmetic system responsively generates the analog output signal.

Owner:GEORGIA TECH RES CORP

Reconfigurable mixed-signal VLSI implementation of distributed arithmetic

ActiveUS20070040712A1Electric signal transmission systemsDigital-analogue convertorsVoltage referenceMixed signal vlsi

Disclosed herein is a reconfigurable mixed signal distributed arithmetic system including: an array of tunable voltage references operable for receiving a delayed digital input signal; a combination device in electrical communication with the array of tunable floating-gate voltage references that selectively combines an output of the array of tunable voltage references into an analog output signal; and a feedback element in electrical communication with the combination device, wherein the array of tunable voltages and the delayed digital input signal combine to perform a distributed arithmetic function and the reconfigurable mixed signal distributed arithmetic system responsively generates the analog output signal.

Owner:GEORGIA TECH RES CORP

A local cache file sharing method based on mobile swarm intelligence network

ActiveCN106708923BImprove satisfactionReduce transmission delayDigital data information retrievalTransmissionEngineeringMobile device

Owner:WUHAN UNIV

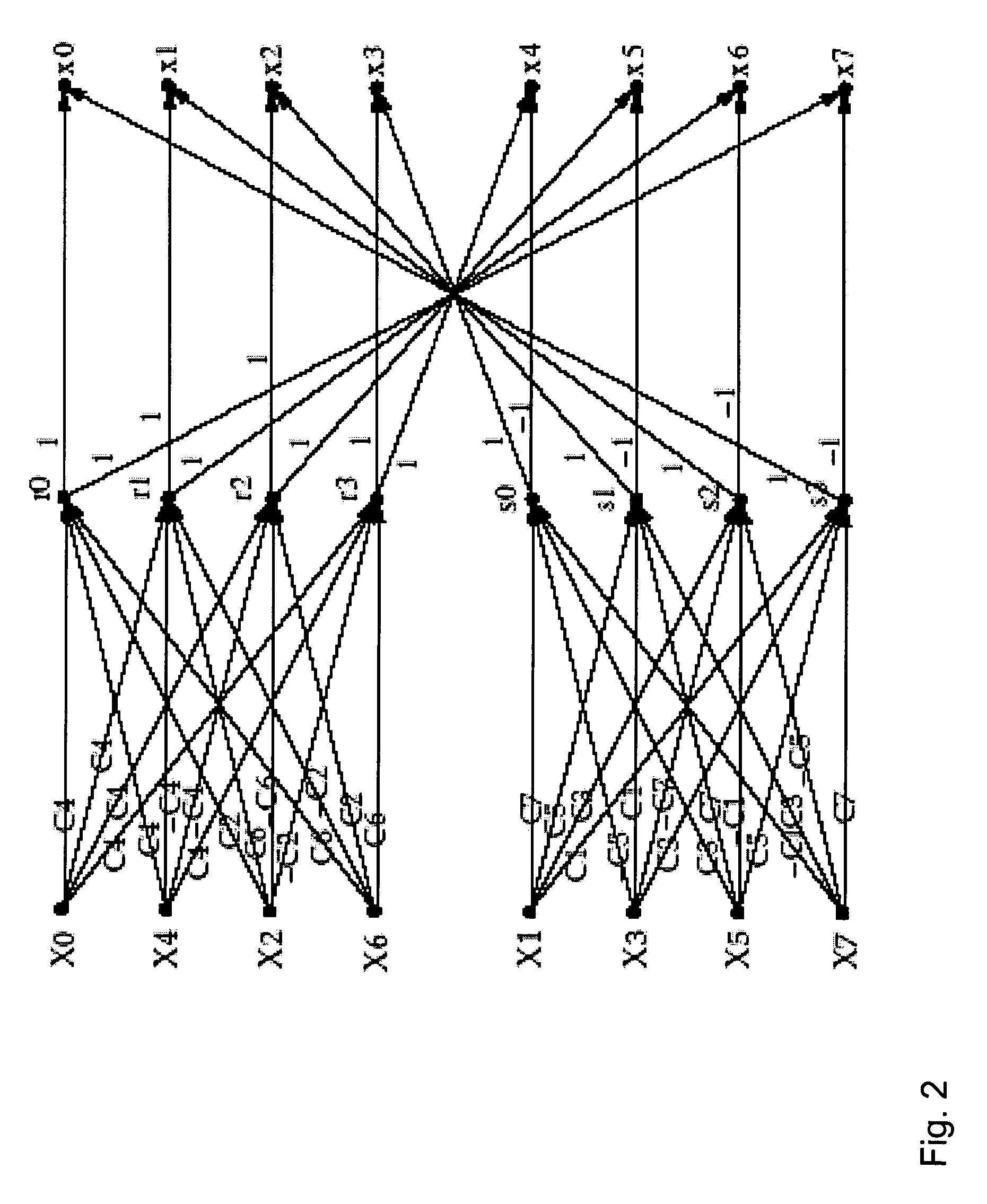

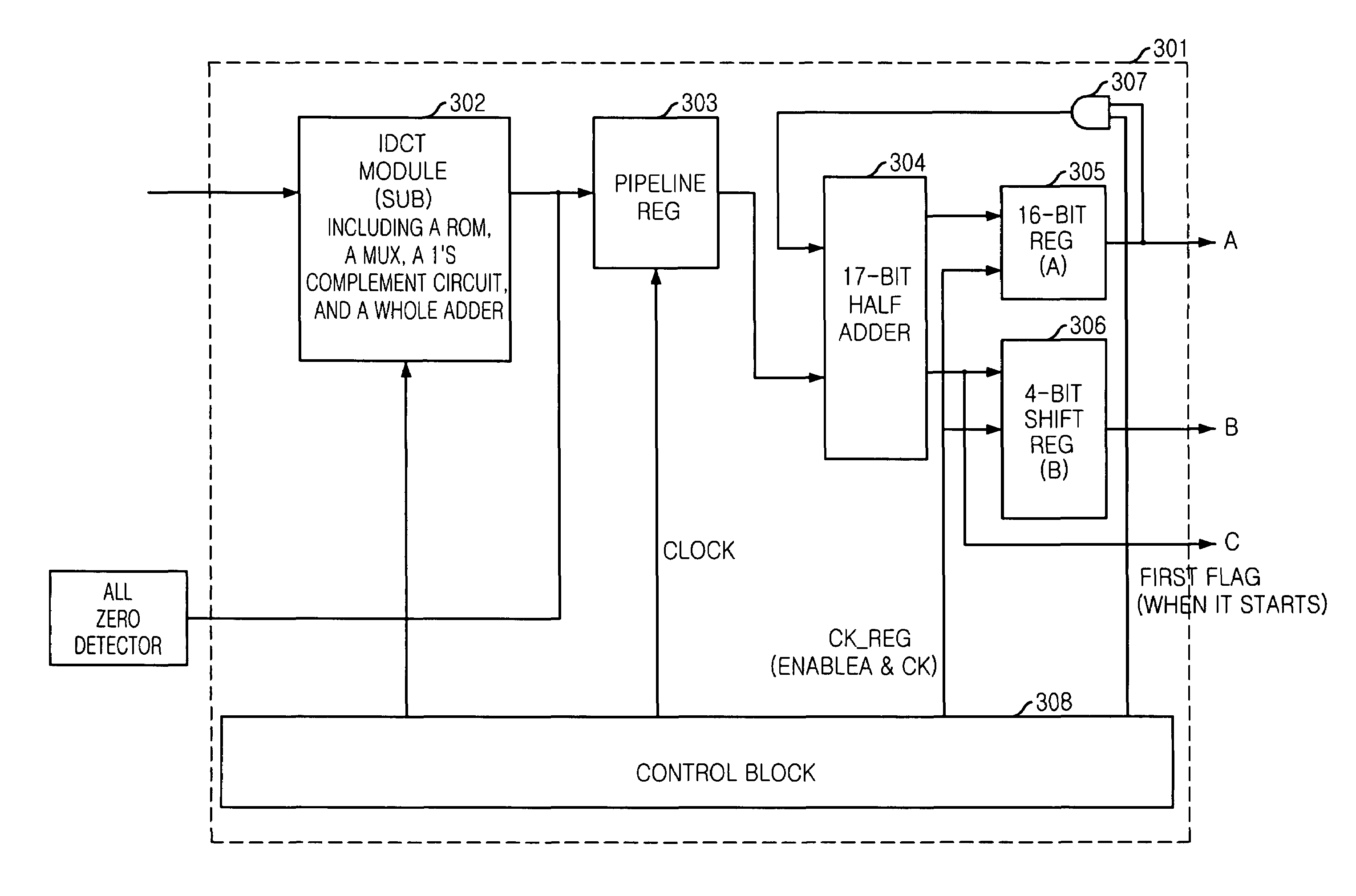

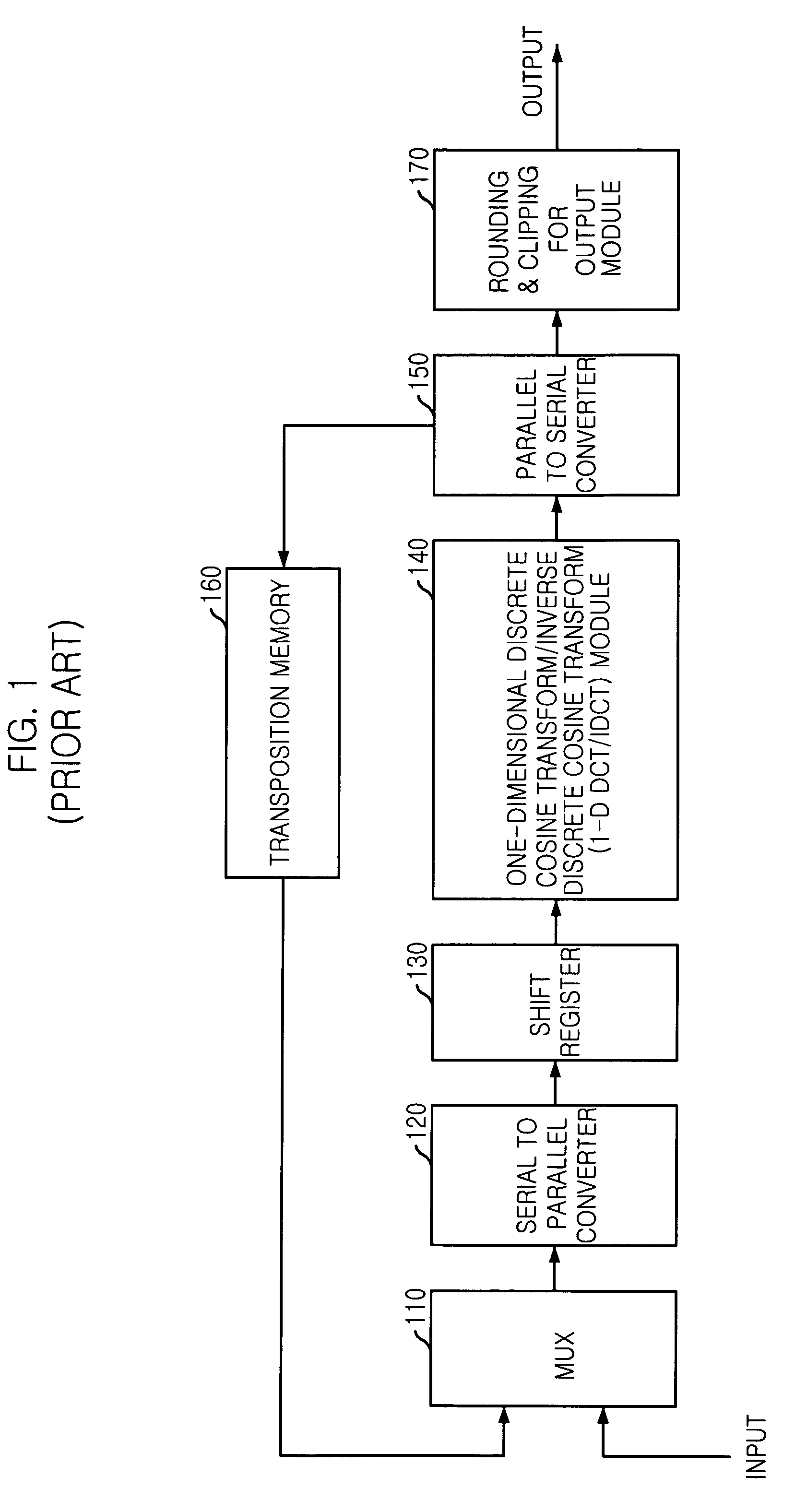

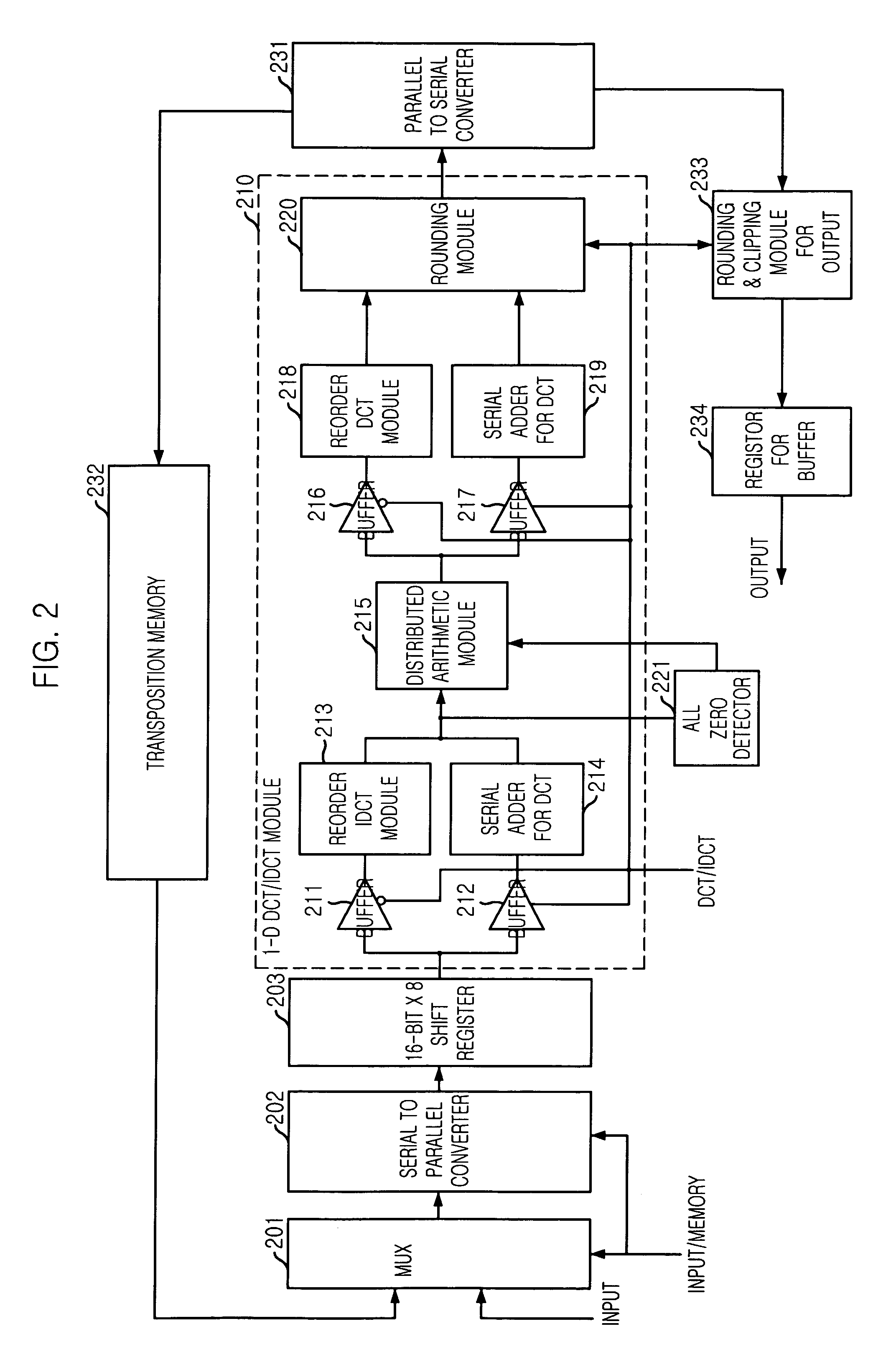

Apparatus and method for 2-D discrete transform using distributed arithmetic module

ActiveUS7065543B2Reduce power consumptionTelevision systemsDigital video signal modificationComputer moduleDiscrete cosine transform

The present invention relates to a distributed arithmetic module employing a zero input detection circuit that reduces electric power consumption by avoiding unnecessary calculation. An apparatus for performing a discrete cosine transform (DCT) on a video signal, including; input unit for receiving the video signal in a block by block basis; discrete cosine transform (DCT) unit for receiving each image data block from the input unit and conducting a discrete cosine transform / inverse discrete cosine transform (DCT / IDCT) operation on the received image data block to generate a transformed image data block containing N×M pixel value; zero input detect unit for determining whether pixel values of a current image data block are all “0” and generating a detection signal in order to bypass the DCT / IDCT performing on the current image block; and output unit for outputting the transformed image data block as a transformed video signal.

Owner:MTEKVISION CO LTD +1

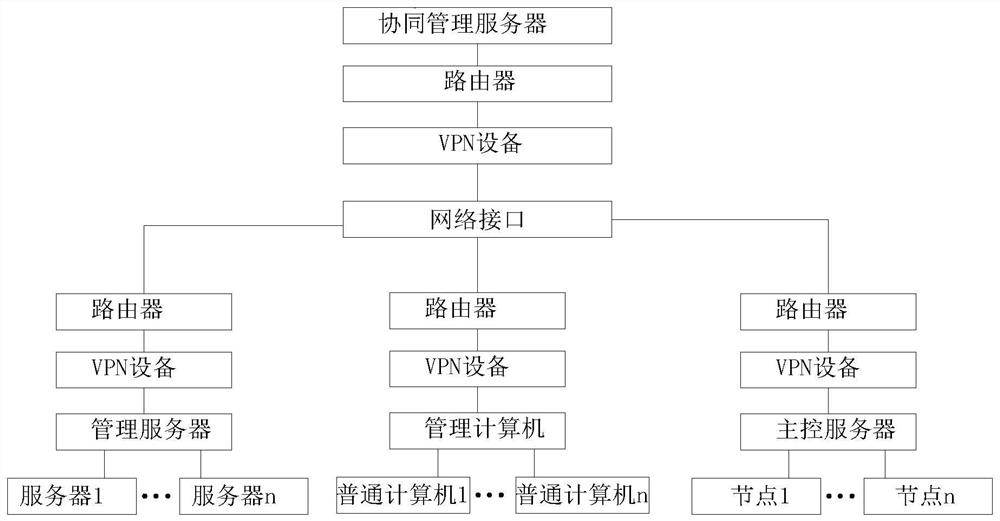

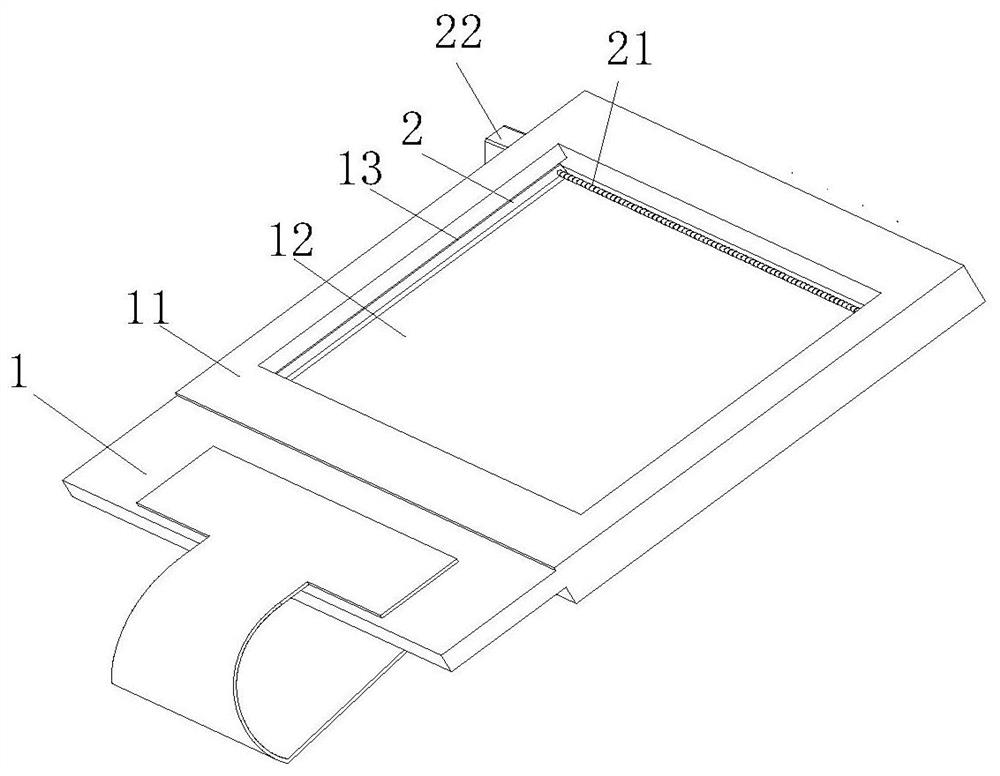

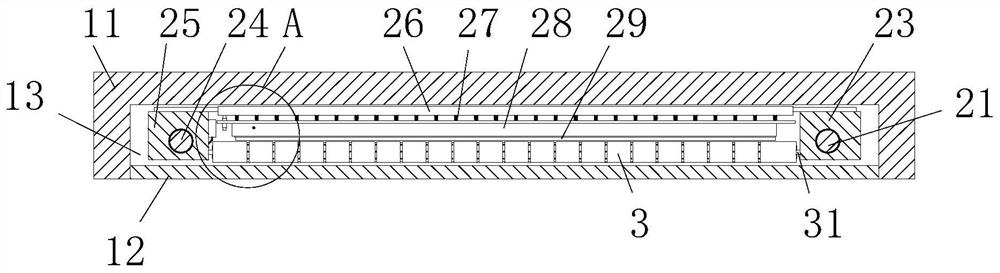

A Distributed Computer Management System

The present invention relates to the field of computer technology, specifically a distributed computer management system, including a collaborative management server, a router, multiple VPN devices, multiple server computing resource clusters, multiple distributed computing resource clusters, and multiple supercomputers Central computing resource cluster; the collaborative management server, router, multiple VPN devices, multiple server computing resource clusters, multiple distributed computing resource clusters, and multiple supercomputer central computing resource clusters are all connected through network interfaces; The setting of screw rod, micro motor, polishing rod and cleaning roller can successfully complete the cleaning of the screen, avoiding the situation that the screen is not able to guarantee the smooth use of the screen due to dust adhered to the screen, and at the same time, it also enables smooth retrieval and improves the efficiency of retrieval.

Owner:北京国联视讯信息技术股份有限公司

A Hidden Markov Correlation Source Coding Method Based on Distributed Arithmetic Coding

The invention discloses a hidden Markov related source coding method based on distributed arithmetic coding. The hidden Markov related source coding method includes the following steps of generating sources, coding the Markov related sources, and decoding the Markov related sources by utilizing a forward algorithm. According to the hidden Markov related source coding method, the sources related to memory are compressed through a DAC. In the concrete realization process, the dependency among the sources is modeled to be one hidden Markov process. Experimental results show that execution results of the new scheme are close to the Slepian-Wolf theory bound, and the problems that ambiguous code words can exist on decoding ends and an SWC is asymmetrical after areas are overlapped in the existing SWC technology based on entropy coding are well solved. According to the hidden Markov related source coding method, the existing technology is well utilized, experimental results are good, and good application value is possessed.

Owner:NORTHWEST A & F UNIV

A Depth-First Based Distributed Arithmetic Code Decoding Method

The invention discloses a distributed arithmetic code decoding method based on depth-first, and the method comprises the following contents: a data structure and a global variable; depth-first decoding summary; single-path searching; decoder behaviors at a fork node; compression end node pause path list; online memory releasing; optimal pause path selection; and ending conditions. According to the invention, compared with the conventional breadth-first decoding, the depth-first decoding is better in short code execution.

Owner:CHANGAN UNIV

DA-RNS (distributed arithmetic-residue number system) algorithm based FIR (finite impulse response) filter realizing method

ActiveCN103001605BReduce areaReduce power consumptionDigital technique networkChinese remainder theoremLow resource

The invention relates to a DA-RNS (distributed arithmetic-residue number system) algorithm based FIR (finite impulse response) filter realizing method. The DA-RNS algorithm based FIR filter realizing method includes steps of firstly, subjecting filter input and filter coefficient to conversion from decimal weighting system to remainder non-weighting system by means of step-by-step table lookup; secondly, decomposing filter input into a single-byte mode; thirdly, subjecting the filter input and the filter coefficient to single-byte convolution operation; fourthly, scaling the filter input after remainder of the filter input is subjected to convolution operation under the remainder non-weighting system; and fifthly, restoring the remainder to decimal system by means of China remainder theorem. Compared with the prior art, the DA-RNS algorithm based FIR filter realizing method has the advantages of low resource consumption, high throughput and the like.

Owner:TONGJI UNIV

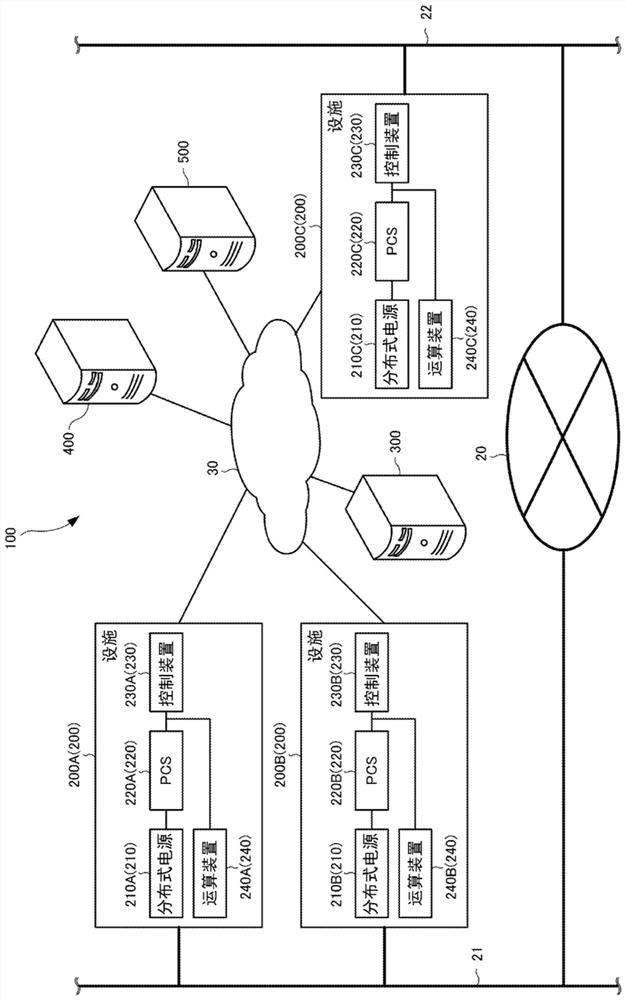

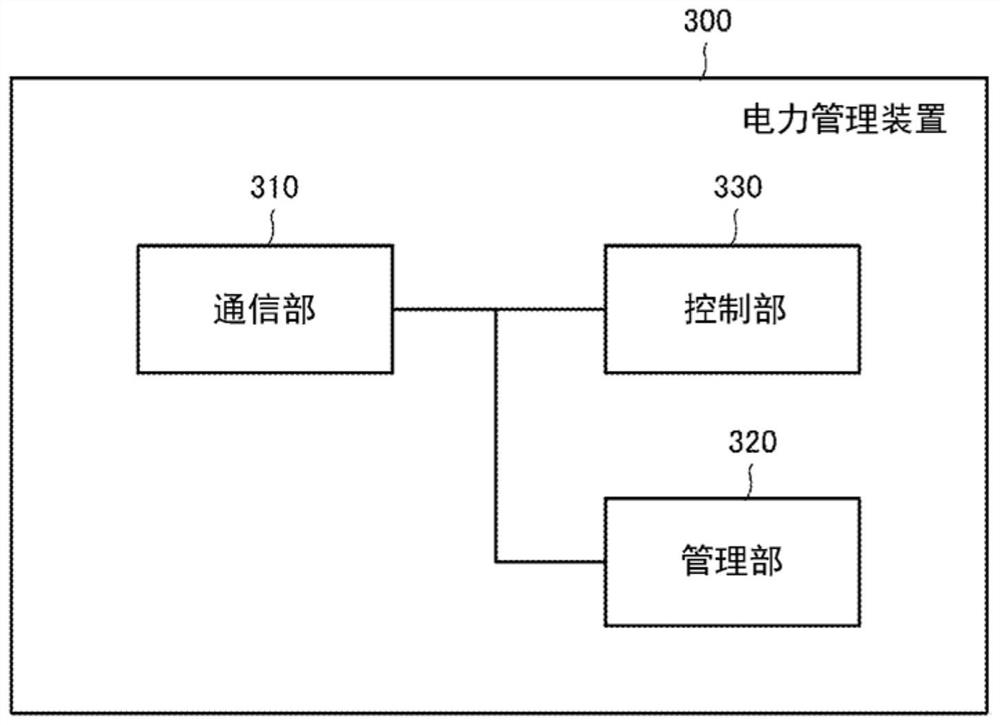

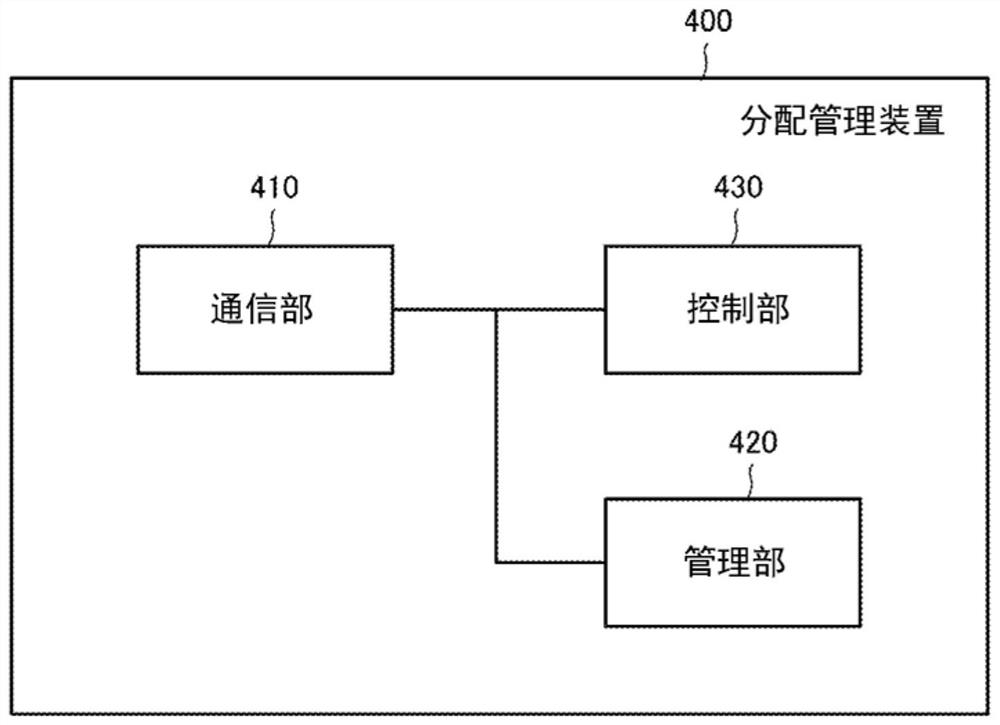

Power management system and power management method

PendingCN114846711AGeneration forecast in ac networkDc network circuit arrangementsControl engineeringElectric power

A power management system is provided with a management device that allocates divided arithmetic processes constituting at least a portion of a predetermined arithmetic process to distributed arithmetic devices located in a facility, the management device being provided with a control unit. And a control unit that executes an allocation process for allocating the division calculation process to the distributed calculation device on the basis of at least one of a predicted value for the output power of a distributed power source located in the facility, a predicted value for the power consumption of the facility, and a predicted value for the remaining power of the facility.

Owner:KYOCERA CORP

Distributed arithmetic logic unit security check

InactiveCN101221444BSafety arrangmentsRegistering/indicating working of vehiclesSecurity checkDiagnostic system

A vehicle diagnostic system is provided. The system includes: a first control module that includes a first processor and that controls a first vehicle subsystem; and second control module that controls a second vehicle subsystem and that validates the functionality of the first processor of the first control module wherein if the second control module determines that the first processor of the first control module is faulty, the second control module shuts down the first control module.

Owner:GM GLOBAL TECH OPERATIONS LLC

Determination method of QOS (quality of service) route longevity path of wireless sensor network in water environment

The invention discloses a determination method of a QOS (quality of service) route longevity path of a wireless sensor network in water environment. The determination method comprises the following steps of: firstly, carrying out a network split on an information acquisition region, enabling a Sink node to broadcast all the information after split, and enabling each node to know the taken framework and position; then, carrying out distributed arithmetic on each framework, seeking one or more than one shortest framework path from each framework to the Sink node, and enabling only can two adjacent frameworks transmit data, so as to ensure that the network transmission energy consumption is least when the network is in normal operation; and finally, seeking a suitable path based on an entropy idea, utilizing the entropy to carry out auto patching on the path after operation for a certain time, namely, achieving the self-healing of the structure of the whole network route after the node is vitiate. Compared with algorithms such as Long-term, DBR, DTN(delay / disruption tolerant network), the QOS route algorithm has better properties on the aspects of route reconstruction times, route success rate, network energy consumption and network delay.

Owner:CHONGQING COLLEGE OF ELECTRONICS ENG

Systems and method for a low power correlator architecture using distributed arithmetic

ActiveUS10879877B1Reduce the amount requiredReduce in quantityDigital technique networkDigital data processing detailsComputer hardwareEngineering

Owner:MITRE SPORTS INT LTD

Systems and method for a low power correlator architecture using distributed arithmetic

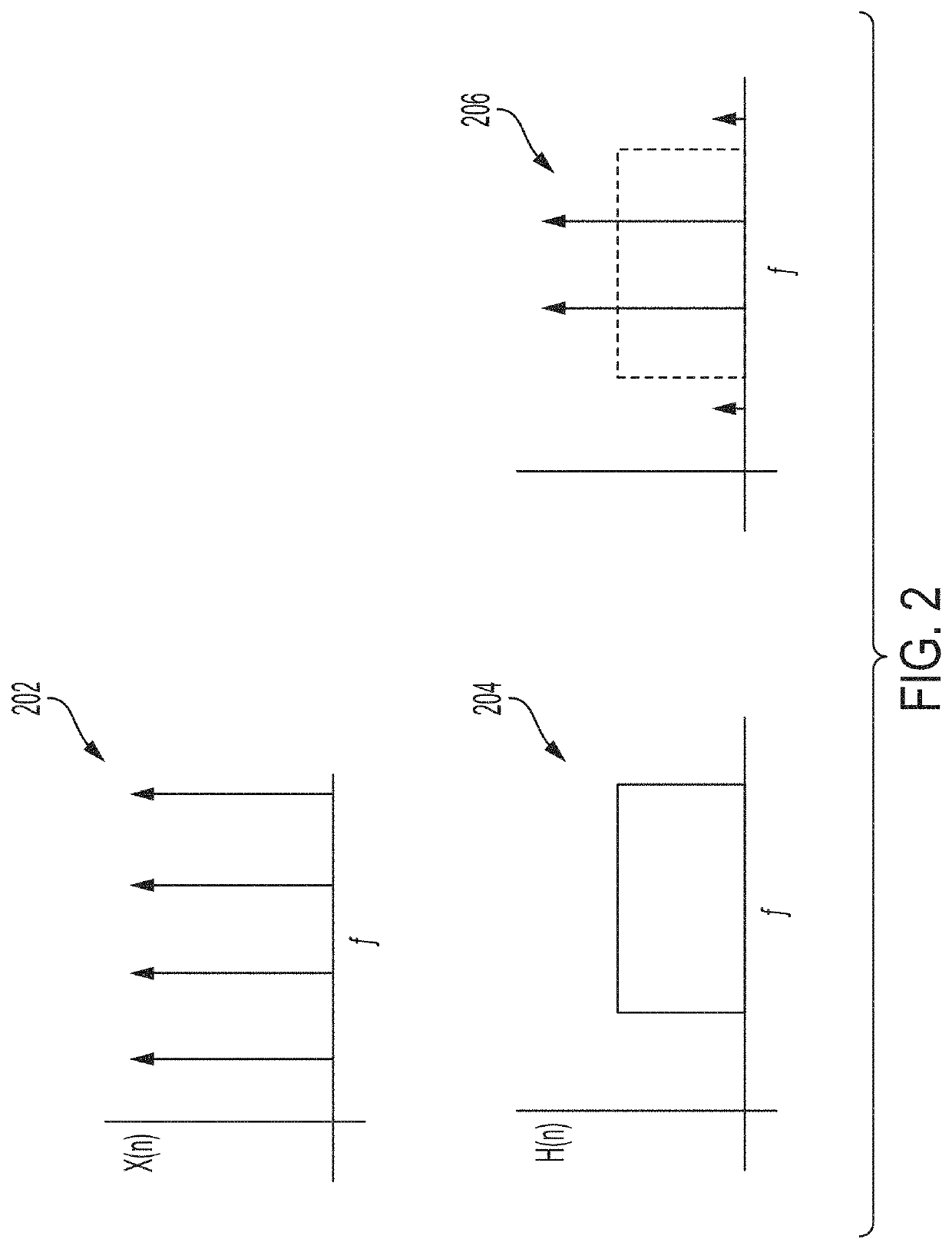

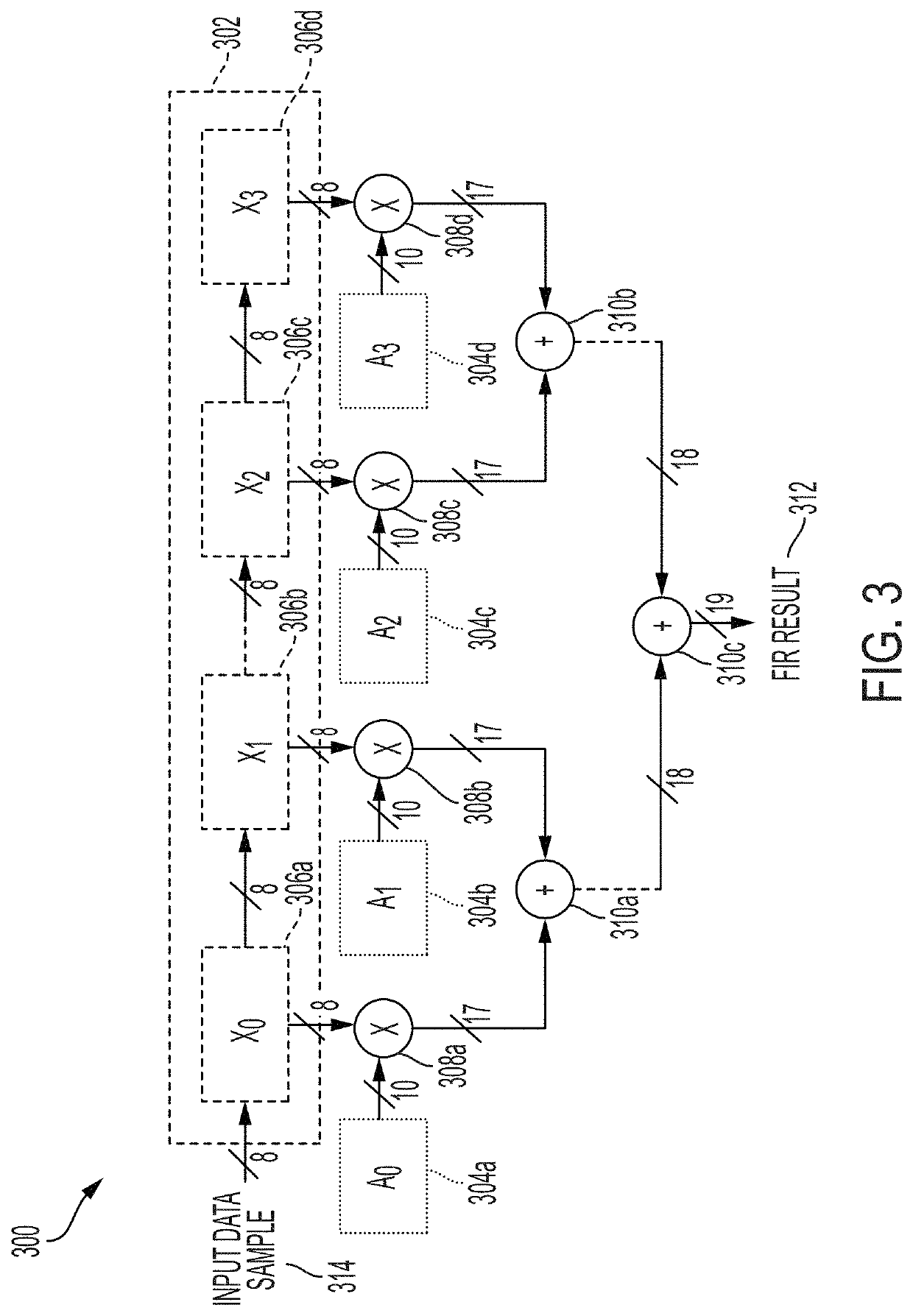

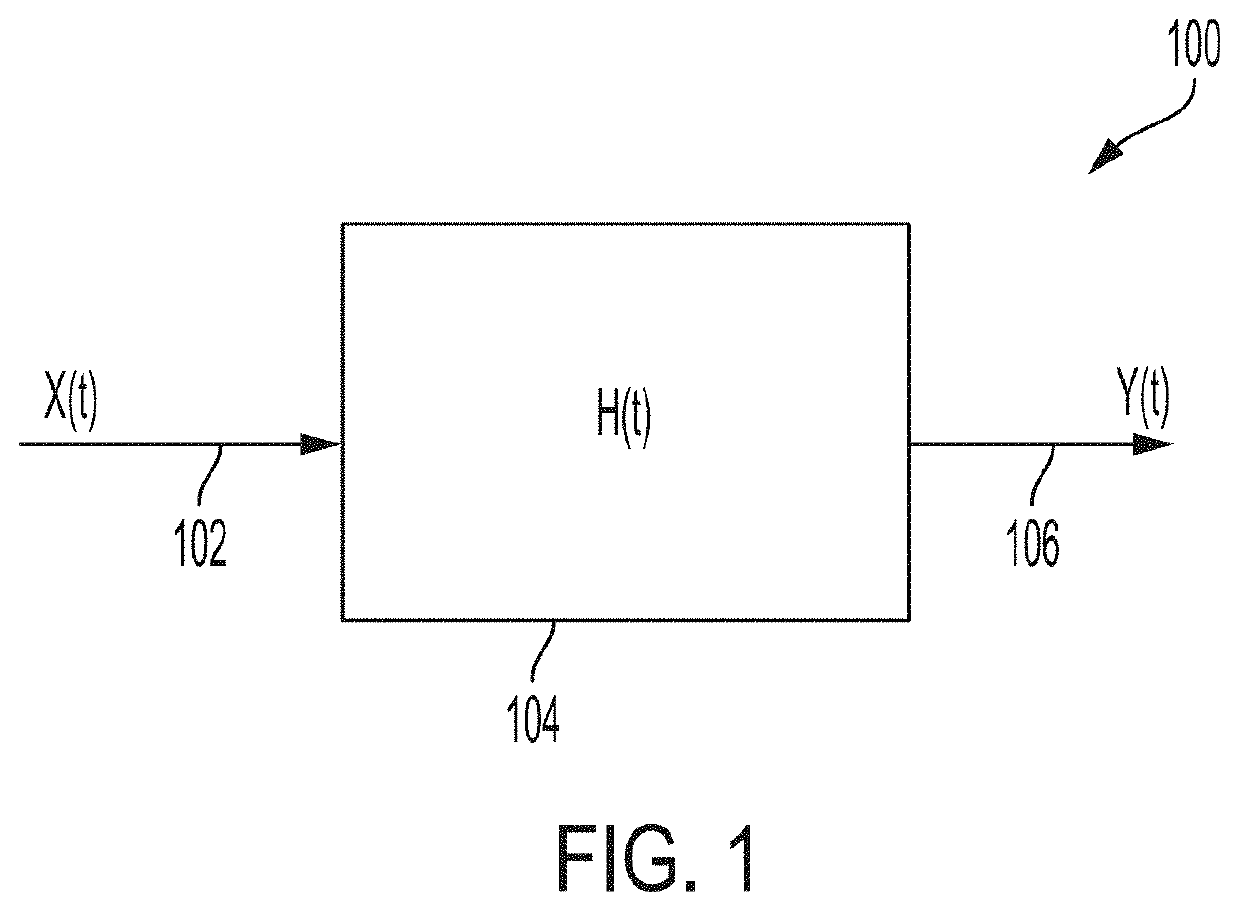

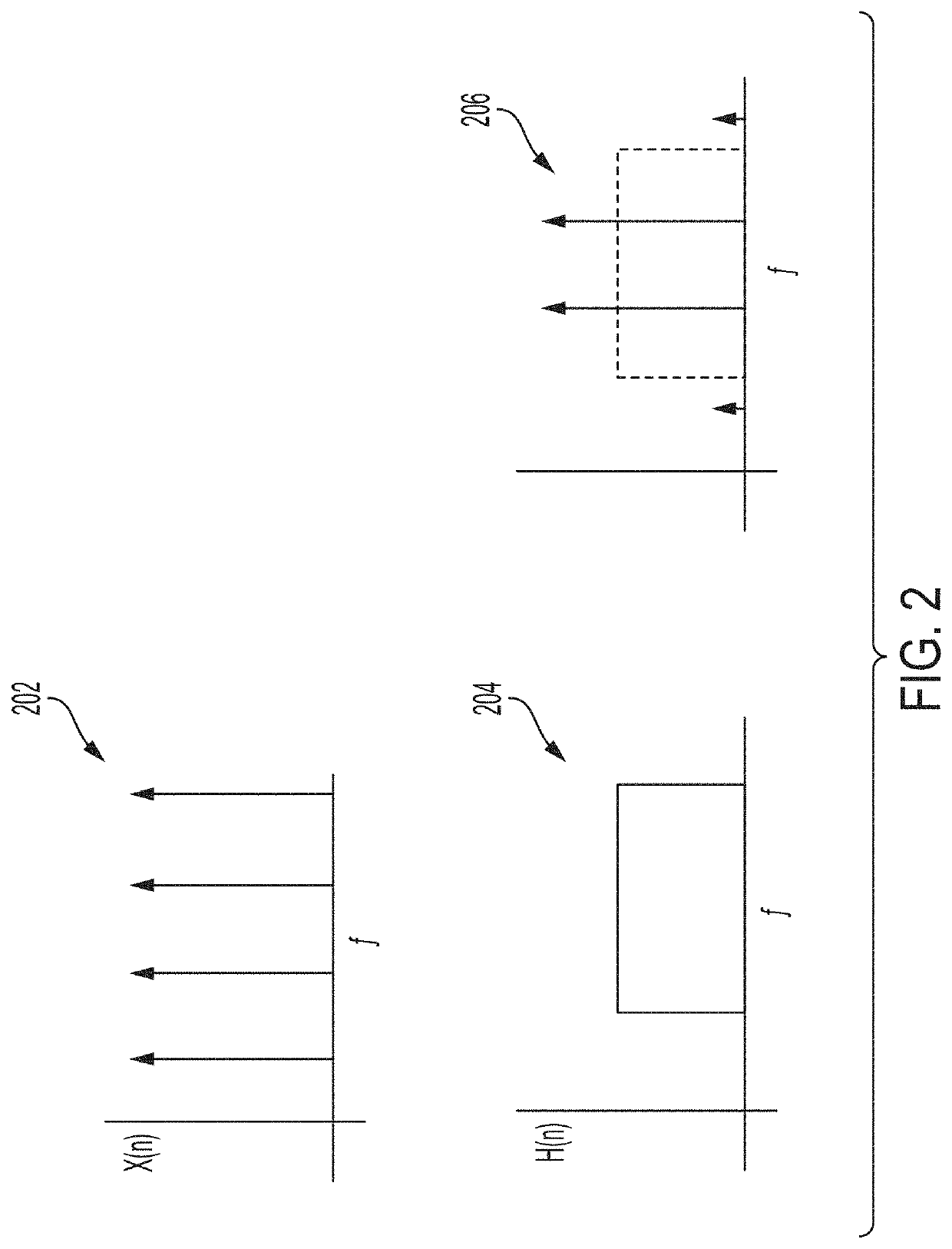

ActiveUS20200394021A1Reduce the amount requiredReduce in quantityDigital technique networkComputations using residue arithmeticComputer hardwareImpulse response

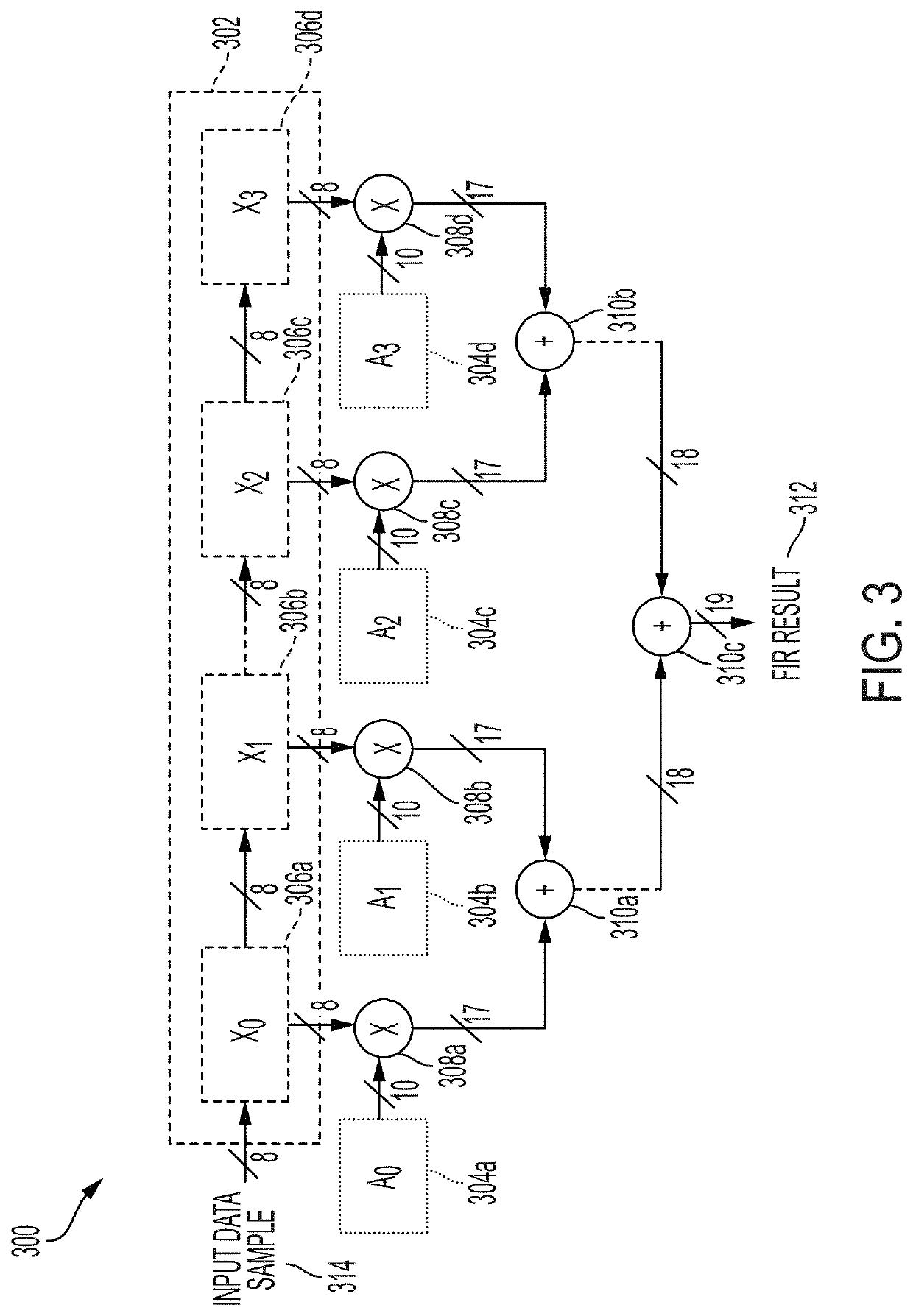

Provided herein is an implementation of a finite impulse response (FIR) filter that uses a distributed arithmetic architecture. In one or more example, a data sample with multiple bits is processed through a plurality of bit-level multiply and accumulate circuits, wherein each bit of the data sample corresponds to a bit of the data sample. The output of each bit-level multiply and accumulate circuit can then be shifted by an appropriate amount based on the bit placement of the bit of the data sample that corresponds to the bit-level multiply and accumulate circuit. After each output is shifted by the appropriate amount, the outputs can be aggregated to form a final FIR filter result.

Owner:MITRE SPORTS INT LTD

Feed forward equalizer with power-optimized distributed arithmetic architecture and method

ActiveUS20200186401A1Reduce complexityReduce power consumptionDigital data processing detailsCode conversionParallel computingEngineering

A distributed arithmetic feed forward equalizer (DAFFE) and method. The DAFFE includes look-up tables (LUTs) in offset binary format. A DA LUT stores sum of partial products values and an adjustment LUT stores adjustment values. DA LUT addresses are formed from same-position bits from all but the most significant bits (MSBs) of a set of digital words of taps and an adjustment LUT address is formed using the MSBs. Sum of partial products values and an adjustment value are acquired from the DA LUT and the adjustment LUT using the DA LUT addresses and the adjustment LUT address, respectively. Reduced complexity downstream adder(s) (which result in reduced power consumption) compute a total sum of the sum of partial products values and the adjustment value (which compensates for using the offset binary format and dropping of the MSBs when forming the DA LUT addresses) to correctly solve a DA equation.

Owner:CAVIUM INT +1

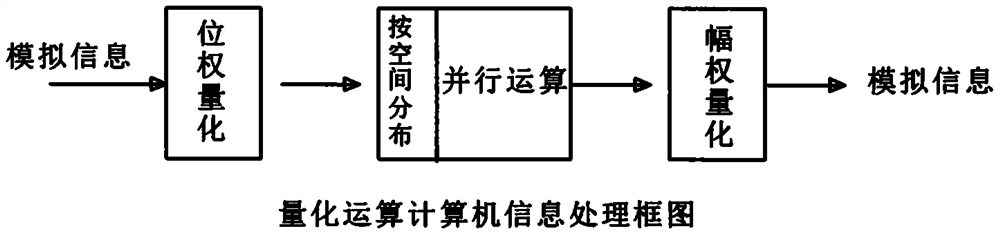

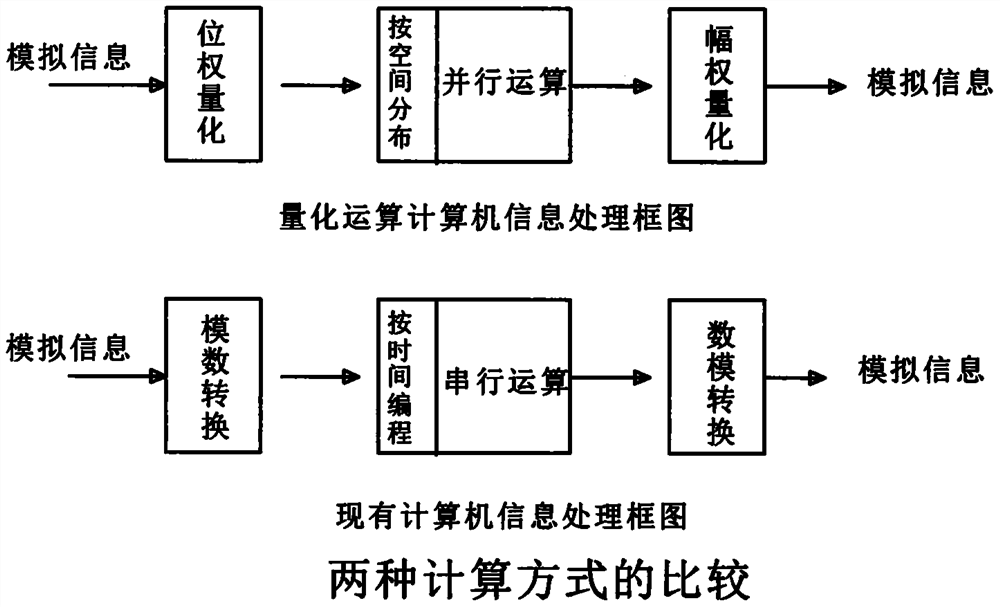

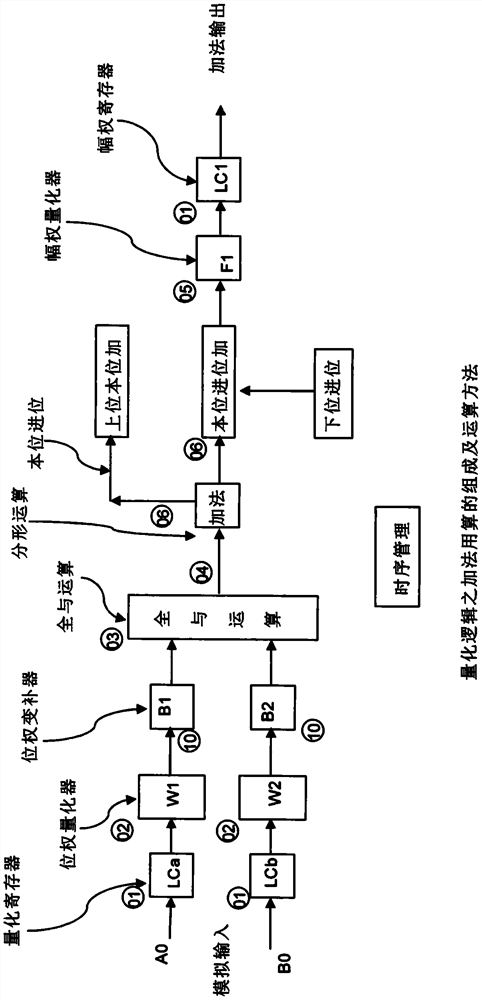

Composition and operation method for multi-system and decimal operation of quantization logic

PendingCN112860217AComputation using denominational number representationInformation processingControl engineering

An information processing operation method is composed of the following steps that obtained natural simulation information is quantized into various spatial information with different carry systems through a quantizer, the spatial information with the carry systems is input into a distributed arithmetic unit, and new spatial information obtained after operation of the distributed arithmetic unit is converted into spatial information with different carry systems. Amplitude weight quantization is performed by another amplitude weight quantizer, and the amplitude weight is converted into analog information and outputted.

Owner:胡五生

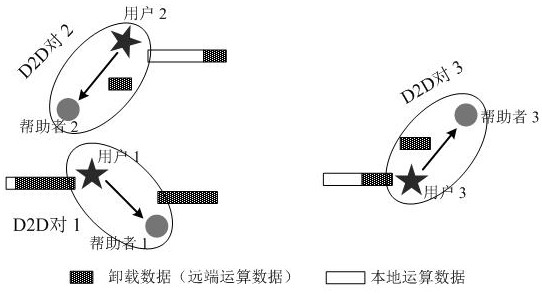

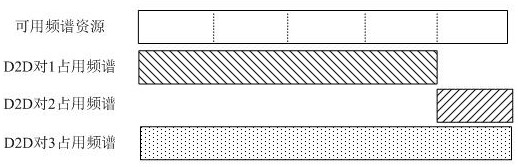

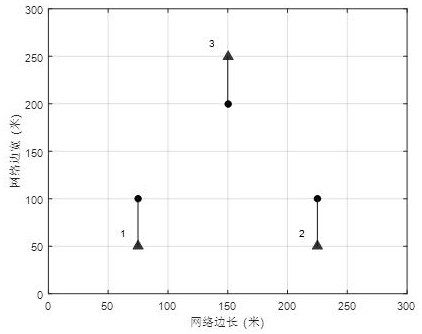

A Distributed Computing Offload Method Based on Variable Bandwidth Channel

ActiveCN113395684BIncrease profitFlexible frequency usageHigh level techniquesNetwork planningComplete dataEngineering

The invention discloses a distributed computing unloading method based on a variable bandwidth channel. In a distributed wireless network, a terminal with a large computing requirement can unload part of data to peripheral terminals for processing, thereby completing data processing within a given time limit tasks, the terminal has differentiated offloading requirements, and can use different amounts of spectrum resources as needed. In addition, the terminal can overlap and use some spectrum resources according to the network topology and other conditions. Through the optimal response learning algorithm, the distributed decision-making method realizes the full Network energy consumption is minimized. The present invention can better adapt differentiated unloading requirements to limited spectrum resources, and the utilization rate of spectrum resources is higher, and terminals can share spectrum resources, the frequency usage mode is more flexible, and communication performance can be improved.

Owner:南京智能信通科技发展有限公司