Semiconductor bonding and layer transfer method

a layer transfer and semiconductor technology, applied in the field of semiconductors, can solve the problems of large chip area consumption of laterally oriented devices, large amount of chip area of processor circuits, and large amount of idle processor circuits for many cycle times,

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

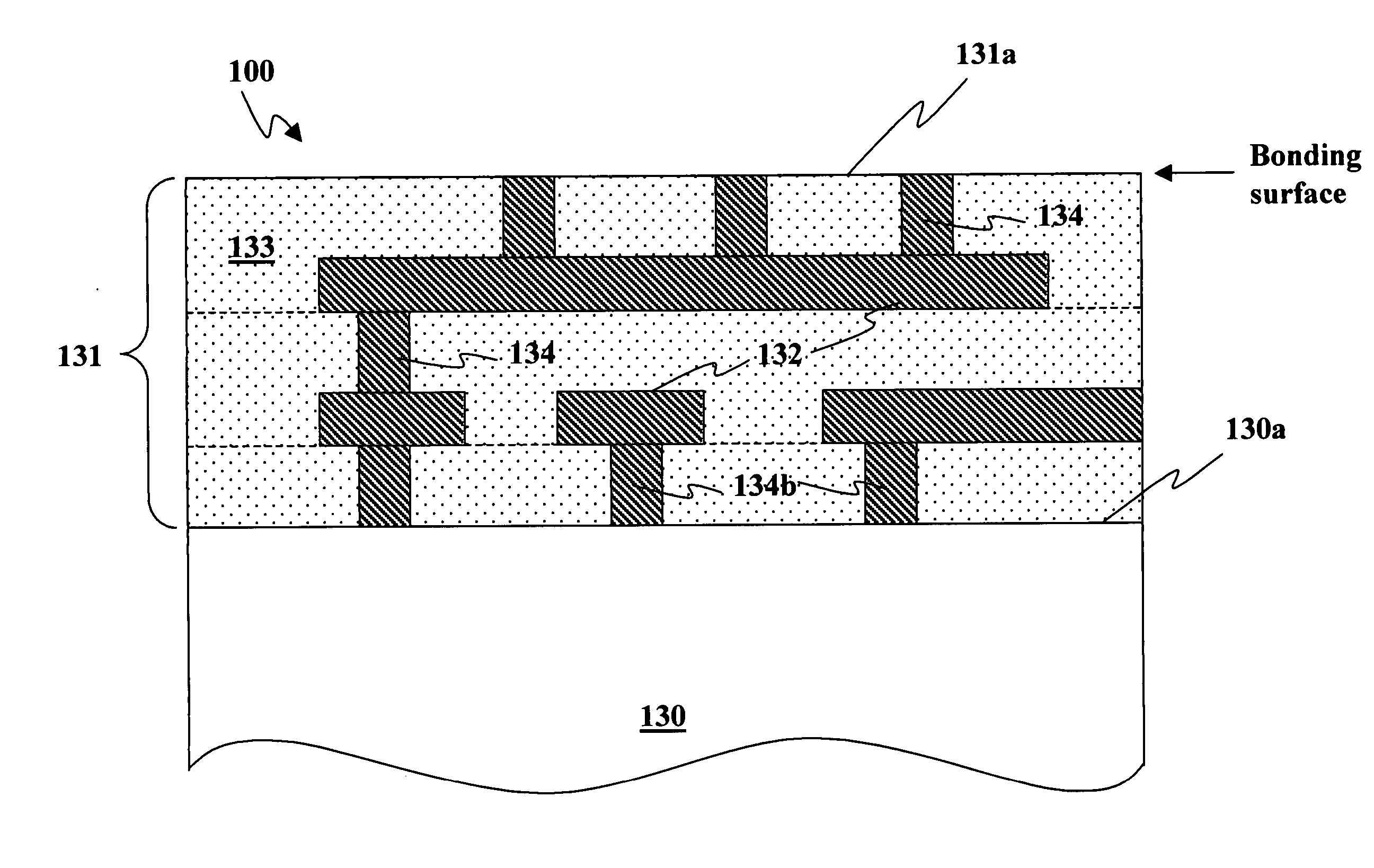

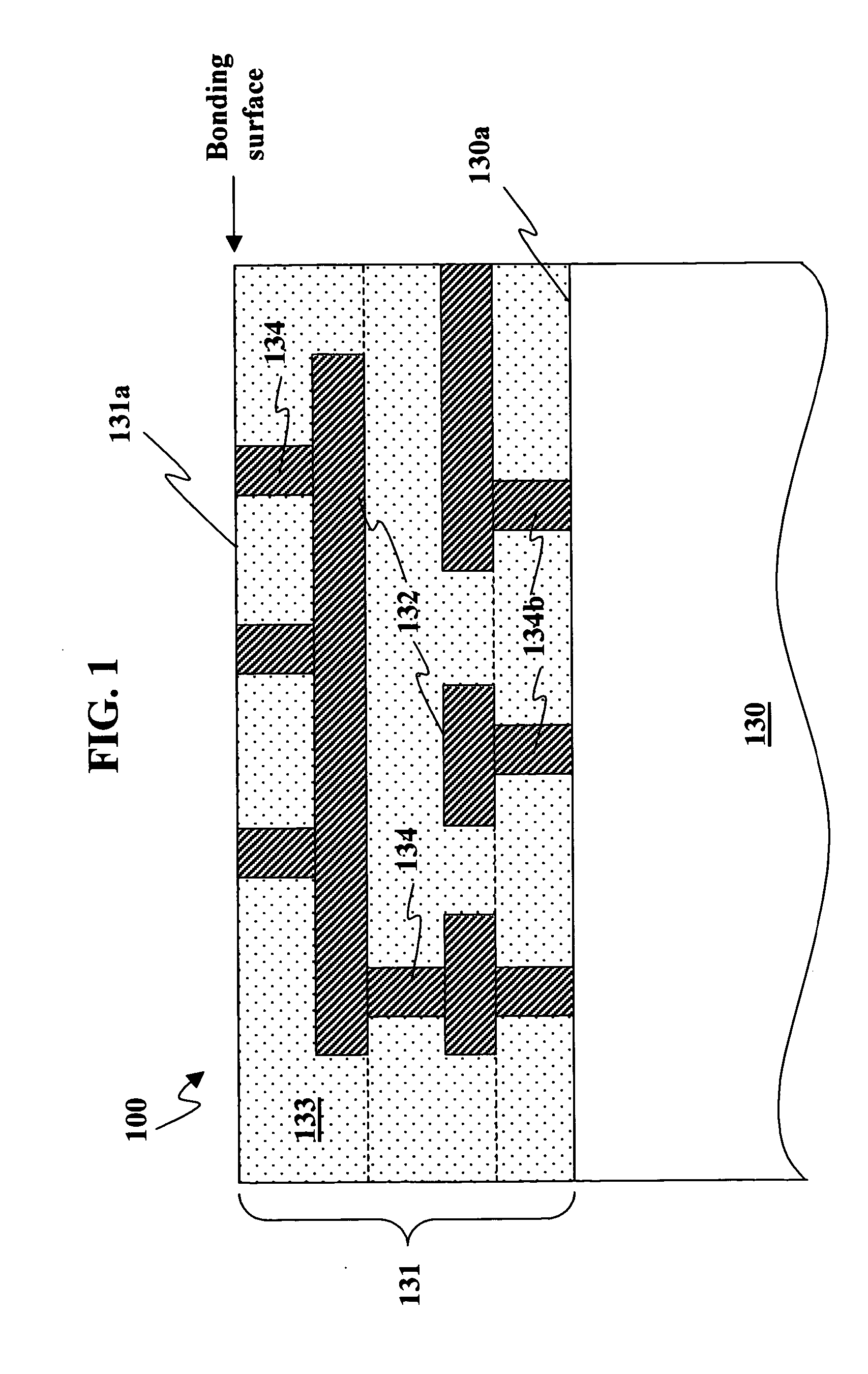

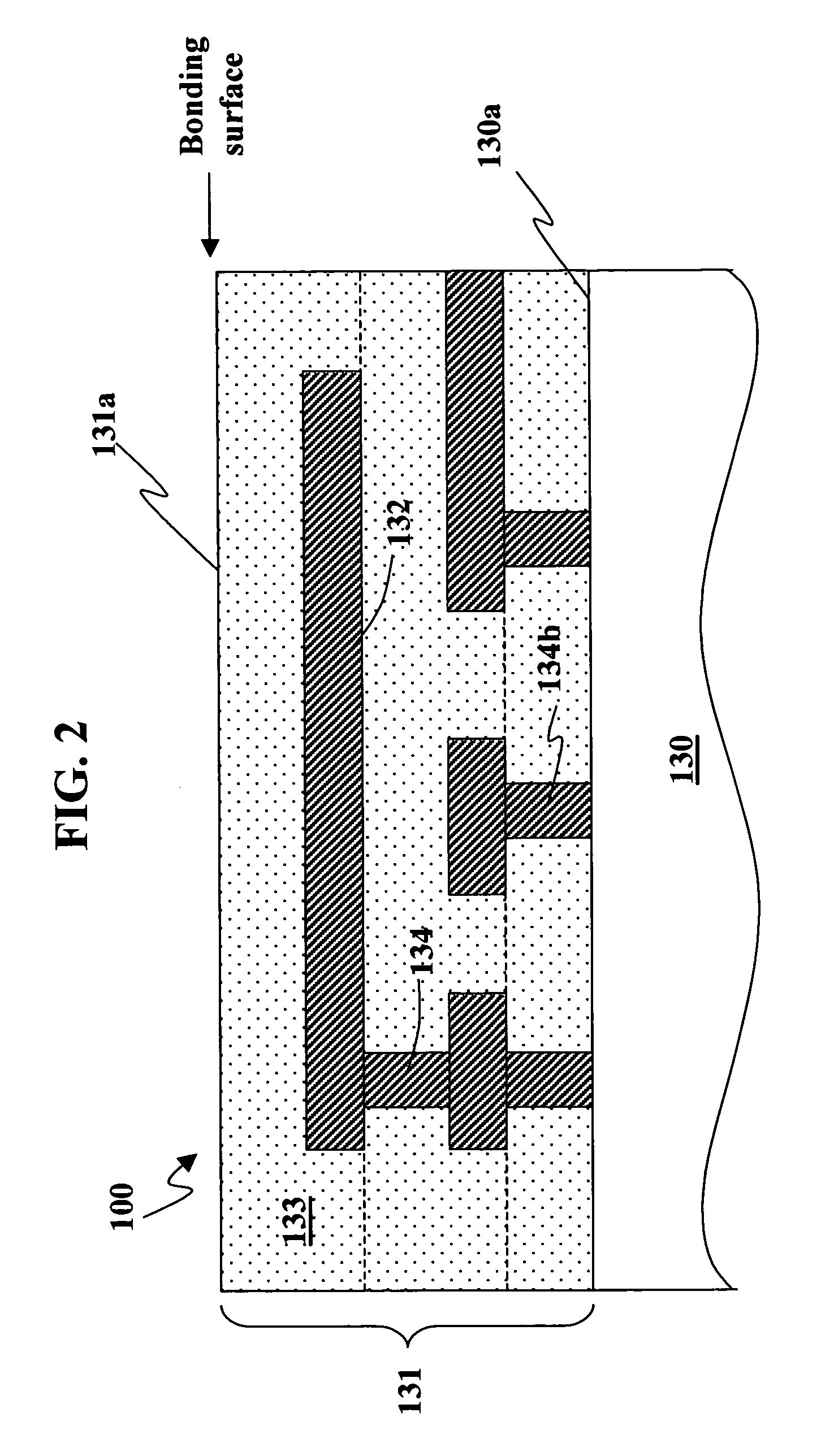

[0023]FIGS. 1-23 are simplified sectional views of steps in fabricating circuitry 100 using a semiconductor bonding transfer method in accordance with the present invention. It should be noted that in the following figures, like reference characters indicate corresponding elements throughout the several views. In this embodiment, circuitry 100 includes separate portions in which it is desired to bond them together. As will be discussed in more detail below, one portion is carried by an acceptor substrate and another portion is carried by a donor substrate. In accordance with the invention, the portion carried by the donor substrate is bonded to the portion carried by the acceptor substrate and then the donor substrate is removed. It should be noted that the portions carried by the donor and acceptor substrates can have many different configurations, but only a few are discussed herein.

[0024] The portions carried by the acceptor substrate are shown in FIGS. 1-5 and the portions carr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More