Plane gate IGBT and manufacturing method therefor

A planar gate and gate electrode technology, applied in the field of planar gate insulated gate bipolar transistors and insulated gate bipolar transistors, can solve the problems of increasing device switching loss, reducing device switching speed, device oscillation, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

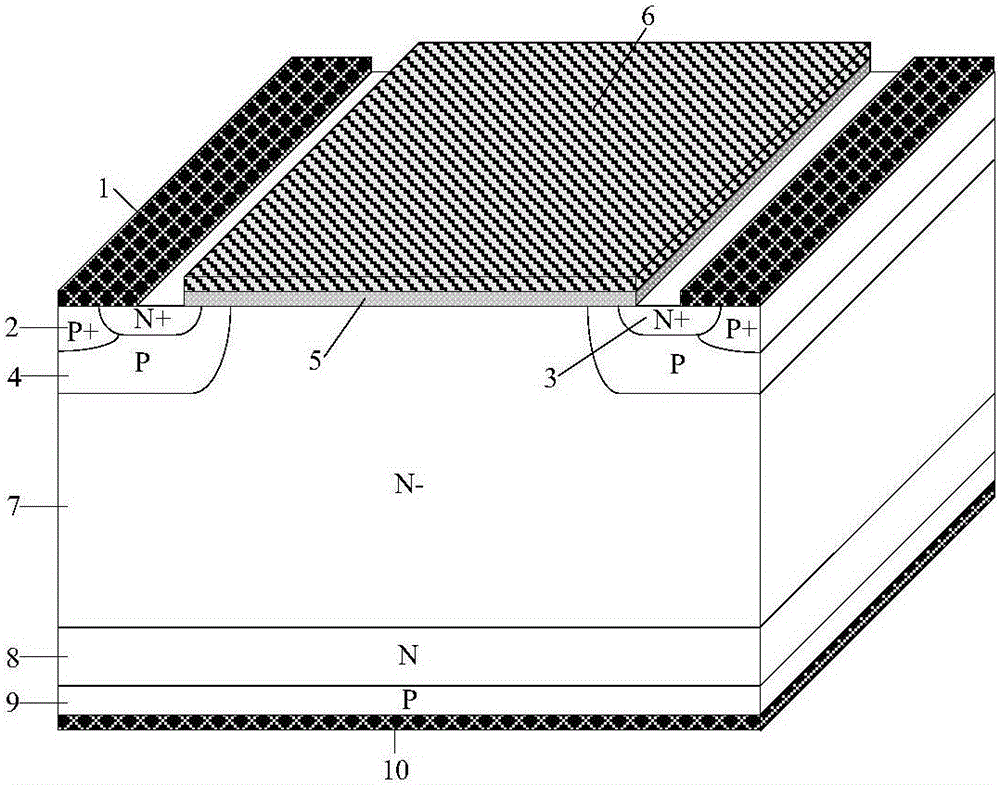

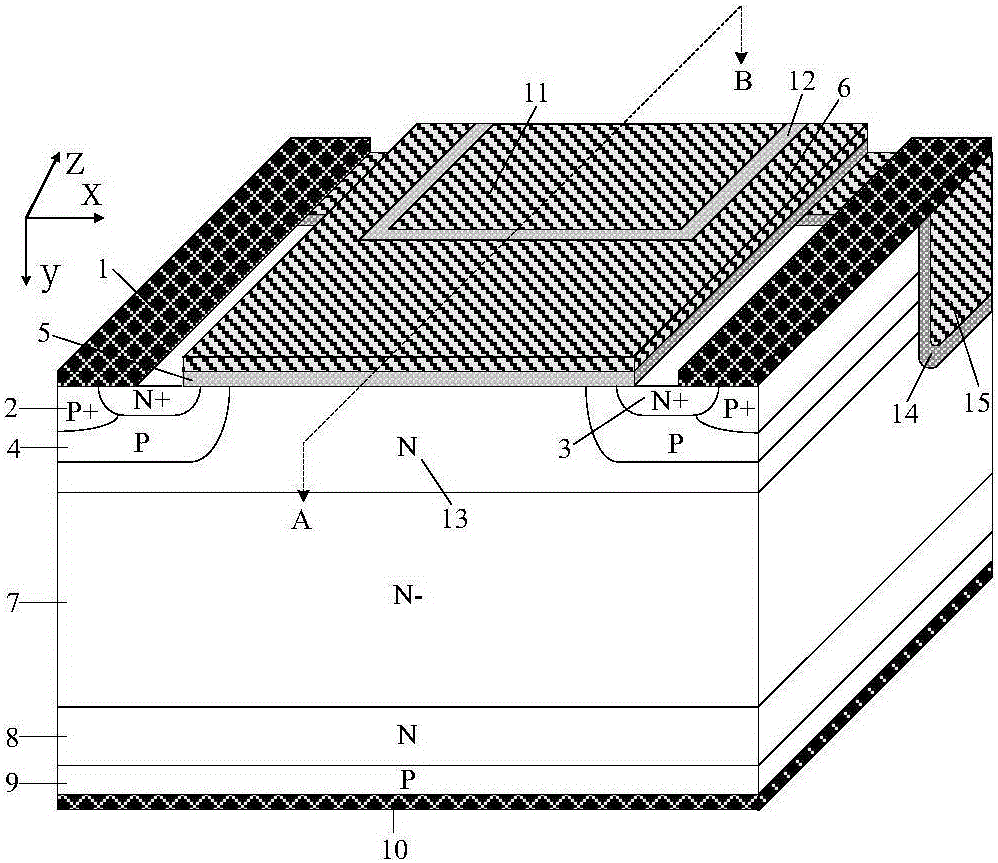

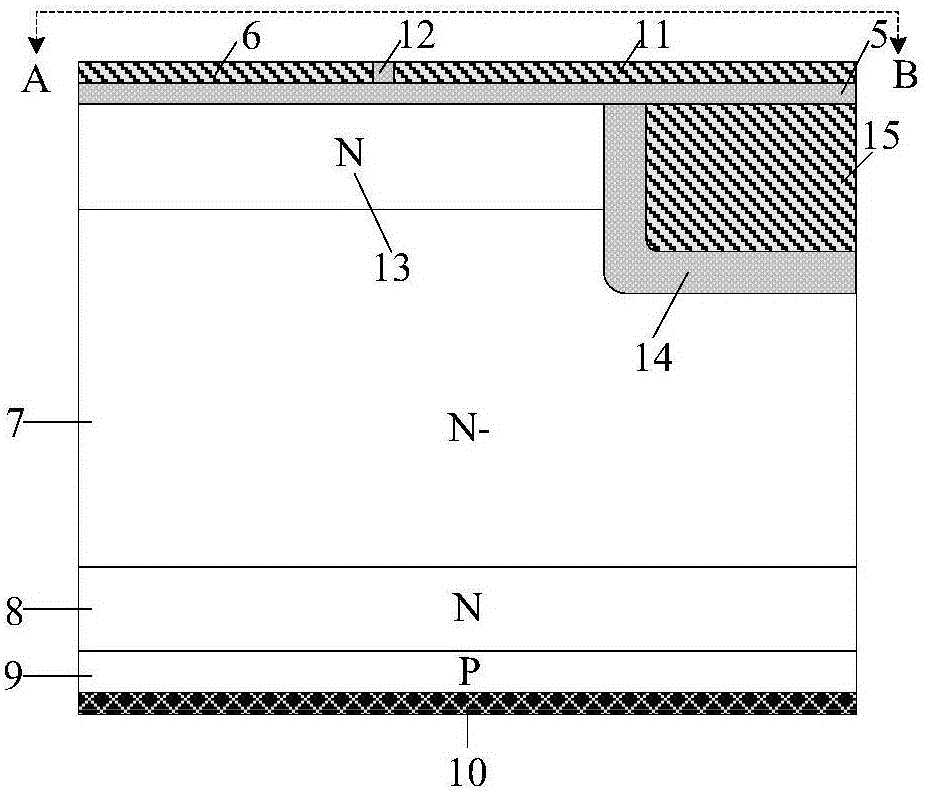

[0051] A planar gate IGBT, its semi-cellular structure and the section along the AB line are as follows figure 2 and image 3As shown, it includes: the back collector metal 10, the P-type collector region 9, the N-type field stop layer 8 and the N-drift region 7 are stacked sequentially from bottom to top; it is characterized in that the upper layer of the N-drift region 7 There is also an N-type layer 13, the doping concentration of the N-type layer 13 is greater than the doping concentration of the N-drift region 7; the two sides of the upper layer of the N-type layer 13 have a p-type base region 4, and the p-type base region 4. The upper layer has mutually independent N+ emitter regions 3 and P+ emitter regions 2; the N-type layer 13 on one side along the longitudinal direction also has a groove structure composed of a first dielectric layer 14 and a first electrode 15, the The depth of the trench structure is greater than the depth of the N-type layer 13 and penetrates t...

Embodiment 2

[0053] A planar gate IGBT, its semi-cellular structure and the section along the AB line are as follows Figure 4 and Figure 5 As shown, on the basis of Example 1, there is also a p-type buried layer with a width of 20-30 microns in the N-type layer 13 between the p-type base regions 4 parallel to the length direction of the MOS channel. Layer 16, the thickness of the p-type buried layer 16 is less than the thickness of the p-type base region 4; in the direction perpendicular to the length of the MOS channel, the p-type buried layer 16 is located at the opposite end of the trench structure, and its width 1-5 microns. The existence of the p-type buried layer 16 has further shielded the influence of the n-type layer 13 on the breakdown voltage of the device, and a high concentration of the n-type layer 13 can be used; simultaneously, the existence of the p-type buried layer 16 also affects the second dielectric layer 5 on its top. It has the function of electric field shieldi...

Embodiment 3

[0055] A plane gate IGBT, its section along the AB line is as follows Figure 6 As shown, on the basis of Embodiment 2, the p-type buried layer 16 is discontinuous and evenly distributed in the n-type layer 13 in the direction perpendicular to the length of the MOS channel. The discontinuous and evenly distributed p-type buried layer 16 can provide better electric field shielding effect and reduce the negative impact on conduction characteristics.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More