Air-gap grapheme transistor and manufacturing method thereof

A graphene and air-gap technology, applied in semiconductor/solid-state device manufacturing, electrical components, semiconductor devices, etc., can solve the problem of reducing graphene carrier mobility, degrading the electrical properties of graphene transistors, and inability to deposit gate dielectrics, etc. question

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

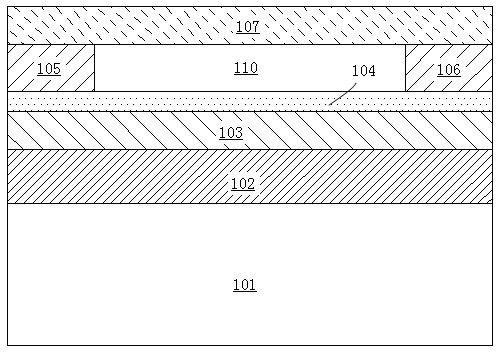

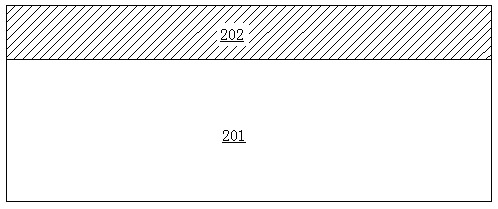

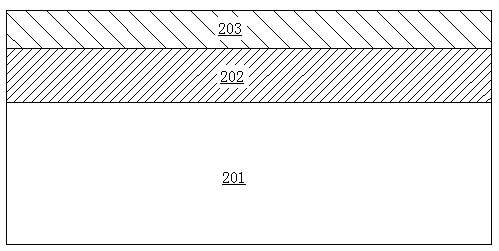

[0031] Exemplary embodiments of the present invention will be described in detail below with reference to the accompanying drawings. In the drawings, the thicknesses of layers and regions are exaggerated for convenience of illustration, and the shown sizes do not represent actual sizes. The referenced figures are schematic illustrations of idealized embodiments of the invention, and the illustrated embodiments of the invention should not be construed as limited to the particular shapes of regions illustrated in the figures but are to include resulting shapes, such as manufacturing-induced deviations. The representations in the figures are schematic, but this should not be considered as limiting the scope of the invention. Meanwhile, in the following description, the term substrate used can be understood to include the semiconductor substrate being processed, possibly including other thin film layers prepared thereon.

[0032] figure 1 An embodiment of the air-gap graphene tr...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More